등록특허 10-2617435

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2023년12월26일

(11) 등록번호 10-2617435

(24) 등록일자 2023년12월19일

- (51) 국제특허분류(Int. Cl.)

*H02M 7/00* (2006.01) *H02M 7/5387* (2007.01)

- (52) CPC특허분류

*H02M 7/003* (2021.05)

*H02M 7/5387* (2013.01)

- (21) 출원번호 10-2018-7006703

- (22) 출원일자(국제) 2016년09월08일

심사청구일자 2020년09월29일

- (85) 번역문제출일자 2018년03월08일

- (65) 공개번호 10-2018-0050661

- (43) 공개일자 2018년05월15일

- (86) 국제출원번호 PCT/JP2016/004105

- (87) 국제공개번호 WO 2017/043088

국제공개일자 2017년03월16일

- (30) 우선권주장

JP-P-2015-177757 2015년09월09일 일본(JP)

- (56) 선행기술조사문헌

JP2000152662 A\*

JP2006019367 A\*

US20100132193 A1\*

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

고오슈우하네쓰렌 가부시기가이샤

일본국 도쿄도 시나가와구 히가시고탄다 2초메 1

7반 1고

- (72) 발명자

카나이, 타카히코

일본 1418639 도쿄 시나가와-구 히가시-고탄다 2

-초메 17-1 고오슈우하네쓰렌 가부시기가이샤 씨

/오

- 스기모토, 마사토

일본 1418639 도쿄 시나가와-구 히가시-고탄다 2

-초메 17-1 고오슈우하네쓰렌 가부시기가이샤 씨

/오

- 요시다, 하루키

일본 1418639 도쿄 시나가와-구 히가시-고탄다 2

-초메 17-1 고오슈우하네쓰렌 가부시기가이샤 씨

/오

- (74) 대리인

허용록

전체 청구항 수 : 총 3 항

심사관 : 광인구

(54) 발명의 명칭 유도 가열 전원 장치

### (57) 요 약

유도 가열 전원 장치는 DC 전력 공급부로부터 출력되는 DC 전력의 맥동 전류를 평활화하는 평활부; 및 평활부에 의해 평활화되는 DC 전력을 AC 전력으로 변환시키는 인버터를 포함한다. 평활부는 인버터에 연결되는 한 쌍의 버스 바들 및 한 쌍의 버스 바들에 연결되는 커페시터를 포함한다. 버스 바들 각각은 전류 흐름 방향으로 연장되는 외부 표면을 포함하며, 외부 표면은 전류 흐름 방향에 수직인 방향으로 외부 표면의 다른 면보다 더 큰 표면 치수를 갖는 평탄 면을 포함한다. 버스 바들은 버스 바들의 평탄 면들이 서로 대향되고 절연체가 버스 바들의 평탄 면들 사이에 개재되는 것과 같은 적층 방식으로 배열된다.

### 대 표 도

(52) CPC특허분류

***H05B 6/04*** (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

유도 가열 전원 장치로서,

DC 전력 공급부로부터 출력되는 DC 전력의 맥동 전류를 평활화하도록 구성되는 평활부; 및

상기 평활부에 의해 평활화되는 상기 DC 전력을 AC 전력으로 변환시키도록 구성되는 인버터를 포함하며,

상기 인버터는 서로 병렬로 연결된 제1 브리지 및 제2 브리지를 포함하고,

상기 평활부는 상기 인버터에 연결되는 한 쌍의 버스 바들, 상기 한 쌍의 버스 바들에 연결되는 적어도 하나의 커페시터, 및 적어도 하나의 연결부를 포함하고,

상기 적어도 하나의 커페시터는 제1 커페시터 및 제2 커페시터를 포함하고, 상기 적어도 하나의 연결부는 제1 연결부 및 제2 연결부를 포함하고,

상기 버스 바들 각각은 전류 흐름 방향으로 연장되는 외부 표면을 포함하고, 상기 외부 표면은 상기 전류 흐름 방향에 수직인 방향으로 상기 외부 표면의 다른 면보다 더 큰 표면 치수를 갖는 적어도 하나의 평탄 면을 포함하며,

상기 한 쌍의 버스 바들은, 상기 한 쌍의 버스 바들의 상기 평탄 면들이 서로 대향하고 절연체가 상기 한 쌍의 버스 바들의 상기 평탄 면들 사이에 개재되는 적층 방식으로 배열되고,

상기 한 쌍의 버스 바들은 상기 제1 연결부 및 상기 제2 연결부를 통해 상기 인버터와 연결되고,

상기 제1 커페시터는 상기 인버터의 상기 한 쌍의 버스 바들을 통해 상기 인버터의 상기 제1 브리지 및 상기 제1 연결부와 연결되고,

상기 제2 커페시터는 상기 한 쌍의 버스 바들을 통해 상기 인버터의 상기 제2 브리지 및 상기 제2 연결부와 연결되고,

상기 제1 연결부 및 상기 제2 연결부 각각은 한 쌍의 컨덕터들 및 절연체를 포함하고,

상기 한 쌍의 컨덕터들은, 상기 한 쌍의 컨덕터들의 상기 평탄 면들이 서로 대향하고, 상기 절연체가 상기 한 쌍의 컨덕터들의 상기 평탄 면들 사이에 개재되는 적층 방식으로 배열되고,

상기 한 쌍의 컨덕터들 중 하나의 베이스 단부는 상기 한 쌍의 컨덕터들 중 상기 하나가 상기 버스 바들로부터 전기적으로 절연되도록 상기 버스 바들 중 하나와 상기 베이스 단부 사이에 상기 절연체가 개재되도록 상기 버스 바들 중 하나에 배열되고,

상기 한 쌍의 컨덕터들 중 다른 하나의 베이스 단부는 상기 한 쌍의 컨덕터들 중 상기 다른 하나가 상기 버스 바들에 전기적으로 결합되도록 상기 버스 바들 중 상기 하나 상에 직접 배열되는 것을 특징으로 하는 유도 가열 전원 장치.

#### 청구항 2

제1항에 있어서,

상기 적어도 하나의 커페시터는 상기 상기 적어도 하나의 커페시터의 일 측 상에 나란히 배열되는 한 쌍의 단자들을 포함하고,

상기 한 쌍의 단자들은 상기 한 쌍의 버스 바들에 연결되어, 상기 한 쌍의 단자들이 상기 버스 바들 및 상기 절연체가 적층되는 방향으로 상기 한 쌍의 버스 바들 및 상기 절연체를 통해 연장되는, 유도 가열 전원 장치.

#### 청구항 3

삭제

## 청구항 4

제2항에 있어서,

상기 제1 연결부 및 상기 제2 연결부 각각에 대해:

상기 컨덕터들 각각은 상기 컨덕터들 각각의 전류 흐름 방향으로 연장되는 외부 표면을 포함하고, 상기 외부 표면은 상기 컨덕터들 각각의 전류 흐름 방향에 수직인 방향으로 상기 외부 표면의 다른 면보다 더 큰 표면 치수를 갖는 적어도 하나의 평탄 면을 포함하는

유도 가열 전원 장치.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 유도 가열 전원 장치에 관한 것이다.

### 배경 기술

[0002]

유도 가열은 강재들(steel workpieces)의 가공 처리에서 가열 방법으로 사용된다. 유도 가열에서, AC 전력을 가열 코일이 자기 필드를 생성하게 하기 위해 가열 코일에 인가되고, 자기 필드에 배치되는 공작물은 공작물에 유도되는 전류에 의해 가열된다.

[0003]

AC 전력을 그러한 가열 코일에 공급하기 위한 종래 기술의 전원 장치는 상용 전원의 AC 전력을 DC 전력으로 변환시키는 컨버터, DC 전력의 맥동 전류를 평활화하는 커패시터, 및 가열 코일에 공급될 고주파 AC 전력을 생성하기 위해 평활화된 DC 전력을 AC 전력으로 다시 변환시키는 인버터를 갖는다(예를 들어, JP 2009-277577A 참조).

[0004]

인버터는 전형적으로 고주파 AC 전력을 생성하기 위해 고속 스위칭 동작을 수행할 수 있는 복수의 전력 반도체 디바이스들을 포함하는 브리지 회로를 갖는다.

### 발명의 내용

#### 해결하려는 과제

[0005]

전력 반도체 디바이스의 고속 스위칭 동작은 전력 반도체 디바이스에 흐르는 전류의 급격한 변화를 야기한다. 전류 변화( $di/dt$ )는 전력 반도체 디바이스와 전압 소스의 역할을 하는 커패시터 사이의 도전성 경로의 기생 인덕턴스(L)로 인해 전력 반도체 디바이스의 단자들 사이에 서지 전압( $Lxdi/dt$ )을 생성한다.

[0006]

과도한 서지 전압은 전력 반도체 디바이스에 손상을 야기한다. 전류 변화( $di/dt$ )는 주로 전력 반도체 디바이스의 특성에 의해 결정된다. 따라서, 기생 인덕턴스(L)를 감소시키는 것은 서지 전압을 억제하는 방법이다.

[0007]

본 발명의 예시적인 양태들은 서지 전압이 인버터의 보호를 개선하기 위해 억제되는 유도 가열 전원 장치를 제공한다.

#### 과제의 해결 수단

[0008]

본 발명의 예시적인 양태에 따르면, 유도 가열 전원 장치는 DC 전력 공급부로부터 출력되는 DC 전력의 맥동 전류를 평활화하도록 구성되는 평활부, 및 평활부에 의해 평활화되는 DC 전력을 AC 전력으로 변환시키도록 구성되는 인버터를 포함한다. 평활부는 인버터에 연결되는 한 쌍의 버스 바들 및 한 쌍의 버스 바들에 연결되는 적어도 하나의 커패시터를 포함한다. 버스 바들 각각은 전류 흐름 방향으로 연장되는 외부 표면을 갖는다. 외부 표면은 전류 흐름 방향에 수직인 방향으로 외부 표면의 다른 면보다 더 큰 표면 치수를 갖는 적어도 하나의 평탄 면을 포함한다. 한 쌍의 버스 바들은 한 쌍의 버스 바들의 평탄 면들이 서로 대향되고 절연체가 한 쌍의 버스 바들의 평탄 면들 사이에 개재되는 것과 같은 적층 방식으로 배열된다.

#### 도면의 간단한 설명

[0009]

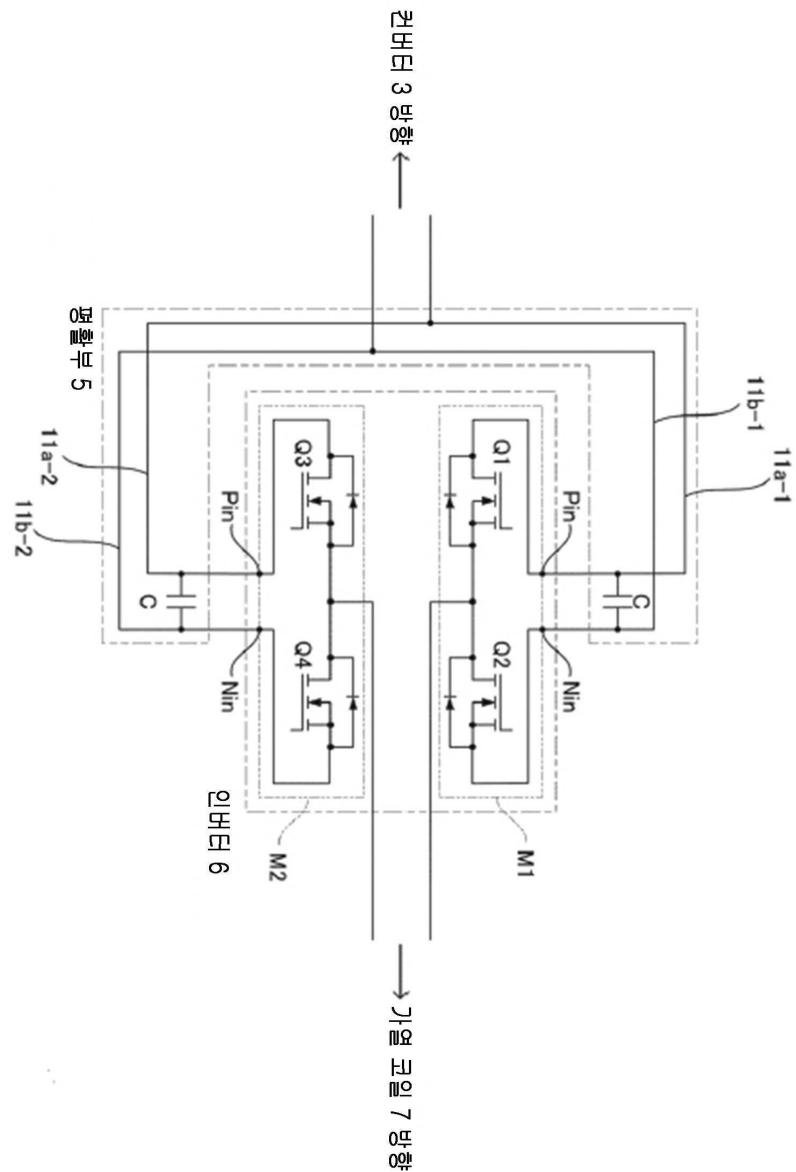

도 1은 본 발명의 일 실시예에 따른 유도 가열 전원 장치의 회로도이다.

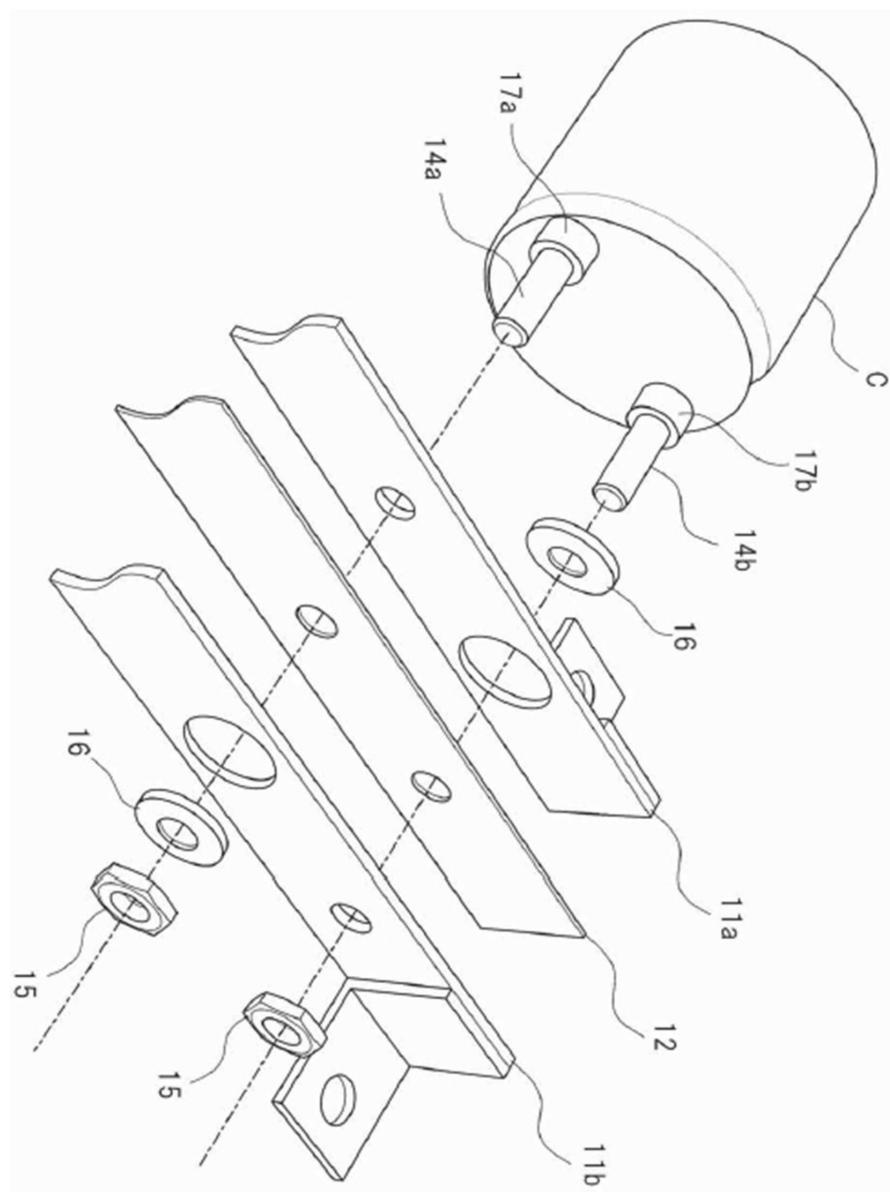

도 2는 도 1의 유도 가열 전원 장치의 평활부의 구성의 일 예를 예시하는 사시도이다.

도 3은 도 2의 평활부의 분해 사시도이다.

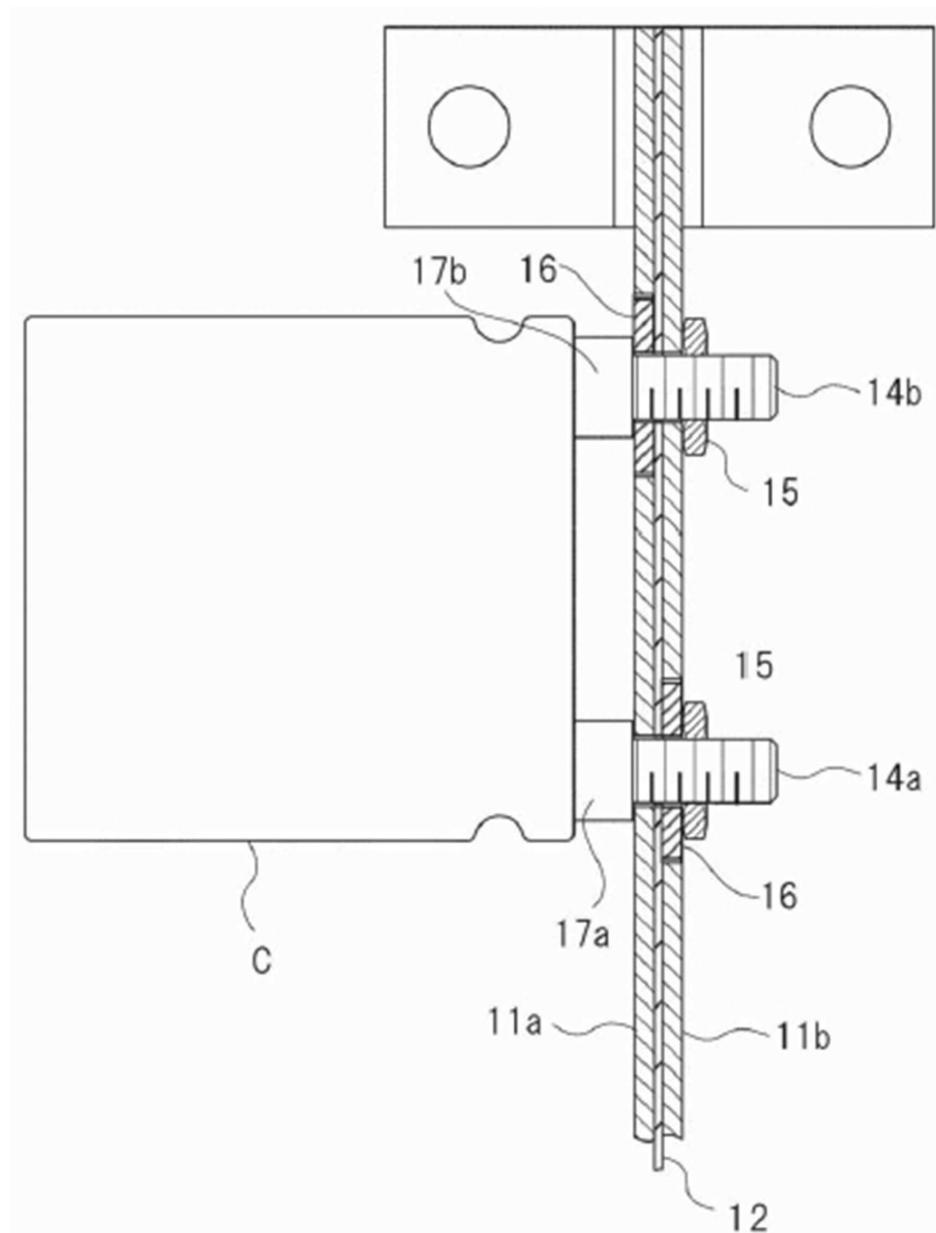

도 4는 도 2의 평활부의 단면도이다.

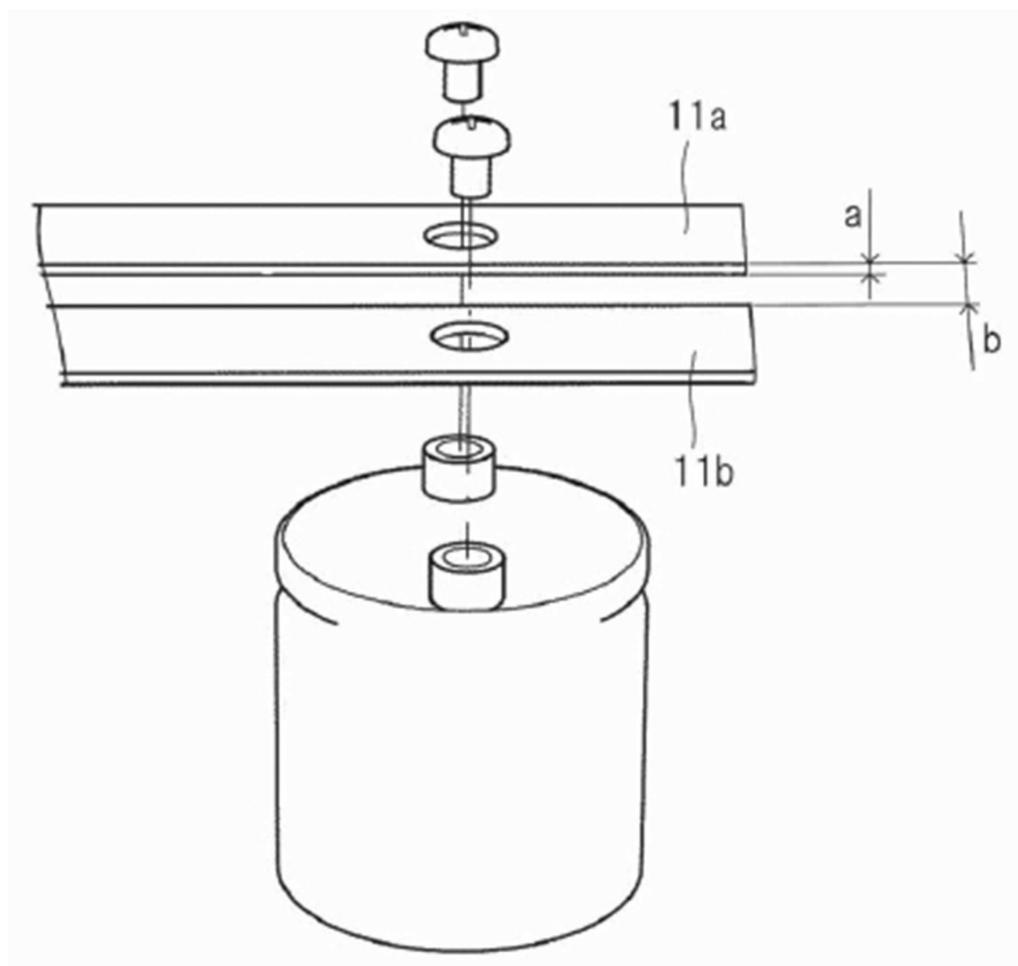

도 5는 평활부의 참고 예의 사시도이다.

도 6은 평활부의 다른 참고 예의 사시도이다.

도 7은 본 발명의 다른 실시예에 따른 유도 가열 전원 장치의 회로도이다.

도 8은 본 발명의 다른 실시예에 따른 유도 가열 전원 장치의 회로도이다.

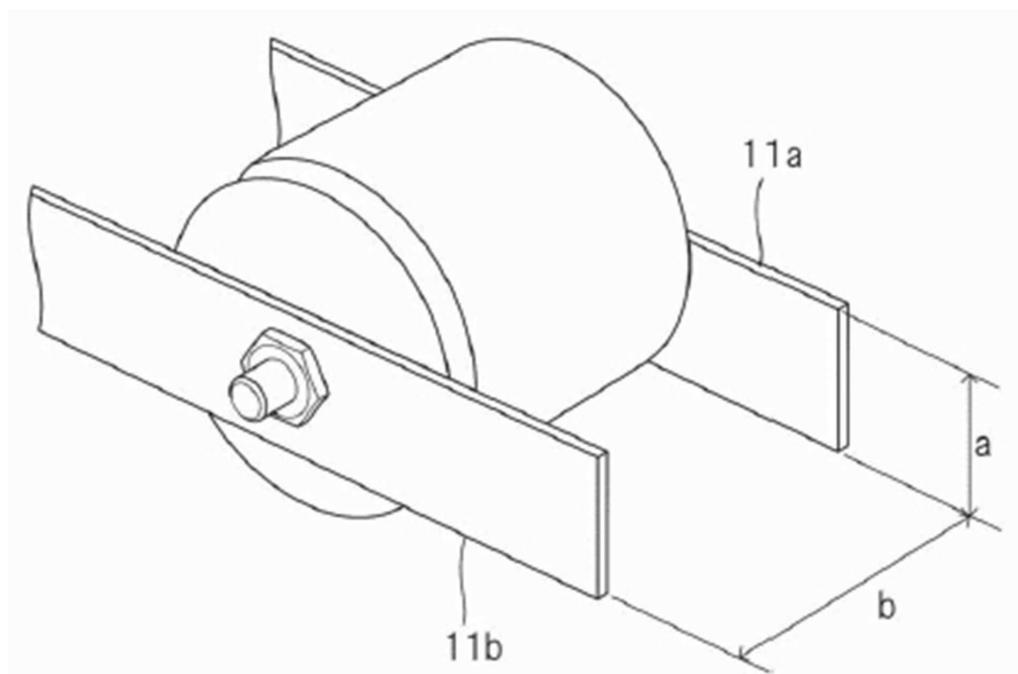

도 9는 도 8의 유도 가열 전원 장치의 평활부의 구성의 일 예를 예시하는 사시도이다.

도 10은 도 9의 평활부의 단면도이다.

도 11은 본 발명의 다른 실시예에 따른 유도 가열 전원 장치의 회로도이다.

### 발명을 실시하기 위한 구체적인 내용

[0010]

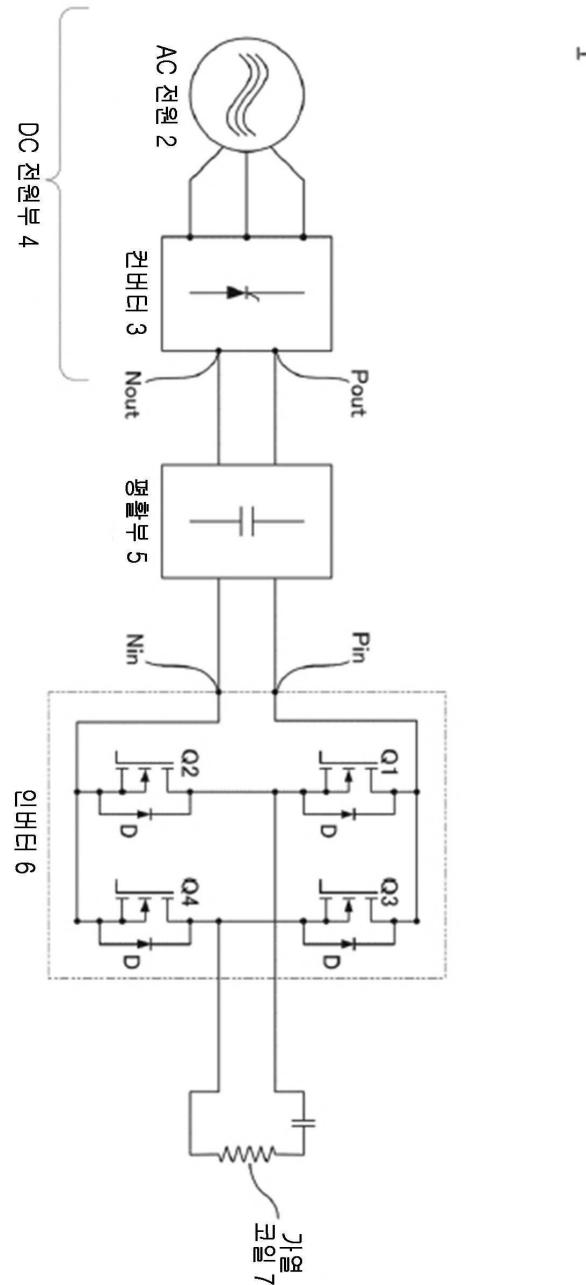

도 1은 본 발명의 일 실시예에 따른 유도 가열 전원 장치(1)를 예시한다.

[0011]

유도 가열 전원 장치(1)는 DC 전력 공급부(4), 평활부(5) 및 인버터(6)를 갖는다. DC 전력 공급부(4)는 상용 AC 전력 공급(2)으로부터 공급되는 AC 전력을 DC 전력으로 변환시키도록 구성되는 컨버터(3)를 포함한다. 평활부(5)는 DC 전력 공급부(4)로부터 출력되는 DC 전력의 맥동 전류를 평활화하도록 구성된다. 인버터(6)는 평활부(5)에 의해 평활화되는 DC 전력을 고주파 AC 전력으로 변환시키도록 구성된다.

[0012]

인버터(6)는 직렬로 연결되는 전력 반도체 디바이스들(Q1, Q2)을 포함하는 아암, 및 직렬로 또한 연결되는 전력 반도체 디바이스들(Q3, Q4)을 포함하는 다른 아암을 갖는다. 인버터(6)는 풀 브리지 회로로 구성됨으로써 아암들 각각의 전력 반도체 디바이스들 사이의 직렬 연결 포인트가 출력 단자의 역할을 한다. 프리휠 다이오드들(Freewheel diodes)(D)은 전력 반도체 디바이스들(Q1, Q2, Q3, Q4) 각각과 병렬로 연결된다.

[0013]

예를 들어, 스위칭 동작을 수행할 수 있는 다양한 전력 반도체 디바이스들, 예컨대 절연 게이트 양극성 트랜지스터(insulated gate bipolar transistor (IGBT)) 및 금속 산화물 반도체 전계 효과 트랜지스터(metal-oxide-semiconductor field-effect transistor(MOSFET))는 각각의 전력 반도체 디바이스로 사용될 수 있다. 전력 반도체 디바이스의 재료의 예들은 실리콘(Si) 및 실리콘 카바이드(SiC)를 포함할 수 있다.

[0014]

가열 코일(7)이 전력 반도체 디바이스들(Q1, Q2)의 직렬 연결 포인트와 전력 반도체 디바이스들(Q3, Q4)의 직렬 연결 포인트 사이에 연결됨으로써 고주파 전력이 전력 반도체 디바이스들(Q1, Q2, Q3, Q4)의 스위칭 동작들에 의해 가열 코일(7)에 공급된다.

[0015]

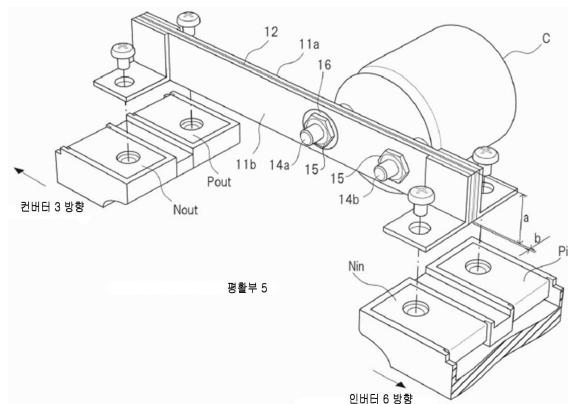

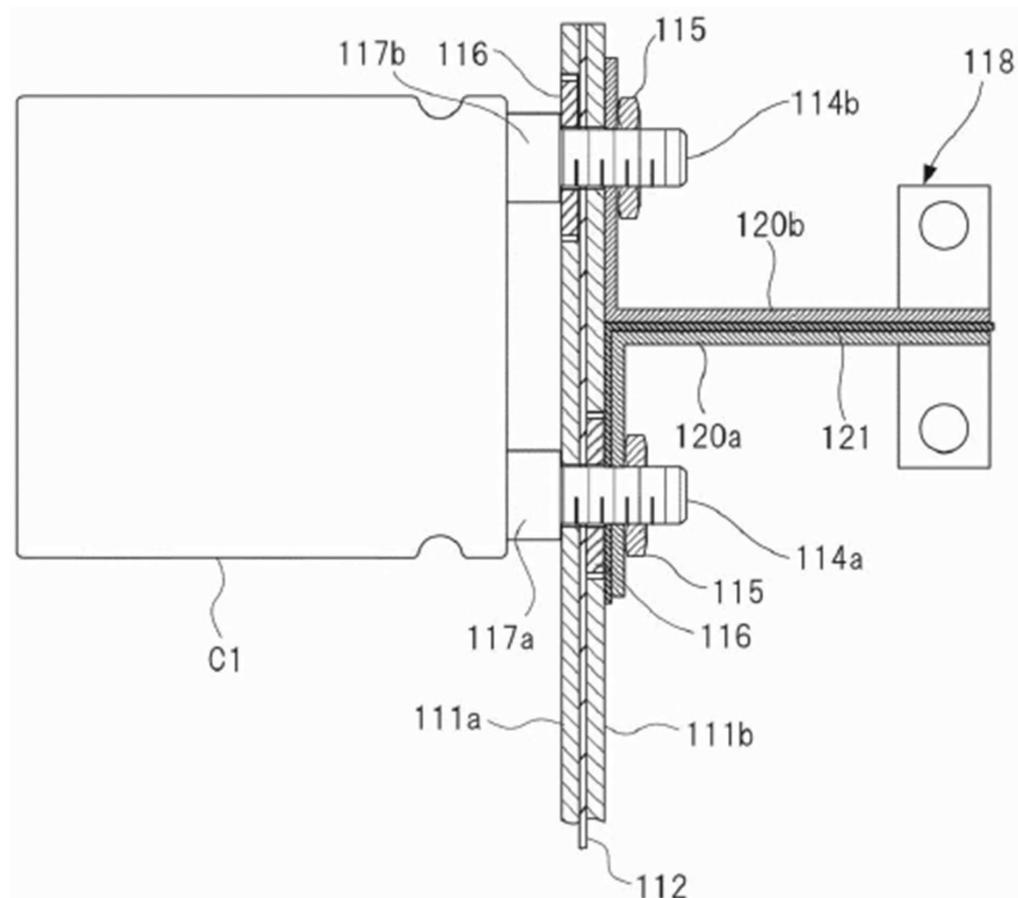

도 2 내지 도 4는 평활부(5)의 구성의 일 예를 예시한다.

[0016]

평활부(5)는 한 쌍의 버스 바들(11a, 11b), 및 한 쌍의 버스 바들(11a, 11b)에 연결되는 적어도 하나의 커페시터(C)를 포함한다.

[0017]

버스 바들(11a, 11b) 각각은 한 쌍의 평탄 플레이트 면들 및 한 쌍의 평탄 사이드 면들을 갖는 평탄 플레이트 컨덕터이며, 한 쌍의 평탄 플레이트 면들 및 한 쌍의 평탄 사이드 면들은 전류 흐름 방향(종 방향)으로 연장되는 컨덕터의 외부 표면을 형성한다. 버스 바들(11a, 11b)은 전류 흐름 방향에 수직인 방향(폭 방향)으로 비교적 큰 표면 치수를 갖는 버스 바들(11a, 11b)의 평탄 플레이트 면들 또는 버스 바들(11a, 11b)의 평탄 사이드 면들이 서로 대향되고 절연체 시트(12)가 버스 바들(11a, 11b) 사이에 개재되는 것과 같은 적층 방식으로 배열된다.

[0018]

버스 바(11a)의 일 단부는 컨버터(3)의 출력 단자의 양극(Pout)에 연결되는 반면에 버스 바(11a)의 타 단부는 인버터(6)의 입력 단자의 양극(Pin)에 연결된다. 버스 바(11b)의 일 단부는 컨버터(3)의 출력 단자의 음극(Nout)에 연결되는 반면에 버스 바(11b)의 타 단부는 인버터(6)의 입력 단자의 음극(Nin)에 연결된다.

[0019]

버스 바들(11a, 11b)에 연결되는 커페시터(C)의 한 쌍의 단자들(14a, 14b)은 나사 단자들로 형성되고 커페시터(C)의 일 측 상에 나란히 배열된다. 단자들(14a, 14b)은 버스 바들(11a, 11b) 및 절연체(12)들이 버스 바(11a), 절연체(12) 및 버스 바(11b)의 순서로 적층되는 방향으로 버스 바들(11a, 11b) 및 절연체(12)를 통해 연장되도록 배열된다. 너트들(15)이 단자들(14a, 14b) 각각의 원위 단부들 상으로 나사 고정됨으로써 커페시터

(C)는 버스 바들(11a, 11b)에 고정된다.

[0020] 도 3 및 도 4에 도시된 바와 같이, 단자(14a) 및 단자(14a)에 나사 고정되는 너트(15)는 절연 와셔(16)에 의해 버스 바(11b)로부터 전기적으로 절연된다. 반면에, 단자(14a)의 베이스 단부에 형성되는 대구경 플랜지부(17a)가 버스 바(11a)와 접촉함으로써 단자(14a) 및 버스 바(11a)는 서로 전기적으로 결합된다. 따라서, 단자(14a)는 버스 바(11a)에만 연결된다.

[0021] 단자(14b) 및 단자(14b)의 베이스 단부에 형성되는 대구경 플랜지부(17b)는 절연 와셔(16)에 의해 버스 바(11a)로부터 전기적으로 절연된다. 반면에, 단자(14b)에 나사 고정되는 너트(15)가 버스 바(11b)와 접촉함으로써 단자(14b) 및 버스 바(11b)는 너트(15)를 통해 서로 전기적으로 결합된다. 따라서, 단자(14b)는 버스 바(11b)에만 연결된다.

[0022] 도 5 및 도 6은 각각 평활부(5)의 참조 예들을 예시한다.

[0023] 도 5에 도시된 예에서, 한 쌍의 버스 바들(11a, 11b)은 버스 바들(11a, 11b)의 사이드 면들이 서로 대향하도록 배열된다. 도 6에 도시된 예에서, 한 쌍의 버스 바들(11a, 11b)은 버스 바들(11a, 11b)의 플레이트 면들이 커패시터가 버스 바들(11a, 11b) 사이에 개재된 채 서로 대향되도록 배열된다. 도 6에 도시된 예에서, 한 쌍의 단자들 중 하나는 커패시터의 일 측 상에 제공되고 다른 단자는 커패시터의 대향 측 상에 제공된다.

[0024] 한 쌍의 평행한 평탄 플레이트 컨덕터들의 인덕턴스는  $b/a$ 와 연관되며, 여기서 “a”는 한 쌍의 평행한 평탄 플레이트 컨덕터들의 대향 면들의 폭, 즉 컨덕터들의 연장 방향(전류의 흐름 방향)에 수직인 방향의 치수, 및 “b”는 컨덕터들의 대향 면들 사이의 거리이다. 보다 구체적으로, 인덕턴스는  $b/a$  가 더 작아짐에 따라 더 작아진다. 대향 면들의 폭 “a”가 일정하면, 인덕턴스는 대향 면들 사이의 거리 “b”가 더 작아짐에 따라 더 작아진다. 대향 면들 사이의 거리 “b”가 일정하면, 인덕턴스는 대향 면들의 폭 “a”가 더 커짐에 따라 더 작아진다.

[0025] 도 2 내지 도 4에 도시된 바와 같이, 버스 바들(11a, 11b)은 버스 바들(11a, 11b)의 플레이트 면들이 서로 대향되고 절연체 시트(12)가 버스 바들(11a, 11b) 사이에 개재되는 것과 같은 적층 방식으로 배열된다. 이 경우, 한 쌍의 버스 바들(11a, 11b)의 사이드 면들이 서로 대향되는 도 5에 도시된 참고 예와 비교하여, 한 쌍의 버스 바들(11a, 11b)의 대향 면들의 폭 “a”가 더 커짐에 따라 한 쌍의 버스 바들(11a, 11b)의 인덕턴스는 감소된다.

[0026] 더욱이, 한 쌍의 버스 바들(11a, 11b)의 플레이트 면들이 서로 대향되고 커패시터가 버스 바들(11a, 11b) 사이에 개재되는 도 6에 도시된 참고 예와 비교하여, 한 쌍의 버스 바들(11a, 11b)의 대향 면들 사이의 거리 “b”가 더 짧아짐에 따라 한 쌍의 버스 바들(11a, 11b)의 인덕턴스는 추가로 감소된다.

[0027] 따라서, 한 쌍의 버스 바들(11a, 11b)의 플레이트 면들이 서로 대향되고 절연체 시트(12)가 버스 바들(11a, 11b) 사이에 개재되는 것과 같은 적층 방식으로 버스 바들(11a, 11b)을 배열함으로써, 커패시터(C)와 DC 전력이 커패시터(C)로부터 공급되는 전력 반도체 디바이스들(Q1, Q2, Q3, Q4) 사이의 도전성 경로의 기생 인덕턴스가 감소될 수 있다. 따라서, 기생 인덕턴스로 인해 전력 반도체 디바이스들(Q1, Q2, Q3, Q4)의 대향 단자들 사이에 발생하는 서지 전압이 억제됨으로써 인버터(6)의 보호는 개선된다.

[0028] 전해 커패시터보다 내부 인덕턴스에서 더 작은 필름 커패시터, 세라믹 커패시터 등등이 커패시터(C)로서 사용되는 것이 바람직하다.

[0029] 하나의 커패시터(C)가 위에 설명되는 예들에서 한 쌍의 버스 바들(11a, 11b)에 연결되지만, 복수의 커패시터들(C)이 별별로 한 쌍의 버스 바들(11a, 11b)에 연결될 수 있다.

[0030] 도 7에 도시된 예에서, 전력 반도체 디바이스들(Q1, Q2)을 포함하는 아암 및 전력 반도체 디바이스들(Q3, Q4)을 포함하는 아암은 각각 모듈로서 구성된다. 전력 반도체 디바이스들(Q1, Q2)을 포함하는 제1 모듈(M1)은 한 쌍의 버스 바들(11a-1, 11b-1)에 연결되고, 전력 반도체 디바이스들(Q3, Q4)을 포함하는 제2 모듈(M2)은 한 쌍의 버스 바들(11a-2, 11b-2)에 연결된다. 이 경우, 한 쌍의 버스 바들(11a-1, 11b-1) 및 한 쌍의 버스 바들(11a-2, 11b-2)은 평활부(5)에 제공될 수 있고, 한 쌍의 버스 바들(11a-1, 11b-1) 및 한 쌍의 버스 바들(11a-2, 11b-2) 각각은 위에 설명된 한 쌍의 버스 바들(11a, 11b)과 같이, 한 쌍의 버스 바들이 절연체 시트(12)가 한 쌍의 버스 바들의 플레이트 면들 사이에 개재되는 적층 방식으로 배열되는 것과 같이 구성될 수 있다. 적어도 하나의 커패시터(C)가 한 쌍의 버스 바들(11a-1, 11b-1)에 연결되고, 적어도 하나의 커패시터(C)가 한 쌍의 버스 바들(11a-2, 11b-2)에 연결된다.

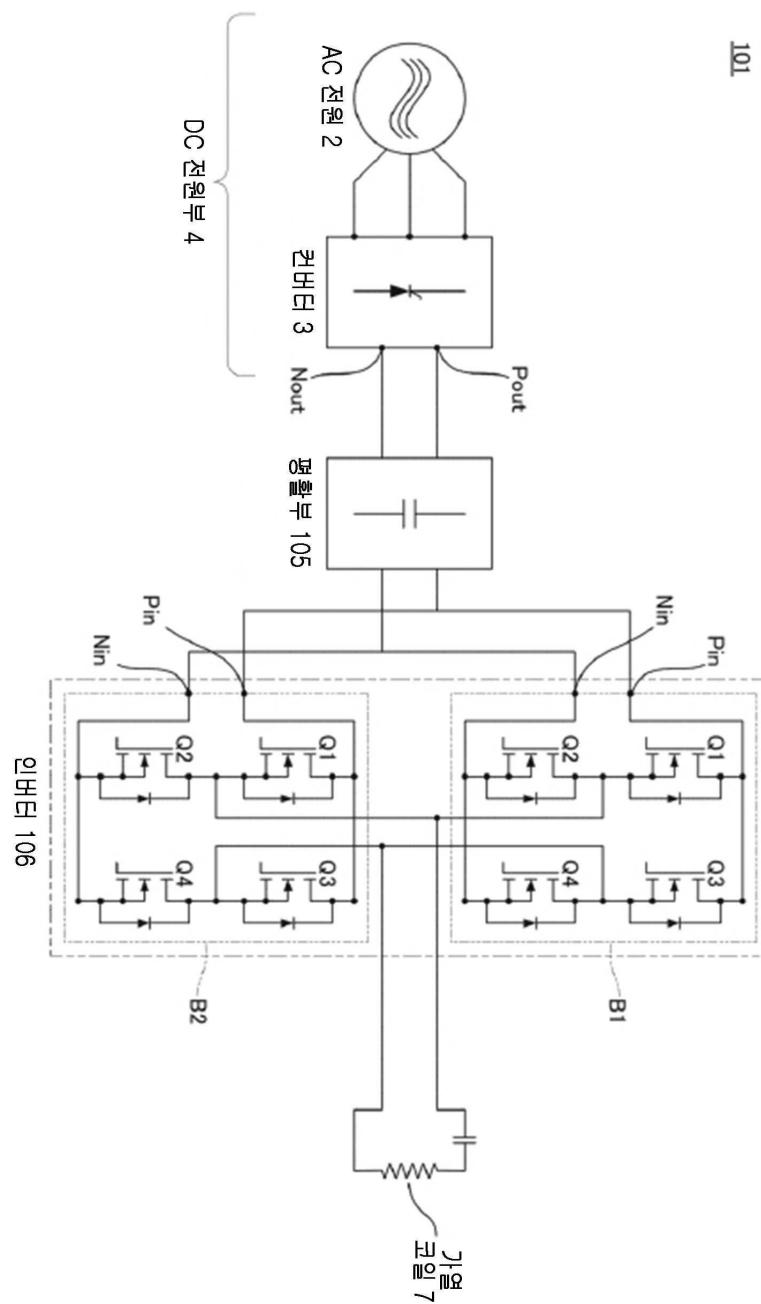

[0031] 도 8은 본 발명의 다른 실시예에 따른 유도 가열 전원 장치(101)를 예시한다. 위에 설명된 유도 가열 전원 장치

(1)의 요소들과 동일한 유도 가열 전원 장치(101)의 요소들은 동일한 참조 부호들로 표시되고 그 설명은 생략되거나 간략화될 것이다.

[0032] 유도 가열 전원 장치(101)는 DC 전력 공급부(4), 평활부(105), 및 인버터(106)를 포함한다. DC 전력 공급부(4)는 AC 전력 공급(2) 및 컨버터(3)를 포함한다. 평활부(105)는 DC 전력 공급부(4)로부터 출력되는 DC 전력의 맥동 전류를 평활화하도록 구성된다. 인버터(106)는 평활부(105)에 의해 평활화되는 DC 전력을 고주파 AC 전력으로 변환시키도록 구성된다.

[0033] 한 세트의 전력 반도체 디바이스들(Q1, Q2, Q3, Q4)에 의해 각각 형성되는 복수의 브리지 회로들은 인버터(106)에 제공된다. 예시된 예에서, 2개의 브리지 회로들, 즉 제1 브리지(B1) 및 제2 브리지(B2)는 인버터에 제공된다. 제1 브리지(B1) 및 제2 브리지(B2)가 병렬로 가열 코일(7)에 연결됨에 따라 가열 코일(7)에 공급될 전력은 제1 브리지(B1) 및 제2 브리지(B2)로 분배될 수 있다.

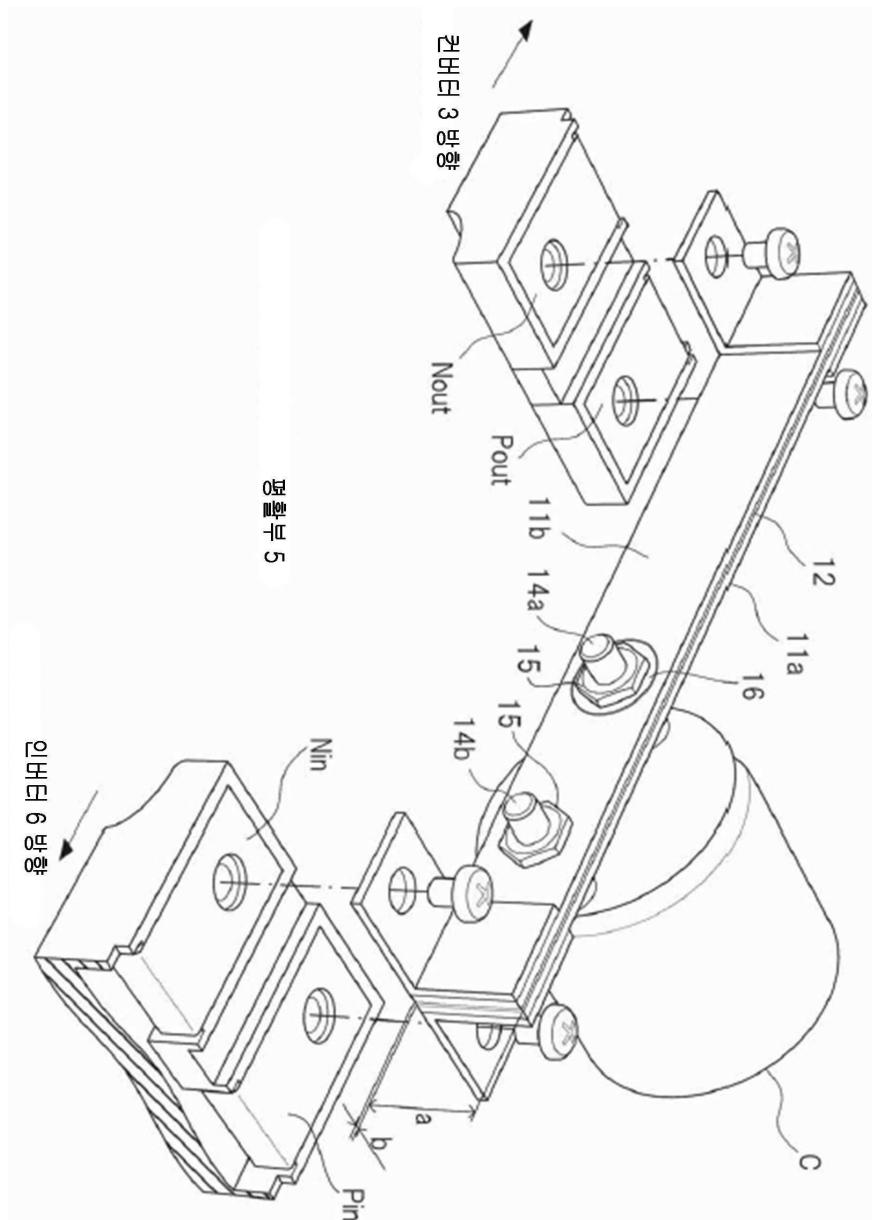

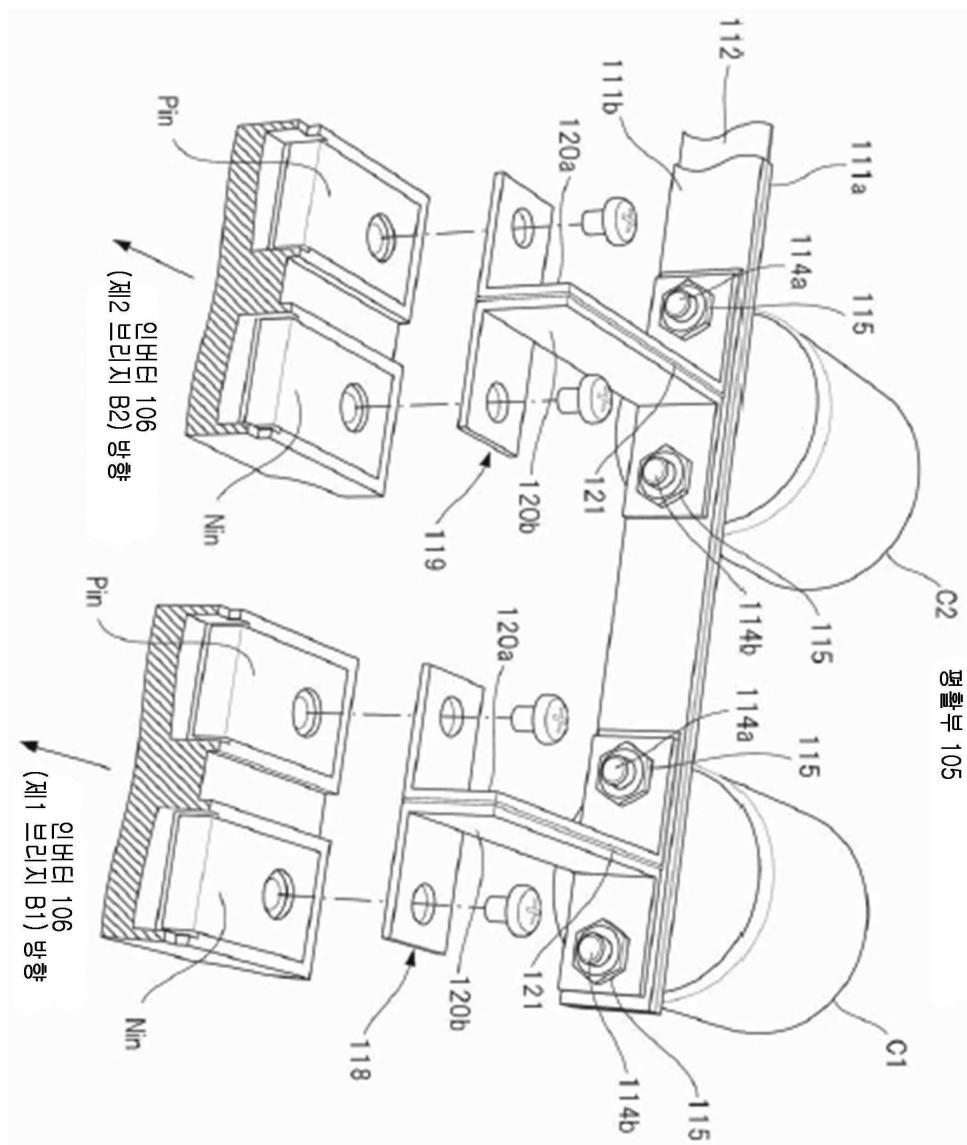

[0034] 도 9 및 도 10은 평활부(105)의 구성 예 도시한다.

[0035] 평활부(105)는 한 쌍의 버스 바들(111a, 111b), 커패시터들(C1, C2) 및 연결부들(118, 119)을 포함한다. 커패시터들(C1, C2)은 한 쌍의 버스 바들(111a, 111b)에 연결된다. 한 쌍의 버스 바들(111a, 111b)은 연결부들(118, 119)을 통해 인버터(106)에 연결된다.

[0036] 한 쌍의 버스 바들(111a, 111b) 각각은 한 쌍의 평탄 플레이트 면들 및 한 쌍의 평탄 사이드 면들을 갖는 평탄 플레이트 컨덕터이며, 한 쌍의 평탄 플레이트 면들 및 한 쌍의 평탄 사이드 면들은 전류 흐름 방향(종 방향)으로 연장되는 컨덕터의 외부 표면을 형성한다. 버스 바들(111a, 111b)은 전류 흐름 방향에 수직인 방향(폭 방향)으로 비교적 큰 표면 치수를 갖는, 버스 바들(111a, 111b)의 평탄 플레이트 면들 또는 버스 바들(111a, 111b)의 평탄 사이드 면들이 서로 대향되고 절연체 시트(112)가 버스 바들(111a, 111b) 사이에 개재되는 것과 같은 적층 방식으로 배열된다. 이러한 방식에서, 버스 바들(111a, 111b)의 인덕턴스는 위에 설명된 평활부(5)의 한 쌍의 버스 바들(111a, 111b)과 같이, 감소될 수 있다.

[0037] 연결부들(118, 119)은 인버터(106)의 브리지 회로들에 대해 각각 제공된다. 연결부(118)는 제1 브리지(B1)에 연결된다. 연결부(119)는 제2 브리지(B2)에 연결된다.

[0038] 연결부(118)는 한 쌍의 평탄 플레이트 컨덕터들(120a, 120b), 및 절연체 시트(121)를 포함한다. 한 쌍의 컨덕터들(120a, 120b) 각각은 한 쌍의 평탄 플레이트 면들 및 한 쌍의 평탄 사이드 면들을 가지며, 한 쌍의 평탄 플레이트 면들 및 한 쌍의 평탄 사이드 면들은 그 전류 흐름 방향으로 연장되는 컨덕터의 외부 표면을 형성한다. 한 쌍의 컨덕터들(120a, 120b)은 전류 흐름 방향에 수직인 방향으로 비교적 큰 표면 치수를 갖는, 컨덕터들(120a, 120b)의 평탄 플레이트 면들 또는 컨덕터들(120a, 120b)의 평탄 사이드 면들이 서로 대향되고 절연체(121)가 컨덕터들(120a, 120b) 사이에 개재되는 것과 같은 적층 방식으로 배열된다. 컨덕터(120a)의 베이스 단부는 절연체(121)가 버스 바(111b)와 컨덕터(120a)의 베이스 단부 사이에 개재되도록 버스 바(111b) 상에 배열된다. 따라서, 컨덕터(120a) 및 버스 바(111b)는 서로 전기적으로 절연된다. 컨덕터(120b)의 베이스 단부는 버스 바(111b) 상에 직접 배열된다. 따라서, 컨덕터(120b) 및 버스 바(111b)는 서로 전기적으로 결합된다.

[0039] 연결부(119)는 또한 한 쌍의 평탄 플레이트 컨덕터들(120a, 120b), 및 절연체 시트(121)를 포함한다. 한 쌍의 컨덕터들(120a, 120b)은 컨덕터들(120a, 120b)의 플레이트 면들이 서로 대향되고 절연체(121)가 컨덕터들(120a, 120b) 사이에 개재되는 것과 같은 적층 방식으로 배열된다. 컨덕터(120a)의 베이스 단부는 절연체(121)가 버스 바(111b)와 컨덕터(120a)의 베이스 단부 사이에 개재되는 것과 같이 버스 바(111b) 상에 배치된다. 따라서, 컨덕터(120a) 및 버스 바(111b)는 서로 전기적으로 절연된다. 컨덕터(120b)의 베이스 단부는 버스 바(111b) 상에 직접 배열된다. 따라서, 컨덕터(120b) 및 버스 바(111b)는 서로 전기적으로 결합된다.

[0040] 커패시터(C1)의 한 쌍의 단자들(114a, 114b)은 나사 단자들로서 형성되고 커패시터의 일 측 상에 나란히 배열된다. 단자들(114a, 114b)은 버스 바들(111a, 111b) 및 절연체(112)가 버스 바(111a), 절연체(112) 및 버스 바(111b)의 순서로 적층되는 방향으로 버스 바들(111a, 111b) 및 절연체(112)를 통해 연장되도록 배열된다. 단자(114a)의 원위 단부는 버스 바(111b) 상에 배치되는 연결부(118)의 컨덕터(120a) 및 절연체(121)를 통해 더 연장된다. 단자(114b)의 원위 단부는 버스 바(111b) 상에 중첩되는 연결부(118)의 컨덕터(120b)를 통해 더 연장된다. 너트들(115)이 단자들(114a, 114b)의 원위 단부들 상으로 나사 고정됨에 따라 커패시터(C1)는 버스 바들(111a, 111b) 및 연결부(118)에 고정된다.

[0041] 단자(114a) 및 버스 바(111b)는 절연 와셔(116)에 의해 서로 전기적으로 절연된다. 단자(114a)의 베이스 단부에 형성되는 대구경 플랜지부(117a)가 버스 바(111a)와 접촉함으로써 단자(114a) 및 버스 바(111a)는 서로 전기적

으로 결합된다. 게다가, 단자(114a)에 나사 고정되는 너트(115)가 연결부(118)의 컨덕터(120a)와 접촉함에 따라 단자(114a) 및 컨덕터(120a)는 너트(115)를 통해 서로 전기적으로 결합될 수 있다. 따라서, 단자(114a)는 버스 바(111a) 및 컨덕터(120a)에 연결된다.

[0042] 단자(114b) 및 단자(114b)의 베이스 단부에 형성되는 대구경 플랜지부(117b)는 절연 와셔(16)에 의해 버스 바(111a)로부터 전기적으로 절연된다. 반면에, 단자(114b)에 나사 고정되는 너트(115)가 연결부(118)의 컨덕터(120b)와 접촉함으로써 단자(114b)는 너트(115)를 통해 컨덕터(120b) 및 버스 바(111b)에 전기적으로 결합될 수 있다. 따라서, 단자(114b)는 버스 바(111b) 및 컨덕터(120b)에 연결된다.

[0043] 연결부(118)의 컨덕터(120a)의 원위 단부는 제1 브리지(B1)의 입력 단자의 양극(Pin)에 연결된다. 연결부(118)의 컨덕터(120b)의 원위 단부는 제1 브리지(B1)의 입력 단자의 음극(Nin)에 연결된다. DC 전력은 커패시터(C1)로부터 제1 브리지(B1)로 공급된다.

[0044] 커패시터(C2)의 한 쌍의 단자들(114a, 114b)은 커패시터(C1)의 단자들(114a, 114b)과 유사하게, 버스 바들(111a, 111b) 및 연결부(119)에 고정된다. 단자(114a)는 버스 바(111a) 및 컨덕터(120a)에 연결된다. 단자(114b)는 버스 바(111b) 및 컨덕터(120b)에 연결된다.

[0045] 연결부(119)의 컨덕터(120a)의 원위 단부는 제2 브리지(B2)의 입력 단자의 양극(Pin)에 연결된다. 연결부(119)의 컨덕터(120b)의 원위 단부는 제2 브리지(B2)의 입력 단자의 음극(Nin)에 연결된다. DC 전력은 커패시터(C2)로부터 제2 브리지(B2)로 공급된다.

[0046] 한 쌍의 버스 바들(111a, 111b)이 인버터(106)에 연결되는 복수의 연결부들이 인버터(106)의 브리지들에 대해 각각 제공된다. 커패시터들은 연결부들(118, 119) 각각에 연결된다. 이러한 방식으로, 제1 브리지(B1)와 제1 브리지(B1)의 전압 소스인 커패시터(C1) 사이의 도전성 경로의 길이, 및 제2 브리지(B2)와 제2 브리지(B2)의 전압 소스인 커패시터(C2) 사이의 도전성 경로의 길이 둘 다가 단축될 수 있어서 두 도전성 경로들 각각의 기생 인덕턴스는 감소될 수 있다. 따라서, 기생 인덕턴스로 인해 전력 반도체 디바이스들(Q1, Q2, Q3, Q4)의 대향 단자들 사이에 발생하는 서지 전압이 억제될 수 있어서 인버터(106)의 보호는 향상될 수 있다.

[0047] 또한, 컨덕터들(120a, 120b)의 플레이트 면들이 서로 대향되고 절연체 시트(121)가 컨덕터들(120a, 120b) 사이에 개재되는 것과 같은 적층 방식으로 연결부들(118, 119) 각각의 한 쌍의 컨덕터들(120a, 120b)을 배열함으로써, 연결부들(118, 119) 각각의 인덕턴스는 한 쌍의 버스 바들(111a, 111b)과 같이, 감소될 수 있다. 따라서, 기생 인덕턴스로 인해 전력 반도체 디바이스들(Q1, Q2, Q3, Q4)의 대향 단자들에서 발생하는 서지 전압은 인버터(106)를 보호하기 위해 더 억제된다.

[0048] 하나의 커패시터가 위에 설명된 예에서 연결부들(118, 119) 각각에 연결되지만, 복수의 커패시터들이 병렬로 연결부들(118, 119) 각각에 연결될 수 있다.

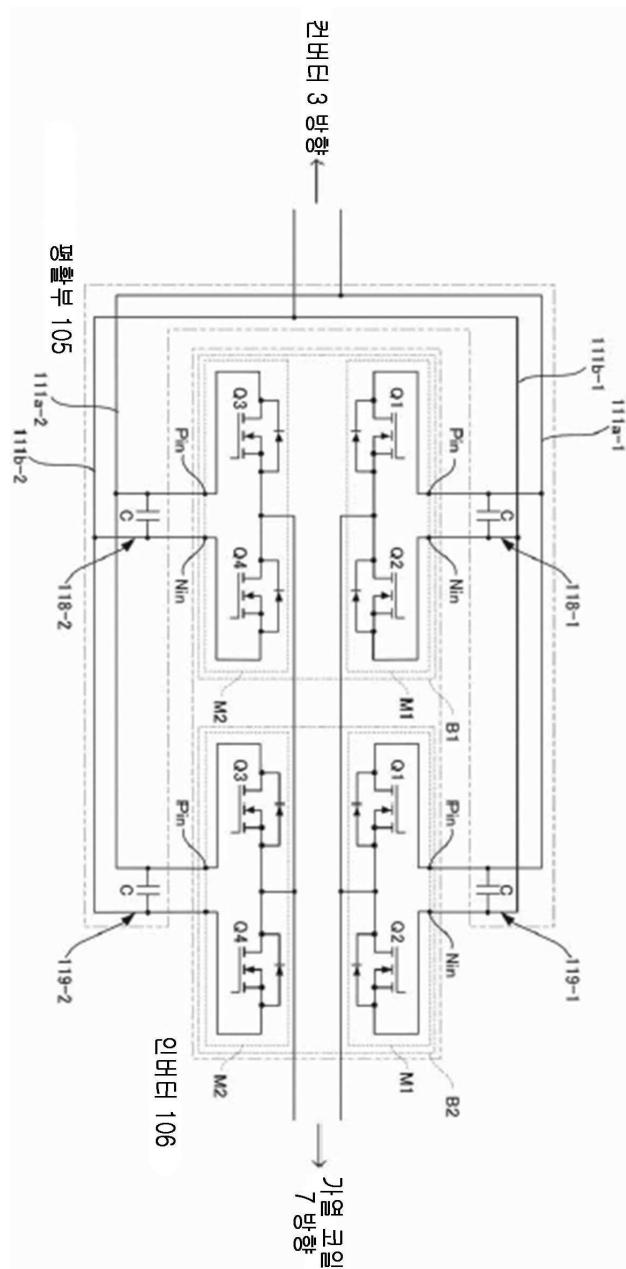

[0049] 도 11에 도시된 예에서, 전력 반도체 디바이스들(Q1, Q2)을 포함하는 각각의 아암 및 전력 반도체 디바이스들(Q3, Q4)을 포함하는 각각의 아암은 각각 모듈로서 구성된다. 전력 반도체 디바이스들(Q1, Q2)을 각각 포함하고 제1 브리지(B1) 및 제2 브리지(B2) 각각에 속하는 제1 모듈들(M1)은 한 쌍의 버스 바들(111a-1, 111b-1)에 연결된다. 전력 반도체 디바이스들(Q3, Q4)을 각각 포함하고 제1 브리지(B1) 및 제2 브리지(B2) 각각에 속하는 제2 모듈들(M2)은 한 쌍의 버스 바들(111a-2, 111b-2)에 연결된다. 이 경우, 한 쌍의 버스 바들(111a-1, 111b-1) 및 한 쌍의 버스 바들(111a-2, 111b-2)은 평활부(105)에 제공될 수 있고, 한 쌍의 버스 바들(111a-1, 111b-1) 및 한 쌍의 버스 바들(111a-2, 111b-2) 각각은 위에 설명된 한 쌍의 버스 바들(111a, 111b)과 같이, 한 쌍의 버스 바들이 절연체가 한 쌍의 버스 바들의 플레이트 면들 사이에 개재되는 적층 방식으로 배열되는 것과 같이 구성될 수 있다. 제1 모듈들(M1)에 대한 연결부들은 개별 모듈 기반으로 한 쌍의 버스 바들(111a-1, 111b-1)에 제공될 수 있고, 제2 모듈들(M2)에 대한 연결부들은 개별 모듈 기반으로 한 쌍의 버스 바들(111a-2, 111b-2)에 제공될 수 있다. 적어도 하나의 커패시터(C)는 한 쌍의 버스 바들(111a-1, 111b-1)에서 연결부들(118-1, 119-1) 각각에 연결된다. 적어도 하나의 커패시터는 한 쌍의 버스 바들(111a-2, 111b-2)에서 연결부들(118-2 및 119-2) 각각에 연결된다.

[0050] 위의 설명에서, 한 쌍의 버스 바들(111a, 111b), 한 쌍의 버스 바들(111a, 111b) 및 컨덕터들(120a, 120b)은 모두 평탄 플레이트들이며, 즉 전류 흐름 방향에 수직인 평면을 따라 취해지는 직사각형 단면을 갖는다. 그러나, 그들 버스 바들은 평탄 플레이트들이 아닐 수 있다. 예를 들어, 그들은 전류 흐름 방향에 수직인 평면에서 반원 단면을 가질 수 있다. 이 경우, 전류 흐름 방향으로 연장되는 버스 바들 각각의 외부 표면은 반원 단면의 직경 부분을 형성하는 평탄 면 및 반원 단면의 원호 부분을 형성하는 반 원통 면을 갖고, 버스 바들은 버스 바들의

평탄 면들이 절연체가 버스 바들의 평탄 면들 사이에 개재된 채 서로 대향되는 것과 같은 적층 방식으로 배열된다.

[0051]

본 출원은 2015년 9월 9일에 출원된 일본 특허 출원 번호 제2015-177757호를 기반으로 하며, 그 전체 내용은 참조로 본원에 통합된다.

## 도면

### 도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

101

도면9

도면10

## 도면11