(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4376388号

(P4376388)

(45) 発行日 平成21年12月2日(2009.12.2)

(24) 登録日 平成21年9月18日(2009.9.18)

(51) Int.Cl.

H01L 23/12 (2006.01)

H01L 21/60 (2006.01)

F 1

H01L 23/12

H01L 21/60 311S

請求項の数 3 (全 17 頁)

(21) 出願番号 特願平11-352757

(22) 出願日 平成11年12月13日(1999.12.13)

(65) 公開番号 特開2001-168231(P2001-168231A)

(43) 公開日 平成13年6月22日(2001.6.22)

審査請求日 平成18年10月27日(2006.10.27)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100094134

弁理士 小山 廣毅

(72) 発明者 佐原 隆一

大阪府高槻市幸町1番1号 松下電子工業

株式会社内

(72) 発明者 戒能 憲幸

大阪府高槻市幸町1番1号 松下電子工業

株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項1】

素子電極が配列された主面と、前記主面の外縁を規定する側面とを有する半導体素子と、

前記半導体素子の前記主面上および前記半導体素子の前記側面上に形成され、前記素子電極を露出する開口部を有する絶縁層と、

前記絶縁層上に形成され、前記開口部内において前記素子電極と電気的に接続された配線層と、

前記配線層のうち前記絶縁層上に形成された部分の上に、形成された外部電極端子とを備え、

前記半導体素子の側面は、前記主面と鈍角をなす斜面であり、

前記斜面は、前記主面に対向する裏面に接続し、

前記斜面上に形成された前記絶縁層は、前記半導体素子の前記裏面に対して垂直な面を有し、前記裏面に対して垂直な前記絶縁層の前記面と前記斜面との距離が前記半導体素子の前記裏面から前記主面へ向かうにつれて大きくなるように形成されている半導体装置。

## 【請求項2】

前記配線層は、前記素子電極と接合されたコンタクト部と、前記絶縁層上において前記外部電極端子と接続されたランド部と、前記絶縁層上において前記コンタクト部と前記ランド部とを電気的に接続する接続配線部とを有している請求項1に記載の半導体装置。

## 【請求項3】

10

20

前記半導体素子の前記裏面上に樹脂層が形成されている請求項 1 または 2 に記載の半導体装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体素子を備えた半導体装置およびその製造方法に関する。特に、半導体素子を保護し、外部装置と半導体素子との電気的な接続を確保する半導体装置およびその製造方法に関する。

【0002】

【従来の技術】

近年、半導体集積回路装置（以下、「半導体装置」と称する。）を搭載した電子機器の小型化及び低価格化の進展は目ざましく、これに伴って、半導体装置に対する小型化及び低価格化の要求が強くなっている。

【0003】

半導体装置の小型化の要求に対して、半導体ウェハから切り出した半導体チップ（ベアチップ）のサイズでパッケージを施した半導体装置（以下、このパッケージ形態または半導体装置を「CSP（チップ・サイズ・パッケージ）」と称する。）が開発された。また、CSPの製造コストの低減を図る目的で、ウェハ状態のまま複数のCSPを製造する技術が開発されている（特開平8-102466号公報参照）。なお、本明細書においては、ウェハ状態のCSPを「ウェハレベルCSP」と呼ぶこととする。また、ダイシング等によって最終的にウェハから切り出されるチップを、ウェハから切り出される前の状態においても、「チップ」と呼ぶこととする。

【0004】

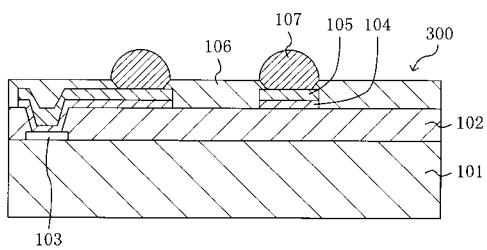

以下、図9を参照しながら、従来のウェハレベルCSPを説明する。図9は、従来のウェハレベルCSP300の一部の断面を模式的に示している。図9ではウェハレベルCSP300の一部を示しているが、ウェハレベルCSP300は、一枚の半導体ウェハにおいて複数形成されている。

【0005】

ウェハレベルCSP300は、半導体ウェハ内に形成された半導体チップ101と、半導体チップ101の主面上に配列された素子電極（電極パット）103と、半導体チップ101の主面上に形成されたパッシベーション膜102と、パッシベーション膜102上に形成され、素子電極103に電気的に接続されたA1配線層104およびNiメッキ層105とを有している。Niメッキ層105の一部には、半田バンプ107が接合されており、パッシベーション膜102上には、A1配線層104およびNiメッキ層105を被覆し、且つ半田バンプ107の一部を露出するカバーコート膜106が形成されている。

【0006】

次に、従来のウェハレベルCSP300の製造方法を説明する。まず、複数の半導体チップ101が形成された半導体ウェハを用意した後、スピンドルコート法を用いて半導体ウェハ上にパッシベーション膜102を形成する。次に、周知の露光技術およびエッチング技術によって、半導体チップ101の主面上に位置する素子電極103を露出する開口部をパッシベーション膜102に形成する。次に、露出した素子電極103に一端が電気的に接続されたA1配線層104をパッシベーション膜102上に形成する。

【0007】

次に、マスクを用いてスパッタなどの薄膜形成技術により、A1配線層104上にNiメッキ層105を形成する。次に、A1配線層104およびNiメッキ層105を被覆するカバーコート膜106をパッシベーション膜102上に形成する。次に、半田バンプ107の接合部位を露出する開口部をパッシベーション膜102に格子状に複数個形成した後、露出した接合部位に半田バンプ107を接合する。このようにして従来のウェハレベルCSP300は製造される。ウェハレベルCSP300のそれぞれを分離すれば、CSPが得られる。

## 【0008】

## 【発明が解決しようとする課題】

しかしながら、従来のウェハレベルCSP300には、次のような問題がある。すなわち、ウェハレベルCSP300を分離して得られるCSPは、半導体チップ101の側面および裏面が露出しているため、機械的な衝撃によってチッピングが起こりやすく、信頼性が乏しい。

## 【0009】

本発明はかかる諸点に鑑みてなされたものであり、その主な目的は、機械的な衝撃から半導体チップを保護することができ、信頼性を向上させた半導体装置およびその製造方法を提供することにある。

10

## 【0010】

## 【課題を解決するための手段】

本発明による半導体装置は、素子電極が配列された正面と、前記正面の外縁を規定する側面とを有する半導体素子と、前記半導体素子の前記正面と前記半導体素子の前記側面上に形成され、前記素子電極を露出する開口部を有する絶縁層と、前記絶縁層上に形成され、前記開口部内において前記素子電極と電気的に接続された配線層と、前記配線層のうち前記絶縁層上に形成された部分の上に形成された外部電極端子とを備え、前記半導体素子は、前記正面と前記側面とのなす角が鈍角となるように、形成されており、これにより上記目的が達成される。

## 【0011】

20

前記配線層は、前記素子電極と接合されたコンタクト部と、前記絶縁層上において前記外部電極端子と接続されたランド部と、前記絶縁層上において前記コンタクト部と前記ランド部とを電気的に接続する接続配線部とを有していることが好ましい。

## 【0012】

前記半導体素子の前記正面に対向する裏面上に樹脂層が形成されていることが好ましい。

## 【0013】

本発明による第2の半導体装置は、素子電極が配列された正面と、前記正面の外縁を規定する側面とを有する半導体素子と、前記半導体素子の前記正面と前記半導体素子の前記側面上に形成され、前記素子電極を露出する開口部を有する絶縁層と、前記絶縁層上に形成され、前記開口部内において前記素子電極と電気的に接続された配線層と、前記半導体素子の前記側面上に位置する絶縁層上に形成された側面配線層と、前記半導体素子の前記正面に対向する裏面の一部分を露出するように前記裏面に設けられた金属層とを備え、前記側面配線層は、前記配線層に電気的に接続されており、前記金属層は、前記側面配線層に電気的に接続されており前記側面配線層を介して前記配線層に電気的に接続されている。

30

## 【0014】

## 【発明の実施の形態】

以下、図面を参照しながら本発明の実施形態を説明する。以下の図面においては、簡単さのために、実質的に同一の機能を有する構成要素を同一の参照符号で示す。

40

## (実施形態1)

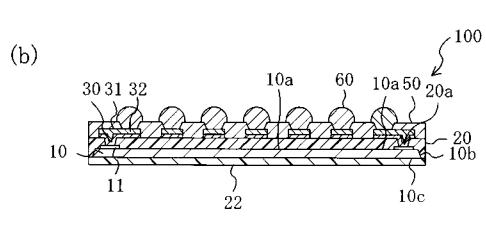

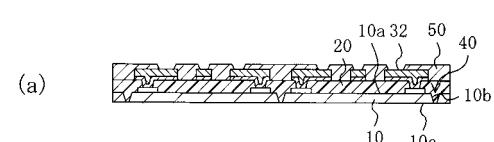

図1から図4を参照しながら、本発明による実施形態1を説明する。図1(a)は、本実施形態にかかる半導体装置100の上面を一部切り欠いて模式的に示している。図1(b)は、半導体装置100の断面を模式的に示している。本実施形態の半導体装置100は、半導体素子10と、半導体素子10の正面10a上に配列された素子電極11と、正面10a上および正面10aの外縁を規定する側面10b上に形成された絶縁層20と、正面10aに対向する裏面10c上に形成された樹脂層22と、絶縁層20上に形成された配線層33とを備えている。

## 【0015】

配線層33は、素子電極11に接合されたコンタクト部30と、外部機器に電気的に接

50

続可能なランド32と、コンタクト部30とランド32とを電気的に接続する配線31とを有している。ランド32は、外部機器と半導体素子10との間で伝達される信号の入出力を行う外部電極として機能し、半導体素子10の主面10a上に二次元的に配置されている。ランド32は、配線層33の一部として形成されており、コンタクト部30、配線32およびランド32は、同一金属（例えば、銅）から形成され得る。

#### 【0016】

絶縁層20上には、配線層33を被覆し且つランド32の一部を露出するソルダーレジスト層50が形成されており、ランド32には、外部電極端子として機能する金属ボール60が接合されている。ランド32に金属ボール60が接合されていると、簡便なプロセスで迅速に、金属ボール60を介してランド32と配線基板（プリント基板）とを電気的に接続することができる。金属ボール60は、例えば、半田、半田メッキされた銅、ニッケル等から構成されている。

10

#### 【0017】

半導体素子10は、例えば半導体チップであり、トランジスタ等を含む半導体集積回路部（不図示）を備えており、半導体集積回路部は素子電極11と電気的に接続されている。半導体集積回路部を保護するため、半導体素子10の主面10aには、素子電極11を露出する開口部を有するパッシベーション膜（不図示）が形成されていることが好ましい。本実施形態では、半導体チップの主面10aの外周部に素子電極が配置されている。

#### 【0018】

また、本実施形態では、半導体素子10の側面10bは、主面10aとなす角が鈍角（100度程度）をなすよう傾斜して形成されている。半導体素子10の側面10bが傾斜していることによって、製造工程において側面10b上に塗布される絶縁性樹脂材料の濡れやすさを向上させることができる。さらに、半導体素子10の裏面10cは研磨されており、そのため半導体素子10の厚さ（例えば、150μm程度）は、従来のCSPの厚さ（例えば、500μm程度）よりも薄くなっている。半導体素子10の厚さを薄くすることによって、半導体装置100全体の見掛けの熱膨張係数（線膨張係数）を、半導体素子10の熱膨張係数よりも、絶縁層20および樹脂層22を構成している材料（例えば、絶縁性樹脂材料）の熱膨張係数の方に近づけることができる。このため、半導体装置10を配線基板に実装した後、配線基板との接続部に発生する応力を低減することが可能となる。

20

#### 【0019】

なお、本実施形態では半導体素子10として半導体チップを用いているが、半導体チップに分離する前の半導体ウェハを用いてもよい。また、素子電極11が配置される領域（電極配置領域）は、半導体チップの主面10aの外周部の全ての辺に設けられている必要はない。また、電極配置領域を主面10aの外周部に設けずに、例えば主面10aの中央部に設けることも可能である。なお、素子電極11上に耐メッキ液性を有するバリアメタルを形成することもできる。

30

#### 【0020】

絶縁層20は、主面10a上に加えて、側面10b上にも形成されている。従って、絶縁層20によって、従来のCSPでは保護されていなかった半導体素子10の側面10bを保護することができる。本実施形態では、側面10b全面に絶縁層20が形成されている。主面10a上の絶縁層20の厚さは、配線基板との接合部に発生する応力の緩和という観点から、例えば5～100μm程度の範囲内、好ましくは30μm程度である。側面10b上の絶縁層20の厚さは、絶縁性の観点から、例えば3～20μm程度の範囲内、好ましくは5μm程度である。なお、側面10bの保護の観点から実質的に影響がない場合、側面10b全面に樹脂層20が形成されてなくとも、絶縁層20によって側面10bが実質的に被覆されていると言えるので、側面10bの一部に絶縁層20が形成されていない領域が存在していてもよい。

40

#### 【0021】

絶縁層20は、絶縁性を有する材料から構成されており、例えば、エステル結合型ポリ

50

イミドやアクリレート系エポキシ等の高分子材料から構成されている。絶縁層20は、単一層に限定されず、複数の層（または複数の部分）から形成されていてもよい。例えば、絶縁層20のうち主面10a上の部分と側面10b上の部分とを異なる材料から形成することも可能である。なお、同一材料を用いて单一層として形成した場合、絶縁層20全体が同一の熱膨張係数を有することになるため、絶縁層20内に熱応力が発生することを防止することができる。

#### 【0022】

また、絶縁層20は、絶縁性の弾性材料から構成されていることが好ましい。低弾性率材料（弾性率が例えば2000kg/mm<sup>2</sup>以下の材料）から構成した場合、配線基板（プリント基板）と半導体素子10との間に熱膨張係数の違いに起因して発生する熱応力を絶縁層20によって緩和することができる。低弾性率材料として、例えば、エスチル結合型ポリイミドやアクリレート系エポキシ等の高分子材料を用いることができる。

10

#### 【0023】

絶縁層20は、素子電極11を露出する開口部20aを有している。開口部20a内において素子電極11と配線層33とが電気的に接続されている。配線層33の断線防止の観点より、開口部20aを規定する側面と絶縁層20の上面とが鈍角（例えば、100～150度程度）をなすように開口部20aが形成されていることが好ましい。

#### 【0024】

半導体素子の裏面10c上に形成された樹脂層22は、例えば、絶縁性を有する樹脂材料から構成されており、具体的には、エスチル結合型ポリイミドやアクリレート系エポキシ等の高分子材料から構成されている。樹脂層22を低弾性率材料から構成することもできる。なお、樹脂層22は、単一層に限定されず、複数の層（または複数の部分）から形成されていてもよい。

20

#### 【0025】

絶縁層20と樹脂層22とは、同一の絶縁性樹脂材料から形成されていることが好ましい。両層が同一材料から形成された場合、両層の硬化収縮や熱膨張係数が等しくなるため、絶縁性樹脂材料の硬化収縮や熱膨張によって生じる半導体素子10の反りを抑制・防止することができる。その結果、半導体装置100の実装面の平坦性を確保することができ、検査時および実装時に容易かつ確実に電気的接続が可能な半導体装置100を提供することができる。半導体素子10の反りをさらに効果的に抑制・防止するため、樹脂層22の厚さは、絶縁層20の厚さと同程度にすることが好ましい。樹脂層22の厚さは、例えば5～100μm程度の範囲内、好ましくは30μm程度にする。

30

#### 【0026】

樹脂層22は、半導体素子の裏面10cの一部を露出する開口部を有してもよい。樹脂層22が開口部を有していると、半導体装置100が吸湿したときにリフローを行っても、吸湿した水分を開口部から水蒸気として放出させることができるために、水蒸気爆発などの発生を防止することができる。開口部の形状は例えば円形や矩形であり、具体的には、直径0.2mmの円形や寸法0.2×0.2mmの矩形の開口部が複数個（例えば50個程度）形成されればよい。吸湿した水分を水蒸気として放出させる目的のため、開口部の総面積は、半導体素子の裏面10cの面積の1～5%程度であることが好ましい。開口部は、例えば、公知のフォトリソグラフィ技術およびエッチング技術、またはレーザを用いて形成すればよい。

40

#### 【0027】

本実施形態の半導体装置100では、半導体素子の側面10bが絶縁層20によって被覆されているので、物理的な衝撃を緩和して半導体素子の側面10bを保護することができ、その結果、半導体素子10のチッピングを防止することができる。半導体素子の裏面10c上に樹脂層22を形成すると、半導体素子の裏面10cも保護することができる。従って、信頼性に優れた半導体装置を提供することができる。

#### 【0028】

また、主面10a上に絶縁層20が形成されているので、ランド32を二次元的に配置

50

することができ、狭い面積に多数の外部電極を設けることが可能となる。従って、多ピン化に対応可能な半導体装置（CSP）を提供することができる。さらに、半導体装置100はウェハレベルCSPとして製造可能な構成をしており、加えて、ランド32を配線層33の一部として形成することができる構成をしているので、製造コストが極めて低い半導体装置を提供することができる。

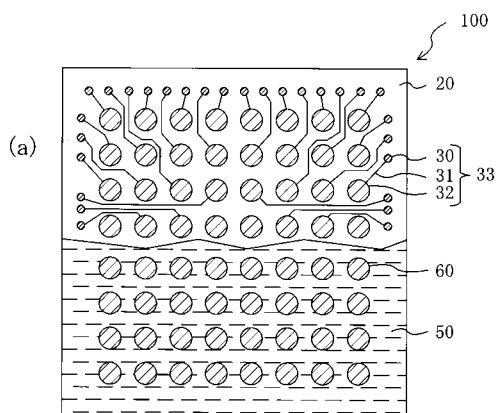

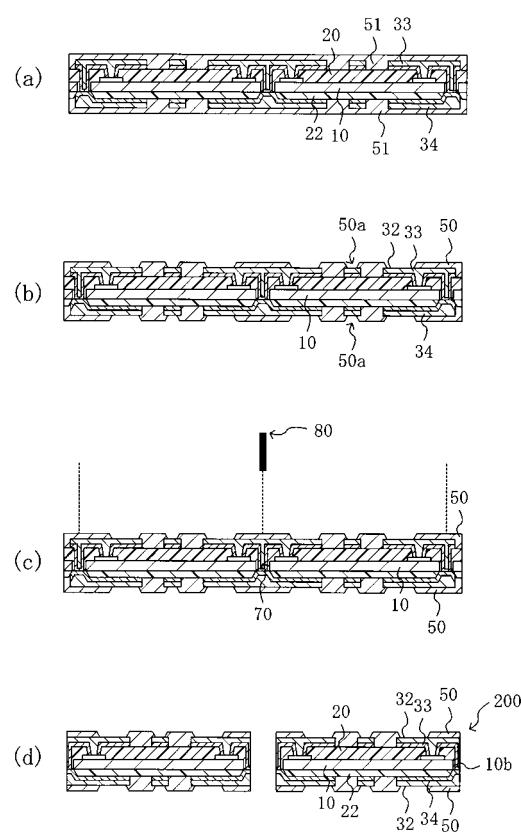

（実施形態2）

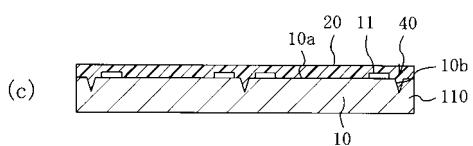

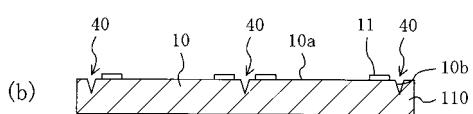

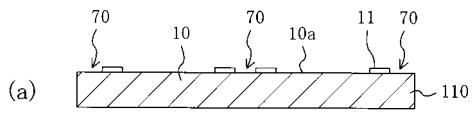

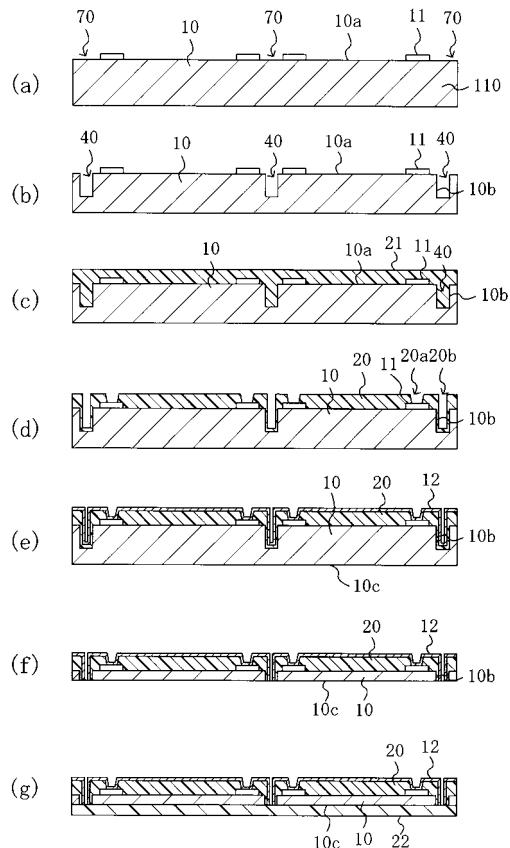

次に、図2（a）～（e）、図3（a）～（e）および図4（a）～（e）を参照しながら、実施形態2にかかる半導体装置100の製造方法を説明する。

【0029】

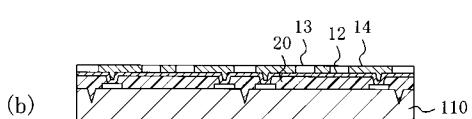

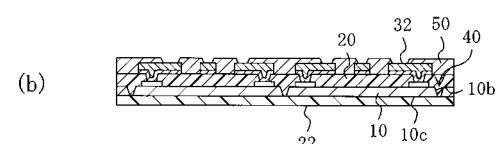

まず、図2（a）に示すように、複数の半導体チップ10が形成された半導体ウェハ110を用意する。複数の半導体チップ10のそれぞれは、素子電極11が配列された主面10aを有している。なお、半導体チップ10の主面および裏面は、それぞれ、半導体ウェハ110の主面および裏面を意味する場合がある。

【0030】

半導体ウェハ110には、複数の半導体チップ10のそれぞれを分割するスクライブレーン70が形成されている。半導体ウェハ110の厚さは、例えば625μm程度であり、スクライブレーン70の幅は、例えば80μm程度である。半導体ウェハ110の主面には、予めパッシベーション膜（不図示）が形成されていることが好ましい。

【0031】

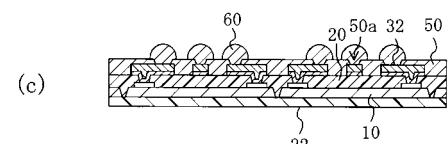

次に、図2（b）に示すように、複数の半導体チップ10のそれぞれの主面10aの外縁を規定する側面10bを露出する溝40を半導体ウェハ110に形成する。例えば、ダイシングソーを用いて半導体ウェハ40の主面側からスクライブレーン70に沿って溝40を形成する。溝40の幅は、例えば100μm程度であり、溝40の深さは、例えば300μm程度である。主面10aと側面10bとが鈍角（例えば100度程度）をなすようにV字型に溝は形成される。V字型に溝を形成すると、後の工程で側面10b上に塗布される絶縁性樹脂材料の濡れやすさを向上させることができる。なお、V字型に代えて、凹字型の溝を形成してもよい。溝40の形成方法は、レーザやプラズマによる機械的な加工、またはエッティングなどの化学的な加工によって行ってもよい。

【0032】

次に、図2（c）に示すように、溝40内に露出した側面10bと主面10aとの上に絶縁層20を形成する。本実施形態では、側面10b全面に絶縁層20を形成する。絶縁層20の形成は、例えば、感光性絶縁材料を塗布した後、乾燥することによって行う。絶縁層20の厚さは、例えば5～15μm程度、好ましくは10μm程度にする。

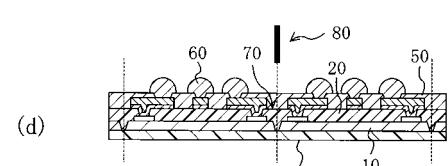

【0033】

次に、図2（d）に示すように、素子電極11を露出する開口部20aを絶縁層20に形成する。開口部20aの形成は、絶縁層20を露光・現像することによって行う。開口部20aを形成する場合、露光工程において平行光ではなく例えば拡散光（散乱光を含む）を使用することが好ましい。拡散光を使用することによって、開口部の側面と絶縁層20の上面とが鈍角（例えば、100～140度程度）をなすように、開口部20aを形成することができる。

【0034】

絶縁層20を形成するための感光性絶縁材料としては、例えばエステル結合型ポリイミドやアクリレート系エポキシ等の高分子材料を用いることができ、絶縁性を有する材料であれば特に限定されない。なお、感光性絶縁材料は液状である必要はなく、予めフィルム状に形成された材料を用いてもよい。この場合、フィルム状の感光性絶縁材料を半導体素子10上に貼りあわせた後に、露光と現像とを順次行って開口部20aを形成することができる。また、感光性を有していない絶縁材料を用いることも可能である。この場合、例えば、レーザやプラズマを用いる機械的な加工、またはエッティングなどの化学的な加工によって開口部20aを形成すればよい。

【0035】

10

20

30

40

50

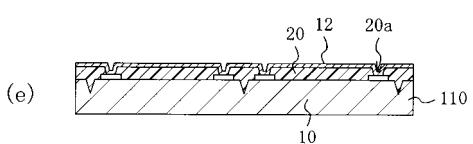

次に、図2(e)に示すように、絶縁層20および素子電極11の上に薄膜金属層12を形成する。薄膜金属層12の形成は、真空蒸着法、スパッタリング法、CVD法、または無電解めっき法を用いて、例えば、Ti膜(厚さ:0.2μm程度)を堆積した後、Ti膜上にCu膜(厚さ:0.5μm程度)を堆積することによって行う。

【0036】

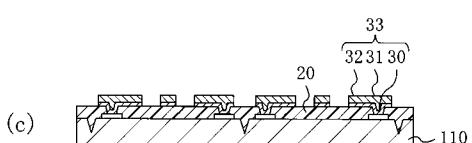

次に、図3(a)に示すように、薄膜金属層12の上にメッキレジスト膜13を形成する。メッキレジスト膜13の形成は、薄膜金属層12上にポジ型感光性レジストを塗布した後、このレジストのうち仕上げ製品の所望のパターン部の部分を分解し、次いで所望のパターン部を除去することによって行う。なお、ポジ型感光性レジストに代えて、ネガ型感光性レジストを用いてメッキレジスト膜13を形成してもよい。

10

【0037】

次に、図3(b)に示すように、メッキレジスト膜13の形成された部分以外の薄膜金属層12上に厚膜金属層14を形成する。厚膜金属層14の形成は、例えば電解めっき法を用いて行う。厚膜金属層14の厚さは、例えば5μm~15μmの範囲内、好ましくは10μm程度にする。電解めっき法を用いると、他の方法よりも短時間で厚膜を形成することができるという利点がある。

【0038】

次に、図3(c)に示すように、メッキレジスト膜13を分解除去した後、薄膜金属層12を選択的に除去することによって、コンタクト部30、配線31およびランド32から構成される配線層33を形成する。薄膜金属層12を溶解できるエッティング液(例えば、Cu膜に対して塩化第二銅溶液、Ti膜に対してEDTA溶液)を用いて全面エッティングを行うと、厚膜金属層14よりも厚さの薄い薄膜金属層12が先行して除去されるので、薄膜金属層12を選択的に除去することができる。

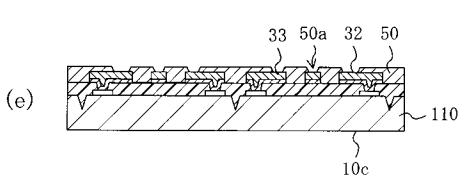

20

【0039】

次に、図3(d)に示すように、感光性ソルダーレジスト材料51を絶縁層20の上に堆積する。その後、図3(e)に示すように、配線層33のランド32の少なくとも一部を露出する開口部50aを感光性ソルダーレジスト材料51にフォトリソグラフィ技術を用いて形成し、ソルダーレジスト層50を得る。ソルダーレジスト層50を形成することによって、コンタクト部30と金属配線31を溶融したはんだから保護することができる。

30

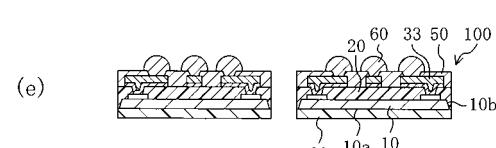

【0040】

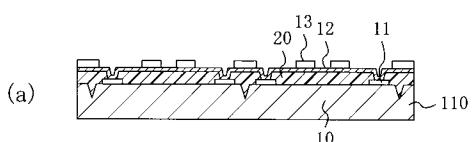

次に、図4(a)に示すように、半導体チップ(または半導体ウェハ)の正面10aに対向する裏面10cを研磨することによって、側面10b上に形成された絶縁層20(溝40内の絶縁層20)を裏面10cから露出させる。研磨後の半導体チップ10の厚さは300μm程度である。

【0041】

裏面10cの研磨は、半導体ウェハ101の正面10aを保護するために使用するバックグラインドテープ(不図示)を正面10aに接着させた後に実行することが好ましい。裏面10cを研磨した後は、絶縁層20の残留応力によって、樹脂層20側が凹になるよう半導体ウェハ10が反るため、この反りをバックグラインドテープによって防ぐことが望ましいからである。バックグラインドテープとしては、厚さが100μm以上であり、ヤング率が200kg/cm<sup>2</sup>以上あることが好ましい。

40

【0042】

また、バックグラインドテープの代わりに、プレート(例えば、シリコン基板やセラミック基板)を接着剤を介して正面10aに接着させた後、裏面10cの研磨を行っても良い。この場合、一定温度で接着性がなくなるように設計された接着剤を用いることが好ましい。

【0043】

次に、図4(b)に示すように、研磨された裏面10c上および裏面10cから露出した絶縁層20上に、すなわち、半導体ウェハ110の裏面10c上に樹脂層22を形成す

50

る。樹脂層 2 2 の形成は、例えば、絶縁性樹脂材料を塗布した後、乾燥することによって行う。樹脂層 2 2 を形成する材料として、絶縁層 2 0 と同一の材料を用いることが好ましい。両層を同一材料から形成することによって、両層の硬化収縮や熱膨張係数を等しくすることができ、絶縁性樹脂材料の硬化収縮や熱膨張によって生じる半導体ウェハ 1 0 1 ( または半導体チップ 1 0 ) の反りを抑制・防止することができるからである。また、同一材料を用いれば、材料コストの低減を図ることもできる。半導体ウェハ 1 1 0 の反りをさらに効果的に抑制・防止するため、樹脂層 2 2 の厚さを、絶縁層 2 0 の厚さと同程度にすることが望ましい。樹脂層 2 2 の厚さは、例えば 5 ~ 1 0 0  $\mu\text{m}$  程度の範囲内、好ましくは 3 0  $\mu\text{m}$  程度にする。

## 【 0 0 4 4 】

10

樹脂層 2 2 の形成は、バックグラインドテープまたはプレートを正面 1 0 a に接着させた状態で行うことが好ましい。このようにすれば、半導体ウェハ 1 0 1 が複数の半導体チップ 1 0 のそれぞれに分離することを防止することができるため、半導体ウェハ 1 0 1 の裏面全面に樹脂層 2 2 を形成でき、製造効率を向上させることができるからである。

## 【 0 0 4 5 】

次に、図 4 ( c ) に示すように、開口部 5 0 a 内に露出したランド 3 2 上に金属ボール 6 0 を載置した後、ランド 3 2 と金属ボール 6 0 とを溶融結合させる。

## 【 0 0 4 6 】

最後に、図 4 ( d ) に示すように、半導体ウェハ 1 0 1 のスクライプレーン 7 0 に沿って、例えば 3 0  $\mu\text{m}$  幅のダイシングソーを用いてダイシングを行うと、図 4 ( e ) に示すように、半導体ウェハ 1 0 1 から半導体チップ 1 0 のそれぞれが分離され、半導体装置 1 0 0 が得られる。

20

## 【 0 0 4 7 】

本実施形態によれば、半導体ウェハ 1 0 1 の裏面 1 0 c を研磨し、溝 4 0 内の絶縁層 2 0 を裏面 1 0 c から露出させることによって、半導体チップ 1 0 の側面 1 0 b を樹脂層 2 0 で被覆した半導体装置 ( または、ウェハレベル C S P ) を簡便なプロセスで製造することができる。また、配線層 3 3 の一部としてランド 3 2 を形成することができるので、製造工程の削減を図ることができる。

## ( 実施形態 3 )

30

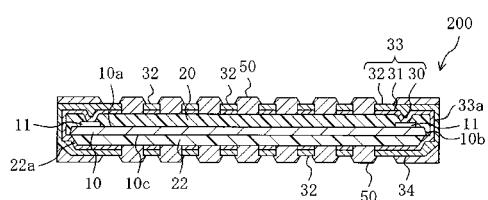

図 5 を参照しながら、本発明による実施形態 3 を説明する。図 5 は、本実施形態にかかる半導体装置 2 0 0 の断面を模式的に示している。本実施形態の半導体装置 2 0 0 は、樹脂層 2 2 上に金属配線層 3 2 を有している点において、実施形態 1 の半導体装置 1 0 0 と異なる。本実施形態の説明を簡明にするため、以下では、実施形態 1 と異なる点を主に説明し、実施形態 1 と同様の点の説明は省略する。

## 【 0 0 4 8 】

半導体装置 2 0 0 は、半導体チップ ( 半導体素子 ) 1 0 と、半導体チップ 1 0 の正面 1 0 a 上および側面 1 0 b 上に形成された絶縁層 2 0 と、裏面 1 0 c 上に形成された絶縁性樹脂層 2 2 と、絶縁層 2 0 上に形成された配線層 3 3 と、絶縁性樹脂層 2 2 上に形成された金属配線層 3 4 を備えている。配線層 3 3 および金属配線層 3 4 は、外部電極として機能するランド 3 2 を有しており、絶縁層 2 0 上および絶縁性樹脂層 2 2 上には、配線層 3 3 および金属配線層 3 4 を被覆し、且つランド 3 2 の一部を露出するソルダーレジスト層 5 0 が形成されている。

40

## 【 0 0 4 9 】

絶縁層 2 0 上に形成された配線層 3 3 は、半導体素子 1 0 の側面上に位置する絶縁層上に形成された側面配線層 3 3 a を有している。側面配線層 3 3 a は、正面 1 0 a 上に配列された複数の素子電極 1 1 の一部に電気的に接続されている。また、側面配線層 3 3 a は、絶縁性樹脂層 2 2 上に形成された金属配線層 3 4 に電気的に接続されている。側面配線層 3 3 a に電気的に接続された金属配線層 3 4 の断線を防止するために、絶縁性樹脂層 2 2 の側面 2 2 a はテーパー状に形成されていることが好ましい。側面配線層 3 3 a は、例えば、配線層 3 3 と同一の材料から形成されており、側面配線層 3 3 a の厚さは、例えば

50

3 ~ 20  $\mu\text{m}$  程度であり、5  $\mu\text{m}$  程度であることが好ましい。

【0050】

本実施形態の半導体装置200は、半導体チップ10の裏面10c上に金属配線層34を有しているので、半導体チップ10の熱を金属配線層34に伝えて放熱させることができる。このため、放熱性に優れた半導体装置を提供することができる。また、金属配線層34が側面配線層33aに電気的に接続されているので、半導体チップ10を電気的にシールドした構造にすることができる。従って、電磁シールド性に優れた半導体装置を提供することができる。その結果、半導体装置の信頼性を向上させることができる。

【0051】

さらに、半導体装置200では、半導体チップ10の正面10aおよび裏面10cの両面上にランド32が形成されているので、半導体装置200の両面を利用して3次元的な実装をすることが可能である。また、半導体チップ10の側面10bおよび裏面10cが絶縁層20および絶縁性樹脂層22によって保護されているので、実施形態1の半導体装置100と同様に、チッピングの発生を防止することができる。

【0052】

本実施形態では、絶縁性樹脂層22上に金属配線層34が形成されているが、放熱性の向上という観点から、金属配線層34に代えて、単に金属層が形成されていてもよい。この金属層を側面配線層33aに電気的に接続した構造にすれば、半導体チップ10を電気的にシールドすることができるため、電磁シールド性を向上させることができる。

【0053】

また、金属配線層34および絶縁樹脂層22に代えて、半導体チップ10の裏面10cに導電性樹脂層を形成した構成にすることも可能である。裏面10cに形成した導電性樹脂層によって、半導体素子の放熱性を向上させることができ、この導電性樹脂層と素子電極11の一部とを、例えば側面配線層33aを介して相互に接続すれば、電磁シールド性を向上させることができる。導電性樹脂層は、例えば、炭素(微粒子)、銅またはニッケル等の導電性フィラーを含む樹脂材料から形成することができ、高熱伝導性を有する樹脂層である。また、放熱性の向上を主目的とするならば、アルミナまたは窒化アルミナ等の高熱伝導性を示す絶縁フィラーを含む樹脂材料から形成した絶縁性樹脂層を、導電性樹脂層に代えて、形成することも可能である。

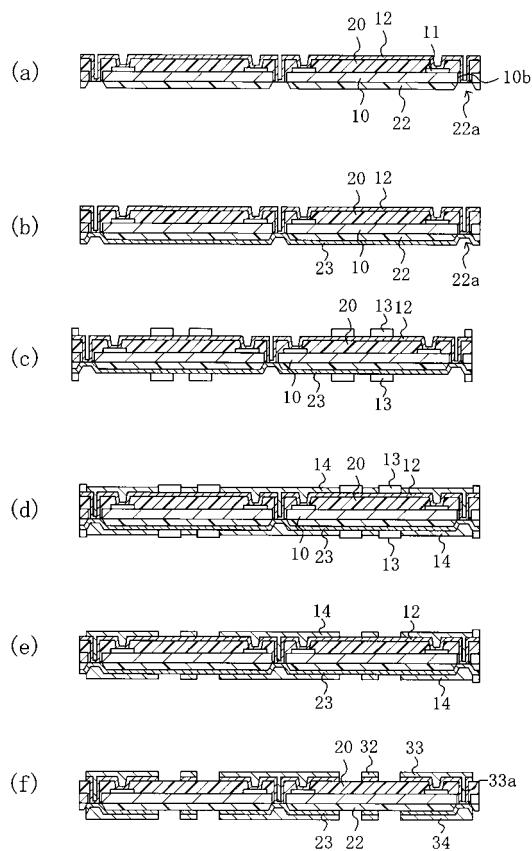

(実施形態4)

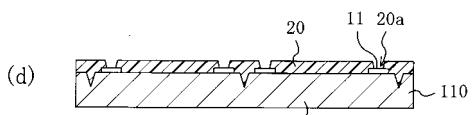

次に、図6(a)~(g)、図7(a)~(f)および図8(a)~(d)を参照しながら、実施形態4にかかる半導体装置200の製造方法を説明する。本実施形態の説明を簡明にするため、以下では、実施形態2と異なる点を主に説明し、実施形態2と同様の点の説明は省略する。

【0054】

まず、図6(a)に示すように、複数の半導体チップ10が形成された半導体ウェハ110を用意した後、図6(b)に示すように、複数の半導体チップ10の側面10bを露出する溝40を半導体ウェハ110に形成する。本実施形態では、スクライブレーン70に沿って、凹型の溝40(幅:100  $\mu\text{m}$  程度、深さ:300  $\mu\text{m}$  程度)を形成する。なお、凹型に代えて、V字型の溝を形成してもよい。

【0055】

次に、図6(c)に示すように、溝40内に露出した側面10bと正面10aとの上に絶縁層20を形成する。絶縁層20の厚さは、例えば5~100  $\mu\text{m}$  程度、好ましくは30  $\mu\text{m}$  程度にする。

【0056】

次に、図6(d)に示すように、素子電極11を露出する開口部20aと、側面10b上に形成された絶縁層20を溝40内に露出する開口部20bとを絶縁層20に形成する。開口部20aおよび開口部20bの形成は、絶縁層20を露光・現像することによって行う。

【0057】

10

20

30

40

50

次に、図 6 ( e ) に示すように、半導体チップの正面 10 a および側面 10 b 上に位置する絶縁層 20 と、素子電極 11 との上に薄膜金属層 12 を形成する。薄膜金属層 12 の形成は、真空蒸着法、スパッタリング法、CVD 法、または無電解めっき法を用いて、例えば、Ti 膜 ( 厚さ : 0.2 μm 程度 ) を堆積した後、Ti 膜上に Cu 膜 ( 厚さ : 0.5 μm 程度 ) を堆積することによって行う。なお、スパッタリング法で堆積を行う場合、図 6 ( a ) の工程で V 字型の溝を形成して影ができないにすると、蒸着しやすくできる。このとき、スパッタリング法による堆積が好ましくなければ、指向性の少ない電子ビーム蒸着法や CVD 法を用いることができる。

#### 【 0058 】

次に、図 6 ( f ) に示すように、半導体チップ ( または半導体ウェハ ) の裏面 10 c を研磨することによって、側面 10 b 上に形成された絶縁層 20 および薄膜金属層 12 ( 溝 40 内の絶縁層 20 および薄膜金属層 12 ) を裏面 10 c から露出させる。研磨後の半導体チップ 10 の厚さは 150 μm 程度である。研磨の際には、半導体チップ 10 の反りを防止するために、バックグラインドテープ ( 厚さ : 100 μm 以上、ヤング率 : 200 kg / cm<sup>2</sup> 以上 ) 、または接着剤を介してプレート ( 例えば、シリコン基板やセラミック基板 ) を正面 10 a に接着することができる。

#### 【 0059 】

次に、図 6 ( g ) に示すように、研磨された裏面 10 c 上と、裏面 10 c から露出した絶縁層 20 および薄膜金属層 12 の上に、すなわち、半導体ウェハ 110 の裏面上に樹脂層 22 を形成する。樹脂層 22 の形成は、例えば、感光性絶縁樹脂材料を塗布した後、乾燥することによって行う。実施形態 2 と同様の理由により、樹脂層 22 を形成する材料は、絶縁層 20 と同一の材料を用いることが好ましい。また、樹脂層 22 の厚さは、絶縁層 20 の厚さと同程度にすることが望ましい。樹脂層 22 の厚さは、例えば 5 ~ 100 μm 程度の範囲内、好ましくは 30 μm 程度にする。

#### 【 0060 】

次に、図 7 ( a ) に示すように、研磨によって露出した溝 40 内の絶縁層 20 および薄膜金属層 12 を露出する開口部 22 a を樹脂層 22 に形成する。開口部 22 a の形成は、樹脂層 22 を露光・現像することによって行う。開口部 22 a を形成する場合、露光工程において平行光ではなく例えば拡散光 ( 散乱光を含む ) を使用することが好ましい。拡散光を使用することによって、開口部の側面と樹脂層 22 の上面とが鈍角 ( 例えば、100 ~ 140 度程度 ) をなすように、開口部 22 a を形成することができる。このようにテーパー状に開口部 22 a を形成することによって、後の工程で形成される金属配線層 34 の断線を防止することができる。

#### 【 0061 】

次に、図 7 ( b ) に示すように、樹脂層 22 と、開口部 22 a 内に露出した絶縁層 20 および薄膜金属層 12 との上に、薄膜金属層 23 を形成する。薄膜金属層 23 の形成は、真空蒸着法、スパッタリング法、CVD 法、または無電解めっき法を用いて、例えば、Ti 膜 ( 厚さ : 0.2 μm 程度 ) を堆積した後、Ti 膜上に Cu 膜 ( 厚さ : 0.5 μm 程度 ) を堆積することによって行う。

#### 【 0062 】

次に、図 7 ( c ) に示すように、薄膜金属層 12 および 23 の上にメッキレジスト膜 13 を形成する。メッキレジスト膜 13 の形成は、薄膜金属層 12 および 23 上にポジ型感光性レジストを塗布した後、このレジストのうち仕上げ製品の所望のパターン部の部分を分解し、次いで所望のパターン部を除去することによって行う。なお、ポジ型感光性レジストに代えて、ネガ型感光性レジストを用いてメッキレジスト膜 13 を形成してもよい。

#### 【 0063 】

次に、図 7 ( d ) に示すように、メッキレジスト膜 13 の形成された部分以外の薄膜金属層 12 および 23 上に厚膜金属層 14 を形成する。厚膜金属層 14 の形成は、例えば電解めっき法を用いて行う。厚膜金属層 14 の厚さは、例えば 5 μm ~ 15 μm の範囲内、好ましくは 10 μm 程度にする。

10

20

30

40

50

## 【0064】

次に、図7(e)に示すように、メッキレジスト膜13を分解除去する。その後、図7(f)に示すように、薄膜金属層12および23を選択的に除去することによって、側面配線層33aを有する配線層33と、金属配線層34とを形成する。薄膜金属層12および23を溶解できるエッティング液(例えば、Cu膜に対して塩化第二銅溶液、Ti膜に対してEDTA溶液)を用いて全面エッティングを行うと、厚膜金属層14よりも厚さの薄い薄膜金属層12および23が先行して除去されるので、薄膜金属層12を選択的に除去することができる。配線層33および金属配線層34の両層とも、外部電極として機能するランド32を備えている。

## 【0065】

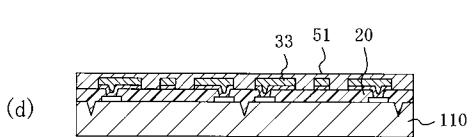

次に、図8(a)に示すように、感光性ソルダーレジスト材料51を絶縁層20および22の上に堆積する。その後、図8(b)に示すように、配線層33と金属配線層34との両層のランド32の少なくとも一部を露出する開口部50aを感光性ソルダーレジスト材料51にフォトリソグラフィ技術を用いて形成し、ソルダーレジスト層50を得る。

## 【0066】

最後に、図8(c)に示すように、半導体ウェハ101のスクライブレーン70に沿って、例えば30μm幅のダイシングソーを用いてダイシングを行うと、図8(d)に示すように、半導体ウェハ101から半導体チップ10のそれぞれが分離され、半導体装置200が得られる。なお、ランド32に金属ボールを載置して溶融接合させてもよい。

## 【0067】

本実施形態では、半導体ウェハ110裏面の研磨によって側面配線層33aを裏面10cから露出させた後、裏面10cから露出した側面配線層33aに電気的に接続される金属配線層34を形成する。このため、放熱性および電磁シールド性に優れ、且つ3次元実装可能な半導体装置(または、ウェハレベルCSP)を簡便なプロセスで製造することができる。

## (他の実施形態)

上記実施形態では薄膜金属層および厚膜金属層を構成する材料としてTiおよびCuを使用したが、これに代えてCr、W、Ti/Cu、Ni等を使用してもよい。また、薄膜金属層と厚膜金属層とをそれぞれ異なる金属材料により構成しておき、最終的なエッティング工程で薄膜金属層のみを選択的にエッティングするエッチャントを用いてもよい。

## 【0068】

上記実施形態では、金属ボール60を設けたが、これに代えて突起電極を設けてよい。突起電極として、例えば、はんだクリームをランド32上に印刷、溶融することによって形成されたはんだバンプ、溶融はんだ内にディップすることによって形成されたはんだバンプ、無電解めっきによって形成されたニッケル/金バンプなどを設けることができる。突起電極は、導電性を有し、かつソルダーレジスト層50から突出していればよい。突起電極を設けることによって、金属ボール60を順次搭載する手間の掛かる工程とが不要となるため、低コストの半導体装置を実現することができる。

## 【0069】

また、ランド32を外部電極端子として機能させるランド・グリッド・アレイ(LGA)型の構成を採用してもよい。LGA型の構成を採用した半導体装置を配線基板上に実装する際には、配線基板の接続端子の上にはんだクリームを塗布した後リフローさせるなどの方法によって、ランド32と配線基板との電気的な接続を容易に行なうことができる。

## 【0070】

## 【発明の効果】

本発明の半導体装置によれば、半導体素子の側面上に絶縁層が形成されているので、物理的な衝撃を緩和して半導体素子の側面を保護することができ、チッピングの発生を防止することができる。その結果、信頼性に優れた半導体装置を提供することができる。

## 【0071】

半導体素子の裏面上に樹脂層が形成された場合、半導体素子の裏面を保護することができ

10

20

30

40

50

き、さらに信頼性を向上させることができる。絶縁層と樹脂層とが同一の絶縁性樹脂材料から形成されているときには、両層の硬化収縮や熱膨張係数が等しくなるため、半導体素子の反りを効果的に抑制・防止することができる。その結果、半導体装置の実装面の平坦性を確保することができ、検査時および実装時に容易かつ確実に電気的接続が可能な半導体装置を提供することができる。

【0072】

半導体素子の裏面上に導電性樹脂層が形成された場合、半導体素子の裏面を保護することができ、さらに、半導体装置の放熱性を向上させることができる。導電性樹脂層が素子電極の一部に電気的に接続されているときには、半導体素子を電気的にシールドした構造にすることができるため、電磁シールド性に優れた半導体装置を提供することができる。

10

【0073】

半導体素子の裏面の一部を露出する開口部を樹脂層に形成した場合には、半導体装置が吸湿したときにリフローを行っても、吸湿した水分を開口部から水蒸気として放出させることができるために、水蒸気爆発などの発生を防止することができる。このため、信頼性に優れた半導体装置を提供することができる。

【0074】

半導体素子の裏面上に金属層が形成された場合、半導体装置の放熱性を向上させることができる。金属層が側面配線層に電気的に接続されているときには、半導体素子が電気的にシールドされた構造にすることができる、その結果、電磁シールド性に優れた半導体装置を提供することができる。また、金属層として金属配線層が形成されている場合、半導体素子の裏面にある外部電極によっても外部機器との電気的接続が可能となる。このため、半導体素子の主面および裏面の両面に実装可能な半導体装置を提供することができる。

20

【0075】

本発明による半導体装置の製造方法では、半導体素子の側面上に形成した絶縁層を、裏面を研磨することによって裏面から露出させる。これにより、半導体素子の側面が絶縁層で被覆された構造の半導体装置を簡便なプロセスで製造することができる。また、裏面に樹脂層を形成すると、半導体素子の裏面を保護した半導体装置を製造することができる。

【0076】

裏面を研磨する際に、半導体素子の主面にバックグラインドテープを接着させることによって、半導体素子の反りを防止することができる。また、バックグラインドテープによって、複数の半導体素子がそれぞれに分離することを防止して、裏面に樹脂層を形成することができる。バックグラインドテープの代わりに、プレートおよび接着剤を使用することもできる。

30

【0077】

側面配線層を有する配線層を形成した後、側面配線層を裏面の研磨によって裏面から露出させ、裏面から露出した側面配線層に電気的に接続される金属層を裏面上に形成すると、放熱性および電磁シールド性に優れた半導体装置を簡便なプロセスで製造することができる。

【0078】

裏面から絶縁層を露出させた後に、半導体ウェハを複数の半導体素子のそれぞれに分離することによって、半導体チップに分離される前の半導体ウェハを用いて各工程を行うことができるため、製造コストを大幅に低減することができる。

40

【図面の簡単な説明】

【図1】(a)は、実施形態1にかかる半導体装置100を一部切り欠いて模式的に示す平面図であり、(b)は、半導体装置100を模式的に示す断面図である。

【図2】(a)～(e)は、実施形態2にかかる半導体装置の製造方法を説明するための工程断面図である。

【図3】(a)～(e)は、実施形態2にかかる半導体装置の製造方法を説明するための工程断面図である。

【図4】(a)～(e)は、実施形態2にかかる半導体装置の製造方法を説明するため

50

の工程断面図である。

【図5】 実施形態3にかかる半導体装置200を模式的に示す断面図である。

【図6】 (a)～(g)は、実施形態4にかかる半導体装置の製造方法を説明するための工程断面図である。

【図7】 (a)～(f)は、実施形態4にかかる半導体装置の製造方法を説明するための工程断面図である。

【図8】 (a)～(d)は、実施形態4にかかる半導体装置の製造方法を説明するための工程断面図である。

【図9】 従来のウェハレベルCSP300を模式的に示す断面図である。

【符号の説明】

|             |               |    |

|-------------|---------------|----|

| 1 0         | 半導体素子(半導体チップ) | 10 |

| 1 1         | 素子電極(電極パッド)   |    |

| 1 2         | 薄膜金属層         |    |

| 1 3         | メッキレジスト層      |    |

| 1 4         | 厚膜金属層         |    |

| 2 0         | 絶縁層           |    |

| 2 2         | 樹脂層           |    |

| 2 3         | 薄膜金属層         |    |

| 3 0         | コンタクト部        |    |

| 3 1         | 配線            | 20 |

| 3 3         | 配線層           |    |

| 3 3 a       | 側面配線層         |    |

| 3 4         | 金属配線層         |    |

| 4 0         | 溝             |    |

| 5 0         | ソルダーレジスト層     |    |

| 6 0         | 金属ボール         |    |

| 7 0         | スクライブレーン      |    |

| 8 0         | ダイシングソー       |    |

| 1 0 0、2 0 0 | 半導体装置         |    |

| 1 0 1、1 1 0 | 半導体ウェハ        | 30 |

| 1 0 2       | パッシベーション膜     |    |

| 1 0 3       | 素子電極(電極パッド)   |    |

| 1 0 4       | A1配線          |    |

| 1 0 5       | Niメッキ層        |    |

| 1 0 6       | カバーコート膜       |    |

| 1 0 7       | 半田バンプ         |    |

| 3 0 0       | ウェハレベルCSP     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 下石坂 望

大阪府高槻市幸町1番1号 松下電子工業株式会社内

(72)発明者 中村 嘉文

大阪府高槻市幸町1番1号 松下電子工業株式会社内

(72)発明者 饗川 隆博

大阪府高槻市幸町1番1号 松下電子工業株式会社内

(72)発明者 渡瀬 和美

大阪府高槻市幸町1番1号 松下電子工業株式会社内

審査官 宮本 靖史

(56)参考文献 特開平10-223626 (JP, A)

特開平06-302604 (JP, A)

特開平11-251493 (JP, A)

特開平11-214434 (JP, A)

特開平08-330313 (JP, A)

特開平11-074400 (JP, A)

特開平11-121507 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 21/60