(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-312214

(P2008-312214A)

(43) 公開日 平成20年12月25日(2008.12.25)

(51) Int.Cl.

H03K 19/0185 (2006.01)

H03K 19/0944 (2006.01)

F 1

H03K 19/00

H03K 19/094101B

A

テーマコード(参考)

5J056

審査請求 有 請求項の数 5 O L (全 17 頁)

(21) 出願番号 特願2008-158397 (P2008-158397)

(22) 出願日 平成20年6月17日 (2008.6.17)

(31) 優先権主張番号 11/764, 262

(32) 優先日 平成19年6月18日 (2007.6.18)

(33) 優先権主張国 米国(US)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(71) 出願人 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク州

アーモンク ニューオーチャード

ロード

(74) 代理人 100058479

弁理士 鈴江 武彦

最終頁に続く

(54) 【発明の名称】 A C接続を用いたレベル・シフトするためのシステムおよび方法

## (57) 【要約】

【課題】従来の装置のより高い周波数で動作できないという問題を煩わないレベル・シフトのためのシステムおよび方法を提供する。

【解決手段】2進信号をレベル・シフトする方法は、A C成分と第1電圧の第1共通モード成分とを有する入力2進信号を受け取ることを含む。A C成分は第1共通モードから分離される。第2電圧の第2共通モード成分はA C成分に加えられる。A C成分と第2電圧の第2共通モード成分とを有する2進出力信号が提供される。負荷サイクル補償(DCC)が行われる。本方法は、第1モードまたは第2モードのいずれかで交互に動作することを含む。第1モードにおいて、DCCが行なわれ、第2モードにおいて、DCCが行なわれない。

【選択図】 図9

図9

## 【特許請求の範囲】

## 【請求項 1】

A C成分と第1電圧の第1共通モード成分とを有する入力2進信号を受け取り、前記A C成分を前記第1共通モードから分離し、第2電圧の第2共通モード成分を前記A C成分に加え、前記A C成分と前記第2電圧の前記第2共通モード成分とを有する2進出力信号を提供し、負荷サイクル補償(DCC)を行い、第1モードまたは第2モードのいずれかで交互に動作すること、具備し、前記第1モードにおいて、DCCが行なわれ、前記第2モードにおいて、DCCが行なわれない、2進信号をレベル・シフトする方法。

10

## 【請求項 2】

前記入力2進信号の負荷サイクルが許容範囲外にあるとき、前記第1モードで動作する、請求項1の方法。

## 【請求項 3】

2進入力信号のA C成分とD C成分とを分離し、前記A C成分を新しいD C成分に付加することによって、レベル・シフトされた2進出力信号を生成するように構成され、2進入力信号を受け取るとともに前記A C成分を中間ノードへと渡すように構成されたキャパシタを含み、それによって、前記A C成分と前記D C成分とを分離し、前記中間ノードで所望の電圧を維持するように構成され、供給電圧とグランドとの間に直列接続された2つの抵抗を具備する、分圧器を具備し、前記中間ノードは、前記2つの抵抗の間に位置する、システム。

20

## 【請求項 4】

負荷サイクルを修正して前記負荷サイクルを所望の値へと変化させるように構成された負荷サイクル補償(DCC)回路をさらに具備する、請求項3のシステム。

## 【請求項 5】

前記DCC回路は、分圧器、キャパシタ、インバータを具備し、前記インバータは2つの抵抗に接続され、前記第1抵抗は前記インバータと供給電圧との間に接続され、前記第2抵抗は前記インバータとグランドとの間に接続された構造を有する、第1素子構造と、前記第1素子構造と等価の構造を有する第2素子構造と、を具備し、前記第1素子構造および前記第2素子構造は差動増幅器の入力に接続され、前記第1素子構造は入力信号を受け取るように接続され、前記第2素子構造は反転された前記入力信号を受け取るように接続され、前記差動増幅器の出力はアンプに接続される、請求項4のシステム。

30

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、概して集積回路(IC)に関し、特にIC中のある電力領域から別の電力領域へと渡る信号の共通モード電圧を変化させるためのシステムおよび方法に関する。

## 【背景技術】

## 【0002】

ディジタル・デバイス(例えば集積回路)がより複雑になり、また動作速度が上がり続けるに連れて、装置の複雑さが、電力要求の相違する複数の回路領域を取り込んだデザインの実現を含む様々な形で明らかになった。例えば、幾つかの回路はアナログおよびディ

40

50

ジタル部品を組み合わせている。この場合、アナログ回路は典型的にはデジタル回路より高電圧で動作する。

#### 【0003】

多くの場合、領域間でデータを転送する必要がある。領域間でデータまたは信号を転送する場合、信号は、行き先の領域にとって適切な特性を有するように調節されねばならない。

#### 【0004】

クロック信号の配給は、そのような例である。クロック信号のような信号は相違する電力領域の部品相互間で受け渡されねばならず、よって、相違する領域の境界を横断するはずである。したがって、信号は行き先の領域に適するために変更される必要があり得。 10

#### 【0005】

信号を第1の供給電圧を用いる領域から異なる供給電圧を有する領域へと転送する場合、共通モード電圧を、起点領域のレベルによるものから信号の行き先領域のレベルによるものへと変化させることが典型的に必要である。これは一般にレベル・シフトと呼ばれる。レベル・シフトを行なうための幾つかの従来のデザインがあるが、これらの仕組みを実行するために典型的に用いられる装置は、現代のシステムで要求される周波数でこのタスクを行なうのに適していない。

#### 【0006】

この出願の発明に関連する先行技術文献情報としては次のものがある。

#### 【特許文献1】米国特許第6,819,159号明細書

20

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

したがって、従来の装置のより高い周波数で動作できないという問題を煩わないレベル・シフトのためのシステムおよび方法を提供することが望ましいであろう。

#### 【課題を解決するための手段】

#### 【0008】

本発明の一態様による、2進信号をレベル・シフトする方法は、AC成分と第1電圧の第1共通モード成分とを有する入力2進信号を受け取り、前記AC成分を前記第1共通モードから分離し、第2電圧の第2共通モード成分を前記AC成分に加え、前記AC成分と前記第2電圧の前記第2共通モード成分とを有する2進出力信号を提供し、負荷サイクル補償(DCC)を行い、第1モードまたは第2モードのいずれかで交互に動作すること、具備し、前記第1モードにおいて、DCCが行なわれ、前記第2モードにおいて、DCCが行なわれない。 30

#### 【0009】

本発明の一態様によるシステムは、2進入力信号のAC成分とDC成分とを分離し、前記AC成分を新しいDC成分に付加することによって、レベル・シフトされた2進出力信号を生成するように構成され、2進入力信号を受け取るとともに前記AC成分を中間ノードへと渡すように構成されたキャパシタを含み、それによって、前記AC成分と前記DC成分とを分離し、前記中間ノードで所望の電圧を維持するように構成され、供給電圧とグランドとの間に直列接続された2つの抵抗を具備する、分圧器を具備し、前記中間ノードは、前記2つの抵抗の間に位置する。 40

#### 【発明を実施するための最良の形態】

#### 【0010】

本発明の様々な実施形態は、相違する供給電圧を有する領域内の集積回路(I.C.)部品相互間で信号を伝送するためのシステムおよび方法を具備し、AC接続が用いられて信号の共通モード電圧があるレベルから別のレベルへと変化させられる速度が上げられる。幾つかの実施形態は負荷サイクル補償(DCC)を含んでいる。

#### 【0011】

一実施形態は、I.C.中の2進信号をレベル・シフトするための方法を具備する。この方

50

法は、入力 2 進信号を受け取ることと、その共通モード成分からその A C 成分を分離することを含んでいる。第 2 共通モード成分が A C 成分に加えられて、2 進出力信号を提供する。入力信号の共通モード電圧は出力信号の共通モード電圧より大きい（または小さい）かもしれない。

#### 【 0 0 1 2 】

本方法の一実施形態では、負荷サイクル補償（D C C）が行なわれる。D C C は、負荷サイクルを所望値へと変化させ得る。別の実施形態は、D C C が行なわれるモードと D C C が行なわれないモードの 2 つのモードで交互に動作する。さらに別の実施形態では、D C C モードは、入力 2 進信号の負荷サイクルが許容範囲外になったときに、有効にされる / 選択される。

10

#### 【 0 0 1 3 】

代替的な実施形態は、2 進入力信号の A C 成分および D C 成分を分離するように構成されたレベル・シフタを具備する。A C 成分は、次に、新たな D C 成分に付加され、これによって、レベル・シフトされた 2 進出力信号を生成する。レベル・シフタは、キャパシタを用いて 2 進入力信号の A C 成分を中間ノードへ渡し得る。中間ノードは、例えば分圧器によって、所望の電圧に維持され得る。この電圧は、信号の新しい D C 成分として役立つ。一実施形態では、分圧器は、供給電圧とグランドの間に直列接続された 2 つの抵抗から構成される。中間ノードは、2 つの抵抗の間に位置する。

#### 【 0 0 1 4 】

一実施形態では、レベル・シフタは、さらに負荷サイクルを修正する負荷サイクル補償（D C C）回路を具備する。例えば、負荷サイクルは、所望の値によりよく一致するように修正されることが可能である。D C C 回路は、差動増幅器の入力に接続された類似の構造の 2 本の枝（素子構造）によって実行され得る。各枝は、インバータ、キャパシタ、分圧器を含んでいる。各インバータは、供給電圧に接続された第 1 抵抗、およびグランドに接続された第 2 抵抗を含んでいる。一方の枝は入力信号を受け取り、他方の枝は反転された入力信号を受け取る。差動増幅器がさらなる下流の増幅器に接続されて、2 進出力信号を提供し得る。

20

#### 【 0 0 1 5 】

一実施形態では、スイッチング回路が含められて、D C C を選択的に有効および無効にする。これは、トランジスタを用いて、2 つの枝の各々のインバータに接続されている抵抗を分路することによって、行なわれ得る。スイッチング回路は、幾つかの測定基準を評価するとともにトランジスタに制御信号を供給してトランジスタのオン、オフを切り替える D C C 決定ユニットに接続されるか、または D C C 決定ユニットを含み得る。この測定基準は、（例として入力信号の、または出力信号の、または中間信号の）負荷サイクルを許容可能な閾値または範囲と比較したものであり得る。または、この測定基準は、他のデータ（例えば動作周波数）を用い得る。例えば、システムが、D C C が実行されるには高過ぎる周波数で動作する必要があるかもしれない。

30

#### 【 0 0 1 6 】

また、多くのさらなる実施形態が可能である。本発明の様々な実施例は、従来のシステムおよび方法に対する多くの利点を提供し得る。例えば、幾つかの実施形態は、従来のレベル・シフタより実質的に高い周波数で動作することができ得る。さらに、幾つかの実施形態は、許容可能な範囲または値の外側にある負荷サイクルを有する信号に対して D C C を行なうように構成され得る。さらなる他の利点は、本発明の当業者にとって明白になるであろう。

40

#### 【 0 0 1 7 】

本発明のその他の目的および利点は、以下の詳細な説明を読み、添付の図面を参照することによって、明らかとなるであろう。

#### 【 0 0 1 8 】

本発明は、様々な変形や代替的な形態の対象となる一方、本発明の具体的な実施形態が、図面およびこれに伴う詳細な説明において例として示される。図面および詳細な説明は

50

、記載されている特定の実施形態に本発明を限定することが意図されていないことが理解されるべきである。そうではなく、本開示は、添付の請求項において規定される本発明の範疇に含まれる全ての変形物、等価物、代替物を網羅することが意図されている。

#### 【0019】

本発明の実施形態が以下に記載される。以下に記載されるこれらの実施形態およびその他のあらゆる実施形態は、限定的ではなく、例示的でまた本発明を例証するものであることに留意されたい。

#### 【0020】

本明細書に記載されているように、本発明の様々な実施形態は、相違する供給電圧を有する領域内のIC部品相互間で信号を伝送するためのシステムおよび方法を具備し、AC接続が用いられて信号の共通モード電圧があるレベルから別のレベルへと変化させられる速度が上げられる。

10

#### 【0021】

一実施形態では、回路デザインは、供給電圧が相違する2つの電力領域を接続するAC接続レベル・シフタを含んでいる。入力信号は起点供給電圧においてバッファされ、また、AC成分はDC成分（起点共通モード電圧）から分離される。AC成分は、次に、行き先共通モード電圧のレベルへと変えられ、行き先供給電圧でバッファされる。AC接続によって、回路は従来のレベル・シフト回路を用いて達成可能な周波数より高い周波数で動作することが可能になる。この回路は負荷サイクル補償／補正（DCC）を含み得る。DCCの適用は、所望により、交互に有効または無効にされ得る。

20

#### 【0022】

本発明の実施形態によって、従来のシステムに対する多くの利点が提供され得る。第1に、本システムおよび方法は置換の対象である従来システムによって可能な周波数よりも高い周波数で動作することが企図されている。また、上記のように、本発明の幾つかの実施形態は、レベル・シフトされた信号の負荷サイクルを修正することさえ可能である。

#### 【0023】

一実施形態では、回路デザインは、供給電圧が相違するとともにこれに相応して共通モード電圧が相違する2つの電力領域を接続するAC接続レベル・シフタを含んでいる。負荷サイクル補償を可能にするために、入力信号および反転された入力信号が別々に処理され、次いで結合される。それらは、複製された複数の回路枝を介して、同時に同様のやり方で処理される。

30

#### 【0024】

入力信号は、增幅バッファを用いて起点領域の供給電圧でバッファされ、入力信号が電圧範囲（すなわち0から供給電圧まで）に亘って十分に振れることを保証する。さらに、下に説明されるように、電圧推移は、DCCの目的のために意図して遅延させられる。次に、AC成分は、キャパシタを用いて、DC成分から分離される。次に、共通モード（DC）成分は、行き先領域の供給電圧の半分で入力信号へ再度、導入される。反転された入力信号は回路の複製された枝を通過し、同じ共通モード電圧の入力信号の反転されたコピーを生成する。

40

#### 【0025】

レベル・シフトによって信号の負荷サイクルが変化し得るので、入力および反転された入力の両方に由来する処理された信号は差動増幅器内で結合される。遅延させられた信号推移と共にモード電圧の変化させられたレベルとの影響の組合せによって、信号の負荷サイクルが補正される。そして、得られた（負荷サイクル補正された）信号は、行き先領域の供給電圧でバッファされます。負荷サイクル補正を行なう回路が選択的に無効にされてシステムがより高い周波数で動作することが可能にされ得る。

#### 【0026】

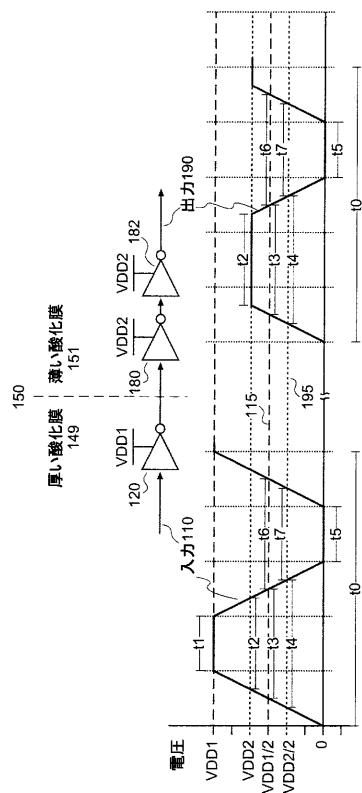

本発明について詳細に記載する前に、従来のレベル・シフト回路を見直すことが有用であり得る。図1は単純なバッファ・システムの図である。この単純な配置が用いられて領域149および領域151のような異なる電力領域内の部品が接続されてきた。領域14

50

9 および領域 151 は、それぞれ、信号の起点および行き先領域である。入力信号 110 は、0 V (ゼロボルト) と VDD1 (起点領域の供給電圧) の間で振れ、VDD1 / 2 (115) の共通モード電圧付近に中心を置いている。この信号は、起点領域供給電圧 VDD1 でインバータ 120 を通過し、次いで、行き先供給電圧 VDD2 のインバータ 180、182 へと向う。この例において、VDD1 は VDD2 より大きい。インバータ 182 の出力が (入力に対して) 切り詰められて、信号は、今や、0 から VDD2 まで振れるようになる。

#### 【0027】

この配置によって、負荷サイクルが変化する。図 1 中の入出力信号を比較することによって、負荷サイクルの変化が明らかになる。負荷サイクルは、本質的に信号がハイである (すなわち、共通モード電圧を越えている) 時間の割合である。特に、負荷サイクルは、全領域の割合としての、共通モード電圧を越えている領域である。この領域は、信号と共通モード電圧によって区画される領域として定義されます。

10

#### 【0028】

入力信号 110 は、50% の負荷サイクルを有している。最小電圧は 0 であり、最大電圧は VDD1 である。間隔 t1 は間隔 t5 と等しく、間隔 t3 は間隔 t6 と等しく、VDD1 / 2 の共通モード電圧からの振れは等しい (VDD1 / 2)。出力信号 190 は、入力信号 110 が一部切断されたものである。出力信号 190 が 0 と VDD2 の間の値だけを有することができるので、信号の VDD2 を越える部分は結果的に切り取られている。

20

#### 【0029】

出力信号 190 を考えてみると、最小電圧は 0 であり、最大電圧は VDD2 であり、VDD2 / 2 の共通モード電圧からの振れは等しい (VDD2 / 2)。間隔 t2 は間隔 t5 より大きく、間隔 t4 は間隔 t7 より大きい。したがって、出力信号 190 は、50% を超える負荷サイクルを有している。

#### 【0030】

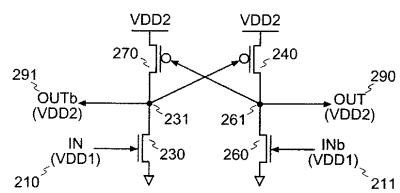

ただ今記載されたこの配置によって作製された負荷サイクル・エラー (50% から 50% を超える値までの変化) を回避するために、レベル・シフタが使用される。図 2 は典型的なレベル・シフタの図である。

#### 【0031】

図 2 のレベル・シフタは 2 つの NMOS および 2 つの PMOS トランジスタを用いて実現されている。(1 つの NMOS および 1 つの PMOS トランジスタから構成される) NMOS / PMOS トランジスタ・ペアは各々、供給電圧 VDD2 とグランドと直列接続されている。レベル・シフタ入力は、それぞれ、NMOS トランジスタ 230、260 に接続された入力信号 (210) および反転された入力信号 (211) である。NMOS / PMOS トランジスタ・ペアは、ノード 231、261 から PMOS トランジスタ入力 240 および 270 にそれぞれクロス接続されている。その出力 (および反転された出力) はノード 231 (また 261) で提供される。

30

#### 【0032】

図 2 のレベル・シフタにおいて、入力 210 が VDD1 (ハイ) であると、トランジスタ 230 はグランドへと短絡し、トランジスタ 240 は VDD2 へと短絡する。その結果、出力 290 は VDD2 (ハイ) である。入力 210 がハイであるので、反転入力 211 は、0 (ロー) であり、トランジスタ 260 は開いており、PMOS トランジスタ 270 のノード 261 からの入力は VDD2 (ハイ) であろう。トランジスタ 240 が VDD2 へと短絡されているのでトランジスタ 270 は閉じており、トランジスタ 230 がグランドへと短絡されているので出力 291 は 0 (ロー) であろう。反対に、入力 210 が 0 (ロー) で、反転入力 211 が VDD1 (ハイ) であると、出力 290 は 0 (ロー) であり、出力 291 は VDD2 (ハイ) である。

40

#### 【0033】

一般に、図 2 の従来の回路は、1 GHz を越えて動作するシステムでのように高周波で用いられることがない。高速動作用に用いられることが可能な AC 接続レベル・シフ

50

タの実施形態が、次に記載される。

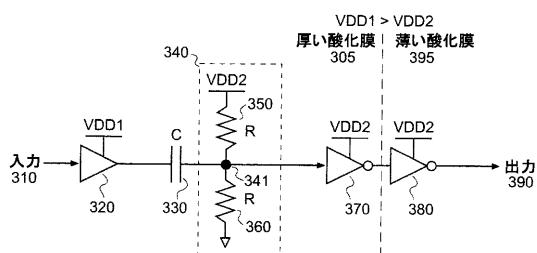

【0034】

図3、図4に例示されているのは、高速動作用のAC接続レベル・シフタである。両方のレベル・シフタは同様に構成されている。図3のレベル・シフタの部品はバッファ320、キャパシタ330、分圧器340、インバータ370、380を含んでいる。これらの部品は直列接続されている。分圧器340は供給電圧とグランドとの間に直列接続された抵抗350、360を含んでおり、抵抗相互間の中間ノード341を伴っている。2つの電力領域がある。すなわち、高電圧領域と低電圧領域である。高電圧領域は、例えばアナログ回路に関連し得、他方低電圧領域はデジタル回路に関連し得る。典型的には、高電圧領域はより厚い酸化膜で実現され、低電圧領域はより薄い酸化膜で実現されるであろう。

10

【0035】

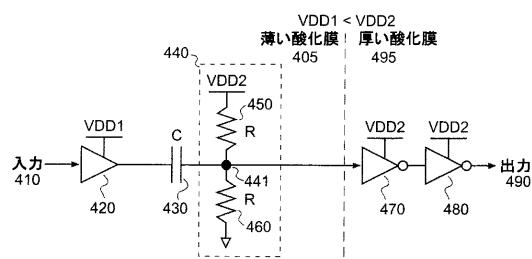

同様に、図4のレベル・シフタの部品は、直列に接続された、バッファ420、キャパシタ430、分圧器440、インバータ470、480を含んでいる。分圧器340も、供給電圧とグランドの間で直列接続された2つの抵抗(350、360)を含んでおり、抵抗相互間の中間ノード(441)を伴っている。やはり、電力領域の一方はより厚い酸化膜で実現され、他方はより薄い酸化膜で実現されている。

【0036】

電力領域が2つの図の中で反対になっていることに留意されたい。図3では、起点領域(305)は、(VDD2 < 供給電圧VDD1を有する)高電圧領域である。図4では、起点領域(405)は、(VDD > 供給電圧VDD1を有する)低電圧領域である。図3では、部品320、330、340、370は起点である高電圧領域305にあり、部品380は行き先である低電圧領域395にある。図4では、部品420、430、440は起点である低電圧領域405にあり、部品470、480は行き先である高電圧領域495にある。

20

【0037】

図4は図3と本質的に同じ構造を有している。以下の図3の記載において、図4の対応する部品は括弧の中に示されている。

【0038】

入力310(410)は、バッファ320(420)の入力に接続されている。バッファ320(420)は、供給電圧VDD1を有している。バッファ320(420)の出力は、キャパシタ330(430)を介してインバータ370(470)の入力に接続されている。このキャパシタはAC接続をもたらし、入力のDC成分を分離するとともにAC成分を通過させる。分圧器340(440)の抵抗350(450)は供給電圧VDD2に接続されており、分圧器340(440)の抵抗360(460)はグランドに接続されている。中間ノード341(441)はVDD2/2の電圧に維持されている。2つの抵抗は、相互に接続されるとともに中間ノード341(441)において回路の残り部分に接続されている。インバータ370(470)、380(480)は直列接続されており、インバータ380(480)の出力は出力信号390(490)である。

30

【0039】

入力信号310(410)は、0V(セロボルト)とVDD1(起点領域の供給電圧)の間で振れる。入力信号310(410)は、ほぼ共通モード電圧VDD1/2を中心を置いている。出力信号390(490)は、0V(ゼロボルト)とVDD2(行き先領域の供給電圧)の間で振れる。AC接続および分圧器340(440)を用いることによって、中間ノード341(441)における信号の共通モード電圧は、VDD2/2へ変化させられる。この信号はインバータ370(470)へ入力される。インバータ380(480)の出力390(490)は、VDD1 - VDD2電圧差に関わらず、入力310の(410の)負荷サイクルとほぼ同じ負荷サイクルを有している。

40

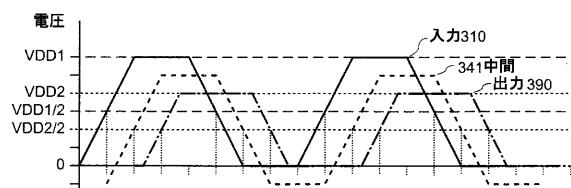

【0040】

図5では、3つの波形が例示されている。すなわち、入力信号、中間信号、出力信号で

50

ある。この例において、図3のように、VDD1はVDD2より大きい。入力310は、0V(ゼロボルト)および供給電圧VDD1の間で振れるとともにVDD1/2の共通モード電圧を有している。例示されているように、負荷サイクルは50%である。(中間ノード341における)中間信号541は、入力310と同じAC変化を有する。ただし、分圧器340によって設定されるように、共通モード電圧はVDD2/2である。中間信号541の負荷サイクルは50%である。出力信号390は、中間信号541と同じ共通モード電圧を有する。ただし、インバータ370、380によって設定されるように、0V(ゼロボルト)および供給電圧VDD2の間で振れる。出力信号390の負荷サイクルは50%である。

【0041】

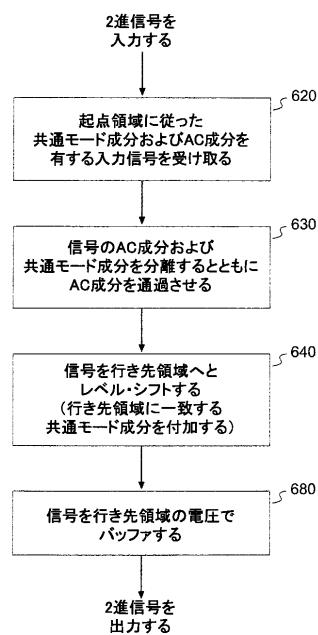

10

図3乃至図5との関連で記載された実施形態の基本動作は、図6に示されているように要約されることが可能である。図6は、一実施形態に従ったレベル・シフト方法のフローチャートである。この図において示されているように、(起点領域の供給電圧に従ったAC成分および共通モード成分を有する)起点領域の入力2進信号が受け取られる(ブロック620)。この信号のAC成分が、起点共通モード電圧から分離される(ブロック630)。次に、このAC成分は、行き先領域の共通モード電圧のレベルへと変化させられる(ブロック640)とともに行き先供給電圧でバッファされる(ブロック680)。この出力された2進信号が、次に、行き先領域において利用されることが可能である。

【0042】

20

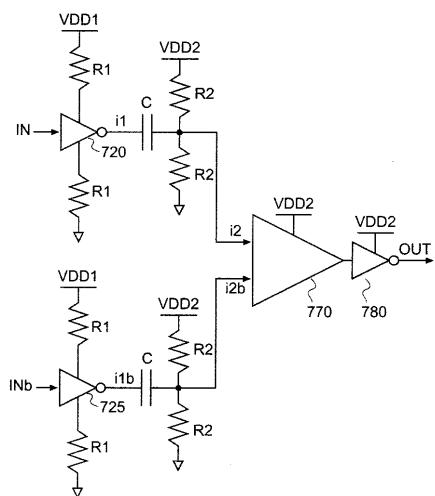

図3および図4の実施形態は、非常に高い周波数で動作することができるとともに供給電圧依存性を有していないが、入力信号における負荷サイクル・エラーについて補正を行うことができない。図7は一実施形態に従った、負荷サイクル補償/補正(DCC)を附加されたAC接続レベル・シフタを例示している。2つの処理された信号の組合せが用いられて出力信号を決定する。図8は、一実施形態、例として図7に例示されている実施形態に関連し得る例示的な信号(波形)を例示している。

【0043】

30

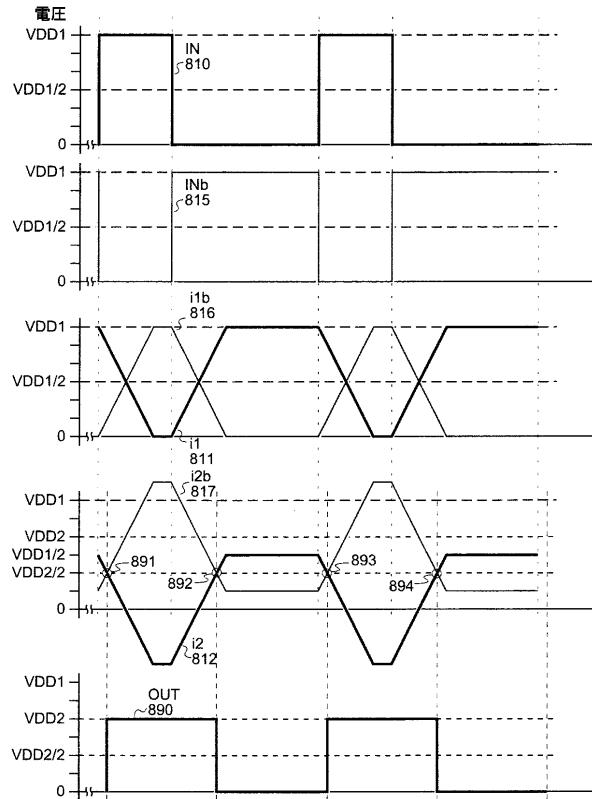

図7の回路は、2本の上流の枝を有している。これらの枝は同じデザインである。しかし、各々の入力信号は他方の反転信号である。入力信号810および反転入力信号815は、2つの枝によって別々に処理される。そして、それらが結合されるとともに反転されてDCCを完成させる。

【0044】

30

図7の中の枝のうちの1つ目は、直列接続されたインバータ720、キャパシタ730、分圧器740を含んでいる。同様に、枝のうちの2つ目は、直列に接続されたインバータ725、キャパシタ735、分圧器745を含んでいる。各枝は差動増幅器770の入力のうちの1つに接続されている。差動増幅器の出力はインバータ780に接続されている。

【0045】

40

回路の動作が、図8に例示されている典型的な波形の援助を用いて説明される。この例において、起点電力領域の供給電圧VDD1は、行き先電力領域の供給電圧VDD2より大きい。入力信号810は0V(ゼロボルト)からVDD1まで振れ、50パーセント未満の負荷サイクルを有している。波形が実質的に正方形で、信号は時間のおよそ3分の1の間ハイであることに留意されたい。信号INb(815)は信号IN(810)を反転したものである。

【0046】

40

インバータ720、725は、ゼロとVDD1の間の電圧推移を修正するための抵抗を含んでいる。その信号i1(811)、i1b(816)の波形においてそれぞれ示されているように、入力IN(810)、INb(815)の正方形波形において見られるほぼ瞬間的な電圧変化は、インバータ720、725によって時間に亘って引き延ばされる。これは、インバータ720/725とVDD1/グランドとの間に抵抗を加えた結果であり、これによってインバータを通って流れる電流を減じる。キャパシタ730、735

50

は A C 接続をもたらす。分圧器 740、745 は、キャパシタから受け取った信号を変化させて V D D 2 / 2 の共通モード電圧を提供する。この変化は、信号 i2(812)、i2b(817) の波形において見ることができる。

#### 【0047】

差動増幅器 770 は入力として信号 i2(812)、i2b(817) を取る。その入力の差をとる際に、差動増幅器 770 は結果的に信号を増幅し、電圧推移のタイミングを修正する。信号 i2(812)、i2b(817) の、波形交差(交差点) 891、892、893、894 に留意されたい。これらの点は、信号間の差はゼロである。交差点 891、892 の間で、差はゼロ未満である。交差点 892、893 の間で、差はゼロより大きい。そして、増幅された電圧差は、インバータ 780 によって反転される。インバータ 780 は、差動増幅器 770 の出力をバッファし、行き先領域の動作電圧範囲へと切り詰められた信号を生成する(すなわち、信号はゼロから V D D 2 までの振れに制限される)。その結果、出力信号 OUT(890) は、0 V(ゼロボルト) から V D D 2 まで振れる実質的に正方形の波形であり、負荷サイクルは 50 パーセントである。

10

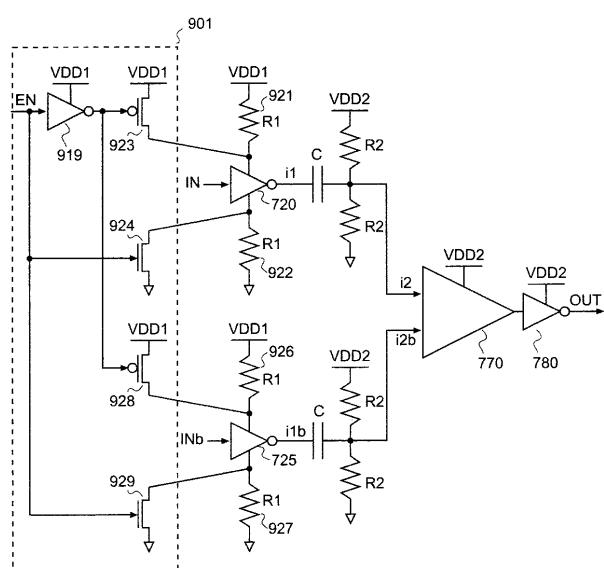

#### 【0048】

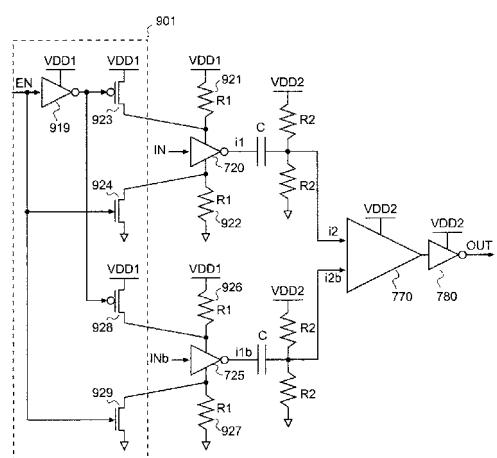

図 7 の回路は、図 2 の従来の回路よりは高いレートで動作することが可能であるが、図 3 の回路ほどの高レートで動作することはできない。これは、D C C 回路内の信号の増幅の結果である。図 9 の A C 接続レベル・シフタ実施形態は、図 7 の回路にスイッチング回路 901 を加えて D C C 機能がオン、オフされることを可能にする。

20

#### 【0049】

スイッチング回路 901 は、インバータ 710、715 の振る舞いを修正するために用いられる 2 つの N M O S および 2 つの P M O S スイッチング・トランジスタを含んでいる。各スイッチング・トランジスタは、インバータとインバータに取り付けられる抵抗のうちの 1 つとの間に接続される。P M O S トランジスタ 923 は供給電圧 V D D 1 をインバータ 720 に接続し、N M O S トランジスタ 924 はインバータ 720 をグランドに接続する。P M O S 928 は供給 V D D 1 をインバータ 725 に接続し、他方 N M O S トランジスタ 929 はインバータ 725 をグランドに接続する。

20

#### 【0050】

スイッチング・トランジスタ入力はスイッチング信号 E N に接続されている。信号 E N は、N M O S スイッチング・トランジスタ 924、929 に直接接続され、またインバータ 919 を介して P M O S スイッチング・トランジスタ 923、928 に接続されている。E N = 0 のとき、4 つのトランジスタはすべて開いたスイッチとして振る舞い、この結果、インバータ 720、725 は抵抗 921、922、926、927 を介して V D D 1 とグランドに接続される。E N = 1 のとき、4 つのトランジスタはすべて閉じたスイッチとして振る舞い、結果的に抵抗 921、922、926、927 を迂回させるとともにインバータ 720、725 を V D D 1 とグランドに本質的に直接接続する。

30

#### 【0051】

D C C が有効にされているとき (E N = 0)、回路は、図 7 と同様の D C C 有りの A C 接続レベル・シフタ(低速動作)として動作する。D C C が無効にされているとき (E N = 1)、回路は、D C C 無しの A C 接続レベル・シフタ(高速動作)として動作する。すなわち、スイッチング回路が「活性とされている」場合、スイッチング回路の各 N M O S ・ P M O S トランジスタ・ペアは、それぞれ接続されたインバータを供給電圧とグランドに直接分路し、それによって D C C を無効にする。そうではなく、スイッチング回路が「非活性とされている」場合、図 9 の回路は図 7 の回路の説明において上で説明されているように機能する。

40

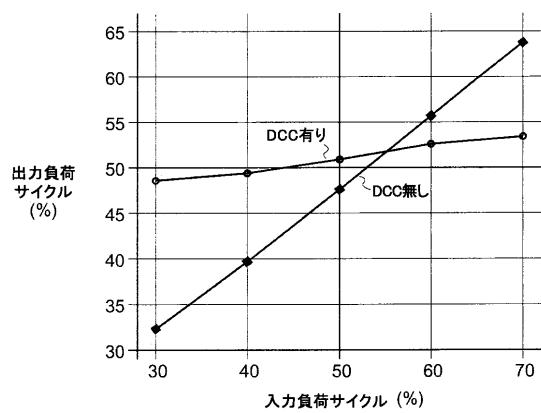

#### 【0052】

図 11 は、図 9 に例示されている実施形態のシミュレーションの結果を示している。5 G h z のシステム周波数が用いられた。供給電圧は、V D D 1 = 1.5 V、V D D 2 = 1.0 V に設定された。結果は、図 11 において表にされるとともにプロットされている。入力信号の負荷サイクルは 30 % から 70 % まで変化させられた。D C C 無しでは、得ら

50

れる出力信号の負荷サイクルはわずかに改善され、32%と64%の間で変化する。DCCが有効にされていると、得られる出力信号の負荷サイクルは著しく改善され、45%から50%までに亘る。

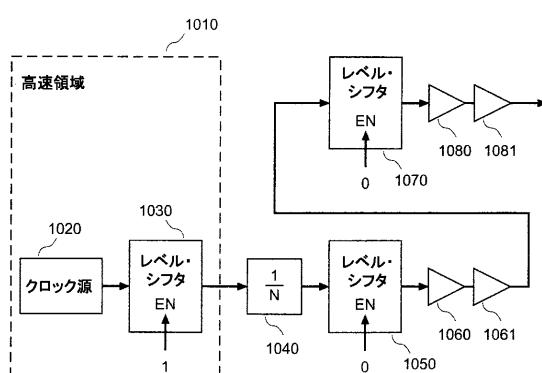

#### 【0053】

図9の回路は、例えばクロック・ツリー内の負荷サイクル・エラーを補正するためのクロック・バッファとして用いられることが可能である。図10はそのようなシステムを例示している。第1クロック速度で動作する、クロック源1020（例えば、電圧制御発振器）によって駆動されるクロック・ツリーを検討する。このクロック・ツリーによって供給された集積回路の幾つかの部分は第1クロック速度のクロック信号を用い得、他方、集積回路の他の部分はより遅いクロック速度で動作し得る。クロック分割器1040は因数Nだけクロック速度を減少させてより遅いクロック信号を供給する。

10

#### 【0054】

負荷サイクル・エラーは、様々な地点でクロック・ツリーに導入され得る。例えば、負荷サイクルは、インバータ1060、1061、1080、1081による増幅によって影響され得る。（スイッチング回路を備えた）図9のAC接続レベル・シフタが、この例において3回現われている。すなわち、レベル・シフタ1030、1050、1070である。クロック分割器1040の上流において、レベル・シフタ1030はより高いクロック速度で動作できなければならない。レベル・シフタ1030のDCC回路を無効にすることによって、レベル・シフタ1030は、この高いクロック速度で動作することができる。クロック分割器1040の下流において、クロック周波数はクロック信号に修正を適用できほどに十分に低い。したがって、レベル・シフタ1050、1070のDCC回路が有効にされてクロック信号の負荷サイクルの修正が可能になる。よって、DCCは、レベル・シフタ1030用のより高速の領域1010内では有効にされない（EN=1）が、レベル・シフタ1050、1070用のより低速の領域内では有効にされる（EN=0）。したがって、DCCは、修正しないと累積するとともに集積回路の動作を妨げる負荷サイクル・エラーを修正することができる。

20

#### 【0055】

先行する記載は幾つか具体的な典型的な実施形態を示しているが、代替的な実施形態において、記載された特徴および部品の多くの変形体があり得る。例えば、スイッチング回路は様々な方法で実現され得る。一実施形態では、DCCスイッチング回路は、NMOSおよびPMOSトランジスタの両方の代わりに1つのタイプのトランジスタを用いることが可能である。別の実施形態では、スイッチング回路は、DCC回路を選択的に有効におよび無効にするDCC決定ユニットに接続される。DCC決定ユニットは、評価用の様々な測定値または評価値のうちのいずれか（すなわち、入力信号、中間信号、出力信号、クロック周波数など）を用いることが可能である。例えば、その評価は、入力負荷サイクルの閾値との比較に基づくことができる。

30

#### 【0056】

代替的な実施形態は、上で用いられている基準と異なる基準を用いて、負荷サイクル補償を実行し得る。上の記載におけるインバータに接続された抵抗の対は、同数で且つ固定されているが、そうであることは必須ではない。さらに別の実施形態では、差動増幅器が用いられてAC接続を行なうことが可能である。他の多くの変形体も、本開示を読めば当業者に対して明白になるであろう。

40

#### 【0057】

当業者は、情報および信号が様々な異なる技術および手法を用いて表現され得ることを理解するであろう。例えば、上の記載を通じて言及されたデータ、情報、信号等は、電圧、電流等によって表現され得る。情報および信号は、ワイヤ、金属配線、ビア等を含むあらゆる適切な輸送媒体を用いて、開示のシステムの部品相互間で通信される。

#### 【0058】

本明細書に開示の実施形態との関連で説明された様々な説明用の論理ブロック、モジュール、回路は、特定用途向け集積回路（ASIC）、フィールド・プログラマブル・ゲ

50

ト・アレイ (FPGA) または他の論理装置、ディスクリート・ゲートまたはトランジスタ・ロジック、ディスクリート・ハードウェア要素、これらの本明細書に記載の機能を実行するように設計されたあらゆる組み合わせとともに実現および実行されることが可能である。

【0059】

本発明によってもたらされる利益および利点は、具体的な実施形態に関して上に記載された。これらの利益および利点、およびこれらの利益および利点を生み出すまたはよりはつきりしたものとする要素および限定事項は、いずれも、請求項のいずれかまたは全ての限定的な、必要な、必須の特徴と解釈されるべきではない。本明細書で用いられているように、「具備する」という文言またはその変形体は、これらの文言に先行する要素および限定事項を非排他的に含むものとして解釈されることが意図されている。よって、要素の組を具備するシステム、方法または他の実施形態は、これらの要素のみに限定されるではなく、明白に列挙されていないまたは請求項に記載の実施形態に本来備わっている他の要素を含み得る。

【0060】

開示された実施形態のここまで説明は、当業者が本発明を実行および使用することを可能にするために提供される。これらの実施形態に対する様々な変形は、当業者にとって容易に明らかとなり、本明細書で定義されている包括的な原理は、本発明の思想および範疇から逸脱することなく他の実施形態に適用されてよい。よって、本発明は、本明細書に示す実施形態に限定されることが意図されるのではなく、本明細書に開示された請求項内で列挙される原理および新規な特徴に従った最も広い範疇に一致するべきである。

【0061】

また、この発明は以下の実施態様を取り得る。

【0062】

(1) A C 成分と第1電圧の第1共通モード成分とを有する入力2進信号を受け取り、前記A C成分を前記第1共通モードから分離し、第2電圧の第2共通モード成分を前記A C成分に加え、前記A C成分と前記第2電圧の前記第2共通モード成分とを有する2進出力信号を提供する、ことを具備する、2進信号をレベル・シフトする方法。

【0063】

(2) 負荷サイクル補償 (DCC) を行なうことをさらに具備する、(1)の方法。

【0064】

(3) 第1モードまたは第2モードのいずれかで交互に動作することをさらに具備し、前記第1モードにおいて、DCCが行なわれ、前記第2モードにおいて、DCCが行なわれない、(2)の方法。

【0065】

(4) 前記入力2進信号の負荷サイクルが許容範囲外にあるとき、前記第1モードで動作する、(3)の方法。

【0066】

(5) 前記第1電圧は前記第2電圧より大きい、(1)の方法。

【0067】

(6) 前記第2電圧は前記第1電圧より大きい、(1)の方法。

【0068】

(7) 2進入力信号のA C成分とD C成分とを分離し、前記A C成分を新しいD C成分に付加することによって、レベル・シフトされた2進出力信号を生成するように構成されたレベル・シフタ。

【0069】

(8) 前記レベル・シフタは、2進入力信号を受け取るとともに前記A C成分を中間ノードへと渡すように構成されたキャパシタを含み、それによって、前記A C成分と前記D C成分とを分離する、(7)のレベル・シフタ。

【0070】

10

20

30

40

50

(9) 前記中間ノードで所望の電圧を維持するように構成された回路をさらに具備する、

(8) のシステム。

【0071】

(10) 前記所望の電圧を維持するように構成された前記回路は分圧器を具備する、(9)

のシステム。

【0072】

(11) 前記分圧器は、供給電圧とグランドとの間に直列接続された2つの抵抗を具備し、

前記中間ノードは、前記2つの抵抗の間に位置する、(10) のシステム。

【0073】

(12) 前記負荷サイクルを修正して前記負荷サイクルを所望の値へと変化させるように

構成された負荷サイクル補償(DCC)回路をさらに具備する、(7) のシステム。 10

【0074】

(13) 前記負荷サイクルを修正して前記負荷サイクルを所望の値へと変化させるように

構成された負荷サイクル補償(DCC)回路をさらに具備する、(11) のシステム。

【0075】

(14) 前記DCC回路は、分圧器、キャパシタ、インバータを具備し、前記インバータ

は2つの抵抗に接続され、前記第1抵抗は前記インバータと供給電圧との間に接続され、

前記第2抵抗は前記インバータとグランドとの間に接続された構造を有する、第1素子構

造と、前記第1素子構造と等価の構造を有する第2素子構造と、を具備し、両方の枝は差

動増幅器の入力に接続され、前記第1素子構造は入力信号を受け取るように接続され、前

記第2素子構造は反転された前記入力信号を受け取るように接続され、前記差動増幅器の

出力はアンプに接続される、(13) のシステム。 20

【0076】

(15) 前記DCCを選択的に有効および無効にするように構成されたスイッチング回路

をさらに具備する、(14) のシステム。

【0077】

(16) 前記スイッチング回路は、すべては開いた状態またはすべて閉じた状態のいずれ

かであるように構成された4つのトランジスタを具備し、各トランジスタは、前記抵抗の

うちの前記インバータのうちの1つと接続された1つを選択的に分路する、(15) のシ

ステム。 30

【0078】

(17) 測定基準を評価するとともに前記スイッチング回路へ制御信号を供給するように

構成されたDCC決定ユニットをさらに具備する、(15) のシステム。

【0079】

(18) 前記測定基準は負荷サイクル値を許容範囲または閾値と比較したものである、(17)

のシステム。

【0080】

(19) 前記負荷サイクルは前記入力信号の負荷サイクルである、(18) のシステム。

【図面の簡単な説明】

【0081】

【図1】従来技術に従った2つの異なる供給電圧領域間のインターフェースを跨ぐための

単純なシステムを示す機能ブロック図である。

【図2】従来技術に従った典型的なレベル・シフタを示す機能ブロック図である。

【図3】一実施形態に従った単純なレベル・シフト・システムを示す機能ブロック図である。

【図4】別の実施形態に従った単純なレベル・シフト・システムを示す機能ブロック図である。

【図5】一実施形態に従った負荷サイクルの変化を伴ったレベル・シフテトの例である。

【図6】一実施形態に従った方法を示すフローチャートである。

【図7】一実施形態に従った、負荷サイクル補償を伴ったレベル・シフト・システムを示

す機能ブロック図である。

【図 8】一実施形態に従った、負荷サイクル補償を伴ったレベル・シフトの例である。

【図 9】一実施形態に従った、負荷サイクル補償スイッチング回路を組み込んだレベル・シフト・システムを示す機能ブロック図である。

【図 10】一実施形態に従った、レベル・シフトを用いたクロック・ツリーを例示する機能ブロック図である。

【図 11】一実施形態に従ったレベル・シフタにおける負荷サイクル補償の効果の例である。

【図 1】

図 1

【図 2】

図 2

【図 3】

図 3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

| 入力負荷<br>サイクル<br>(%) | 出力負荷サイクル (%)    |                 |

|---------------------|-----------------|-----------------|

|                     | EN=0<br>(DCC有り) | EN=1<br>(DCC無し) |

| 30                  | 48.6            | 32.3            |

| 40                  | 49.4            | 39.7            |

| 50                  | 50.9            | 47.6            |

| 60                  | 52.6            | 55.7            |

| 70                  | 53.4            | 63.8            |

## フロントページの続き

(74)代理人 100108855

弁理士 蔵田 昌俊

(74)代理人 100091351

弁理士 河野 哲

(74)代理人 100088683

弁理士 中村 誠

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100100952

弁理士 風間 鉄也

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100070437

弁理士 河井 将次

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 金子 正昭

アメリカ合衆国、 カリフォルニア州、 サンノゼ、 リンコン・サークル 1060 東芝アメリカ電子部品社内

(72)発明者 デビッド・ボアストロー

アメリカ合衆国、 テキサス州、 オースチン、 バーネットロード 11400

(72)発明者 エスキンダー・ハイル

アメリカ合衆国、 テキサス州、 オースチン、 バーネットロード 11400

(72)発明者 ジーミン・キ

アメリカ合衆国、 テキサス州、 オースチン、 バーネットロード 11400

F ターム(参考) 5J056 AA03 AA11 BB02 CC00 CC21 DD13 DD28 DD51 FF08 FF09

KK01