# PATENT SPECIFICATION

(11) 1 594 476

1 594 476

(21) Application No. 42935/77 (22) Filed 14 Oct. 1977

(31) Convention Application No. 51/123166

(32) Filed 14 Oct. 1976 in

(33) Japan (JP)

(44) Complete Specification published 30 July 1981

(51) INT CL<sup>3</sup> H03K 4/00 G09G 1/10

(52) Index at acceptance

H4T 4S BSA

(19)

## (54) IMPROVEMENTS IN ELECTRON BEAM DEFLECTION CONTROL SYSTEM

(71) We, HITACHI, LTD., of 1—5—1, Marunouchi, Chiyoda-ku, Tokyo, Japan, a body corporate organized according to the laws of Japan, and 5 NIPPON TELEGRAPH and TELEPHONE PUBLIC CORPORATION of 1—16, 1-chome, Uchiasawai-cho, Chiyada-ku, Tokyo, Japan, a body corporate organized according to the laws of Japan, do hereby 10 declare the invention, for which we pray that a patent be granted to us, and the method by which it is to be performed, to be particularly described in and by the following statement:—

15 The present invention relates to an electron beam deflection control system which is suitable for use in an electron beam exposure system, or a graphic display system.

20 The electron beam exposure system functions to form a minute pattern of a semiconductor device or circuit on a mask or a semiconductor wafer with an electron beam. In order to draw the necessary 25 pattern with the electron beam, it employs an electron beam deflection control system which deflects the electron beam linearly at a uniform speed and which, upon completion of the drawing of one pattern, 30 cuts off the electron beam and moves it to the starting point of the next pattern.

The electron beam deflection control system of this type includes a digital system and an analog system.

35 A known electron beam deflection control system based on the digital system is one wherein coordinate data corresponding to respective points of a line pattern are sequentially generated in 40 accordance with data fed from a digital computer, and are then converted into an analog signal in a stepped shape by a digital-to-analog converter, the electron beam being deflected stepwise.

45 With such a known system, however, the settling time of the digital-to-analog converter, which determines each step

width of the stepped signal, is long. Disadvantageously, therefore, as the line pattern becomes longer, the drawing time becomes longer. 50

A known electron beam deflection control system based on the analog system is one wherein a closed loop circuit consisting of a differential amplifier with limiter function and an integrator is provided, start point and end point levels of a drawing pattern generated by a digital-to-analog converter being sequentially impressed on the closed loop circuit, and the outputs of the integrator converge to the end point level, thereby producing a triangular deflection signal.

With such analog system, however, the outputs of the integrator become inaccurate thus degrading the precision of the drawing pattern. Besides, the convergence time of the first-order lag system constructed of the differential amplifier and the integrator increases as a dead time. Therefore, in cases where the drawing pattern is short, the dead time is no longer negligible compared with the drawing time. Since the triangular deflection signal is used also for the movement of the beam between the patterns, the dead time increases still more. 70

It is an object of the present invention to provide an electron beam deflection control system which makes it possible to execute drawing at a very high speed, and also to enhance the precision of a drawing pattern. 75

According to the present invention there is provided an electron beam deflection control system including: generation means to selectively generate either a ramp wave signal varying at a comparatively low speed or a stepped wave signal varying at a comparatively high speed; change-over means to control said generation means so as to generate either the ramp wave signal or the stepped wave signal in response to the required deflection length of an electron beam; and, deflection means to deflect the 80 85 90

electron beam with the signal from said generation means.

5 The present invention will now be described in greater detail by way of example with reference to the accompanying drawings, wherein:—

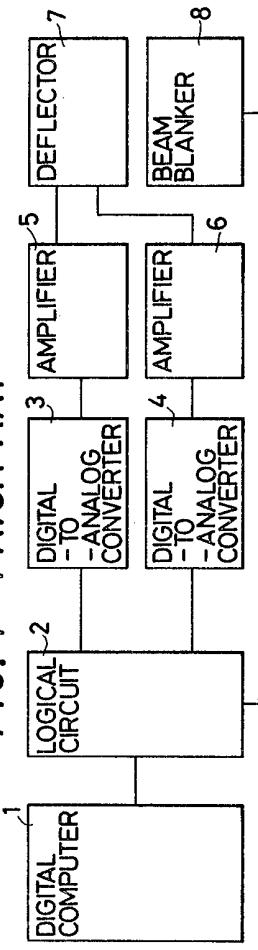

Fig. 1 is a block diagram of a known charged beam deflection control system based on the digital system;

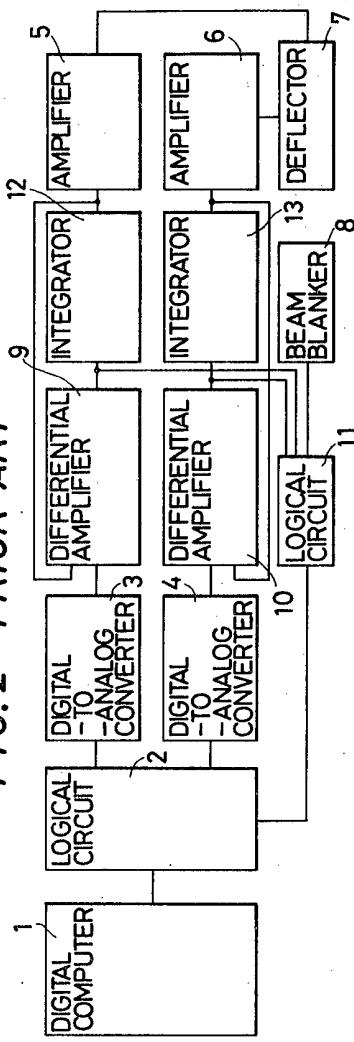

10 Fig. 2 is a block diagram of a known charged beam deflection control system based on the analog system;

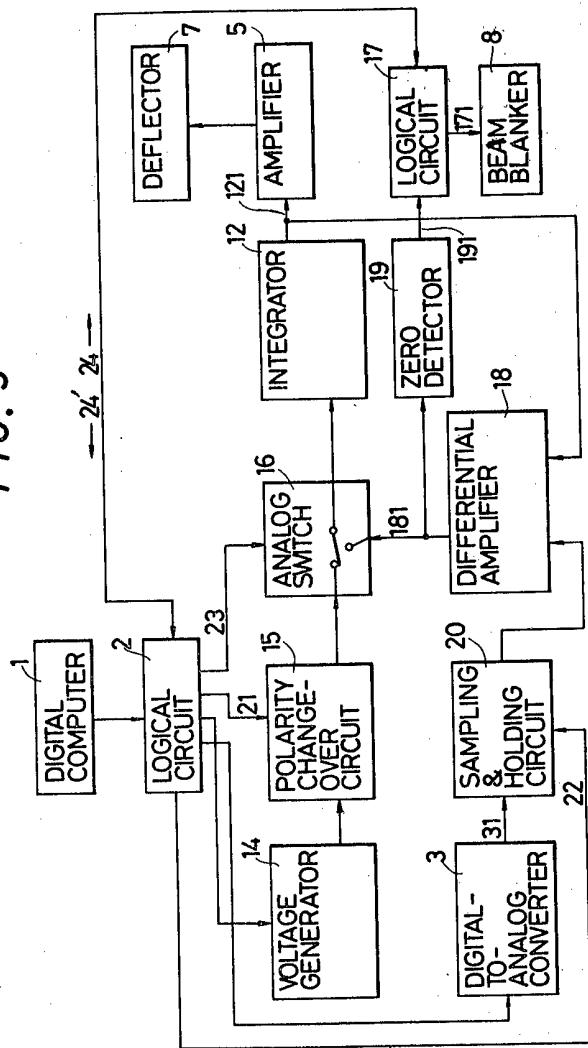

15 Fig. 3 is a block diagram which shows a first preferred embodiment of a charged beam deflection control system;

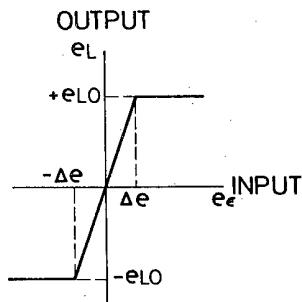

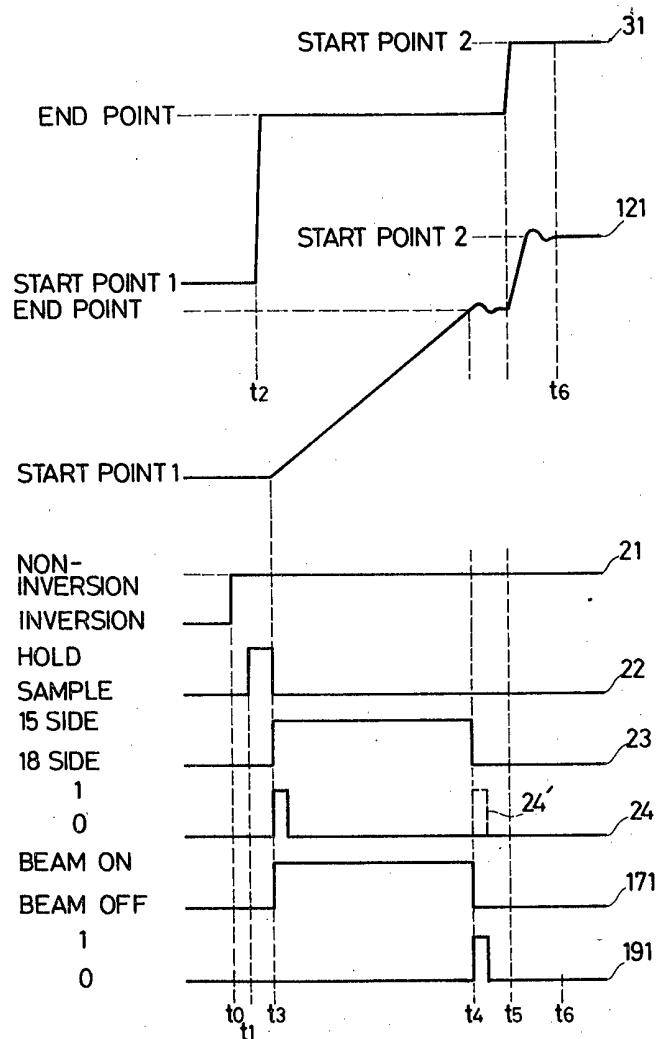

20 Fig. 4 is a graph explaining the operation of the embodiment shown in Fig. 3 as the analog system;

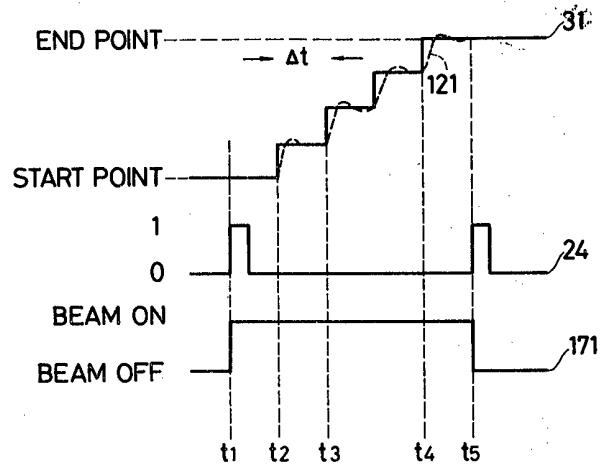

25 Fig. 5 is a graph explaining the operation of the embodiment of Fig. 3 as the digital system;

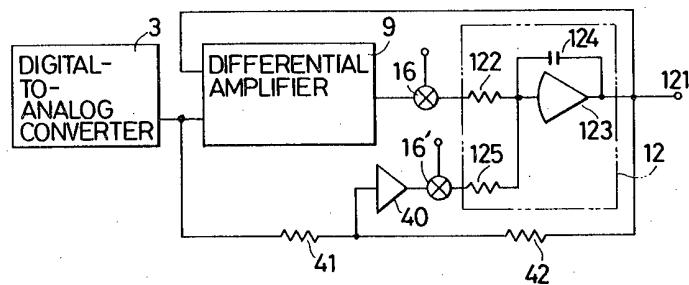

30 Figs. 6(a) and 6(b) are a block diagram and a graph, respectively, which illustrate a second preferred embodiment of the charged beam deflection control system;

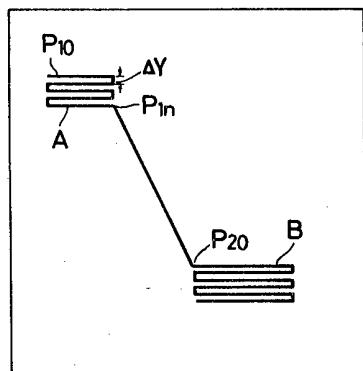

35 Fig. 7 shows an example of a pattern drawn by the second embodiment shown in Figs. 6(a) and 6(b).

40 Referring first to the known beam deflection control system based on the digital system shown in Fig. 1, the system comprises a digital computer 1, a logical circuit 2 for producing a control signal, digital-to-analog converters 3 and 4, amplifiers 5 and 6, for deflection signals, a deflector 7, and a beam blander 8. In operation, coordinate data corresponding to respective points of a pattern are sequentially produced by the logical circuit 2 in accordance with data fed from the digital computer 1. The resultant data are converted into analog signals (voltages or currents) by the digital-to-analog converters 3 and 4. The converter 3 and the amplifier 5 correspond to the x-direction, and the converter 4 and the amplifier 6 to the y-direction. Since the analog signals are in a stepped shape, a beam is deflected stepwise. In this system, the time at which the step is advanced is controlled by a signal of a clock generator contained within the logical circuit 2. A beam blanking signal can be digitally generated by the logical circuit 2. In the case where the movement of the beam is done in the beam blanking state, the digital-to-analog converter 3 or 4 is controlled by the logical circuit 2 so that the beam may arrive at a target point in one block. In the case of this system, the precision of the drawing pattern is excellent. On the other hand the system has the following disadvantage. Each step width of the stepped signal is determined by the settling time of the digital-to-analog

converter. In general, the setting time is long. Therefore, as the drawing pattern becomes longer, the drawing time becomes longer proportionally. The system is accordingly very inconvenient for drawing a long pattern.

70 Referring next to the known beam deflection control system based on the analog system shown in Fig. 2, the system includes the same components 1 to 8 as in the known system shown in Fig. 1. The system additionally includes differential amplifiers 9 and 10 with voltage limiters, a logical circuit 11 for beam blanking signal generation and containing a voltage

75 comparator therein, and integrators 12 and 13. In operation, when the x-directional deflection is considered, an analog signal level corresponding to the start point of line drawing is generated by the digital-to-analog converter 3. Subsequently, an analog signal level corresponding to the end point of the line drawing is generated by the converter 3. Then, owing to the closed loop constructed of the differential amplifier 9 and the integrator 12, when the difference

80 between the output of the converter 3 and an output of the integrator 12 is great and an output of the differential amplifier 9 is limited, the output of the integrator 12 varies at a fixed rate. At this time, a line is

85 drawn whilst providing a beam ON signal at an output of the logical circuit 11 under the control of the logical circuit 2. When the output of the integrator 12 approaches the output of the converter 3, the output of the differential amplifier 9 enters a linear region,

90 and the first-order lag circuit composed of the differential amplifier 9 and the integrator 12 converges to a point at which the output of the converter 3 and that of the differential amplifier 9 coincide. At this time the output of the differential amplifier 9 becomes zero. It is detected by the voltage

95 comparator contained in the logical circuit 11, and a beam OFF signal is provided at the output of the logical circuit 11 so as to

100 blank the beam. This process is repeated, and the scanning and drawing are done by triangular waves. The y-directional deflection is similarly executed by the converter 4, the operational amplifier 10 and the integrator 13.

105 The disadvantages of this system are that the output of the integrator 12 becomes inaccurate in the vicinities of the start and end points of the line thus degrading the

110 quality of the drawing pattern, and that the convergence time of the first-order lag system constituted of the differential amplifier 9 and the integrator 12 increases

115 as a dead time. This is particularly the case, when the length of the drawing line becomes less than about 10  $\mu\text{m}$ , the dead

120 time is no longer negligible in comparison.

125

130

5 with the drawing time. Furthermore it leads to an increase of the dead time to carry out the beam movement under the beam blanking state by the use of the triangular wave signal.

10 Referring now to the first preferred embodiment of an electron beam deflection control system shown in Fig. 3, the components 1, 2, 3, 5, 7, 8 and 12 correspond to the components of the systems shown in Figs. 1 and 2.

15 The system further includes a voltage generator 14 for determining the line speed, polarity change-over circuit 15 for changing-over the polarity of an output from the voltage generator 14, an analog switch 16, a logical circuit 17 for beam blanking signal generation, a differential amplifier 18, a zero detector 19, and a sampling and holding circuit 20. Except for the digital computer 1, the logical circuit and the beam blunker 8, the components corresponding to one axis (x-axis or y-axis) are illustrated in Fig. 3. An identical construction applies to the other axis.

20 The operation of this system will now be explained. First of all, in case of drawing a comparatively long line by the analog system, an analog output signal 31 corresponding to the start point of the line is generated by the digital computer 1, the logical circuit 2 and the converter 3. The sampling and holding circuit 20 is set at a 25 sampling mode in advance, and the output signal therefrom is applied to a first input terminal of the differential amplifier 18. Since an output signal 121 from the integrator 12 is applied to a second input terminal of the differential amplifier 18, an 30 output 181 from the differential amplifier 18 becomes equal to the gain thereof times a voltage which is equal to the difference between the output signals 31 and 121. 35 When a control signal 23 is previously given so as to energize the analog switch 16 so as to pick-up the output from the differential amplifier 18, then the analog switch 16, the integrator 12 and the differential amplifier 40 18 form a first-order lag closed loop. Therefore, the circuitry operates so as to bring the output signals 121 and 31 into 45 coincidence, and the start point of the line is set. The subsequent operation will be explained in conjunction with the graphs 50 shown in Fig. 4. At a time  $t_0$ , data of the end point of the line are compared with data of the start point and the decision of the magnitudes is made by means of the logical 55 circuit 2. A signal 21 for controlling the polarity of the polarity change-over circuit 15 so as to direct the output signal 121 towards the end point is obtained, with 60 which the polarity of the polarity change-over circuit 15 is set to non-inversion or

65 inversion. At a time  $t_1$ , the sampling and holding circuit 20 is placed into a holding mode by a control signal 22 from the logical circuit 2. At a time  $t_2$  slightly later than  $t_1$ , the data of the end point are placed in the converter 3, and an output signal 31 of an analog voltage corresponding to the end point is generated. At a time  $t_3$  slightly after the time  $t_2$ , the analog switch 16 is changed-over from being connected to the differential amplifier 18 to being connected to the polarity change-over circuit 15, by means of a control signal 23 from the logical circuit 2. Then, the integrating operation of the integrator 12 is initiated in conformity with the line speed set by the voltage generator 14 and the polarity set by the polarity change-over circuit 15, and the output signal 121 varies linearly with respect to time. Simultaneously therefore, the logical circuit 17 is rendered operative by a control signal 24, and an output signal in the form of a beam blanking signal 171 energizes the beam blunker 8 in order to start the drawing. At the time  $t_3$ , the sampling and holding circuit 20 is changed-over from the holding mode to the sampling mode by the control signal 22 from the logical circuit 2, and the output signal 31 is applied to the differential amplifier 18. When, at a time  $t_4$ , the output signal 121 coincides with the output signal 31, the output 181 becomes zero, the zero detector 19 operates, providing an output signal 191. The coincidence between the output signal 191 and the beam blanking signal 171 in the logical circuit 17 causes the beam blanking signal to be switched off, so that the drawing is stopped. Simultaneously, a control signal 24' from the logical circuit 17 is fed to the logical circuit 2, the analog switch 16 is changed-over to being connected to the differential amplifier 18 by means of the control signal 23, and a closed loop consisting of the analog switch 16, the logical circuit 17 and the differential amplifier 18 is established so as to settle the output signal 121 to the same level as that of the output signal 31. As will be described in detail later, the output signal 121 is settled to the next start point level between a time  $t_5$  and a time  $t_6$ . The output signal 121 is amplified by the deflection amplifier 6 and then applied to the deflector 7, to deflect the beam. By repeating this process, the pattern can be drawn as a set of lines. In this manner, the triangular wave signal is used for drawing the long line, whereby a higher speed than in the digital system is achieved.

70 75 80 85 90 95 100 105 110 115 120 125 130

Secondly, there will be explained a case of performing the beam movement between patterns by the digital system. For this purpose it will be assumed that at the time  $t_5$  in Fig. 4 the drawing of the first pattern is

completed, and the beam is shifted to the second pattern. At this time, the sampling and holding circuit 20 remains in the sampling mode, to supply the converter 3 with data of the start point of the second pattern and to generate an output signal 31 of an analog voltage corresponding thereto. In this case, the analog switch 16 receives an output from the differential amplifier 18, and the closed loop consisting of the analog switch 16, the integrator 12 and the differential amplifier 18 is established to bring the output signal 121 into coincidence with the output signal 31 at the time  $t_6$ . At this time, the time in which the output signal 121 follows up the output signal 31 is determined by the time-constant of the integrator 12 divided by the gain of the differential amplifier 18, and the speed of drawing is high. Meanwhile, the logical circuit 17 is inhibited by a control signal 24 so as not to operate, and the output signal 171 remains "off".

Next, the system will be described in the case of drawing a short line by the digital system. The sampling and holding circuit 20 is set at the sampling mode by a control signal 22, while the analog switch 16 is connected to receive the output from the differential amplifier 18 by the control signal 23. Accordingly, the output signal 121 follows up the output signal 31 very quickly as shown in Fig. 5.

Digital data corresponding to the start point of the line are fed from the digital computer 1 through the logical circuit 2 to the converter 3. At a time  $t_1$ , the output signal 31 has settled to a level corresponding to the start point. The output signal 171 of the logical circuit 17 is switched on by a control signal 24, and the drawing of a first dot is initiated. At the time  $t_2$ , the clock generator and the counter contained in the logical circuit 2 are started, data corresponding to a second dot are fed from the logical circuit 2 to the converter 3, and the output signal 31 of the converter 3 is shifted and settles to a level corresponding to the position of the second dot. At the time  $t_3$ , the output signal 31 is similarly shifted and settles to a level corresponding to the position of a third dot. In the case,  $\Delta t = t_2 - t_1 = t_3 - t_2$  needs to be greater than the settling time of the digital-to-analog converter, and the interval between the first and second dots needs to be smaller than the diameter of the dot. By this process, the line is drawn as a row of dots. When the dot reaches the end point of the line at the time  $t_4$ , the output signal 171 of the logical circuit 17 is switched off by the control signal 24 at a time  $t_5 = t_4 + \Delta t$ , and the line drawing is completed.

Whether the digital system or the analog system is to be used may be determined by

operating the logical circuits contained in the block 2 in conformity with the data fed from the digital computer 1 and this controlling the control signals 22, 23 and 24 as well as the input signal of the digital-to-analog converter 3.

Referring now to the second embodiment of the electron beam deflection control system shown in Figs. 6(a) and 6(b), there is shown the principal portions of a deflection signal generator circuit for the X-axis or Y-axis. For the sake of convenience, the illustrated circuit will hereinafter be referred to as the circuit for the X-axis. First, an analog switch 16 is switched on.

Then, a difference  $e_\epsilon$  between an output signal 31 from a digital-to-analog converter 3 and an output signal 121 from an integrator 12 are fed to the two inputs of a differential amplifier 9 provided with a voltage limiter. An output  $e_L$  from the differential amplifier 9 is applied via the analog switch 16 to an integration resistor 122 of the integrator 12. It is assumed here that a switch 16' is held in the off position. A current of a value obtained by dividing the output  $e_L$  of the amplifier 9 by the sum of the internal resistance of the switch 16 and the resistance of the integration resistor 122 flows through the integration resistor 122.

Under the action of an operational amplifier 123, it is integrated by an integration capacitor 124 and produces an integrator output signal 121. The input-output characteristic of the differential amplifier 9 is as illustrated in Fig. 6(b). This circuit provides a constant value of  $e_{L0}$  for  $|e_\epsilon| > \Delta e$ . As a result, the integration capacitor 124 integrates a fixed current, so that the output current 121 is constituted by a signal which varies at a fixed rate with respect to time.

Since the output signal 121 always varies so as to bring  $e_\epsilon$  near to zero,  $|e_\epsilon| = \Delta e$  is subsequently established. The differential amplifier 9 performs a linear operation with further lapse of time, so that  $e_L$  decreases and the varying rate of the output signal 121 also decreases. When the output signal 121 has become equal to the absolute value of the output signal 31,  $e_\epsilon = 0$  holds, that is, the current to be integrated becomes zero, so that the output signal 121 settles at this value. Accordingly, by prescribing to below a predetermined error the value  $\Delta e$  at which the limiting characteristic of the differential amplifier 9 begins, the deflection signal has satisfactory linearity.

Although not shown in Fig. 6(a), an appropriate voltage comparator may be used for monitoring the output  $e_L$  of the differential amplifier 9 so as to control the electron beam intensity upon detection of the state  $|e_L| < e_{L0}$ . Thus, in an electron beam exposure system, the excessive exposure of the electron beam to a photo resist film or a

70

75

80

85

90

95

100

105

110

115

120

125

130

fluorescent film as attributed to the lowering of the beam deflecting speed at the end point can be effectively avoided. Subsequently, the switch 16 is turned off. This 5 does not change the output signal 121 because the integration current is zero under the present state. Thereafter, the X-coordinate of the next target point is fed to the digital-to-analog converter to slightly shift a Y-axial deflection signal (refer to  $\Delta Y$  in Fig. 7). After a sufficient period of time which allows the output voltage of the digital-to-analog converter to settle, the switch 16 is turned on, whereby the output 10  $e_o$  of the integrator 12 initiates the deflection at uniform speed. At this time, accordingly, the electron beam is switched on to execute the exposure. By repeating such procedure, smearing exposure as 15 illustrated in Fig. 7 is carried out. Supposing that the exposure of an area A in Fig. 7 has been begun at a point  $P_{10}$  and finished at a point  $P_{1n}$  by the procedure described above the operation of high-speed deflection to a 20 start point  $P_{20}$  for the smearing operation of the next area B will be stated below. When the output signal 121 has settled at the final point  $P_{1n}$  of the area A, the switch 16 is turned off, and the X-coordinate of the 25 point  $P_{20}$  is fed to the digital-to-analog converter, the digital-to-analog converter of the Y-axial deflection circuit being fed with the Y-coordinate at the point  $P_{20}$ . When the switch 16' is subsequently turned on, the 30 output signals 31 and 121 are added through resistors 41 and 42 respectively and the sum is amplified by a coefficient multiplier 40. The current obtained by dividing an output voltage of the coefficient multiplier 40 by 35 the sum between the internal resistance of the switch 16' and the resistance of a resistor 125 is integrated by the integration capacitor 124. Here, a path which extends from the input point of the operational 40 amplifier 123 via the operational amplifier 123, resistor 42, coefficient multiplier 40, switch 16' and resistor 125 back to the above referred to input point constitutes a 45 negative feedback loop. Therefore, the operation after turning the switch 16' "on" is controlled so as to establish  $e_o + e_{DA} = 0$ , where  $e_o$  and  $e_{DA}$  denote the output voltages 50 of the integrator 12 and the converter 3, respectively. The settling takes place under the state in which the above equation is 55 fulfilled. The time constant  $T$  of the circuit at this high-speed deflection operation is given by:

$T \approx 2 c.r/k$

60 on condition that the resistors 41 and 42 have equal values of resistance. In the above formula,  $c$ ,  $r$  and  $k$  represent the capacitance of the integration capacitor,

the sum of the resistance of the resistor 125 and the internal resistance of the switch 16', and the coefficient of the coefficient multiplier 40, respectively. By properly selecting  $r/k$  to a small value, therefore, the output signal 121 can be settled to the target point in a much shorter time than in the foregoing operation of the low-speed mode, it being comparatively easy to shorten the settling time to several tenths of a second. After the start point has been reached in this way, the smearing operation for the area B is executed by the low-speed mode employing the switch 16'. 65

As set forth above, the scanning and drawing in the analog system and the digital system can be easily accomplished by the block arrangements in Fig. 3 and Fig. 6(a). Therefore, by drawing a long pattern with the analog system very quickly and executing the beam movement between lines or between patterns with the digital system very quickly, a high-speed system can be provided. It is also possible to draw a short pattern or a pattern requiring an especially high precision by the use of the digital system. 70

It is also possible that, whilst drawing a pattern along the first axis with the analog system, the second axis is moved to draw oblique lines with the digital system by means of the clock generator and the counter which are contained in the logical circuit 2. Further, it is possible to compensate for a deflection distortion or a sample rotation error. 75

Owing to the system of this invention, there can be realized an electron beam exposure system which skillfully exploits the high drawing speed of the analog system in the case of drawing a long pattern and the high speed and high precision of the digital system in the case of drawing a short pattern and the case of moving a beam between patterns. It should be particularly noted that the above described systems are not limited by the conversion speed of the digital-to-analog converter. Therefore, the good results can be achieved with a converter of low speed, and a system of high cost performance can be provided. 80

WHAT WE CLAIM IS:— 100

1. An electron beam deflection control system including: generation means to selectively generate either a ramp wave signal varying at a comparatively low speed or a stepped wave signal varying at a comparatively high speed; change-over means to control said generation means so as to generate either the ramp wave signal or the stepped wave signal in response to the required deflection length of an electron beam; and, deflection means to deflect the 105

120

125

electron beam with the signal from said generation means. 40

2. An electron beam deflection control system according to Claim 1, wherein said 5 change-over means comprises means to control said generation means so as to generate the ramp wave signal when a relatively long line pattern is to be drawn by the electron beam, and so as to generate the stepped wave signal during either a time 10 when the electron beam is to be moved between patterns or a time when a relatively short line pattern is to be drawn by the electron beam. 15

3. An electron beam deflection control system according to Claim 1 or 2, wherein said generation means comprises digital-to-analog conversion means to generate an analog signal corresponding to coordinate data of a pattern to be drawn, differential 20 amplification means receiving an output of said conversion means as one input thereof, voltage generation means to generate a predetermined voltage and integration means to integrate one of outputs of said 25 differential amplification means and said voltage generation means, selectively applied through said change-over means and to deliver the integrated output as the 30 other input of said differential amplification means, the integrated output being applied to said deflection means, and said change-over means comprises a switch means to selectively apply one of the outputs of said 35 differential amplification means and said voltage generation means of said integration means. 4. An electron beam deflection control system according to Claim 3, further

including a computer which generates the coordinate data for said conversion means. 45

5. An electron beam deflection control system according to Claim 3 or 4, further including detector means to detect that the output of said differential amplification means has become substantially zero, and means to perform blanking of the electron beam with a detection output of said detection means. 50

6. An electron beam deflection control system according to any one of the preceding Claims 3 to 5, further including means to sample or hold the output signal of said conversion means, said sampling or holding means being connected between said conversion means and said differential amplification means. 55

7. An electron beam deflection control system according to Claim 4, wherein said switch means comprises: first switch means to conduct or cut off the output of said amplification means; and second switch means to conduct or cut off a sum between the outputs of said digital-to-analog conversion means and said integration means and to deliver the conducted output to said integration means. 60

8. An electron beam deflection control system constructed and arranged to operate substantially as herein described with reference to and as illustrated in Fig. 3 or Fig. 6(a) of the accompanying drawings. 65

MEWBURN, ELLIS & CO.,

Chartered Patent Agents,

70/72 Chancery Lane,

London WC2.

Agents for the Applicants.

Printed for Her Majesty's Stationery Office, by the Courier Press, Leamington Spa, 1981

Published by The Patent Office, 25 Southampton Buildings, London, WC2A 1AY, from

which copies may be obtained.

FIG. 1 PRIOR ART

FIG. 2 PRIOR ART

FIG. 3

FIG. 4

FIG. 5

FIG. 7

1594476

COMPLETE SPECIFICATION

5 SHEETS

This drawing is a reproduction of

the Original on a reduced scale

Sheet 5

FIG. 6

(a)

(b)