(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6725671号

(P6725671)

(45) 発行日 令和2年7月22日(2020.7.22)

(24) 登録日 令和2年6月29日(2020.6.29)

(51) Int.Cl.

F 1

G06F 12/109 (2016.01)

G06F 12/109

12/109

G06F 12/1009 (2016.01)

G06F 12/1009

12/1009

G06F 12/02 (2006.01)

G06F 12/02

12/02 570A

請求項の数 13 (全 18 頁)

(21) 出願番号 特願2018-538747 (P2018-538747)

(86) (22) 出願日 平成29年1月18日 (2017.1.18)

(65) 公表番号 特表2019-506676 (P2019-506676A)

(43) 公表日 平成31年3月7日 (2019.3.7)

(86) 國際出願番号 PCT/US2017/013934

(87) 國際公開番号 WO2017/132026

(87) 國際公開日 平成29年8月3日 (2017.8.3)

審査請求日 令和2年1月10日 (2020.1.10)

(31) 優先権主張番号 62/286,618

(32) 優先日 平成28年1月25日 (2016.1.25)

(33) 優先権主張国・地域又は機関

米国(US)

(31) 優先権主張番号 15/130,793

(32) 優先日 平成28年4月15日 (2016.4.15)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国 95054 カリフォル

ニア州、サンタクララ、オーガスティ

ン ドライブ 2485

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100111615

弁理士 佐野 良太

(74) 代理人 100162156

弁理士 村雨 圭介

最終頁に続く

(54) 【発明の名称】拡張されたシステム性能のための適応可能な値範囲のプロファイリング

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリ要求のストリーム内のメモリアドレスの連続する範囲のセット及び対応するアクセス頻度を識別するために、処理システムにおいてメモリ要求のストリーム内のメモリアドレスの範囲を適応的にプロファイリングすることであって、前記適応的にプロファイリングすることは、マージ閾値及びスプリット閾値に基づいており、連続する範囲のセットは、メモリアドレスの範囲空間全体に及び、前記マージ閾値は、前記メモリアドレスの連続する範囲のセット内の前記メモリアドレスの範囲毎の最小アクセス頻度を示しており、前記スプリット閾値は、前記メモリアドレスの連続する範囲のセット内の前記メモリアドレスの範囲毎の最大アクセス頻度を示している、ことと、

所定の閾値アクセス頻度を上回る対応するアクセス頻度を有する前記メモリアドレスの範囲のターゲットセットを識別するために、前記メモリアドレスの連続する範囲のセット及び対応するアクセス頻度を周期的にトラバースすることであって、前記メモリアドレスの範囲のターゲットセットは、所定数の範囲以下の範囲の総数を有しており、前記メモリアドレスの範囲のターゲットセットの範囲は、前記メモリアドレスの範囲空間全体の少なくとも一部に及ぶ、ことと、

前記メモリアドレスの範囲のターゲットセット内の前記メモリアドレスの範囲を使用して第1動作を実行することと、を含み、

前記メモリアドレスは仮想メモリアドレスであって、

前記第1動作は、

10

20

前記メモリアドレスの範囲のターゲットセットを、ベースアドレス値及びリミット値に基づいて決定された物理アドレス範囲のセットに仮想 - 物理メモリアドレス変換することと、

物理アドレス範囲のセットを、対応するベースアドレス値及びリミット値のペアとして、ベースリミットレジスタのセットに記憶することであって、前記所定数の範囲は、ベースリミットレジスタのセット内のベースリミットレジスタの総数に対応している、ことと、を含む、

方法。

**【請求項 2】**

前記メモリアドレスの範囲のターゲットセットは、前記メモリアドレスの範囲空間全体より狭い、 10

請求項 1 の方法。

**【請求項 3】**

前記メモリアドレスの範囲のターゲットセットは、前記メモリアドレスの非連続範囲を含む、

請求項 1 又は 2 の方法。

**【請求項 4】**

前記第 1 動作は、

前記メモリアドレスの範囲のターゲットセットの連続する範囲を、メモリの大きなページのアドレス範囲に変換することをさらに含む、 20

請求項 1 又は 2 の方法。

**【請求項 5】**

前記第 1 動作は、

前記メモリアドレスのターゲット範囲に関連するメインメモリの内容を、マルチレベルのメモリシステム内の高帯域メモリに割り当てるこことをさらに含む、

請求項 1 又は 2 の方法。

**【請求項 6】**

前記第 1 動作を実行することは、

複数のリクエスタによるメモリアドレスへの複数のメモリ要求を識別することと、

複数の要求に応じてコヒーレンス動作を実行することと、を含む、 30

請求項 1 の方法。

**【請求項 7】**

前記コヒーレンス動作を実行することは、メモリアドレスに対応するキャッシュラインを無効にすることを含む、

請求項 6 の方法。

**【請求項 8】**

メモリ要求のストリーム内のメモリアドレスの連続する範囲のセット及び対応するアクセス頻度を識別するために、処理システムにおいてメモリ要求のストリーム内のメモリアドレスの範囲を適応的にプロファイリングするように構成された適応範囲プロファイラであって、前記適応的にプロファイリングすることは、マージ閾値及びスプリット閾値に基づいており、連続する範囲のセットは、メモリアドレスの範囲空間全体に及び、前記マージ閾値は、前記メモリアドレスの連続する範囲のセット内の前記メモリアドレスの範囲毎の最小アクセス頻度を示しており、前記スプリット閾値は、前記メモリアドレスの連続する範囲のセット内の前記メモリアドレスの範囲毎の最大アクセス頻度を示している、適応範囲プロファイラと、 40

所定の閾値アクセス頻度を上回る対応するアクセス頻度を有する前記メモリアドレスの範囲のターゲットセットを識別するために、前記メモリアドレスの連続する範囲のセット及び対応するアクセス頻度を周期的にトラバースするように構成された範囲合体及びカリングロジックであって、前記メモリアドレスの範囲のターゲットセットは、所定数の範囲以下の範囲の総数を有しており、前記メモリアドレスの範囲のターゲットセットの範囲は 50

、前記メモリアドレスの範囲空間全体の少なくとも一部に及ぶ、範囲合体及びカリングロジックと、

前記メモリアドレスの範囲のターゲットセット内の前記メモリアドレスの範囲を使用して第1動作を実行するように構成されたロジックと、を備え、

前記ロジックは、

前記メモリアドレスの範囲のターゲットセットを、ベースアドレス値及びリミット値を有する物理アドレスのセットに変換することを含む第1動作を実行するように構成された仮想-物理アドレストランスレータと、

物理アドレスの範囲のセットを記憶するように構成されたベースリミットレジスタのセットであって、前記所定数の範囲は、ベースリミットレジスタのセット内のベースリミットレジスタの総数に対応している、ベースリミットレジスタのセットと、を備える、

装置。

【請求項9】

前記メモリアドレスの範囲のターゲットセットは、前記メモリアドレスの範囲空間全体より狭く、前記メモリアドレスの非連続範囲を含む、

請求項8の装置。

【請求項10】

ベースリミットレジスタのセットのメモリマッピングに対して冗長なメモリマッピングを含むページテーブルを備える、

請求項8の装置。

10

【請求項11】

前記第1動作は、

前記メモリアドレスの範囲のターゲットセットの連続する範囲を、メモリの大きなページのアドレス範囲に変換することをさらに含む、

請求項8、9又は10の装置。

【請求項12】

高帯域メモリを備え、

前記第1動作は、

前記メモリアドレスのターゲット範囲に関連するメインメモリの内容を前記高帯域メモリに割り当てるごとをさらに含む、

30

請求項8、9又は10の装置。

【請求項13】

前記ロジックは、複数のリクエスタによるメモリアドレスへの複数のメモリ要求を識別し、複数の要求に応じてコピーレンス動作を実行するように構成されている、

請求項8、9又は10の装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コンピューティングシステムに関し、特に、値範囲の分類を使用するコンピューティングシステムに関する。

40

【背景技術】

【0002】

従来の値範囲分類システムは、イベントストリーム内の値へのアクセスをカウントし、値範囲に対するアクセスの頻度を動的に判別する。しかしながら、そのようなシステムによって使用される範囲の数は、実際のシステムで実装するのが非常に高価になる可能性のあるかなりの量の高帯域幅の記憶位置を必要とすることがある。したがって、値範囲分類システムを利用するための改良された技術が望まれている。

【発明の概要】

【課題を解決するための手段】

【0003】

50

本発明の少なくとも1つの実施形態では、方法は、メモリ要求のストリーム内のメモリアドレスの連続する範囲のセット及び対応するアクセス頻度を識別するために、処理システムにおいてメモリ要求のストリーム内のメモリアドレスの範囲を適応的にプロファイリングすることを含む。適応的にプロファイリングすることは、マージ閾値及びスプリット閾値に基づいている。連続する範囲のセットは、メモリアドレスの範囲空間全体に及ぶ。マージ閾値は、メモリアドレスの連続する範囲のセット内のメモリアドレスの範囲毎の最小アクセス頻度を示している。スプリット閾値は、メモリアドレスの連続する範囲のセット内のメモリアドレスの範囲毎の最大アクセス頻度を示している。

#### 【0004】

方法は、所定の閾値アクセス頻度を上回る対応するアクセス頻度を有するメモリアドレスの範囲のターゲットセットを識別するために、メモリアドレスの連続する範囲のセット及び対応するアクセス頻度を周期的にトラバースすることを含む。メモリアドレスの範囲のターゲットセットは、所定数の範囲以下の範囲の総数を有する。メモリアドレスのターゲット範囲は、メモリアドレスの範囲空間全体の少なくとも一部に及ぶ。方法は、メモリアドレスの範囲のターゲットセット内のメモリアドレスの範囲を使用して第1動作を実行することを含む。メモリアドレスの範囲のターゲットセットは、メモリアドレスの範囲空間全体より狭くてもよい。メモリアドレスの範囲のターゲットセットは、メモリアドレスの非連続範囲を含んでもよい。メモリアドレスは、仮想メモリアドレスであってもよく、第1動作は、メモリアドレスの範囲のターゲットセットを、ベースアドレス値及びリミット値に基づいて決定された物理アドレス範囲のセットに仮想-物理メモリアドレス変換することを含んでもよい。第1動作は、物理アドレス範囲のセットを、対応するベースアドレス値及びリミット値のペアとして、ベースリミットレジスタのセットに記憶することを更に含んでもよい。所定数の範囲は、ベースリミットレジスタのセット内のベースリミットレジスタの総数に対応してもよい。

#### 【0005】

メモリアドレスは、仮想メモリアドレスであってもよく、第1動作は、メモリアドレスの範囲のターゲットセットの連続する範囲を、メモリの大きなページのアドレス範囲に変換することを含んでもよい。第1動作は、メモリアドレスのターゲット範囲に関連するメインメモリの内容を、マルチレベルのメモリシステム内の高帯域メモリに割り当てるることを含んでもよい。第1動作を実行することは、複数のリクエスタによるメモリアドレスへの複数のメモリ要求を識別することと、複数の要求に応じてコピーレンス動作を実行することと、を含んでもよい。コピーレンス動作を実行することは、メモリアドレスに対応するキャッシュラインを無効にすることを含んでもよい。

#### 【0006】

本発明の少なくとも1つの実施形態では、装置は、メモリ要求のストリーム内のメモリアドレスの連続する範囲のセット及び対応するアクセス頻度を識別するために、処理システムにおいてメモリ要求のストリーム内のメモリアドレスの範囲を適応的にプロファイリングするように構成された適応範囲プロファイラを備える。適応的にプロファイリングすることは、マージ閾値及びスプリット閾値に基づいている。連続する範囲のセットは、メモリアドレスの範囲空間全体に及ぶ。マージ閾値は、メモリアドレスの連続する範囲のセット内のメモリアドレスの範囲毎の最小アクセス頻度を示している。スプリット閾値は、メモリアドレスの連続する範囲のセット内のメモリアドレスの範囲毎の最大アクセス頻度を示している。装置は、所定の閾値アクセス頻度を上回る対応するアクセス頻度を有するメモリアドレスの範囲のターゲットセットを識別するために、メモリアドレスの連続する範囲のセット及び対応するアクセス頻度を周期的にトラバースするように構成された範囲合体及びカリング(culling)ロジックを備える。メモリアドレスの範囲のターゲットセットは、所定数の範囲以下の範囲の総数を有し、メモリアドレスのターゲット範囲は、メモリアドレスの範囲空間全体の少なくとも一部に及ぶ。装置は、メモリアドレスの範囲のターゲットセット内のメモリアドレスの範囲を使用して第1動作を実行するように構成されたロジックを備える。メモリアドレスの範囲のターゲットセットは、メモリアドレスの

10

20

30

40

50

範囲空間全体より狭くてもよく、メモリアドレスの非連続範囲を含んでもよい。

【0007】

ロジックは、範囲のターゲットセットを、ベースアドレス値及びリミット値を有する物理アドレスのセットに変換することを含む第1動作を実行するように構成された仮想・物理アドレストランスレータを備えてもよい。ロジックは、物理アドレスの範囲のセットを記憶するように構成されたベースリミットレジスタのセットを備えてもよい。所定数の範囲は、ベースリミットレジスタのセット内のベースリミットレジスタの総数に対応してもよい。装置は、ベースリミットレジスタのセットのメモリマッピングに対して冗長なメモリマッピングを含むページテーブルを備えてもよい。ロジックは、ターゲットセットの連続する範囲を、メモリの大きなページのアドレス範囲に変換することを含む第1動作を実行するように構成された仮想・物理アドレストランスレータを備えてもよい。装置は、高帯域メモリを備えてもよい。第1動作は、メモリアドレスのターゲット範囲に関連するメインメモリの内容を高帯域メモリに割り当てるることを含んでもよい。ロジックは、複数のリクエスタによるメモリアドレスへの複数のメモリ要求を識別し、複数の要求に応じてコヒーレンス動作を実行するように構成されてもよい。

【0008】

本発明の少なくとも1つの実施形態では、方法は、イベントストリーム内のデータ値の連続する範囲のセット及び対応するアクセス頻度を識別するために、処理システムにおいてイベントストリーム内のデータ値の範囲を適応的にプロファイリングすることを含む。適応的にプロファイリングすることは、マージ閾値及びスプリット閾値に基づいている。連続する範囲のセットは、データ値の範囲空間全体に及ぶ。マージ閾値は、データ値の連続する範囲のセット内のデータ値の範囲毎の最小アクセス頻度を示している。スプリット閾値は、データ値の連続する範囲のセット内のデータ値の範囲毎の最大アクセス頻度を示している。方法は、所定の閾値アクセス頻度を上回る対応するアクセス頻度を有するデータ値の範囲のターゲットセットを識別するために、データ値の連続する範囲のセット及び対応するアクセス頻度を周期的にトラバースすることを含む。データ値の範囲のターゲットセットは、所定数の範囲以下の範囲の総数を有し、データ値のターゲット範囲は、データ値の範囲空間全体の少なくとも一部に及ぶ。方法は、データ値の範囲のターゲットセット内のデータ値の範囲を使用して第1動作を実行することを含む。データ値の範囲のターゲットセットは、データ値の範囲空間全体より狭くてもよく、データ値の範囲のターゲットセットは、データ値の非連続範囲を含んでもよい。イベントストリームは、メモリ要求のストリームであってもよく、データ値は、メモリアドレスであってもよい。イベントストリームは、制御フロー命令のストリームであってもよく、データ値は、ターゲットプログラムアドレスであってもよく、第1動作を実行することは、対応する制御フロー命令のターゲットを予測することを含んでもよい。イベントストリームは、データ計算命令のストリームであってもよく、データ値は、データオペランドであってもよく、第1動作を実行することは、1つ以上のデータオペランドに基づいてデータ計算の出力の値を予測することを含んでもよい。

【0009】

添付図面を参照することによって、本発明をより良く理解することができ、その多くの目的、特徴及び利点が当業者に明らかになるであろう。

【図面の簡単な説明】

【0010】

【図1】本発明の少なくとも1つの実施形態による、例示的な値範囲プロファイラの機能プロック図である。

【図2】例示的な値範囲プロファイリングロジックの機能プロック図である。

【図3】値範囲プロファイラの例示的な状態の状態図である。

【図4】スプリット動作後の値範囲プロファイラの例示的な状態の状態図である。

【図5】マージ操作前の値範囲プロファイラの例示的な状態の状態図である。

【図6】本発明の少なくとも1つの実施形態による、拡張された値範囲プロファイリング

10

20

30

40

50

を使用した例示的なシステムの機能ブロック図である。

【図7】本発明の少なくとも1つの実施形態による、拡張された値範囲プロファイリングを使用したシステムの情報及び制御フローを示す図である。

【図8】例示的な処理システムの機能ブロック図である。

【図9】本発明の少なくとも1つの実施形態による、拡張された値範囲プロファイリングを使用した例示的なシステムの一部の機能ブロック図である。

【図10】仮想アドレスから、ベース及びリミットによって表される物理アドレスへの例示的な範囲変換を示す図である。

【図11】例示的な冗長メモリマッピングシステムの機能ブロック図である。

【発明を実施するための形態】

10

【0011】

異なる画面において同じ符号を使用することは、類似又は同一の項目を示している。

【0012】

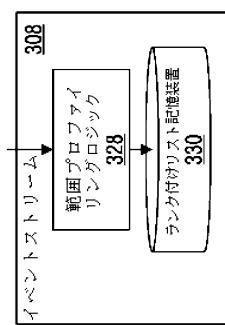

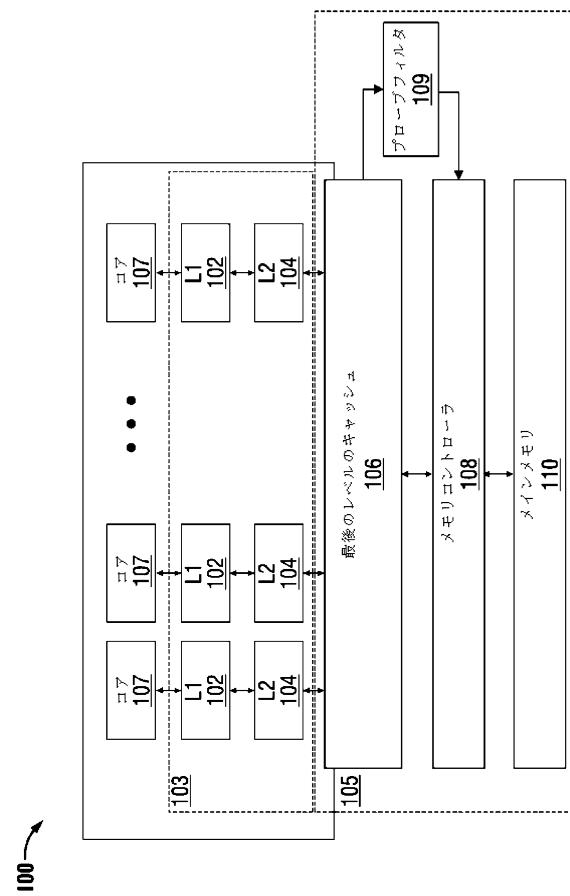

図1を参照すると、例示的な値範囲プロファイラ308は、（例えば、メモリアドレス幅、オペランド幅又はプログラムカウンタ幅に基づいて）可能な値の範囲全体に及ぶ値範囲のランク付けされたリストを生成する範囲プロファイリングロジック328を含む。範囲プロファイリングロジック328は、アクセスの値範囲及び対応する頻度をランク付けリスト記憶装置330に記憶する。少なくとも1つの実施形態では、値範囲プロファイラ308は、イベントストリーム内のこれらの発生の頻度に従って値を範囲に階層的に分類するために、ストリーミングワンパス技術を実装している。値範囲プロファイラ308は、より頻繁にアクセスされた値範囲をより正確なサブ範囲に分類する。値範囲プロファイラ308がより多くのイベントを分析すると、サブ範囲が更なるサブ範囲に分割されてもよいし、まばらにアクセスされた値範囲に起因してより大きな値範囲を形成するために、サブ範囲がマージされてもよい。値範囲プロファイラ308は、イベントストリーム全体から収集された情報を、比較的小さい有限量のメモリにワンパスで記憶する。値範囲プロファイラ308は、ランク付けされたリストを、各値範囲及び関連するカウンタを含むメモリにデータアレイとして記憶された範囲のプロファイルツリーとして生成してもよい。値範囲プロファイラ308は、以下に更に説明するように、値範囲の精度を高アクセス頻度の範囲値及び固定された記憶サイズに適用することによって、従来の適応範囲プロファイリング技術の性能を向上させる拡張を含む。

20

【0013】

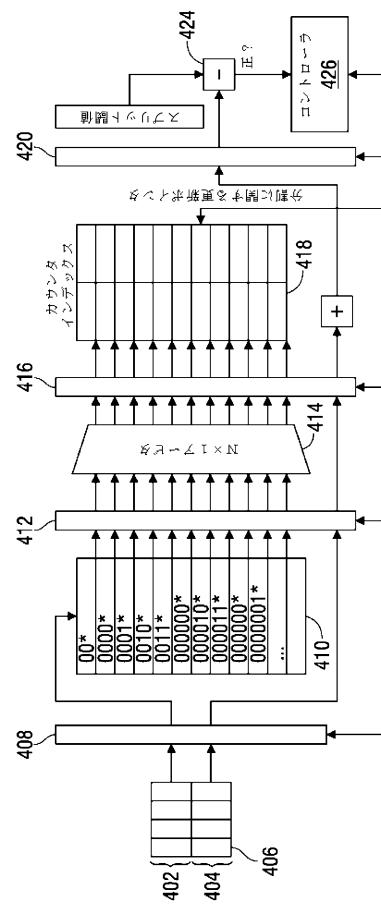

範囲プロファイリングロジック328のパイプライン型の実装についての例示的なアーキテクチャが図2に示されている。バッファ406は、イベント（例えば、メモリ要求、算術命令又はプログラム制御命令）のストリームを受信し、関連する値402が範囲プロファイリングロジック328によって以前に観察されてから観察された頻度404を記憶する。バッファ406は、これらのイベントをパイプラインに入力する。少なくとも1つの実施形態では、バッファ406は、イベントを前処理し、同一の値を有するイベントを組み合わせる。範囲マッチャ（range matcher）410は、特定の受信イベントの値と一致する値範囲を識別する。アービタ414は、値を含む最小範囲を識別し、1つ以上の対応する値範囲についての1つ以上のカウンタをカウンタ418に更新させる。プロファイルデータ構造（例えば、ツリー）の各々の更新は、実際のカウンタのインクリメントを除いて、以前の更新から独立している。

30

【0014】

バッファ406は、それらが処理されるまで、到着イベントを記憶する。コントローラ426は、範囲マージインジケータ（例えば、周期的であるが、指數関数的に減少する頻度）に応じて、潜在的なマージ範囲についてカウンタを検索しながらパイプラインをストールさせる。範囲のスプリット及び範囲のマージは、より多くのイベントを処理する前に満たす必要があるイベント間の依存関係を生成する。しかしながら、範囲のスプリット及び範囲のマージがイベント数よりも大幅に少なく発生し、これにより、発生するストールが比較的少なくなり、ストールが性能にわずかな影響しか与えない。コントローラ426

40

50

は、範囲プロファイリングロジック 328 のパイプラインにおいてストールを引き起こす値範囲をスプリットしてもよいし、マージしてもよく、例えば、コントローラ 426 は、パイプラインレジスタ 408, 412, 416, 420 の更新を抑制する。この時間の間、イベントは、後の処理のためにバッファ 406 に並んでもよい。範囲スプリットの場合、コントローラ 426 は、パイプラインのフラッシュを開始し、範囲プロファイリングロジック 328 を、範囲スプリットが発生する状態の直前の状態にリセットする。

#### 【0015】

コントローラ 426 は、バッファ 406 から処理されるイベント毎に、イベントの対応する値を含む値範囲のセットを検索する。この動作は、三値連想 (ternary content-addressable) メモリセル 410 を使用して実行されてもよい。三値連想メモリセル 410 は、値に一致する全ての値範囲に対して適切なマッチラインを高く設定する。少なくとも 1 つの実施形態では、各セルは、値の範囲に対応する最上位ビットの値を含む。セルに記憶されたビットが少ないほど、対応する値の範囲が大きくなる。同様に、セルに記憶されたビット数が多いほど、対応する値の範囲が小さくなる。コントローラ 426 は、三値連想メモリセル 410 のエントリをプレフィックス長さによってソートすることによって、最長のプレフィックスを有する最小の範囲を決定することができる。値は、同じ範囲幅を有する三値連想メモリセルの 410 の 2 つの異なるエントリと一致することに留意されたい。少なくとも 1 つの実施形態では、三値連想メモリセル 410 は、比較毎に個々のビット又は個々のバイトを観察するために、更にパイプライン化される。

#### 【0016】

範囲プロファイリングロジック 328 がイベントの値を 1 つ以上の値範囲に一致させた後に、範囲プロファイリング論理 328 は、三値連想メモリセル 410 の最後に一致するエントリに対応する、一致する値範囲の最長プレフィックスを識別する。三値連想メモリセル 410 が  $N$  個のマッチラインを順番に記憶し、プレフィックス長によってソートされている場合に、 $N \times 1$  アービタ 414 は、最長の一一致に対して最高の優先度を与え、1つの一致する値範囲のみを進めるのを可能にする。最高の優先度のラインの出力は、対応するカウンタのワードラインをトリガする。範囲プロファイリングロジック 328 の実施形態は、三値連想メモリセル 410 と、 $b$  の分岐因子とを使用するが、範囲プロファイリングロジック 328 は、マルチビットツリーであってもよく、他のネットワークアルゴリズムに基づいて高速な実装を構築するための他の技術を使用してもよいことに留意されたい。

#### 【0017】

範囲プロファイリング論理 328 は、最小の範囲の一一致（すなわち、最も正確な値範囲）を識別した後、カウンタ 418 の適切なカウンタを更新する。少なくとも 1 つの実施形態では、カウンタ 418 は、アレイへのイベントの連続ストリームを取り扱うのに十分な、1つの読み出しポート及び 1 つの書き込みポートを含む。スプリット処理ステージは、コンパレータ 424 を使用して、更新されたカウンタの結果を所定の範囲スプリット閾値と比較する。カウンタが範囲スプリット閾値を上回る場合、コントローラ 426 は、ノードを、複数の子（例えば、分岐因子  $b = 4$  である 4 つの子）を有するように拡張し、ゼロカウントを有するように各々の子のカウンタを初期化する。別個の記憶素子は、範囲スプリット閾値及び範囲マージ閾値を記憶してもよいが、同一の値を有してもよいし、1つの記憶素子のみを使用してもよい。閾値は、イベントの数  $n$  が変化する毎に、1 つ以上の対応する所定の値に基づいて再計算されてもよい。範囲プロファイリングロジック 328 は、イベント数  $n$  及びいくつかの所定の値にのみ依存するので、他の動作と並行して計算を実行してもよい。コントローラ 426 が値範囲をスプリットする場合、範囲プロファイリングロジック 328 は、新たなノードを適切な割合で占めるようにパイプラインをフラッシュしてもよい。

#### 【0018】

少なくとも 1 つの実施形態では、範囲プロファイリングロジック 328 は、値範囲全体に及ぶ範囲ツリー内のルートノードから開始する。関連するシステムがより多くのイベン

10

20

30

40

50

トを流すと、値範囲プロファイリング技術は、特定のツリーノードに関連するカウンタ値を所定のスプリット閾値と比較することによって、ツリーノードを子ノードに分割すべきか否かを判別する。所定のスプリット閾値は、値の最大範囲、ツリーの高さ、処理されるイベントの数、及び／又は、ユーザ定義のエラー閾値に従って選択されてもよい。カウンタ値が所定の範囲スプリット閾値を上回る場合、適応範囲プロファイリング技術は、ツリーノードを子ノードに分割する。適応範囲プロファイリング技術は、所定の分岐因子に基づいて、分割から生じた子ノードの数を判別する。所定の分岐因子が高いほど、得られるプロファイルがより正確になる。しかしながら、子ノードの数が増えると、メモリオーバヘッドが増えるという欠点がある。

## 【0019】

10

範囲プロファイリングロジック328の少なくとも1つの実施形態では、値範囲のスプリットは、三値連想メモリセル410に新たなエントリを生成し、ツリーデータ構造に対してメモリデータアレイを生成することを必要とする。コントローラ426は、新たな子ノードを生成し、対応する識別子を、各々が親の範囲の一部に及ぶ範囲であって、適切に設定された範囲で三値連想メモリセル410に挿入する。コントローラ426は、対応するエントリを、カウンタ及びツリーデータ構造の新たに生成されたノードの他の情報を記憶するメモリに挿入する。分割ノードは、リーフノードであってもよいし、親ノードであってもよい。ノードがリーフノードである場合、分割動作は、親から新たに生成された子へのポインタを設定することを含む。ノードが既に親ノードであるが、その子ノードが親の範囲全体をカバーしていない場合（例えば、内部範囲マージの後）、分割には、既存の子の新たな親を識別し、子のポインタを設定する追加の動作が含まれる。

## 【0020】

20

コントローラ426は、範囲のマージ動作を個別又はバッチで処理することができる。コントローラ426は、バッチ範囲マージを周期的に開始してもよい。範囲マージの各バッチでは、コントローラ426は、範囲のマージャについての候補ノードを識別するために、三値連想メモリセル410をボトムアップでスキャンする。コントローラ426は、メモリ内の対応するデータアレイエントリを削除する。再帰的な動作は、範囲プロファイルデータ構造を取り除いて、圧縮されたプロファイル情報を提供する。必要なメモリサイズは、実験的に決定されてもよいが、いくつかのアプリケーションでは制限されていてもよい。スプリット閾値は、ノードが総イベントの割合よりも多くのイベントをカウントするとすぐに、ノードをサブ範囲に分割するように設定されてもよい。同様に、範囲マージは、正確なプロファイリングを正当化するのに十分なアクセス頻度を有する範囲をマージしない。よって、適応範囲プロファイリング技術は、最小の範囲でのプロファイリングが可能であることを保証する。

## 【0021】

30

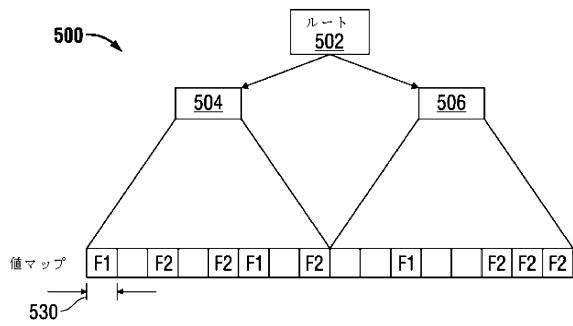

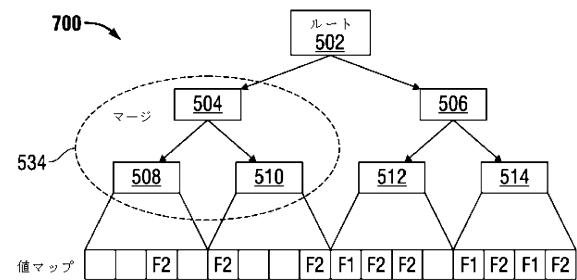

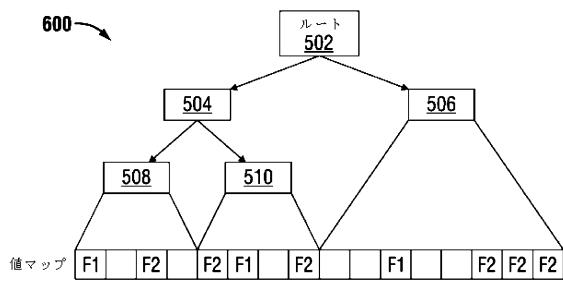

図3、図4及び図5を参照すると、F1で示される値範囲は、少なくともF1のアクセス頻度を有し、高いアクセス頻度範囲を表す。F2で示される値範囲は、最大でF2のアクセス頻度を有し、低いアクセス頻度範囲を表す。図3は、ルートノード502の子ノード504, 506を有する例示的な適応範囲プロファイリングツリーを示している。イベントストリームが観察されると、範囲プロファイリングロジックは、図4に示すように、ノード504の高アクセス頻度範囲を子ノード508, 510に分割する値範囲スプリット動作を実行する。範囲プロファイリングロジックが値範囲を分割する場合、範囲プロファイリングロジックは、プロファイリングツリーの値範囲を分割する。これらの新たな分岐は、これらの高アクセス頻度範囲に対してより正確なカウンタのセットを維持する。

## 【0022】

40

また、値範囲プロファイリング技術は、高アクセス頻度範囲が低アクセス頻度範囲に変化したことに応じて、値範囲プロファイリングツリー内のノード数を制限するためにノードをマージする。値範囲プロファイリング技術は、これらのノードを親ノードにマージし、これにより、これらのあまり重要でない範囲に対する正確なカウンタの必要性を低減する。図5は、対応する値範囲が低アクセス頻度範囲になっているために、子ノード508

50

及び子ノード 510 をノード 504 にマージする例示的なマージ動作 534 を示している。結果として得られるノードカウンタは、子ノード 508, 510 のカウンタ値の合計に等しいカウントを有する。適応範囲プロファイリング技術を使用する例示的なイベントプロファイラは、任意の適切な数のカウンタ（例えば、256 個のカウンタ）を含んでもよい。適応範囲プロファイリングツリーサイズは、ワーカーロードフットプリントサイズ、イベント値パターン及びエラー閾値に関連する。適応範囲プロファイリング技術は、メモリ位置を使用して実装されるカウンタを効果的且つ効率的に使用する。

#### 【 0023 】

上記の値範囲プロファイリング技術によって生成されたランク付けリストは、値空間全体に及び、ターゲットアプリケーションにとって有用でない値の範囲を含むことがあり、ターゲットアプリケーションにおける処理のための値の範囲が多すぎる可能性がある。したがって、拡張された値範囲プロファイリング技術は、ターゲットアプリケーションの値範囲のターゲットセットを生成するために、ランク付けリストのプロファイルされた値範囲を周期的にカリング (cull) 及び合体 (coalesce) する。例えば、値範囲のターゲットセットは、第 1 動作で使用するための所定の閾値よりも大きいアクセス頻度を有する値範囲のみを含んでもよい。ターゲットアプリケーションは、デフォルトの動作を、値範囲のターゲットセットに含まれていない値範囲に適用してもよい。値範囲の別のターゲットセットは、第 2 動作で使用するための所定の閾値よりも小さいアクセス頻度を有する値範囲のみを含んでもよい。この拡張された値範囲プロファイリング技術は、アクセス頻度が高い値範囲又は集中した値範囲を有する値範囲に焦点を当てたものとして、ターゲットアプリケーションにおけるリソースの利用を改善することができる。

#### 【 0024 】

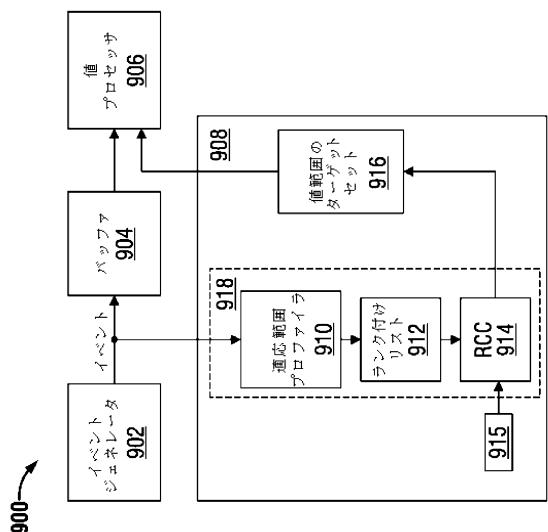

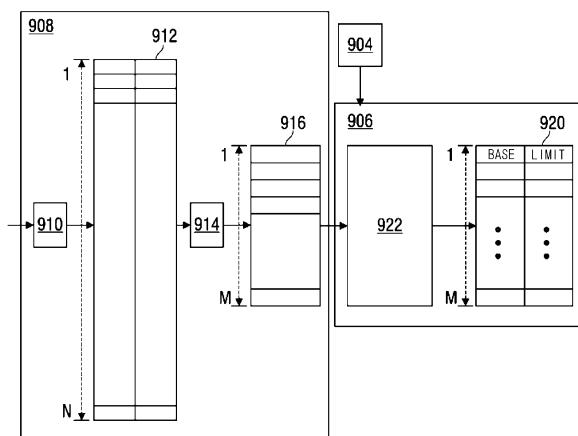

図 6 及び図 7 を参照すると、拡張された値範囲プロファイリング技術 900 の少なくとも 1 つの実施形態では、イベントジェネレータ 902 は、特定のタイプ（例えば、メモリアドレス、データオペランド又はプログラムカウンタ値）の値を含むイベントストリームであって、値プロセッサ 906 による使用のためにパイプラインバッファ 904 に記憶されるイベントストリームを生成する。適応範囲プロファイラ 910 は、イベントストリーム内の値を観測し、値範囲のランク付けリストと、値の値空間全体（例えば、メモリアドレス幅、データオペランド幅又はプログラムカウンタ幅全体に基づく範囲空間）に及ぶ対応するアクセス頻度と、を含むランク付けリスト 912 を生成する。ランク付けリスト 912 は N 個の値範囲を含み、N は所定の整数である。

#### 【 0025 】

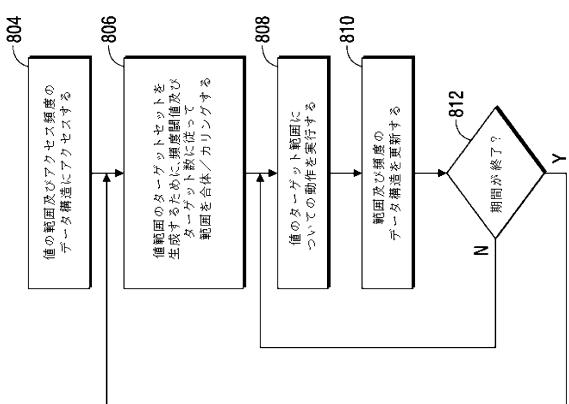

範囲合体及びカリングロジック (RCC) 914 は、レジスタ 915 に記憶された少なくとも 1 つのアクセス頻度閾値、及び、ターゲット範囲のセットのサイズ M に基づいて、値範囲のターゲットセット 916 に含まれる値範囲を周期的に選択する。ここで、M は所定の整数であり、M < N である。範囲合体及びカリングロジック 914 は、ランク付けリスト 912 を処理し、値範囲のターゲットセット 916 を生成する（図 7 のステップ 804）。範囲合体及びカリングロジック 914 は、ランク付けリスト 912 より小さくてもよいが、ランク付けリスト 912 よりも正確な範囲を記憶することができる所定のサイズを有する値範囲のターゲットセット 916 を生成するために、対応するマージ及びスプリット閾値（例えば、レジスタ 915 に記憶されている）に基づいて、値の範囲をマージ及び / 又は除去する（図 7 のステップ 806）。

#### 【 0026 】

値プロセッサ 906 は、例えば、値プロセッサ 906 によって実装されたターゲット動作を実行するために、値範囲のターゲットセット 916 を使用する（図 7 のステップ 808）。一方、適応範囲プロファイラ 910 は、イベントストリームに従って、ランク付けリスト 912 の更新を継続する。所定の期間が終了するまで（図 7 のステップ 812）、値プロセッサ 906 は、値範囲のターゲットセット 916 内の値の範囲を処理し続け（図 7 のステップ 808）、適応範囲プロファイラ 910 は、値範囲のターゲットセット 916 を更新することなく、ランク付けリスト 912 を更新する。所定の期間の終了に応じて

10

20

30

40

50

(図7のステップ812)、範囲合体及びカリングロジック914は、値範囲のターゲットセット916を生成するために(図7のステップ806)、レジスタ915に記憶された所定のアクセス頻度閾値、マージ閾値、スプリット閾値、及び/又は、ターゲット範囲数に基づいて、ランク付けリスト912の更新されたバージョンの値範囲を分割、マージ及び/又は除去することによって、値範囲のターゲットセット916を更新する。所定のスプリット閾値は、ランク付けリスト912の範囲毎の最大アクセス頻度を示している。アドレス範囲のアクセス頻度がスプリット閾値よりも大きい場合、範囲合体及びカリングロジック論理914は、範囲を複数の範囲に分割してもよい。マージ閾値は、ランク付けリスト912の範囲毎の最小アクセス頻度を示している。関連するアドレス範囲のアクセス頻度がマージ閾値よりも小さい場合、範囲合体及びカリングロジック914は、これらの範囲をマージしてもよく、これにより、重要度の低い範囲に対する正確なカウンタの必要性が低減される。範囲合体及びカリングロジック914は、ターゲットアプリケーション内の異なる目的に従って構成されてもよい。例えば、範囲合体及びカリングロジック914は、領域サイズを最大化し、領域の総数を削減し、又は、範囲のサブセット外に存在すると推定される値の数を最小化するために(例えば、冗長マッピングアプリケーションにおいて)、アクセス頻度閾値、マージ閾値、スプリット閾値、及び/又は、ターゲット範囲数の所定の値で構成されてもよい。

#### 【0027】

図6及び図8を参照すると、少なくとも1つの実施形態では、拡張プロファイリング技術のイベントは、処理システム100のマルチレベルキャッシュシステムによってフィルタリングされたメインメモリ110へのメモリ要求である。処理システム100は、複数の処理ノード(例えば、ノード0、ノード1、ノード2及びノード3)と、マルチレベルメモリシステムと、を含む。各ノードは、自身のメモリ又は別のノード内のメモリにアクセスすることができる。プローブフィルタ109又は他のコヒーレンス機構は、複数のキャッシュが、コヒーレンス領域103のメインメモリの同じ位置(例えば、プロセッサ102のコア0、コア1、コア2、コア3のレベル2のキャッシュ)の内容を含む場合に、メモリイメージのコヒーレンシを維持するために、プロセッサ間通信を提供してもよい。図6のイベントジェネレータ902は、図8の最後のレベルのキャッシュ106である。最後のレベルのキャッシュ106は、メモリコントローラ108へのメモリアクセスのストリームを提供する。拡張された値範囲プロファイラ908は、最後のレベルのキャッシュ106とメインメモリ110との間に接続されたメモリコントローラ108に含まれる。

#### 【0028】

例示的な実施形態における図6、図8及び図9を参照すると、バッファ904と、値プロセッサ906と、拡張された値範囲プロファイラ908とが、処理システム100のメモリコントローラ108に含まれている。拡張された値範囲プロファイラ908は、メモリアドレスを値として含むイベントとして、最後のレベルのキャッシュ106からメモリ要求を受信する。値プロセッサ906は、仮想メモリアドレスを物理メモリアドレスにマッピングする回路を含む。

#### 【0029】

仮想メモリのページベースの実装は、メインメモリ110を固定サイズのページに分割する。従来のメモリコントローラは、ページテーブルを使用して、仮想ページを固定サイズの物理ページにマッピングし、連想メモリ又はトランスレーションルックアサイドバッファを使用して、アドレスルックアップを加速することができる。概して、トランスレーションルックアサイドバッファは、メモリ変換を高速化するために使用されるキャッシュである。トランスレーションルックアサイドバッファは、より高速な検索のために、仮想メモリアドレスの直近の変換を物理メモリアドレスに記憶する。トランスレーションルックアサイドバッファは、仮想アドレスに応じて、物理アドレスを生成する。トランスレーションルックアサイドバッファは、マルチレベルの構造を有してもよく、異なるサイズのページ(例えば、標準的な4キロバイト( $2^{12}$ バイト)のページ、大きなページ(例え

10

20

30

40

50

ば、2メガバイト(2<sup>21</sup>バイト)、又は、標準的なページサイズよりも実質的に大きく、「ヒュージページ」若しくは「スーパーページ」とも呼ばれる他のページサイズ))についての変換を記憶してもよい。少なくとも1つの実施形態では、値範囲のターゲットセット916及び値プロセッサ906は、ページベースのメモリシステムのトランスレーションルックアサイドバッファに加えて、またはその代わりに、範囲トランスレーションルックアサイドバッファに使用される。

#### 【0030】

範囲トランスレーションルックアサイドバッファは、複数の範囲の変換を保持するハードウェアキャッシュである。各エントリは、連続する仮想ページの範囲を、連続する物理ページにマッピングする。各範囲は、異なるサイズを有することができる。範囲トランスレーションルックアサイドバッファは、完全に連想的であってもよく、各エントリは、仮想範囲及び範囲アドレス変換を含む。仮想範囲は、仮想アドレス範囲マップのBASE及びLIMITとして記憶されてもよい。変換は、物理メモリ内の範囲の開始からBASEを減算したものを保持するOFFSETを記憶する。しかしながら、範囲トランスレーションルックアサイドバッファの制限された範囲は、メモリアクセスレイテンシに有害なアドレス変換のレイテンシを増加させる場合がある。

#### 【0031】

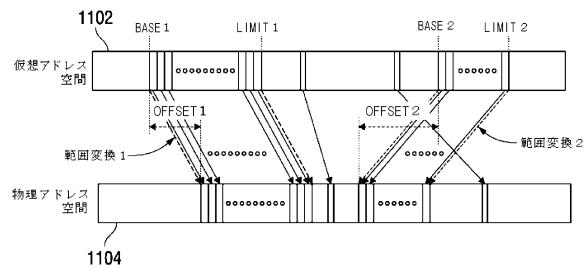

メモリアクセスのレイテンシを減少させる技術は、値範囲のターゲットセット916に記憶された仮想アドレス範囲を、ベースリミットレジスタ920に記憶された物理メモリアドレス範囲に変換するアドレストランスレータ922を含む。例えば、アドレストランスレータ922は、連続する仮想ページのアドレス範囲と、連続する物理ページのアドレス範囲とをマッピングする。範囲変換は、ベースページで調整されてもよく、ベースリミットレジスタ920のBASE及びLIMITフィールドによって識別されてもよい。図11を参照すると、少なくとも1つの実施形態では、アドレストランスレータ922は、仮想アドレス空間1102の仮想範囲アドレスを、物理アドレス空間1104の物理範囲アドレスに変換する。変換は、対応する範囲の仮想ベースアドレスに対してオフセットを追加することと、関連するLIMITフィールドの値によって物理アドレスの範囲を制限することと、を含んでもよい。

#### 【0032】

図9を再度参照すると、例示的なメモリシステムは、所定数の要素を有するベースリミットレジスタ920を含むので、拡張された値範囲プロファイラ908は、範囲の数を、範囲適応プロファイリング技術によって生成された仮想アドレス空間全体に及ぶ仮想メモリアドレス範囲と対応するアクセス頻度とを含むランク付けリスト912のサイズNから、ベースリミットレジスタ920のM個の要素に記憶され得る範囲Mのターゲット数まで減少させる。拡張された値範囲プロファイリング技術は、ベースリミットレジスタ920内の特定の閾値よりも高い頻度でアクセスされるメモリアドレス範囲のみを記憶することによって、ベースリミットレジスタ920のヒット率を含む範囲精度を向上させ、仮想-物理アドレス変換のレイテンシを低減させ、これにより、関連する処理システムの性能を向上させることができる。M>Nであり、ベースリミットレジスタ920は、仮想メモリアドレス空間(例えば、所定の閾値を上回る十分な頻度でアクセスされる仮想アドレス範囲)の一部のみに及ぶことができる非連続仮想アドレス範囲を含んでもよいことに留意されたい。したがって、拡張された値範囲プロファイリング技術を使用して、仮想メモリアドレス空間へのアクセスにおける連続性を示すメモリアドレス変換アプリケーションの性能を向上させ、制限されたサイズの記憶空間内の連続する仮想メモリアドレスを表すために使用される範囲の精度を向上させることができる。

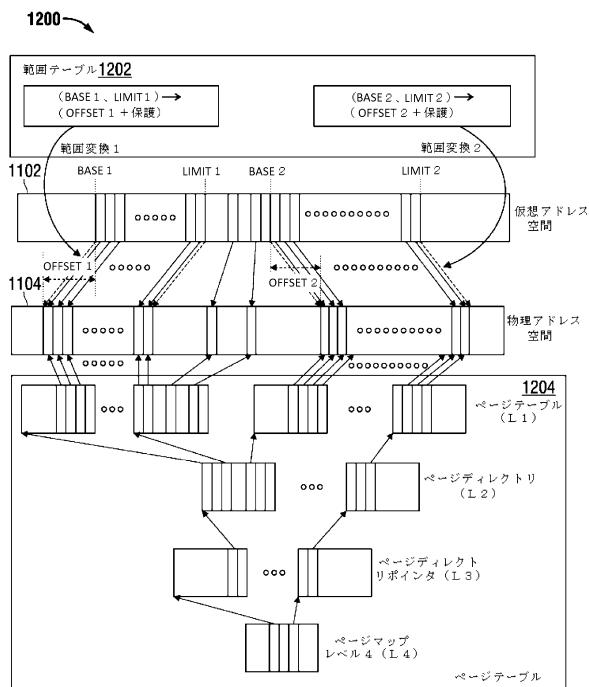

#### 【0033】

拡張された値範囲プロファイリング技術は、上述したように単独で使用されてもよく、冗長メモリマッピングシステムにおいて使用されてもよい。例えば、図9、図10及び図11を参照すると、拡張された値範囲プロファイリング技術は、上述したように、ベースリミットレジスタ920に記憶された範囲と、仮想-物理アドレス変換と、連続する仮想

10

20

30

40

50

アドレスを冗長メモリマッピングシステム1200の連続する物理アドレスにマッピングする冗長ページテーブルと、を使用することによって、冗長メモリマッピング技術の性能を向上させる。

#### 【0034】

冗長メモリマッピングは、固定トランスレーションルックアサイドバッファサイズによって制限されるページングシステムの性能を向上させるために使用される技術である。冗長メモリマッピング技術は、アドレス空間の一部を範囲変換及びページの両方とマッピングする。冗長メモリマッピングは、範囲テーブル及び範囲トランスレーションルックアサイドバッファを、最後のレベルのページトランスレーションルックアサイドバッファと並列に使用する。範囲テーブルに記憶された情報が、ページテーブルに記憶された情報に対して冗長であるため、システムは、必要に応じて（例えば、範囲テーブル内のミスに応じて）ページングを使用してもよいし、ページングに戻ってもよい。冗長メモリマッピングは、物理的及び仮想的に連続し、範囲変換に依存するページの範囲の変換情報を記憶する。範囲変換の各々は、上述したように、任意のサイズの範囲の変換を実行するために、BASE、LIMIT及びOFFSET値を使用して、連続する仮想アドレス範囲を、連続する物理ページにマッピングする。範囲変換は、単に、ベースページで調整され、ページングに冗長であり、仮想アドレス空間全体をマッピングするページテーブルを含む。

10

#### 【0035】

図11は、従来のページテーブルシステム及び範囲変換を使用して冗長にマッピングされた2つの例示的な範囲を示している。冗長メモリマッピングシステム1200は、ページテーブル1204と並列にアクセスされる範囲変換テーブル1202を含む。ページングメモリ管理スキームは、ソフトウェア（例えば、処理システム100の1つ以上のコア上で実行されるオペレーティングシステム又はハイパーバイザ）によって管理され、図8のメインメモリ110で使用されるページと呼ばれる同じサイズブロックで、補助的記憶装置（例えば、ディスク）からデータを記憶及び取り出す。図11を再度参照すると、ページテーブルシステムは、複数のレベルを使用したメモリマッピングのための4レベルのテーブルの階層（例えば、ページテーブル（L1）、ページディレクトリ（L2）、ページディレクトリポインタ（L3）、及び、最上位テーブルであるページマップレベル4（L4））を有する。しかしながら、異なる数のレベルを有する他のページテーブルシステムが使用されてもよい。ページマップレベル4は、仮想アドレス用のページディレクトリポインタを提供する。ページディレクトリポインタテーブル（L3）は、ページディレクトリポインタを使用して、ページディレクトリテーブル（L2）のアドレスを提供する。ページディレクトリテーブル（L2）は、対応するページテーブル（L1）のアドレスを提供する。仮想アドレスの最下位ビットは、ページテーブル内のターゲット物理アドレスを特定するためのページテーブル内のオフセットとして使用される。同じ仮想アドレス空間及び物理アドレス空間に及ぶより少ないレベルのページテーブルが使用されてもよい（例えば、ヒュージページの実装）。範囲テーブル1202は、関連する処理システムの1つ以上のコア上で実行されるソフトウェアによって管理され、仮想アドレスと物理アドレスとの間のマッピングを記憶するページテーブルシステム1204に記憶された情報に対して冗長な情報を記憶する。

20

#### 【0036】

少なくとも1つの実施形態では、値プロセッサ906は、頻繁にアクセスされる物理メモリの範囲に対してアドレス変換を実行し、ベースリミットレジスタの制限されたセットを使用して範囲テーブル1202を実装する仮想-物理アドレストランスレータを含む。上述した拡張された値範囲プロファイリング技術を使用して、頻繁にアクセスされるアドレス範囲の変換を生成することによって、メモリアクセス時間を短縮することができる。利用可能なベースリミットレジスタがメモリシステムのM個のレジスタに制限されるので、メモリアドレス範囲のターゲットセット内のメモリアドレスの範囲の数は、値プロセッサ906のベースリミットレジスタの数以下となるべきである。したがって、最も頻繁にアクセスされる仮想アドレスの範囲は、値プロセッサ906によって、ベースアドレス及

30

40

50

び対応するリミットとしてベースリミットレジスタ920の各々に記憶される物理メモリアドレスに変換される。メモリコントローラ108は、メモリアクセスに応じて、仮想アドレスが、フルアソシエイティブキャッシュメモリである値範囲のターゲットセット916に存在するか否かを判別することができる。メモリコントローラ108は、アドレスが存在する場合に、変換を実行するのではなく、ベースリミットレジスタ920から対応する変換にアクセスし、これにより、アドレス変換に起因するメモリのレイテンシを減少させる。仮想アドレスが値範囲のターゲットセット916の範囲に含まれない場合、値プロセッサ906は、物理メモリアドレスを判別するために、従来のページテーブル又は他の仮想-物理アドレス変換技術を使用する。

## 【0037】

10

図6、図8及び図9を再度参照すると、少なくとも1つの実施形態では、拡張された値範囲プロファイリング技術の他のアプリケーションには、拡張された値範囲プロファイラ908においてメモリアドレス（例えば、物理又は仮想）の範囲を適応的に追跡して、大きなページに転換され得る値範囲のターゲットセット916における連続する変換の広い範囲を識別することが含まれる。値プロセッサ906は、大きな範囲をベースリミットレジスタ920に記憶する。これらの大きなページは、複数のページマッピングが対応するトランスレーションルックアサイドバッファの1つのエントリのみを使用することを可能にし、これにより、トランスレーションルックアサイドバッファの必要サイズを縮小し、より大きな固定サイズのメモリ範囲のマッピングを可能にする。ベースリミットレジスタ920又は他の記憶素子を使用して、連続する変換の広い範囲を識別することができる。拡張された値範囲プロファイリング技術は、メインメモリ110の大きなページを管理する際に使用するために、ランク付けリスト912又は値範囲のターゲットセット916に記憶された情報を、システムソフトウェア（例えば、オペレーティングシステム、ハイパーテイム、カーネル、又は、他の適切なソフトウェア）に提供してもよい。

20

## 【0038】

少なくとも1つの実施形態では、拡張された値範囲プロファイリング技術、拡張された値範囲プロファイラ908及び値プロセッサ906の他のアプリケーションは、マルチレベルのメモリシステム内の高速メモリ（例えば、最後のレベルのキャッシュ）又は低速メモリ（例えば、メインメモリ若しくはディスク）における割り当てのために、メモリアドレス（例えば、物理又は仮想）の範囲を適応的に追跡するメモリコントローラを含む。範囲追跡機構の計数能力は、広範囲のアクセスの識別についての機能と共に、マルチレベルのメモリシステム内で頻繁にアクセスされるページ範囲をメインメモリから高速メモリ（例えば、高帯域メモリ又はNレベルのメモリシステム等）に割り当てるためのシステムについての十分な情報を提供する。例示的な高帯域メモリは、メモリチップのスタックと、インタポーラを使用してメモリチップをプロセッサに密接に接続する、関連する超高速メモリインタフェースと、を含む。結果として得られるシステムでは、高帯域メモリ性能がオンチップの内蔵RAMの性能とわずかに異なるが、利用可能なシステムストレージの量が拡大する。

30

## 【0039】

処理システム100の少なくとも1つの実施形態では、最後のレベルのキャッシュ106、メモリコントローラ108、又は、他のコヒーレンス回路は、最後のレベルのキャッシュ106に移動されたデータ若しくは最後のレベルのキャッシュ106から移動されたデータがコヒーレンシルールに違反していないことを保証するコヒーレンスシステムを含む。例えば、プローブフィルタ109は、コヒーレンシルール（例えば、コアに対するプローブと、コアに返されるヒットデータとの間、又は、最後のレベルのキャッシュに対するプローブと、最後のレベルのキャッシュに割り当てられるコアからのビクティムデータとの間の競合条件に違反しないこと等）を適用する。プローブフィルタ109は、プローブをコアに送る前に、最後のレベルのキャッシュデータの移動に対するプローブの衝突検出を実行する。したがって、プローブフィルタ109は、コヒーレンス動作を迅速に行うために、メモリアドレスの範囲（例えば、物理メモリアドレス範囲又は仮想メモリアドレ

40

50

ス範囲)を適応的に追跡する、拡張された値範囲プロファイラ908を含んでもよい。占有されているメモリ領域をカバーするアドレス範囲は、メモリコヒーレンス動作が必要であるか否かを決定するために、スヌーピング機構で利用される値範囲のターゲットセット916に記憶されてもよい。フルアソシエイティブメモリとすることができる値範囲のターゲットセット916におけるヒットは、複数の異なるリクエスタによって同じメモリアアドレス範囲に複数のメモリ要求があることを示すことができる。したがって、値プロセッサ906は、コヒーレンス動作を実行するための制御論理を含んでもよい。コヒーレンス回路は、プローブフィルタとして説明されているが、コヒーレンス機構を含む処理システムの他の実施形態では、他のコヒーレンスシステムにおける拡張された値範囲プロファイラ908及び値プロセッサ906を含んでもよい。

10

#### 【0040】

図6を再度参照すると、拡張されたプロファイリング技術の少なくとも1つの実施形態では、イベントジェネレータ902は命令デコーダであり、値プロセッサ906はパイプライン型処理コアのプログラムカウンタアドレスジェネレータである。イベントは、パイプライン型処理コアによって処理される制御フロー命令を含む。例えば、プログラムカウンタアドレスジェネレータは、推測的若しくは非推測的命令実行、条件的若しくは非条件的分岐若しくはジャンプ命令実行、又は、他の命令実行のためのターゲット命令アドレスを生成する。値は、コアによって処理されるメモリからフェッチされる次の命令のアドレスである。拡張された値範囲プロファイリング技術は、高頻度アクセスを有するターゲットアドレスの範囲を識別し、実行ユニット(命令フェッチユニット)は、プロセッサの動作を高速化するために、値範囲のターゲットセット916に記憶された高頻度アクセス(例えば、所定数よりも多い)を有するターゲットアドレスの範囲についてベース分岐予測及び推測的命令決定を行ってもよい。

20

#### 【0041】

少なくとも1つの実施形態では、イベントジェネレータ902は、パイプライン型プロセッサコアの命令デコーダであり、値プロセッサ906は、算術論理ユニット、浮動小数点演算ユニット、又は、パイプライン型プロセッサコアの他の適切な実行ユニットである。イベントは、実行ユニットによって処理される算術又は論理命令であり、値は、コアの実行ユニットによって処理される対応するデータオペランドである。拡張された値範囲プロファイリング技術は、高頻度アクセスを有するデータオペランドの範囲を識別し、実行ユニットは、高頻度アクセスを有するデータオペランドの範囲に基づいて結果を予測し、これにより、関連する実行ユニットの計算時間を短縮し、関連する処理システムの性能を向上させる。拡張された値範囲プロファイリング技術は、実行速度の増加及び/又は消費電力の低減のトレードオフとして精度の低下が許容されるアプリケーションにおいて、推測的実行及び/又は低電力動作を可能にするために使用してもよい。

30

#### 【0042】

本明細書で説明される構造は、プロセッサ上で実行されるソフトウェア(ファームウェアを含む)を使用して、又は、ソフトウェア及びハードウェアの組み合わせによって実装されてもよい。本明細書で説明するように、ソフトウェアは、少なくとも1つの有形のコンピュータ可読媒体で符号化されてもよい。本明細書で言及される有形のコンピュータ可読媒体は、少なくともディスク、テープ、又は、他の非一時的な磁気、光学若しくは電気記憶媒体を含む。

40

#### 【0043】

本発明の実施形態を説明するにあたり、回路及び物理構造が全体として想定されているが、現代の半導体設計及び製造において、物理構造及び回路は、後続の設計、シミュレーション、テスト又は製造段階で使用するのに適したコンピュータ可読記述形式で具体化されてもよい。例示的な構成において個別の構成要素として提示される構造及び機能は、組み合わされた構造又は構成要素として実装されてもよい。本発明の様々な実施形態は、全てが本明細書で説明され、添付の特許請求の範囲において定義されているように、回路、回路のシステム、関連する方法、並びに、かかる回路、システム及び方法を符号化したも

50

のを有する有形のコンピュータ可読媒体（例えば、VHASICハードウェア記述言語（VHDL）、Verilog、GDSIIデータ、EDIF（Electronic Design Interchange Format）及び／又はGerberファイル）を含むことが意図されている。また、コンピュータ可読媒体は、本発明を実施するために使用することができる命令と共にデータを記憶することができる。命令／データは、ハードウェア、ソフトウェア、ファームウェア又はこれらの組み合わせに関連してもよい。

【 0 0 4 4 】

本明細書に記載された発明の説明は例示であって、以下の特許請求の範囲において示された発明の範囲を限定することを意図していない。例えば、本発明は、特定のプロセッサ及びメモリアーキテクチャを使用する実施形態で説明されたが、当業者であれば、異なるキャッシュスキーム及びコーヒーレンスプロトコルを使用して、他のプロセッサ及びメモリシステムアーキテクチャと共に本明細書の教示を利用することができるることを認識するであろう。以下の特許請求の範囲において示される発明の範囲から逸脱することなく、本明細書で開示される実施形態の変形及び修正が、本明細書で示される説明に基づいて行われてもよい。

10

【 四 1 】

【 図 2 】

【図3】

【図5】

【図4】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

---

フロントページの続き

早期審査対象出願

(72)発明者 マウリシオ ブレーターニツツ

アメリカ合衆国 78735 テキサス州、オースティン、サウスウェスト パークウェイ 71

71、エイ・エム・ディー・ユー・エス オースティン

審査官 萩島 豪

(56)参考文献 特表2015-534200 (JP, A)

国際公開第2012/095901 (WO, A1)

特開2010-157218 (JP, A)

米国特許出願公開第2015/0169227 (US, A1)

米国特許出願公開第2010/0169602 (US, A1)

米国特許出願公開第2013/0185475 (US, A1)

特開2007-249971 (JP, A)

特開2015-084260 (JP, A)

特開2000-276397 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00 - 12/128

G06F 13/16 - 13/18