(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4939847号

(P4939847)

(45) 発行日 平成24年5月30日(2012.5.30)

(24) 登録日 平成24年3月2日(2012.3.2)

(51) Int.Cl.

F 1

|             |              |                  |      |       |         |

|-------------|--------------|------------------|------|-------|---------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/36  |         |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20  | 6 7 O D |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G09G | 3/20  | 6 1 2 L |

|             |              |                  | G09G | 3/20  | 6 2 3 G |

|             |              |                  | GO2F | 1/133 | 5 0 5   |

請求項の数 7 (全 12 頁)

(21) 出願番号

特願2006-162971 (P2006-162971)

(22) 出願日

平成18年6月13日 (2006.6.13)

(65) 公開番号

特開2007-114732 (P2007-114732A)

(43) 公開日

平成19年5月10日 (2007.5.10)

審査請求日

平成21年6月3日 (2009.6.3)

(31) 優先権主張番号

10-2005-0098210

(32) 優先日

平成17年10月18日 (2005.10.18)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者

390019839

三星電子株式会社

Samsung Electronics

C o . , L t d .大韓民国京畿道水原市靈通区梅灘洞 416

416, Maetan-dong, Yeo-

ngtong-gu, Suwon-si,

Gyeonggi-do, Republic

of Korea

(74) 代理人

110000408

特許業務法人高橋・林アンドパートナーズ

(72) 発明者

朴 宇一

大韓民国京畿道城南市盆唐区亭子洞 ハン

ソルマウル住公5団地アパートメント51

2-504

最終頁に続く

(54) 【発明の名称】平板ディスプレイ装置及びその動作方法

## (57) 【特許請求の範囲】

## 【請求項 1】

データライン、ゲートライン、並びに前記データライン及び前記ゲートラインに接続されたピクセルを含むディスプレイパネルと、

画像データ信号と前記画像データ信号が前記データラインに供給される時点を示す第1ラインラッチ信号を含む制御信号とを出力するタイミングコントローラと、

前記タイミングコントローラからの第一群の前記制御信号及び前記画像データ信号に応答して前記データラインを駆動するデータドライバと、

前記タイミングコントローラからの第二群の前記制御信号に応答して前記ゲートラインを駆動するゲートドライバと、

パワーオン時、所定時間の間前記データラインが駆動されないように前記データドライバを制御する制御回路と、を備え、

前記制御回路は、

外部から供給される外部電源電圧を遅延させ、遅延された外部電源電圧を出力する遅延回路と、

前記外部電源電圧及び前記遅延された外部電源電圧を受信してパルス信号を発生させるパルス発生器と、

前記パルス発生器からの前記パルス信号及び前記タイミングコントローラからの前記第1ラインラッチ信号を受信して、前記画像データ信号を前記データドライバにラッチさせて

ラッチされた画像データ信号が前記データラインに供給される時点を示す第2ラインラッ

10

20

チ信号を生成して前記データドライバに出力するロジック回路と、を含むことを特徴とするディスプレイ装置。

【請求項 2】

前記制御回路は、

前記パワーオン後、前記遅延回路によって遅延させた前記外部電源電圧の遅延時間に応する前記所定時間の間、ハイレベルの前記第2ラインラッチ信号を出力することを特徴とする請求項1に記載のディスプレイ装置。

【請求項 3】

前記制御回路は、

前記パワーオンの開始後で前記所定時間の経過後、前記タイミングコントローラから出力される前記第1ラインラッチ信号と同一の前記第2ラインラッチ信号を出力することを特徴とする請求項2に記載のディスプレイ装置。

10

【請求項 4】

前記ロジック回路はロジックOR演算回路であることを特徴とする請求項1乃至3のいずれか一項に記載のディスプレイ装置。

【請求項 5】

前記制御回路は、

外部から供給された電源電圧と一端が接続された第1抵抗と、

前記第1抵抗の他端と接地電圧との間に接続された容量と、

前記電源電圧と一端が接続された第2抵抗と、

20

前記第2抵抗の他端と前記接地電圧との間に接続された電流通路及び前記第1抵抗の前記他端と接続されたゲートを有するトランジスタと、

前記第2抵抗の前記他端と接続された入力端及び出力端を有する第1ダイオードと、

前記タイミングコントローラからの前記第1ラインラッチ信号と接続された入力端及び出力端を有する第2ダイオードとを含み、

前記第1及び第2ダイオードそれぞれの前記出力端は共通に接続され、前記第1及び第2ダイオードそれぞれの前記出力端は前記第2ラインラッチ信号を出力することを特徴とする請求項4に記載のディスプレイ装置。

【請求項 6】

前記データドライバは、

30

水平開始信号に同期してクロック信号をシフトするシフトレジスタと、

前記シフトレジスタから出力されるクロック信号に応答して前記タイミングコントローラからの前記画像データ信号を蓄積するデータレジスタと、

前記制御回路からの前記第2ラインラッチ信号に応答して前記データレジスタに蓄積された前記画像データ信号をラッチするラッチと、

前記ラッチから出力される前記画像データ信号をアナログ画像信号に変換するデジタル-アナログコンバータと、

前記第2ラインラッチ信号に応答して前記デジタル-アナログコンバータからの前記アナログ画像信号を前記データラインに出力する出力バッファとを含むことを特徴とする請求項1乃至5のいずれか一項に記載のディスプレイ装置。

40

【請求項 7】

データライン、ゲートライン、並びに前記データライン及び前記ゲートラインに接続されたピクセルを含むディスプレイパネルと、

画像データ信号と前記画像データ信号が前記データラインに供給される時点を示す第1ラインラッチ信号を含む制御信号とを出力するタイミングコントローラと、

前記タイミングコントローラからの第一群の前記制御信号及び前記画像データ信号に応答して前記データラインを駆動するデータドライバと、

前記タイミングコントローラからの第二群の前記制御信号に応答して前記ゲートラインを駆動するゲートドライバと、

パワーオン時、所定時間の間前記データラインが駆動されないように前記データドライバ

50

を制御する制御回路と、を備え、

前記制御回路は、

外部から供給される外部電源電圧を遅延させ、遅延された外部電源電圧を出力する遅延回路と、

前記外部電源電圧及び前記遅延された外部電源電圧を受信してパルス信号を発生させるパルス発生器と、

前記パルス発生器からの前記パルス信号及び前記タイミングコントローラからの前記第1ラインラッチ信号を受信して、前記画像データ信号を前記データドライバにラッチさせてラッチされた画像データ信号が前記データラインに供給される時点を示す第2ラインラッチ信号を生成して前記データドライバに出力するロジック回路と、を含むディスプレイ装置の動作方法において

パワーオンする段階と、

前記所定時間の間前記データドライバをリセットする段階とを含むことを特徴とするディスプレイ装置の動作方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は平板ディスプレイ装置に関する。

**【背景技術】**

**【0002】**

ユーザインターフェースの一つとして電子デバイスに表示装置を搭載することは必須になっており、軽量薄型であり低消費電力である平板ディスプレイ装置が表示装置として多用されている。平板ディスプレイ装置は、画像表示パネルの種類に応じてOLED(Organic Light Emitting Diode)、LCD(Liquid Crystal Display)、FED(Field Emission Display)、VFD(Vacuum Fluorescent Display)、PDP(Plasma Display Panel)などがある。特に近年では、スペース及び電力の節約をはかるため、小型軽量化のための携帯型電子デバイス以外にもコンピュータディスプレイやテレビディスプレイとして平板ディスプレイ装置が利用されている。

**【0003】**

液晶ディスプレイ装置(LCD)のディスプレイパネルは行列形態に配列されており、スイッチング素子である薄膜トランジスタを含む複数のピクセルアレイを含む。各ピクセルは薄膜トランジスタを通じて画像信号に該当するデータ電圧を選択的に受け入れる。液晶ディスプレイ装置はまたゲートラインにゲートオン電圧を印加するゲートドライバとデータラインに画像信号を印加するデータドライバと、これらを制御する信号制御回路とを含む。

**【0004】**

ゲートラインはスイッチング素子である薄膜トランジスタをターンオンさせるためのゲートオン電圧またはスイッチング素子をターンオフさせるためのゲートオフ電圧で駆動される。例えば、パワーオン時、液晶ディスプレイ装置内のDC/DCコンバータは-13Vのゲートオフ電圧を出し、パワーオン時点からゲートオフ電圧が-13Vに安定するまでは所定の時間がかかる。ゲートオフ電圧が-13V迄十分に低くなる前に約-6Vまで液晶パネル内のピクセルを構成する薄膜トランジスタは弱くターンオンされた状態を維持するようになる。この時、データラインの電位が任意のレベル値であれば、データラインの信号レベルに対応する望まない画像が液晶パネルに表示されてしまう。このような不良画像は信号制御回路から有効なピクセルデータ信号が出力される(例えば60ms以後)まで持続して液晶パネルに表示される。

**【0005】**

特に、パワーオン時、データ駆動回路を構成する複数の集積回路のうち特定集積回路と接続されたデータラインが任意の同一のレベルデータ信号で駆動されれば、液晶パネルに表

10

20

30

40

50

示された不良画像はさらに著しくなる。

【0006】

したがって、パワーオン時点からゲートオフ信号が十分に安定するまでかかる時間の間データラインの電位が任意のレベル値とならないようにする技術が要求されている。

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明の目的は、パワーオン時、不良画像の表示を防止することができる平面ディスプレイ装置及びその動作方法を提供することにある。

【課題を解決するための手段】

10

【0008】

上述のような目的を解決するために、本発明の特徴によれば、ディスプレイ装置は、画像データ信号を出力するタイミングコントローラと、制御信号及び前記画像データ信号に応答してデータラインを駆動するデータドライバと、前記制御信号を発生する制御回路とを含み、前記制御信号は前記ディスプレイ装置の電源状態を示す。また前記データドライバは、前記ディスプレイ装置のパワーオン状態の開始を示す前記制御信号の次に所定時間の間、前記データラインがリセット状態を維持するように駆動される。

【0009】

この実施形態において、前記タイミングコントローラは、前記データドライバによって前記データラインが駆動される時点を示すラインラッチ信号をさらに出力する。

20

【0010】

この実施形態において、前記制御回路に外部から提供された電源電圧及び前記ラインラッチ信号が入力され、前記所定時間が経過した後、前記制御信号は前記ラインラッチ信号と同一である。

【0011】

この実施形態において、前記制御回路は、外部電源電圧を遅延させる遅延回路と、前記外部電源電圧及び前記遅延回路によって遅延された外部電源電圧が入力されてパルス信号を発生するパルス発生器と、前記ラインラッチ信号及び前記パルス信号の和である前記制御信号を出力するロジック回路とをさらに含む。

【0012】

30

この実施形態において、ディスプレイ装置は、ゲートラインを駆動するゲートドライバをさらに含み、前記制御回路は、前記パワーオン時、前記ゲートドライバが前記ゲートラインをターンオフするのに十分なゲートオフ電圧で駆動するまで前記データラインがリセット状態を維持するように前記制御信号を発生する。

【0013】

本発明の他の特徴に係るディスプレイ装置は、第1ラインラッチ信号及び画像データ信号を出力するタイミングコントローラと、第2ラインラッチ信号及び前記画像データ信号に応答してデータラインを駆動するデータドライバと、外部電源電圧及び前記第1ラインラッチ信号が入力され、パワーオン時、所定時間の間前記データラインがリセット状態を維持するように前記第2ラインラッチ信号を発生する制御回路とを含む。

40

【0014】

この実施形態において、前記制御回路は、外部電源電圧を遅延させる遅延回路と、前記外部電源電圧及び前記遅延回路によって遅延された外部電源電圧が入力されてパルス信号を発生するパルス発生器と、前記第1ラインラッチ信号及び前記パルス信号の和である前記第2ラインラッチ信号を出力するロジック回路とをさらに含む。

【0015】

この実施形態において、前記データドライバは、前記第2ラインラッチ信号に応答して前記タイミングコントローラからの前記画像データ信号をラッチするラッチ回路と、前記ラッチ回路から前記画像データ信号が入力され、前記第2ラインラッチ信号に応答して前記データラインを駆動する出力駆動回路とを含む。

50

## 【0016】

この実施形態において、前記制御回路は、パワーオン時、前記所定時間の間前記ラッチ回路の出力がリセットされるように前記第2ラインラッチ信号を出力する。

## 【0017】

本発明の他の特徴に係るディスプレイ装置は、データライン、ゲートライン、並びに前記データライン及び前記ゲートラインに接続されたピクセルを含むディスプレイパネルと、制御信号と画像データ信号とを出力するタイミングコントローラと、前記タイミングコントローラからの一群の制御信号及び前記画像データ信号に応答して前記データラインを駆動するデータドライバと、前記タイミングコントローラからの他群の制御信号に応答して前記ゲートラインを駆動するゲートドライバと、パワーオン時、所定時間の間前記データラインが駆動されないように前記データドライバを制御する制御回路とを含む。 10

## 【0018】

この実施形態において、前記タイミングコントローラから出力される前記制御信号は、前記画像データ信号が前記データラインに供給される時点を示す第1ラインラッチ信号を含む。

## 【0019】

この実施形態において、前記制御回路は、前記データドライバを制御するための第2ラインラッチ信号を出力する。

## 【0020】

この実施形態において、前記制御回路は、前記パワーオン後、前記所定時間の間所定レベルの第2ラインラッチ信号を出力する。 20

## 【0021】

この実施形態において、前記制御回路は、前記パワーオン後、前記所定時間が経過すれば、前記タイミングコントローラからの第1ラインラッチ信号を前記第2ラインラッチ信号として出力する。

## 【0022】

この実施形態において、前記制御回路は、外部から供給された電源電圧を遅延させて出力する遅延回路と、前記遅延回路によって遅延された電源電圧を反転させるパルス発生器と、前記パルス発生器の出力及び前記タイミングコントローラからの前記第1ラインラッチ信号が入力されて前記第2ラインラッチ信号とを出力する。 30

## 【0023】

この実施形態において、前記制御回路は、外部から供給された電源電圧と一端が接続された第1抵抗と、前記第1抵抗の他端と接地電圧との間に接続された容量と、前記電源電圧と一端が接続された第2抵抗と、前記第2抵抗の他端と前記接地電圧との間に接続された電流通路及び前記第1抵抗の前記他端と接続されたゲートを有するトランジスタと、前記第2抵抗の前記他端と接続された入力端及び出力端を有する第1ダイオードと、前記タイミングコントローラからの前記第1ラインラッチ信号と接続された入力端及び出力端を有する第2ダイオードとを含み、前記第1及び第2ダイオードそれぞれの前記出力端は共通に接続され、前記第1及び第2ダイオードそれぞれの前記出力端は前記第2ラインラッチ信号を出力する。 40

## 【0024】

この実施形態において、前記データドライバは、水平開始信号に同期してクロック信号をシフトするシフトレジスタと、前記シフトレジスタから出力されるクロック信号に応答して前記タイミングコントローラからの前記画像データ信号を蓄積するデータレジスタと、前記制御回路からの前記第2ラインラッチ信号に応答して前記データレジスタに蓄積された前記画像データ信号をラッチするラッチと、前記ラッチから出力される前記画像データ信号をアナログ画像信号に変換するデジタル-アナログコンバータと、前記第1ラインラッチ信号に応答して前記デジタル-アナログコンバータからの前記アナログ画像信号を前記データラインに出力する出力バッファとを含む。

## 【0025】

本発明の他の特徴に係る画像データ信号に応答してデータラインを駆動するデータドライバを含むディスプレイ装置の動作方法は、パワーオンする段階と、所定時間の間前記データラインをリセットする段階とを含む。

**【0026】**

この実施形態において、前記所定時間は前記ゲートラインがゲートラインと接続された一つ以上のトランジスタをターンオフするのに十分なゲートオフ電圧に駆動するのに必要な時間である。

**【0027】**

本発明の他の特徴に係る画像データ信号に応答してデータラインを駆動するデータドライバを含むディスプレイ装置の動作方法は、電源電圧を供給する段階と、前記電源電圧を遅延させる段階と、前記電源電圧と前記遅延された電源電圧に応答してパルス信号を生成する段階と、前記データラインをリセットするために前記パルス信号を前記データドライバに供給する段階とを含む。10

**【0028】**

この実施形態において、前記パルス信号はラインラッチ信号である。

**【発明の効果】**

**【0029】**

本発明によれば、パワーオン時、データ駆動電圧が入力される前にデータ駆動回路内のラッチ回路を制御するラインラッチ信号をハイレベルに設定することで、データ駆動電圧が入力された後、ラッチ回路からどんな信号も出力されない。したがって、ゲートオフ信号が十分に低くなるまでデータラインが駆動されないため、パワーオン時、望まない不良画像が表示されることを防止することができる。20

**【発明を実施するための最良の形態】**

**【0030】**

次に、本発明に係る液晶ディスプレイ装置及びその動作方法を実施するための最良の形態の具体例を図面を参照しながら説明する。

**【0031】**

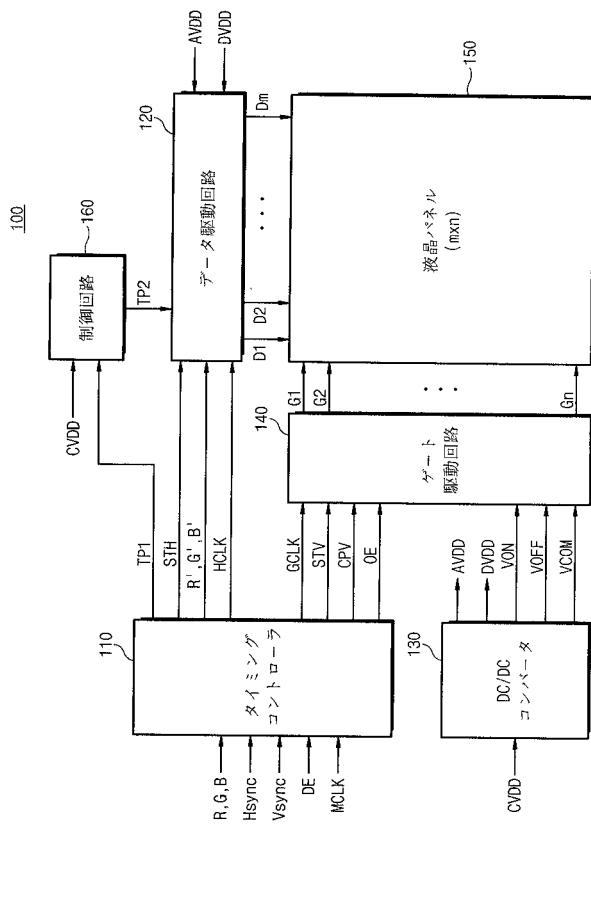

図1は平板（フラットパネル）ディスプレイ装置である液晶ディスプレイ装置の構成を示すブロック図である。

**【0032】**

図1を参照すれば、液晶ディスプレイ装置は、タイミングコントローラ110、データ駆動回路120、DC/DCコンバータ130、ゲート駆動回路140、液晶パネル150、及び制御回路160を含む。30

**【0033】**

液晶パネル150は、複数のゲートラインG<sub>1</sub>～G<sub>n</sub>と、ゲートラインに交差する複数のデータラインD<sub>1</sub>～D<sub>m</sub>と、ゲートライン及びデータラインの交差点に形成されたピクセルとを含み、ピクセルはマトリクス構造に配置されている。各ピクセルは、ゲートライン及びデータラインにゲート電極及びソース電極がそれぞれ接続される薄膜トランジスタ（図示しない）と、薄膜トランジスタのドレイン電極に接続される液晶（図示しない）と、蓄積容量（ストレージキャパシタ）（図示しない）とを含む。このようなピクセル構造では、ゲート駆動回路140によってゲートラインが順に選択され、選択されたゲートラインにゲートオン電圧V<sub>ON</sub>がパルス形態で印加されれば、ゲートラインに接続されたピクセルの薄膜トランジスタがターンオンされ、次に、データ駆動回路120によって各データラインにピクセル情報を含む電圧が印加される。この電圧は、該当するピクセルの薄膜トランジスタを経て液晶容量と蓄積容量とに印加され、液晶及び蓄積容量が駆動されることによって所定の表示動作が行われる。40

**【0034】**

タイミングコントローラ110に外部のグラフィックソースから垂直同期信号V<sub>sync</sub>、水平同期信号H<sub>sync</sub>、データイネーブル信号DE、クロック信号MCLK及びピクセルデータR、G、Bが入力される。タイミングコントローラ110は、液晶パネル1550

0の仕様に適するようにデータフォーマットを変換したピクセルデータ信号R'、G'、B'、水平同期開始信号(S T H ; s t a r t h o r i z o n t a l)及びクロック信号H C L Kをデータ駆動回路120に出力して、第1ラインラッチ信号T P 1を制御回路160に出力する。

#### 【0035】

また、タイミングコントローラ110は水平同期信号H s y n c、垂直同期信号V s y n c及びデータイネーブル信号D Eに応答して垂直同期開始信号(S T V ; s t a r t v e r t i c a l)、ゲートクロック信号C P V、及び出力イネーブル信号(O E ' o u T P u t e n a b l e)などの制御信号をゲート駆動回路140に出力する。

#### 【0036】

データ駆動回路120は、タイミングコントローラ110から供給されるピクセルデータ信号R'、G'、B'、及制御信号S T H、H C L K、及びデータ出力制御回路160からの第2ラインラッチ信号T P 2とに応答して液晶パネル150のデータラインD 1～D mを駆動するための信号を発生する。一般的にデータ駆動回路120は複数の集積回路で構成される。

#### 【0037】

ゲート駆動回路140は、タイミングコントローラ110から供給される制御信号に応じて液晶パネル150のゲートラインG 1～G nを順に走査(スキャニング)する。ここで、走査とは、ゲートラインにゲートオン電圧を順に印加してゲートオン電圧が印加されたゲートラインのピクセルをデータ記録が可能な状態にさせることを言う。例えば、ピクセルは液晶容量を含み、液晶容量と関連するゲートラインに十分なゲートオン電圧を供給することによって、関連するデータライン電圧と液晶容量との間に電気的通信が行われる。

#### 【0038】

D C / D C コンバータ130に外部から電源電圧C V D Dが供給され、液晶表示装置100の動作に必要な電源すなわち、データ駆動電圧D V D D、A V D D、ゲートオン電圧V O N、ゲートオフ電圧V O F F、共通電極電圧V C O Mなどを発生する。

#### 【0039】

データ出力制御回路160は、外部電源電圧C V D D及びタイミングコントローラ110から第1ラインラッチ信号T P 1が入力され、第2ラインラッチ信号T P 2を出力する。

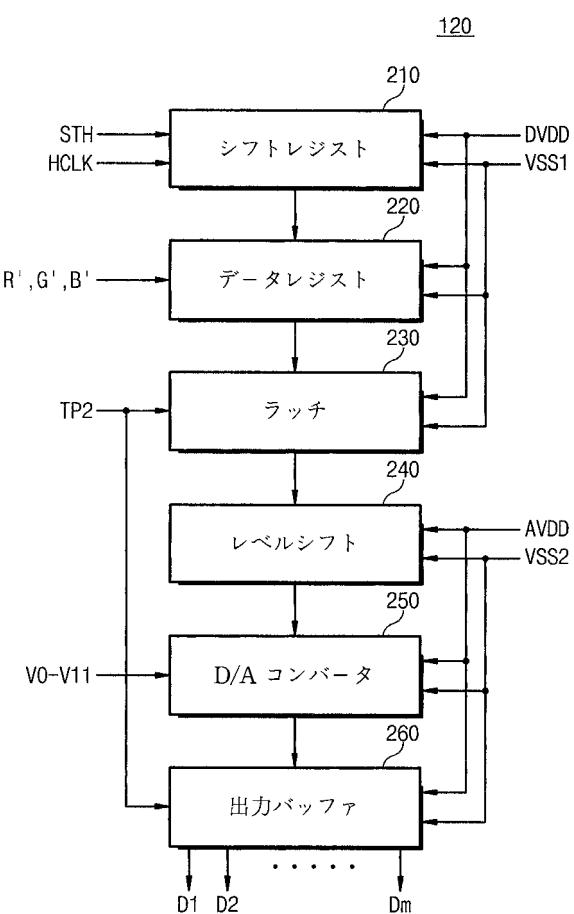

#### 【0040】

データ駆動回路120の具体的な構成が図2に示している。データ駆動回路120は順次なサンプリング信号を供給するシフトレジスタ210、サンプリング信号に応答して入力ピクセルデータを蓄積するデータレジスタ220、データレジスタ220から出力されるデータをラッチするラッチ230、ラッチからのピクセルデータの振幅を増幅するレベルシフト240、レベルシフト240から出力されるデジタルピクセルデータをアナログ信号に変換するデジタル-アナログコンバータ250、及び出力バッファ260を含む。

#### 【0041】

シフトレジスタ210は、タイミングコントローラ310からの水平同期開始信号S T Hをクロック信号H C L Kに応じて順にシフトさせてサンプリング信号として出力する。

#### 【0042】

データレジスタ220は、シフトレジスタ210からのサンプリング信号に応答してタイミングコントローラ310からのピクセルデータR'、G'、B'を一定単位ずつ順にサンプリングして蓄積する。この時、データレジスタ220の大きさは(水平方向ピクセルの数×ピクセルデータそれぞれのビット数)である。ラッチ230は、データレジスタ220からのピクセルデータをラッチして、データ出力制御回路160からの第2ラインラッチ信号T P 2に応答してラッチされたピクセルデータを出力する。レベルシフト240はラッチ230から出力されるピクセルデータの電圧スイング幅を広げるためのレベルシフティングを実行する。デジタル-アナログコンバータ250は、階調電圧V O - V 1 1を用いてレベルシフト240からのピクセルデータをアナログピクセル信号に変換する。階調電圧V O - V 1 1は階調電圧発生器(図示しない)によって発生する。出力バッファ

10

20

30

40

50

260は、デジタル-アナログコンバータ250から出力されるアナログピクセル信号を蓄積した後、ラインラッチ信号TP2に同期して液晶パネルのソースラインD1～Dmにアナログピクセル信号を供給する。例えば、ラッチ230は、第2ラインラッチ信号TP2のライジングエッジ(rising edge)でデータレジスタ220からのピクセルデータをレベルシフト240に出力して、出力バッファ260は第2ラインラッチ信号TP2のフォーリングエッジ(falling edge)からデジタル-アナログコンバータ250の出力をデータラインD1～Dkに伝達する。

#### 【0043】

パワーオン後、データ駆動電圧DVDDが供給され始めれば、シフトレジスタ210、レジスタ220及びラッチ230は駆動され始め、第2ラインラッチ信号TP2が入力される前、ラッチ230の出力は不正状態(indeterminate state)である。DC/DCコンバータ130によってデータ駆動電圧AVDDがデータ駆動回路320に供給されることによって、ラッチ230から出力される任意のレベルのピクセルデータ信号はレベルシフト240、デジタル-アナログコンバータ250及び出力バッファ260を通してデータラインD1～Dmに伝達される。ゲートオフ電圧VOFFが薄膜トランジスタをターンオフするのに十分な電圧(例えば、-13V)迄低くなる前に、薄膜トランジスタが弱くターンオンされた状態でデータラインD1～Dmに伝達されたピクセルデータ信号は薄膜トランジスタを通して液晶容量に伝達されて画像が表示される。

#### 【0044】

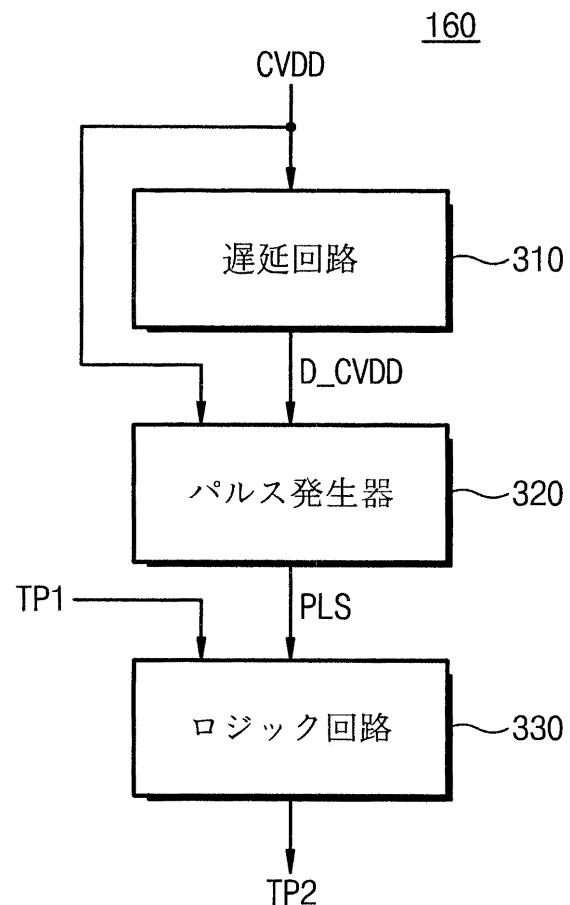

このような望まない不良画像を防止するために、本発明の実施形態に係るデータ出力制御回路160は、パワーオン後、少なくともゲートオフ電圧が十分に低くなるまで第2ラインラッチ信号TP2をハイレベルに出力することで、ラッチ230の出力をリセットする。したがって、第2ラインラッチ信号TP2がハイレベルである間データ駆動回路120はリセット状態を維持するようになる。

#### 【0045】

図3は図1に示したデータ出力制御回路160の構成を示す図である。図5を参照すれば、データ出力制御回路160は、遅延回路310、パルス発生器320、及びロジック回路330を含む。遅延回路310は、外部から供給される電源電圧CVDDを所定時間の間遅延させて、信号D\_CVDDを出力する。パルス発生器320には遅延回路310からの信号D\_CVDD及び電源電圧CVDDが入力される。パルス発生器320はパルス信号PLSを出力する。ロジック回路330にはタイミングコントローラ310からの第1ラインラッチ信号TP1とパルス発生器320からのパルス信号PLSとが入力される。ロジック回路330は第2ラインラッチ信号TP2を出力する。本発明の一実施形態においては、ロジック回路330はロジックOR演算回路によって実現される。

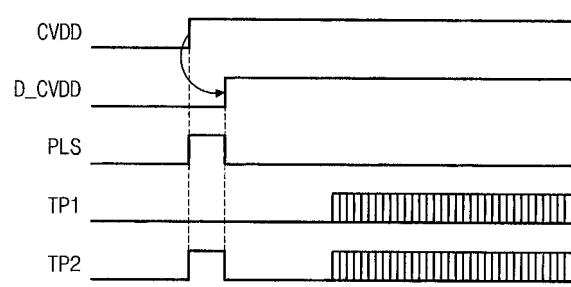

#### 【0046】

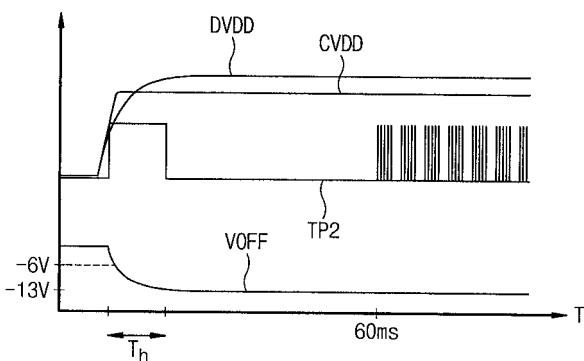

図4は図3に示したデータ出力制御回路160に用いられる信号のタイミング図であり、図5はゲートオフ電圧VOFFと第2ラインラッチ信号TP2との関係を示す図である。

#### 【0047】

図4及び図5を参照すれば、外部電源電圧CVDDが供給され始めた後、所定時間の間第2ラインラッチ信号TP2はハイレベルに維持される。第2ラインラッチ信号TP2のハイレベル期間は遅延回路310の遅延時間に該当する。この第2ラインラッチ信号TP2のハイレベル期間は、ゲートオフ信号VOFFが十分に低くなるまで要求される時間である。第2ラインラッチ信号TP2のハイレベル期間は、例えば5ms以上であれば十分である。

#### 【0048】

電圧DVDD、AVDDが入力される前に、第2ラインラッチ信号TP2がハイレベルに設定されるので、電圧DVDD、AVDDが入力された後、図2に示したラッチ230及び出力バッファ260の出力はリセットされる。したがって、ゲートオフ信号VOFFが十分に低くなるまでデータラインD1～Dmは駆動されない。したがって、パワーオン時、望まない不良画像が表示されることを防止することができる。遅延回路310の遅延時

10

20

30

40

50

間が経過した後、第2ラインラッチ信号TP2の波形はタイミングコントローラ310から入力された第1ラインラッチ信号TP1の波形と同一である。

#### 【0049】

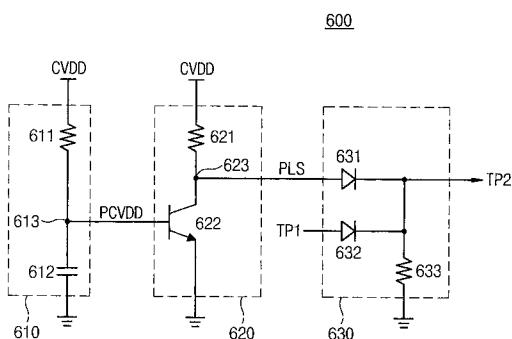

図6は図1に示したデータ出力制御回路160の他の実施形態に係る構成を示す図である。図6を参照すれば、データ出力制御回路160は、遅延回路610、パルス発生回路620、及び出力回路630を含む。遅延回路610は、外部電源電圧CVDと接地電位との間に直列に接続された抵抗611及び容量612を含む。ノード613の電位は、図6に示すPCVDDとなる。パルス発生回路620は、外部電源電圧CVDと一端が接続された抵抗621と、抵抗621と接地電位との間の電流通路と、抵抗611と容量612との間の接続ノード613と接続されたゲートを有するトランジスタ622とを含む。出力回路630は、抵抗621とトランジスタ622の接続ノード623と接続された入力端及び出力端を有するダイオード631と、タイミングコントローラ310からの第1ラインラッチ信号TP1が入力される入力端及び出力端を有するダイオード632と、ダイオード631、632の出力端と接地電圧との間に接続された抵抗633とを含む。ダイオード631、632の出力端は共通に接続され、ダイオード631、632の出力端は第2ラインラッチ信号TP2を出力する。

10

#### 【0050】

図6に示したデータ出力制御回路600の動作は次のとおりである。外部電源電圧CVDが供給された後、トランジスタ622がターンオフ状態である間、外部電源電圧CVDが抵抗621及びダイオード631を通して第2ラインラッチ信号TP2として出力される。外部電源電圧CVDが供給された後、抵抗611及び容量612によって設定された時間が経過すれば、トランジスタ622がターンオンされ、その結果、タイミングコントローラ310からの第1ラインラッチ信号TP1がダイオード632の出力端に出力される。したがって、パワーオン後、抵抗611及び容量612による遅延時間が経過すれば、第2ラインラッチ信号TP2は第1ラインラッチ信号TP1と同一となる。

20

#### 【0051】

上述したとおり、ディスプレイのパワーオン時、データ駆動電圧が入力される前にデータ駆動回路内のラッチ回路を制御するラインラッチ信号をハイレベルに設定することで、データ駆動電圧が入力された後、ラッチ回路からどんな信号も出力されない。したがって、ゲートオフ信号が十分に低くなるまでデータラインが駆動されないため、パワーオン時、望まない不良画像が表示されることを防止することができる。

30

#### 【0052】

例示的な好ましい実施形態を用いて本発明を説明したが、本発明の範囲は開示された実施形態に限定されず、本発明の範囲には多様な変形例及びその類似の構成が全部含まれる。したがって、特許請求の範囲はそのような変形例及びその類似の構成の全部を含み、できる限り幅広く解釈されなければならない。

#### 【図面の簡単な説明】

#### 【0053】

【図1】本発明の一実施形態に係る液晶ディスプレイ装置の構成を示す図である。

【図2】図1に示したデータ駆動回路の具体的な構成を示すブロック図である。

40

【図3】図1に示したデータ出力制御回路の構成を示す図である。

【図4】図3に示したデータ出力制御回路で使用される信号のタイミング図である。

【図5】ゲートオフ電圧と第2ラインラッチ信号との関係を示す図である。

【図6】図1に示したデータ出力制御回路の他の実施形態に係る構成を示す図である。

#### 【符号の説明】

#### 【0054】

100 液晶表示装置

110 タイミングコントローラ

120 データ駆動回路

130 DC/DCコンバータ

50

- 140 ゲート駆動回路

150 液晶パネル

160 データ出力制御回路

210 シフトレジスタ

220 データレジスタ

230 ラッチ

240 レベルシフタ

250 デジタル-アナログ変換器

260 出力バッファ

310 遅延回路

320 パルス発生器

330 ロジック回路

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 金 大 燐

大韓民国京畿道安城市堂旺洞 ダエウーアパートメント 103 - 1405

審査官 西島 篤宏

(56)参考文献 特開昭 61 - 238026 (JP, A)

特開平 04 - 278988 (JP, A)

特開平 01 - 253798 (JP, A)

特開平 08 - 304773 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 00 - 3 / 38

G 02 F 1 / 133 505 - 580