(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5784317号

(P5784317)

(45) 発行日 平成27年9月24日(2015.9.24)

(24) 登録日 平成27年7月31日(2015.7.31)

(51) Int.Cl.

H02M 3/28 (2006.01)

F 1

H02M 3/28

H

請求項の数 20 外国語出願 (全 34 頁)

(21) 出願番号 特願2011-23056 (P2011-23056)

(22) 出願日 平成23年2月4日 (2011.2.4)

(65) 公開番号 特開2011-167060 (P2011-167060A)

(43) 公開日 平成23年8月25日 (2011.8.25)

審査請求日 平成26年1月30日 (2014.1.30)

(31) 優先権主張番号 12/703,072

(32) 優先日 平成22年2月9日 (2010.2.9)

(33) 優先権主張国 米国(US)

(73) 特許権者 501315784

パワー・インテグレーションズ・インコーポレーテッド

アメリカ合衆国、95138・カリフォルニア州・サン・ホゼ・ヘリヤー・アベニュー

・5245

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 ユーリ・ガクノキ

アメリカ合衆国、95138 カリフォルニア州、サン・ノゼ、グレンイーグルス・サークル、5973

最終頁に続く

(54) 【発明の名称】スイッチモード電源のためのコントローラおよびスイッチモード電源

## (57) 【特許請求の範囲】

## 【請求項 1】

スイッチモード電源であって、

スイッチと、

前記スイッチに結合され、入力電圧に応答して出力を生成するように結合されるエネルギー転送要素と、

前記エネルギー転送要素および前記スイッチの両端に結合されるフィルタコンデンサと、

前記入力電圧に応答して前記出力を調整するように結合されるコントローラとを備え、

前記コントローラは、

前記電源の入力電圧のゼロ交差の前に第1の信号を生成するように結合されるゼロ交差検出器と、

前記電源の前記出力を表わすフィードバック信号に応答して駆動論理出力信号を生成するように結合されるべき駆動論理とを備え、前記駆動論理出力信号は初期オン時間を表わし、さらに

前記駆動論理出力信号に応答して駆動信号を生成するように前記ゼロ交差検出器および前記駆動論理に結合されるオン時間延長ブロックを備え、前記駆動信号は、前記電源の前記フィルタコンデンサから電荷を除去する前記スイッチのスイッチングを制御するものであり、前記駆動信号は、前記初期オン時間と延長されたオン時間との和に等しい前記スイッチの全オン時間を表わし、前記延長されたオン時間は前記第1の信号に応答する、スイッチモード電源。

10

20

**【請求項 2】**

前記第1の信号は、前記電源の前記入力電圧の前記ゼロ交差について前提条件が存在するか否かを示す前提条件信号である、請求項1に記載のスイッチモード電源。

**【請求項 3】**

前記オン時間延長ブロックは、前記前提条件がもはや存在しないことを前記前提条件信号が示すまで、または前記全オン時間がゼロ交差時間しきい値に達するまで、前記スイッチの前記延長されたオン時間を増大するよう適合される、請求項2に記載のスイッチモード電源。

**【請求項 4】**

前記オン時間延長ブロックは、前記ゼロ交差時間しきい値を表わす期間を含むゼロ交差パルス信号を受けるように結合される、請求項3に記載のスイッチモード電源。 10

**【請求項 5】**

前記ゼロ交差検出器は、前記電源の前記入力電圧がゼロ交差電圧しきい値未満であることに応答して前記第1の信号を生成する、請求項1に記載のスイッチモード電源。

**【請求項 6】**

前記ゼロ交差検出器は、前記スイッチを通って流れるスイッチ電流がゼロ交差電流しきい値未満であることに応答して前記第1の信号を生成する、請求項1に記載のスイッチモード電源。

**【請求項 7】**

前記ゼロ交差検出器は、ゼロ交差条件が存在することを示すゼロ交差信号を生成するように結合され、前記駆動論理は、前記ゼロ交差信号および前記フィードバック信号に応答して前記駆動論理出力信号を生成する、請求項1に記載のスイッチモード電源。 20

**【請求項 8】**

前記コントローラおよび前記スイッチは集積回路に含まれる、請求項1に記載のスイッチモード電源。

**【請求項 9】**

前記コントローラは、スイッチモード電源のための集積回路コントローラである、請求項1に記載のスイッチモード電源。

**【請求項 10】**

スイッチモード電源であって、 30

スイッチと、

前記スイッチに結合され、入力電圧に応答して出力を生成するように結合されるエネルギー転送要素と、

前記エネルギー転送要素および前記スイッチの両端に結合されるフィルタコンデンサと、前記入力電圧に応答して前記出力を調整するように結合されるコントローラとを備え、前記コントローラは、

前記電源の入力電圧のゼロ交差の前に第1の信号を生成するように結合されるゼロ交差検出器と、

前記電源の前記出力を表わすフィードバック信号に応答して駆動論理出力信号を生成するように結合されるべき駆動論理とを備え、前記駆動論理出力信号は初期オン時間を表わし、さらに 40

前記電源に含まれるスイッチのスイッチングを制御するように駆動信号を生成するラッチを有するオン時間延長ブロックを備え、前記ラッチは前記駆動論理出力信号に応答してセットされるように結合され、前記駆動信号は、前記電源の前記フィルタコンデンサから電荷を除去するように前記コントローラに結合されるべき前記スイッチのスイッチングを制御するものであり、前記駆動信号は、前記初期オン時間と延長されたオン時間との和に等しい前記スイッチの全オン時間を表わし、前記延長されたオン時間は前記第1の信号に応答する、スイッチモード電源。

**【請求項 11】**

前記第1の信号は、前記電源の前記入力電圧の前記ゼロ交差について前提条件が存在す 50

るか否かを示す前提条件信号である、請求項 10 に記載のスイッチモード電源。

**【請求項 12】**

前記ラッチは、前記前提条件がもはや存在しないことを前記前提条件信号が示すか、または前記全オン時間がゼロ交差時間しきい値に達した場合のいずれかにリセットされるよう<sup>10</sup>に結合される、請求項 11 に記載のスイッチモード電源。

**【請求項 13】**

スイッチモード電源であって、

スイッチと、

前記スイッチに結合され、入力電圧に応答して出力を生成するように結合されるエネルギー転送要素と、

前記エネルギー転送要素および前記スイッチの両端に結合されるフィルタコンデンサと、

前記入力電圧に応答して前記出力を調整するように結合されるコントローラとを備え、前記コントローラは、

前記入力電圧のゼロ交差の前に第 1 の信号を生成するように結合されるゼロ交差検出器と、

前記電源の前記出力を表わすフィードバック信号に応答して駆動論理出力信号を生成するように結合されるべき駆動論理とを含み、前記駆動論理出力信号は初期オン時間を表わし、さらに前記コントローラは、

前記駆動論理出力信号に応答して駆動信号を生成するように前記ゼロ交差検出器および前記駆動論理に結合されるオン時間延長ブロックを含み、前記駆動信号は、前記フィルタコンデンサから電荷を除去して前記フィルタコンデンサの電圧が前記入力電圧の大きさに実質的に従うように前記フィルタコンデンサの前記電圧をプルダウンするように前記コントローラに結合されるべきスイッチのスイッチングを制御するものであり、前記駆動信号は、前記初期オン時間と延長されたオン時間との和に等しい前記スイッチの全オン時間を表わし、前記延長されたオン時間は前記第 1 の信号に応答する、スイッチモード電源。<sup>20</sup>

**【請求項 14】**

前記入力電圧が前記エネルギー転送要素から切り離されて前記入力電圧を調節する時間量を制御するように、前記エネルギー転送要素と前記電源の入力との間に結合される調光器回路をさらに備える、請求項 13 に記載のスイッチモード電源。

**【請求項 15】**

前記調光器回路はトライアック調光器回路である、請求項 14 に記載のスイッチモード電源。<sup>30</sup>

**【請求項 16】**

前記トライアック調光器回路は、前記トライアック調光器回路がオフしないようにする最小保持電流を含み、前記オン時間延長ブロックは、前記トライアック調光器回路を通る電流が前記最小保持電流を下回らないように前記トライアック調光器回路を通る前記電流を維持するように構成される、請求項 15 に記載のスイッチモード電源。

**【請求項 17】**

前記電源の前記出力は、発光ダイオードのアレイを含む負荷に結合されるものである、請求項 13 に記載のスイッチモード電源。<sup>40</sup>

**【請求項 18】**

スイッチモード電源であって、

スイッチと、

前記スイッチに結合され、入力電圧に応答して出力を生成するように結合されるエネルギー転送要素と、

前記入力電圧に応答して前記出力を調整するように結合されるコントローラとを備え、前記コントローラは、

出力と、前記電源の前記スイッチを通る電流を表わす電流検知信号を受信するように結合された第 1 の入力と、ゼロ交差電流しきい値を表わす参照信号を受信するように結合された第 2 の入力とを有する比較器と、<sup>50</sup>

前記電流検知信号に応答するとともに前記電源の前記出力を表わすフィードバック信号に応答して、駆動論理出力信号を生成するように結合された駆動論理とを備え、

前記駆動論理出力信号は、前記電源の出力を調整するための前記スイッチのオン時間を表わし、

前記コントローラは、

前記比較器の出力に応答するとともに前記駆動論理出力信号に応答して、前記スイッチを制御するように結合されたオン時間延長ブロックをさらに備え、

前記オン時間延長ブロックは、前記電流検知信号が前記ゼロ交差電流しきい値に到達したことを前記比較器の出力が示すまで、あるいは、前記スイッチのオン時間がゼロ交差時間しきい値に到達するまで、前記スイッチのオン時間を増加する、スイッチモード電源。 10

#### 【請求項 19】

スイッチモード電源であって、

スイッチと、

前記スイッチに結合され、入力電圧に応答して出力を生成するように結合されるエネルギー転送要素と、

前記入力電圧に応答して前記出力を調整するように結合されるコントローラとを備え、前記コントローラは、

前記電源のゼロ交差条件を示すゼロ交差信号を生成するように結合されたゼロ交差検出器と、

前記ゼロ交差検出器に結合されて、前記ゼロ交差信号に応答するとともに前記電源の前記出力を表わすフィードバック信号に応答して、駆動論理出力信号を生成する駆動論理とを備え、 20

前記駆動論理出力信号は、前記電源の前記出力を表わすフィードバック信号に応答するための前記スイッチのオン時間を表わし、

前記コントローラは、

前記スイッチを通る電流を表わす第1の信号、およびゼロ交差時間しきい値を表わす第2の信号を受信するように結合された論理ゲートをさらに備え、

前記論理ゲートは、前記スイッチを通る電流がゼロ交差電流しきい値に到達するまで、あるいは、前記スイッチのオン時間が前記ゼロ交差時間しきい値に到達するまで、前記スイッチのオン時間を延長するようにさらに結合される、スイッチモード電源。 30

#### 【請求項 20】

スイッチモード電源であって、

スイッチと、

前記スイッチに結合され、入力電圧に応答して出力を生成するように結合されるエネルギー転送要素と、

前記入力電圧に応答して前記出力を調整するように結合されるコントローラとを備え、前記コントローラは、

前記電源のゼロ交差条件を示すゼロ交差信号を生成するように結合されたゼロ交差検出器と、

前記ゼロ交差検出器に結合されて、前記ゼロ交差信号に応答するとともに、前記電源の前記出力を表わすフィードバック信号に応答して、駆動論理出力信号を生成する駆動論理とを備え、 40

前記駆動論理出力信号は、前記電源の前記出力を表わすフィードバック信号に応答するための前記スイッチのオン時間を表わし、

前記コントローラは、

前記スイッチを通る電流を表わす第1の信号、およびゼロ交差時間しきい値を表わす第2の信号を受信するように結合された論理ゲートをさらに備え、

前記論理ゲートは、前記スイッチを通る電流がゼロ交差電流しきい値よりも小さく、かつ前記スイッチのオン時間が前記ゼロ交差時間しきい値よりも小さい場合に、前記スイッチのオン時間を延長するようにさらに結合される、スイッチモード電源。 50

## 【発明の詳細な説明】

## 【技術分野】

[ 0 0 0 1 ]

## 1. 発明の分野

本発明は一般的に電源に関し、より特定的にはスイッチモード電源のためのコントローラに関する。

## 【背景技术】

〔 0 0 0 2 〕

## 2. 関連技術の検討

電子機器は動作するのに電力を用いる。スイッチモード電源は、それらが高効率、小型および軽量であるために、今日の電子機器の多くへの電力供給に一般的に用いられている。従来のコンセントは高圧交流電流を与える。スイッチング電源において、高圧交流 ( a c ) 入力は、エネルギー転送要素を通して十分に調整された直流 ( d c ) 出力を与えるように変換される。スイッチモード電源制御回路は通常、出力を検知し、これを閉ループで制御することによって出力調節を行なう。動作の際、スイッチモード電源中のスイッチのデューティサイクル（典型的には全スイッチング周期に対するスイッチのオン時間の比率）を変化させることによって所望の出力を与えるようにスイッチを利用する。

〔 0 0 0 3 〕

効率、サイズ、重量、およびコストなどの要件は、スイッチモード電源を設計する際に通常考慮される。典型的に、スイッチモード電源のスイッチングを制御するコントローラは、入力端子、出力端子、または両方として機能し得るさまざまな端子を有する集積回路として設計される。スイッチモード電源のスイッチがコントローラと一体化される場合、集積回路の2つの端子がスイッチの2つの端に対応する。集積回路のさまざまな端子を、フィードバック端子、機能プログラム端子、またはコントローラ用入力電圧検知端子として利用してもよい。スイッチモード電源のいくつかの適用例について、a c 入力電圧を検知して a c 入力電圧のゼロ交差を判定する。一般的に、a c 入力電圧は本明細書中ではライン入力電圧とも称される。ゼロ交差は一般的に a c 入力電圧がゼロ電圧と交差するときを指す。換言すると、ゼロ交差は、a c 入力電圧が正から負にまたは負から正に符号を変えるときを指す。ライン入力電圧のゼロ交差をさまざまな適用例に用い得る。ライン入力電圧のゼロ交差を、a c ライン周波数を判定するのに用いてもよく、または電源のコントローラの内部クロックを更新するのに用いてもよい。

## 【発明の概要】

#### 【発明が解決しようとする課題】

[ 0 0 0 4 ]

イアック調光器はLEDランプのちらつき、高い位相角でのLEDランプの点滅、およびLEDランプのカラーシフトなどの許容できない結果を生じやすい。このように、電源は、a c 入力電圧を直接に検知してa c 入力電圧が調光回路によりいつ遮断されるかを判定することによってトライアック調光器回路に応答するように設計される、改良された従来の電源コントローラを含み得る。典型的に、a c 入力電圧は、従来のコントローラの集積回路の外部の回路構成によって直接に検知される。検知されたa c 入力電圧は、検知されたa c 入力電圧を受ける専用の端子において、または複数の機能を果たす別の端子において、改良された従来のコントローラの集積回路によって受けられ得る。

#### 【0005】

LEDランプと共にトライアック調光回路を用いる際の別の困難はトライアック自体の特徴に由来する。トライアックは、制御されたa c スイッチとして振舞う半導体構成要素である。換言すると、これは、スイッチを閉じさせるトリガ信号を制御端子で受けるまで、a c 電圧に対する開いたスイッチとして振舞う。スイッチは、スイッチを通る電流が保持電流と称される値を上回る限りは閉じたままである。大部分の白熱灯はa c 電力源から十分以上の電流を取得して、トライアックの信頼性ある一貫した動作を可能にする。しかしながら、a c 電力源からLEDランプを駆動する効率的な電源によって取得される低電流は、a c ライン周期の予測される部分の間トライアックを導通した状態に保つには十分でない可能性がある。したがって、従来の電源コントローラ設計は通常、トライアックがトリガされた後にトライアックを導通した状態に保つために電源の入力から十分な余分電流を取得するために、時にはブリーダ回路と呼ばれるダミー負荷を含む電源に頼る。一般的に、従来のブリーダ回路は、従来の電源コントローラの集積回路の外部のものである。しかしながら、従来の電源コントローラの外部の従来のブリーダ回路の使用により余分の構成要素の使用が必要となり、これはコストおよび効率における関連の不利を伴ってしまう。

#### 【0006】

電源の設計についての別の重要な考慮点は、a c 入力電圧波形に対するa c 電力源から引き込まれる)入力電流の形および位相である。a c 電力源の電圧波形は公称では正弦波である。しかしながら、多くのスイッチング電源がa c 電力源に対して与える非線形負荷により、電源によってa c 電力源から引き込まれる電流の波形は非正弦波であるおよび/またはa c 入力電圧と位相がずれている。これは、a c 電源分配システムにおける損失の増大に繋がり、世界の多くの地域では、電源によって引き込まれる入力電流が正弦波でありかつa c 入力電圧波形と位相が確実に合うように電源の製造者に強制する、法律で定められたまたは自発的な要件の主題に今やなっている。

#### 【0007】

このような入力電流波形の補正は力率改善(PFC)と称され、しばしば、力率改善機能を実行するように特別に設計された、電源への入力段を必要とする。入力a c 電流および電圧波形が正弦波でありかつ完全に位相が合っていれば、電源の力率は1である。換言すると、力率改善された入力は、a c 源両端への可変抵抗の結合と同等の負荷をa c 源に与えるであろう。a c 源電圧に対する入力電流の高調波歪および/または位相のずれが増大するにつれ、力率は1を下回っていく。力率の要件は典型的に0.9よりも大きな力率を要件とし、入力電流波形の高調波含有量についての要件を有することがある。

#### 【0008】

電源の力率を増大させる一般的な方法は、a c 源電圧と位相を合わせつつ理想的な正弦波形に近い入力電流波形を確立する昇圧コンバータまたはフライバックコンバータの使用を含む。電源の力率を増大させる別の方法はブリーダ回路を利用する事である。スイッチモード電源は典型的に、スイッチモード電源のスイッチを通る高周波電流をフィルタリングするフィルタコンデンサを含む。ブリーダ回路はフィルタコンデンサの放電を容易にし得、これは、フィルタコンデンサ両端の電圧がa c 入力電圧の正の大きさに実質的に従うようにフィルタコンデンサに対する電圧をプルダウンするのを助ける。このように、ブリーダ回路は、a c 源電圧と位相を合わせつつ理想的な正弦波形に近い入力電流波形を確

10

20

30

40

50

立するのを助ける。しかしながら、多数の適用例については、従来のブリーダ回路は典型的に、電源コントローラの集積回路の外部の回路である。典型的に、従来のブリーダ回路は、電源の入力で結合される抵抗器によって実現される。しかしながら、以上述べたように、従来の電源コントローラの外部の従来のブリーダ回路を使用すると余分の構成要素を用いる必要があるため、コストおよび効率の点で関連の不利を伴ってしまう。

#### 【0009】

本発明のいくつかの実施例の上記および他の局面、特徴および利点が以下の図面と関連して提示される以下により特定的な説明からより明らかになるであろう。

#### 【図面の簡単な説明】

#### 【0010】

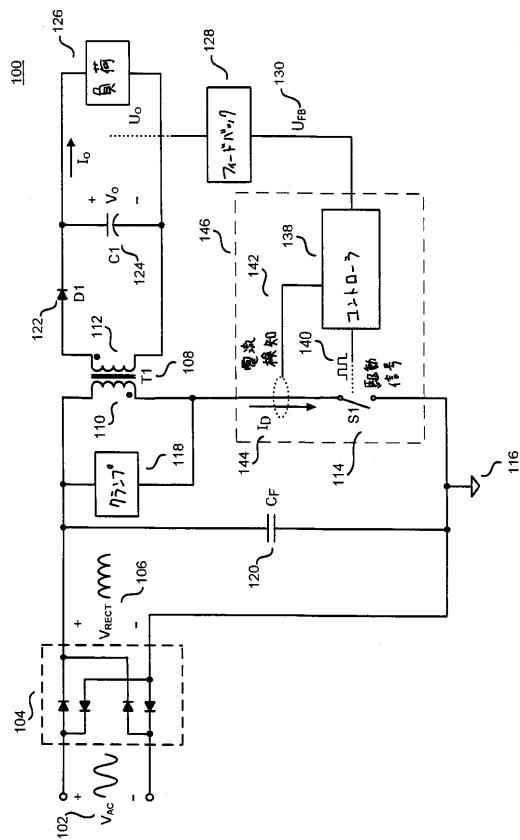

【図1】本発明の実施例に従うコントローラを利用する例示的なスイッチング電源を図示する機能ブロック図である。

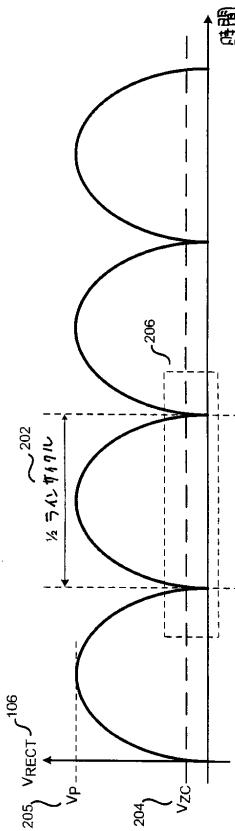

【図2A】本発明の実施例に従う、図1のスイッチング電源の例示的な整流された入力電圧波形を図示する図である。

【図2B】本発明の実施例に従う、図2Aの例示的な整流された入力電圧の一部と、対応するゼロ交差信号とを図示する図である。

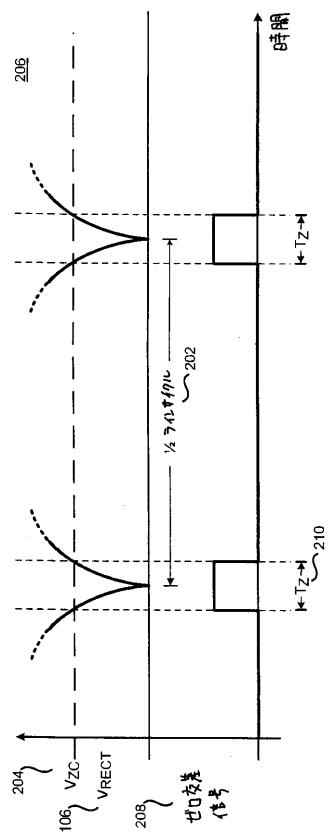

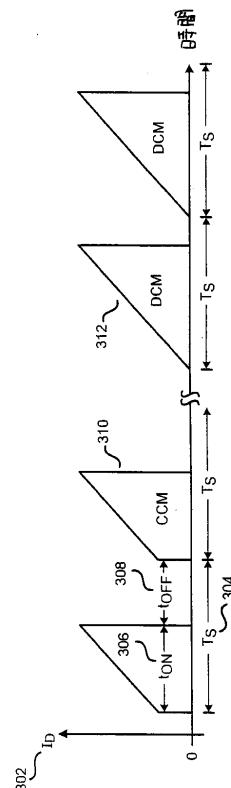

【図3】本発明の実施例に従う、連続導通モード（CCM）および不連続導通モード（DCM）で動作するスイッチング電源の例示的なスイッチ電流波形を図示する図である。

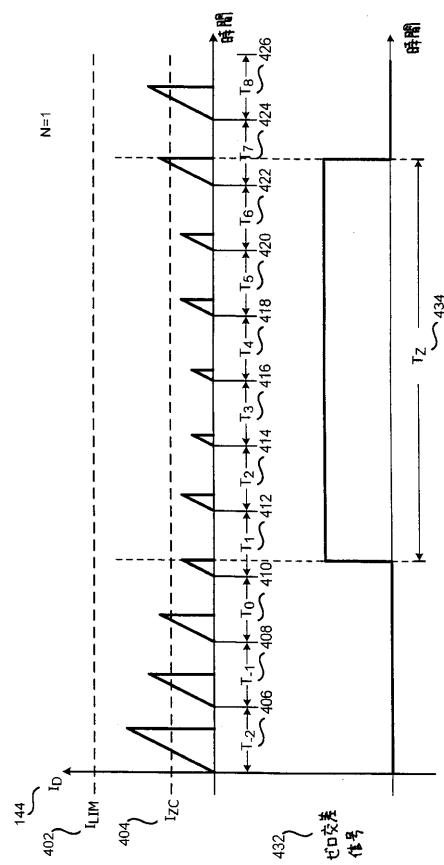

【図4A】本発明の実施例に従う、DCMで動作するスイッチング電源の例示的なスイッチ電流波形と対応するゼロ交差信号とを図示する図である。

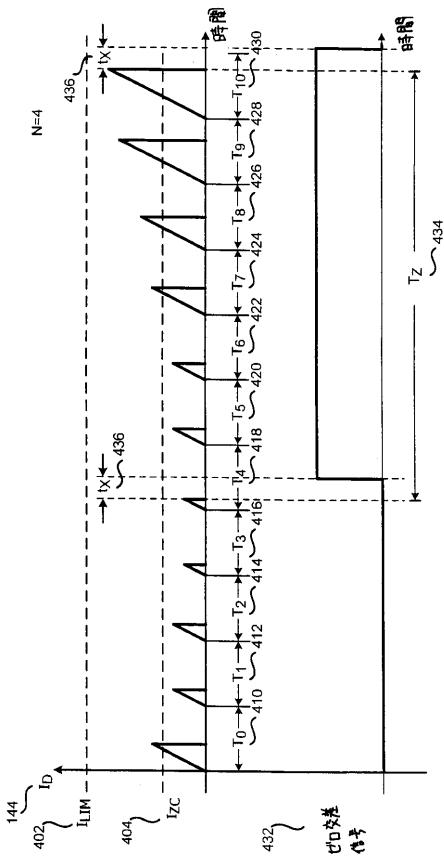

【図4B】本発明の実施例に従う、DCMで動作するスイッチング電源のスイッチ電流波形と、対応するゼロ交差信号との別の例を図示する図である。

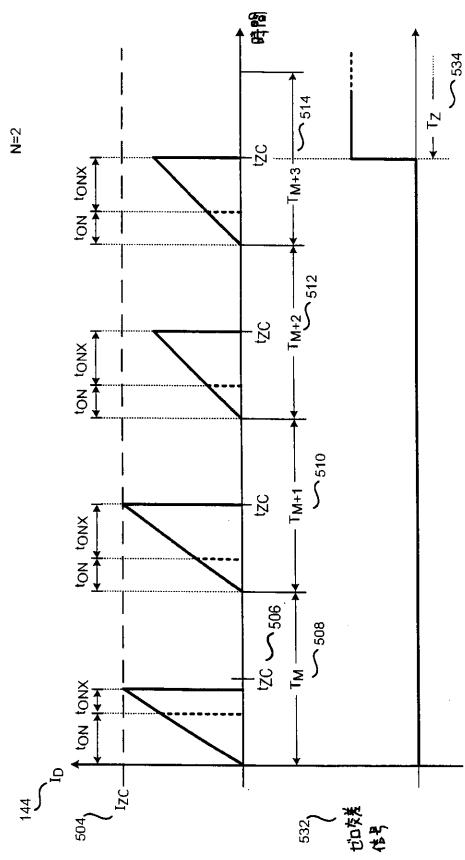

【図5】本発明の実施例に従う、例示的なスイッチ電流波形と、対応するゼロ交差信号とを図示する図である。

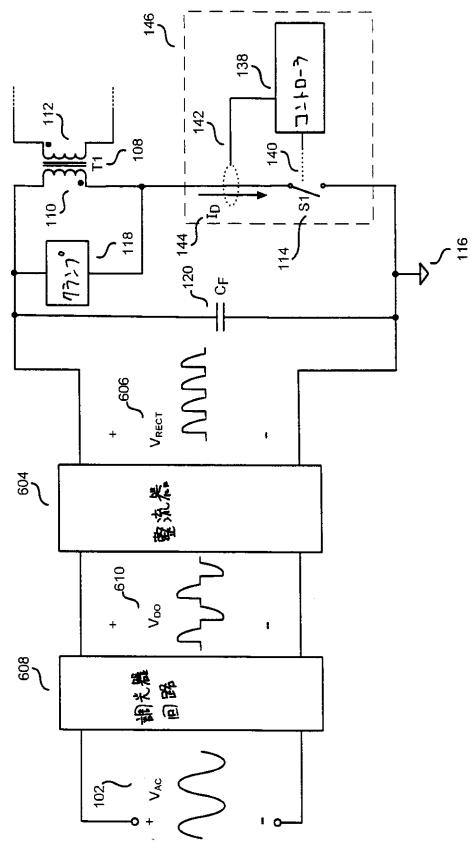

【図6】本発明の実施例に従う調光器回路およびコントローラを利用する例示的なスイッチング電源を図示する機能ブロック図である。

【図7A】本発明の実施例に従う、図6のスイッチング電源の例示的な整流された入力電圧波形を図示する図である。

【図7B】本発明の実施例に従う、図7Aの例示的な整流された入力電圧の一部と、対応するゼロ交差信号とを図示する図である。

【図8A】本発明の実施例に従う、スイッチング電源の別の例示的な整流された入力電圧波形を図示する図である。

【図8B】本発明の実施例に従う、図8Aの例示的な整流された入力電圧の一部と、対応するゼロ交差信号とを図示する図である。

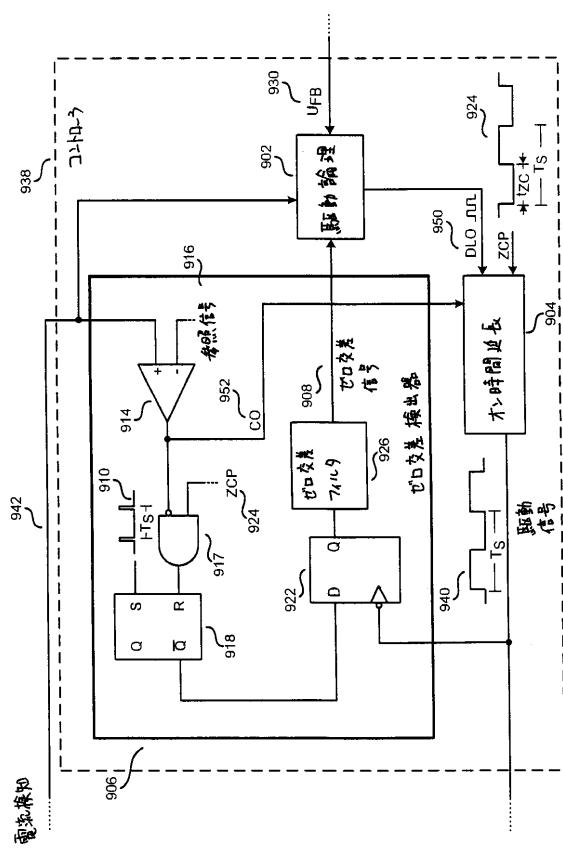

#### 【図9A】本発明の実施例に従うコントローラの機能ブロック図である。

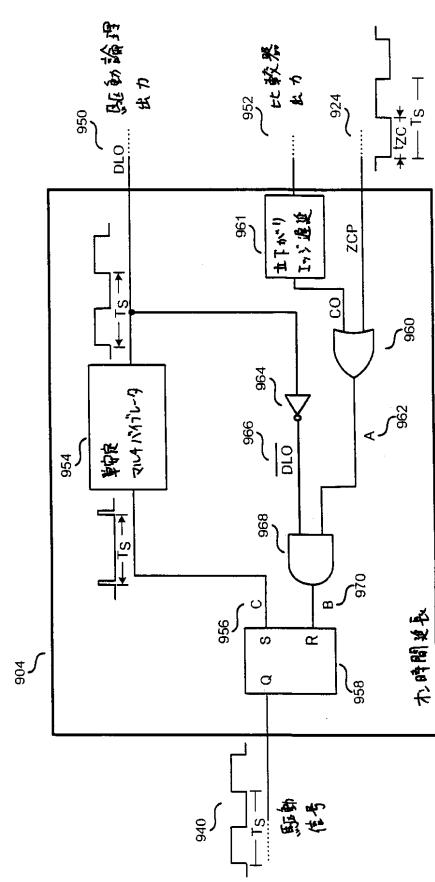

【図9B】本発明の実施例に従う、図9Aのコントローラのオン時間延長ブロックの機能ブロック図である。

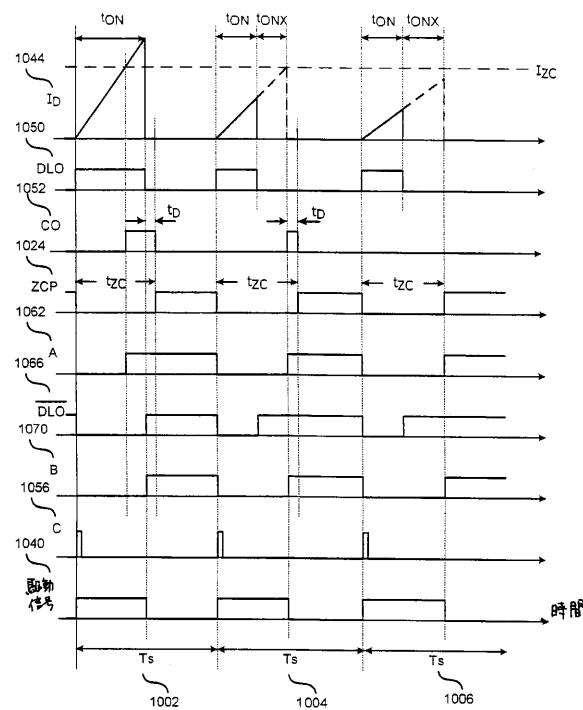

【図10】本発明の実施例に従う、図9Aおよび図9Bのコントローラおよびオン時間延長ブロックの信号のさまざまな波形を図示する図である。

#### 【発明を実施するための形態】

#### 【0011】

##### 詳細な説明

図面のいくつかの図を通して、対応の参照番号は対応の構成要素を示す。当業者は、図中の要素が簡潔さおよび明瞭さのために図示されており、かつ縮尺通りに必ずしも描かれていないことを認めるであろう。たとえば、図中の要素のうちいくつかの寸法は、本発明のさまざまな実施例の理解を向上させるのを助けるために他の要素に対して誇張されているかもしれない。また、商業的に見込みのある実施例で有用なまたは必要な、一般的であるが十分に理解される要素は、本発明のこれらのさまざまな実施例のより妨げられない見方を容易にするために、示されていないことがしばしばある。

#### 【0012】

10

20

30

40

50

照明用 L E D ドライバのトライアック調光のための無損失集積ブリーダのための方法および装置の実施例が本明細書中に記載される。以下の説明では、実施例の完全な理解を与えるため、数多くの具体的な詳細を述べる。しかしながら、具体的な詳細のうち 1 つ以上がなくても、または他の方法、構成要素、材料などを用いて、本明細書中に記載の技術を実践可能であることを当業者は認識するであろう。他の事例では、ある局面を曖昧にすることを回避するため、周知の構造、材料または動作を詳細に示したり説明したりしていない。

#### 【 0 0 1 3 】

この明細書を通じて、「一実施例」、「ある実施例」、「一例」、または「ある例」に対する参照は、実施例または例と関連して説明される特定的な特徴、構造、または特性が本発明の少なくとも一実施例に含まれることを意味する。したがって、「一実施例では」、「ある実施例では」、「一例」、または「ある例」という、この明細書を通じてさまざまな場所に現われる文言は、必ずしも同じ実施例または例をすべて指しているわけではない。さらに、特定的な特徴、構造、または特性は、1 つ以上の実施例または例において任意の好適な組合せおよび / または副次的組合せで組合されてもよい。さらに、ここで与えられる図は当業者への説明目的のためのものであり、図面は必ずしも縮尺通りに描かれているわけではないことが認められる。

#### 【 0 0 1 4 】

スイッチモード電源のいくつかの適用例について、d c 入力電圧を検知して、a c 入力電圧のゼロ交差を判定する。発光ダイオード ( L E D ) の位相調光適用例については、電源コントローラがライン入力電圧のゼロ交差の持続時間を検知するであろう。a c 入力電圧のゼロ交差の持続時間の判定は、電源コントローラに調光器回路が利用されていることを示し、したがって電源の出力が調整される量を変更する。本発明の実施例については、電源コントローラはオン時間延長を利用してスイッチのオン時間を延長し、これによりライン入力電圧のゼロ交差の判定が容易になる。

#### 【 0 0 1 5 】

さらに、トライアック調光回路を利用する L E D の位相調光適用例については、ブリーダ回路を利用して、電源の入力から余分の電流を取得してトライアック調光器回路のトライアックを導通した状態に保つのを助け得る。トライアックは、制御された a c スイッチとして振舞う半導体構成要素である。換言すると、これは、スイッチを閉じるトリガ信号を制御端子で受けるまでは、a c 電圧に対する開いたスイッチとして振舞う。スイッチは、スイッチを通る電流が保持電流と称される値を上回る限りは閉じたままである。大部分の白熱灯は、a c 電力源から十分以上の電源を取得してトライアックの信頼性ある一貫した動作を可能にする。しかしながら、a c 電力源からの、L E D を駆動する効率的な電源によって取得される低電流は、a c ライン周期の予測される部分の間トライアックを導通した状態に保つには十分でない可能性がある。ブリーダ回路を利用して、電源の入力から余分の電流を取得してトライアック調光器回路のトライアックを導通した状態に保つのを助け得る。一般的に、ブリーダ回路は電源コントローラの外部のものである。しかしながら、本発明の実施例については、スイッチのオン時間を延長するために電源コントローラによって利用されるオン時間延長はブリーダ回路としても機能し得る。オン時間延長により、電源のスイッチはその意図されるオン時間よりも長い間オンのまま留まることができる。このように、フィルタコンデンサからより多くの電荷が除去され、余分の電流が電源の入力から取得される。

#### 【 0 0 1 6 】

力率改善 ( P F C ) 目的のためにブリーダ回路も利用してもよい。電源の力率を増大させる 1 つの方法はブリーダ回路を利用することである。スイッチモード電源は典型的に、スイッチモード電源のスイッチを通る高周波電流をフィルタリングするフィルタコンデンサを含む。ブリーダ回路はフィルタコンデンサの放電を容易にし得、フィルタコンデンサ両端の電圧が a c 入力電圧の正の大きさに実質的に従うようにフィルタコンデンサに対する電圧をプルダウンするのを助ける。このように、ブリーダ回路は、a c 源電圧と位相を

10

20

30

40

50

合わせつつ理想的な正弦波形に近い入力電流波形を確立するのを助ける。しかしながら、多数の適用例については、ブリーダ回路は典型的に電源コントローラの集積回路の外部の回路である。典型的に、ブリーダ回路は、電源の入力で結合される抵抗器によって実現される。この解決策は望ましくないであろう。なぜならブリーダ回路は（熱の形態で）エネルギーを損失するであろうからであり、またブリーダ回路のために余分の構成要素を用いる必要があるため、コストおよび効率の点で関連の不利を伴ってしまうからである。しかしながら、本発明の実施例については、スイッチのオン時間を延長するために電源コントローラにより利用されるオン時間延長もブリーダ回路として機能し得る。意図されるオン時間を過ぎてスイッチのオン時間を延長することにより、フィルタコンデンサから多くの電荷が除去され、フィルタコンデンサ両端の電圧がa c入力電圧の正の大きさに従う。

10

#### 【0017】

さらに、典型的にa c入力電圧は、従来のコントローラの集積回路の外部の回路構成によって直接に検知される。検知されたa c入力電圧は、検知されたa c入力電圧を専用に受ける端子において、または複数の機能を果たす別の端子において、従来のコントローラによって受けられてもよい。しかしながら、付加的な端子はスイッチモード電源の従来のコントローラに不要なコストおよびサイズを付加してしまう。従来のコントローラの集積回路の外部の回路構成はスイッチモード電源にもコストを付加してしまう。本発明の実施例では、入力電圧は、スイッチモード電源のスイッチを通る電流を用いて間接的に検知され得る。その結果、スイッチの一方端がa c入力電圧を間接的に検知するのにも既に用いられている端子を用いれば、a c入力電圧を単に検知するだけの専用の端子の必要性をなくし、かつa c入力電圧を検知するための外部回路構成の必要性もなくすであろう。

20

#### 【0018】

まず図1を参照して、例示的なスイッチング電源100の機能ブロック図を図示する。これは、a c入力電圧 $V_{AC}102$ 、ブリッジ整流器104、整流された電圧 $V_{RECT}106$ 、エネルギー転送要素T1 108、エネルギー転送要素T1 108の1次巻線110、エネルギー転送要素T1 108の2次巻線112、スイッチS1 114、入力帰還116、クランプ回路118、フィルタコンデンサC<sub>F</sub>120、整流器D1 122、出力コンデンサC1 124、出力量U<sub>o</sub>、出力電圧V<sub>o</sub>、出力電流I<sub>o</sub>、フィードバック回路128、フィードバック信号U<sub>FB</sub>130、コントローラ138、駆動信号140、電流検知入力信号142、およびスイッチ電流I<sub>D</sub>144を含む。図1にはスイッチング電源100に結合された負荷126も図示する。図1に図示される例示的なスイッチング電源100は、本発明の教示から利するであろうスイッチング電源トポロジの一例であるフライバックレギュレータとして一般的に構成される。しかしながら、スイッチング電源レギュレータの他の公知のトポロジおよび構成も本発明の教示から利するであろうことが認められる。

30

#### 【0019】

スイッチング電源100は未調整入力電圧から負荷126に出力電力を与える。一例では、入力電圧はa c入力電圧 $V_{AC}102$ である。別の例では、入力電圧は整流された電圧 $V_{RECT}106$ などの整流されたa c入力電圧である。示されるように、ブリッジ整流器104はa c入力電圧 $V_{AC}102$ を受け、整流された電圧 $V_{RECT}106$ を生成する。ブリッジ整流器104はさらにエネルギー転送要素T1 108に結合する。本発明のいくつかの実施例では、エネルギー転送要素T1 108は結合されたインダクタであり得る。他の実施例では、エネルギー転送要素T1 108は変圧器であり得る。図1の例では、エネルギー転送要素T1 108は、2つの巻線、すなわち1次巻線110と2次巻線112とを含む。しかしながら、エネルギー転送要素T1 108は2つよりも多くの巻線を有してもよいことが認められるべきである。1次巻線110はスイッチS1 114にさらに結合され、これは次に入力帰還116にさらに結合される。一実施例では、スイッチS1 114は、金属酸化物半導体電界効果トランジスタ(MOSFET)などのトランジスタであり得る。別の例では、コントローラ138は、モノリシック集積回路として実現されてもよく、または個別の電気的要素もしくは個別のおよび集積された要素の組合せによって実

40

50

現されてもよい。コントローラ 138 およびスイッチ S1 114 はハイブリッドまたはモノリシック集積回路のいずれかとして製造される集積回路 146 の一部を形成し得る。

#### 【0020】

さらに、図 1 の実施例のクランプ回路 118 は、エネルギー転送要素 T1 108 の 1 次巻線 110 の両端に結合されて図示される。フィルタコンデンサ Cf120 は 1 次巻線 110 およびスイッチ S1 114 の両端に結合し得る。換言すると、フィルタコンデンサ Cf120 はブリッジ整流器 104 および入力帰還 116 に結合し得る。エネルギー転送要素 T1 108 の 2 次巻線 112 は整流器 D1 122 に結合される。図 1 の例では、整流器 D1 122 はダイオードとして例示される。しかしながら、いくつかの実施例では、整流器 D1 122 は、同期整流器として用いられるトランジスタであってもよい。出力コンデンサ C1 124 および負荷 126 の両者とも図 1 では整流器 D1 122 に結合されて示される。出力が負荷 126 に与えられ、調整された出力電圧  $V_o$ 、調整された出力電流  $I_o$ 、またはこの 2 つの組合せのいずれかとして与えられ得る。

#### 【0021】

スイッチモード電源 100 はさらに、出力量  $U_o$  として例示される出力を調整する回路構成を備える。一般的に、調整された出力量  $U_o$  は出力電圧  $V_o$ 、出力電流  $I_o$ 、またはその 2 つの組合せのいずれかである。フィードバック回路 128 は、スイッチモード電源 100 の出力量  $U_o$  を検知するように結合され、フィードバック信号  $U_{FB} 130$  を生成する。他の実施例では、フィードバック信号  $U_{FB} 130$  は、出力量  $U_o$  を表わす変圧器の入力側で 1 つ以上の量を検知することから導出され得る。フィードバック回路 128 は、コントローラ 138 がフィードバック信号  $U_{FB} 130$  を受けるように、コントローラ 138 の端子にさらに結合される。コントローラ 138 は、電流検知入力信号 142 を受けるための端子をさらに含む。電流検知入力信号 142 は、スイッチ S1 114 のスイッチ電流  $I_D 144$  を表わす。さらに、スイッチ S1 114 はコントローラ 138 から駆動信号 140 を受ける。

#### 【0022】

動作の際、図 1 のスイッチング電源 100 は、a c 入力電圧  $V_{AC} 102$  などの未調整入力から負荷 126 への出力電力を与える。ブリッジ整流器 104 が a c 入力電圧  $V_{AC} 102$  を受け、整流された電圧  $V_{RECT} 106$  を生成する。フィルタコンデンサ Cf120 はスイッチ S1 114 からの高周波電流をフィルタリングする。他の適用例については、フィルタコンデンサ Cf120 は、d c 電圧がエネルギー転送要素 T1 108 に印加されるように十分に大きいものであってもよい。しかしながら、力率改善 (PFC) を有する電源については、小さなフィルタコンデンサ Cf120 を利用して、エネルギー転送要素 T1 108 に印加される電圧が整流された電圧  $V_{RECT} 106$  に実質的に従うこと可能にし得る。

そのため、フィルタコンデンサ Cf120 の値は、フィルタコンデンサ Cf120 の電圧が入力ライン電圧の各々のハーフラインサイクルの間実質的に 0 に達するように選択され得る。または、換言すると、フィルタコンデンサ Cf120 の電圧は、a c 入力電圧  $V_{AC} 102$  の正の大きさに実質的に従う。その結果、コントローラ 138 がゼロ交差条件を検出し得る。また、さらに論じられるように、コントローラ 138 が利用するオン時間延長によりフィルタコンデンサ Cf120 からより多くの電荷が除去される。その結果、フィルタコンデンサ Cf120 の放電は 1 次巻線 110 の電圧をプルダウンするのを助け、これはコントローラ 138 が a c 入力電圧  $V_{AC} 102$  のゼロ交差を検出するのを助け得る。

#### 【0023】

スイッチング電源 100 はエネルギー転送要素 T1 108 を利用して 1 次巻線 110 と 2 次巻線 112 との間で電圧を転送する。クランプ回路 118 は 1 次巻線 110 に結合されて、スイッチ S1 114 の最大電圧を制限する。スイッチ S1 114 は駆動信号 140 に応答して開閉される。閉じたスイッチは電流を導通し得、オンと考えられる一方で、開いたスイッチは電流を導通することができず、オフと考えられることが一般的に理解される。いくつかの実施例では、スイッチ S1 114 はトランジスタであり得、スイッ

10

20

30

40

50

チ S 1 114 およびコントローラ 138 は集積回路 146 の一部を形成し得る。動作の際、スイッチ S 1 114 のスイッチングにより、整流器 D 1 122 において脈動電流が生成する。整流器 D 1 122 の電流は出力コンデンサ C 1 124 によってフィルタリングされ、負荷 126 において実質的に一定の出力電圧  $V_o$ 、出力電流  $I_o$ 、またはその 2 つの組合せを生成する。いくつかの実施例では、負荷 126 は LED アレイである。

#### 【0024】

フィードバック回路 128 は、電源 100 の出力量  $U_o$  を検知して、コントローラ 138 にフィードバック信号  $U_{FB} 130$  を与える。フィードバック信号  $U_{FB} 130$  は電圧信号または電流信号であってもよく、出力量  $U_o$  に関する情報をコントローラ 138 に与える。さらに、コントローラ 138 は、スイッチ S 1 114 中のスイッチ電流  $I_D 144$  を中継する電流検知入力信号 142 を受ける。スイッチ電流  $I_D 144$  は、たとえば、個別の抵抗器の両端の電圧、またはトランジスタが導通しているときのトランジスタの両端の電圧など、さまざまな態様で検知され得る。コントローラ 138 は、電流検知入力信号 142 が示すスイッチ電流  $I_D 144$  を利用して、a c 入力電圧  $V_{AC} 102$  のゼロ交差を判定する。さらに論じられるように、コントローラ 138 は次に、a c 入力電圧  $V_{AC} 102$  のゼロ交差についての情報を表わすゼロ交差信号を生成する。また、以下にさらに説明されるように、コントローラ 138 はスイッチ S 1 114 のオン時間延長を利用して、a c 入力電圧  $V_{AC} 102$  がいつゼロ交差条件にあるのかを判定する。ゼロ交差信号を用いて、コントローラの内部周波数を較正したり、またはいつ位相調光回路が利用されるかを判定したりしてもよい。

#### 【0025】

コントローラ 138 は駆動信号 140 を出力し、さまざまなシステム入力に応答してスイッチ S 1 114 を動作させ、出力量  $U_o$  を所望の値に実質的に調整する。一実施例では、駆動信号 140 は、論理ハイおよび論理ローのセクションの長さが変化する矩形パルス波形であり得る。論理ハイの値が閉じたスイッチに対応し、論理ローが開いたスイッチに対応する。別の実施例では、駆動信号 140 は実質的に長さが固定された論理ハイ（またはオン）パルスを備え、かつ発振器サイクルの数毎にオンのパルスの数を変化させることによって調整され得る。

#### 【0026】

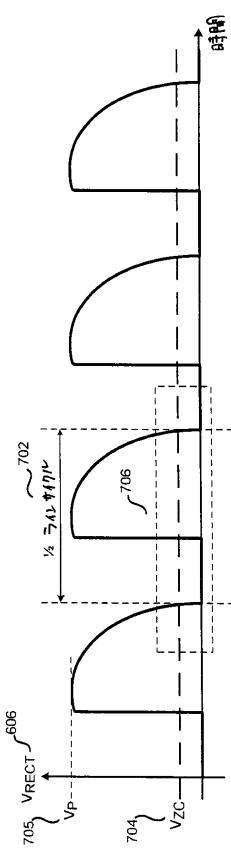

次に図 2 A を参照して、図 1 のスイッチング電源の整流された電圧  $V_{RECT} 106$  の例示的な波形の図を図示する。これは、ハーフラインサイクル 202、ゼロ交差電圧しきい値 204、ピーク電圧  $V_p 205$ 、および部分 206 を含む。図 2 B は、例示的な整流された電圧  $V_{RECT} 106$  の部分 206 および対応のゼロ交差信号 208 を図示する。

#### 【0027】

一般的に、a c 入力電圧  $V_{AC} 102$  は正弦波形であり、a c 入力電圧  $V_{AC} 102$  の周期がフルラインサイクルと称される。数学的には、 $V_{AC}(t) = V_p \sin(2\pi f_L t)$  である。式中、 $V_p 205$  が a c 入力電圧  $V_{AC} 102$  のピーク電圧であり、 $f_L$  がライン入力電圧の周波数である。または、換言すると、 $f_L$  は a c 入力電圧  $V_{AC} 102$  のライン周波数である。フルラインサイクルはライン周波数  $f_L$  の逆数である、または数学的にはフルラインサイクル =  $1 / f_L$  であることが認められるべきである。以上で言及したように、整流された電圧  $V_{RECT} 106$  は、ブリッジ整流器 104 への入力が a c 入力電圧  $V_{AC} 102$  である場合の、ブリッジ整流器 104 の結果的な出力である。図 2 A に示される例示的な整流された電圧  $V_{RECT} 106$  については、ブリッジ整流器 104 は、ブリッジ整流器 104 の出力が正の大きさとなるように、または数学的には  $V_{RECT} = |V_{AC}| = |V_p \sin(2\pi f_L t)|$  となるように、a c 入力電圧  $V_{AC} 102$  を変換した。その結果、整流された電圧  $V_{RECT} 106$  はハーフラインサイクル 202 をすべて繰返す。図 2 A はゼロ交差電圧しきい値  $V_{zc} 204$  も図示する。いくつかの実施例については、ゼロ交差電圧  $V_{zc} 204$  は実質的に 0 に等しい。他の実施例については、ゼロ交差電圧  $V_{zc} 204$  は、整流された電圧  $V_{RECT} 106$  のピーク電圧  $V_p 205$  の実質的に 5 分の 1 である。たとえば、整流された電圧  $V_{RECT} 106$  のピーク電圧  $V_p 205$  が実質的に 125 V に等し

10

20

30

40

50

い場合、ゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  は実質的に 25V に等しい。別の実施例では、ゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  は、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  のピーク電圧  $V_p\ 2\ 0\ 5$  の実質的に 4 分の 1 である。ゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  の値がゼロ電圧に近づくにつれ、ゼロ交差信号 208 がより正確になることが認められるべきである。しかしながら、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  の値がゼロ電圧に近づくにつれ、コントローラ 138 の実施例については、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  の値を検知することがより難しくなるであろう。特に、コントローラ 138 は、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  がゼロ電圧にあるまたはその近くにある場合、電流検知入力信号 142 が与えるスイッチ電流  $I_D\ 1\ 4\ 4$  を通して整流された電圧  $V_{RECT\ 1\ 0\ 6}$  の値を検知するのにいくらかの困難を有し得る。このように、コントローラ 138 の実施例は、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  の値がゼロ電圧にあるまたはその近くにある場合にゼロ交差条件の検知を可能にするように、ゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  の非ゼロの値を有し得る。さらに、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  は、部分的にはフィルタコンデンサ  $C_F\ 1\ 2\ 0$  の選択された値により、ゼロに達しないかもしれない。

10

### 【0028】

図 2B は例示的な整流された電圧  $V_{RECT\ 1\ 0\ 6}$  の部分 206 および対応のゼロ交差信号 208 を図示する。コントローラ 138 は、a c 入力電圧  $V_{AC\ 1\ 0\ 2}$  および整流された電圧  $V_{RECT\ 1\ 0\ 6}$  の値を検知してゼロ交差信号 208 を生成する。整流された電圧  $V_{RECT\ 1\ 0\ 6}$  がゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  未満である場合、ゼロ交差信号 208 は、ゼロ交差条件が存在することを示す状態に変化する。ゼロ交差信号 208 は、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  がゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  を上回るまではその状態から変化しない。

20 図 2B に示される例については、ゼロ交差信号 208 は、論理ハイおよび論理ローのセクションを有する矩形パルス波形である。整流された電圧  $V_{RECT\ 1\ 0\ 6}$  がゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  未満である場合、ゼロ交差信号 208 の値は論理ハイである。整流された電圧  $V_{RECT\ 1\ 0\ 6}$  がゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  を上回る場合、ゼロ交差信号 208 の値は論理ローである。ゼロ交差信号 208 がゼロ交差条件が存在すると示す時間の長さはゼロ交差パルス幅  $T_z\ 2\ 1\ 0$  で示される。図 2B に示される例については、ゼロ交差パルス幅  $T_z$  は、ゼロ交差信号 208 が論理ハイである時間の長さを示す。

### 【0029】

図 2A に示される整流された電圧  $V_{RECT\ 1\ 0\ 6}$  は、正の大きさまたは数学的には  $V_{RECT} = |V_{AC}| = |V_p \sin(2\pi f_L t)|$  である a c 入力電圧  $V_{AC\ 1\ 0\ 2}$  である。整流された電圧  $V_{RECT\ 1\ 0\ 6}$  の値が 0 に近い電圧である時間は、a c 入力電圧  $V_{AC\ 1\ 0\ 2}$  の値が交差ゼロ電圧、したがって「ゼロ交差」という用語に近い場合に対応する。換言すると、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  がいつ 0 に近い電圧であるかを検出することは、a c 入力電圧  $V_{AC\ 1\ 0\ 2}$  がいつゼロ電圧と交差するかを検出することに対応する。図 2B に示されるように、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  がゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  未満である場合、ゼロ交差信号 208 はハイのパルスを出力し、コントローラ 138 にゼロ交差条件を示す。換言すると、 $-V_{ZC} < V_{AC}(t) < V_{ZC}$  である場合、ゼロ交差信号 208 はハイのパルスを出力してゼロ交差条件を示す。本発明の実施例については、コントローラ 138 はスイッチ S1 114 のオン時間延長を利用して、a c 入力電圧  $V_{AC\ 1\ 0\ 2}$  のゼロ交差を判定する。

30 40

### 【0030】

図 3 にさまざまな動作モードのスイッチ電流を図示する。図 1 のスイッチモード電源の例示的なスイッチ電流波形の図を図示する。これは、スイッチング周期  $T_S\ 3\ 0\ 4$ 、スイッチオン時間  $t_{ON}\ 3\ 0\ 6$ 、スイッチオフ時間  $t_{OFF}\ 3\ 0\ 8$ 、台形 310、および三角形 312 を含む。図 3 は、コントローラが連続導通モード (CCM) および不連続導通モード (DCM) の両方で動作している時間についてのスイッチ電流  $I_D\ 3\ 0\ 2$  の一般的な波形を図示する。スイッチ電流  $I_D\ 3\ 0\ 2$  の一般的な波形は、図 1 に図示されるスイッチ電流  $I_D\ 1\ 4\ 4$  の例を表わす。

### 【0031】

任意のスイッチング周期  $T_s$  3 0 4 の間、スイッチ S 1 1 1 4 はコントローラ 1 3 8 からの駆動信号 1 4 0 に応答して導通し、出力量  $U_o$  を調整し得る。スイッチング周期  $T_s$  3 0 4 は、スイッチオン時間  $t_{ON}$  3 0 6 およびスイッチオフ時間  $t_{OFF}$  3 0 8 の 2 つの時間のセクションに分けられ得る。スイッチオン時間  $t_{ON}$  3 0 6 は、スイッチ S 1 1 1 4 が導通し得るスイッチング周期  $T_s$  3 0 4 の部分を示す。スイッチオフ時間  $t_{OFF}$  3 0 8 は、スイッチ S 1 1 1 4 が導通することができないスイッチング周期  $T_s$  3 0 4 の残余の部分を示す。図 3 の電流波形は 2 つの基本的な動作モードを図示する。台形 3 1 0 は連続導通モード (CCM) の特徴である一方で、三角形 3 1 2 は不連続導通モード (DCM) の特徴である。CCM の間、スイッチ電流  $I_D$  3 0 2 は、スイッチオン時間  $t_{ON}$  3 0 6 の開始直後は実質的に非ゼロである。DCM では、スイッチ電流  $I_D$  3 0 2 は、スイッチオン時間  $t_{ON}$  3 0 6 の開始直後は実質的にゼロである。スイッチオフ時間  $t_{OFF}$  3 0 8 の間、スイッチ電流  $I_D$  3 0 2 は CCM および DCM の両方について実質的にゼロである。本発明の実施例に従うスイッチング電源 1 0 0 は、CCM または DCM のいずれかで動作し得る。

10

#### 【0032】

次に図 4 A を参照して、例示的なスイッチ電流波形および結果的に生じるゼロ交差信号 4 3 2 の図を図示する。これは、スイッチ電流  $I_D$  1 4 4、電流リミットしきい値  $I_{LIM}$  4 0 2、ゼロ交差電流しきい値  $I_{ZC}$  4 0 4、スイッチングサイクル  $T_{-2}$  4 0 6 から  $T_8$  4 2 6、およびゼロ交差パルス  $T_Z$  4 3 4 を含む。図 4 A は、電源 1 0 0 が不連続導通モード (DCM) で動作している間に亘るスイッチ電流  $I_D$  1 4 4 の一般的な波形の一例を実証する。一般的に、スイッチングサイクル  $T_{-2}$  4 0 6 から  $T_8$  4 2 6 の各々はスイッチング周期  $T_s$  3 0 4 を有する。本発明のいくつかの実施例では、スイッチング周期  $T_s$  3 0 4 は一定の時間の長さであり得る。本発明の他の実施例では、コントローラ 1 3 8 はスイッチング周期  $T_s$  3 0 4 の長さを変えてもよい。本発明のさらなる実施例では、スイッチング周期  $T_s$  3 0 4 (およびしたがってスイッチング周波数  $f_s$ )、ここで

20

#### 【0033】

#### 【数 1】

$$f_s = \frac{1}{T_s}$$

30

#### 【0034】

) および意図されるスイッチオン時間  $t_{ON}$  3 0 6 はすべて 1 つのハーフラインサイクル 2 0 2 の間一定に維持される。

#### 【0035】

本発明の実施例については、コントローラ 1 3 8 は、スイッチ S 1 1 1 4 のオン時間延長を利用して、a c 入力電圧  $V_{AC}$  1 0 2 がいつゼロ電圧と交差したかを判定する。図 4 A は、いくつかのスイッチングサイクル  $T_{-2}$  4 0 6 から  $T_8$  4 2 6 に亘るスイッチ電流  $I_D$  1 4 4 の例を図示する。電流リミットしきい値  $I_{LIM}$  4 0 2 は、スイッチ S 1 1 1 4 について許される最大電流を定める。スイッチ電流  $I_D$  1 4 4 が電流リミットしきい値  $I_{LIM}$  4 0 2 に達すれば、スイッチ S 1 1 1 4 はスイッチングサイクルの残余の間オフする。スイッチ電流  $I_D$  1 4 4 がある時間量までにゼロ交差電流しきい値  $I_{ZC}$  4 0 4 に達しない場合、図 5 に関してさらに論じられるように、可能なゼロ交差条件が存在し得る。

40

#### 【0036】

N は、コントローラ 1 3 8 がゼロ交差条件が確かに存在すると判定する前に可能なゼロ交差条件として検出する連続したスイッチングサイクルの数であり、ゼロ交差信号 4 3 2 は、非ゼロ交差条件を示す状態からゼロ交差条件を示す状態に変化することが認められるべきである。さらに、ゼロ交差信号 4 3 2 がゼロ交差条件が存在すると示している場合、コントローラは N 個の連続スイッチングサイクル待機して、コントローラ 1 3 8 がゼロ交差信号 4 3 2 の状態を変化させる前にゼロ交差条件が存在しないと決定できるようにして

50

非ゼロ交差条件を示す。コントローラ 138 は N 個の連続したスイッチングサイクル待機して、ゼロ交差条件の誤った検出に繋がり得る如何なるノイズリングもなくし得る。たとえば、N が（図 4B に示されるように）4 に等しい場合、コントローラ 138 は、可能なゼロ交差条件が 4 個の連続したスイッチングサイクルの間起こると、ゼロ交差条件が存在すると判定する。別の例では、N が（図 4A に示されるように）1 に等しい場合、コントローラ 138 は、可能なゼロ交差条件の最初の事象でゼロ交差条件が存在すると判定する。N の値は、部分的に電源 100 の入力での予測されるノイズ量により、選択され得る。N の値が小さいほど、コントローラ 138 はゼロ交差条件が存在するか存在しないかをより迅速に判定するが、ゼロ交差条件の判定は電源 100 の入力におけるノイズの影響をより受けやすくなり得る。このように、ゼロ交差信号 432 はゼロ交差条件を誤って示したり、または a c 入力電圧  $V_{AC} 102$  の非ゼロ交差条件を誤って示したりし得る。しかしながら、N の値は、ゼロ交差条件が存在するとコントローラ 138 が検出できないほど大きくなつてはならない。なぜなら、整流された電圧  $V_{RECT} 106$  はゼロ交差電圧しきい値  $V_{ZC} 204$  よりも下に降下し、次に N の値に達する前にゼロ交差電圧しきい値  $V_{ZC} 204$  よりも上に上昇しているからである。10

#### 【0037】

一実施例では、ゼロ交差信号 432 の論理ローの値はゼロ交差条件が存在しないことを示す一方で、ゼロ交差信号 432 の論理ハイの値はゼロ交差条件が存在することを示す。別の実施例では、ゼロ交差信号 432 の論理ハイの値はゼロ交差条件が存在しないことを示す一方で、ゼロ交差信号 432 の論理ローの値はゼロ交差信号が存在することを示す。20

#### 【0038】

図 4A に示される例について、N は 1 に等しく、コントローラ 138 は、可能なゼロ交差条件の最初の事象でゼロ交差条件が存在すると判定し、同じスイッチングサイクルの間にゼロ交差信号 432 の状態を変化させる。図 4A の例では、ゼロ交差信号 432 は、スイッチ S1\_114 がオフし、スイッチ電流  $I_D 144$  がゼロ電流に降下すると、ゼロ交差条件を示す状態に変化する。スイッチングサイクル  $T_2 406$ 、 $T_1 408$ 、および  $T_0 410$  で、スイッチ電流  $I_D 144$  はゼロ交差電流しきい値  $I_{ZC} 404$  を超え、その結果コントローラ 138 は非ゼロ交差条件を検出する。図 4A の例については、ゼロ交差条件が存在しない場合、ゼロ交差信号 432 は論理ローの値である。しかしながら、スイッチングサイクル  $T_1 412$  で、スイッチ電流  $I_D 144$  は、ある時間量内でゼロ交差電流しきい値  $I_{ZC} 404$  に達しない。N は図 4A の例では 1 に等しいので、コントローラ 138 は a c 入力電圧  $V_{AC} 102$  についてゼロ交差条件が存在すると判定する。その結果、ゼロ交差信号 432 は、スイッチングサイクル  $T_1 412$  の間にゼロ交差条件を示す状態に変化する。30

#### 【0039】

スイッチングサイクル  $T_2 414$  から  $T_6 422$  の間、スイッチ電流  $I_D 144$  は依然としてゼロ交差電流しきい値  $I_{ZC} 404$  に達せず、コントローラ 138 は a c 入力電圧  $V_{AC} 102$  のゼロ交差条件が存在し続けていると判定する。その結果、ゼロ交差信号 432 は論理ハイの値に留まる。スイッチングサイクル  $T_7 424$  で、スイッチ電流  $I_D 144$  はゼロ交差電流しきい値  $I_{ZC} 404$  を超え、コントローラ 138 はゼロ交差条件が存在しないと判定する。N は 1 に等しいので、ゼロ交差信号 432 はスイッチングサイクル  $T_7 424$  の間に論理ローの値に変化する。図 4A の例については、ゼロ交差信号 432 は、スイッチ S1\_114 がスイッチングサイクル  $T_7 424$  の間オフし、スイッチ電流  $I_D 144$  がゼロ電流に降下すると、非ゼロ交差条件を示す状態に変化する。図 4A に示されるように、ゼロ交差パルス幅  $T_z 434$  は、ゼロ交差信号 432 がゼロ交差条件を示す時間の長さである。40

#### 【0040】

次に図 4B を参照して、例示的なスイッチ電流波形および結果的に生じるゼロ交差信号 432 の別の図を図示する。これは、スイッチ電流  $I_D 144$ 、電流リミットしきい値  $I_L_{IM} 402$ 、ゼロ交差電流しきい値  $I_{ZC} 404$ 、スイッチングサイクル  $T_0 410$  から  $T_{10}$ 50

430、ゼロ交差パルス幅  $T_z 434$ 、および遅延時間  $t_x 436$  を含む。図 4B は、電源 100 が DCM で動作している間に亘るスイッチ電流  $I_D 144$  の一般的な波形の一例を実証する。図 4B は図 4A に示されるのと同じスイッチ電流  $I_D 144$  も図示するが、図 4B については N が 4 に等しく、また図 4B は、(図 4A に示されるようなスイッチングサイクル  $T_2$  から  $T_8$  よりもむしろ) スイッチングサイクル  $T_0$  から  $T_{10}$  を示す。コントローラ 138 は、ゼロ交差条件が確かに存在すると判定し、ゼロ交差信号 432 がゼロ交差条件を示す状態に変化する前に、可能なゼロ交差条件の後の 4 個の連続したスイッチングサイクル待機する。さらに、ゼロ交差信号 432 がゼロ交差条件が存在すると示す場合、コントローラ 138 は、コントローラ 138 がゼロ交差信号 432 の状態を変化させて非ゼロ交差条件を示す前に、非ゼロ交差条件を有する 4 個の連続したスイッチングサイクル待機する。コントローラ 138 は、4 個の連続したスイッチングサイクルの間待機して、いずれのノイズリングもなくし、かつゼロ交差条件が確かに存在することを確実にする。図 4B は N が 4 に等しいと図示するが、N はいずれの正の整数であってもよい。しかしながら、N の値は、ゼロ交差条件が存在するとコントローラ 138 が検出できないほど大きくなつてはならない。なぜなら、スイッチ電流  $I_D 144$  はゼロ交差電流しきい値  $I_{zc} 404$  よりも下に降下し、次に N の値に達する前にゼロ交差電流しきい値  $I_{zc} 404$  よりも上に上昇しているからである。

#### 【0041】

スイッチングサイクル  $T_0 410$  で、スイッチ電流  $I_D 144$  はゼロ交差電流しきい値  $I_{zc} 404$  を超え、その結果、コントローラ 138 はゼロ交差条件が存在すると判定せず、ゼロ交差信号 432 は論理ローの値に留まる。スイッチングサイクル  $T_1 412$  の間、スイッチ電流  $I_D 144$  はある時間量内でゼロ交差電流しきい値  $I_{zc} 404$  に達せず、コントローラ 138 は可能なゼロ交差条件が存在すると判定するが、ゼロ交差信号 432 は依然として論理ローの値に留まる。なぜなら、コントローラ 138 はゼロ交差条件が存在すると判定する前に可能なゼロ交差条件の 4 個の連続したスイッチングサイクル待機するからである。図 4B の例から、スイッチ電流  $I_D 144$  も、スイッチングサイクル  $T_2 414$  から  $T_4 418$  のある時間量内でゼロ交差電流しきい値  $I_{zc} 404$  に達しない。スイッチングサイクル  $T_4 418$  は、可能なゼロ交差条件が存在する 4 番目の連続したスイッチングサイクルである。したがって、コントローラ 138 は、ゼロ交差条件が a c 入力電圧  $V_{AC} 102$  について確かに存在すると判定し、ゼロ交差信号 432 は、ゼロ交差条件が存在すると示す状態に変化する。図 4B に示される例については、ゼロ交差信号 432 は、論理ローの値から論理ハイの値に遷移する。しかしながら、ゼロ交差信号 432 は遅延時間  $t_x 436$  の終わりまで論理ハイの値に遷移しない。遅延時間  $t_x 436$  は、コントローラ 138 がゼロ交差条件が確かに存在すると判定するのと、コントローラ 138 がゼロ交差信号 432 を更新するとの間の時間の長さを示す。一実施例では、ゼロ交差信号が更新する遅延時間  $t_x 436$  は、数 N を実現するのに用いられるフィルタによるものであり得る。さらなる実施例では、遅延時間  $t_x 436$  は次のスイッチングサイクルまでゼロ交差信号 432 の更新を遅延させ得る。図 4A に戻ると、遅延時間  $t_x 436$  は実質的に 0 に等しい。本発明の実施例については、ゼロの遅延時間  $t_x 436$  が好みしいであろう。しかしながら、ゼロの遅延時間  $t_x 436$  を含むコントローラ 138 の実施例は、付加的な回路構成(図示せず)を要件とし得る。このように、コントローラ 138 のいくつかの実施例は、コストおよび/または回路の複雑さを低減するため、非ゼロ遅延時間  $t_x 436$  を含み得る。

#### 【0042】

スイッチングサイクル  $T_5 420$  および  $T_6 422$  の間、スイッチ電流  $I_D 144$  は依然としてゼロ交差電流しきい値  $I_{zc} 404$  に達しておらず、コントローラは a c 入力電圧  $V_{AC} 102$  のゼロ交差条件が存在し続けていると判定し、ゼロ交差信号 432 は論理ハイの値に留まる。スイッチングサイクル  $T_7 424$  で、スイッチ電流  $I_D 144$  は a c 入力電圧  $V_{AC} 102$  のゼロ交差条件がもはや存在していない可能性があることを示すある期間内にゼロ交差電流しきい値  $I_{zc} 404$  を超えるが、コントローラ 138 は、a c 入力電圧  $V_{AC}$

10

20

30

40

50

102がもはやゼロ交差条件がないと判定する前に、スイッチ電流  $I_D$  144がゼロ交差条件がもはや存在しない可能性があることを示す4個の連続したスイッチングサイクル待機する。スイッチングサイクル  $T_8$  426から  $T_{10}$  430の間、スイッチ電流  $I_D$  はある期間内にゼロ交差電流しきい値  $I_{zc}$  404を超える。スイッチングサイクル  $T_{10}$  430は、ゼロ交差条件がもはや存在しない可能性がある4番目の連続したスイッチングサイクルであり、コントローラ138はゼロ交差条件が存在しないと判定する。その結果、ゼロ交差信号432は、ゼロ交差条件が存在しないと示す状態に変化する。しかしながら、ゼロ交差信号432は、遅延時間  $t_x$  436の終わりまで論理ローの値に遷移しない。遅延時間  $t_x$  436は、コントローラ138がゼロ交差条件が存在しないことを判定するのと、コントローラ138がゼロ交差信号432を更新するとの間の時間の長さを示す。さらなる実施例では、遅延時間  $t_x$  436は、次のスイッチングサイクルまでゼロ交差信号432の更新を遅延させ得る。図4Bに示されるように、ゼロ交差パルス幅  $T_z$  434は、ゼロ交差信号432がゼロ交差条件が存在することを示す時間の長さである。

#### 【0043】

次に図5を参照して、例示的なスイッチ電流波形および結果として生じるゼロ交差信号532の別の図を図示する。これは、スイッチ電流  $I_D$  144、ゼロ交差電流しきい値  $I_z$  504、ゼロ交差時間しきい値  $t_{zc}$  506、スイッチングサイクル  $T_M$  508から  $T_{M+3}$  514、およびゼロ交差パルス幅  $T_z$  534を含む。さらに、各々のスイッチングサイクル  $T_M$  508から  $T_{M+3}$  514の間に、スイッチS1 114のオン時間  $t_{ON}$  および延長されたオン時間  $t_{ONX}$  が存在する。一般的に、スイッチングサイクル  $T_M$  508から  $T_{M+3}$  514の各々はスイッチング周期  $T_s$  304を有する。本発明のいくつかの実施例では、スイッチング周期  $T_s$  304は一定の時間の長さであり得る。本発明の他の実施例では、コントローラ138はスイッチング周期  $T_s$  304の長さを変え得る。図5に示される例示的なゼロ交差信号532については、Nの値は2であり、遅延時間  $t_x$  は実質的に0に等しい。

#### 【0044】

本発明の一実施例では、コントローラ138は、スイッチS1 114のオン時間延長を利用して、ac入力電圧  $V_{AC}$  102についてゼロ交差条件が存在するかどうかを判定する。さらに論じられるように、コントローラ138は無損失集積ブリーダ回路としてスイッチS1 114のオン時間延長も利用する。コントローラ138は、スイッチ電流  $I_D$  144がゼロ交差時間しきい値  $t_{zc}$  506内にゼロ交差電流しきい値  $I_{zc}$  504に達しない場合にゼロ交差条件が存在すると判定する。スイッチ電流  $I_D$  144がスイッチS1 114の初期オン時間  $t_{ON}$  の間にゼロ交差電流しきい値  $I_{zc}$  504に達しない場合、コントローラ138はゼロ交差電流しきい値  $I_{zc}$  504に達するまでまたは延長されたオン時間  $t_{ONX}$  がゼロ交差時間しきい値  $t_{zc}$  506に達するまで、オン時間  $t_{ON}$  を延長する。オン時間  $t_{ON}$  が延長される時間量は、延長されたオン時間  $t_{ONX}$  と称される。いくつかの実施例については、ゼロ交差時間しきい値  $t_{zc}$  506は実質的に5μsに等しい。ゼロ交差時間しきい値  $t_{zc}$  506の値を選択する際、ゼロ交差時間しきい値  $t_{zc}$  506は最小の意図されるオン時間  $t_{ON}$  よりも長くあるべきであるが、スイッチング周期  $T_s$  304よりも大幅に長くなってはならない。一般的に、コントローラ138は、ゼロ交差時間しきい値  $t_{zc}$  506の値がより大きくなると、スイッチ電流  $I_D$  144をより正確に検知し得る。

#### 【0045】

スイッチングサイクル  $T_M$  508で、スイッチ電流  $I_D$  144は、スイッチS1 114の初期オン時間  $t_{ON}$  内にゼロ交差電流しきい値  $I_{zc}$  504に達しない。スイッチS1 114をオフする代わりに、スイッチS1 114はオンのままであり、スイッチのオン時間  $t_{ON}$  は、スイッチ電流  $I_D$  144がゼロ交差電流しきい値  $I_{zc}$  504に達するまたは全オン時間（たとえばオン時間  $t_{ON}$  と延長されたオン時間  $t_{ONX}$  との和）がゼロ交差時間しきい値  $t_{zc}$  506に達するまで、延長される。スイッチングサイクル  $T_M$  508の間、オン時間  $t_{ON}$  は延長されたオン時間  $t_{ONX}$  だけ延長されるが、スイッチ電流  $I_D$  144は、オン時間  $t_{ON}$  と延長されたオン時間  $t_{ONX}$  との和がゼロ交差時間しきい値  $t_{zc}$  506に達す

10

20

30

40

50

る前にゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達する。その結果、スイッチ S1 114 は、スイッチ電流  $I_D\ 1\ 4\ 4$  がゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達しスイッチ電流  $I_D\ 1\ 4\ 4$  が実質的に 0 に降下するときにオフされる。コントローラ 138 はゼロ交差条件を検出せず、その結果、ゼロ交差信号 532 は非ゼロ交差条件を示す。

#### 【 0 0 4 6 】

スイッチングサイクル  $T_{M+1}\ 5\ 1\ 0$  で、スイッチ電流  $I_D\ 1\ 4\ 4$  は初期オン時間  $t_{ON}$  内にゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達せず、コントローラ 138 は延長されたオン時間  $t_{ONX}$  だけオン時間  $t_{ON}$  を延長する。図示されるように、スイッチ電流  $I_D\ 1\ 4\ 4$  は延長されたオン時間  $t_{ONX}$  の間にゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達する。スイッチングサイクル  $T_M\ 5\ 0\ 8$  とは異なり、スイッチ電流  $I_D\ 1\ 4\ 4$  は、オン時間  $t_{ON}$  と延長されたオン時間  $t_{ONX}$  との和がゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  に実質的に等しくなったときにゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達する。コントローラ 138 はゼロ交差条件を検出せず、ゼロ交差信号 532 は論理ローの値に留まる。

10

#### 【 0 0 4 7 】

スイッチングサイクル  $T_{M+2}\ 5\ 1\ 2$  で、スイッチ電流  $I_D\ 1\ 4\ 4$  は初期オン時間  $t_{ON}$  内にゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達せず、コントローラ 138 は延長されたオン時間  $t_{ONX}$  だけオン時間  $t_{ON}$  を延長する。以上で言及されたように、コントローラ 138 は、延長されたオン時間  $t_{ONX}$  がゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  に達しかつスイッチ電流  $I_D\ 1\ 4\ 4$  がゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  未満であるときに、スイッチ S1 114 をオフする。図 5 に示される例では、スイッチ電流  $I_D\ 1\ 4\ 4$  は初期オン時間  $t_{ON}$  内にゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達せず、コントローラ 138 はスイッチ S1 114 のオン時間を延長する。オン時間  $t_{ON}$  は、スイッチ電流  $I_D\ 1\ 4\ 4$  がゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達するまでまたは延長されたオン時間  $t_{ONX}$  がゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  に達するまで延長される。スイッチングサイクル  $T_{M+2}\ 5\ 1\ 2$  の間に、延長されたオン時間  $t_{ONX}$  は、スイッチ電流  $I_D\ 1\ 4\ 4$  がゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達しないうちにゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  に達する。その結果、コントローラ 138 は可能なゼロ交差条件が存在し得ると判定する。しかしながら、ゼロ交差信号 532 は状態を変化させない。なぜなら、コントローラ 138 は、ゼロ交差条件が存在すると判定する前に可能なゼロ交差条件の 2 つの連続するスイッチングサイクル待機するからである。

20

#### 【 0 0 4 8 】

スイッチングサイクル  $T_{M+3}\ 5\ 1\ 4$  で、スイッチ電流  $I_D\ 1\ 4\ 4$  は初期オン時間  $t_{ON}$  内にゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達せず、コントローラ 138 は延長されたオン時間  $t_{ONX}$  だけオン時間  $t_{ON}$  を延長する。スイッチングサイクル  $T_{M+2}\ 5\ 1\ 2$  と同様に、スイッチ電流  $I_D\ 1\ 4\ 4$  は、延長されたオン時間  $t_{ONX}$  がゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  に達する前にゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達しない。このように、スイッチングサイクル  $T_{M+3}\ 5\ 1\ 4$  は、可能なゼロ交差条件を有する 2 番目の連続したスイッチングサイクルである。その結果、コントローラ 138 はゼロ交差条件が存在すると判定し、ゼロ交差信号 532 は状態を変化させる。

30

#### 【 0 0 4 9 】

ゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  およびゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  は、ゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  に対応するように選択される。以上で言及されたように、コントローラ 138 は、スイッチ電流  $I_D\ 1\ 4\ 4$  がゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  までにゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  に達しないときにゼロ交差条件を検出する。ゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  およびゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  は、ゼロ交差条件が、ゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  を下回る、整流された電圧  $V_{RECT\ 1\ 0\ 6}$  の値に対応するように固定される。換言すると、ゼロ交差電流しきい値  $I_{ZC\ 5\ 0\ 4}$  およびゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  は、ゼロ交差条件が正のゼロ交差電圧しきい値  $V_{ZC\ 2\ 0\ 4}$  およびゼロ交差時間しきい値  $t_{ZC\ 5\ 0\ 6}$  との間に降下する a c 入力電圧  $V_{AC\ 1\ 0\ 2}$  の値、または数学的には  $-V_{ZC} < V_{AC}(t) < V_{ZC}$ 、に対応するように固定される。

40

#### 【 0 0 5 0 】

スイッチ S 1 114 がオンであるときのスイッチ S 1 114 の電圧と電流との間の関係は

【 0 0 5 1 】

【 数 2 】

$$V(t) = L_p \frac{di(t)}{dt}$$

【 0 0 5 2 】

として表現され得る。式中、  $L_p$  が 1 次巻線 110 のインダクタンスである。DCM で動作する電源 100 については、いずれのスイッチングサイクルの間のこの関係も

10

【 0 0 5 3 】

【 数 3 】

$$V_{AC} = L_p \frac{I_{PEAK}}{t_{ON}}$$

【 0 0 5 4 】

としてさらに表わされ得る。式中、  $I_{PEAK}$  はスイッチ電流  $I_D$  144 のピーク値である。しかしながら、1つのスイッチングサイクルにおいては、  $V_{AC}$  の値は、オン時間  $t_{ON}$  が入力電圧  $V_{AC}$  102 の周期に対して小さいために一定であると考えられ得る。以上で言及されたように、ゼロ交差電流しきい値  $I_{ZC}$  504 およびゼロ交差時間しきい値  $t_{ZC}$  506 は固定され、スイッチ S 1 114 が DCM でオンであるときのスイッチ S 1 114 の電圧と電流との間の関係、または数学的には

20

【 0 0 5 5 】

【 数 4 】

$$V_{ZC} = L_p \frac{I_{ZC}}{t_{ZC}}$$

【 0 0 5 6 】

を利用して、ゼロ交差電圧しきい値  $V_{ZC}$  204 に対応するように選択され得る。

スイッチ S 1 114 がオンである時間が長いほど、フィルタコンデンサ C\_F 120 からより多くの電荷が除去される。このように、ゼロ交差時間しきい値  $t_{ZC}$  506 を定めるようにコントローラ 138 が利用するオン時間延長により、オン時間延長なしのコントローラよりも、フィルタコンデンサ C\_F 120 からより多くの電荷が除去され得る。その結果、フィルタコンデンサ C\_F 120 の放電は、力率改善 (PFC) によりコントローラ 138 を助け得る 1 次巻線 110 における電圧をプルダウンし、かつ ac 入力電圧  $V_{AC}$  102 のゼロ交差を検出するのを助ける。以上言及されたように、従来のスイッチング電源においては、ブリーダ回路は、電源 100 のフィルタコンデンサ C\_F 120 の放電を容易にし、かつエネルギー転送要素 T 1 108 の 1 次巻線 110 の電圧をプルダウンするのを助けるように設けられる。しかしながら、従来のブリーダ回路は典型的に集積回路コントローラの外部のものである。コントローラ 138 の集積回路 146 の外部の回路構成はスイッチモード電源に不要なコストを追加し得る。さらに、典型的なブリーダ回路（すなわち抵抗器）は熱の形態でエネルギーを損失し、スイッチモード電源の効率を低下させてしまう。コントローラ 138 が利用するオン時間延長は電源 100 にコントローラ 138 と共に集積されるブリーダ回路を設ける。このように、オン時間延長ブロック 904 は本明細書中で、コントローラ 138 内部の（すなわちその中に集積される）ブリーダ回路と称され得る。さらに、オン時間延長により多くの電流が 1 次巻線を流れることが可能になるので、伝統的なブリーダによって損失されたであろうエネルギーは電源 100 の出力に転送される。このように、コントローラ 138 が利用するオン時間延長は無損失ブリーダ回路として働く。さらに、スイッチング周期  $T_S$  304（およびしたがってスイッチング周波数  $f_S$ 、なお

30

40

50

【0057】

【数5】

$$f_s = \frac{1}{T_s}$$

【0058】

) および意図されるスイッチオン時間  $t_{ON}$  が 1 つのハーフラインサイクル 202 の間一定であると、コントローラ 138 によるオン時間延長は適合的な放出 (bleeding) も可能にする。なぜなら、延長されたオン時間  $t_{ONX}$  の値は変化し得るからである。以上言及されたように、DCM で動作する電源 100 については、スイッチ S1 114 の電圧と電流との間の関係は 10

【0059】

【数6】

$$V_{AC} = L_p \frac{I_{PEAK}}{t_{ON}}$$

【0060】

と表わせ得る。意図されるスイッチオン時間  $t_{ON}$  が全ハーフラインサイクル 202 の間一定であれば、スイッチ電流のピーク値  $I_{PEAK}$  は ac 入力電圧  $V_{AC}$  102 の値に依存する。このように、ac 入力電圧  $V_{AC}$  の値が高いほど、スイッチ電流のピーク値  $I_{PEAK}$  がゼロ交差電流しきい値  $I_{ZC}$  504 を上回る見込みがより高くなる。さらに、ac 入力電圧  $V_{AC}$  102 の値がより高いほど、スイッチ電流  $I_D$  144 がより迅速にゼロ交差電流しきい値  $I_Z$  504 に到達する。このように、コントローラ 138 は、オン時間延長によって与えられる放出の量が ac 入力電圧  $V_{AC}$  102 の値に適合するように ac 入力電圧  $V_{AC}$  102 の値に応答して延長されたオン時間  $t_{ONX}$  の量を変化させることによって適合的な放出を提供し得る。 20

【0061】

次に図 6 を参照して、調光器回路 608 を利用する例示的なスイッチング電源の機能ブロック図を示す。これは、ac 入力電圧  $V_{AC}$  102、エネルギー転送要素 T1 108、エネルギー転送要素 T1 108 の 1 次巻線 110、エネルギー転送要素 T1 108 の 2 次巻線 112、スイッチ S1 114、入力帰還 116、クランプ回路 118、フィルタコンデンサ C<sub>F</sub> 120、コントローラ 138、駆動信号 140、電流検知入力信号 142、およびスイッチ電流  $I_D$  144 を含む。さらに、スイッチング電源は、整流器 604、整流された電圧  $V_{RECT}$  606、調光器回路 608、調光器出力電圧  $V_{DO}$  610、および入力電流  $I_{IN}$  612 をさらに含む。図 6 に示されるスイッチング電源は、図 1 に示されるスイッチング電源 100 に調光器回路 608 が追加されたものと同様であることが認められるべきである。 30

【0062】

エネルギー転送要素 T1 108、エネルギー転送要素 T1 108 の 1 次巻線 110、エネルギー転送要素 T1 108 の 2 次巻線 112、スイッチ S1 114、入力帰還 116、クランプ回路 118、フィルタコンデンサ C<sub>F</sub> 120、コントローラ 138、駆動信号 140、電流検知入力信号 142、およびスイッチ電流  $I_D$  144 は上述のように結合しかつ機能する。調光器回路 608 は ac 入力電圧  $V_{AC}$  102 に結合し、調光器出力電圧  $V_{DO}$  610 を生成する。調光器回路 608 は整流器 604 にさらに結合する。整流器 604 は調光器出力電圧  $V_{DO}$  610 を受け、整流された電圧  $V_{RECT}$  606 を出力する。図 6 に示されるように、整流器 604 はフィルタコンデンサ C<sub>F</sub> 120 の両端に結合される。本発明のいくつかの実施例については、整流器 604 は図 1 に図示されるようなブリッジ整流器である。 40

【0063】

調光器回路 608 は、電源に結合された負荷 126 が発光ダイオード (LED) アレイ 50

である場合に利用され、電源に送達される電力の量を制限し得る。その結果、L E D アレイである負荷に送達される電流が制限され、L E D アレイが薄暗くなる。一実施例では、調光器回路 6 0 8 は位相調光器回路である。別の実施例では、トライアック調光器回路が調光器回路 6 0 8 として利用され得る。トライアック調光器は、a c 入力電圧  $V_{AC} 1 0 2$  がゼロ電圧と交差する際に、電源から a c 入力電圧  $V_{AC} 1 0 2$  を切り離す。所与の時間量の後、トライアック調光器は、電源に a c 入力電圧  $V_{AC} 1 0 2$  を再接続する。求められる調光量に依存して、トライアック調光器は、a c 入力電圧  $V_{AC} 1 0 2$  が電源から切り離される時間量を制御する。一般的に、より多くの調光は、トライアック調光器が a c 入力電圧  $V_{AC} 1 0 2$  を切り離すより長い期間に対応する。トライアック調光器回路を利用する L E D の位相調光適用例について、トライアックは、最小保持電流がトライアック自体をオフしないようにすることを要件とする。本発明の実施例に従うと、コントローラ 1 3 8 は、トライアックを通る電流(すなわち  $I_{IN} 6 1 2$ )がトライアックの保持電流を下回らないことを確実にするのを助ける無損失集積ブリーダ回路としてスイッチ S 1 1 1 4 のオン時間延長を利用する。図 7 A および図 7 B は、整流された電圧  $V_{RECT} 6 0 6$  およびその後のゼロ交差信号の例を図示する。

## 【 0 0 6 4 】

図 7 A は、図 6 に示される整流された電圧  $V_{RECT} 6 0 6$  の例示的な波形を図示し、これは、ハーフラインサイクル 7 0 2、ゼロ交差電圧しきい値 7 0 4、ピーク電圧  $V_p 7 0 5$ 、および部分 7 0 6 を含む。図 7 B は、整流された電圧  $V_{RECT} 6 0 6$  の部分 7 0 6 および対応のゼロ交差信号 7 0 8 を図示する。ハーフラインサイクル 7 0 2、ゼロ交差電圧しきい値  $V_{zc} 7 0 4$ 、およびゼロ交差信号 7 0 8 は、図 2 A および図 2 B のハーフラインサイクル 2 0 2、ゼロ交差電圧しきい値  $V_{zc} 2 0 4$ 、およびゼロ交差信号 2 0 8 のさらなる例である。

## 【 0 0 6 5 】

以上論じたように、a c 入力電圧  $V_{AC} 1 0 2$  は、フルラインサイクルと称される a c 入力電圧  $V_{AC} 1 0 2$  の周期の正弦波形である。数学的には  $V_{AC}(t) = V_p \sin(2\pi f_L t)$  である。式中、 $V_p 7 0 5$  は a c 入力電圧  $V_{AC} 1 0 2$  のピーク電圧であり、 $f_L$  はライン入力電圧の周波数である。整流された電圧  $V_{RECT} 6 0 6$  は、ブリッジ整流器 6 0 4 および調光回路 6 0 8 の結果的な出力である。図 7 A の例については、整流された電圧  $V_{RECT} 6 0 6$  の各々のハーフラインサイクル 7 0 2 の開始時の電圧レベルは、調光器回路 6 0 8 が a c 入力電圧  $V_{AC} 1 0 2$  を電源から切り離すときに対応するゼロに実質的に等しい。調光器回路 6 0 8 が a c 入力電圧  $V_{AC} 1 0 2$  を電源に再接続する際、整流された電圧  $V_{RECT} 6 0 6$  は a c 入力電圧  $V_{AC} 1 0 2$  の正の大きさに実質的に従う。または、数学的には  $V_{RECT} = |V_{DO}|$  である。

## 【 0 0 6 6 】

図 2 A と同様に、いくつかの実施例については、ゼロ交差電圧しきい値  $V_{zc} 7 0 4$  は実質的に 0 に等しい。他の実施例については、ゼロ交差電圧しきい値  $V_{zc} 7 0 4$  は、整流された電圧  $V_{RECT} 6 0 6$  のピーク電圧  $V_p 7 0 5$  の実質的に 5 分の 1 である。一例では、整流された電圧  $V_{RECT} 6 0 6$  のピーク電圧  $V_p 7 0 5$  が 125 V に実質的に等しい場合、ゼロ交差電圧しきい値  $V_{zc} 7 0 4$  は実質的に 25 V に等しい。別の実施例では、ゼロ交差電圧しきい値  $V_{zc} 7 0 4$  は、整流された電圧  $V_{RECT} 6 0 6$  のピーク電圧  $V_p 7 0 5$  の実質的に 4 分の 1 である。ゼロ交差電圧しきい値  $V_{zc} 7 0 4$  の値がゼロ電圧に近づくにつれ、ゼロ交差信号 7 0 8 がより正確になることが認められるべきである。しかしながら、図 2 A に関して以上論じたように、ゼロ交差電圧しきい値  $V_{zc} 7 0 4$  について非ゼロの値が選択されてもよい。

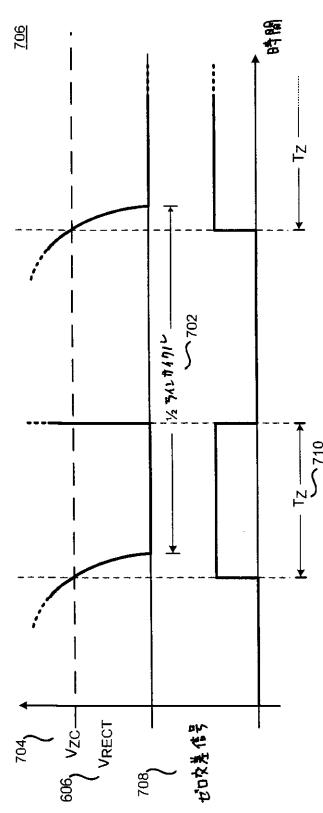

## 【 0 0 6 7 】

図 7 B は、整流された電圧  $V_{RECT} 6 0 6$  の部分 7 0 6 および対応のゼロ交差信号 7 0 8 を図示する。本発明の実施例は、スイッチ S 1 1 1 4 のオン時間延長を利用して、ゼロ交差信号 7 0 8 を生成する。整流された電圧  $V_{RECT} 6 0 6$  がゼロ交差電圧しきい値  $V_{zc} 7 0 4$  未満である場合、ゼロ交差信号 7 0 8 はゼロ交差条件が存在すると示す。ゼロ交差信

号 7 0 8 は、論理ハイおよび論理ローのセクションを有する矩形パルス波形である。図 7 B に図示される例については、整流された電圧  $V_{RECT} 6 0 6$  がゼロ交差電圧しきい値  $V_{ZC} 7 0 4$  未満である場合、ゼロ交差信号 7 0 8 の値は論理ハイである。整流された電圧  $V_{RECT} 6 0 6$  がゼロ交差電圧しきい値  $V_{ZC} 7 0 4$  よりも大きい場合、ゼロ交差信号 7 0 8 の値は論理ローである。本発明の実施例については、コントローラ 1 3 8 はスイッチ S 1 1 1 4 のオン時間延長を利用して、a c 入力電圧  $V_{AC} 1 0 2$  のゼロ交差を判定する。

#### 【 0 0 6 8 】

図 2 B について以上で言及されたように、整流された電圧  $V_{RECT} 6 0 6$  がいつゼロ電圧に近いかを検出することは、a c 入力電圧  $V_{AC} 1 0 2$  がいつゼロ電圧と交差するかを検出することに対応する。図 7 B に示されるゼロ交差信号 7 0 8 と図 2 B に示されるゼロ交差信号 2 0 8 とを比較すると、図 7 B のゼロ交差パルス  $T_z 7 1 0$  は、調光器回路 6 0 8 による a c 入力電圧  $V_{AC} 1 0 2$  の切り離しのために、図 2 B のゼロ交差パルス  $T_z 2 1 0$  よりも長くなっている。以上で言及されたように、調光量は、調光器回路 6 0 8 が電源から a c 入力電圧  $V_{AC} 1 0 2$  を切り離す時間の長さに対応する。調光器回路 6 0 8 が a c 入力電圧  $V_{AC} 1 0 2$  を電源から切り離した状態に保つ時間が長いほど、整流された電圧  $V_{RECT} 6 0 6$  が実質的にゼロ電圧に等しい時間が長くなる。その結果、ゼロ交差パルス  $T_z 7 1 0$  の長さは、調光器回路 6 0 8 が与える調光量に対応する。

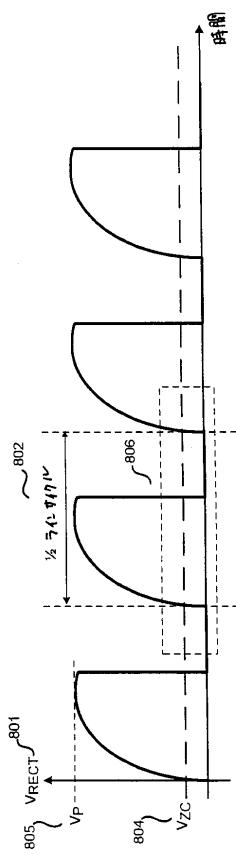

#### 【 0 0 6 9 】

次に図 8 A を参照して、整流された電圧  $V_{RECT} 8 0 1$  の別の例示的な波形を図示する。これは、ハーフラインサイクル 8 0 2、ゼロ交差電圧しきい値  $V_{ZC} 8 0 4$ 、ピーク電圧  $V_P 8 0 5$ 、および部分 8 0 6 を含む。図 8 B は、整流された電圧  $V_{RECT} 8 0 1$  の部分 8 0 6 および対応のゼロ交差信号 8 0 8 を図示する。

#### 【 0 0 7 0 】

整流された電圧  $V_{RECT} 8 0 1$  の例示的な波形は、図 7 A に示される整流された電圧  $V_{RECT} 6 0 6$  と同様である。図 7 A の例では、整流された電圧  $V_{RECT} 6 0 6$  は、調光器回路 6 0 8 および整流器 6 0 4 を通過した a c 入力電圧  $V_{AC} 1 0 2$  の結果である。図 6、図 7 A および図 7 B に関して言及したように、整流された電圧  $V_{RECT} 6 0 6$  は、すべてのハーフラインサイクル 8 0 2 の開始時に a c 入力電圧  $V_{AC} 1 0 2$  を切り離すトライアック調光器などの調光器回路 6 0 8 の結果である。しかしながら、図 8 A および図 8 B に図示される整流された電圧  $V_{RECT} 8 0 1$  は、すべてのハーフラインサイクル 8 0 2 の終わりに a c 入力電圧  $V_{AC} 1 0 2$  を切り離す調光器回路 6 0 8 の結果である。その結果、整流された電圧  $V_{RECT} 8 0 1$  は、ハーフラインサイクル 8 0 2 の終わりにゼロ電圧に実質的に等しくなる。ハーフラインサイクル 8 0 2 の開始時に、整流された電圧  $V_{RECT} 8 0 1$  は、調光器回路 6 0 8 が電源から a c 入力電圧  $V_{AC} 1 0 2$  を切り離すまで、a c 入力電圧  $V_{AC} 1 0 2$  の正の大きさに実質的に従う。整流された電圧  $V_{RECT} 8 0 1$  の値は次に、次のハーフラインサイクルの開始時まで、実質的にゼロ電圧まで放電する。

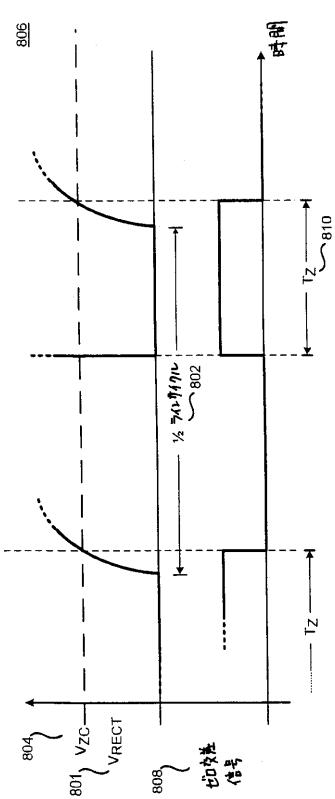

#### 【 0 0 7 1 】

図 8 B は整流された電圧  $V_{RECT} 8 0 1$  の部分 8 0 6 および対応のゼロ交差信号 8 0 8 を図示する。a c 入力電圧  $V_{AC} 1 0 2$  は、スイッチ電流  $I_D 1 4 4$  を通して間接的に検知されてゼロ交差信号 8 0 8 を生成する。整流された電圧  $V_{RECT} 8 0 1$  がゼロ交差電圧しきい値  $V_{ZC} 8 0 4$  未満である場合、ゼロ交差信号 8 0 8 はゼロ交差条件が存在すると示す。本発明の実施例については、コントローラ 1 3 8 はスイッチ S 1 1 1 4 のオン時間延長を利用して、a c 入力電圧  $V_{AC} 1 0 2$  のゼロ交差を判定する。

#### 【 0 0 7 2 】

図 8 B に示されるゼロ交差信号 8 0 8 と図 2 B に示されるゼロ交差信号 2 0 8 とを比較すると、図 8 B のゼロ交差パルス  $T_z 8 1 0$  は、調光器回路 6 0 8 による a c 入力電圧  $V_{AC} 1 0 2$  の切り離しにより、図 2 B のゼロ交差パルス  $T_z 2 1 0$  よりも長くなっている。図 8 B に示されるゼロ交差信号 8 0 8 と図 7 B に示されるゼロ交差信号 7 0 8 とを比較すると、図 8 B のゼロ交差パルス  $T_z 8 1 0$  は、図 7 B に示されるようなハーフラインサイクル 8 0 2 の開始時ではなく、ハーフラインサイクル 8 0 2 の終わりに向けて生じる。

10

20

30

40

50

## 【0073】

次に図9Aを参照して、コントローラ938の機能ブロック図を図示する。これは、フィードバック信号 $U_{FB}930$ 、駆動信号940、電流検知信号942、駆動論理ブロック902、オン時間延長ブロック904、ゼロ交差検出器906、ゼロ交差信号908、およびゼロ交差時間しきい値パルスZCP924を含む。ゼロ交差検出器906は、クロック信号910、比較器914、参照信号916、ANDゲート917、S-Rラッチ918、フリップフロップ922、およびオプションのゼロ交差フィルタ926をさらに含む。コントローラ938、フィードバック信号 $U_{FB}930$ 、駆動信号940、および電流検知信号942は、図1および図6に図示されるコントローラ138、フィードバック信号 $U_{FB}130$ 、駆動信号140、および電流検知信号142の例である。さらに、ゼロ交差信号908は、図2、図4A、図4B、図7B、および図8Bに示されるゼロ交差信号の一例である。一例では、駆動論理ブロック902およびオン時間延長ブロック904は本明細書中では駆動信号生成器と総称され得る。駆動論理出力DLO950、ゼロ交差時間しきい値パルスZCP924、および比較器出力CO952という信号表記も図9Aおよび図9Bに示される。それぞれの信号の波形は図10に図示する。

## 【0074】

コントローラ938、フィードバック信号 $U_{FB}930$ 、駆動信号940、および電流検知信号942は上述のように結合しかつ機能する。コントローラ938内では、駆動論理ブロック902は、オン時間延長ブロック904およびゼロ交差検出器906に結合する。駆動論理ブロック902は電流検知信号942およびフィードバック信号 $U_{FB}930$ を受け、オン時間延長ブロック904へ駆動論理出力DLO950を出力する。駆動論理ブロック902はゼロ交差検出器906にさらに結合し、ゼロ交差信号908を受ける。ゼロ交差検出器906は電流検知信号942に結合しかつこれを受ける。さらに説明されるように、ゼロ交差検出器906は電流検知信号942を受け、駆動論理ブロック902にゼロ交差信号908を出力する。

## 【0075】

駆動論理ブロック902はフィードバック信号 $U_{FB}930$ 、電流検知信号942およびゼロ交差信号908を利用して、駆動信号940の状態およびコントローラ938の状態に関する情報をオン時間延長ブロック904に与える駆動論理出力信号DLO950を生成する。オン時間延長ブロック904はゼロ交差検出器906にさらに結合し、本明細書中では比較器出力CO952（すなわち前提条件信号）と称される比較器914の出力を受ける。さらに、オン時間延長ブロック904はゼロ交差時間しきい値パルスZCP924を受ける。ゼロ交差時間しきい値パルスZCP924は、論理ハイおよび論理ローのセクションを有する矩形パルス波形である。論理ローのセクションの長さはゼロ交差時間しきい値 $t_{ZC}506$ に実質的に等しく、ゼロ交差時間しきい値パルスZCP924の連続した立下がりエッジ同士の間の時間の長さはスイッチング周期 $T_s$ に実質的に等しい。

## 【0076】

オン時間延長ブロック904は、受けた駆動論理出力DLO950、ゼロ交差時間しきい値パルスZCP924および比較器出力CO952を利用して、駆動信号940を出力する。以上で言及されたように、駆動信号940は、電源のスイッチ（たとえば図1のスイッチS1 114）のスイッチングを制御するのに利用される。ゼロ交差検出器906のフリップフロップ922も駆動信号940を受ける。さらに、オン時間延長ブロック904は、図5に関して論じたオン時間延長を実現する。

## 【0077】

駆動論理ブロック902は、電流検知信号942からのスイッチ電流 $I_D144$ に関する情報およびフィードバック信号 $U_{FB}930$ からの出力量 $U_o$ に関する情報を、ゼロ交差信号908とともに受ける。この情報をを利用して、駆動論理ブロック902は、意図される駆動信号に関する情報を与えて、スイッチS1 114のオンおよびオフを制御する。一例では、駆動論理ブロック902は電流検知信号942を利用して、いつスイッチ電流 $I_D144$ が電流リミットしきい値 $I_{LIM}402$ に達して、スイッチS1 114をオフす

るかを判定し得る。オン時間延長ブロック 904 は、比較器出力 CO952 およびゼロ交差時間しきい値パルス ZCP924 とともに、駆動論理出力 DLO950 を受ける。さらに論じられるように、比較器出力 CO952 およびゼロ交差時間しきい値パルス ZCP924 の値に依存して、オン時間延長ブロック 904 は、駆動論理ブロック 902 が与える意図される駆動信号のオン時間を延長し得る。

#### 【0078】

ゼロ交差検出器 906 は、電流検知信号 942 および参照信号 916 を受ける比較器 914 をさらに含む。図 9A の例では、比較器 914 は、比較器 914 の非反転入力で電流検知信号 942 を受け、比較器 914 の反転入力で参照信号 916 を受ける。このように、一実施例では、電流検知信号 942 が参照信号 916 未満であること（およびしたがって、比較器 914 の出力がローであること）が電源のゼロ交差条件の前提条件の存在を（すなわちゼロ交差条件が存在し得ると）示す。電流検知信号 942 および参照信号 916 は電流信号または電圧信号であり得る。電流検知信号 942 はスイッチ電流 ID144 に関する情報を与える。電流検知信号 942 が電流信号である場合、参照信号 916 はゼロ交差電流しきい値 IZC404 であり得、比較器 914 は電流比較器である。以上で言及されたように、スイッチ電流 ID144 は、たとえば個別の抵抗器の両端の電圧またはトランジスタが導通しているときのトランジスタの両端の電圧などのさまざまな態様で検知され得る。それらの例については、電流検知信号 942 は電圧信号である。電流検知信号 942 が電圧信号である場合、参照信号 916 はゼロ交差電流しきい値 IZC404 に対応する参照電圧であり、比較器 914 は電圧比較器である。

10

20

#### 【0079】

比較器 914 は AND ゲート 917 およびオン時間延長ブロック 904 にさらに結合される。比較器 914 の出力はオン時間延長ブロック 904 によって受けられる。AND ゲート 917 はゼロ交差時間しきい値パルス ZCP924 を受けるようにも結合される。比較器出力 CO952 を受ける AND ゲート 917 の入力に結合される丸印は、AND ゲート 917 が反転された比較器出力 CO952 を受けるように、比較器 914 と AND ゲート 917 との間に反転器が結合されることを示す。たとえば、AND ゲート 917 の出力は、ゼロ交差時間しきい値パルス ZCP924 が論理ハイの値にありかつ比較器出力 CO952 が論理ローの値にある場合、論理ハイの値にある。

#### 【0080】

30

S-R ラッチ 918 は、本明細書中では S-R ラッチ 918 の R 入力とも称されるリセット入力で AND ゲート 917 の出力を受ける。さらに、S-R ラッチ 918 は、本明細書中では S 入力とも称されるセット入力でクロック信号 910 を受ける。クロック信号 910 はスイッチング周期  $T_s$  に関する情報を与え、いくつかの実施例では、発振器（図示せず）から入来し得る。クロック信号 910 は、論理ハイおよび論理ローのセクションの長さが変化する矩形パルス信号である。クロック信号 910 の連続した立上がりエッジ同士の間の時間の長さがスイッチング周期  $T_s$  に実質的に等しい。クロック信号 910 が一旦論理ハイの値のパルスを出力すると、クロック信号 910 は論理ローの値に素早く立下がる。このように、S-R ラッチ 918 はクロック信号 910 の立上がりエッジでセットされる。しかしながら、S-R ラッチ 918 は、AND ゲート 917 の出力が論理ハイの値にあるとリセットする。換言すると、電流検知信号 942 によって与えられるスイッチ電流 ID144 が参照信号 916 によって与えられるゼロ交差電流しきい値 IZC404 を超えていないことを比較器出力 CO952 が示すと、ラッチ 918 はリセットする。図 9A の例では、S-R ラッチ 918 の出力は Q バー出力から取得される。このように、S-R ラッチ 918 がセットされると、S-R ラッチ 918 の出力は論理ローの値である。S-R ラッチ 918 がリセットされると、S-R ラッチ の出力は論理ハイの値である。

40

#### 【0081】

フリップフロップ 922 は S-R ラッチ 918 に結合し、S-R ラッチ 918 の出力を受ける。一実施例では、フリップフロップ 922 は D フリップフロップである。フリップフロップ 922 は D 入力でラッチ 918 の出力を受ける。さらに、フリップフロップ 92

50

2 はクロック入力で駆動信号 940 を受ける。駆動信号 940 は、論理ハイおよび論理ローのセクションの長さが変化する矩形パルス波形である。一実施例では、閉じている（すなわちオンの）スイッチ S1\_114 は駆動信号 940 の論理ハイの値に対応する一方で、開いている（すなわちオフの）スイッチ S1\_114 は駆動信号 940 の論理ローの値に対応する。フリップフロップ 922 のクロック入力に結合された丸印は、フリップフロップ 922 が駆動信号 940 の立下がりエッジで更新することを示す。換言すると、フリップフロップ 922 の出力は、スイッチ S1\_114 がオフするときに更新する。フリップフロップ 922 はゼロ交差フィルタ 926 にさらに結合される。図示されるように、ゼロ交差フィルタ 926 はフリップフロップ 922 の出力を受け、ゼロ交差信号 908 を出力する。フリップフロップ 922 の出力はゼロ交差信号 908 に実質的に等しいが、ゼロ交差フィルタ 926 は、ゼロ交差信号 908 の出力のノイズを低減するように結合される。さらに、ゼロ交差フィルタ 926 は、N 個の連続したスイッチングサイクルが可能なゼロ交差条件を有していないければゼロ交差条件が存在するとゼロ交差信号 908 が示さないようにして、以上で論じたように数 N を実現する。しかしながら、N が 1 に等しい場合は、ゼロ交差フィルタ 926 はゼロ交差検出器 906 から省略されてもよい。

#### 【0082】

スイッチング周期  $T_s$  の開始時に電流検知信号 942 は参照信号 916 未満であり、したがって比較器 914 の出力は論理ローである。換言すると、スイッチング周期  $T_s$  の開始時に、スイッチ電流  $I_{D144}$  はゼロ交差電流しきい値  $I_{ZC404}$  未満である。以上で言及したように、一実施例では、ゼロ交差電流しきい値  $I_{ZC404}$  は非ゼロの値であり、その結果、比較器 914 は、ac 入力電圧  $V_{AC102}$  のゼロ交差の前に前提条件信号（すなわち比較器出力 952）を出力する。クロック信号 910 は、スイッチング周期  $T_s$  の開始時に論理ハイの値のパルスを出力し、S-R ラッチ 918 の出力は論理ローの値にセットされる。クロック信号 910 は迅速に論理ローの値のパルスを出力し、S-R ラッチ 918 は以前の値を保持する。この例については、S-R ラッチ 918 は論理ローの値を保持する。

#### 【0083】

フリップフロップ 922 はスイッチ S1\_114 が開く（すなわちオフになる）と更新する。換言すると、フリップフロップ 922 は、フリップフロップ 922 の出力を更新して、駆動信号 940 の立下がりエッジでフリップフロップ 922 の D 入力を反映する。一般的に、D フリップフロップはクロック入力の立上がりエッジで更新する。しかしながら、フリップフロップ 922 のクロック入力における丸印が反転器を示す場合、フリップフロップ 922 は駆動信号 940 の立下がりエッジで更新する。

#### 【0084】

電流検知信号 942 によって与えられるスイッチ電流  $I_{D144}$  が、ゼロ交差時間しきい値パルス ZCP924 によって与えられるゼロ交差時間しきい値  $T_{M+3}$  に達する前に（または換言すると、ゼロ交差時間しきい値パルス ZCP924 が論理ハイの値に遷移する前に）参照信号 916 によって与えられるゼロ交差電流しきい値  $I_{ZC404}$  を超えなければゼロ交差条件が検出され、AND ゲート 917 の出力は論理ハイの値である。AND ゲート 917 の論理ハイの出力は S-R ラッチ 918 をリセットし、S-R ラッチ 918 の出力は論理ハイの値である。駆動信号 940 の立下がりエッジでフリップフロップ 922 が更新し、フリップフロップ 922 の出力は S-R ラッチ 918 の論理ハイの出力を転送する。一例では、フリップフロップ 922 の出力はゼロ交差フィルタ 926 によってフィルタリングされ、結果的に得られるゼロ交差信号 908 は論理ハイの値である。一実施例では、ゼロ交差フィルタ 926 の出力は、図 4B に関して論じられたように、遅延時間  $t_{x436}$  の後で更新される。別の実施例では、ゼロ交差フィルタ 926 の出力は次のスイッチングサイクルで更新される。さらに、ゼロ交差フィルタ 926 は、ゼロ交差検出器 906 がゼロ交差条件が存在すると決定する前に可能なゼロ交差条件を有する N 個の連続したスイッチングサイクルを実現してもよい。一例では、ゼロ交差フィルタ 926 は、フリップフロップ 922 の出力が論理ハイの値である連続したスイッチングサイクルの数を数

10

20

30

40

50

える論理回路を含んでもよい。このように、ゼロ交差フィルタ 926 は、図 4B を参照して上述されたように、N 回の可能なゼロ交差条件が生じた後でのみゼロ交差条件の存在を示すゼロ交差信号 908 を出力してもよい。一例では、ゼロ交差フィルタ 926 はフリップフロップおよびマルチブレクサを利用して数 N を実現してもよい。別の例では、ゼロ交差フィルタ 926 はカウンタを利用して数 N を実現してもよい。いくつかの例では、図 4B に関する論じられた遅延時間  $t_{x436}$  は、ゼロ交差フィルタ 926 に利用される構成要素によるものであってもよい。本発明の実施例については、ゼロの遅延時間  $t_{x436}$  が好ましいであろう。しかしながら、ゼロの遅延時間  $t_{x436}$  を含むコントローラ 138 の実施例は付加的な回路構成を要件とし得る。このように、コントローラ 138 のいくつかの実施例は、コストおよび / または回路の複雑さを低減するために、非ゼロ遅延時間  $t_{x436}$  を含んでもよい。

10

#### 【0085】

電流検知信号 942 によって与えられるスイッチ電流  $I_D144$  が、ゼロ交差時間しきい値パルス ZCP924 によって与えられるゼロ交差時間しきい値  $t_{zc}$  に達する前に（または換言すると、ゼロ交差時間しきい値パルス ZCP924 が論理ハイの値に遷移する前に）参照信号 916 によって与えられるゼロ交差電流しきい値  $I_{zc}404$  を超えるとゼロ交差条件が検出されず、AND ゲート 917 の出力は論理ローの値である。S-R ラッチ 918 はリセットされず、S-R ラッチ 918 の論理ローの値は駆動信号 940 の立下がりエッジでフリップフロップ 922 の出力に転送される。一例では、フリップフロップ 922 の出力はゼロ交差フィルタ 926 によってフィルタリングされ、結果的に得られるゼロ交差信号 908 は論理ローの値にある。一例では、ゼロ交差フィルタ 926 は、図 4B に関する論じられたように、遅延時間  $t_{x436}$  の後にその出力を更新する。別の例では、ゼロ交差フィルタ 926 の出力は次のスイッチングサイクルで更新される。さらに、ゼロ交差フィルタ 926 は、ゼロ交差検出器 906 がゼロ交差条件がもはや存在しないと決定する前に非ゼロ交差条件を有する N 個の連続したスイッチングサイクルを実現してもよい。たとえば、ゼロ交差フィルタ 926 は、フリップフロップ 922 の出力が論理ローの値である連続したスイッチングサイクルの数を数える論理回路を含んでもよい。このように、一例では、ゼロ交差フィルタ 926 は、図 4B を参照して上述されたように、非ゼロ交差条件を有する N 個のスイッチングサイクルの後でのみ、ゼロ交差条件がもはや存在しないことを示すゼロ交差信号 908 を出力してもよい。

20

30

#### 【0086】

次に図 9B を参照して、オン時間延長ブロック 904 のブロック図を図示する。これは、ゼロ交差時間しきい値パルス ZCP924、駆動信号 940、駆動論理出力 DLO950、比較器出力 CO952、オプションの単安定マルチバイブレータ 954、反転器 964、S-R ラッチ 958、OR ゲート 960、立下がりエッジ遅延 961、および AND ゲート 968 を含む。さらに、図 9B は、信号表記 A 962、B 970、C 956、および反転された駆動論理出力

#### 【0087】

#### 【数 7】

DLO 966

40

#### 【0088】

を図示する。それぞれの信号の波形は図 10 に図示する。

ゼロ交差時間しきい値パルス ZCP924、駆動信号 940、駆動論理出力 DLO950、および比較器出力 CO952 は上述のように結合しあつ機能する。さらに、オン時間延長ブロック 904 は、任意的に、駆動論理出力 DLO950 に結合しあつこれを受ける単安定マルチバイブレータ 954 を含んでもよい。上述のように、駆動論理出力 DLO950 は、コントローラの状態に関する情報および意図される駆動信号をオン時間延長ブロック 904 に与える。駆動論理出力 DLO950 は、論理ハイおよび論理ローのセクションの長さが変化する矩形パルス波形であり、連続した立上がりエッジ同士の間の時間の長

50

さがスイッチング周期  $T_s$  に実質的に等しい。単安定マルチバイブレータ 954 は駆動論理出力 DLO950 を受け、駆動論理出力 DLO950 の毎立上がりエッジにパルスを生成する。単安定マルチバイブレータ 954 の出力は信号 C 956 と表記され、その例示的な波形が波形 C 1056 として図 10 に図示される。単安定マルチバイブレータ 954 は S-R ラッチ 958 に結合する。図 9B に示される例については、単安定マルチバイブレータ 954 は S-R ラッチ 958 の S 入力に結合する。S-R ラッチ 958 は、S 入力で単安定マルチバイブレータ 954 の出力である信号 C 956 を受ける。別の実施例では、信号 C 956 は発振器（図示せず）によって生成されてもよい。

#### 【0089】

さらに、オン時間延長ブロック 904 は比較器出力 952 およびゼロ交差時間しきい値パルス ZCP924 に結合する。遅延時間  $t_D$  だけ比較器出力 952 の立下がりエッジを遅延させる立下がりエッジ遅延 961 が比較器出力 952 を受ける。立下がりエッジ遅延 961 は OR ゲート 960 にさらに結合し、OR ゲート 960 の一方の入力で信号 CO と表記される立下がりエッジ遅延 961 の出力を受ける。OR ゲート 960 の他方の入力はゼロ交差時間しきい値パルス ZCP924 を受ける。OR ゲート 960 は AND ゲート 968 にさらに結合し、AND ゲート 968 の一方の入力が信号 A 962 と表記される OR ゲート 960 の出力を受ける。

#### 【0090】

さらに、AND ゲート 968 も反転器 964 に結合する。反転器 964 は駆動論理出力 DLO950 に結合しつつこれを受ける。反転された駆動論理出力

#### 【0091】

#### 【数 8】

DLO 966

#### 【0092】

が反転器 964 から出力され、AND ゲート 968 がこれを受ける。AND ゲート 968 は S-R ラッチ 958 の R 入力にさらに結合する。S-R ラッチ 958 の R 入力で信号 B 970 と表記される AND ゲート 968 の出力を受ける。S-R ラッチ 958 は S 入力および R 入力での値を利用して駆動信号 940 を出力する。

#### 【0093】

図 9B に示されるように、比較器出力 CO952 が、スイッチ電流  $I_D144$  がゼロ交差電流しきい値  $I_{zc}$  未満であると示す場合、OR ゲート 960 の出力は、AND ゲート 968 が S-R ラッチ 958 をリセットしないようにし得る。換言すると、比較器出力 CO952 が、スイッチ電流  $I_D144$  がゼロ交差電流しきい値  $I_{zc}$  未満であると示す場合、OR ゲート 960 の出力は、S-R ラッチ 958 が論理ローの値を出力しないようにし、こうしてスイッチ S1 114 のオン時間を延長し得る。図 10 にさらに図示されるように、OR ゲート 960 の出力は S-R ラッチ 958 がリセットしないようにし、こうして比較器出力 CO952 が、スイッチ電流  $I_D144$  がゼロ交差電流しきい値  $I_{zc}$  に達したと示すか、またはゼロ交差時間電流しきい値 ZCP924 がゼロ交差時間しきい値  $t_{zc}$  に達したと示すまで、スイッチ S1 114 のオン時間を延長する。しかしながら、スイッチ電流  $I_D144$  が、駆動論理出力 DLO950 が与える初期スイッチオン時間の間にゼロ交差電流しきい値  $I_{zc}$  を超えれば、または換言すると駆動論理出力 DLO950 が論理ハイの値にある場合、S-R ラッチ 958 は駆動論理出力 DLO950 の立下がりエッジでリセットする。なぜなら、駆動論理出力 DLO950 は、意図される駆動信号に関する情報を与え、AND ゲート 968 の出力は、その入力の両者ともが同時に論理ハイになると S-R ラッチ 958 のリセットのみを行なうからである。図 9A および図 9B に関して論じた信号のさまざまな波形を図 10 に図示する。

#### 【0094】

次に図 10 を参照して、図 9A および図 9B に対応するさまざまな波形を図示する。図 10 は、コントローラ 938 およびゼロ交差検出のためのオン時間延長を実現するオン時

10

20

30

40

50

間延長ブロック 904 のさまざまな波形同士の間の差を図示する。例示的な波形  $I_D$  1044、 $DLO$  1050、

【0095】

【数9】

DLO 1066

【0096】

、 $C O$  1052、 $Z C P$  1024、 $A$  1062、 $B$  1070、 $C$  1056、および

駆動信号 1040 は、スイッチ電流  $I_D$  1044、駆動論理出力  $DLO$  950、反転器駆動

論理出力

10

【0097】

【数10】

DLO 966

【0098】

、立下がりエッジ遅延比較器出力  $C O$ 、ゼロ交差時間電流しきい値  $Z C P$  924、ならび

に信号表記  $A$  962、 $B$  970、 $C$  956、および駆動信号 940 に対応する。さら

に、図 10 は、スイッチングサイクル 1002、1004、および 1006 を図示する。

図示されるように、各々のスイッチングサイクルはスイッチング周期  $T_S$  を有する。

20

【0099】

図 10 に示される例については、すべてのスイッチングサイクルの開始時に、駆動論理

出力  $DLO$  1050 は論理ハイの値にある。さらに、スイッチ電流  $I_D$  1044 がゼロ交

差電流しきい値  $I_{ZC}$  未満であるため、比較器出力  $C O$  1052 は論理ローの値にある。ゼ

ロ交差時間しきい値パルス  $Z C P$  1024 は、すべてのスイッチングサイクルの開始時に

論理ローの値にある。OR ゲート 960 の出力である波形  $A$  1062 は論理ローの値に

ある。AND ゲート 968 は波形  $A$  1062 の論理ローの値および（現在は論理ローの

値にある）反転された駆動論理出力

【0100】

【数11】

DLO 1066

30

【0101】

を受け、その結果、波形  $B$  1070 はすべてのスイッチングサイクルの開始時に論理ロー

の値である。単安定マルチバイブレータ 954 は駆動論理出力  $DLO$  1050 を受け、

波形  $C$  1056 で示される論理ハイのパルスを出力する。すべてのスイッチングサイクル

の開始時に波形  $C$  1056 は論理ハイの値にある一方で、波形  $B$  1070 は論理ロー

の値にある。その結果、S-R ラッチ 958 は論理ハイの値にある駆動信号 1040 を

出力し、スイッチ S1 114 がオンし、スイッチ電流  $I_D$  1044 が増加し始める。波形

$C$  1056 は論理ローの値に迅速に立下がり、S-R ラッチ 958 は以前の値を保持

する。すべてのスイッチングサイクルの開始時に、S-R ラッチ 958 は論理ハイの値を

保持し、スイッチ S1 114 はオンのままである。しかしながら、S-R ラッチ 958

は論理ローの値を出力し、したがって R 入力の波形  $B$  1070 が論理ハイの値のパルス

を出力するとスイッチ S1 114 をオフする。波形  $B$  1070 が論理ハイの値のパルス

を出力するさまざまな条件を以下にさらに論じる。

40

【0102】

スイッチングサイクル 1002 で、スイッチ電流  $I_D$  1044 は、駆動論理出力  $DLO$

1050 が与える初期オン時間  $t_{ON}$  の間にゼロ交差電流しきい値  $I_{ZC}$  を超える。または換

言すると、スイッチ電流  $I_D$  1044 は、駆動論理出力  $DLO$  1050 の立下がりエッジ

の前にゼロ交差電流しきい値  $I_{ZC}$  を超える。スイッチ電流  $I_D$  1044 がゼロ交差電流

しきい値  $I_{ZC}$  を超えると、比較器出力  $C O$  1052 は論理ハイの値に遷移する。スイッチ

50

グサイクル 1002 の間、比較器出力 CO1052 が論理ハイの値に遷移しても波形 ZC P1024 は依然として論理ローの値にあり、その結果、波形 A 1062 は論理ハイの値に遷移する。例示的なスイッチングサイクル 1002 について、波形 B 1070 は、駆動論理出力 DLO1050 が論理ローの値に遷移すると論理ハイの値のパルスを出力する。なぜなら、AND ゲート 968 は、反転器 964 のために、反転された駆動論理出力

【0103】

【数12】

DLO 1066

【0104】

10

を受けるからである。換言すると、波形 B 1070 は、反転された駆動論理出力

【0105】

【数13】

DLO 1066

【0106】

が論理ハイの値に遷移すると論理ハイの値に遷移する。駆動論理出力 DLO1050 の立下がりエッジで、波形 B は論理ハイの値に遷移し、S-R ラッチ 958 はリセットされ、駆動信号 1040 は論理ローの値に立下がる。このように、スイッチ S1 114 はオフし、スイッチ電流 ID1044 は実質的に 0 に降下する。スイッチ電流 ID1044 がゼロ交差電流しきい値  $I_{ZC}$  を下回ると、比較器出力 CO1052 は論理ローの値に立ち下がる。しかしながら、比較器出力 CO1052 の立下がりエッジは、立下がりエッジ遅延 961 により遅延時間  $t_D$  だけ遅延される。

20

【0107】

スイッチングサイクル 1004 で、スイッチ電流 ID1044 は、駆動論理出力 DLO1050 が与える初期オン時間  $t_{ON}$  の間にゼロ交差電流しきい値  $I_{ZC}$  を超えず、コントローラはスイッチ S1 114 のオン時間を延長する。または換言すると、スイッチ電流 ID1044 は、駆動論理出力 DLO1050 の立下がりエッジの前にゼロ交差電流しきい値  $I_{ZC}$  を超えず、比較器出力 CO1052 は論理ローの値に留まる。図 10 に図示されるように、延長されたオン時間  $t_{ONX}$  は、駆動論理出力 DLO1050 の立下がりエッジと、スイッチ S1 114 がオフするときとの間の時間の長さである。換言すると、延長されたオン時間  $t_{ONX}$  は、駆動論理出力 DLO1050 の立下がりエッジと、駆動信号 1040 の立下がりエッジとの間の時間の長さである。さらに、スイッチ電流 ID1044 は、ゼロ交差時間しきい値パルス ZCP1024 の立上がりエッジの前にゼロ交差電流しきい値  $I_{ZC}$  を確かに超える。スイッチ電流 ID1044 がゼロ交差電流しきい値  $I_{ZC}$  を超えると、比較器出力 CO1052 は論理ハイの値のパルスを出力し、OR ゲート 960 は（論理ハイの値に遷移する波形 A 1062 として図 10 に図示される）論理ハイの値を出力する。AND ゲート 968 の一方の入力は波形 A 1062 からの論理ハイの値を受け、AND ゲート 968 の他方の入力は反転された駆動論理出力

30

【0108】

40

【数14】

DLO 1066

【0109】

からの論理ハイの値を受ける。その結果、波形 B 1070 は論理ハイの値に遷移し、ラッチ 958 をリセットする。駆動信号 1040 は論理ローの値に立下がり、スイッチ S1 114 をオフし、スイッチ電流 ID1044 は実質的に 0 に降下する。スイッチ電流 ID1044 がゼロ交差電流しきい値  $I_{ZC}$  を下回ると、比較器出力 CO1052 は論理ローの値に立下がる。しかしながら、比較器出力 CO1052 の立下がりエッジは、立下がりエッジ遅延 961 により、遅延時間  $t_D$  だけ遅延される。

50

## 【0110】

スイッチングサイクル1006で、スイッチ電流 $I_D1044$ は、駆動論理出力DLO1050が与える初期オン時間 $t_{ON}$ の間にゼロ交差電流しきい値 $I_{ZC}$ を超えず、コントローラはスイッチS1 1114のオン時間を延長する。さらに、スイッチ電流 $I_D1044$ は、ゼロ交差時間しきい値パルスZCP1024の立上がりエッジの前にゼロ交差電流しきい値 $I_{ZC}$ を超えない。示されるように、延長されたオン時間 $t_{ONX}$ は、駆動論理出力DLO1050の立下がりエッジとスイッチS1 1114がオフするときとの間の時間の長さである。比較器出力CO1052はスイッチングサイクル1006全体の間論理ローの値に留まる。したがって、波形Aはゼロ交差時間しきい値パルスZCP1024の立上がりエッジで論理ハイの値に遷移する。波形ZCP1024が論理ハイの値に遷移すると、波形B 1070は論理ハイの値に遷移し、次にS-Rラッチ958がリセットし、駆動信号1040が論理ローの値に立下がり、スイッチS1 1114をオフし、スイッチ電流 $I_D1044$ が実質的に0に降下する。

## 【0111】

本明細書中に開示された発明が、その具体的な実施例、例および適用例によって説明されたが、請求項に述べた発明の範囲から逸脱することなく、当業者によって本発明に対して数多くの修正および変形がなされ得る。

## 【符号の説明】

## 【0112】

100 電源、102 ac入力電圧、S1 1114 スイッチ、138 コントローラ、902 駆動論理ブロック、904 オン時間延長ブロック、906 ゼロ交差検出器。

【図1】

【図2 A】

【図2B】

【 四 3 】

【図4A】

【図4B】

【図5】

【図6】

【図7A】

【図7B】

【図 8 A】

【図 8 B】

【図 9 A】

【図 9 B】

【図10】

---

フロントページの続き

(72)発明者 ミンミン・モウ

アメリカ合衆国、95014 カリフォルニア州、クバチーノ、セレスト・サークル、20735

(72)発明者 ティツィアーノ・パストーレ

イタリア、20052 モンツァ、ピア・アリストイデ・デ・アンティキ、1

審査官 安食 泰秀

(56)参考文献 特開平06-022546(JP,A)

特開2000-350462(JP,A)

特開2007-020395(JP,A)

特開2006-319172(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/28