OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

⑪ Número de publicación: **2 241 593**

⑯ Int. Cl.:

**G06F 13/36** (2006.01)

**G06F 13/38** (2006.01)

⑫

## TRADUCCIÓN DE PATENTE EUROPEA MODIFICADA

T5

⑯ Número de solicitud europea: **00916466 .6**

⑯ Fecha de presentación : **20.03.2000**

⑯ Número de publicación de la solicitud: **1092193**

⑯ Fecha de publicación de la solicitud: **18.04.2001**

⑯ Título: **Arquitectura para un dispositivo de memoria flash PC con bus serie universal.**

⑯ Prioridad: **05.04.1999 US 285706**

⑯ Titular/es: **SanDisk IL Ltd.**

7 Atir Yeda Street

Kfar Saba 44425, IL

⑯ Fecha de publicación de la mención y de la traducción de patente europea: **01.11.2005**

⑯ Inventor/es: **Ban, Amir;**

**Moran, Dov** y

**Ogdan, Oron**

⑯ Fecha de la publicación de la mención de la patente europea modificada BOPI: **31.03.2010**

⑯ Agente: **Torner Lasalle, Elisabet**

⑯ Fecha de publicación de la traducción de patente europea modificada: **31.03.2010**

## DESCRIPCIÓN

Arquitectura para un dispositivo de memoria flash PC con bus serie universal.

5 La presente invención se refiere a los dispositivos de memoria semiconductor, y en particular, a los módulos de memoria no volátil borrable y programable que son conectados a una plataforma de ordenador principal usando el bus de PC USB (bus de PC USB = bus de ordenador personal que como tal bus está realizado según el estándar USB (USB = bus serie universal)).

10 Los módulos de memoria no volátil borrable y programable, a los que se llama de aquí en adelante dispositivos de memoria flash o dispositivos flash, son conocidos en la técnica para el almacenamiento de información. Los dispositivos flash incluyen las memorias de sólo lectura programables y borrables eléctricamente (EEPROMs), que están hechas de transistores de puerta flotante y de tipo flash y son memorias no volátiles cuya funcionalidad y rendimiento son similares a los de las memorias EPROM (Memorias EPROM = memorias únicamente de lectura programables y 15 borrables), con una funcionalidad adicional que le permite a una operación programable y ejecutada en circuito borrar páginas de la memoria. Un ejemplo de una implementación de un dispositivo flash de este tipo se da en la Patente U.S. Nº 5.799.168, que queda incorporada a la presente por referencia como si hubiera sido expuesta aquí en su totalidad.

20 Los dispositivos flash tienen la ventaja de ser relativamente económicos y requerir relativamente poca energía eléctrica en comparación con los tradicionales discos de almacenamiento magnético. Sin embargo, en un dispositivo flash no resulta viable regrabar en una zona de la memoria en la que previamente se haya efectuado una grabación sin un precedente borrado en modo página de la zona. Esta limitación de los dispositivos flash hace que los mismos sean incompatibles con los típicos programas de sistemas operativos existentes, puesto que no pueden grabarse datos en una zona de memoria dentro del dispositivo flash en la cual se hayan grabado datos anteriormente, a no ser que la zona 25 sea primeramente borrada. Para manejar estas funciones del dispositivo de memoria flash es necesario un sistema de manejo del soporte lógico informático tal como el descrito en la Patente U.S. Nº 5.404.485, que fue presentada el 5 de marzo de 1993.

30 En la actualidad, estos dispositivos de memoria flash tienen una segunda limitación, que es la que radica en el hecho de que los mismos deben ser unidos estáticamente a la plataforma del ordenador principal, o bien son unidos y separados dinámicamente usando la interfaz de la PCMCIA [Asociación Internacional para la Estandarización de las Tarjetas de Memoria para Ordenadores Personales]. Ambas implementaciones presentan inconvenientes, entre los que se incluyen la dificultad de uso y el alto coste.

35 Una implementación más útil seguiría el estándar USB como el descrito en la Especificación USB Versión 1.1. El estándar USB ofrece un menor factor de forma y una mayor facilidad de uso para el usuario final, reduciendo el coste de la implementación. Este estándar está destinado a ser usado en toda la industria y es promovido por empresas tales como la Compaq Computer Corporation, Microsoft, IBM e Intel para servir de ampliación de la arquitectura de PC con vistas a la Integración de la Telefonía Informatizada (CTI), al consumidor y a las aplicaciones en el campo de la 40 productividad.

45 Los criterios que fueron aplicados para definir la arquitectura para el estándar USB incluyen la facilidad de expansión de periféricos del PC (ordenador personal), el bajo coste, la capacidad para soportar velocidades de transferencia de hasta 12 Mb/segundo y la capacidad de proporcionar pleno soporte para datos en tiempo real, voz, audio y vídeo comprimido. Este estándar también ofrece flexibilidad en materia de protocolos para transferencias de datos isócronos en modo mixto y transmisión asíncrona de mensajes, para su integración en las tecnologías de los dispositivos comerciales y para proporcionar una interfaz estándar para una rápida integración en cualquier tipo determinado de producto que constituya un ordenador principal. Además, el estándar USB representa un modelo único para el cableado y la 50 unión de conectores, de forma tal que quedan aislados del usuario final todos los detalles de las funciones eléctricas, incluyendo las conexiones terminales de bus. Mediante el estándar, los dispositivos periféricos se autoidentifican y soportan la transferencia por proyección automática de funciones a un controlador. Además, el estándar permite que todos los dispositivos periféricos puedan ser incorporados dinámicamente y sean reconfigurables.

55 Un sistema construido según el estándar USB queda descrito por tres sectores definidos e independientes: la interconexión USB, los dispositivos USB y la plataforma de ordenador principal para USB. La interconexión USB es la manera como los dispositivos USB son conectados a la plataforma del ordenador principal y se comunican con la misma. Las correspondientes funciones y los correspondientes componentes incluyen la topología de bus, que es el modelo de conexión entre los dispositivos USB y la plataforma del ordenador principal.

60 La interconexión física del USB tiene una topología en estrella escalonada. Hay en el centro de cada estrella un núcleo. Cada segmento de cable es una conexión punto a punto entre la plataforma del ordenador principal y un núcleo o función, o un núcleo conectado a otro núcleo o función.

65 En cuanto a la pila de capacidades, las tareas de USB que son ejecutadas en cada capa en el sistema incluyen un modelo de flujo de datos y una planificación. El modelo de flujo de datos es la manera como los datos se mueven en el sistema a través del USB entre los elementos que producen datos y los elementos que consumen datos. La planificación determina el acceso a la interconexión, que es compartido. Tal planificación permite que sean soportadas las transferencias de datos isócronos y elimina la carga general de arbitraje.

El propio USB es un bus sondeado. En la plataforma del ordenador principal el controlador del ordenador principal inicia todas las transferencias de datos. Todas las transacciones por bus suponen la transmisión de hasta tres paquetes. Cada transacción comienza cuando el controlador del ordenador principal envía de manera planificada un paquete de USB que describe el tipo y la dirección de transacción, la dirección del dispositivo USB y el número del punto terminal.

5 Este paquete es el llamado “paquete de señal”. El dispositivo USB al cual está dirigido el paquete se autoselecciona decodificando los apropiados campos de dirección. En una transacción determinada, los datos son transferidos ya sea de la plataforma del ordenador principal a un dispositivo o bien de un dispositivo a la plataforma del ordenador principal. La dirección de la transferencia de datos está especificada en el paquete de señal. El origen de la transacción envía entonces un paquete de datos o indica que el origen no tiene datos para transferir. El destino responde en general 10 con un paquete de establecimiento de comunicación que indica si la transferencia tuvo lugar con éxito.

El modelo de transferencia de datos de USB entre un origen y destino en la plataforma del ordenador principal y un punto terminal en un dispositivo recibe el nombre de “tubería”. Hay dos tipos de tuberías: de flujo y de mensaje. Los datos de flujo no tienen una estructura definida como de USB, mientras que los datos de mensaje sí la tienen. 15 Adicionalmente, las tuberías tienen asociaciones de ancho de banda de datos, tipo de servicio de transferencia y características de punto final como la direccionalidad y los tamaños de memoria intermedia. En su mayoría las tuberías pasan a existir cuando se configura un dispositivo USB. Una tubería de mensaje, que es la tubería de control por defecto, existe siempre una vez que se ha dado corriente a un dispositivo, a fin de proporcionar acceso a la configuración, al estado y a la información de control para el dispositivo.

20 El plan de transacción para el estándar USB permite el control de flujo para algunas tuberías de flujo. Al nivel del soporte físico, esto impide que se den situaciones en las cuales las memorias intermedias se vean sometidas a condiciones de trabajo situadas por debajo o por encima de su capacidad, usando un establecimiento de comunicación con reconocimiento negativo para reducir la velocidad de transferencia de datos. Con el establecimiento de comunicación 25 con reconocimiento negativo se reintenta una transacción cuando está disponible tiempo de bus. El mecanismo de control de flujo permite el establecimiento de planes flexibles que permiten la concurrente puesta en servicio de una mezcla heterogénea de tuberías de flujo. Así, múltiples tuberías de flujo pueden ser puestas en servicio a intervalos distintos con paquetes de distintos tamaños.

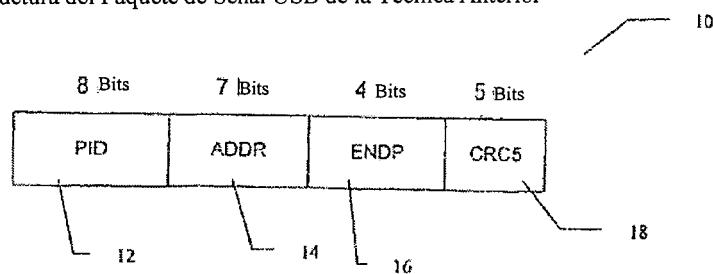

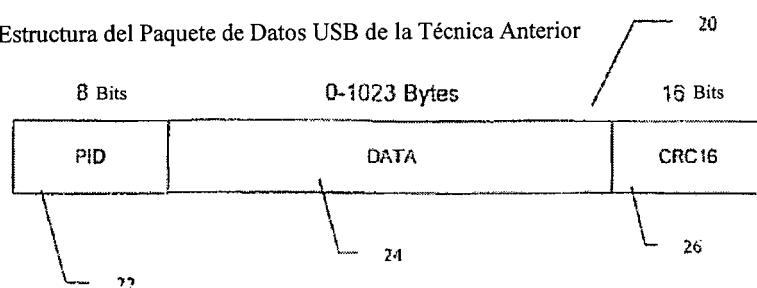

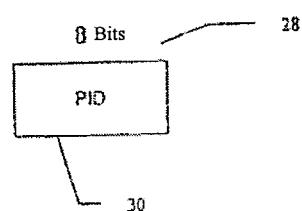

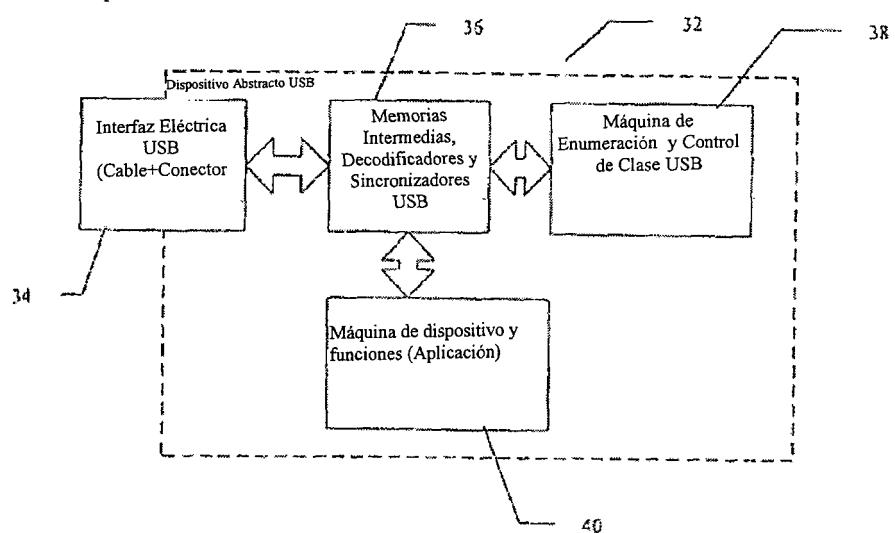

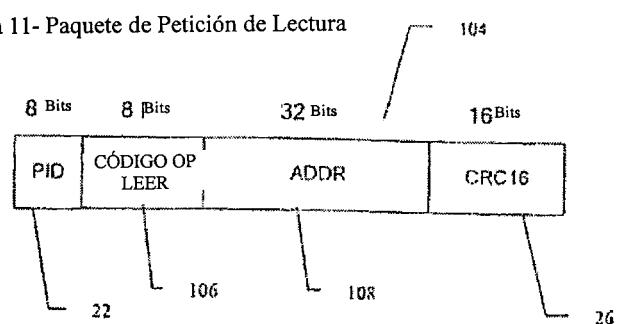

30 Como se ha descrito, el estándar USB tiene tres tipos principales de paquetes, que incluyen los paquetes de señal, los paquetes de datos y los paquetes de establecimiento de comunicación. En las Figuras 1-3 de la técnica anterior se ilustra un ejemplo de cada tipo de paquete. La Figura 4 de la técnica anterior ilustra un ejemplo de dispositivo abstracto USB.

35 Un paquete de señal 10 como el que se ilustra en la Figura 1 de la técnica anterior presenta un campo PID (de identificación de paquete) 12 que especifica uno de tres tipos de paquete: IN, OUT o SETUP. Si el campo PID 12 especifica el tipo de paquete IN la transacción de datos está definida como de una función a la plataforma del ordenador principal. Si el campo PID 12 especifica el tipo de paquete OUT o SETUP, la transacción de datos está definida como de la plataforma del ordenador principal a una función.

40 Un campo ADDR 14 especifica la dirección, mientras que un campo ENDP 16 especifica el punto terminal para el paquete de señal 10. Para las transacciones OUT y SETUP, en las cuales el campo PID 12 especifica que el paquete de señal 10 es un paquete del tipo OUT o un paquete del tipo SETUP, el campo ADDR 14 y el campo ENDP 16 identifican singularmente el punto terminal para recibir el paquete de datos subsiguiente, que está ilustrado en la Figura 2, que viene a continuación del paquete de señal 10. Para las transacciones IN, en las cuales el campo PID 12 especifica que el paquete de señal 10 es un paquete del tipo IN, el campo ADDR 14 y el campo ENDP 16 identifican singularmente qué puntos terminales transmiten un paquete de datos. Un campo CRC5 18 contiene la suma de verificación, para determinar que el paquete de señal 10 ha sido recibido sin corrupción. Solamente la plataforma del ordenador principal puede emitir paquetes de señal 10, de forma tal que los paquetes de señal 10 proporcionan un control de la transmisión 50 de los subsiguientes paquetes de datos.

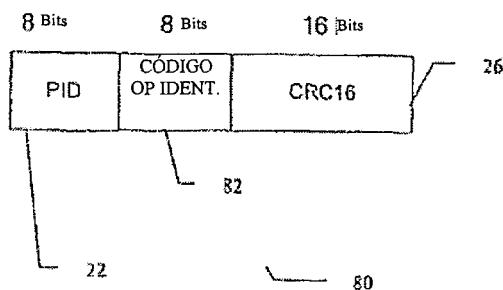

55 Como se muestra en la Figura 2 de la técnica anterior, un paquete de datos 20 de USB también presenta un campo PID (de identificación de paquete) 22 para identificar el tipo de paquete de datos. El paquete de datos 20 también presenta un campo de datos 24 que es para contener opcionalmente datos, y un campo CRC 26 para contener la suma de verificación como se ha descrito anteriormente.

La Figura 3 de la técnica anterior muestra un paquete de establecimiento de comunicación 28 para USB de la técnica anterior que presenta solamente un campo PID (de identificación de paquete) 30. Los paquetes de establecimiento de comunicación 28 se usan para informar sobre el estado de una transacción de datos y pueden devolver valores que indican las condiciones de exitosa recepción de datos, aceptación o rechazo de órdenes, control de flujo y detención. 60 Solamente los tipos de transacción que soportan el control de flujo pueden devolver paquetes de establecimiento de comunicación 28. Los paquetes de establecimiento de comunicación 28 son siempre devueltos en la fase de establecimiento de comunicación de una transacción y pueden ser devueltos en lugar de paquetes de datos 20 en la fase de datos de una transacción.

65 Estos tres tipos distintos de paquetes son intercambiados durante distintas fases de la transacción que incluye un dispositivo USB. Se muestra en la Figura 4 para un dispositivo USB abstracto de la técnica anterior un diagrama de bloques de los bloques funcionales de un típico dispositivo USB 32. El dispositivo USB 32 típicamente incluye una

interfaz eléctrica 34 para USB que presenta un cable y un conector y es una interfaz física para recibir y transmitir señales eléctricas que son compatibles con la especificación USB que ha sido descrita anteriormente. Las señales son entonces pasadas a una interfaz lógica 36 que incluye una o varias memorias intermedias, el decodificador de direcciones de dispositivos para decodificar la dirección del dispositivo que constituye el origen de las señales, y

5 un sincronizador del campo SYNC para sincronizar las señales. La información y las estructuras que se requieren para el manejo de un dispositivo abstracto USB 32 como dispositivo USB están almacenadas en una máquina 38 de enumeración y control de clase de USB. Una máquina 40 de dispositivo y funciones, a la que también se denomina la “aplicación”, controla y maneja las propiedades y funciones específicas del dispositivo abstracto USB 32. Además, la máquina 40 de dispositivo y funciones también consume y produce la mayor parte de los datos a través del bus USB.

10 La especificación USB no define la relación entre las distintas entidades del dispositivo abstracto USB 32. En lugar de ello, la especificación USB solamente describe las exigencias que deberán satisfacer los paquetes y la conexión eléctrica y física entre el dispositivo abstracto USB 32 y el bus. Por consiguiente, las conexiones y relaciones que se ilustran en la Figura 4 de la técnica anterior constituyen tan sólo un ejemplo de una implementación que cumple con las exigencias de la especificación USB. Así, todo dispositivo específico destinado a cumplir con la especificación USB debe tener una arquitectura específicamente definida y descrita.

20 Desgraciadamente, no existe tal arquitectura para un dispositivo de memoria flash que contiene uno o varios módulos de memoria flash; cuya arquitectura le permitiría al dispositivo de memoria flash conectarse a un bus definido según la especificación USB y formar con ello parte de un sistema USB en una plataforma de ordenador principal. Por ejemplo, la Patente U.S. Nº 5.799.168 no describe ni sugiere una implementación de este tipo para el dispositivo flash. Como se ha mencionado anteriormente, una arquitectura de este tipo sería particularmente útil por una serie de razones entre las que se incluyen el bajo coste, la facilidad de uso y la transparencia para el usuario final.

25 El documento WO9901820A describe un dispositivo periférico que está destinado a ser usado con un ordenador principal. En lugar de almacenar las características del dispositivo periférico como tal dispositivo en la memoria del dispositivo periférico, como en el estado de la técnica que está descrito en el documento WO9901820A, el sistema del documento WO9901820A almacena las características del dispositivo en el ordenador principal y descarga las características del dispositivo al dispositivo periférico cuando el dispositivo periférico es conectado al ordenador principal.

30 El documento también menciona que la memoria podría ser una memoria flash.

35 El documento WO9908196A describe un dispositivo periférico USB genérico, tal como un dispositivo de almacenamiento masivo, en el cual solamente uno o dos FIFOs ponen en servicio hasta el máximo de 16 puntos terminales permitidos por el estándar USB.

40 Por consiguiente, hay necesidad de y sería útil contar con una arquitectura para definir y describir un dispositivo de memoria flash que sea compatible con un sistema USB y siga la especificación USB de forma tal que el dispositivo de memoria flash pudiese sentarse en un bus definido según el estándar USB y comunicarse con la plataforma del ordenador principal a través de este bus.

45 En consecuencia, la presente invención consiste en un dispositivo de memoria flash USB para conectar a un bus definido como USB, comprendiendo el dispositivo de memoria flash:

(a) al menos un módulo de memoria flash;

50 (b) un conector que es un conector USB que está adaptado para la conexión a un bus definido como USB y para enviar y recibir paquetes definidos como de USB a y desde dicho bus definido como USB; y

(c) un controlador USB que interactúa con un ordenador principal a través de dicho conector USB y al menos ejecuta una operación de las operaciones de lectura y de grabación en dicho módulo de memoria flash que es al menos uno de acuerdo con dichos paquetes definidos como de USB;

55 estando dicho dispositivo de memoria flash caracterizado por el hecho de que dicho controlador comprende un intérprete de órdenes que está adaptado para extraer e interpretar órdenes de lectura y grabación recibidas como código de operación extraído de paquetes de datos definidos como de USB y recibidos a través de dicho conector USB convirtiéndolas en acciones de lectura y grabación para dicho módulo de memoria flash que es al menos uno.

Se especifican en las reivindicaciones dependientes adjuntas adicionales realizaciones de la invención.

60 La presente invención es de un dispositivo de memoria flash que contiene uno o varios módulos flash, siendo la memoria flash proyectada en el espacio de direccionamiento de un ASIC (ASIC = circuito integrado de aplicación específica) o un controlador que tiene una interfaz eléctrica definida como de USB y una interfaz lógica definida como de USB. Este controlador/ASIC (al que se llama de aquí en adelante “controlador”) soporta la funcionalidad de USB según el estándar USB, soportando con ello la enumeración sobre el bus USB, así como la recepción y transmisión de datos a través de tuberías USB hacia y desde puntos terminales de USB. Este controlador también soporta la funcionalidad y el control del dispositivo de memoria flash, así como el procesamiento de los paquetes de órdenes y de datos procedentes del controlador del ordenador principal. El controlador del ordenador principal usa uno de varios posibles protocolos, ya sea estándar o bien privados, para indicar al controlador flash USB la siguiente orden

# ES 2 241 593 T5

a ejecutar. Así, todo el dispositivo actúa como un dispositivo de almacenamiento no volátil incorporable/separable dinámicamente para la plataforma del ordenador principal.

De aquí en adelante, el vocablo “ordenador” incluye, aunque sin carácter limitativo, los ordenadores personales

- 5 (PC) que tienen un sistema operativo tal como el llamado DOS, Windows<sup>MF</sup> (MF = Marca de Fábrica), OS/2<sup>MF</sup> o Linux; los ordenadores Macintosh<sup>MF</sup>; los ordenadores que tienen el JAVA<sup>MF</sup> -OS como sistema operativo; y las estaciones gráficas de trabajo tales como los ordenadores de Sun Microsystems<sup>MF</sup> y de Silicon Graphics<sup>MF</sup> y otros ordenadores que tengan alguna versión del sistema operativo UNIX tales como los AIX<sup>MF</sup> o SOLARIS<sup>MF</sup> de Sun Microsystems<sup>MF</sup>; o cualquier otro sistema operativo conocido y disponible, incluyendo los sistemas operativos tales como el Windows 10 CE<sup>MF</sup> para sistemas informatizados, incluyendo teléfonos móviles, dispositivos informatizados de mano y dispositivos informatizados de bolsillo y cualquier otro dispositivo informatizado que pueda ser conectado a una red. De aquí en adelante, la expresión “Windows<sup>MF</sup>” incluye, aunque sin carácter limitativo, a Windows 95<sup>MF</sup>, Windows 3.x<sup>MF</sup>, en el que “x” es un entero tal como “1”, Windows NT<sup>MF</sup>, Windows 98<sup>MF</sup>, Windows CE<sup>MF</sup> y cualesquiera versiones mejoradas de estos sistemas operativos de Microsoft Inc. (de Seattle, Washington, EE.UU.).

15

Se describe a continuación la invención a título de ejemplo y haciendo referencia a los dibujos acompañantes, en los cuales:

20 La Fig. 1 es un diagrama de bloques de una estructura de paquete de señal USB de la técnica anterior;

la Fig. 2 es un diagrama de bloques de una estructura de paquete de datos USB de la técnica anterior;

25 la Fig. 3 es un diagrama de bloques de una estructura de paquete de datos de establecimiento de comunicación USB de la técnica anterior;

la Fig. 4 es un diagrama de bloques de un ejemplo de dispositivo USB de la técnica anterior;

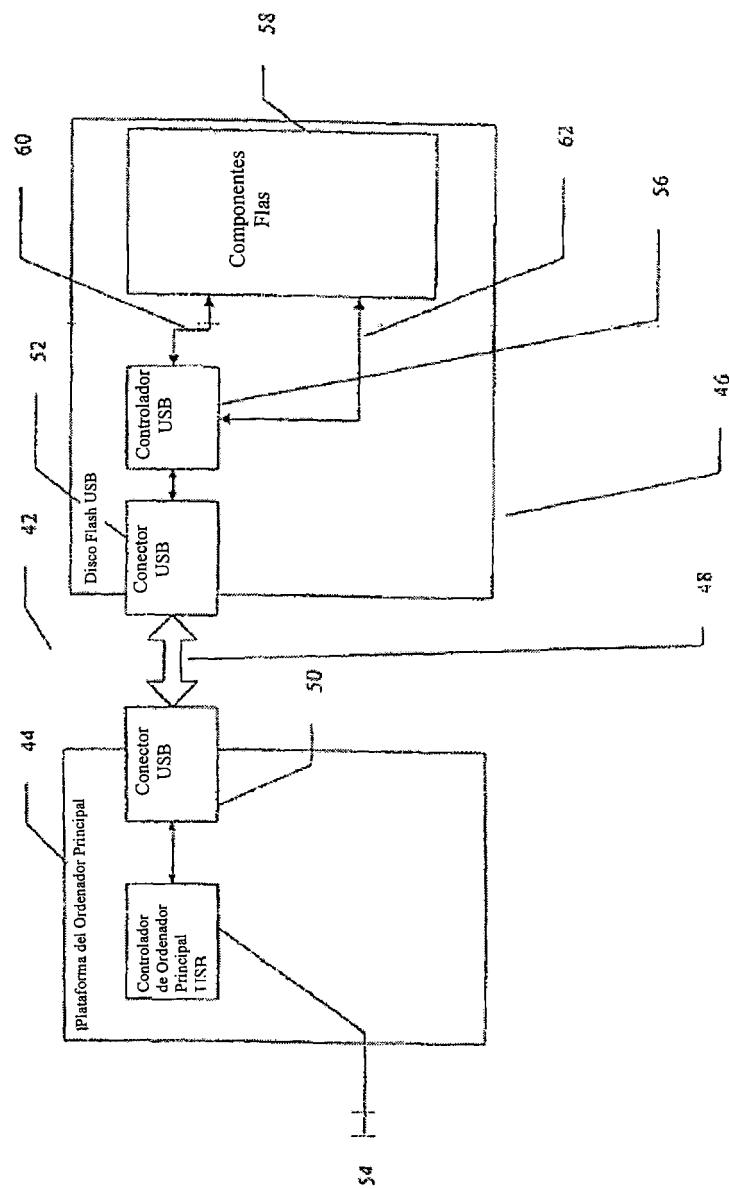

30 la Fig. 5 es un diagrama de bloques de un sistema con una funcionalidad de dispositivo USB flash según la presente invención;

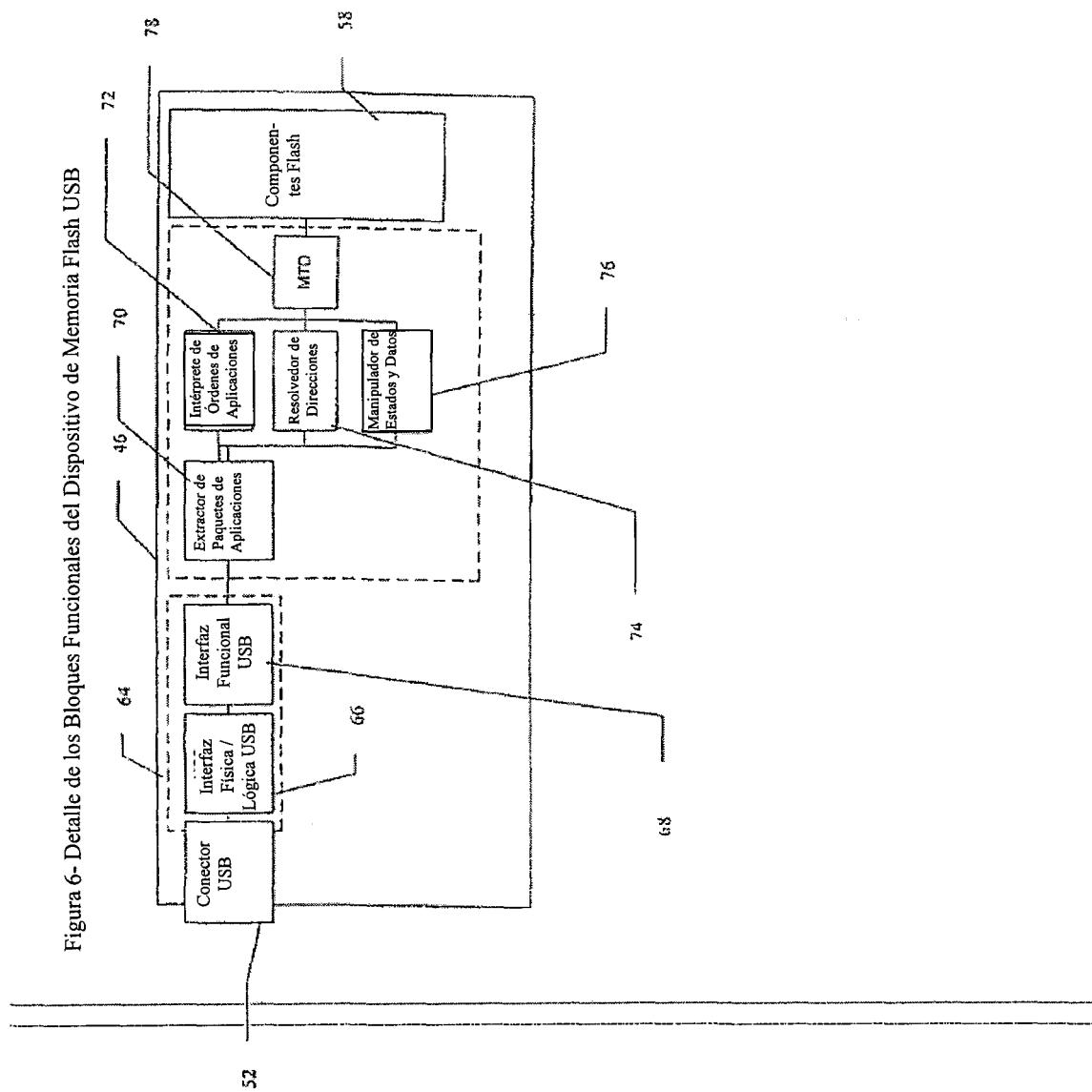

la Fig. 6 es un diagrama de bloques del disco flash USB;

la Fig. 7 es un diagrama de bloques de un paquete de petición de identificación flash;

35 la Fig. 8 es un diagrama de bloques de un paquete de estado de identificación flash;

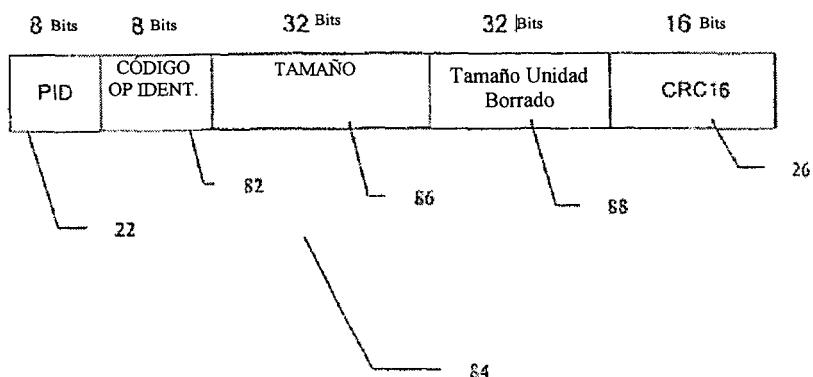

la Fig. 9 es un diagrama de bloques de un paquete de petición de grabación flash;

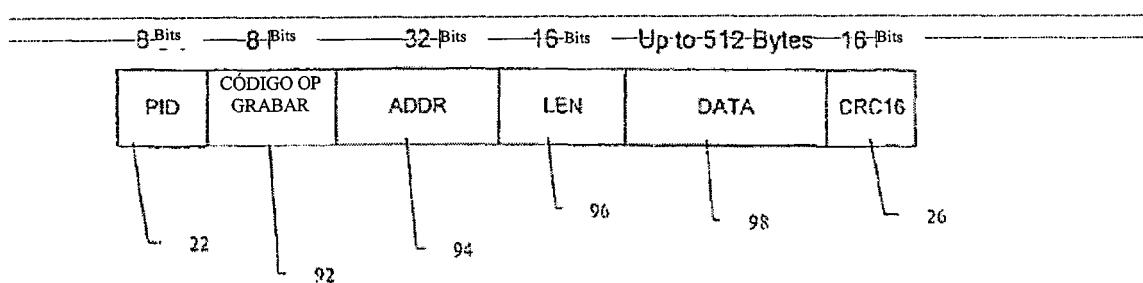

la Fig. 10 es un diagrama de bloques de un paquete de estado de grabación flash;

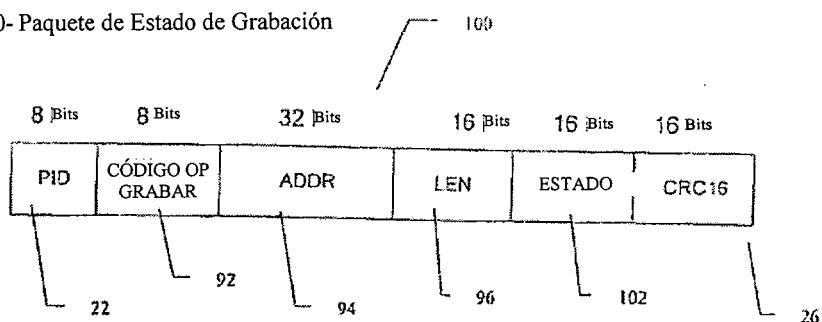

40 la Fig. 11 es un diagrama de bloques de un paquete de petición de lectura flash;

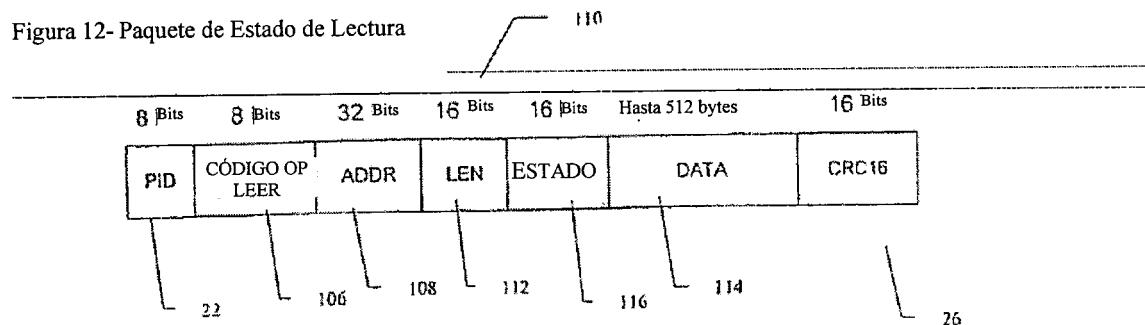

la Fig. 12 es un diagrama de bloques de un paquete de estado de lectura flash;

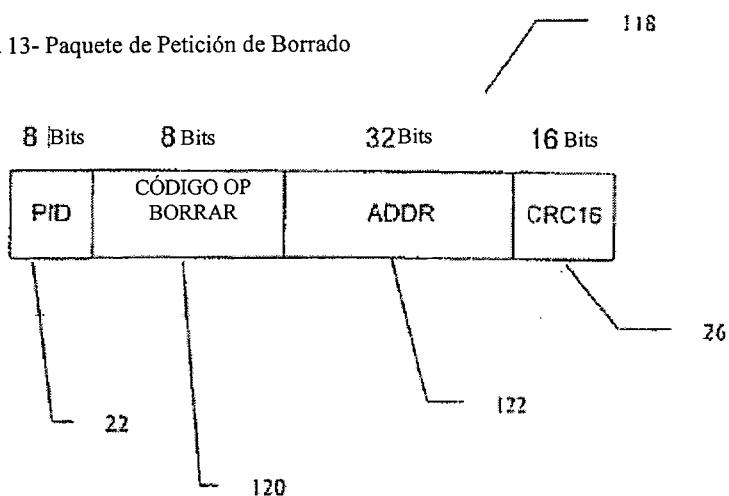

45 la Fig. 13 es un diagrama de bloques de un paquete de petición de borrado flash; y

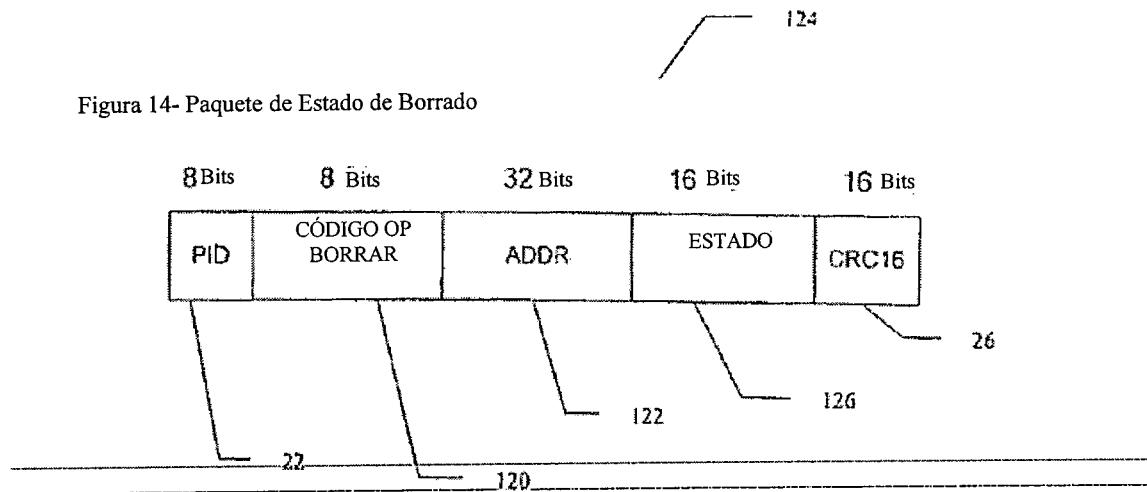

la Fig. 14 es un diagrama de bloques de un paquete de estado de borrado flash.

La presente invención es de un dispositivo de memoria flash que contiene uno o varios módulos flash, siendo la 50 memoria flash proyectada en el espacio de direccionamiento de un ASIC o un controlador que tiene una interfaz eléctrica definida como de USB y una interfaz lógica definida como de USB. Este controlador/ASIC (al que se llama de aquí en adelante “controlador”) soporta la funcionalidad USB según el estándar USB, soportando con ello la enumeración sobre el bus USB, así como la recepción y transmisión de datos a través de tuberías USB hacia y desde puntos terminales de USB. Este controlador también soporta la funcionalidad y el control del dispositivo de memoria flash, así como el procesamiento de paquetes de órdenes y de datos procedentes del controlador del ordenador principal. El controlador del ordenador principal usa uno de varios posibles protocolos, ya sea estándar o bien privados, para indicarle al controlador flash USB la siguiente orden a ejecutar. Así, todo el dispositivo actúa como un dispositivo de almacenamiento no volátil incorporable/separable dinámicamente para la plataforma del ordenador principal.

60 Podrán comprenderse mejor los principios y el funcionamiento de un sistema y dispositivo flash USB según la presente invención haciendo referencia a los dibujos y a la descripción acompañante, entendiéndose que estos dibujos se dan tan sólo con fines ilustrativos y no pretenden ser limitativos.

65 Haciendo ahora referencia a los dibujos, la Figura 5 es un diagrama de bloques de los principales componentes de un sistema y dispositivo de memoria flash según la presente invención. Un sistema de memoria flash 42 incluye una plataforma 44 de ordenador principal como la ilustrada. La plataforma 44 del ordenador principal maneja el dispositivo flash USB 46 como espacio de almacenamiento no volátil.

La plataforma 44 del ordenador principal está conectada al dispositivo flash USB 46 según la presente invención a través de un cable USB 48. La plataforma 44 del ordenador principal se conecta al cable USB 48 a través de un conector USB 50 del ordenador principal, mientras que el dispositivo flash USB 46 se conecta al cable USB 48 a través de un conector 52 de dispositivo flash USB. La plataforma 44 del ordenador principal presenta un controlador 5 USB 54 del ordenador principal para controlar y gestionar todas las transferencias USB por el bus USB.

El dispositivo flash USB 46 presenta un controlador 56 de dispositivo flash USB para controlar los otros componentes del dispositivo flash USB 46 y para establecer una interfaz entre el dispositivo flash USB 46 y el bus USB, el conector de dispositivo flash USB 52 y al menos un módulo de memoria flash 58. El módulo de memoria de flash 58 es preferiblemente un conjunto de módulos de memoria flash 58 en el cual son almacenados los datos.

Siempre que el dispositivo flash USB 46 queda conectado a la plataforma 44 del ordenador principal, tiene lugar un proceso de enumeración USB estándar. En este proceso la plataforma 44 del ordenador principal configura el dispositivo flash USB 46 y el modo de comunicación con el dispositivo flash USB 46. A pesar de que hay muchos 15 métodos distintos para configurar el dispositivo flash USB 46, tan sólo en aras de la claridad y sin pretender constituir con ello limitación alguna, se explica más detalladamente a continuación la presente invención con respecto a un método en el cual la plataforma 44 del ordenador principal emite órdenes y peticiones al dispositivo flash USB 46 a través de un punto terminal. La plataforma 44 del ordenador principal interroga al dispositivo flash USB 46 a través del otro punto terminal con respecto a los cambios de estado, y recibe los correspondientes paquetes si están a la espera 20 de ser recibidos cualesquiera paquetes de este tipo.

La plataforma 44 del ordenador principal solicita servicios del dispositivo flash USB 46 enviando paquetes de petición al controlador 54 del ordenador principal USB. El controlador 54 del ordenador principal USB transmite paquetes por el cable USB 48. Estas peticiones son recibidas por el controlador 56 del dispositivo flash USB cuando el 25 dispositivo flash USB 46 es el dispositivo que está en el punto terminal de la petición. El controlador 56 del dispositivo flash USB ejecuta entonces varias operaciones tales como las de leer, grabar o borrar datos en el (los) módulo(s) de memoria flash 58, o las de soportar funcionalidades USB básicas tales como la configuración y enumeración del dispositivo. El controlador 56 del dispositivo flash USB controla el (los) módulo(s) de memoria flash 58 usando una 30 línea de control 60 para controlar la energía eléctrica del (de los) módulo(s) de memoria flash 58, y también a través de otras varias señales tales como las de habilitación de chip y las señales de lectura y grabación, por ejemplo. El (los) módulo(s) de memoria flash 58 está(n) también conectado(s) al controlador 56 del dispositivo flash USB mediante un bus de direcciones/datos 62. El bus de direcciones/datos 62 transfiere órdenes para ejecutar órdenes de lectura, grabación o borrado en el (los) módulo(s) de memoria flash 58, así como las direcciones y los datos para estas órdenes 35 según haya definido el fabricante del (de los) módulo(s) de memoria flash 58.

A fin de que el dispositivo flash USB 46 notifique a la plataforma 44 del ordenador principal el resultado y el estado para las distintas operaciones peticionadas por la plataforma 44 del ordenador principal, el dispositivo flash USB 46 transmite paquetes de estado usando el “punto final de estado”. Según este procedimiento, la plataforma 44 del ordenador principal efectúa una comprobación (sondeo) para determinar si hay paquetes de estado, y el dispositivo 40 flash USB 46 devuelve un paquete vacío sino están presentes paquetes para nuevos mensajes de estado, o bien devuelve el propio paquete de estado.

Está ilustrada en la Figura 6 una estructura más detallada de los componentes funcionales del dispositivo flash USB 46. El dispositivo flash USB 46 incluye la interfaz física y eléctrica que está definida según el estándar USB y 45 está aquí ilustrada como el conector 52 del dispositivo flash USB y una interfaz de conector 64. El conector 52 del dispositivo flash USB recibe las señales eléctricas del cable USB 48 que conduce las señales eléctricas del controlador del ordenador principal (no ilustrado). Estas señales son entonces pasadas a través de la interfaz de conector 64. Cada milisegundo un cuadro USB es conducido por el bus definido como USB, de forma tal que podrían ser enviados paquetes al dispositivo flash USB 46.

50 La interfaz de conector 64 recibe entonces estos paquetes a través de un primer componente de la interfaz, que es una interfaz física y lógica combinada 66. Una interfaz funcional 68 está diseñada específicamente para recibir paquetes de señal como los definidos en la especificación USB y como los descritos anteriormente con respecto a la Figura 1. Estos paquetes de señal están relacionados tan sólo con aspectos funcionales particulares del dispositivo flash 55 USB 46 que se requieren para el estándar USB, y no tienen relación alguna con la particular aplicación del dispositivo flash USB 46 como disco flash según la presente invención. Estos paquetes de señal y sus respectivos paquetes de datos devueltos les permiten al controlador 54 del ordenador principal USB (no ilustrado) y a la plataforma 44 del ordenador principal (no ilustrada) identificar al dispositivo flash USB 46 y asignar recursos para el dispositivo flash 60 USB 46 por el bus USB. Así, la interfaz funcional 48 solamente soporta la funcionalidad USB que es necesaria para la identificación y el registro del dispositivo flash USB 46 sobre el bus USB.

El dispositivo flash USB 46 también presenta un extractor de paquetes de aplicaciones 70 que extrae los datos de aplicaciones y las órdenes de los paquetes de aplicaciones USB, de tal manera que el extractor de paquetes de aplicaciones 70 soporta solamente los paquetes relacionados con aplicaciones. A continuación, todas las peticiones 65 efectuadas al dispositivo flash USB 46 por la plataforma 44 del ordenador principal (no ilustrada) en forma de órdenes de lectura, grabación, identificación y borrado son interpretadas por un intérprete de órdenes de aplicaciones 72. Para todas aquellas órdenes que impliquen datos o una dirección, tales como las órdenes de lectura, grabación y borrado, un módulo resolutor de direcciones 74 traduce la dirección del espacio de direccionamiento lógico al espacio de

direcccionamiento físico. La plataforma 44 del ordenador principal (no ilustrada) está relacionada con un espacio de direcccionamiento lineal de direcciones lógicas, mientras que el dispositivo flash USB 46 contiene al menos un módulo flash, y preferiblemente una pluralidad de módulos flash 58 que tienen cada uno un espacio de direcccionamiento físico. Así, debe ser llevada a cabo una traducción entre el espacio de direcccionamiento lógico de la plataforma 44 del ordenador principal (no ilustrada) y el espacio de direcccionamiento físico o los espacios de direcccionamiento físico del dispositivo flash USB 46. Hay muchas maneras de implementar una traducción de este tipo que son adecuadas para la presente invención. Un ejemplo de una adecuada implementación de un método de traducción de direcciones está descrito con respecto a la Patente U.S. Nº 5.404.485, que describe un método que es para manejar una memoria flash como un disco flash y es adecuado para ser utilizado con la presente invención.

5 10 Un manipulador de datos 76 manipula los aspectos relativos a datos de cualesquiera órdenes recibidas, siendo los datos transportados a través de la interfaz funcional 78 hacia y desde el (los) módulo(s) flash 58. Opcionalmente y con preferencia, el manipulador de datos 76 ejecuta todos los métodos de detección y corrección de errores. El intérprete de órdenes de aplicaciones 72, el manipulador de datos 76 y el módulo resolvidor de direcciones 74 operan todos ellos con un controlador Memory Technology Driver (MTD) subyacente 78 para grabar, leer o borrar un determinado módulo flash 58 y la deseada dirección en ese módulo flash 58.

15 La plataforma 44 del ordenador principal comprueba si hay cambios de estado en el dispositivo flash USB 46 y lee los paquetes de estado del dispositivo flash USB 46 cuando está disponible un nuevo paquete de estado. Usando estos paquetes de estado, el dispositivo flash USB 46 puede transmitir a la plataforma 44 del ordenador principal los resultados de las distintas órdenes emitidas por la plataforma 44 del ordenador principal en sus peticiones (no ilustrado). Por ejemplo, el paquete de estado de orden de lectura contiene una de las palabras de estado disponibles tales como "éxito", "error" o "dirección no válida", lo cual le permite a la plataforma 44 del ordenador principal determinar el resultado de la orden de lectura (no ilustrado). Análogamente, el paquete de estado de borrado contiene una palabra de estado que indica la consumación del proceso de borrado. El dispositivo flash USB 46 usa un paquete de estado de grabación para notificar a la plataforma 44 del ordenador principal el resultado de la orden de grabación, como por ejemplo si la orden fue ejecutada con éxito o dio lugar a error, y si el dispositivo flash USB 46 está listo para adicionales peticiones de grabación procedentes de la plataforma 44 del ordenador principal.

20 25 La plataforma 44 del ordenador principal comprueba si hay cambios de estado en el dispositivo flash USB 46 y lee los paquetes de estado del dispositivo flash USB 46 cuando está disponible un nuevo paquete de estado. Usando estos paquetes de estado, el dispositivo flash USB 46 puede transmitir a la plataforma 44 del ordenador principal los resultados de las distintas órdenes emitidas por la plataforma 44 del ordenador principal en sus peticiones (no ilustrado). Por ejemplo, el paquete de estado de orden de lectura contiene una de las palabras de estado disponibles tales como "éxito", "error" o "dirección no válida", lo cual le permite a la plataforma 44 del ordenador principal determinar el resultado de la orden de lectura (no ilustrado). Análogamente, el paquete de estado de borrado contiene una palabra de estado que indica la consumación del proceso de borrado. El dispositivo flash USB 46 usa un paquete de estado de grabación para notificar a la plataforma 44 del ordenador principal el resultado de la orden de grabación, como por ejemplo si la orden fue ejecutada con éxito o dio lugar a error, y si el dispositivo flash USB 46 está listo para adicionales peticiones de grabación procedentes de la plataforma 44 del ordenador principal.

30 35 40 Un dispositivo Memory Technology Driver o MTD 78 típicamente contiene rutinas para leer, grabar y borrar el dispositivo flash que es controlado por el controlador que maneja al MTD 78. Adicionalmente, el MTD 78 contiene opcionalmente una rutina de identificación para reconocer el correcto tipo de dispositivo de memoria flash para el cual fue diseñado el MTD 78, con lo que el controlador puede determinar qué MTD deberá ser activado al interactuar con un determinado conjunto de dispositivos de memoria flash. Adicionalmente, una rutina de identificación deberá ser capaz de detectar el tamaño del conjunto de dispositivos de memoria flash, incluyendo el número de dispositivos de memoria flash dentro del conjunto y varias características de la geometría del conjunto flash, tales como la intercalación y la anchura de bus. Esta información le permite posteriormente a la plataforma 44 del ordenador principal determinar el espacio de direcccionamiento y el tamaño de los medios de almacenamiento. La Patente U.S. Nº 5.799.168 describe un ejemplo de un MTD de este tipo para un dispositivo flash.

45 Usando el protocolo y la arquitectura que han sido descritos anteriormente, la plataforma 44 del ordenador principal puede opcionalmente implementar toda aplicación que sea implementable con cualquier dispositivo de memoria flash ordinario con mapas de memoria o mapas de E/S. Por ejemplo, la plataforma 44 del ordenador principal puede dar a un dispositivo de bloques estándar interfaz para cada aplicación, tal como una unidad "de disco duro" como medio de almacenamiento magnético, como se describe en la Patente U.S. Nº 5.404.485 que ha sido descrita anteriormente.

50 55 Como ejemplo de una realización preferida de la presente invención, se describe el funcionamiento de un sistema de ordenador principal conectado a un dispositivo flash USB según la presente invención con respecto a los procesos de identificar, programar, leer y borrar el dispositivo flash. A efectos tan sólo ilustrativos y sin pretender que ello constituya limitación alguna, el ejemplo de dispositivo flash USB tiene un conjunto de dos módulos de memoria flash cada uno de los cuales tiene un tamaño de 64 Mbits. La tabla de traducción de direcciones está dentro del dispositivo flash para que la plataforma del ordenador principal opere con direcciones lógicas. Todas las órdenes y todos los códigos de retorno entre el dispositivo flash y la plataforma del ordenador principal son ejecutados en paquetes de datos USB y son transferidos a través de tuberías de datos USB. Están descritas en la especificación USB la exacta estructura de los paquetes, las tuberías y las temporizaciones.

60 El funcionamiento del ejemplo de dispositivo y sistema según la presente invención es el siguiente: Cuando el dispositivo flash USB es primeramente conectado a la plataforma del ordenador principal, el controlador del ordenador principal USB asigna una dirección al dispositivo flash USB sobre el bus USB, y también asigna recursos como se describe en la especificación USB. El dispositivo flash USB de hecho le pide a la plataforma del ordenador principal que asigne estos recursos, y debe informar a la plataforma del ordenador principal qué cantidad de estos recursos se necesita. Así, el disco flash USB puede opcionalmente soportar menores velocidades de dispositivo si la plataforma del ordenador principal USB ya ha asignado recursos a otros dispositivos.

65 El controlador USB también negocia con los módulos flash y determina el tamaño y el tipo de fabricación de estos módulos. El controlador construye entonces una estructura de identificación que contiene esta información, así como la tabla de traducción y el espacio de direcccionamiento lógico.

Después de que el controlador del ordenador principal USB ha identificado el dispositivo flash USB, la plataforma del ordenador principal a menudo se sube un controlador de cliente USB. El controlador emite una orden de petición de identificación al controlador del ordenador principal USB, haciendo que el controlador transmita un paquete de datos de identificación 80 que está ilustrado en la Figura 7. El paquete de identificación 80 contiene el campo PID 22 y el campo de la suma de verificación 26, como se ha descrito anteriormente para la Figura 2 de la técnica anterior. El paquete de identificación 80 también contiene un código de operación de “identificar” en un campo de código de operación 82. El extractor de paquetes del dispositivo flash USB recibe el paquete de datos de identificación 80 y transfiere el código operativo de la orden de “identificar” al intérprete de órdenes de aplicaciones.

En respuesta a la orden de “identificar”, el dispositivo flash envía entonces un paquete de datos de identificación 84, que está ilustrado en la Figura 8. Además de los campos que están ilustrados en la Figura 7, el paquete de datos de identificación 84 también contiene información acerca del tamaño del dispositivo flash en un campo 86 del tamaño del dispositivo flash, así como información acerca del tamaño de la mínima unidad de borrado para borrar la memoria flash en un campo 88 del tamaño de la unidad de borrado.

Todos los paquetes que se describen en este ejemplo son solamente paquetes de datos que son enviados por el bus USB. Antes de que sea enviado cada paquete de datos, es transmitido un paquete de señal USB que informa al controlador USB acerca de la identidad del punto final de dispositivo al cual debe transmitirse el paquete de datos. Al haber sido recibido con éxito el paquete, el controlador USB emite un paquete ACK USB como el descrito en la especificación USB.

Una vez que los controladores de dispositivo en la plataforma del ordenador principal han recibido este paquete de estado, los controladores pueden empezar a emitir órdenes de lectura y grabación al dispositivo flash USB con las órdenes de aplicación. Cuando es enviada una petición de grabación, es transferido al dispositivo flash USB un paquete de datos USB con el código de operación para la orden de “grabar” y la memoria intermedia que contiene los datos. Están ilustrados en la Figura 9 un paquete de datos de grabación 90 que de nuevo incluye los campos anteriormente ilustrados en la Figura 8, exceptuando el hecho de que el paquete de datos de grabación 90 también incluye un campo de grabación 92 con el código operacional de “grabar”, un campo ADDR 94 con la dirección lógica para la grabación, un campo LEN 96 con la longitud a grabar, y un campo DATA 98 que contiene los datos que de hecho deben ser grabados. El extractor de paquetes extrae el código operacional del paquete de datos de grabación 90 y transfiere este código al intérprete de órdenes de aplicación. La dirección lógica es transferida al módulo resolvenor de direcciones, que traduce esta dirección lógica a una dirección física en uno de los módulos flash. El manipulador de datos opcionalmente calcula los mecanismos de detección y corrección de errores en caso de ser los mismos empleados por el dispositivo flash USB. Una vez que todos los módulos de memoria flash están listos, es enviada una orden de “grabar” al módulo o a los módulos flash que contienen la dirección física, la cual puede opcionalmente abarcar más de un módulo flash, al bloque MTD. El bloque MTD emite entonces una orden de “grabar” por el bus de datos/direcciones que conecta los módulos flash al controlador del dispositivo USB. Una vez concluida la operación y retornado un paquete de estado al MTD, el resultado de la operación es transmitido al controlador del ordenador principal y pasado al controlador de dispositivo en la plataforma del ordenador principal.

Cuando el controlador flash finaliza el proceso de grabación, el controlador indica a la plataforma del ordenador principal que ha cambiado el estado del dispositivo de memoria flash USB a base de enviar un paquete de “estado de grabación” 100 como el que se ilustra en la Figura 10. En lugar del campo de datos 98, el paquete de estado de grabación 100 contiene un campo de estado 102. La plataforma del ordenador principal lee los paquetes de estado del dispositivo de memoria flash, y del paquete de estado de grabación 100 la plataforma del ordenador principal recupera información sobre el estado de consumación de la orden de grabación leyendo el campo de estado 102. En este ejemplo, el dispositivo de memoria flash repite el campo ADDR 94 y el campo LEN 96 a fin de que la plataforma del ordenador principal tenga una referencia sobre la orden específica relacionada con el paquete de estado 100.

Como se muestra en la Figura 11, un paquete de “petición de lectura” 104 contiene el código de operación para la orden de “leer” en un campo de lectura 106 y la dirección lógica del punto deseado en el que el controlador flash deberá efectuar la lectura en un campo ADDR 108. Al recibir esta orden, el controlador flash emite una orden de lectura al bloque MTD, después de que el módulo resolvenor de direcciones ha traducido la dirección contenida en el campo ADDR 108 a una dirección física específica en uno de los componentes flash.

Entonces el controlador flash recibe los datos del dispositivo flash, ya sea después de haber sido emitida la orden de lectura, o bien, si se produjo un error, el controlador flash envía una señal a la plataforma del ordenador principal para indicar que debe ser leído un nuevo paquete de estado. La plataforma del ordenador principal emite una petición de lectura y recibe un paquete de “estado de lectura” 110 como el que se ilustra en la Figura 12. El paquete de estado de lectura 110 contiene la dirección de los datos de lectura en el campo ADDR 108, así como la longitud de los datos de lectura en un campo LEN 112 y los propios datos en un campo de datos 114. El paquete de estado de lectura 110 también presenta la palabra de estado, según la cual la operación fue consumada, en un campo de estado 116. La operación de lectura puede ser consumada con muchas distintas situaciones de estado tales como las de éxito, fracaso, error detectado, dirección no válida, longitud no válida y así sucesivamente.

Cuando la plataforma del ordenador principal necesita borrar una unidad de borrado en el dispositivo flash, la plataforma del ordenador principal emite un paquete de “petición de borrado” 118 que está ilustrado en la Figura 13. Este paquete contiene el código de operación de “borrar” en un campo de borrado 120 y la dirección lógica de

## ES 2 241 593 T5

la unidad de borrado en un campo ADDR 122. Al recibir una petición de este tipo, el controlador flash traduce la dirección lógica a una dirección de unidad de borrado física en uno de los espacios de direccionamiento físico de los módulos flash, y emite una orden de borrado al bloque MTD.

- 5        El proceso de borrado lleva en general más tiempo que un proceso de lectura o grabación. Cuando ha sido finalizado este proceso de borrado, el controlador notifica a la plataforma del ordenador principal que está listo para ser transmitido un nuevo paquete de estado. El controlador transmite entonces un paquete de “estado de borrado” 124 como el que se ilustra en la Figura 14. El paquete de estado de borrado 124 contiene la dirección de la unidad borrada en el campo ADDR 122, proporcionando con ello a la plataforma del ordenador principal una referencia a las peticiones de borrado. El estado según el cual fue consumada la operación es aportado en un campo de estado 126.

- 10

15

20

25

30

35

40

45

50

55

60

65

**REIVINDICACIONES**

1. Dispositivo de memoria flash USB (46) para conectar a un bus (48) definido como USB, comprendiendo el dispositivo de memoria flash (46):

5 (a) al menos un módulo de memoria flash (58);

10 (b) un único conector (52) que es un conector USB adaptado para la conexión a un bus definido como USB y para enviar y recibir paquetes definidos como USB a y desde dicho bus (48) definido como USB; y

15 (c) un controlador USB (56) que interactúa con un ordenador principal (44) a través de dicho conector USB (52) y al menos ejecuta una operación de las operaciones de lectura y de grabación en dicho módulo de memoria flash (58) que es al menos uno de acuerdo con dichos paquetes definidos como USB;

20 15 en el que dicho dispositivo se proporciona como una unidad integral con dicho único conector y dicho controlador (56) comprende un intérprete de órdenes (72) que está adaptado para interpretar órdenes de lectura y grabación recibidas como códigos de operación extraídos de paquetes de datos definidos como USB (90, 104) a través de dicho conector USB (52) convirtiéndolas en acciones de lectura y grabación para dicho módulo de memoria flash (58) que es al menos uno y un módulo resolvelor de direcciones (74) que está adaptado para traducir direcciones lógicas (94) desde dichos paquetes de datos definidos como USB (90, 104) hacia una dirección física en uno o más de dicho módulo de memoria flash (58) que es al menos uno.

25 20 25 2. Dispositivo de memoria flash USB (46) según la reivindicación 1, en el que dicho módulo resolvelor de direcciones (74) está adaptado para recibir dichos paquetes de datos definidos como USB (90, 104) y para resolver las direcciones (94, 108) contenidas en dichos paquetes de datos definidos como USB (90, 104), siendo dichas direcciones (94, 108) enviadas a dicho controlador USB (56), de forma tal que dichas órdenes de lectura y grabación son ejecutadas según dichas direcciones (94, 108).

30 30 3. Dispositivo de memoria flash USB (46) según la reivindicación 2, en el que, si dicha orden es una orden de grabación para grabar datos (98) en dicho módulo de memoria flash (58) que es al menos uno y si dicha dirección (94) es una dirección lógica para grabar dichos datos (98), dicho módulo resolvelor de direcciones (74) resuelve dicha dirección lógica (94) transformándola en una dirección física de dicho módulo de memoria flash (58) que es al menos uno.

35 40 4. Dispositivo de memoria flash USB (46) según la reivindicación 2, en el que, si dicha orden es una orden de lectura para leer datos (114) en dicho módulo de memoria flash (58) que es al menos uno y si dicha dirección (108) es una dirección lógica para leer dichos datos (114), dicho módulo resolvelor de direcciones (74) resuelve dicha dirección lógica (108) transformándola en una dirección física de dicho módulo de memoria flash (58) que es al menos uno.

40 5. Dispositivo de memoria flash USB (46) según la reivindicación 2, que comprende además:

45 un manipulador de datos (76) para ejecutar una rutina de detección y corrección de errores para dicho módulo de memoria flash (58) que es al menos uno.

50 45 6. Dispositivo de memoria flash USB (46) según la reivindicación 5, que comprende además:

55 un manipulador de estados (76) para recibir dichos paquetes definidos como USB (90, 104) y para enviar paquetes de estado (100, 110) relativos a un estado de dicho módulo de memoria flash (58) que es al menos uno según dichos paquetes definidos como USB (90, 104).

60 55 7. Dispositivo de memoria flash USB (46) según la reivindicación 6, que comprende además:

55 60 un controlador Memory Technology Driver MTD (78) para recibir una orden de grabación y la dirección física de dicho módulo de memoria flash (58) que es al menos uno y para ejecutar dicha orden de grabación en dicha dirección física.

65 65 8. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones 1 a 7, en el que dicho dispositivo (46) actúa como un dispositivo de almacenamiento no volátil incorporable/separable dinámicamente para dicho ordenador principal (44).

9. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones anteriores en el que dicho controlador USB (56) está implementado como un único circuito integrado.

65 65 10. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones anteriores en el que dicho controlador USB (56) interpreta las órdenes de grabación y extrae datos (98) a ser grabados desde dichos paquetes de datos definidos como USB (90).

# ES 2 241 593 T5

11. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones anteriores, en el que dicho bus definido como USB está conectado a dicho ordenador principal (44) y en el que dicho ordenador principal (44) da órdenes a dicho controlador USB (56) usando un protocolo privado.

- 5 12. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones anteriores, en el que dicho bus definido como USB está conectado a dicho ordenador principal (44) y en el que dicho ordenador principal (44) da órdenes a dicho controlador USB (56) usando un protocolo estándar.

- 10 13. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones anteriores, que comprende un bus de direcciones/datos (62) que interconecta a dicho controlador USB (56) y a dicho módulo de memoria flash (58) que es al menos uno.

- 15 14. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones anteriores, en el que dicho controlador USB (56) negocia con dicho módulo de memoria flash (58) que es al menos uno para determinar al menos una característica de la geometría del módulo flash.

- 15 15. Dispositivo de memoria flash USB (46) según la reivindicación 14, en el que dicha característica que es al menos una comprende un tamaño.

- 20 16. Dispositivo de memoria flash USB (46) según la reivindicación 14 o la reivindicación 15, en el que dicha característica que es al menos una comprende un tipo de fabricación.

- 25 17. Dispositivo de memoria flash USB (46) según la reivindicación 16, en el que dicho controlador USB (56) usa dicho tipo determinado para determinar un Memory Technology Driver MTD (78) para ser usado para dicha memoria flash (58).

18. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones 14 a 17, en el que dicho controlador USB (56) notifica a dicho ordenador principal (44) que está listo después de dicha negociación.

- 30 19. Dispositivo de memoria flash USB (46) según la reivindicación 14, en el que dicha característica que es al menos una comprende un tamaño y un tipo de fabricación.

- 35 20. Dispositivo de memoria flash USB (46) según la reivindicación 19, en el que dicho determinado tamaño y tipo de fabricación son usados para generar una tabla de traducción y un espacio de direccionamiento.

21. Dispositivo de memoria flash USB (46) según la reivindicación 20, en el que dicho controlador USB (56) genera dicha tabla de traducción y dicho espacio de direccionamiento.

- 40 22. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones anteriores, en el que dicho controlador (56) incluye una pluralidad de líneas (60) de señales de habilitación de chip para su unión a una pluralidad de módulos de memoria flash (58).

- 45 23. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones anteriores, en el que dicho conector (52) está unido a dicho controlador (56) mediante una interfaz física/lógica combinada (66).

24. Dispositivo de memoria flash USB (46) según la reivindicación 23, en el que dicha interfaz física/lógica combinada (66) es parte de dicho controlador (56).

- 50 25. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones anteriores, en el que dicho módulo de memoria flash (58) que es al menos uno comprende una pluralidad de módulos de memoria flash (58).

26. Dispositivo de memoria flash USB según cualquiera de las reivindicaciones anteriores, en el que dicho controlador USB comprende además:

- 55 (i) una interfaz funcional adaptada para recibir dichos paquetes definidos como USB, de forma tal que si uno de dichos paquetes definidos como USB es un paquete de señal USB, dicha interfaz funcional actúa en dicho paquete de señal; y

- 60 (ii) un extractor de paquetes que está conectado en serie después de dicha interfaz funcional y adaptado para recibir dichos paquetes definidos como USB, extrayendo dicho extractor de paquetes al menos dichas órdenes de dichos paquetes definidos como USB;

- en el que dicho dispositivo es incorporable/separable dinámicamente.

- 65 27. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones 1 a 26, que comprende además:

- (d) medios (66, 68) para proporcionar una funcionalidad de interfaz USB a dicho conector (52);

# ES 2 241 593 T5

comprendiendo dicho controlador (56) además:

(i) medios (70) para extraer órdenes de memoria flash de dichos paquetes definidos como USB (90, 104) recibidos a través de dicho conector (52); y

5 (ii) medios (72, 74, 78) para controlar dichos medios de memoria flash en respuesta a dichas órdenes.

28. Dispositivo de memoria flash USB (46) según cualquiera de las reivindicaciones 1 a 26, que comprende:

10 (d) medios (66, 68) para proporcionar una funcionalidad de interfaz USB a dicho conector (52);

y en el que dicho controlador (56) además comprende:

15 (i) un extractor de órdenes (70) que sirve para extraer órdenes de memoria flash de dichos paquetes de datos definidos como USB (90, 104) recibidos a través de dicho conector (52); y

(ii) un controlador Memory Technology Driver (78) que sirve para controlar a dichos medios de memoria en respuesta a dichas órdenes.

20

25

30

35

40

45

50

55

60

65

# ES 2 241 593 T5

Figura 1- Estructura del Paquete de Señal USB de la Técnica Anterior

Figura 2- Estructura del Paquete de Datos USB de la Técnica Anterior

Figura 3- Paquete de Establecimiento de Comunicación USB de la Técnica Anterior

Figura 4- Bloques Funcionales de un Dispositivo USB de la Técnica Anterior

Figura 5- Sistema de Ordenador Principal con un Dispositivo de Memoria Flash USB

Figura 6- Detalle de los Bloques Funcionales del Dispositivo de Memoria Flash USB

# ES 2 241 593 T5

Figura 7- Paquete de Petición de Identificación Flash

Figura 8- Paquete de Datos de Identificación Flash

Figura 9- Paquete de Petición de Grabación

# ES 2 241 593 T5

Figura 10- Paquete de Estado de Grabación

Figura 11- Paquete de Petición de Lectura

Figura 12- Paquete de Estado de Lectura

# ES 2 241 593 T5

Figura 13- Paquete de Petición de Borrado

Figura 14- Paquete de Estado de Borrado