(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-129769

(P2005-129769A)

(43) 公開日 平成17年5月19日(2005.5.19)

(51) Int.Cl.<sup>7</sup>

**H01L 21/20**

**G02F 1/1368**

**H01L 21/268**

**H01L 21/336**

**H01L 29/786**

F 1

H01L 21/20

G02F 1/1368

H01L 21/268

H01L 29/78

H01L 29/786

テーマコード(参考)

2 H092

5 F052

5 F110

審査請求 未請求 請求項の数 20 O L (全 26 頁)

(21) 出願番号

特願2003-364539 (P2003-364539)

(22) 出願日

平成15年10月24日 (2003.10.24)

(71) 出願人 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(71) 出願人 502356528

株式会社 日立ディスプレイズ

千葉県茂原市早野3300番地

(74) 代理人 100093506

弁理士 小野寺 洋二

(72) 発明者 武田 一男

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 佐藤 健史

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】半導体薄膜の改質方法、改質した半導体薄膜とその評価方法、およびこの半導体薄膜で形成した薄膜トランジスタ、並びにこの薄膜トランジスタを用いて構成した回路を有する画像表示装置

## (57) 【要約】

【課題】多結晶半導体をレーザアニール法によって形成する方法に於いて、多結晶半導体膜の表面ラフネスを低減する。

【解決手段】レーザアニール装置の光学系に非晶質シリコン半導体薄膜を成膜した基板の走査方向における照射光強度分布を、高エネルギーの光強度側の微結晶しきい値以上のエネルギー領域と表層のみ融合するエネルギー領域を有する分布として制御する透過率分布フィルタを設置し、通常のラインビームを利用するエキシマレーザアニール法または位相シフトストライプマスク法またはSLS法に適用する事によって、それぞれの方法で得られる多結晶の表面突起の高さを低減する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

ラインビーム形状のレーザ光を該ラインビームの長軸方向と交叉する方向で走査しながら非晶質半導体薄膜に照射して結晶化することにより該非晶質半導体薄膜を多結晶半導体薄膜に改質する半導体薄膜の改質方法であって、

前記ラインビーム内の光強度分布を一定の透過率面内分布に制御する透過率分布フィルタを透過させることによって前記結晶化を行うことを特徴とする半導体薄膜の改質方法。

**【請求項 2】**

前記透過率分布フィルタの前記透過率面内分布は、前記レーザ光の透過率が前記ラインビームの短軸方向で異なる領域からなることを特徴とする請求項 1 に記載の半導体薄膜の改質方法。 10

**【請求項 3】**

前記透過率分布フィルタの前記透過率面内分布は、前記レーザ光の透過率が異なる領域が前記ラインビームの短軸方向で交互に分布している分布形状であることを特徴とする請求項 2 に記載の半導体薄膜の改質方法。

**【請求項 4】**

レーザ光を走査しながら非晶質半導体薄膜に照射して結晶化することにより該非晶質半導体薄膜を多結晶半導体薄膜に改質する半導体薄膜の改質方法であって、

前記レーザ光の前記走査方向における照射レーザ光内の光強度分布を、改質された前記多結晶半導体薄膜が厚さ方向で全体が溶融するエネルギーを有する領域と該多結晶半導体薄膜が厚さ方向で表層のみが溶融するエネルギーを有する領域とからなる強度分布に制御して、結晶化を行うことを特徴とする半導体薄膜の改質方法。 20

**【請求項 5】**

前記レーザ光を一定の透過率面内分布を有する透過率分布フィルタと位相シフトマスクとを透過させることで、前記照射レーザ光内の光強度分布を制御することを特徴とする請求項 4 に記載の半導体薄膜の改質方法。

**【請求項 6】**

前記透過率分布フィルタの前記透過率面内分布は、前記レーザ光の透過率が前記ラインビームの短軸方向で異なる領域からなることを特徴とする請求項 5 に記載の半導体薄膜の改質方法。 30

**【請求項 7】**

前記透過率分布フィルタの前記透過率面内分布は、前記レーザ光の透過率が異なる領域が前記ラインビームの短軸方向で交互に分布している分布形状であることを特徴とする請求項 5 に記載の半導体薄膜の改質方法。

**【請求項 8】**

レーザ光を走査しながら非晶質半導体薄膜に照射して結晶化することにより該非晶質半導体薄膜を多結晶半導体薄膜に改質する半導体薄膜の改質方法であって、

照射レーザビーム内の光強度分布を、一定の透過率面内分布を有する透過率分布フィルタとスリットマスクとを透過させることで前記照射レーザ光内の光強度分布を制御することを特徴とする請求項 4 に記載の半導体薄膜の改質方法。 40

**【請求項 9】**

前記透過率分布フィルタは、前記レーザ光の透過率が前記ラインビームの短軸方向で異なる領域からなることを特徴とする請求項 8 に記載の半導体薄膜の改質方法。

**【請求項 10】**

レーザ光を走査しながら非晶質半導体薄膜に照射して結晶化することにより該非晶質半導体薄膜を多結晶半導体薄膜に改質するレーザアニール装置であって、

前記ラインビーム内の光強度分布を一定の透過率面内分布に制御する透過率分布フィルタを装置内光学系の結像面近傍に設置することによって、照射ビーム強度分布プロファイルを制御して前記結晶化を行うことを特徴とするレーザアニール装置。

**【請求項 11】**

10

20

30

40

50

ラインビーム形状のレーザ光を該ラインビームの長手方向と交叉する方向で走査しながら非晶質半導体薄膜に照射して結晶化することにより改質された多結晶半導体薄膜であって、

前記改質された多結晶半導体薄膜の結晶粒は一方向に横方向成長した形状を有し、且つ前記結晶粒の粒界と粒内とに突起が存在し、且つ前記突起の前記一方向の配列の位置が変化する周期が1種類のみ存在することを特徴とする多結晶半導体膜。

【請求項12】

ラインビーム形状のレーザ光を該ラインビームの長手方向と交叉する方向で走査しながら非晶質半導体薄膜に照射して結晶化することにより改質された多結晶半導体薄膜であって、

10

前記改質された多結晶半導体薄膜の結晶粒は面内二方向に横方向成長した形状を有し、且つ前記結晶粒の粒界と粒内とに突起が存在し、且つ前記突起の前記方向の配列の位置が変化する周期が各方向で1種類のみ存在することを特徴とする多結晶半導体薄膜。

【請求項13】

前記多結晶半導体薄膜は、その粒界のサイズが、その一方向が1.5μm以上あり、且つ前記一方向とほぼ直交する他方向の粒界のサイズが0.5μm以下である結晶粒を含み、表面の前記突起の高さが数μm角の面積内でのPV値が70nm以下であることを特徴とする請求項11に記載の多結晶半導体薄膜。

【請求項14】

前記多結晶半導体薄膜は、その粒界のサイズが、その一方向が1.5μm以上あり、且つ前記一方向とほぼ直交する他方向の粒界のサイズも1.5μm以上ある結晶粒を含み、表面の前記突起がほぼ直交する直線上に配列されていると共に、該突起の高さが数μm角の面積内でPV値が70nm以下であることを特徴とする請求項12に記載の多結晶半導体膜。

20

【請求項15】

透明基板上の半導体膜を評価する半導体膜評価装置であって、

前記半導体膜にレーザ光を照射し反射率と透過率とを測定し、「1-(反射率+透過率)」の値を計測することを特徴とする半導体薄膜評価装置。

【請求項16】

多結晶半導体膜を評価する多結晶半導体薄膜評価装置であって、

前記多結晶半導体薄膜の光回折パターン面上の回折スポットの強度および散乱光強度の角度分布を計測する事によって多結晶の表面ラフネスと粒径の評価を行うことを特徴とする多結晶半導体薄膜評価装置。

30

【請求項17】

粒界の一方向サイズが1.5μm以上あり、且つ前記一方向とほぼ直交する粒界の他方向サイズが0.5μm以下である結晶粒を含むと共に、表面に直線状に配列された突起を有し、該突起の高さが数μm角の面積内でのPV値が70nm以下である多結晶半導体薄膜で形成したことを特徴とする薄膜トランジスタ。

【請求項18】

粒界の一方向サイズが1.5μm以上あり、且つ前記一方向とほぼ直交する粒界の他方向サイズも1.5μm以上ある結晶粒を含むと共に、表面にほぼ直交する直線上に配列された突起を有し、PV値で表した該突起の高さが数μm角の面積内で70nm以下である多結晶半導体膜を含むことを特徴とする薄膜トランジスタ。

40

【請求項19】

粒界の一方向サイズが1.5μm以上あり、且つ前記一方向とほぼ直交する粒界の他方向サイズが0.5μm以下である結晶粒を含むと共に、表面にほぼ直交する直線上に配列された突起を有し、PV値で表した該突起の高さが数μm角の面積内で70nm以下である多結晶半導体薄膜で形成した薄膜トランジスタ回路を含むことを特徴とする画像表示装置。

【請求項20】

50

粒界の一方方向サイズが  $1.5 \mu m$  以上あり、且つ前記一方方向とほぼ直交する粒界の他方向サイズも  $1.5 \mu m$  以上ある結晶粒を含むと共に、表面にほぼ直交する直線上に配列された突起を有し、PV値で表した該突起の高さが数  $\mu m$  角の面積内で  $70 nm$  以下である多結晶半導体膜を含むことを特徴とする画像表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、非晶質半導体薄膜を多結晶半導体薄膜に改質するための半導体薄膜の改質方法および改質した半導体薄膜の評価方法、その半導体薄膜で形成した薄膜トランジスタ並びにこの薄膜トランジスタを用いて構成した回路を有するフラットパネル型の画像表示装置を含む半導体装置に好適なものである。

10

【背景技術】

【0002】

例えば、液晶表示装置等のフラットパネル型の画像表示装置は、ガラスを好適とする絶縁基板（以下、単に基板とも称する）上に成膜した半導体薄膜に作り込んだ画素回路や駆動回路を有する。画素回路や駆動回路を構成する駆動素子としては薄膜トランジスタ（Thin Film Transistor : TFT）が多く用いられる。この薄膜トランジスタの活性層として、近年は非晶質半導体薄膜（典型的にはアモルファスシリコン半導体薄膜、あるいはa-Si膜とも称する）に代えて多結晶半導体薄膜（同じく典型的にはポリシリコン半導体薄膜、あるいはpoly-Si膜とも称する）を用いることで高精細で高画質の画像表示を得ることができる。

20

【0003】

薄膜トランジスタの活性層として用いる半導体薄膜をシリコン半導体薄膜を例として説明する。この活性層としての半導体薄膜を多結晶シリコン半導体薄膜とすることが非晶質シリコン半導体薄膜を用いることより優れた特性を得ることができる。その理由は、多結晶シリコン半導体薄膜は、非晶質シリコン半導体薄膜に比較してキャリア（nチャネルでは電子、pチャネルでは正孔）の移動度が高いことを挙げることができ、その結果、セルサイズ（画素サイズ）を小さくできることによる高精細化が可能となる。さらに、通常のポリシリコン半導体薄膜で形成した薄膜トランジスタの形成には、 $1000^{\circ}C$  以上の高温プロセスが必要であるが、レーザ光によるシリコン層のみのアニールにより半導体薄膜を担持する基板が高温にならない低温ポリシリコン半導体薄膜形成技術では、安価なガラス基板の使用が可能な低温プロセスにおいて、移動度の高い薄膜トランジスタTFTの形成が可能となる。

30

【0004】

通常、多結晶シリコン半導体薄膜の結晶の粒径が大きいほど移動度が高いので、大粒径の多結晶シリコン半導体薄膜を形成する方法としてさまざまな技術が提案してきた。一般的には、「特許文献1」に示されるように、パルスレーザ光をラインビーム状に整形し、その強度分布のプロファイルを台形としてラインビームの短軸方向に短軸幅の約  $1/20$  程度のピッチで1ショット単位でずらしながら非晶質シリコン半導体薄膜にパルス照射の繰り返しを行う方法がとられる。非晶質シリコン半導体薄膜は照射されたレーザ光を吸収することによって温度が上昇し、溶けることで温度が低下する。このプロセスに伴ってシリコン半導体薄膜の結晶化が起こり、非晶質シリコン半導体薄膜は多結晶シリコン半導体薄膜へ変化する（ここで、これを改質と称する）。多結晶シリコン半導体薄膜の平均粒径は照射したレーザ光のエネルギー密度に依存して変化するが、非晶質シリコン半導体薄膜の結晶化に必要な最低エネルギー密度以上では、エネルギー密度を上げていくと粒径が大きくなるが、ある閾値以上では粒径が平均  $100 nm$ （ナノメートル）以下の微結晶になる。そのため、この微結晶の閾値以下のエネルギー密度で照射を行わなければならない。

40

【0005】

これに対して「特許文献2」では、パルスレーザの照射領域の強度分布のプロファイル

50

を台形として、最大強度を非晶質シリコン半導体薄膜が微結晶の多結晶シリコン半導体薄膜に変化する閾値以上の値を有する強度分布プロファイルとして、当該プロファイルの裾の強度分布で大粒径化する方法を開示している。

#### 【0006】

以上は、平均粒径が  $1 \mu m$  (ミクロンメートル) 程度の技術であり、例えば膜厚  $50 nm$  の非晶質シリコン半導体薄膜を多結晶シリコン半導体薄膜に変化する場合に  $0.3 \mu m$  以上の粒径となるレーザエネルギー密度のマージンは、約  $10\%$  程度であるが、そのうち半分程度は突起の PV 値が  $70 nm$  以上になる。なお、PV 値とは測定範囲内の最高値と最低値との差で定義される。

#### 【0007】

シリコン半導体薄膜の大粒径化技術の別の方法として、光強度分布を制御する方法がある。この従来技術の一つとしては、「特許文献3」に開示されている様に、逐次的横方向結晶成長法 (SLS 法) と呼ばれる方法がある。この方法は、面内方向にレーザ光の強度分布をミクロンメートルのサイズの複数のビーム素片に細切れにすることにより面内方向に温度勾配を形成し、強制的に横方向の結晶成長を促す方法である。この方法では、複数の結晶粒の結晶成長の向きがお互いにぶつかり会う境界において表面に突起が形成される。

#### 【0008】

この突起が形成される位置は、各ビーム素片の光強度のピーク位置に対応する。なぜならば、この位置が最も温度が高くなるので当該ピーク位置の両側から結晶化が該ピーク位置に向かって進行し、ピーク位置において結晶成長がぶつかるからである。この突起は前述の台形プロファイルのラインビーム整形したレーザ光照射による多結晶シリコン半導体薄膜の突起より高く、PV 値で  $100 nm$  以上になる場合がある。

#### 【0009】

「特許文献4」と「特許文献7」で提案された方法は、「特許文献2」に開示される方法の改良技術であり、レーザ光を最初に高強度のエネルギーで照射した後、それよりも低い強度のエネルギーで照射する強度分布制御により結晶化することで結晶粒を大きくする方法である。この分布制御の方法については、焦点位置と基板表面との位置を変化させることで非対称的な強度分布が得られるとしている。但し、この方法により非対称的な分布形状の変化が得られる因果関係は開示されていない。これに対して、「特許文献5」では同様に焦点位置と基板表面との位置を変化させることで、台形形状から逆釣鐘形状になるとしており、「特許文献4」の結果と矛盾する。「特許文献6」にも、同様の照射分布で大粒径の結晶が得られるとしているが、レーザ光のビーム形成方法に関する記述はない。

#### 【0010】

上記した従来技術は、レーザ光としてパルスレーザを用いたものである。この様なパルスレーザを用いたシリコン半導体薄膜の結晶化方法すなわち、ここで言う改質方法では、結晶化後の多結晶シリコン半導体薄膜の表面に突起が形成されるため、その表面凹凸が大きい。そのため、この半導体薄膜に例えば薄膜トランジスタを作り込む場合には、多結晶シリコン半導体薄膜上に形成するゲート絶縁膜を厚くする必要がある。その結果、ゲート絶縁膜の膜厚に反比例してトランジスタのオン電流が小さくなるという問題がある。

#### 【0011】

台形プロファイルとしたレーザ光のラインビーム照射で形成された多結晶シリコン薄膜の突起を低減するための改良された方法として、レーザアニールを複数回行い、それぞれ異なるエネルギー密度で照射する方法によって、突起を低減する方法が「特許文献8」に開示されている。特許文献8に開示された内容は次のとおりである。すなわち、非晶質シリコン半導体薄膜の成膜時に含まれる水素がレーザアニールによって急激に放出されて膜表面が荒れる。このとき、結晶化が起こる閾値値以下の低エネルギー密度のレーザ光を照射し、結晶化アニールの前に水素を放出させることによって膜表面のあれを防止するというものである。

#### 【0012】

10

20

30

40

50

また、SLS法における突起低減方法として、レーザ光照射で結晶化アニールを行った後に完全溶融のエネルギー密度の25%から75%の値で2回目にレーザ光照射することにより、突起を低減する方法が「特許文献9」に開示されている。

#### 【0013】

しかし、以上のように方法には以下のような欠点がある。すなわち、レーザ光を多段で照射するため、基板上を何回もレーザ光を走査する必要があり、アニール工程に要する時間が長くなるという欠点がある。さらに、複数のエネルギー密度をそれぞれ異なる照射時間で複数走査で行う場合は、パルスレーザの繰り返し周波数が一定であるために照射時間の相違は走査速度を変えることになり、半導体薄膜を成膜した基板上における各走査のレーザ光の照射パルスを重ねた場合、突起低減効果が基板上でまだらになるという欠点がある。

10

#### 【0014】

突起低減が効果的な方法を用いて多結晶シリコン半導体薄膜を形成しても、レーザ出力の時間変動や結晶化前の非晶質シリコン薄膜厚の面内変動が存在するために、結晶化後に突起の検査を行い、突起が高い領域、言い換れば表面ラフネスが大きい領域を検出して、その領域を再度結晶化するなどの工程を含めなければ、基板全面で管理基準以下の表面ラフネスとすることはできない。このような表面ラフネスを計測する公知技術としては、原子間力顕微鏡による評価方法がある。しかし、この方法では10μm×10μmの微小領域を評価するのに少なくとも数分程度を要するので、基板全面の表面ラフネスを評価することは時間的に不可能である。

20

#### 【0015】

この表面ラフネスを高速に評価する方法としては表面光沢度（反射率）で評価する方法が「特許文献10」に示されている。この方法は、反射率で評価するので多結晶シリコン半導体薄膜の厚さやガラス基板と多結晶シリコン半導体薄膜の間の下地膜の厚さによる干渉の影響が存在するという欠点がある。多結晶シリコン半導体薄膜の粒径の面内分布を高速に評価する方法に関しては、「特許文献11」に開示されているように、散乱光の角度分布の広がり幅で粒径を計測する方法が知られている。

30

【特許文献1】特開昭64-76715号公報

【特許文献2】特開平9-246183号公報

【特許文献3】WO97/45827号公報

【特許文献4】特開平10-64815号公報

【特許文献5】特開平10-312963号公報

【特許文献6】特開2000-11417号公報

【特許文献7】特開2002-313724号公報

【特許文献8】特開2000-353664号公報

【特許文献9】WO01/71791号公報

【特許文献10】特開平11-274078号公報

【特許文献11】特開2003-109902号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0016】

非晶質シリコン半導体薄膜をレーザアニールして結晶化した多結晶シリコン半導体薄膜の表面に形成される突起を低減するために、非晶質シリコン半導体薄膜を複数のエネルギー密度のレーザ光で照射する方法では、照射するレーザ光のエネルギー密度ごとに走査回数が多くなり、結晶化工程の時間が長くなるという欠点がある。さらに、走査ピッチの異なる複数の走査の重ね合わせによる突起低減効果が、基板上（ガラス等の基板に成膜された半導体薄膜上、以下同じ）でまだらになるという欠点がある。このことを図を用いて説明する。

40

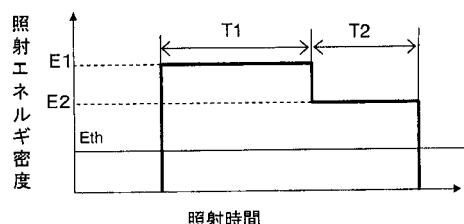

#### 【0017】

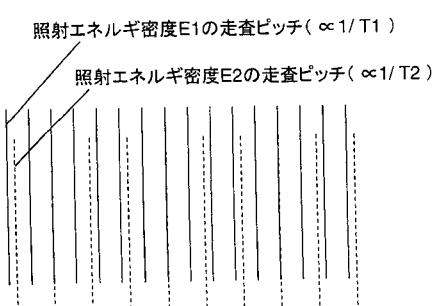

図22はレーザ光照射エネルギー密度の時間変化の説明図である。図22の縦軸におけるE<sub>th</sub>は結晶化が起こる下限の閾値を示す。また、図23は図22の時間変化を複数のレ

50

レーザ光走査で実施する場合に起こる副作用の説明図であり、実線はレーザ光の照射エネルギー密度  $E_1$  の走査ピッチ、破線はレーザ光の照射エネルギー密度  $E_2$  の走査ピッチを示す。ここでは、図 2-2 に示す様に、基板の同一箇所を 1 回目のエネルギー密度を  $E_1$ 、時間  $T_1$  の間で照射し、2 回目のエネルギー密度は  $E_2$ 、時間  $T_2$  の間で照射する条件で基板全体を走査しながらレーザ光を照射する場合を考える。パルスレーザの繰り返し周波数は一定であるので、1 回目の走査のピッチは  $1/T_1$  に比例した値 ( $1/T_1$ ) であり、2 回目の走査ピッチは  $1/T_2$  に比例した値 ( $1/T_2$ ) となる。そうすると、上記 2 種類の走査ピッチの重ね合わせを考えたとき、図 2-3 に示した様に基板上での重ね合わせがまだら状に不均一になる。この影響によって、突起の平均高さはまだら状に面内変動した分布となる。

10

## 【0018】

したがって、このような周期的な突起の高い領域の発生が無い突起低減方法およびそれを可能とするレーザアニール方法を用いた半導体薄膜の製造方法およびその製造装置を提供することが本発明の第 1 の目的である。また、本発明の製造方法で製造した半導体薄膜を提供することが本発明の第 2 の目的である。

## 【0019】

さらに、大粒径化でかつ突起を低減する方法で結晶化を行ったとしても、レーザ出力の時間変動や非晶質シリコン半導体薄膜厚の基板面内変動によって、粒径および突起の高さが管理基準以内で形成されているとは限らない。したがって、基板全面で粒径の他に突起の高さの全数検査が可能な計測方法で製造した半導体薄膜の特性を評価する評価方法及びその評価装置を提供することが本発明の第 3 の目的である。

20

## 【0020】

そして、本発明の半導体薄膜で形成した薄膜トランジスタを提供することが本発明の第 4 の目的である。そして、この薄膜トランジスタを用いて構成した回路を備えた画像表示装置を提供することが本発明の第 5 の目的である。

## 【課題を解決するための手段】

## 【0021】

本発明の半導体薄膜の製造方法は、レーザ光の照射による溶融と凝固を行う、所謂レーザアニール手法を用いて非晶質シリコン半導体薄膜を多結晶シリコン半導体薄膜化するにあたり、多結晶化したシリコン半導体薄膜の表面ラフネスを低減するために多段のエネルギー密度照射でアニールする方法である。このアニールする方法では、レーザ光透過率の面内分布を制御した透過率分布フィルタを照射光学系に設置し、レーザ光を走査方向と直交する方向に長軸方向を有するラインビームに整形する。そして、ラインビームに整形したレーザ光の走査方向である該ラインビームの短軸方向の光強度分布を制御することで、走査方向において複数のエネルギー密度による照射を 1 回の走査で行うことを主要な特徴とする。

30

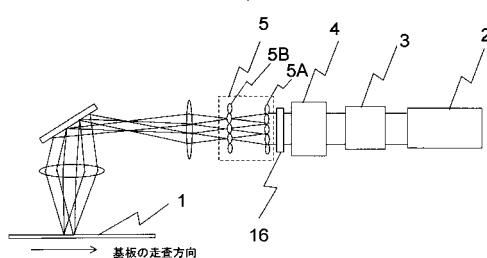

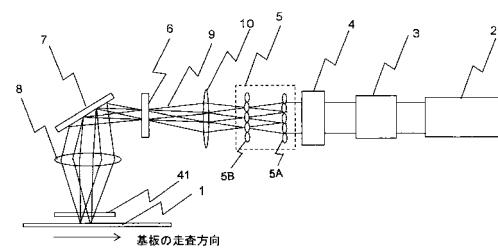

## 【0022】

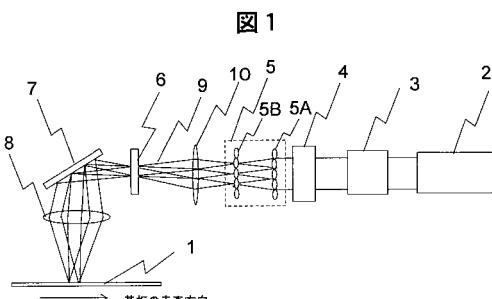

本発明による半導体薄膜の改質方法と、改質した半導体薄膜の評価方法の特徴を、後述する実施例の説明にも用いる各図を参照して説明する。なお、ここでの説明と後述する実施例での説明とが重複する箇所もあることを予め明示しておく。図 1 は本発明による半導体薄膜の製造方法を実現するためのレーザアニール光学系である。図 1 に示したレーザアニール装置の光学系は、短軸ホモジナイザ 5 と長軸ホモジナイザ 4 によって、強度が均一なラインビーム分布を形成している。短軸ホモジナイザ 5 は対向する一組のシリンドリカルレンズアレイ 5A と 5B で構成される。この短軸ホモジナイザ 5 にはレーザ光源 2 からのレーザ光をアッテネータ 3 および長軸ホモジナイザ 4 を透過して入射させる。アッテネータ 3 はレーザ光源 2 から発生したレーザビームが所定のエネルギーを有するように調節するためのものである。

40

## 【0023】

短軸ホモジナイザ 5 より後に設置されたレンズ 10 によって短軸ホモジナイザ 5 内のシリンドリカルレンズアレイ 5A と 5B の各レンズ素子を透過したレーザ光 9 が一次結像面

50

で重ね合わされる。この1次結像面に重ね合わされるのは、短軸ホモジナイザ5の前段のシリンドリカルレンズアレイ5Aの各レンズ素子内部の光強度分布である。シリンドリカルレンズアレイ5Aの各レンズ素子が小さく、数が多いほど一次結像面における光強度分布が均一になる。

#### 【0024】

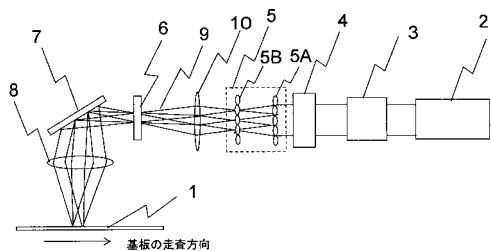

この一次結像面の位置に透過率の面内分布を形成したフィルタ(透過率分布フィルタ)6を設置する。この透過率分布フィルタ6は透明石英製であり、図2に示す様に表面に反射率コーティングを施すことによって、透過率の面内分布を±0.5%程度の精度で制御したフィルタとなっている。なお、透過率分布フィルタ6の詳細構成は実施例の項で説明する。一次結像面の光強度分布は、このフィルタの透過率分布によって±0.5%程度の精度で制御され、この光強度分布を有するレーザ光が、ミラー7とレンズ8によって半導体薄膜が成膜された基板1の表面に縮小投影される。以上の短軸分布制御法を一次結像面制御方法と呼ぶことにする。

#### 【0025】

次に、短軸方向の強度分布を制御する別の方法を、図5および図6を参照して説明する。短軸方向の強度分布を制御する別の方法は、短軸ホモジナイザ5の前段で、該短軸ホモジナイザ5を構成するシリンドリカルレンズアレイ5Aの各レンズ素子内部の光強度分布を透過率分布フィルタ16で制御することで、合成された分布の形状を制御するようにしたものである。図5に示す様に、透過率分布フィルタ16は短軸ホモジナイザ5の直前に設置する。この場合の透過率分布フィルタ16は、図6に示す様に、その透過率分布がシリンドリカルレンズアレイ5Aに対応して反射率制御コーティング膜をストライプ状に形成して、各レンズ素子の短軸方向の光強度分布を制御する様に設置する。最終的に、基板1の表面上での光強度分布形状は各レンズ素子内の強度分布の重ね合わせの分布になる。図6はレンズ素子3個分のストライプを示している。この方法をホモジナイザ素子内分布制御方法と呼ぶことにする。なお、透過率分布フィルタ16の詳細構成は実施例の項で説明する。

#### 【0026】

上記した2種類の短軸分布制御方法は、レーザ光をラインビーム形状に整形するレーザアニール装置における光学系および結晶化方法の改良であるが、ラインビームではないレーザアニール方法にも適用可能である。以下に特許文献1に開示されているようなSLS法への本発明の適用方法を説明する。

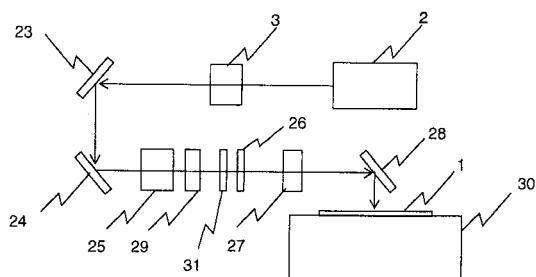

#### 【0027】

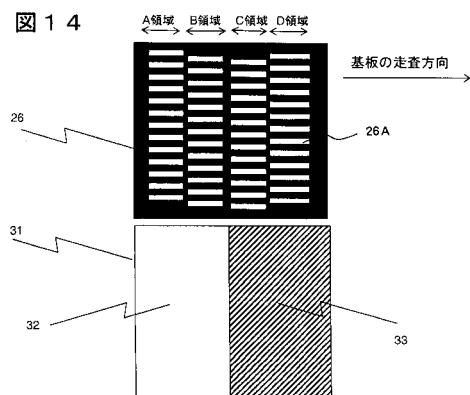

一般的なSLS結晶化装置は、図13に示したように、光源2とアッテネータ3、ホモジナイザ25、レンズ29、マスク26、イメージングレンズ27、そして非晶質シリコン半導体薄膜を成膜した基板1が置かれる移動ステージ30から構成される。アッテネータ3とホモジナイザ25間、及びイメージングレンズ27と移動ステージ30間には入射したレーザ光を所定の角度で反射してレーザ光の方向を変化させるためのミラー23、24、28が各々配置される。ホモジナイザ25はレーザ光のビーム整形と整形したレーザビーム内光強度を均一にするための光学系であり、レンズ29との組み合わせによってマスク26の位置に均一なビーム内強度分布を形成するようにしてある。

#### 【0028】

このマスク26の位置は、図1に示した光学系の一次結像面に対応する。このマスク26によって、基板1の表面上に光強度の明暗のパターンを形成し、面内方向に温度勾配を形成することで、横方向(走査方向と直交する方向、幅方向)への結晶成長を促して大粒径の結晶を形成する方法である。本発明の透過率面内分布制御フィルタすなわち透過率分布フィルタ31は、下記の図14で説明するように、マスク26の近傍に設置することによって、当該マスク内の各パターンを透過する光強度を制御する。

#### 【0029】

図14に図13におけるマスクパターンとフィルタ透過率パターンとの組み合わせの一例を示す。マスクの開口部すなわちスリット26Aは基板1の走査方向に長軸を有する。

10

20

30

40

50

マスクパターンの構成は次のとおりである。A領域とB領域はお互いに走査方向に対してスリット26Aの間隔の配列周期の位相が1/2周期だけずらされ、同様にC領域とD領域も互いに位相を走査方向に対して1/2周期だけずらし、且つA領域とC領域との周期位相のずれを互いに1/2周期とは異なる様に例えば1/4周期の様に設定する。この様に設定する理由は、非晶質シリコン半導体薄膜を多結晶シリコン半導体薄膜に改質したときのA領域とB領域のパターンの照射によって形成される突起の位置と、C領域とD領域のパターンの照射によって形成される突起の位置とを相対的にずらすためである。

#### 【0030】

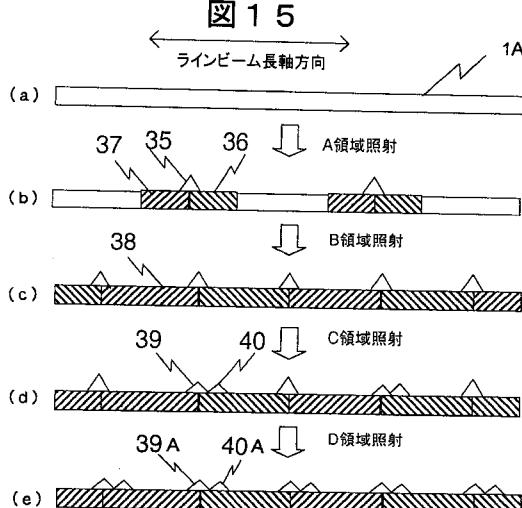

上記マスク26に対応する透過率分布フィルタ31は、反射防止膜を形成した領域32と反射膜を形成した領域33の透過率の差が10%以上有する。この透過率分布フィルタ31をマスク26の近傍に設置する。設置場所は、マスク26の設置位置より上流側でも下流側でも良い。パルスレーザの繰り返し発振周波数に対して走査ピッチを調整し、マスクパターンの各領域が1ショットだけ照射されるようとする。1回の走査中の照射の過程を図15を参照して説明する。図15(a)の基板上に成膜した非晶質シリコン膜1AにA領域のパターンが1ショットだけ照射されると、照射されていない領域が残る。この照射されていない領域はA領域のマスクされている部分に対応しており、結晶化していない部分である。

#### 【0031】

図15(b)のように、結晶化した領域であるA領域には、2つの横方向に成長した結晶粒36と37が、突起35が形成された粒界を挟んで存在する形状となる。次のショット時はB領域のパターンが同一エネルギー密度で1ショット照射される(図15(c))。このショットにより先のショットで結晶化していなかった領域は、両側の結晶を種にして結晶が中心に向かって成長する。この結果、突起間距離が平均粒界サイズとなる多結晶シリコン半導体薄膜が形成される。この後、図15(d)に示したC領域パターン、図15(e)に示したD領域パターンが10%以上低いエネルギーのレーザ光で照射される。

#### 【0032】

この場合、突起が形成される位置が異なる様に10%以上低いエネルギー密度で照射される。このエネルギー密度のレーザ光では、シリコン半導体薄膜の厚さ方向全体を溶融することが不可能であり、シリコン半導体薄膜の表層のみ溶融されるので、粒界を形成することができず、シリコン半導体薄膜の表層に突起のみが形成される。この結果、図15(d)のように粒界位置ではない場所に低い突起40が形成される。もともと高い突起は低い突起の形成のためにシリコン半導体薄膜が移動するために、B領域照射後まで形成されていた突起39の高さは低くなる。以上の様に、本発明は突起を低減するために多段のエネルギー密度によるSLS法を1回の走査で行うことを特徴とするものである。

#### 【0033】

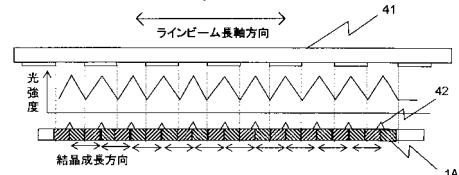

さらに、上記SLS法とは異なる方法で横方向の結晶成長を促進させる方法がある。これは位相シフトマスクを利用して結晶化を行う方法である。この技術は特願2002-284735に記述した様に、SLS法では周期的スリットパターンのマスクを利用するのに対して、この位相シフトマスクを利用して結晶化を行う方法は、図8に示したように、位相シフトストライプパターンのマスク(位相シフトストライプマスク)41を基板上に成膜した非晶質シリコン膜1Aの近傍に設置し、レーザ光の照射強度をそのシリコン膜面上で変調させることによって、基板全面に横方向成長の結晶を走査しながら形成する技術である。この技術はSLS法の様にマスクと試料の間にレンズを用いる必要が無く、数100mmの長さのラインビームに適用できる長所がある。この位相シフトストライプ法に本発明の透過率面内分布フィルタを適用して突起を低減する方法を以下に説明する。

#### 【0034】

図8は、基板1の直上に設置した位相シフトストライプマスク41をパルスレーザ光が透過して基板上に成膜した非晶質シリコン膜1Aに照射した時の光強度分布とシリコン粒の結晶成長方向との関係を示している。位相シフトストライプマスク41のストライプパターンの周期は約3μmである。1ショットで照射領域全面が横方向に成長した結晶粒が

10

20

30

30

40

50

形成される。結晶の成長方向はSLS法と同様にレーザ光強度の低い方から高い方へ向かって成長する。それゆえ、突起42はレーザ光強度のピーク位置に対応して形成される。

#### 【0035】

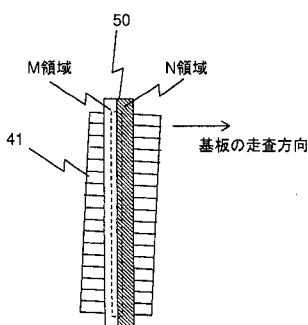

図7は位相シフトストライプ法に透過率分布フィルタを適用する場合の結晶化装置の光学系であり、ラインビームを用いる通常のエキシマレーザアニール装置を利用することができる。さらに本発明の透過率分布フィルタ6を設置する場所も図1や図5と同じである。図7はフィルタ6の設置場所を図1と同じ場所とした場合の装置構成を示している。位相シフトストライプマスク41は基板1の直上に設置する。図9は基板1上から照射領域を見た図であり、基板1の走査方向と位相シフトストライプマスク41のパターン方向とラインビーム50の関係を示している。位相シフトストライプマスク41のストライプパターンは基板1の走査方向に対してある一定の角度を成している。これは、パルスレーザの繰り返し発振間隔の間に位相シフトストライプと基板1との相対的なシフト量が走査方向におけるストライプパターンの1周期以内となり、かつ1ショット毎にずれる様にするためである。これによって1ショット毎に突起が形成する配列の位置がずれることになる。

10

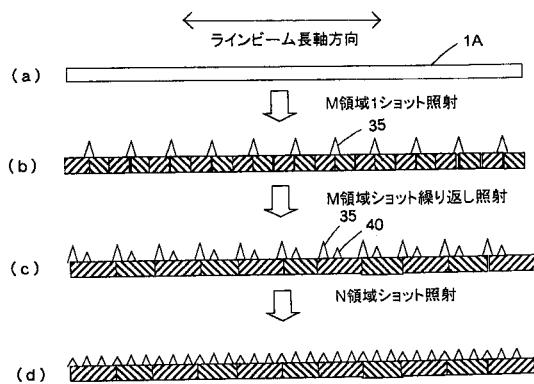

#### 【0036】

ラインビーム50の短軸方向の強度分布は、透過率分布フィルタ6によって、図10に示したM領域よりN領域のエネルギー密度が10%以上低くなる様に設定する。このように設定した場合の結晶化の進行状況を図10を参照して説明する。図10(a)の基板上に成膜した非晶質シリコン膜1Aに対してM領域の1ショット照射により、照射領域内は一括で横方向に成長した結晶粒が形成される。この時の平均結晶粒は突起間隔の約1/2となる。このM領域のショットを繰り返すことにより、多結晶膜厚方向に全体の溶融現象が繰り返されることによって、成長方向の平均粒径は突起間隔と等しくなる(図10(b))。但し、突起の形成位置は最後のショットで形成した突起35が最も高く、この位置が主に粒界となっている。それ以前のショットで形成された突起40は低いまま残っている場合が多い(図10(c))。N領域の照射は膜厚全体を溶融するエネルギーより低いので粒界を形成することはできないが、低い突起のみを形成することが可能である。この低い突起形成において、M領域の最後のショットで形成された高い突起35は、N領域照射による突起形成のための表層のシリコンの流動によって低くなる(図10(d))。

20

#### 【0037】

次に、上記のような突起低減方法を用いて結晶化を行っても、レーザ出力の時間変動や結晶化前の非晶質シリコン半導体薄膜の膜厚に面内変動が存在する。そのために、結晶化後に検査(表面ラフネス評価)を行って、高い突起が存在する領域が検出されたときに、その領域を再度結晶化することにより、基板全面において突起の高さを管理基準以下にすることができる。

30

#### 【0038】

ここでは、先に従来技術でも述べた様に、多結晶シリコン半導体薄膜の膜厚の干渉の影響を受けない表面ラフネスの評価方法を説明する。本発明の表面ラフネス評価方法は、多結晶シリコン半導体薄膜の透過率と反射率との測定によって、「1 - (反射率 + 透過率)」から「全散乱断面積 + 吸收断面積」を求め、これによって表面ラフネスを評価するものである。この方法では、干渉による影響は反射率と透過率との和の値で相殺される。すなわち、干渉の影響で反射率が増大する分だけ、透過率の減少となるので、反射率と透過率の和は干渉の影響を受けない。非晶質シリコン半導体膜に本計測を適用する場合は、表面ラフネスが小さいので散乱断面積は無視できて、吸收断面積から非晶質シリコン半導体膜の膜厚を干渉の影響を受けずに評価することが可能である。

40

#### 【0039】

吸收断面積は多結晶シリコン半導体薄膜と単結晶シリコン半導体薄膜と多重散乱による多重吸収の効果が無視できる薄膜では同じと考える事ができ、多結晶シリコン半導体薄膜においては平均膜厚と波長に依存する量となる。膜厚分布変動は1メートル四方の大型基板において±5%程度であり一定とみなす事ができる。全散乱断面積は、粒径に依存する

50

部分と表面ラフネスに依存する部分とがある。これを粒径評価方法と組み合わせることによって、表面ラフネスを計測することが可能となる。すなわち、本発明では、粒径評価による粒径と「全散乱断面積 + 吸収断面積」の2種類の量を基板全体で測定することによって、表面ラフネスを評価する方法をとる。

#### 【0040】

突起の高さを評価する上記以外の方法を以下に説明する。この方法は、前述したSLS法や位相シフトストライプマスク法で形成した多結晶シリコン半導体薄膜の突起の配列周期とその高さを評価する方法に適している。この方法では、光回折パターンの突起由来の回折スポットの強度で突起の高さを評価するものである。すなわち、回折スポットの強度が強いほど突起の高さが高いとして評価する方法である。

10

#### 【0041】

また、本発明では、上記の改質方法で製造した多結晶シリコン半導体薄膜を用いることで、移動度の高い薄膜トランジスタを得、この薄膜トランジスタを用いて高速かつ高精細の画像表示装置を構成する。

#### 【発明の効果】

#### 【0042】

本発明の半導体薄膜の改質方法によれば、複数のエネルギー密度のレーザ光照射を1回の走査で実現できる。さらに、複数の走査で行っていた複数のエネルギー密度のレーザ光照射による突起低減効果で、走査間のパルス間隔の違いによる基板面内でまだらに発生する現象が低減し、表面ラフネスがPV値70nm以上の領域がなくなる。また、何らかのトラブルで表面ラフネスが70nm以上になったとしても、全面の全数検査によって70nm以上の領域を検出し、その領域を再度結晶化することにより当該突起の高さを低減することで最終的に突起を70nm以下に低減できる。突起が70nmのポリシリコン膜を用いるTFTでは、絶縁破壊不良が発生しないためのゲート絶縁膜の厚さとして、一般的に用いられるテトラエチルオルソシリケート(TEOS)膜の場合は、110nm以下にする事が出来る。

20

#### 【0043】

また、本発明の薄膜トランジスタは高い移動度が得られ、この薄膜トランジスタを用いた画像表示装置によれば駆動回路や画素回路の薄膜トランジスタを高速かつ高精細化でき、表示品質が向上する。

30

#### 【発明を実施するための最良の形態】

#### 【0044】

本発明は、透過率面内分布を有するフィルタを利用することにより走査方向のレーザ光のビーム断面の光強度分布を多段にすることを可能とし、これによって照射エネルギー密度を多段に照射することで突起低減をする方法を1回のレーザアニールの走査で可能とした。その製造方法に関する実施例と突起を評価する実施例を示す。

#### 【実施例1】

#### 【0045】

図1は本発明の半導体改質方法を実現するレーザアニール装置の光学系の一例を説明する模式図である。本実施例は、通常用いられるエキシマレーザアニール装置に本発明の透過率分布制御フィルタを適用したものである。図1において、レーザ2はラムダフィジックス社製STEEL1000型XeC1エキシマレーザである。出力されるレーザ光の波長は308nm、パルス時間幅は約27ナノ秒(ns)、繰り返し周波数は300ヘルツ(Hz)、パルスエネルギーは1J/パルスである。このレーザアニール装置は日本製鋼所製であり、Microlas社製の長軸ホモジナイザ光学系4と短軸ホモジナイザ光学系5とシリンドリカルレンズ10およびシリンドリカルレンズ8とミラー7によって、レーザ光を長軸365mm、短軸400μmのラインビームに整形して基板1に照射する構成となっている。基板1に照射するレーザ光の光強度分布を制御するために、1次結像面に透過率分布フィルタ6を設置している。この透過率分布フィルタ6は、以下に図2を用いて説明する様に、石英板に反射率を制御した表面コーティングを施して、透過率分布を制

40

50

御したものである。

【0046】

図2は図1における透過率分布フィルタ6の表面の構成例を説明する模式的図である。透過率分布フィルタ6の領域11は領域12より透過率が相対的に高い領域である。具体的には、領域11の表面には反射率1%のコーティングを施し、領域12の表面には反射率11%のコーティングを施してある。そして、裏面全体には反射率1%のコーティングを施したものであり、結果的に領域11の透過率を98%、領域12の透過率を88%以下としたものである。

【0047】

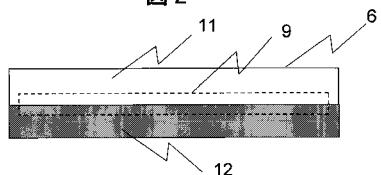

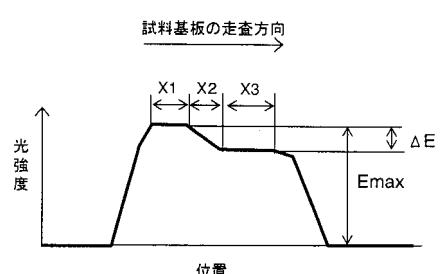

図3は図1の透過率分布フィルタ6の設置によって得た短軸方向の光強度分布の説明図である。図3に示した分布の領域X1の最大の照射エネルギー強度は可変アッテネータ3によって調節するが、その下限は基板1に成膜したアモルファスシリコン半導体薄膜が高エネルギー照射密度側の微結晶になる閾値以上に設定し、調節の上限は分布の後半の領域X3のエネルギー密度は少なくとも表層が溶融するエネルギー密度は、透過率分布フィルタによりEの値が0.1Emax以上である様に調節される。この場合、領域X1で生じた高エネルギー側の微結晶が領域X2のエネルギー密度照射で融合して大きな粒径になり、領域X3で表層のみ溶融させることによって突起を低減させる。

【0048】

図2の領域11と領域12の透過率の差が13%のフィルタで実験を行った結果、平均粒径が0.5μm以上となる照射エネルギー密度のマージンは、領域X1と領域X3の幅が等しい条件に固定した場合12%であり。突起の高さはアッテネータ透過率が上記マージンをカバーする80%から99%の範囲ではすべて70nm以下となつた。

【0049】

図4は透過率分布フィルタを用いないで複数回走査でレーザ光の照射エネルギー密度を変えた場合のシリコン半導体結晶の暗視野光学顕微鏡写真である。ここでは、アッテネータの透過率を変えて2回の走査を行って結晶化した。1回目の結晶化の走査のピッチ間隔が24μmであり、2回目の結晶化の走査ピッチは14μmである。図4(a)は、1回目のアッテネータ透過率が94%であり、2回目は1回目より透過率を6%低下させて照射したものである。この条件では、2回目の照射エネルギー密度も高エネルギー密度側の微結晶の閾値を超えて微結晶領域になっており、微結晶筋が14μmピッチで観察される。分布の裾の部分はエネルギー密度が低いので部分的に微結晶が融合し図4の写真では白っぽい領域となって観察される。

【0050】

図4(b)は1回目のアッテネータ透過率が88%であり、2回目は1回目より透過率を6%低下させて照射したものである。写真の中で黒く見える領域が、1回目の照射で高エネルギー密度側の微結晶が発生して1回目のピッチに相当する24μmの周期となったものを、2回目の低エネルギー密度の照射によって微結晶が融合して粒径が大きくなつた領域である。

【0051】

この様に、透過率分布フィルタを用いないで、多段の走査、かつ多段のエネルギー密度でレーザ光を照射する場合は、エネルギー密度によってシリコン半導体薄膜の試料には異なる走査ピッチ形状が現れることになる。これに対し、透過率分布フィルタを用いた場合は、試料上に現れる走査ピッチは1種類のみとなる。本実施例では、走査ピッチは走査速度できまり、レーザ2の繰り返し発振の1/300秒の時間間隔の移動量に等しい。

【実施例2】

【0052】

次に、実施例2を図5と図6を用いて説明する。図5は本発明の半導体製造方法を実現するレーザアニール装置の光学系の他例を説明する模式図である。図6は図5における透過率分布フィルタ6の表面の構成例を説明する模式的図である。この実施例は、図1で説明した実施例1におけるレーザ2とレーザアニール装置からなる構成は基本的に等しい。

10

20

30

40

50

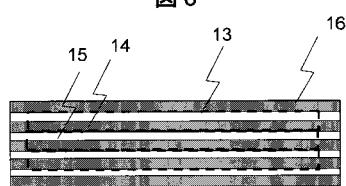

本実施例が実施例 1 の構成と異なる点は、透過率分布フィルタ 16 の設置場所が短軸ホモジナイザ 5 の直前であることと、透過率分布フィルタ 16 の透過率分布が図 6 に示すように短軸ホモジナイザ 5 内の各シリンドリカルレンズアレイ素子の内部の強度分布を制御する様にストライプ状になっていることである。なお、短軸ホモジナイザ 5 のシリンドリカルレンズアレイ 5A のレンズ素子数が 5 個の場合であって、さらにそのうち破線 13 で囲んだ様に 3 個分の広さのレーザビームが入射している場合を図示している。図 1 の実施例と同様に、実際の数は 9 個で構成されており、破線 13 で囲んだ領域すなわちレーザ透過領域は、9 個分以内の領域に設定されている。

### 【0053】

図 6 において、破線 13 に囲んだ各領域（図 6 では 3 個の領域）が各レンズ素子の内部に光が透過する領域であり、この個々の領域内部の強度分布を透過率の異なる領域 14 と領域 15 で示される 2 種類のストライプ領域で制御する。試料基板の表面上の照射光強度分布は短軸ホモジナイザ 5 のレンズアレイ 5A の内部の強度分布の合成になるので、この透過率分布フィルタ 16 は、領域 14 と領域 15 の透過率の差で強度分布の段差分布を制御する。

### 【実施例 3】

### 【0054】

以下に位相シフトストライプマスクによる結晶化方法に透過率分布フィルタを適用した実施例を以下に説明する。図 7 は本発明の半導体製造方法を実現するレーザアニール装置の光学系のさらに他例を説明する模式図であり、位相シフトストライプ法によるレーザアニール装置の光学系を示す。本実施例は、前記した実施例 1 及び実施例 2 のラインビームによる通常のエキシマレーザアニール装置を利用したものである。透過率分布フィルタ 6 を設置する場所は、図 1 や図 5 と同じ位置とすることができる。図 7 では透過率分布フィルタの設置場所を図 1 と同じ場合とした。本実施例では、基板 1 の近傍に位相シフトストライプマスク 41 を設置した。このマスクの設置場所は 1 次結像面でも良い。

### 【0055】

図 8 は位相シフトストライプマスクを用いてシリコン半導体薄膜の結晶化を行う方法の説明図である。位相シフトストライプマスク 41 は、図 8 に示すように、波長 308 nm に対して位相がほぼ 180 度シフトするパターンを 3 μm ピッチで石英基板に凹凸ストライプパターンを形成したものであり、ラインビームに整形したレーザ光の長軸方向とはほぼ垂直方向になるようにストライプパターンを設けてある。そして、基板上に成膜した非晶質シリコン膜 1A の表面から 0.9 mm だけ離して設置する。他の構成は図 1 と同様である。位相シフトマスク透過後の強度分布は、パルスエキシマレーザはホモジナイザ光学系によって種々の位相の光が混在しているため、180 度差の位相シフトマスク透過後の強度分布の谷の強度はゼロとはならない。このため、この最低強度を結晶化のしきい値以上にすれば 1 ショットで非晶質シリコンが残ることは無い。

### 【0056】

図 8 は基板上に成膜した非晶質シリコン膜 1A の直上に設置した位相シフトストライプマスク 41 をパルスレーザ光が透過して基板上の非晶質シリコン薄膜 1A に照射した時の光強度分布と試料の結晶成長との関係を示している。位相シフトストライプマスク 41 のストライプパターンの周期は約 3 μm である。図示したように、本実施例では 1 ショットでレンズ光の照射領域全面が横方向に成長した結晶粒が形成される。結晶の成長方向は SLS 法と同様にレーザ光強度の低い方から高い方へ向かって成長し、レーザ光強度のピーク位置に突起 42 が形成される。

### 【0057】

図 9 は透過率分布フィルタと位相シフトストライプマスクのパターンと基板走査方向の説明図で、基板 1 上からレーザ光照射領域を見た図である。位相シフトストライプパターンと基板走査方向との成す角度は 1 度と設定し、走査速度は 7.2 mm / 秒とした。この場合はパルス間の移動ピッチは約 24 μm となる。また、パルス間の位相シフトストライプパターンと基板 1 との相対的なシフト量が、走査方向におけるストライプパターンの 1

10

20

30

40

50

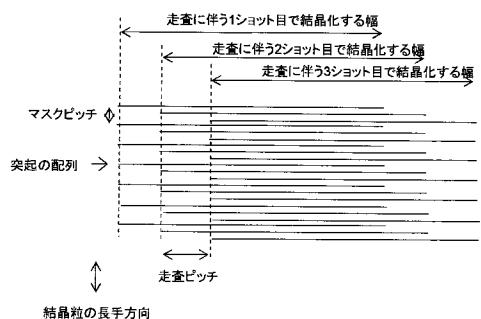

周期以内で約  $0.5 \mu m$  となる。この量だけ 1 ショット毎に突起が形成する配列の位置がずれることになる。図 25 に突起の配列の位置が変化する周期と走査ピッチとの関係を示した。走査にともなって 1 ショットで結晶化する領域が、走査ピッチ毎にずれる。このとき突起の配列もずれる。したがって、突起の配列の位置が変化する周期は、走査ピッチに等しい。結晶が成長する方向はマスクパターンのピッチの方向であり、走査方向とほぼ直交する方向である。

#### 【0058】

透過率分布フィルタは、図 9 に示すように、破線で示したラインビームに平行にかつ透過率のことなる M 領域と N 領域の境界がラインビーム内になる様に設置する。この透過率分布フィルタは石英製であり、M 領域の表面には反射率 1 % のコーティング、N 領域の表面には反射率 11 % 以上のコーティング、裏面全体に反射率 1 % のコーティングを施したものである。これによって、M 領域と N 領域のエネルギー密度差は 10 % 以上となっている。

#### 【0059】

図 10 は透過率分布フィルタを位相シフトストライプマスクを用いた場合のシリコン半導体薄膜の結晶化の説明図である。上記した構成で、図 10 (a) の基板上に成膜した非晶質シリコン膜 1 A に対して M 領域の 1 ショット照射により、照射領域内は一括で横方向に成長した結晶粒が形成される。この時の平均結晶粒は突起間隔の約 1/2 となる (図 10 (b))。基板の走査に伴い M 領域を通過中の複数ショットにより、多結晶膜厚方向に全体の溶融現象が繰り返されることによって、成長方向の平均粒径は突起間隔と等しくなる (図 10 (c))。但し、突起の形成位置は最後のショットで形成した突起 35 が最も高く、この位置が主に粒界となっている。それ以前のショットで形成された突起 40 は低いまま残っている場合が多い。N 領域の照射は膜厚全体を溶融するエネルギーより低いので粒界を形成することはできないが、低い突起のみを形成することが可能である。

#### 【0060】

この低い突起形成において、M 領域の最後のショットで形成された高い突起 35 は、N 領域照射による突起形成のための表層のシリコンの流動によって低くなる (図 10 (d))。図 10 (d) はアッテネータ 3 の透過率を 90 % として結晶化を行った基板上のシリコン半導体薄膜を模式的に示す。結晶の粒界に存在する突起と結晶粒内に存在する突起とが存在する結晶となる。

しかも突起の配列の位置が変化する周期は 1 回の走査ピッチで決まるので約  $24 \mu m$  の周期で 1 種類だけ形成されている多結晶膜が得られた。

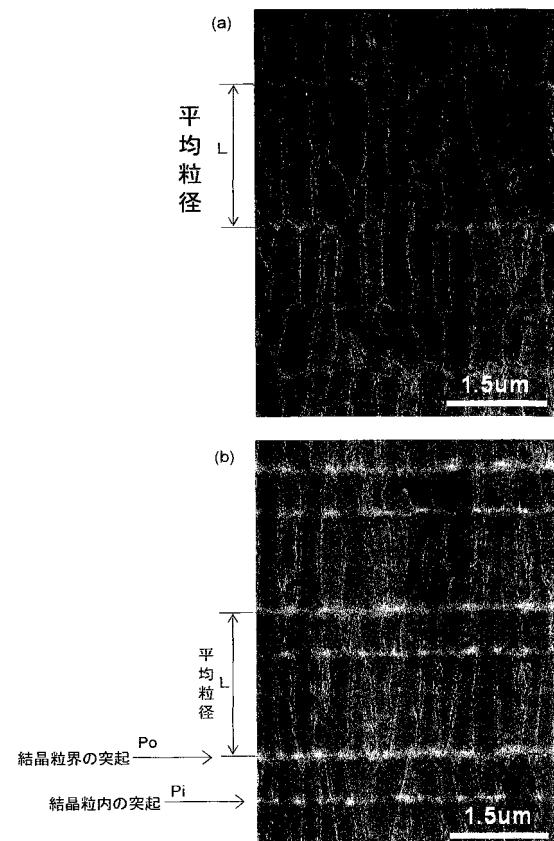

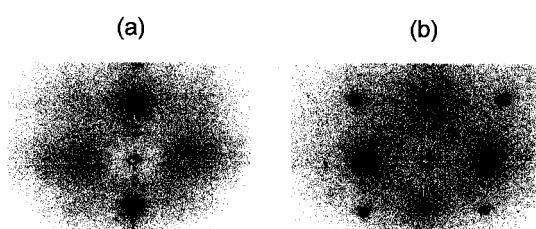

#### 【0061】

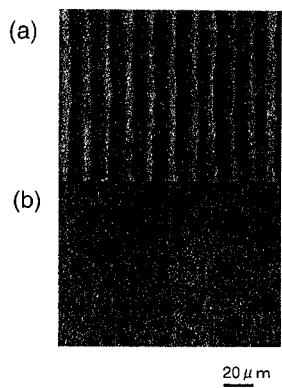

図 11 は透過率分布フィルタを位相シフトストライプマスク法に適用した場合と適用しない場合のシリコン半導体の結晶の走査型電子顕微鏡 (SEM) で観察した写真である。図 11 (a) は透過率分布フィルタを用いて結晶化を行った結晶の SEM 写真であり、図 11 (b) は透過率分布フィルタを用いないで結晶化を行った結晶の SEM 写真である。図 11 の写真で白く観察されるところが表面に形成された突起に対応する部分である。図 11 (a) (b) における参照符号 L は平均粒径、また図 11 (b) における P<sub>o</sub> は主に結晶粒界の突起が配列している箇所、P<sub>i</sub> は主に結晶粒内に突起が配列している箇所を示す。

#### 【0062】

図 11 (b) に示された透過率分布フィルタを用いない場合は、結晶粒界の位置および結晶粒内に白く観察される高い突起が形成されているのが判るが、透過率分布フィルタを用いた図 11 (a) に示したものでは、突起が低いため SEM 写真で白く観察される高い突起が明瞭に観察されない。この場合の突起は PV 値で  $70 nm$  以下であった。

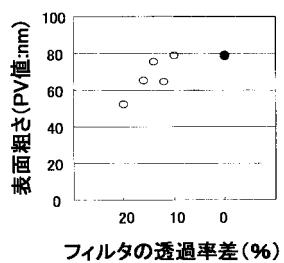

#### 【0063】

図 12 は透過率分布フィルタを位相シフトストライプマスク法に適用した場合の突起の高さと透過率分布フィルタにおける透過率差の関係の説明図である。図 12 は図 9 における透過率分布フィルタの M 領域と N 領域の透過率の差に対して、突起の高さを  $10 \mu m$  四

10

20

30

40

50

方の領域で原子間力顕微鏡で評価した結果をグラフにしたものである。図12に示された結果から、透過率の差が10%以上で突起低減効果があり、15%以上あればPV値で70nm以下になることが判明した。

#### 【0064】

結晶粒のサイズについては、位相シフトストライプパターンのピッチが3μmであるので、そのピッチの半分のサイズまで結晶が成長し、成長方向の結晶粒としては約1.5μmとなる。結晶の成長方向と垂直方向の粒界サイズは、0.5μm以下である。直交する2方向のアニール走査によって、平均粒径を2方向ともに1.5μmとすることができます。

#### 【実施例4】

#### 【0065】

次に、SLS法に透過率分布制御フィルタを適用する実施例を説明する。図13は透過率分布制御フィルタをSLS法に適用したレーザアニール装置の光学系を説明する模式図である。また、図14はSLS法のレーザアニール装置に適用する透過率分布制御フィルタの一例の説明図である。図13に示したように、SLS法のレーザアニール装置(SLS結晶化装置)は光源2については実施例1と同じ構成としたものを利用する。すなわち、レーザ光源2の後段に、アッテネータ3、ホモジナイザ25、レンズ29、マスク26、イメージングレンズ27、そして非晶質シリコン半導体薄膜を成膜した基板1が置かれる移動ステージ30が順次に配列されている。そして、レンズ29とマスク26の間に本発明の透過率分布制御フィルタ31が挿入されている。アッテネータ3とホモジナイザ25間及びイメージングレンズ27と移動ステージ30間には、入射した光を所定の角度で反射して光の方向を変化させるためのミラー23、24、28が各々配置されている。

#### 【0066】

ホモジナイザ25はビーム整形とビーム内光強度を均一にするための光学系であり、レンズ29との組み合わせによってマスク26の位置に均一なビーム内強度分布を形成するようにしてある。図14におけるマスク26はアルミ製であり、マスク開口であるスリット26Aの幅が15μmであり、スリット26A間のマスクの幅も15μmとし、A領域とB領域はお互いに基板の走査方向に対してスリット26Aの間隔の配列周期の位相を15μmだけずらしてある。同様に、C領域とD領域もお互いに15μmだけずらし、且つA領域とC領域との周期位相のずれを互いに15μmとは異なる様に設定する。

#### 【0067】

レンズ27によってマスクパターンが1/5縮小して試料面上に投影される。これによって基板上では、6ミクロン周期で3ミクロン幅の明暗の強度分布となる。マスク26のサイズは、50mm×50mmである。マスク26上でのA、B、C、Dの各領域の幅は各10ミリメートルである。

#### 【0068】

図14に示した透過率分布フィルタ31はマスク26と同一サイズとし、石英基板の表面に反射率1%のコーティング膜を形成した領域32と反射率16%のコーティング膜を形成した領域33を形成し、裏面にはすべて反射率1%のコーティング膜を形成した。これによって領域32と領域33の透過率の差が15%であるフィルタをマスク近傍のすぐ上流側に設置した。マスクパターンの各領域が1ショットだけ照射されるように、パルス間隔が1/300秒の間の走査移動量が、パターンの各領域の試料面上での間隔に一致する様に設定される。

#### 【0069】

図15はSLS法に透過率分布フィルタを用いて得られるシリコン半導体薄膜の結晶化的説明図である。上記した条件で図15(a)の基板表面の非晶質シリコン薄膜1AにA領域照射(図15(b))、B領域照射(図15(c))、C領域照射(図15(d))、D領域照射(図15(e))のプロセスでレーザアニールされる。その結果、結晶化したシリコン半導体薄膜は、図15(e)に示したように、粒界位置に存在する突起39Aと、結晶粒内に存在する突起40とを有する結晶が得られた。しかも、突起の高さはすべ

て 70 nm 以下となつた。

【0070】

この場合の結晶成長方向のサイズは 3  $\mu$ m となる。また、この場合の成長方向と直交方向の粒界のサイズも、実施例 3 の場合と同じように 0.5  $\mu$ m 以下となつた。ほぼ直交する 2 方向のアニール走査によって、2 方向の粒界サイズが 3  $\mu$ m とすることも可能である。

【実施例 5】

【0071】

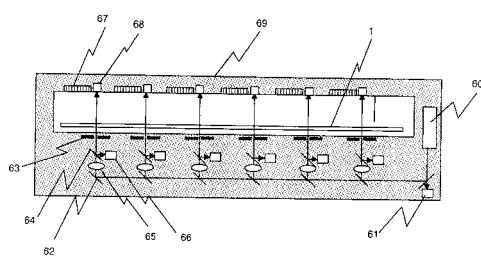

次に、本発明による多結晶シリコン半導体薄膜のラフネス評価方法の実施例を説明する。図 16 は粒径評価装置に表面ラフネス評価機能を追加した本発明の粒径評価方法を実現する粒径評価装置の光学系の模式図である。この装置の基本的な構成は特許文献 11 に開示されたものと同様である。図 16 において、参照符号 69 は枠であり、この枠 69 に、半導体薄膜を成膜した基板 1 の検査用（評価用）の波長 532 nm の連続発振レーザ光源 60、基板 1 にレーザ光を照射するためのミラー 62 とレンズ 65 およびアパー・チャ 63 からなる照射光学系、基板 1 からの散乱光角度分布を検出する光検出器アレイ 67 からなる基本構成が設置されている。これに本実施例のラフネス評価機能を追加するために、反射率と透過率を測定するための構成を追加する。

【0072】

ラフネス評価機能を追加するための反射率と透過率を測定するための構成は、このレーザ光照射光学系にハーフミラー 64 と反射光強度をモニタするための光検出器 66 および透過光強度をモニタするための光検出器 68 とを 6 系統分追加する。さらに、検査用レーザ光の入射強度をモニタするための光検出器 61 を追加する。この追加によって、反射率と透過率を測定することが可能となる。

【0073】

本実施例では、基板全面を短時間で計測するために 6 系統のマルチビームの構成を採用しているが、1 系統当たりのレーザ光照射強度が約 20 mW 以上あれば良いので、出力の高いレーザを検査用光源として用いれば系統数をさらに多くすることができる、検査時間をさらに短縮化することができる。

【0074】

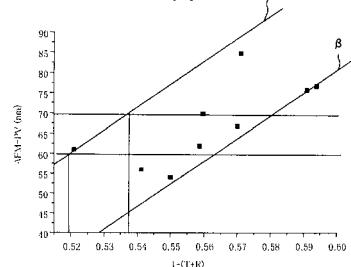

図 17 は図 16 に示した粒径評価装置を用いて測定した表面ラフネス量と原子間力顕微鏡で評価した表面ラフネスとの相関の説明図である。図 17 は前記実施例 3 の各種条件の多結晶膜の基板を測定した結果を原子間力顕微鏡で計測した PV 値と比較したグラフである。縦軸は原子間力顕微鏡で計測した PV 値であり、横軸は「1 - (T + R)」である。但し、T は透過率、R は反射率を表している。図 17 における直線 1 と直線 2 は、それぞれ共通の傾きの相関直線であって、PV 値の分布の上限と下限を示す。この様に PV 値と「1 - (T + R)」とには相関があることが分かる。

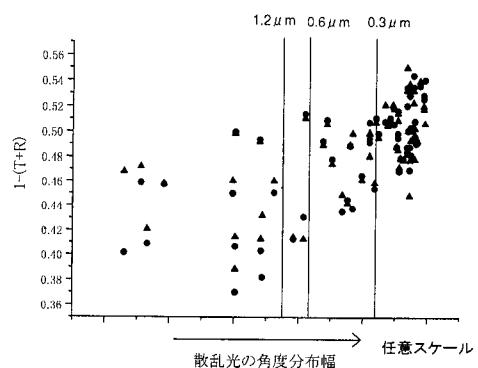

【0075】

図 18 は図 16 に示した粒径評価装置を用いて評価可能とした粒径に関する量と表面ラフネスに関する量との 2 次元分布による多結晶シリコン半導体薄膜の測定結果の一例の説明図である。図 18 は特許文献 11 に開示された内容による散乱角度分布幅に基づく粒径と「1 - (T + R)」との 2 次元分布で表した多結晶膜の評価結果の例である。図 17 に示されたように、多結晶膜を粒径と表面ラフネスの 2 つについて管理基準を設定して、レーザアニール工程の管理を実施する。すなわち、平均粒径の管理基準を 0.5  $\mu$ m とし、平均ラフネスとして PV 値 70 nm 以下と設定し、どちらの管理基準もクリアしなければ再度結晶化し、両管理基準が満足するまで繰り返す。これによって、形成される多結晶膜はすべて両管理基準を満足する。

【実施例 6】

【0076】

実施例 5 のラフネス評価方法は、実施例 1、2、3、4 で結晶化した多結晶シリコン半導体薄膜の表面ラフネスに対してすべて適用することができるが、実施例 3 と実施例 4 の

10

20

30

40

50

横方向の成長した結晶については突起配列が規則正しいので、突起配列間隔と突起の高さの両方を評価可能な方法を説明する。

【0077】

この方法では、実施例5に示した構成の装置を用い、散乱光の角度分布を計測するアレイ検出器を2次元検出器とする。これによって、突起に由来する回折スポットの角度情報から突起間隔を評価し、スポットの強度より突起の高さを評価する。

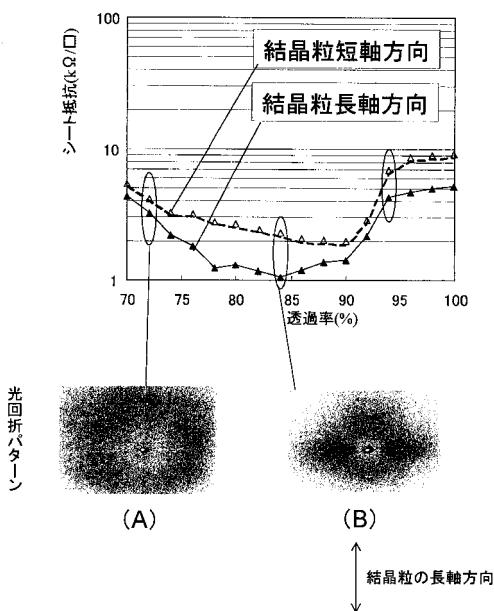

【0078】

図19は本発明の実施例3における透過率分布フィルタを使用しないで3μmピッチの位相シフトストライプパターンを利用して形成した多結晶シリコン半導体薄膜の光回折パターンを説明する写真である。図19(a)1方向にアニール走査して形成した多結晶シリコン半導体薄膜の光回折パターンであり、図19(b)は直交した2方向にアニール走査して形成した多結晶シリコン半導体薄膜の光回折パターンである。

10

【0079】

図19(a)(b)から、それぞれ突起に由来する回折スポットが観察され、その配列はアニール走査方向に依存している事が分かる。回折スポットの強度は、突起の高さと検査用レーザ光の径に含まれる突起の数と突起の配列秩序に依存する。検査用のレーザ光の径は一定であるので突起の数は一定であり、ピッチが一定の位相シフトマスクを用いている場合は配列秩序は一定であるので、回折スポットの光強度は突起の高さのみに依存する量となる。

20

【0080】

図24は、本発明の実施例3における透過率分布フィルタを使用しないで2μmピッチの位相シフトストライプパターンを利用して、照射エネルギー密度を変えて一方向のアニール走査で形成した多結晶シリコン半導体薄膜の光回折パターンとシート抵抗との関係である。横軸の透過率は照射レーザ強度に比例する。シート抵抗は粒径が大きいほど小さく、ほぼ逆数の関係が成り立つ。図11に示したように結晶粒が細長く、結晶の長軸方向のシート抵抗値は短軸方向のシート抵抗値と比べると、透過率84%で約半分程度である事が分かる。このときの光回折パターン(B)における結晶の長軸方向の角度分布と短軸方向の角度分布を比較すると、長軸方向の角度分布の幅が約半分になっている事が分かる。これに対して透過率が72%でレーザ強度が弱すぎる場合は、結晶粒の長軸方向と短軸方向のシート抵抗値との比率は1に近いが、これに対応して散乱光の長軸方向の角度分布の幅と短軸方向の角度分布の幅もほぼ等しくなっている事が分かる。以上によって、結晶粒が細長い場合も散乱光の角度分布幅で粒径が評価できる事が分かる。

30

【0081】

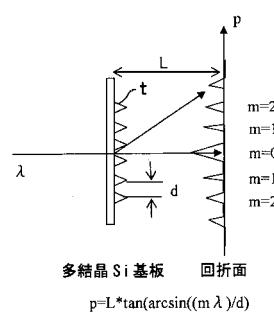

図20は本発明の実施例3と実施例4で形成された多結晶シリコン半導体薄膜の回折パターン上の回折スポットの位置と突起の間隔との関係の説明図である。図20におけるはレーザ光の波長、dは基板上に成膜した多結晶シリコン半導体薄膜に形成された突起(ここではtで示す)の間隔、Lは試料と回折パターン面との距離、pは「 $p = L \times t \tan(\arcsin(m) / d)$ 」である。図20に示した様に、突起tの間隔dは、回折面上における回折スポットの位置pによって評価することができる。すなわち、回折スポットが形成する方向は各突起から発生する散乱光の行路差が波長の整数倍に比例するとして得られる関数により、突起間隔を回折スポットの位置から評価することができる。この突起の評価方法は、SLS法によって形成した多結晶シリコン薄膜の突起の評価にも適用することができる。

40

【0082】

以上により、位相シフトストライプ法やSLS法の様に突起が規則正しく配列する結晶化する製造工程において、透過率分布フィルタを利用した突起低減方法を採用し、さらに光回折スポットの強度を測定してその測定値に管理基準を設定する。管理基準の強度を越える領域があれば、その領域を照射エネルギー密度を変えて再度結晶化することを、管理基準が満足するまで繰り返すことにより、突起の高さをPV値すべて70nm以下にする事ができる。

50

## 【実施例 7】

## 【0083】

次に、上記に記述した各方法で作成する多結晶薄膜を利用して形成した薄膜トランジスタとこの薄膜トランジスタを含む駆動回路や画素回路で構成した表示装置の実施例を説明する。

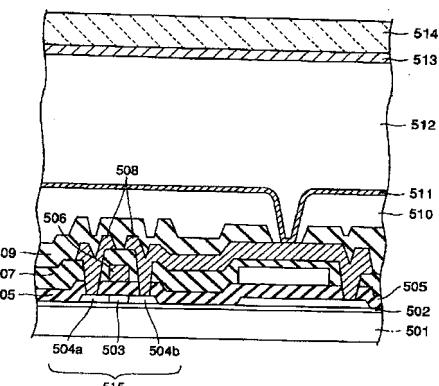

## 【0084】

図21は本発明の製造方法で形成した多結晶シリコン薄膜を用いた薄膜トランジスタを含む表示装置としてのアクティブ・マトリクス型の液晶表示装置の要部構成例を説明する断面図である。この液晶表示装置は次のように構成されている。即ち、薄膜トランジスタ515、カラーフィルタ510及び画素電極511を備えるガラス基板501と、対向電極513を有する対向ガラス基板514との対向間隙に液晶512を介在させて封止している。なお、液晶512と各基板の境界には配向制御膜が成膜されるが、図示を省略した。

10

## 【0085】

ガラス基板501の表面には、アンダーコート層（酸化シリコン膜および窒化シリコン膜）502が形成され、その上に非晶質シリコン半導体層が形成されて、前記製造方法の実施例で説明したように、本発明に係るレーザアニールにより多結晶シリコン薄膜の層に改質されている。このレーザアニールにより得た多結晶シリコン薄膜の層に薄膜トランジスタ515が作り込まれている。即ち、多結晶シリコン半導体薄膜からなる半導体層503の両側に不純物をドープすることにより、多結晶シリコンのソース半導体層504aおよび多結晶シリコンのドレイン層504bが形成され、その上にゲート酸化膜（ゲート絶縁層）505を介してゲート電極506が形成されている。

20

## 【0086】

ソース／ドレイン電極508が、層間絶縁膜507に形成された接続孔（コントクトホール）を介して、それぞれソース半導体層504aおよびドレイン半導体層504bに接続され、その上に保護膜509が設けられる。そして、保護膜509上にカラーフィルタ510及び画素電極511が形成されている。特に、本発明の実施例3および実施例4のレーザアニール法では、1回の走査による結晶は、結晶粒のサイズが方向によって異なるので、薄膜トランジスタ515のソース／ドレイン電極508の方向（すなわち、チャネル方向）を多結晶シリコン半導体結晶粒のサイズの大きい方向になるように揃える。なお、走査方向を2方向としてアニールした多結晶シリコン半導体結晶では、この様に揃える必要は無い。

30

## 【0087】

この薄膜トランジスタは液晶表示装置の画素回路を構成し、図示しない走査線駆動回路からの選択信号で選択され、図示しない信号線駆動回路から供給される画像信号で画素電極511が駆動される。駆動された画素電極511と、対向ガラス基板514の内面に有する対向電極513の間に電界が形成される。この電界により、液晶512の分子配向方向が制御されて表示がなされる。

## 【0088】

なお、上記した走査線駆動回路や信号線駆動回路を構成する薄膜トランジスタも上記画素回路と同様の多結晶シリコン半導体薄膜で形成することもできる。また、本発明は液晶表示装置に限らず、アクティブ・マトリクス型の他の表示装置、例えば有機EL表示装置やプラズマ表示装置、その他の各種表示装置にも適用でき、あるいは太陽電池を構成する半導体薄膜の製造にも同様に適用することができる。

40

## 【0089】

以上のように、本発明のレーザアニール法を用いた半導体製造方法とその評価方法を採用することにより、優れた特性を示す本発明の薄膜トランジスタを量産することができ、この薄膜トランジスタを用いることで、高品質な本発明の表示装置を非常に高い歩留まりで製造することができる。

## 【産業上の利用可能性】

50

## 【0090】

ガラス等の絶縁基板上に薄膜トランジスタに代表されるアクティブ素子を形成して、画像表示装置を形成する場合、あるいは太陽電池を形成する場合の当該半導体薄膜の表面ラフネスを低減した半導体基板として利用することができる。

## 【図面の簡単な説明】

## 【0091】

【図1】本発明の半導体製造方法を実現するレーザアニール装置の光学系の一例を説明する模式図である。

【図2】図1における透過率分布フィルタの表面の構成例を説明する模式的図である。

【図3】図1の透過率分布フィルタの設置によって得た短軸方向の光強度分布の説明図である。

10

【図4】透過率分布フィルタを用いないで複数回走査でレーザ光の照射エネルギー密度を変えた場合のシリコン半導体結晶の暗視野光学顕微鏡写真である。

【図5】本発明の半導体製造方法を実現するレーザアニール装置の光学系の他例を説明する模式図である。

15

【図6】図5における透過率分布フィルタの表面の構成例を説明する模式的図である。

【図7】本発明の半導体製造方法を実現するレーザアニール装置の光学系のさらに他例を説明する模式図である。

20

【図8】位相シフトストライプマスクを用いてシリコン半導体薄膜の結晶化を行う方法の説明図である。

【図9】透過率分布フィルタと位相シフトストライプマスクのパターンと基板走査方向の説明図である。

25

【図10】透過率分布フィルタを位相シフトストライプマスクを用いた場合のシリコン半導体薄膜の結晶化の説明図である。

【図11】透過率分布フィルタを位相シフトストライプマスク法に適用した場合と適用しない場合のシリコン半導体の結晶の走査型電子顕微鏡（S E M）で観察した写真である。

30

【図12】透過率分布フィルタを位相シフトストライプマスク法に適用した場合の突起の高さと透過率分布フィルタにおける透過率差の関係の説明図である。

【図13】透過率分布制御フィルタをS L S法に適用したレーザアニール装置の光学系を説明する模式図である。

35

【図14】S L S法のレーザアニール装置に適用する透過率分布制御フィルタの一例の説明図である。

【図15】S L S法に透過率分布フィルタを用いて得られるシリコン半導体薄膜の結晶化の説明図である。

40

【図16】粒径評価装置に表面ラフネス評価機能を追加した本発明の粒径評価方法を実現する粒径評価装置の光学系の模式図である。

【図17】図16に示した粒径評価装置を用いて測定した表面ラフネス量と原子間力顕微鏡で評価した表面ラフネスとの相関の説明図である。

【図18】図16に示した粒径評価装置を用いて評価可能とした粒径に関する量と表面ラフネスに関する量との2次元分布による多結晶シリコン半導体薄膜の測定結果の一例の説明図である。

45

【図19】本発明の実施例3における透過率分布フィルタを使用しないで3 μmピッチの位相シフトストライプパターンを利用して形成した多結晶シリコン半導体薄膜の光回折パターンを説明する写真である。

【図20】本発明の実施例3と実施例4で形成された多結晶シリコン半導体薄膜の回折パターン上の回折スポットの位置と突起の間隔との関係の説明図である。

【図21】本発明の製造方法で形成した多結晶シリコン薄膜を用いた薄膜トランジスタを含む表示装置としてのアクティブ・マトリクス型の液晶表示装置の要部構成例を説明する断面図である。

【図22】レーザ光照射エネルギー密度の時間変化の説明図である。

50

【図23】図22の時間変化を複数の走査で実施する場合に起こる副作用の説明図である。

【図24】位相シフトストライプマスク法において、エキシマレーザ光強度を変化させて形成した多結晶シリコン膜の光回折パターンとシート抵抗との関係を示す図である。

【図25】位相シフトストライプマスク法において形成された多結晶膜表面の突起配列の位置が変化する周期とアニール走査のピッチとの関係を示す図である。

【符号の説明】

【0092】

1 シリコン半導体薄膜を成膜した基板（試料基板）

1A 基板上に成膜されたシリコン半導体膜

10

2 結晶化用レーザ光源

3 アッテネータ

4 長軸ホモジナイザ

5 短軸ホモジナイザ

5A 短軸ホモジナイザの前段のシリンドリカルレンズアレイ

5B 短軸ホモジナイザの後段のシリンドリカルレンズアレイ

6 透過率分布フィルタ

7 ミラー

8 シリンドリカルレンズ

9 レーザ光

20

10 シリンドリカルレンズ

11 12の領域より透過率が相対的に低い領域

12 11の領域より透過率が相対的に高い領域

13 短軸ホモジナイザのシリンドリカルレンズアレイ各素子に対応する光透過領域

14 15の領域より透過率が相対的に低い領域

15 14の領域より透過率が相対的に高い領域

16 透過率分布フィルタ

23 ミラー

24 ミラー

30

25 ホモジナイザ

26 マスク

27 イメージングレンズ

28 ミラー

29 レンズ

30 移動ステージ

31 透過率分布フィルタ

32 33の領域より透過率が相対的に高い領域

33 32の領域より透過率が相対的に低い領域

41 位相シフトストライプマスク

50 透過率分布フィルタ

40

60 検査用レーザ光源

61 入射光強度モニタ用光検出器（1系統）

62 ハーフミラー（6系統）

63 基板からの反射光の強度モニタ用光検出器（6系統）

64 基板からの透過光の強度モニタ用光検出器（6系統）

65 アパーチャ

66 基板からの散乱光強度の角度分布用アレイ検出器（6系統）

501 ガラス基板

502 アンダーコート層

503 多結晶シリコン膜

50

- 5 0 4 a 多結晶シリコンのソース層

5 0 4 b 多結晶シリコンドレイン層

5 0 5 ゲート酸化膜

5 0 7 層間絶縁膜

5 0 6 ゲート電極

5 0 8 ソース／ドレイン電極

5 0 9 保護膜

5 1 0 カラーフィルタ 5 1 0

5 1 1 画素電極

5 1 2 液晶

5 1 3 対向電極

5 1 4 対向ガラス基板。

10

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図9】

図9

【図10】

図10

【図6】

図6

【図7】

図7

【図8】

図8

【図11】

図11

【図12】

図12

【図14】

図14

【図13】

図13

【図15】

図15

【図17】

図17

【図16】

図16

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

図24

【図25】

図25

---

フロントページの続き

(72)発明者 斎藤 雅和

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

(72)発明者 後藤 順

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

F ターム(参考) 2H092 JA24 JA25 JA28 KA04 MA01 MA30 MA35 NA21 NA25 QA06

5F052 AA02 BA04 BA07 BA12 BB07 CA04 CA08 DA02 EA12 JA01

JA09

5F110 AA24 AA26 BB02 CC02 DD02 DD13 DD14 DD17 FF01 FF02

GG02 GG13 GG16 GG22 NN73 PP03 PP04 PP05 PP06 PP07

PP11 PP23 PP24 PP29 PP40