(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6351691号

(P6351691)

(45) 発行日 平成30年7月4日(2018.7.4)

(24) 登録日 平成30年6月15日(2018.6.15)

(51) Int.Cl.

F 1

H04N 5/378 (2011.01)

H04N 5/374 (2011.01)H04N 5/378

H04N 5/374

請求項の数 9 (全 11 頁)

(21) 出願番号 特願2016-224381 (P2016-224381)

(22) 出願日 平成28年11月17日 (2016.11.17)

(62) 分割の表示 特願2012-155529 (P2012-155529)

の分割

原出願日 平成24年7月11日 (2012.7.11)

(65) 公開番号 特開2017-55441 (P2017-55441A)

(43) 公開日 平成29年3月16日 (2017.3.16)

審査請求日 平成28年12月13日 (2016.12.13)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 小林 大祐

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 山崎 善一

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

審査官 大室 秀明

最終頁に続く

(54) 【発明の名称】光電変換装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

行列状に配列された複数の画素を含む画素アレイと、

各々が前記画素アレイの列に対応して設けられ、前記画素の信号に基づく信号をデジタル信号に変換するA/D変換部を含む複数の信号処理部と、を有する光電変換装置であって、

前記複数の信号処理部は、前記複数の信号処理部の互いに異なる一部であって、かつ、2つ以上の信号処理部を各々が含む複数の組を構成し、

前記光電変換装置は、さらに

前記複数の組の各々に対応して設けられ、前記複数の組の各々において前記2つ以上の信号処理部からの信号を共通に受ける共通配線と、

前記複数の組の各々に対応して設けられた信号出力部と、

駆動信号伝送部と、を有し、

前記駆動信号伝送部は、

駆動信号が入力され、前記駆動信号をバッファする第1のバッファ回路と、前記第1のバッファ回路の出力が入力される第2のバッファ回路とを含むとともに、直列に接続された複数のバッファ回路を含む第1のバッファ回路群と、

前記駆動信号とは別の第2の駆動信号が入力され、直列に接続された複数のバッファ回路を含む第2のバッファ回路群と、を有し、

前記複数の組の一の組の前記信号出力部に前記第1のバッファ回路の出力が入力され、

10

20

前記複数の組の別の組の前記信号出力部に前記第2のバッファ回路の出力が入力され、前記第2のバッファ回路群の前記複数のバッファ回路のうちの一のバッファ回路の出力が前記一の組に入力され、

前記第2のバッファ回路群の前記複数のバッファ回路のうちの別のバッファ回路の出力が前記別の組に入力され、

前記信号出力部の少なくとも1つは、対応する組の前記共通配線の信号を、別の組の前記共通配線へ出力する

ことを特徴とする光電変換装置。

【請求項2】

前記複数の組に対応して設けられ、各々が対応する前記組に含まれる前記2つ以上の信号処理部を選択する複数の列選択部を有し、

前記複数の列選択部の各々は、前記第2のバッファ回路群に含まれるバッファ回路から供給される信号が与えられることを特徴とする請求項1に記載の光電変換装置。

【請求項3】

前記複数の組の各々は、前記信号出力部として、前記2つ以上の信号処理部のデジタル信号を受けるブロック出力部を有し、

前記一の組に対応する前記ブロック出力部は、前記一の組の前記2つ以上の信号処理部が出力したデジタル信号、または、前記別の組の前記ブロック出力部が出力したデジタル信号を出力することを特徴とする請求項1または2のいずれかに記載の光電変換装置。

【請求項4】

前記複数の組の各々は、前記信号出力部として、前記2つ以上の信号処理部のデジタル信号を受けるブロック出力部を有し、

前記複数の信号処理部の各々は、前記A/D変換部から出力されたデジタル信号を保持するメモリ部を有し、

前記複数の組の各々は、前記共通配線として、前記一部の複数の信号処理部の各々の前記メモリ部が接続されたブロック信号線を有し、

前記一の組のブロック信号線には、前記一の組の前記メモリ部のデジタル信号と、前記別の組の前記ブロック出力部から出力される、前記別の組の前記メモリ部のデジタル信号とが入力されることを特徴とする請求項1または2のいずれかに記載の光電変換装置。

【請求項5】

前記複数の組の各々は、前記信号出力部として、前記一部の複数の信号処理部のデジタル信号を、前記駆動信号に同期して出力する同期化回路を有し、

前記一の組の前記同期化回路は、前記一の組の前記2つ以上の信号処理部が出力したデジタル信号、または、前記別の組の前記同期化回路が出力したデジタル信号を出力することを特徴とする請求項1または2のいずれかに記載の光電変換装置。

【請求項6】

前記複数の信号処理部の各々は、前記A/D変換部から出力されたデジタル信号を保持するメモリ部を有し、

前記複数の組の各々は、前記信号出力部として、信号選択部を有し、

前記一の組の前記信号選択部は、前記一の組の前記メモリ部が出力する前記デジタル信号と、前記別の組から出力される前記デジタル信号との一方を出力することを特徴とする請求項1に記載の光電変換装置。

【請求項7】

行列状に配列された複数の画素を含む画素アレイと、

各々が前記画素アレイの列に対応して設けられ、前記画素の信号に基づく信号をデジタル信号に変換するA/D変換部を含む複数の信号処理部と、を有する光電変換装置であつて、

前記複数の信号処理部は、前記複数の信号処理部の互いに異なる一部であつて、かつ、2つ以上の信号処理部を各々が含む複数の組を構成し、

10

20

30

40

50

前記光電変換装置は、さらに

前記複数の組の各々に対応して設けられた信号出力部と、

駆動信号伝送部と、を有し、

前記駆動信号伝送部は、駆動信号が入力され、前記駆動信号をバッファする第1のバッ

ファ回路と、前記第1のバッファ回路の出力が入力される第2のバッファ回路とを含み、

前記複数の組の一の組の前記信号出力部に前記第1のバッファ回路の出力が入力され、

前記複数の組の別の組の前記信号出力部に前記第2のバッファ回路の出力が入力され、

前記一の組の前記信号出力部は、前記一の組の前記2つ以上の信号処理部が出力したデ

ジタル信号を受ける第1の入力ノード、および、前記別の組の前記2つ以上の信号処理部

が出力したデジタル信号を受ける第2の入力ノードを有し、一方を選択する信号選択部を

含む

ことを特徴とする光電変換装置。

**【請求項8】**

前記信号出力部は、前記信号選択部の出力に接続された同期化部を含む

ことを特徴とする請求項7に記載の光電変換装置。

**【請求項9】**

請求項1～8のいずれかに記載の光電変換装置と、

前記複数の画素に像を形成する光学系と、

前記光電変換装置から出力された信号を処理して画像データを生成する映像信号処理部

と、を備えたこと

を特徴とする撮像システム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は光電変換装置に関し、特に、画素アレイの列に対応して信号処理回路を備える光電変換装置に関する。

**【背景技術】**

**【0002】**

画素が行列状に配列された画素アレイの各列、あるいは複数列につき信号処理回路を設けて、並列に信号処理を行う撮像装置が一般に知られている。

**【0003】**

特許文献1には、画素アレイの各列に設けられた信号処理装置として、A/D変換部とその変換結果を保持するメモリを備え、複数のメモリをブロックとしてブロック毎にブロック出力線を持つ撮像装置が記載されている。ブロック出力線に現れたデジタル信号は、同期化回路によりクロック信号に同期して後段へと伝達される。

**【0004】**

また、駆動信号を供給する方法として、バッファ回路をツリー状に接続したバッファ回路ツリー構成が一般的に知られている。

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献1】特開2010-147684号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

特許文献1には、信号処理回路や同期化回路を駆動するための信号が、どのように供給されるのかについては記載がない。仮に、特許文献1に記載された撮像装置において、バッファ回路ツリー構成を用いて駆動信号を供給すると、同時に動作するバッファ回路の数が増大し、過渡的な消費電流が増大することが懸念される。過渡的な消費電流が増大すると、撮像装置の電源ラインのインピーダンスによる電圧の変動が大きくなることで、撮像

10

20

30

40

50

装置の動作余裕範囲が狭くなることや、ノイズ量が増大することが懸念される。

【0007】

本発明は、上記問題を解決することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一つの側面は、行列状に配列された複数の画素を含む画素アレイと、各々が前記画素アレイの列に対応して設けられ、前記画素の信号に基づく信号をデジタル信号に変換するA/D変換部を含む複数の信号処理部と、を有する光電変換装置であって、前記複数の信号処理部は、前記複数の信号処理部の互いに異なる一部であって、かつ、2つ以上の信号処理部を各々が含む複数の組を構成し、前記光電変換装置は、さらに前記複数の組の各々に対応して設けられ、前記複数の組の各々において前記2つ以上の信号処理部からの信号を共通に受ける共通配線と、前記複数の組の各々に対応して設けられた信号出力部と、駆動信号伝送部と、を有し、前記駆動信号伝送部は、駆動信号が入力され、前記駆動信号をバッファする第1のバッファ回路と、前記第1のバッファ回路の出力が入力される第2のバッファ回路とを含むとともに、直列に接続された複数のバッファ回路を含む第1のバッファ回路群と、前記駆動信号とは別の第2の駆動信号が入力され、直列に接続された複数のバッファ回路を含む第2のバッファ回路群と、を有し、前記複数の組の一の組の前記信号出力部に前記第1のバッファ回路の出力が入力され、前記複数の組の別の組の前記信号出力部に前記第2のバッファ回路の出力が入力され、前記第2のバッファ回路群の前記複数のバッファ回路のうちの一のバッファ回路の出力が前記一の組に入力され、前記第2のバッファ回路群の前記複数のバッファ回路のうちの別のバッファ回路の出力が前記別の組に入力され、前記信号出力部の少なくとも1つは、対応する組の前記共通配線の信号を、別の組の前記共通配線へ出力することを特徴とする光電変換装置である。

10

20

30

【発明の効果】

【0010】

本発明によれば、過渡的な消費電流の増大を抑制できる。

【図面の簡単な説明】

【0011】

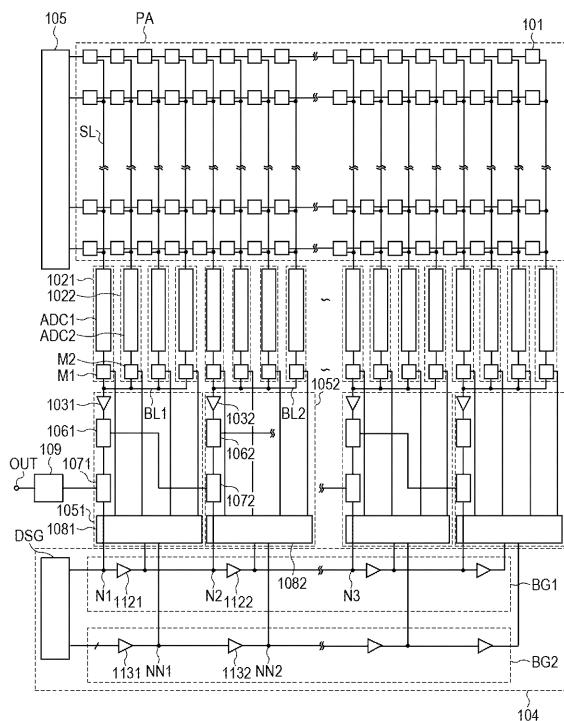

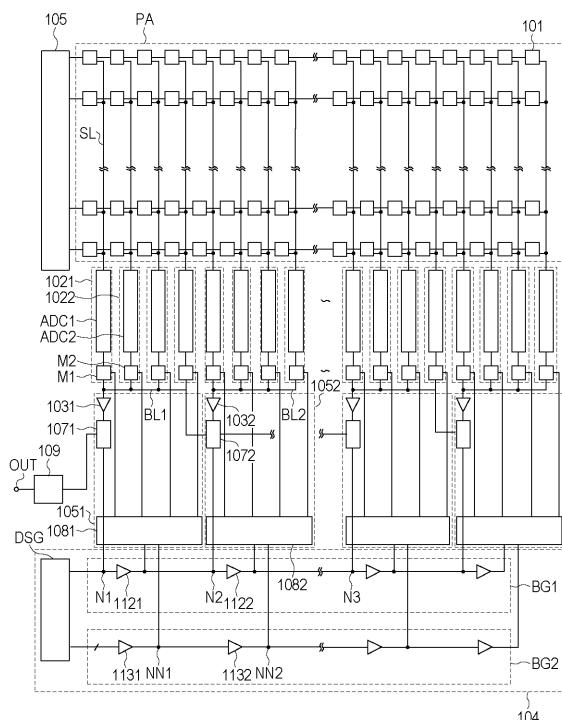

【図1】実施例1に係る光電変換装置の構成を示すブロック図である。

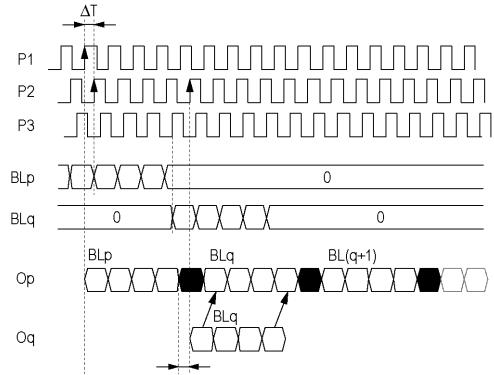

【図2】実施例1に係る光電変換装置の動作を示すタイミング図である。

30

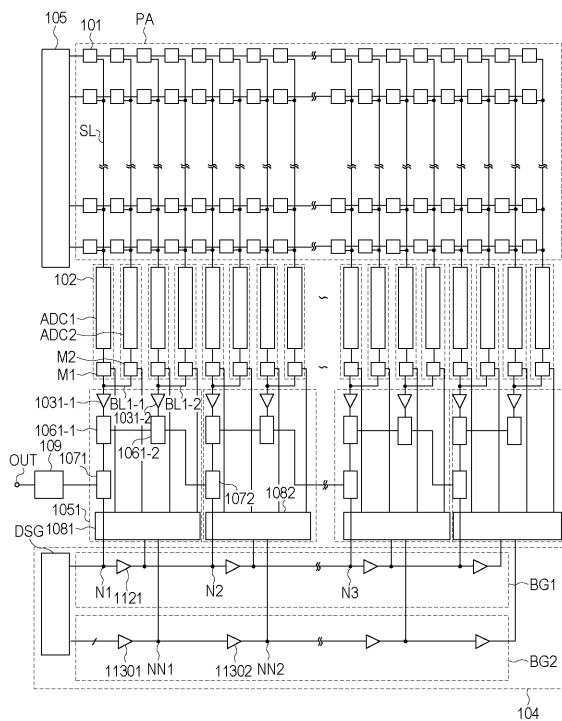

【図3】実施例2に係る光電変換装置の構成を示すブロック図である。

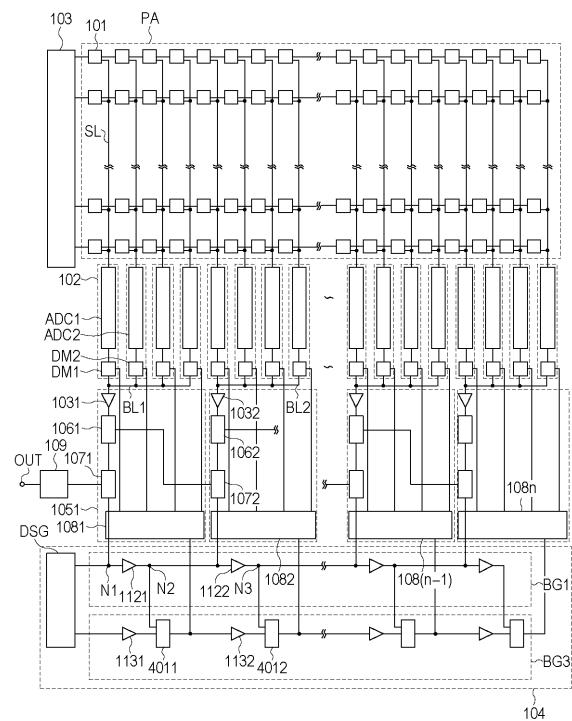

【図4】実施例3に係る光電変換装置の構成を示すブロック図である。

【図5】実施例4に係る光電変換装置の構成を示すブロック図である。

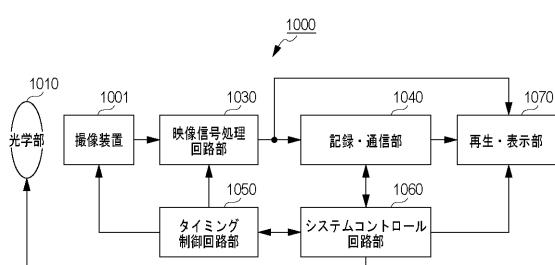

【図6】実施例5に係る撮像装置の構成を示すブロック図である。

【発明を実施するための形態】

【0012】

(実施例1)

図面を参照しながら、本実施例の説明を行う。

【0013】

図1は、光電変換装置1の構成例を示すブロック図である。光電変換装置1は、画素アレイPA、複数の信号処理部102n、複数のブロック出力部103n、駆動信号伝送部104、および行選択部105を含む(nは1以上の整数)。以下では、複数の同じ要素を説明する際にnを付すか末尾の一桁を省略する。つまり、信号処理部であれば、102nと表記するか、102と表記する。

40

【0014】

画素アレイPAは、行列状に配列された複数の画素101を含み、各列に信号線SLが設けられている。画素101は、行選択部105から与えられる制御信号により選択状態になると、対応する信号線SLに信号を出力する。本実施例では、行選択部105が、画素アレイPAに含まれる画素101を行を単位として選択する構成例を示している。また、行選択部105が1行の画素に対して供給する制御信号は2以上あることが一般的である。

50

るが、簡略化のために、図1では1本の線で示している。

【0015】

信号処理部102nは、画素アレイPAの列に対応して設けられ、信号線SLに現れた信号をデジタル信号に変換するA/D変換部を含む。信号処理部102は、ノイズ低減回路や信号増幅する増幅器を有しても良く、その場合には、画素101から出力された信号からノイズの低減を行った上で信号を増幅した信号をA/D変換部に入力すると、S/N比が高いデジタル信号を得ることができる。ノイズ低減回路の一例として、CDS(Correlated Double Sampling)回路が挙げられる。また、増幅器の例として、演算増幅器やソースフォロワ回路、ソース接地回路が挙げられる。また、信号処理部102nはA/D変換部から出力されたデジタル信号を保持するメモリ部Mnを含んでもよい。10

【0016】

次に、ブロック出力部103nについて説明する。図1においては、4個の信号処理部102につきブロック出力線と1個のブロック出力部が設けられている。すなわち、4個の信号処理部102を一つのブロックとして、各ブロックに対してブロック出力部103nが設けられている。ブロック出力線BLnには、信号処理部102nからの出力が与えられ、ブロック出力線はブロック出力部の入力端子に接続される。ブロック出力部103nは、信号選択部106n、同期化回路107n、及び列選択部108nを含む。図1は、ブロック出力部103nが、ブロック出力線BLnに出力されたデジタル信号をバッファ回路するバッファ回路部103nをさらに有する構成を示している。信号選択部106nは、ブロック出力線BLnに出力されたデジタル信号を同期化回路107nに伝達する。20 同期化回路107nは、後述する駆動信号と同期して、デジタル信号を別のブロックの信号選択部106nに伝達する。信号選択部106nは、その信号選択部106nと同一のブロックのブロック信号線BLに出力された信号と、別のブロックの同期化回路107(n+1)から出力された信号とのいずれかを選択的に、同一のブロックの同期化回路107nに出力する。すなわち、図1においては、同期化回路107nがデジタル信号処理部109と接続されたブロックを除いては、各ブロック信号線BLに出力された信号は、別のブロックの信号選択部106および同期化回路107を介してデジタル信号処理部109へと伝達される。列選択部108nは、信号処理部102に対して制御信号を供給し、デジタル信号をブロック信号線BLnに出力させる。列選択部108nは、例えばデコーダやシフトレジスタである。30

【0017】

駆動信号伝送部104は、駆動信号生成部DSGと、第1および第2のバッファ回路群としてのバッファ回路群BG1、BG2を含む。バッファ回路群BG1およびBG2は、それぞれ直列に接続された複数のバッファ回路を含むバッファ回路群を有する。図1は、直列に接続された複数のバッファ回路の組を2個備える構成を例示している。バッファ回路群BG1は、バッファ回路1121、1122、…、112nを有し、バッファ回路群BG2は、バッファ回路1131、1132、…、113nを有する。

【0018】

バッファ回路群BG1が伝達する駆動信号DS1は、同期化回路107nおよびバッファ回路112nに与えられる。同期化回路107nは、駆動信号DS1に同期して信号を次段、すなわち別のブロックの信号選択部106(n-1)またはデジタル信号処理部109に信号を出力する。バッファ回路112nは、次段のバッファ回路および別のブロックの同期化回路107(n+1)に駆動信号DS1を供給する。図1に示す構成では、隣接するブロックの同期化回路107nおよび列選択部108nは、バッファ回路112nによる遅延だけずれたタイミングで駆動される。40

【0019】

バッファ回路群BG2が伝達する駆動信号DS2は、各ブロックの列選択部108nに与えられる。列選択部108nは、駆動信号DS2に同期してアクティブ状態になる。つまり、駆動信号DS2に同期してアクティブになった列選択部108nのうち、アクティ50

ブにする駆動信号 D S 1 が与えられた列選択部 1 0 8 n は、列選択信号を信号処理部 1 0 2 n に供給する。これにより、当該列選択部 1 0 8 n と対応付けられたブロックのブロック出力部 1 0 3 n は、デジタル信号を別のブロックの信号選択部 1 0 6 またはデジタル信号処理部 1 0 9 へと出力する。

【 0 0 2 0 】

駆動信号伝送部 1 0 4 は、少なくとも隣接するブロック出力部 1 0 3 が異なるタイミングで動作するように駆動信号を供給する。図 1 に示すように、バッファ回路群を用いる場合、バッファ回路群を構成する各バッファ回路の特性が揃えば、ブロック同士で一定の位相差をつけて動作させることが可能となる。これにより、従来懸念された過渡的な消費電流の増大ならびにノイズの抑制が可能となる。

10

【 0 0 2 1 】

続いて、図 2 を参照しながら本実施例にかかる動作を説明する。図 2 は、図 1 において左から p 番目の同期化回路 1 0 7 p と、q 番目の同期化回路 1 0 7 q と、同期化回路 1 0 7 p に対応する列選択部 1 0 8 p と、同期化回路 1 0 7 q に対応する列選択部 1 0 8 q との動作タイミングを表すタイミング図である ( p 、 q は、 p < q を満たす自然数 ) 。

【 0 0 2 2 】

信号 P 1 は、図 1 におけるバッファ回路群 B G 1 のノード N 1 に伝達される駆動信号 D S 1 を表す。信号 P 2 および P 3 も同様に、それぞれノード N 2 および N 3 に対応する。本実施例において、駆動信号 D S 1 は、周期的なクロック信号であるとする。

20

【 0 0 2 3 】

図 2 には示さないが、各列選択部 1 0 8 p 、 1 0 8 q は、少なくとも信号を出力する期間は、バッファ回路群 B G 2 を介して与えられる駆動信号 D S 2 によって、アクティブになっている。

【 0 0 2 4 】

B L p および B L q は、それぞれ左から p 番目および q 番目のブロックのブロック信号線 B L に、信号処理部 1 0 2 から出力されるデータを表す。

【 0 0 2 5 】

出力信号 O p および O q は、それぞれ p 番目および q 番目のブロックの同期化回路 1 0 7 から出力される信号を表す。出力信号 O p および O q について、黒いデータは、無効データである。白いデータの上に付した符号は、そのデータが、いずれのブロック信号線から出力されたものであるのかを示す。

30

【 0 0 2 6 】

$p = 1$  、  $q = 2$  である場合を説明する。図 1 から明らかなように、隣接するブロックの同期化回路及び列選択部 1 0 8 に供給される駆動信号 D S 1 は、バッファ回路 1 1 2 を介して伝達される。このため、左から 1 番目のブロックに対して 2 番目のブロックに供給される駆動信号 D S 1 は、バッファ回路 1 1 2 で生じる遅延 T だけ位相がずれる。1 番目のブロックに対応する列選択部 1 0 8 1 は、信号 P 2 に同期して動作する一方、1 番目のブロックに対応する同期化回路 1 0 7 1 は、信号 P 1 に同期して動作する。また、2 番目のブロックに対応する列選択部 1 0 8 2 は、信号 P 3 に同期して、2 番目のブロックに対応する同期化回路 1 0 7 2 は信号 P 2 に同期して動作する。

40

【 0 0 2 7 】

1 番目のブロックの列選択部 1 0 8 1 は、信号 P 2 に同期して動作するため、1 番目のブロックのブロック信号線 B L 1 に対しては信号 P 2 に同期したタイミングでデータが出力される。そして、1 番目のブロックの同期化回路 1 0 7 1 は、信号 P 1 に同期するため、信号 P 2 に同期してブロック信号線 B L 1 に出力されたデータが信号 P 2 に同期してデジタル信号処理部 1 0 9 へと出力される。

【 0 0 2 8 】

同様にして、2 番目のブロックの列選択部 1 0 8 2 は、信号 P 3 に同期して動作するため、2 番目のブロックのブロック信号線 B L 2 に対しては信号 P 3 に同期したタイミングでデータが出力される。そして、2 番目のブロックの同期化回路 1 0 7 2 は、信号 P 2 に

50

同期するため、信号 P 3 に同期してブロック信号線 B L 2 に出力されたデータが信号 P 2 に同期して信号選択部 1 0 6 1 へと出力される。図 2 の期間 A 1 の間に、信号選択部 1 0 6 1 は不図示の制御信号を受けて、ブロック信号線 B L 1 に換えて、同期化回路 1 0 7 2 の出力を同期化回路 1 0 7 1 に出力するように切り替えられる。これにより、ブロック信号線 B L 2 に出力されたデータは、信号 P 1 に同期して、同期化回路 1 0 7 1 から出力される (Op)。

#### 【0029】

上述のように動作させると、同期化回路 1 0 7 1 から出力されたデータは、周期的に無効データを含んだデータとなる。無効データは、二つの異なるブロック信号線から出力されたデータの間に生じる。言い換えると、複数のブロックから出力されるデータは、位相が遅延するものの、それぞれのブロック内での位相関係は保つことができる。したがって、同期化回路 1 0 7 n や列選択部 1 0 8 n の駆動信号と、信号処理部 1 0 2 から出力されるデータの位相管理が容易になる。また、駆動信号がバッファ回路群によって遅延するために、回路の動作タイミングが異なるブロック間でずらすことが可能となる。この結果、過渡的な消費電流の低減、ならびに電源変動に起因するノイズの低減が可能となる。

#### 【0030】

図 1 では、駆動信号生成部 D S G から出力された駆動信号 D S 1 が、直接同期化回路 1 0 7 1 に与えられる構成を示したが、駆動信号生成部 D S G とノード N 1 との間にバッファ回路を設けても良い。逆に、駆動信号 D S 2 は、バッファ回路 1 1 3 1 を介して列選択部 1 0 8 1 に与えられる構成を示したが、駆動信号生成部 D S G から出力された駆動信号 D S 2 が直接列選択部 1 0 8 1 に与えられる構成でも良い。

#### 【0031】

##### (実施例 2)

図面を参照しながら本発明に係る別の実施例を説明する。実施例 1 との相違点を中心に説明する。

#### 【0032】

図 3 は、本実施例に係る光電変換装置の構成を示すブロック図である。実施例 1 と同じ機能を備える要素には同じ符号を付している。図 1 に示した光電変換装置では、各ブロック信号線に対して同期化回路 1 0 7 n を設けていた。

#### 【0033】

これに対して、本実施例に係る光電変換装置は、複数のブロック信号線に対して 1 個の同期化回路を設ける点で、実施例 1 とは異なる。

#### 【0034】

本実施例に係る構成は、同じ駆動信号で駆動されるブロックが複数あり、同じ駆動信号で駆動される複数のブロックにつき一つの同期化回路が設けられている、と言い換えることができる。

#### 【0035】

本実施例の構成によれば、ブロック信号線を短くできるので、信号処理部 1 0 2 が駆動する負荷を低減でき、実施例 1 の構成よりも動作を高速化できる。

#### 【0036】

##### (実施例 3)

図面を参照しながら、本発明に係る別の実施例を説明する。実施例 1 との相違点を中心に説明する。

#### 【0037】

図 4 は、本実施例に係る光電変換装置の構成を示すブロック図である。列選択部 1 0 8 は、例えばデコーダである。駆動信号伝送部 1 0 4 は、同期化回路 1 0 7 を駆動するクロック信号と、列選択部 1 0 8 を選択するアドレスデータとを供給する。駆動信号供給部は、複数のバッファ回路 1 1 2 n が直列に接続された、クロック信号を伝送するバッファ回路群 B G 1 に加えて、バッファ回路 1 1 3 n とアドレスデータ同期化回路 4 0 1 とが交互に接続された、アドレスデータを伝送するバッファ回路群 B G 3 を備える。アドレスデータ

10

20

30

40

50

タ同期化回路 401 は、バッファ回路 113n から与えられたアドレスデータを、バッファ回路群 BG1 で伝送されるクロック信号に同期させて、次段のバッファ回路 113(n+1) に供給する。本実施例においては、バッファ回路群 BG3 が、第 2 のバッファ回路群として機能する。

【0038】

本実施例によれば、アドレスデータの伝送を、同期化回路 107 を駆動する信号に同期させるアドレスデータ同期化回路 401 を導入することにより、ブロック間、並びにブロック内での位相管理を容易にすることができます。

【0039】

(実施例 4)

10

図面を参照しながら、本発明に係る別の実施例を説明する。実施例 1 との相違点を中心に説明する。

【0040】

図 5 は、本実施例に係る光電変換装置の構成を示すブロック図である。信号選択部 106n を持たない点で、本実施例は実施例 1 と異なる。ブロック出力線 BLn に出力された信号は、同期化回路 107n を介して別のブロック出力線と接続される。

【0041】

この構成によれば、ブロック出力線 BLn が、同期化回路 107n 間を接続する配線として兼用されるので、光電変換装置の小面積化に有利である。

【0042】

20

(実施例 5)

図面を参照しながら、本発明に係る実施例を説明する。

【0043】

図 6 は、本実施例に係る撮像システムの構成を示すブロック図である。

【0044】

撮像システム 1000 は、例えば、光学部 1010、撮像装置 1001、映像信号処理回路部 1030、記録・通信部 1040、タイミング制御回路部 1050、システムコントロール回路部 1060、および再生・表示部 1070 を含む。撮像装置 1001 は、前述の各実施形態で説明した光電変換装置が用いられる。

【0045】

30

レンズなどの光学系である光学部は 1010、被写体からの光を撮像装置 1001 の、複数の画素が 2 次元状に配列された画素アレイに結像させ、被写体の像を形成する。撮像装置 1001 は、タイミング制御回路部 1050 からの信号に基づくタイミングで、画素部に結像された光に応じた信号を出力する。

【0046】

撮像装置 1001 から出力された信号は、映像信号処理部である映像信号処理回路部 1030 に入力され、映像信号処理回路部 1030 が、プログラムなどによって定められた方法に従って、入力された電気信号に対して補正などの処理を行う。映像信号処理回路部での処理によって得られた信号は画像データとして記録・通信部 1040 に送られる。記録・通信部 1040 は、画像を形成するための信号を再生・表示部 1070 に送り、再生・表示部 1070 に動画や静止画像が再生・表示させる。記録通信部は、また、映像信号処理回路部 1030 からの信号を受けて、システムコントロール回路部 1060 とも通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。

40

【0047】

システムコントロール回路部 1060 は、撮像システムの動作を統括的に制御するものであり、光学部 1010、タイミング制御回路部 1050、記録・通信部 1040、および再生・表示部 1070 の駆動を制御する。また、システムコントロール回路部 1060 は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラムなどが記録される。また、システムコントロール回路部 1060 は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内で供給す

50

る。具体的な例としては、読み出す行やリセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらしなどである。

【0048】

タイミング制御回路部1050は、制御部であるシステムコントロール回路部1060による制御に基づいて撮像装置1001および映像信号処理回路部1030の駆動タイミングを制御する。

【0049】

(その他)

以上で説明した各実施例は、本発明を実施するための例示的なものに過ぎず、本発明の思想を変更しない限りにおいて、実施例の一部を変更したり、実施例同士を組み合わせたりすることができる。

【符号の説明】

【0050】

101 画素

102 信号処理部

ADC A / D 変換部

104 駆動信号伝送部

106 信号選択部

BG バッファ回路群

BL ブロック出力線

DSG 駆動信号生成部

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特開2008-172609(JP,A)

特開2011-166197(JP,A)

特開2010-147684(JP,A)

特開2011-182095(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/222-5/257

H04N 5/30-5/378