(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7516009号

(P7516009)

(45)発行日 令和6年7月16日(2024.7.16)

(24)登録日 令和6年7月5日(2024.7.5)

(51)国際特許分類

|        |                 |        |       |

|--------|-----------------|--------|-------|

| H 03 B | 7/08 (2006.01)  | H 03 B | 7/08  |

| G 01 N | 21/01 (2006.01) | G 01 N | 21/01 |

| G 01 N | 21/17 (2006.01) | G 01 N | 21/17 |

F I

D

A

請求項の数 17 (全21頁)

(21)出願番号 特願2019-28242(P2019-28242)

(22)出願日 平成31年2月20日(2019.2.20)

(65)公開番号 特開2020-136910(P2020-136910)

A)

(43)公開日 令和2年8月31日(2020.8.31)

審査請求日 令和4年2月18日(2022.2.18)

前置審査

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110002860

弁理士法人秀和特許事務所

香取 篤史

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 海部 紀之

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

審査官 及川 尚人

最終頁に続く

(54)【発明の名称】 発振器、撮像装置

## (57)【特許請求の範囲】

## 【請求項1】

負性抵抗素子を含む共振器と、

前記負性抵抗素子に電圧を印加する電圧バイアス回路と、

抵抗と容量とが電気的に直列に接続されているシャント素子と、

1または複数の第2シャント素子と、

を備え、

前記共振器と前記シャント素子とは、前記電圧バイアス回路の正側電源端子および負側電源端子のそれぞれに並列に接続されて、電源電圧が供給され、

前記シャント素子の一方の端子は、前記共振器と前記電圧バイアス回路間の配線に接続されており、

前記1または複数の第2シャント素子のそれぞれは、容量を含み、

前記電圧バイアス回路に対して、前記1または複数の第2シャント素子のそれぞれと前記負性抵抗素子と前記シャント素子とが電気的に並列に接続されており、

前記シャント素子と前記1または複数の第2シャント素子とはそれぞれ、高周波側のカットオフ周波数に対応する波長の1/4以下の長さの配線によって、前記負性抵抗素子と接続されている、

ことを特徴とする発振器。

## 【請求項2】

前記シャント素子と前記1または複数の第2シャント素子とはそれぞれ、

前記負性抵抗素子と接続する配線の長さが短いほど、より高い周波数帯域の電磁波の発振を抑制する、

ことを特徴とする請求項1に記載の発振器。

**【請求項 3】**

前記1または複数の第2シャント素子のうちいずれかと前記共振器とは、同一のチップに形成されている、

ことを特徴とする請求項1または2に記載の発振器。

**【請求項 4】**

前記シャント素子と前記1または複数の第2シャント素子とのそれぞれは、互いに異なる部材に形成されている、

ことを特徴とする請求項1から3のいずれか1項に記載の発振器。

**【請求項 5】**

前記1または複数の第2シャント素子のそれぞれは、抵抗を含まない、

ことを特徴とする請求項1から4のいずれか1項に記載の発振器。

**【請求項 6】**

負性抵抗素子を含む共振器と、

前記負性抵抗素子に電圧を印加する電圧バイアス回路と、

抵抗と容量とが電気的に直列に接続されているシャント素子と、

を備え、

前記共振器と前記シャント素子とは、前記電圧バイアス回路の正側電源端子および負側電源端子のそれぞれに並列に接続されて、電源電圧が供給され、

前記シャント素子の一方の端子は、前記共振器と前記電圧バイアス回路間の配線に接続されており、

前記シャント素子が有する容量の容量値をCとし、前記シャント素子が有する抵抗の抵抗値をRとし、前記シャント素子の低周波側のカットオフ周波数をf<sub>0</sub>とすると、 $R / 10 \times (2 \times f_0 \times C)$ を満たす、

ことを特徴とする発振器。

**【請求項 7】**

前記負性抵抗素子と前記シャント素子とを接続する配線の長さは、前記共振器が発振する電磁波の波長の1/4以下である、

ことを特徴とする請求項6に記載の発振器。

**【請求項 8】**

前記共振器および前記シャント素子は、同一のチップに形成されている、

ことを特徴とする請求項6または請求項7に記載の発振器。

**【請求項 9】**

前記電圧バイアス回路が形成された第1基板と、

前記共振器が形成された第2基板と、

をさらに有し、

前記第1基板と前記第2基板とは、ケーブルを介して電気的に接続されている、

ことを特徴とする請求項1から8のいずれか1項に記載の発振器。

**【請求項 10】**

前記シャント素子が有する抵抗の抵抗値は、負性抵抗領域における前記負性抵抗素子のインピーダンスの絶対値の1/2倍以上、2倍以下の値であり、

前記負性抵抗領域は、電圧電流特性において、電圧の増加に応じて電流が減少する領域である、

ことを特徴とする請求項1から9のいずれか1項に記載の発振器。

**【請求項 11】**

前記電圧バイアス回路は、交流の電圧を前記負性抵抗素子に印加する、

ことを特徴とする請求項1から10のいずれか1項に記載の発振器。

**【請求項 12】**

10

20

30

40

50

前記共振器は、アンテナを有し、

前記シャント素子は、前記アンテナから離間して配置されている、

ことを特徴とする請求項 1 から 1\_1 のいずれか 1 項に記載の発振器。

【請求項 1 3】

前記シャント素子は、配線を介してアンテナと接続している、

ことを特徴とする請求項 1\_2 に記載の発振器。

【請求項 1 4】

前記容量は、2 つの電極を有する、

ことを特徴とする請求項 1 から 1\_3 のいずれか 1 項に記載の発振器。

【請求項 1 5】

前記共振器と前記シャント素子は、第 2 基板に配され、

前記第 2 基板の上には、第 1 電極と第 2 電極とが配されており、

前記第 1 電極および前記第 2 電極は、前記電圧バイアス回路と電気的に接続する、

ことを特徴とする請求項 1 から 1\_4 のいずれか 1 項に記載の発振器。

10

【請求項 1 6】

前記共振器が発振する電磁波の周波数は、30 GHz 以上 30 THz 以下である、

ことを特徴とする請求項 1 から 1\_5 のいずれか 1 項に記載の発振器。

【請求項 1 7】

請求項 1 から 1\_6 のいずれか 1 項に記載の発振器を有する照明装置と、

前記発振器が発振した電磁波が照射された被対象を撮像する撮像素子と、

を備える、

ことを特徴とする撮像装置。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発振器、撮像装置に関する。

【背景技術】

【0002】

30 GHz ~ 30 THz の周波数帯の所定の電磁波であるテラヘルツ波を発生させる小型の発振器として、共鳴トンネルダイオード (RTD) などの負性抵抗素子を含む発振回路 (共振器) を用いることがある。この発振回路は、負性抵抗素子が負性抵抗の特性を有する電圧値を、負性抵抗素子に印加するような電圧バイアス回路と接続している。なお、負性抵抗素子は、所定の電磁波の周波数 (所定の周波数) だけでなく、広い周波数帯域において利得を持つ。このため、負性抵抗素子と電圧バイアス回路を接続することによって、所定の周波数よりも低い共振点での電磁波の発振 (以下、「寄生発振」と呼ぶ) が生じるので、これを抑制する必要がある。

30

【0003】

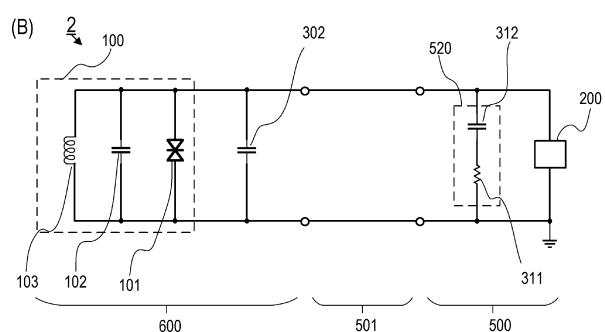

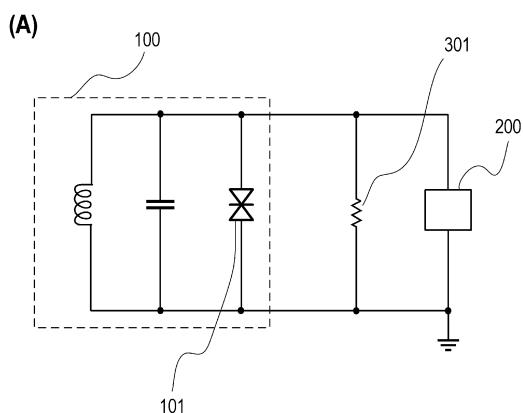

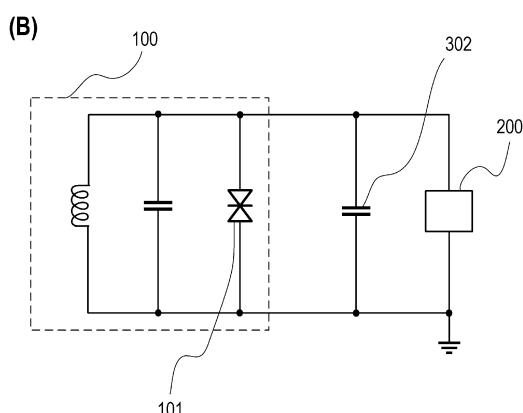

これに關し、特許文献 1 および特許文献 2 には、負性抵抗素子 101 を含む発振回路 100 と電圧バイアス回路 200 とを含む発振器が開示されている。特許文献 1 では、図 15 (A) が示すように、負性抵抗素子 101 に対して並列に抵抗素子 301 (シャント抵抗素子；抵抗) を配置することで、寄生発振を抑制する構成が開示されている。また、特許文献 2 では、図 15 (B) が示すように、負性抵抗素子 101 に対して並列に容量素子 302 (シャント容量素子；容量) を配置することで、寄生発振を抑制する構成が開示されている。

40

【先行技術文献】

【特許文献】

【0004】

【文献】特許第 5717336 号公報

【文献】特許第 5612842 号公報

【発明の概要】

50

## 【発明が解決しようとする課題】

## 【0005】

しかし、特許文献1に係る発振器では、抵抗素子301が存在するため、電圧バイアス回路200は、定的な直流電流を流す必要がある。このため、所定の電磁波の発振を安定に行うために、発振器は電力を消費し続ける必要があるという課題がある。一方、特許文献2に係る発振器では、電圧バイアス回路200は、瞬時電流を流すのみで直流電流が不要なため、特許文献1に係る発振器に比べて消費電力は低減することができる。しかし、容量素子302による寄生発振の抑制には、安定性に課題がある。

## 【0006】

従って、本発明は、消費電力の増加を抑制しつつ、寄生発振の抑制を安定して行うことができる発振器を提供することを目的とする。

10

## 【課題を解決するための手段】

## 【0007】

本発明の1つの態様は、

負性抵抗素子を含む共振器と、

前記負性抵抗素子に電圧を印加する電圧バイアス回路と、

抵抗と容量とが電気的に直列に接続されているシャント素子と、

1または複数の第2シャント素子と、

を備え、

前記共振器と前記シャント素子とは、前記電圧バイアス回路の正側電源端子および負側電源端子のそれぞれに並列に接続されて、電源電圧が供給され、

20

前記シャント素子の一方の端子は、前記共振器と前記電圧バイアス回路間の配線に接続されており、

前記1または複数の第2シャント素子のそれぞれは、容量を含み、

前記電圧バイアス回路に対して、前記1または複数の第2シャント素子のそれぞれと前記負性抵抗素子と前記シャント素子とが電気的に並列に接続されており、

前記シャント素子と前記1または複数の第2シャント素子とはそれぞれ、高周波側のカットオフ周波数に対応する波長の1/4以下の長さの配線によって、前記負性抵抗素子と接続されている、

ことを特徴とする発振器である。

30

## 【発明の効果】

## 【0008】

本発明によれば、発振器において、消費電力の増加を抑制しつつ、寄生発振の抑制を安定して行うことができる。

## 【図面の簡単な説明】

## 【0009】

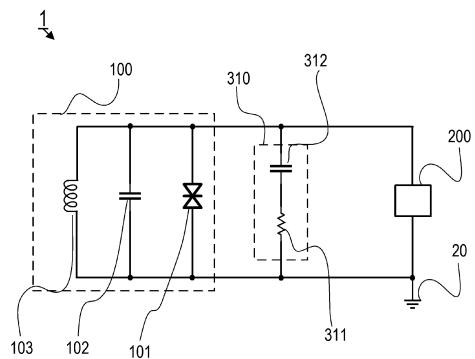

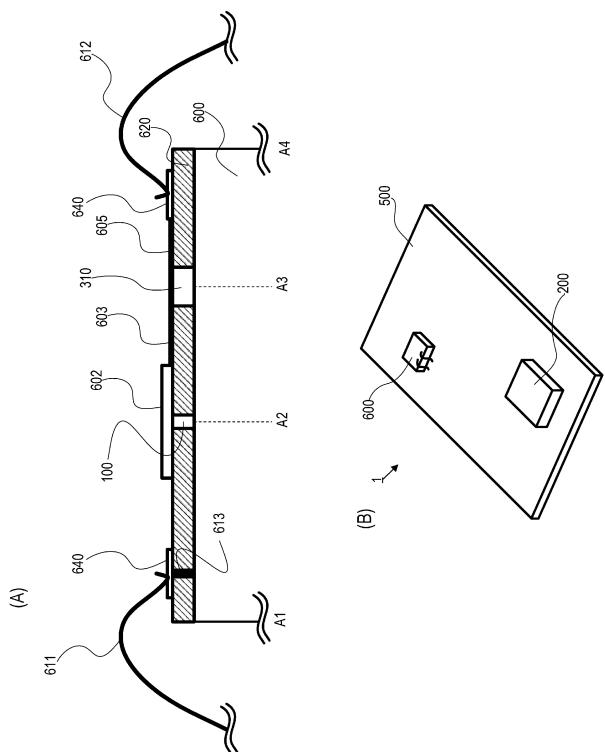

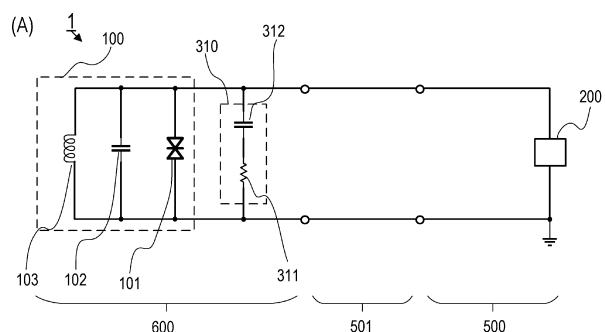

【図1】実施形態1に係る発振器の回路構成図である。

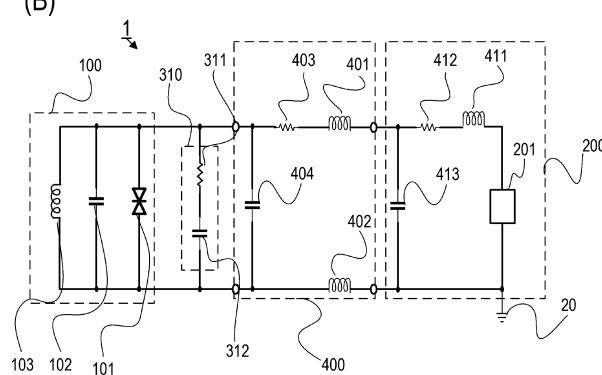

【図2】負性抵抗素子における電圧-電流特性を説明する図である。

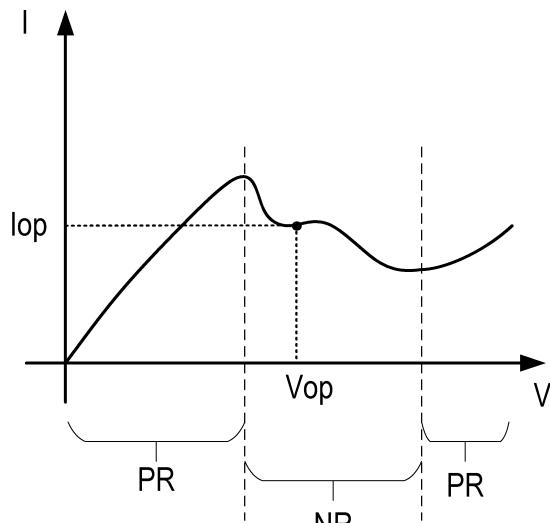

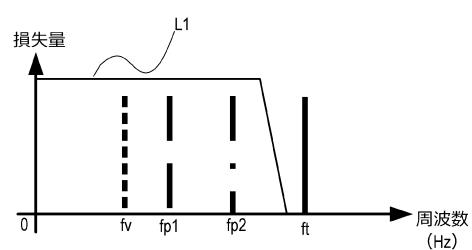

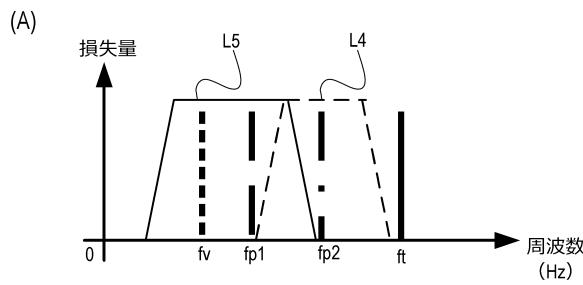

【図3】実施形態1および比較例に係る電磁波の損失を示す図である。

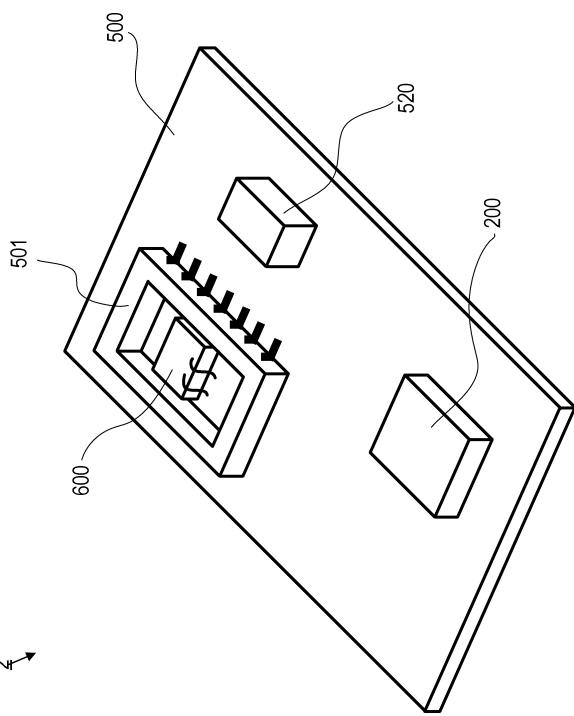

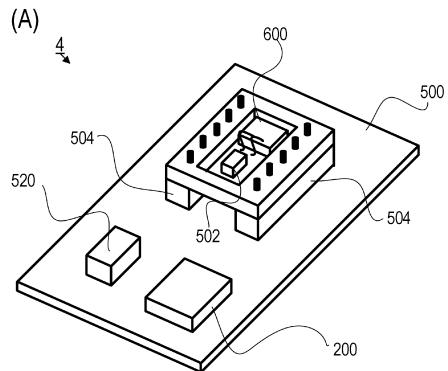

【図4】実施形態1に係る発振器の外部構成を示す図である。

【図5】実施形態1に係る発振器の外部構成を示す図である。

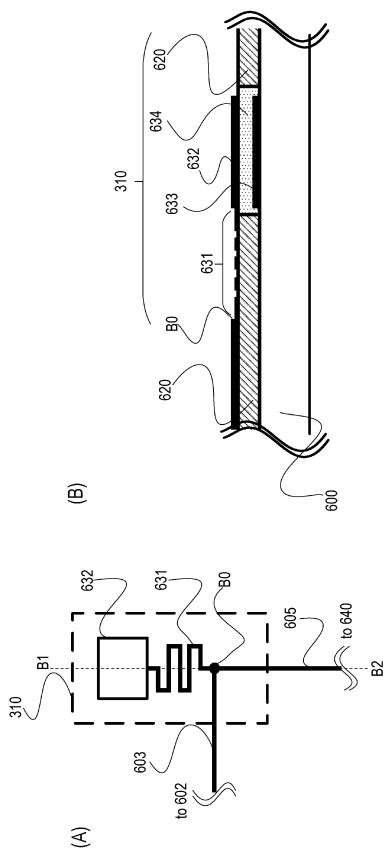

【図6】実施形態1に係るシャント素子の外部構成を示す図である。

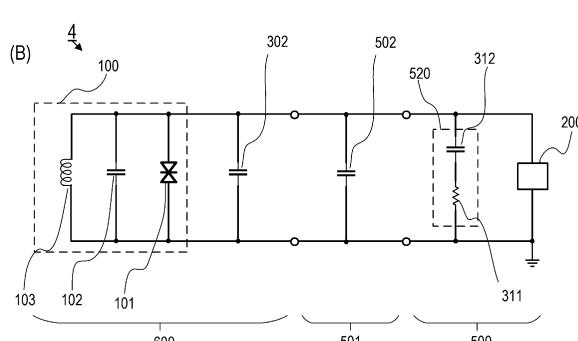

【図7】実施形態1および実施形態2に係る発振器の回路構成図である。

【図8】実施形態2に係る発振器の外部構成を示す図である。

【図9】実施形態2および実施形態3に係る電磁波の損失を示す図である。

【図10】実施形態3および実施形態4に係る発振器の回路構成図である。

【図11】実施形態3に係る発振器の外部構成を示す図である。

【図12】実施形態4および実施形態5に係る発振器の外部構成を示す図である。

【図13】実施形態5に係る発振器を説明する図である。

【図14】実施形態6および変形例1に係る撮像装置を説明する図である。

40

50

【図15】従来の発振器を説明する回路構成図である。

【発明を実施するための形態】

【0010】

以下、図面を用いて本発明の実施形態について説明する。ただし、本発明は、これらの実施形態に限定されず、その要旨の範囲内で種々の変形、変更が可能である。

【0011】

<実施形態1>

本実施形態に係る発振器では、負性抵抗素子に電圧を印加する電圧バイアス回路に対して、当該負性抵抗素子と、直列に配置した抵抗および容量を有するシャント素子とを電気的に並列に接続する。これにより、消費電力の増加を抑制しつつ、寄生発生の抑制を安定して行うことのできる発振器を実現する。

【0012】

【発振器の回路構成】

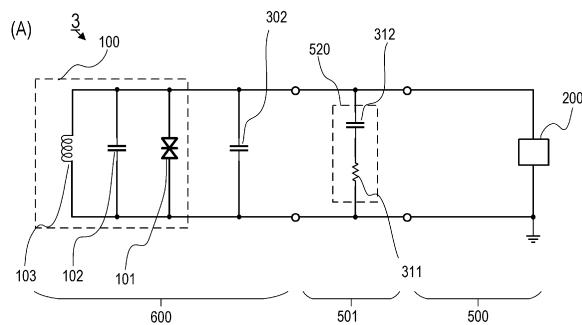

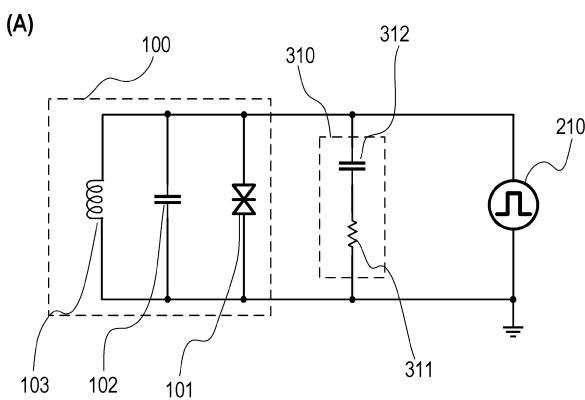

本実施形態に係る発振器1の回路構成について図1(A)、図1(B)を用いて説明する。図1(A)は、発振器1の簡易的な回路構成(最小回路構成)を示しており、図1(B)は、発振器1のより詳細な回路構成を示している。発振器1は、発振回路100、電圧バイアス回路200、シャント素子310を有する。

【0013】

発振回路100は、負性抵抗素子101、容量102、インダクタ103といった素子を有する共振器(テラヘルツ発振回路)である。より詳細には、負性抵抗素子101と、これに対して並列に接続された容量102とインダクタ103が、発振回路100を構成している。発振回路100は、電圧バイアス回路200により、負性抵抗素子101に所定の電圧が印加されることにより、30GHz～30THzの間において、所定の周波数の電磁波(テラヘルツ波；所定の電磁波)の発振を行う。つまり、所定の電磁波は、発振回路100の設計パラメータで主に決まる、発振回路100が発振する(共振する)電磁波である。なお、以下では、発振回路100による所定の電磁波(テラヘルツ波)の発振を、「テラヘルツ発振」と呼ぶ。

【0014】

負性抵抗素子101には、電圧制御型負性抵抗を用いることができる。具体的には、電流注入型の共鳴トンネルダイオード(Resonant tunneling Diode: R T D)を用いることにより、所定の電磁波の周波数(テラヘルツ周波数)での発振回路100を構成することができる。この共鳴トンネルダイオードは、GaAs, InP基板上に格子整合系でエピタキシャル成長されたGaAs/AlGaAs, InGaAs/InAlAsから成る量子井戸により構成される。

【0015】

図2は、負性抵抗素子101(R T D)の両端子(アノード、カソード)間に印加した電圧Vと、負性抵抗素子101に流れる電流Iとの電圧-電流特性(電圧電流特性)を示す。この電圧-電流特性では、電圧増加に対して電流値が増加する領域P Rと、電圧増加に対して電流値が減少する領域N Rとの2つの領域に分けることができる。この電圧増加に対して、電流値が減少する領域N Rが、負性抵抗の特性を有している領域であり、以後、「負性抵抗領域」と呼ぶ。ここで、負性抵抗領域中の電圧値V<sub>op</sub>を、負性抵抗素子101の両端子間に印加することにより、負性抵抗素子101と、容量102およびインダクタ103との間で、テラヘルツ周波数f<sub>t</sub>の電磁波(テラヘルツ波)が発振する。なお、印加する電圧値V<sub>op</sub>は、発振の安定性を高めるために、負性抵抗領域N Rの電圧範囲の中心付近の値を設定することが望ましい。ただし、これに限らず、負性抵抗領域であれば、それ以外の電圧を印加することもできる。

【0016】

また、電圧値V<sub>op</sub>を印加しているときに、負性抵抗素子101に流れる電流値がI<sub>op</sub>である。なお、電圧値V<sub>op</sub>の具体的な値としては、負性抵抗素子101が有するパラメータによって変化するが、一般的には、概ね0.5～1.5V(ボルテージ)の範囲(

10

20

30

40

50

0.5 V 以上 1.5 V 以下) であることが多い。一方、電流値  $I_{op}$  の具体的な値としては、同じように負性抵抗素子 101 が有するパラメータによって変化するが、一般的には、概ね 20 ~ 150 mA (ミリアンペア) の範囲 (20 mA 以上 150 mA 以下) であることが多い。ただし、この電圧値範囲や電流値範囲に限定されず、この範囲以外でも適用可能であり、同様の効果を得ることができる。

#### 【0017】

電圧バイアス回路 200 は、負性抵抗素子 101 (R TD) に負性抵抗領域の電圧値  $V_{op}$  (直流電圧) を印加するための回路である。電圧バイアス回路 200 は、例えば、図 1 (B) が示すように、理想的な電圧源 201 と、寄生インダクタ 411、寄生抵抗 412、寄生容量 413 などを有している。また、電圧バイアス回路 200 自身は、寄生インダクタ 411、寄生抵抗 412、寄生容量 413 といった寄生素子を有するため、理想的な電圧源ではない。そのため、テラヘルツ周波数  $f_t$  以外の周波数での電磁波の発振 (寄生発振) が、発振回路 100 が有する素子と、電圧バイアス回路 200 が有する寄生素子との間で発生する場合がある。

10

#### 【0018】

また、図 1 (A) では省略しているが、図 1 (B) が示すように、発振器 1 における様々な機能を実現するために、発振回路 100 と電圧バイアス回路 200 との間には、配線部 400 が存在する場合が多い。

#### 【0019】

配線部 400 は、発振回路 100 と電圧バイアス回路 200 との間に形成され、例えば、寄生インダクタ 401、寄生インダクタ 402、寄生抵抗 403、寄生容量 404 の 4 つの寄生素子を有する。そのため、発振回路 100 が有する素子と、配線部 400 が有する寄生素子との間で、テラヘルツ周波数  $f_t$  と異なる周波数での、寄生発振が発生する場合がある。

20

#### 【0020】

シャント素子 310 は、上述した発振回路 100 が有する素子と他の寄生素子とによる寄生発振を防止する。シャント素子 310 は、抵抗素子 311 (シャント抵抗素子) と容量素子 312 (シャント容量素子) から構成され、それらが直列に接続された配置である。なお、本実施形態では、「シャント素子」とは、一方の端子が、共通配線 (基板；グラウンド 20) に接続されており、他方の端子が、発振回路 100 と電圧バイアス回路 200 間の配線に接続される素子である。

30

#### 【0021】

##### [電磁波の損失特性]

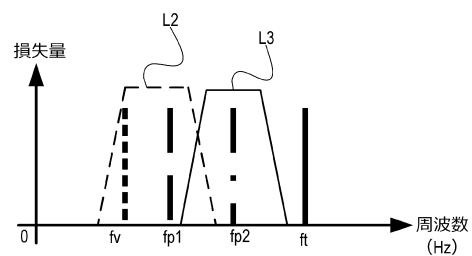

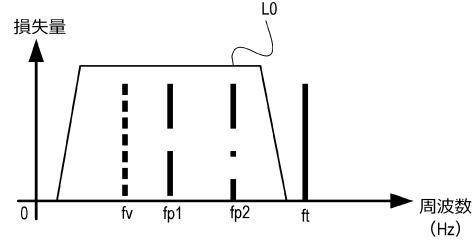

続いて、本実施形態のシャント素子 310 による寄生発振の抑制の効果を図 3 (A) ~ 図 3 (C) を用いて説明する。図 3 (A) および図 3 (B) は、比較例の発振器が有するシャント素子による電磁波の損失特性 (遮断特性) を示す。図 3 (C) は、本実施形態に係る発振器 1 のシャント素子 310 による電磁波の損失特性を示す。

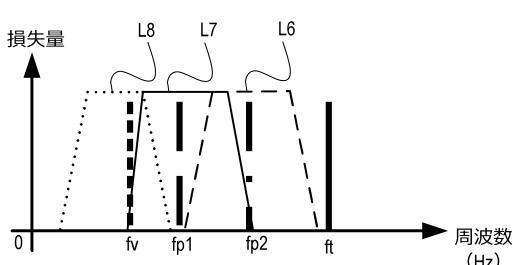

30

#### 【0022】

ここで、図 3 (A) ~ 図 3 (C) は、シャント素子が有する、周波数ごとの電磁波の損失特性を示す模式図である。また、図 3 (A) ~ 図 3 (C) が示すグラフでは、横軸は、周波数を示し、縦軸は、シャント素子での電磁波の損失の大きさの一例を示している。ここで、損失 (損失量) が多いほど、電磁波の発振を抑制することができる。なお、以下では、シャント素子が損失を有する範囲の境界の周波数を「カットオフ周波数 (遮断周波数)」と呼ぶ。つまり、シャント素子は、高周波側のカットオフ周波数と低周波側のカットオフ周波数との間の周波数帯域の電磁波の発振を抑制することができる。

40

#### 【0023】

図 3 (A) ~ 図 3 (C) において、テラヘルツ周波数が  $f_t$  (30 GHz 以上 30 THz 以下) であり、寄生発振周波数が  $f_{p1}$ ,  $f_{p2}$ ,  $f_v$  である。寄生発振周波数  $f_{p1}$ ,  $f_{p2}$  は、発振回路 100 と配線部 400 の寄生素子とにより発振する電磁波の発振周波数である。また、寄生発振周波数  $f_v$  は、発振回路 100 と、電圧バイアス回路 200

50

内の寄生素子とにより発振する電磁波の発振周波数である。

【0024】

(シャント素子として抵抗素子を用いる場合)

まず、図3(A)は、シャント素子として「抵抗素子(抵抗)」を用いた場合の損失特性例を示している。この場合、シャント素子は、テラヘルツ周波数  $f_t$  より少し小さい全ての周波数において、損失  $L_1$  を有しているため、寄生発振周波数  $f_{p1}$ ,  $f_{p2}$ ,  $f_v$  における寄生発振を抑制できる。つまり、本例では、発振器は、広い範囲の周波数帯域に対して損失を有するため、十分に寄生発振を抑制することができる。一方、本例の発振器では、抵抗素子に対して定常的に電流が流れてしまうため、不要な電力消費が生じてしまう。

10

【0025】

(シャント素子として容量素子を用いる場合)

図3(B)は、シャント素子として「容量素子(容量)」を用いた場合の損失特性例を示している。図3(B)では、発振器が、2つの容量素子を備えた構成の例について説明する。より詳細には、発振器は、所定の容量値の容量素子(容量値の小さい容量素子)と、これよりも容量値の大きい容量素子を備える。

【0026】

容量値の小さい容量素子は、テラヘルツ周波数  $f_t$  より低い周波数の  $f_{p2}$  の周辺で損失  $L_3$  を有しており、寄生発振周波数  $f_{p2}$  での寄生発振を抑制する。しかし、当該容量素子のみでは、より低い周波数での損失を発生させることができないため、発振器は、容量値の大きい容量素子をさらに備えている。容量値の大きい容量素子は、寄生発振周波数  $f_{p2}$  より低い寄生発振周波数  $f_{p1}$ ,  $f_v$  の周辺で損失  $L_2$  を有しており、寄生発振周波数  $f_{p1}$ ,  $f_v$  での寄生発振を抑制する。

20

【0027】

しかし、本例では、寄生発振周波数  $f_v$  の周波数が低いような場合や、 $f_v$  より低い寄生発振周波数の成分があった場合には、低周波数領域に対して容量素子により損失を発生させることが難しいため、寄生発振の抑制が難しくなる。これは、周波数が高い領域に対しては、容量素子のインピーダンスを低くすることが容易であるが、周波数が低い領域に対しては、容量素子のインピーダンスを低くすることが難しいためである。また、シャント素子として用いられる容量素子と配線部400が有する寄生インダクタ402による共振が発生して、当該容量素子が寄生発振を引き起こす可能性すらある。

30

【0028】

(シャント素子として抵抗素子および容量素子を用いる場合；本実施形態の場合)

図3(C)は、本実施形態のように、シャント素子310として、抵抗素子311(抵抗)と容量素子312(容量)を直列に接続した素子を用いる場合の損失特性例を示している。図3(C)が示すように、高い周波数においては、抵抗素子311が損失  $L_0$  を有する。つまり、抵抗素子311が、寄生発振を抑制するシャント素子として動作する。このように、発振回路100において発生した不要なエネルギーを抵抗素子311により適正に損失させてしまうことによって、配線部400や電圧バイアス回路200の寄生素子と発振回路100との結合を防ぎ、寄生発振を抑制することができる。

40

【0029】

一方、シャント素子310の低周波側のカットオフ周波数以下においては、容量素子312のインピーダンスが大きいため、シャント素子310によって発生する損失がない。言い換えると、直流付近では、シャント素子310がオープンの状態であり、抵抗素子311によって損失が発生しないため、発振器1全体として電力の消費を抑制できる。従って、低周波側のカットオフ周波数が、発振回路100内における最も低い寄生発振周波数  $f_v$  より低く設定されることによって、発振器1の電力の消費を抑制することができる。なお、低周波側のカットオフ周波数は、容量素子312と抵抗素子311の時定数により決まる周波数であるため、抵抗値と容量値をそれぞれ調整するによって、非常に低い周波数まで調整することが可能である。

50

## 【0030】

なお、本実施形態では、寄生インダクタ401もしくは寄生インダクタ411とシャント素子310内の容量素子312との間の共振があつても、シャント素子310における抵抗素子311の損失により寄生発振を抑制することができる。

## 【0031】

このように本実施形態に係るシャント素子310は、寄生発振を抑制する抵抗素子311（抵抗）と、直流付近での電力の消費を抑える容量素子312（容量）とを有する。このことにより、寄生発振の抑制と不要な電力の抑制を両立することができる。

## 【0032】

なお、抵抗素子311には、安定したテラヘルツ波発振を行うために、負性抵抗領域において負性抵抗素子101が有するインピーダンスの絶対値 $|Z_{rtd}|$ と、近い値の抵抗値が選ばれているとよい。具体的には、当該抵抗値には、 $|Z_{rtd}|$ の半分から2倍まで（1/2倍以上2倍以下）の間の値が選ばれるとよい。さらに、望ましくは、当該抵抗値は、 $|Z_{rtd}|$ の0.8倍から1.2倍（0.8倍以上1.2倍以下）の値であるとよい。

10

## 【0033】

このように抵抗値が選択されることにより、より効果的に、寄生素子による寄生発振を抑制して、発振回路100において安定したテラヘルツ発振をすることができる。なお、抵抗素子311の負性抵抗領域でのインピーダンスの絶対値 $|Z_{rtd}|$ は、典型的には、数オームから数十オームの値の範囲である。また、発振器1の発振周波数によっては、絶対値 $|Z_{rtd}|$ は、より大きな百オーム程度であつてもよい。

20

## 【0034】

一方、容量素子312の容量値は、低周波側のカットオフ周波数 $f_0$ （抵抗素子311と容量素子312との時定数により決まる周波数）が、寄生発振を抑制する下限の周波数以下をとるような値が設定されるとよい。具体的には、容量素子312の容量値 $C$ は、抵抗素子311の抵抗値 $R$ に対して、周波数 $f_0$ における容量素子312のインピーダンス $1/(2\pi f_0 \times C)$ が十分低い値をとるように設定される。好ましくは、インピーダンス $1/(2\pi f_0 \times C)$ が、抵抗値 $R$ の数分の1以下の値をとるように、さらに好ましくは10分の1以下の値をとるように、容量値 $C$ が設定される。つまり、 $R/10 = 1/(2\pi f_0 \times C)$ を満たすことが望ましい。例えば、抵抗値 $R$ が10Ωであり、周波数 $f_0$ が1MHzであれば、容量素子312の容量値 $C$ は160pF以上であることが好ましい。

30

## 【0035】

なお、この容量値 $C$ は、実装サイズの制約や、実施形態6で後述する交流バイアス回路を用いる際のスイッチング速度での問題がなければ、できるだけ大きな値にしておくことが望ましい。これらの抵抗素子311や容量素子312の値は、発振回路が有するパラメータと抑制したい寄生発振周波数との関係に基づいて、最適な値に設定されるとよい。

## 【0036】

加えて、シャント素子310は、配置する位置を考慮する必要がある。具体的には、負性抵抗素子101とシャント素子310とを接続する配線の長さを、シャント素子310が寄生発振を抑制しようとする（損失を有する）最大の寄生発振周波数の電磁波の波長の1/4以下にする必要がある。図3（C）の示す例であれば、当該配線の長さを、寄生発振周波数 $f_{p2}$ の電磁波の波長の1/4にする必要がある。これは、交流信号の波長が短いと、配線の位置が少し変わっただけで、位相が大きく変化してしまい、配線端での反射による等価容量や等価インダクタが発生するからである。特に、波長の短いギガヘルツからテラヘルツでの寄生発振を抑制する場合には、負性抵抗素子101のより近傍にシャント素子310を配置する必要がある。このように、負性抵抗素子101とシャント素子310とを接続する配線の長さが波長の1/4以下であれば、配線端での反射による等価容量や等価インダクタの発生を抑えることができ、寄生発振を抑制することができる。なお、シャント素子310が寄生発振を抑制しようとする最大の寄生発振周波数の電磁波の波長とは、シャント素子310の高周波側のカットオフ周波数に対応する波長というこ

40

50

ともできる。

【0037】

なお、所定の電磁波（テラヘルツ波）の波長  $m$  の  $1/4$  以下に、負性抵抗素子 101 とシャント素子 310 とを接続する配線の長さをしてもよい。これによれば、所定の電磁波のテラヘルツ周波数  $f_t$  よりも周波数の低い寄生発振周波数の全てにおいて、配線端での反射による等価容量や等価インダクタの発生を抑えることができるため、より効果的に寄生発振を抑制することができる。

【0038】

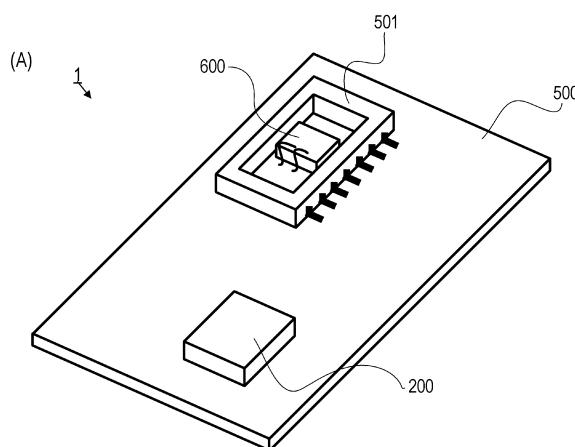

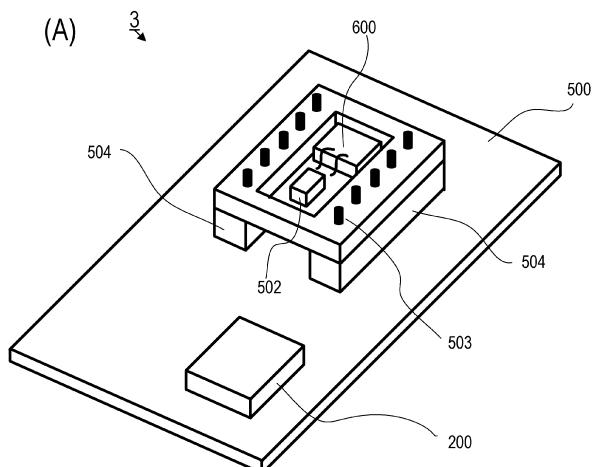

【発振器の外部構成について】

以下にて、発振器 1 の外部構成について、図 4 (A) ~ 図 6 (B) を用いて説明する。

図 4 (A) は、本実施形態の発振器 1 の外部構成を示す模式図であり、図 4 (B) は、発振器 1 が有するチップ 600 および周辺をより詳細に示す模式図である。

【0039】

発振器 1 は、図 4 (A) が示すように、プリント回路基板 500 (PCB)、パッケージ 501 (PKG)、チップ 600 (Chip)、電圧バイアス回路 200 を有する。

【0040】

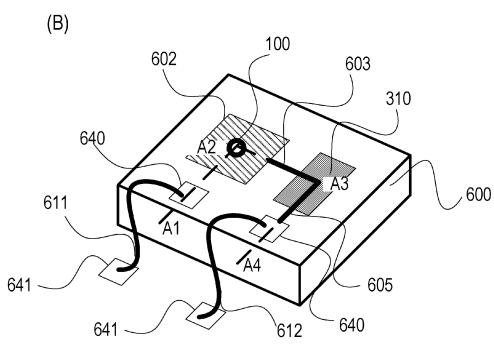

チップ 600 およびその周辺には、図 4 (B) が示すように、チップ 600 およびワイヤー 611、ワイヤー 612、ワイヤーボンディング用（ワイヤボン用）の電極 641 が形成されている。また、チップ 600 には、負性抵抗素子 101 を含む発振回路 100、シャント素子 310、アンテナ 602、配線 603、配線 605、ワイヤーボンディング用の 2 つの電極 640 が形成されている。従って、本実施形態では、発振器 1 は、図 7 (A) が示すような回路構成であり、発振回路 100 とシャント素子 310 がチップ 600 に形成されており、電圧バイアス回路 200 がプリント回路基板 500 に形成されている。

【0041】

チップ 600 は、パッケージ 501 内に実装されている。図 4 (B) が示すように、チップ 600 の 2 つの電極 640 は、パッケージ 501 が有する 2 つの電極 641 とそれぞれ、ワイヤーボンディングによりワイヤー 611, 612 によって電気的に接続されている。なお、チップ 600 は、典型的には、1 mm 弱角から、数 mm 角のものを用いるが、それよりサイズの大きな 10 mm 角のものを用いることもできる。

【0042】

また、プリント回路基板 500 上には、図 4 (A) が示すように、パッケージ 501 と電圧バイアス回路 200 が実装されている。このため、プリント回路基板 500 とパッケージ 501 とが有する配線を介して、チップ 600 における発振回路 100 と電圧バイアス回路 200 とが電気的に接続されている。これにより、電圧値  $V_{op}$  の直流電圧が、電圧バイアス回路 200 から発振回路 100 に印加され、テラヘルツ周波数  $f_t$  において発振回路 100 がテラヘルツ発振するように設定されている。

【0043】

図 5 (A) は、図 4 (B) のチップ 600 における A1 - A2 - A3 - A4 断面を模式的に示す図である。図 5 (A) が示すように、チップ 600 上には、絶縁膜 620 が形成されている。発振回路 100 は、絶縁膜 620 の深さ方向に埋め込まれるように、チップ 600 上に形成されており、発振回路 100 の一方の端子はチップ 600 (チップ 600 の基板電位) に接続されている。発振回路 100 の他方の端子は、チップ 600 上に形成されたアンテナ 602 に接続されている。なお、チップ 600 の基板電位は、絶縁膜 620 を貫通した配線 613 により、電極 640 に接続されている。

【0044】

シャント素子 310 は、一方の端子がチップ 600 (チップ 600 の基板電位) に接続されている。また、シャント素子 310 の他方の端子は、配線 603 を介してアンテナ 602 と、配線 605 を介して電極 640 とに接続されている。従って、本実施形態では、配線 603 が、シャント素子 310 と発振回路 100 (負性抵抗素子 101) とを接続する配線である。

10

20

30

40

50

## 【0045】

アンテナ602のサイズは、テラヘルツ周波数  $f_t$  に応じて、最適な大きさにすればよく、例えば、百  $\mu\text{m}$  角から数百  $\mu\text{m}$  角の大きさである。なお、アンテナ602には、テラヘルツ周波数  $f_t$  によっては、より大きな数  $\text{mm}$  角のものを用いることができる。また、本実施形態の発振器1のアンテナ602は、正方形状のアンテナに限らず、所定の電磁波(テラヘルツ波)を発振することができれば、どのようなアンテナ形状でもよい。

## 【0046】

## (シャント素子の詳細な構成)

シャント素子310の詳細な構成例を、図6(A)、図6(B)を用いて説明する。図6(A)は、図4(B)が示しているシャント素子310付近を拡大した模式図である。

10

## 【0047】

シャント素子310は、アンテナ602への配線603と、電極640への配線605との接点B0に接続されている。図6(A)が示すように、接点B0には、抵抗素子311の抵抗部631が接続され、その先で、容量素子312の上部電極632が接続されている。

## 【0048】

図6(B)は、図6(A)のB1-B2断面によって、シャント素子310を切断した模式図である。チップ600上に、上部電極632と同じ大きさの下部電極633が形成されており、下部電極633と誘電膜634と上部電極632とが順に積層されることにより、コンデンサを形成している。

20

## 【0049】

下部電極633は、チップ600と電気的に接続されているので、負性抵抗素子101の両端子に対して、シャント素子310が電気的に並列に配置された構成となっている。

## 【0050】

抵抗部631は、金属薄膜にパターンを形成して、配線長を長くした構成により容易に形成することができる。当該配線長を長くした構成は、図6(A)が示す例では、ミアンダ配線構成である。金属薄膜は、アルミニウムをはじめとした、半導体の配線に対して用いられる金属であれば、任意のものを用いることができる。また、金属薄膜の抵抗値(シート抵抗値)は、金属の種類、配線の幅、厚さ、長さなどを調整して容易に調整することができる。なお、金属薄膜の代わりには、ポリシリコンへのドーピング量を調整して抵抗値を制御したポリシリコン抵抗をはじめとして、チップ600上に所望の抵抗を形成できるものであれば、任意のものを用いることができる。

30

## 【0051】

誘電膜634は、シリコン酸化膜やシリコン窒化膜などを用いて容易に形成することができる。具体的には、所望の被誘電率に応じて、低誘電率の材料や高誘電率の材料を選択することにより誘電膜634を形成可能である。

## 【0052】

上部電極632および下部電極633は、アルミニウムをはじめとした金属材料により容易に形成することができる。ここで、下部電極633は、誘電膜634を形成する工程において発生する温度に耐えられる材料を選択する必要がある。また、ポリシリコンを上下電極にしたキャパシタやMOSキャパシタをはじめとする所望の容量値をチップ600上に実現できるのであれば、上部電極632および下部電極633の形成に任意のものを用いてよい。また、使用上の問題がなければ、チップ600を下部電極633の代わりとして用いることにより、下部電極633が含まれない構成も同様に用いることができる。

40

## 【0053】

なお、本実施形態では、絶縁膜620と誘電膜634は、別の材料によって構成されるものとするが、この構成に限らない。例えば、所望の容量値を形成することができれば、絶縁膜620と誘電膜634に対して、酸化シリコンや、窒化シリコン膜などの同じ絶縁膜を用いることもできる。同じ絶縁膜を用いることによれば、同じチップ600において異なる絶縁膜(誘電膜)を形成する必要がないため、よい簡易な構成で、簡易な製造プロ

50

口セスでチップ 600 を形成することができる。

【0054】

また、本実施形態では、発振回路 100 とシャント素子 310 とを同一の部材であるチップ 600 上に形成する構成であるため、負性抵抗素子 101 とシャント素子 310 の間の配線の長さ（配線 603 の長さ）を短くすることができる。つまり、負性抵抗素子 101 とシャント素子 310 とを接続する配線 603 の長さを、所定の電磁波の波長  $m$  の  $1/4$  の長さ以下に容易にすることができる。このため、発振器 1 によれば、サイズの小さな構成により、消費電力を抑制しつつ、寄生発振を安定的に抑制することができる。

【0055】

なお、本実施形態では、パッケージ 501 上にチップ 600 を形成した構成について説明したが、この形態に限らない。例えば、図 5 (B) が示すように、パッケージ 501 を介さずに、プリント回路基板 500 上にチップ 600 を直接形成した構成であってもよい。これにより、発振器 1 におけるパッケージ 501 を省くことができるので、より少ない構成要素によって発振器 1 を構成することができる。

【0056】

（効果）

本実施形態によれば、負性抵抗素子を含む発振回路を所定の周波数で発振させる発振器において、消費電力の増加を抑制し、寄生発振の抑制を安定的に行うことができる。

【0057】

<実施形態 2>

実施形態 2 に係る発振器 2 は、シャント素子の数と配置場所が実施形態 1 の発振器 1 と異なり、それ以外は実施形態 1 の発振器 1 と同じである。以下では、図 8 を用いて、本実施形態に係る発振器 2 を説明する。本実施形態に係る発振器 2 では、2 つのシャント素子のそれぞれが、異なる部材（チップとプリント回路基板）に形成されている。

【0058】

発振器 2 は、実施形態 1 に係る発振器 1 が有しているプリント回路基板 500、パッケージ 501、チップ 600、電圧バイアス回路 200 に加えて、シャント素子 520 をプリント回路基板 500 上に有する。

【0059】

チップ 600 は、実施形態 1 におけるシャント素子 310 の代わりに、シャント素子として容量素子 302 を有する。容量素子 302 は、容量素子 302 と発振回路 100（負性抵抗素子 101）とを接続する配線の長さが  $m$  の  $1/4$  以内であるように設計されており、テラヘルツ周波数  $f_t$  以下の高い周波数の寄生発振を抑制する。つまり、例えば、容量素子 302 は、図 9 (A) が示すように、テラヘルツ周波数  $f_t$  以下の寄生発振周波数  $f_{p2}$  の周辺において損失  $L_4$  を有する。なお、必ずしも、容量素子 302 と発振回路 100（負性抵抗素子 101）とを接続する配線の長さが  $m/4$  以内である必要はない。当該長さは、容量素子 302 が発振を抑制する（損失を有する）最大の寄生発振周波数  $f_{p2}$  の電磁波の波長の  $1/4$  以下であればよい。

【0060】

一方、容量素子 302 では、特定の周波数以下（例えば、寄生発振周波数  $f_{p1}$ ）の寄生発振は十分抑制できない。このため、プリント回路基板 500 において、特定の周波数以下の寄生発振を抑制するシャント素子 520 が形成されている。つまり、例えば、シャント素子 520 は、図 9 (A) が示すように、寄生発振周波数  $f_{p1}$ ,  $f_v$  の周辺において損失  $L_5$  を有する。

【0061】

また、シャント素子 520 は、シャント素子 520 と発振回路 100（負性抵抗素子 101）とを接続する配線の長さが、寄生発振周波数  $f_{p1}$  の波長  $p_1$  の  $1/4$  以内であるように設定されている。なお、シャント素子 520 は、電力消費の抑制の効果を得るために、図 7 (B) が示すように、実施形態 1 において説明したシャント素子 310 と同様に抵抗素子 311 と容量素子 312 を有する。また、シャント素子 520 が有する抵抗素

10

20

30

40

50

子 3 1 1 および容量素子 3 1 2 は、実施形態 1 において説明した抵抗値および容量値の条件を満たすように設計されているとよい。

【 0 0 6 2 】

このように、本実施形態では、容量素子 3 0 2 が高い周波数の寄生発振の抑制を行うため、発振回路 1 0 0 からシャント素子 5 2 0 をより遠くに配置することができる。そのため、チップ 6 0 0 上に形成することが難しい大きな部品をシャント素子 5 2 0 に用いる場合にも、シャント素子 5 2 0 を適切な位置に配置することができる。

【 0 0 6 3 】

なお、シャント素子 5 2 0 は、チップ抵抗やチップコンデンサなどの表面実装チップ部品を用いて形成するとよい。これによれば、抵抗素子 3 1 1 の抵抗値や容量素子 3 1 2 の容量値を任意に選択することができるからである。

10

【 0 0 6 4 】

チップ抵抗は、例えば、アルミナ基板上に、金属薄膜被膜などの抵抗体をスクリーン印刷して形成されるため、様々な抵抗値や精度のものを実現することができる。また、チップコンデンサは、誘電体シートを内部電極で挟んだ構造を幾層にも積層し、プレス・焼成して形成される。従って、チップコンデンサは、積層する数や、用いる誘電体シートを選択することにより、小さな容量値（例えば、数  $\mu F$ ）から大容量（例えば、数百  $\mu F$ ）まで対応することができる。

【 0 0 6 5 】

従って、本実施形態では、シャント素子 5 2 0 に対して、大きな容量の値も容易に選択することができるため、より低周波数の寄生発振が生じるような場合には、より安定的に寄生発振を抑制することができる。加えて、発振回路 1 0 0 が形成されているチップ 6 0 0 とは別の部材に、シャント素子 5 2 0 が存在する形態によれば、歩留まりの向上や、シャント素子 5 2 0 の設計の変更が容易であり、カスタマイズが実現し易いというメリットが得られる。

20

【 0 0 6 6 】

なお、本実施形態では、チップ 6 0 0 に形成されるシャント素子として容量素子 3 0 2 を用いたが、当該シャント素子として容量素子と抵抗素子とが電気的に直列に接続された素子を用いてもよい。

【 0 0 6 7 】

30

これにより、発振器は、テラヘルツ周波数の帯域から、十分に低い周波数帯域までの広い周波数領域において、安定的に寄生発振を抑制することができる。さらに、シャント素子 5 2 0 にはチップ部品を用いているので、設計の制約が小さく、寄生発振をより確実に抑制することができる。

【 0 0 6 8 】

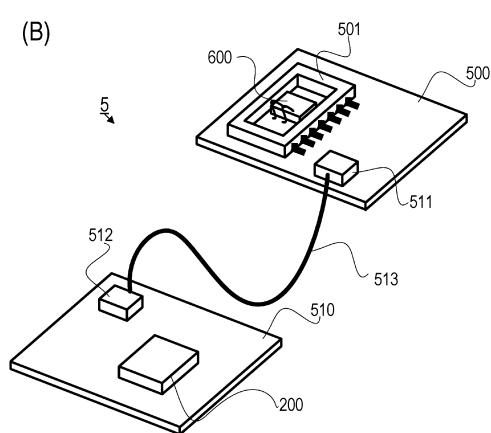

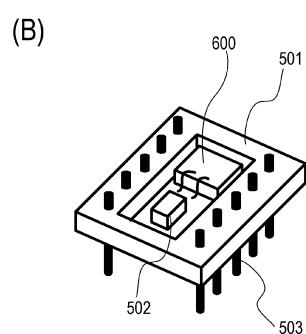

< 実施形態 3 >

実施形態 2 に係る発振器 2 では、プリント回路基板 5 0 0 にシャント素子 5 2 0 が形成されていたが、実施形態 3 に係る発振器 3 では、図 1 0 ( A ) の回路構成図が示すように、パッケージ 5 0 1 にシャント素子 5 2 0 が形成される。以下では、図 1 1 ( A ) および図 1 1 ( B ) を用いて、実施形態 3 に係る発振器 3 について実施形態 2 と異なる部分について説明する。

40

【 0 0 6 9 】

図 1 1 ( A ) は、本実施形態の発振器 3 を説明する模式図である。パッケージ 5 0 1 は、ピン 5 0 3 を備えており、プリント回路基板 5 0 0 は、ピン 5 0 3 に対応したピンソケット 5 0 4 を備えている。そのため、チップ 6 0 0 を備えたパッケージ 5 0 1 は、図 1 1 ( B ) が示すように、プリント回路基板 5 0 0 から挿抜することができる。これにより、発振器 3 の特性の変更をユーザが望む場合や、発振器 3 が故障して交換が必要になった場合にも、パッケージ 5 0 1 を交換することによって容易に対応可能である。

【 0 0 7 0 】

一方、パッケージ 5 0 1 とプリント回路基板 5 0 0 を接続する配線内には、ピンソケツ

50

ト 5 0 4 に起因する寄生インダクタや寄生容量などの寄生素子が含まれる。このため、発振器 3 は、実施形態 2 に係る発振器 2 よりも寄生発振が発生しやすく、テラヘルツ波発振がより妨害されやすい。

【 0 0 7 1 】

しかしながら、本実施形態の構成によれば、パッケージ 5 0 1 内のシャント素子 5 2 0 によって、寄生発振を抑制することができるので、パッケージ 5 0 1 外に寄生素子が付加されても、安定したテラヘルツ波発振が実現できる。具体的には、本実施形態によれば、ピンソケット 5 0 4 に寄生素子を有する場合でも、パッケージ 5 0 1 内において十分低い周波数までの電磁波の損失が実現可能であるので、寄生発振を抑制することができる。

【 0 0 7 2 】

なお、発振回路 1 0 0 (負性抵抗素子 1 0 1) とシャント素子 5 2 0 とを接続する配線の長さの条件、および、発振回路 1 0 0 (負性抵抗素子 1 0 1) と容量素子 3 0 2 とを接続する配線の長さの条件は実施形態 2 と同様に満たされている。また、容量素子 3 0 2 に限らず、容量素子と抵抗素子とが電気的に直列に接続された素子を、容量素子 3 0 2 に代わるシャント素子として用いてもよい。

【 0 0 7 3 】

従って、本実施形態に係る発振器は、交換が容易であり、かつ、消費電力を抑制して、寄生発振の抑制を安定的に行うことができる。

【 0 0 7 4 】

< 実施形態 4 >

実施形態 4 は、実施形態 2 と実施形態 3 とが組み合わさった実施形態である。より詳細には、本実施形態は、3 つのシャント素子が、それぞれ異なる部材 (チップ、パッケージ、プリント回路基板) に形成される形態である。図 1 2 (A) が示すように、本実施形態に係る発振器 4 は、実施形態 2 のように、容量素子 3 0 2 と同様の構成である容量素子 5 0 2 をプリント回路基板 5 0 0 上に備えている。また、発振器 4 は、実施形態 3 のように、パッケージ 5 0 1 がプリント回路基板 5 0 0 から挿抜が可能である。

【 0 0 7 5 】

チップ 6 0 0 には、図 1 0 (B) が示すように、シャント素子として容量素子 3 0 2 が形成されている。一方、パッケージ 5 0 1 に、シャント素子として容量素子 5 0 2 が形成されている。また、プリント回路基板 5 0 0 には、抵抗素子 3 1 1 と容量素子 3 1 2 を有するシャント素子 5 2 0 が形成されている。これらの容量素子 3 0 2, 5 0 2 とシャント素子 5 2 0 のそれぞれは、異なる寄生発振を抑制するようにパラメータが設定されており、図 9 (B) が示すように、損失の周波数特性が連続している。

【 0 0 7 6 】

例えば、本実施形態では、図 9 (B) が示すように、発振回路 1 0 0 と接続する配線の長さが短い容量素子 3 0 2 は、高周波数の寄生発振周波数  $f_{p2}$  の電磁波の発振を抑制する損失  $L_6$  を有する。一方、発振回路 1 0 0 と接続する配線の長さが長い容量素子 5 0 2 は、寄生発振周波数  $f_{p1}$  の電磁波の発振を抑制する損失  $L_7$  を有する。また、さらに長い距離の配線を要するシャント素子 5 2 0 は、寄生発振周波数  $f_v$  の電磁波の発振を抑制する損失  $L_8$  を有する。

【 0 0 7 7 】

言い換えると、容量素子 3 0 2, 5 0 2 およびシャント素子 5 2 0 のそれぞれは、発振回路 1 0 0 (負性抵抗素子 1 0 1) とを接続する配線が短いほど、高い周波数帯域の電磁波の発振を抑制する。また、容量素子 3 0 2, 5 0 2 およびシャント素子 5 2 0 のそれぞれが、自身が発振を抑制する (損失を有する) の最大周波数の電磁波における波長の 1/4 以下の長さの配線によって、発振回路 1 0 0 (負性抵抗素子 1 0 1) と接続されている。なお、上述するように、発振を抑制する (損失を有する) の最大周波数の電磁波における波長とは、高周波側のカットオフ周波数といえる。

【 0 0 7 8 】

なお、容量素子 3 0 2, 5 0 2 に限らず、容量素子と抵抗素子とが電気的に直列に接続

10

20

30

40

50

された素子を、容量素子 302, 502 に代わるシャント素子として用いてもよい。

【0079】

本実施形態に係る発振器によれば、複数のシャント素子を用いて、接続する部分ごと(チップ-パッケージ、パッケージ-プリント回路基板、プリント回路基板-電圧バイアス回路)に寄生発振を抑制できる。このため、それぞれのシャント素子のパラメータを、より最適なパラメータとすることができる、必要最小限の設計値にすることができる。

【0080】

<実施形態 5 >

実施形態 5 に係る発振器 5 は、電圧バイアス回路の配置場所が実施形態 1 に係る発振器 1 と異なり、それ以外は、実施形態 1 に係る発振器 1 と同じである。

10

【0081】

本実施形態では、図 12 (B) が示すように、電圧バイアス回路 200 は、パッケージ 501 を備えたプリント回路基板 500 に形成されずに、他のプリント回路基板 510 に形成される。ここで、プリント回路基板 500 とプリント回路基板 510 との間は、ケーブル 513 によって電気的に接続されている。具体的には、プリント回路基板 500 上のコネクタ 511 と、プリント回路基板 510 上のコネクタ 512 とが、ケーブル 513 により接続されている。

【0082】

このため、プリント回路基板 510 上に形成されている電圧バイアス回路 200 は、ケーブル 513 を介して、パッケージ 501 内のチップ 600 に電圧  $V_{op}$  を印加することができる。

20

【0083】

なお、本実施形態では、発振回路 100 と電圧バイアス回路 200 との間に寄生素子があっても、シャント素子 310 によって寄生発振を抑制することができる。このため、電圧バイアス回路 200 を他のプリント回路基板 510 上に分離しても、ケーブル 513 を用いることによって、発振器 5 は、所定の電磁波(テラヘルツ波)を発振可能である。

【0084】

従って、本実施形態によれば、発振器において、所定の電磁波が発振される部分(発振回路を有する部分)と電圧バイアス回路とを分離することができるので、所定の電磁波を発振する部分の設計の制約を少なくすることができ、配置もより自由にできる。

30

【0085】

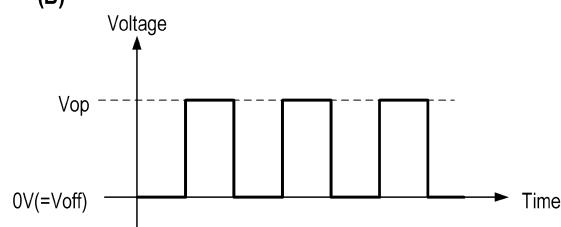

<実施形態 6 >

実施形態 1 に係る発振器 1 では、電圧バイアス回路は、負性抵抗素子に直流電圧を印加していたが、本実施形態に係る発振器 6 では、電圧バイアス回路は、負性抵抗素子に交流電圧を印加する。なお、発振器 6 は、それ以外の構成については、実施形態 1 に係る発振器 1 と同様である。

【0086】

電圧バイアス回路 210 は、図 13 (A) が示すように、発振回路 100(負性抵抗素子 101)に交流の電圧(交流電圧)を印加する。具体的には、交流の電圧として、図 13 (B) が示すように、所定の電磁波の発振をするための電圧値  $V_{op}$  と、所定の電磁波の発振を停止させる電圧値  $V_{off}$  との間を、ある周波数で変化する電圧を用いることができる。電圧値  $V_{off}$  は、負性抵抗領域以外の電圧値であればよく、例えば 0V である。また、交流電圧としては、図 13 (B) が示すように、電圧値  $V_{op}$  と電圧値  $V_{off}$  の 2 値間を変化するパルス波的に遷移する電圧を用いることができる。この電圧の変化の周波数は、所定の電磁波の発振周波数より、十分低い周波数を用いる。

40

【0087】

電圧バイアス回路 210 は、交流の電圧を生成するために、実施形態 1 に係る電圧バイアス回路 200 に比べて複雑な動作をする。そのため、電圧バイアス回路 210 は、実施形態 1 に係る電圧バイアス回路 200 が有する寄生素子もより大きな素子を含み、電圧バイアス回路 210 と発振回路 100 による寄生発振が発生しやすい。しかしながら、発振

50

器 6 は、このように寄生発振がより発生しやすい構成においても、シャント素子 310 を有することによって、効果的に当該寄生発振を抑制することができる。

【 0088 】

なお、シャント素子 310において、容量素子 312 と抵抗素子 311 の時定数により決まる周波数（低周波側のカットオフ周波数）は、電圧バイアス回路 210 が変化する周波数より高い必要がある。例えば、矩形波の電圧を用いる場合は、当該時定数により決まる周波数は、当該変化する周波数の望ましくは数倍以上であることが好ましい。

【 0089 】

本実施形態によれば、寄生発振がより発生しやすい、交流の電圧バイアス回路 210 を用いた場合でも、消費電力の増加を抑制し、寄生発振の抑制を安定的に行うことができる。

10

【 0090 】

< 実施形態 7 >

実施形態 1 に係る発振器 1 は、撮像装置（画像取得装置）に対して適用可能であるため、本実施形態では発振器 1 を用いた撮像装置 10 について説明する。

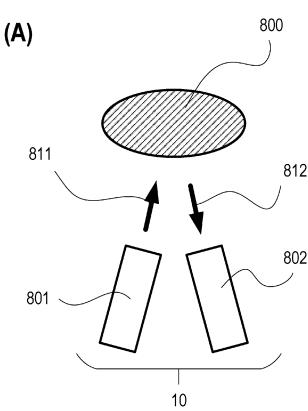

【 0091 】

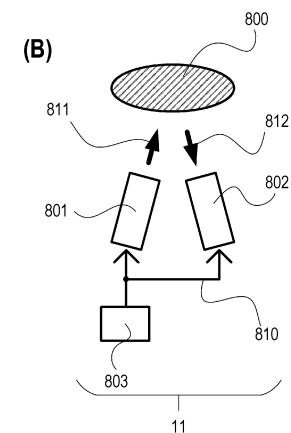

撮像装置 10 は、図 14 (A) が示すように、照明 801 と撮像素子 802 を有する。照明 801 は、実施形態 1 に係る発振器 1 を有することによって、被対象 800 に対してテラヘルツ波 811（所定の電磁波）を照射する照明装置である。撮像素子 802 は、被対象 800 において反射したテラヘルツ波 812 を取得（撮像）する。撮像素子 802 は、被対象 800 の形状や物性値に対応して変化する被対象 800 の情報を、画像として取得することができる。

20

【 0092 】

このように、照明 801 に対して発振器 1 を用いると、撮像装置 10 において、消費電力の増加を抑制し、寄生発振の抑制を安定的に行うことができるので、発熱などによる特性変動が少ない安定したテラヘルツ波の照射を行うことができる。そのため、本実施形態によれば、被対象 800 の情報を正確に取得することができる撮像装置 10 を提供することができる。

【 0093 】

[ 変形例 1 ]

さらに、実施形態 7 に係る撮像装置 10 に限らず、図 14 (B) が示すように、照明 801 には、実施形態 6 の電圧バイアス回路 210 を用いた発振器 6 を用いる撮像装置 11 とすることができる。

30

【 0094 】

図 14 (B) では、撮像装置 11 は、発振器 6 を用いた照明 801 と、撮像素子 802 と、タイミング生成手段 803 を有している。タイミング生成手段 803 は、タイミング信号 810 を、発振器 6 を用いた照明 801 と、撮像素子 802 に入力する。

【 0095 】

照明 801 は、入力されたタイミング信号 810 に基づいて、電圧バイアス回路 210 の電圧変化タイミングを調整する。調整されたタイミングにより、照明 801 が、テラヘルツ波 811 の発振と停止を周期的に繰り返すことによって、被対象 800 において、テラヘルツ波 811 が照射された期間と、照射されていない期間が発生する。

40

【 0096 】

一方、撮像素子 802 は、入力されたタイミング信号 810 に基づいて、照明 801 がテラヘルツ波を照射した期間と、照射していない期間における被対象 800 の撮像をそれぞれ行う。そして、撮像素子 802 は、2 つの期間において撮像した情報の差を判定する。この差によって、撮像素子 802 は、意図して照射していない電磁波の成分（ノイズ成分）を除去することができるため、取得する画像の S/N 比 (S i n g a l t o N o i s e R a t i o ) を向上させることができる。

【 0097 】

本変形例によれば、S/N 比のより高い画像情報を取得できる撮像装置（テラヘルツ撮像

50

装置)を提供することができる。

【符号の説明】

【0098】

1：発振器、100：発振回路、101：負性抵抗素子、200：電圧バイアス回路

310：シャント素子、311：抵抗素子、312：容量素子

10

20

30

40

50

## 【図面】

## 【図 1】

(A)

(B)

## 【図 2】

10

20

## 【図 3】

(A)

(B)

(C)

## 【図 4】

30

40

50

【図 5】

【図 6】

10

20

30

40

50

【図 7】

【図 8】

10

20

30

40

50

【図 9】

【図 10】

(B)

10

20

【図 11】

【図 12】

30

40

50

【図 1 3】

【図 1 4】

(B)

10

20

【図 1 5】

30

40

50

---

フロントページの続き

(56)参考文献 米国特許出願公開第2013/0234762(US, A1)

特開2011-061276(JP, A)

特開2010-252299(JP, A)

特表2014-517620(JP, A)

国際公開第2015/170425(WO, A1)

特開2014-014072(JP, A)

特開2016-111541(JP, A)

特開2013-168928(JP, A)

(58)調査した分野 (Int.Cl., DB名)

H03B 7/08

G01N 21/01

G01N 21/17