(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4826888号

(P4826888)

(45) 発行日 平成23年11月30日(2011.11.30)

(24) 登録日 平成23年9月22日(2011.9.22)

(51) Int.Cl.

F 1

G 11 B 20/14 (2006.01)

H 03 M 7/14 (2006.01)G 11 B 20/14 341 A

H 03 M 7/14 B

請求項の数 12 (全 34 頁)

(21) 出願番号 特願2005-326606 (P2005-326606)

(22) 出願日 平成17年11月10日 (2005.11.10)

(65) 公開番号 特開2007-133980 (P2007-133980A)

(43) 公開日 平成19年5月31日 (2007.5.31)

審査請求日 平成20年11月6日 (2008.11.6)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(72) 発明者 中川 俊之

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 堀 洋介

(56) 参考文献 特開平11-346154 (JP, A)

特開2000-149457 (JP, A)

最終頁に続く

(54) 【発明の名称】復調テーブル、復調装置および復調方法、プログラム、並びに記録媒体

## (57) 【特許請求の範囲】

## 【請求項 1】

最小ランが  $d$  ( $d > 0$ )、最大ランが  $k$  であり、基本符号語長が  $n$  ビットの可変長符号  $(d, k; m, n; r)$  (最大拘束長  $r > 1$ ) を、基本データ長が  $m$  ビットのデータに変換する復調テーブルにおいて、

基本符号語長が  $n$  ビットの基礎符号からなる符号パターンを、基本データ長が  $m$  ビットの基礎データからなるデータパターンに変換する基礎テーブルと、

前記最小ランの連続を  $N$  ( $N > 0$ ) 回以下に制限するように決定されている最小ラン連続制限パターンの符号パターンを、対応するデータパターンに変換する第1の置換テーブルと、

前記最大ランを  $M$  ( $M > 0$ ) に制限するように決定されている符号パターンを、対応するデータパターンに変換する第2の置換テーブルと

を有し、

前記第1の置換テーブルは、

拘束長が第1の値である場合における複数の異なる前記最小ラン連続制限パターンの符号パターンを、対応する同一のデータパターンに変換し、

拘束長が前記第1の値よりも小さな第2の値である場合における单一の前記最小ラン連続制限パターンの符号パターンを、対応するデータパターンに変換するものであり、

$d = 1, k = 7, m = 2, n = 3$  であり、前記最小ランの連続が5回以下に制限されている

10

20

復調テーブル。

【請求項 2】

拘束長が前記第 1 の値である場合における複数の異なる前記最小ラン連続制限パターンの符号パターンに対応するデータパターンは、その一部に、拘束長が前記第 2 の値である場合における单一の前記最小ラン連続制限パターンの符号パターンに対応するデータパターンを含む

請求項 1 に記載の復調テーブル。

【請求項 3】

前記符号パターン内の“1”的個数と、前記データパターン内の“1”的個数が、2で割った際の余りが、どちらも 1 あるいは 0 で一致するような変換規則を有する

10

請求項 1 または 2 に記載の復調テーブル。

【請求項 4】

最小ランが  $d$  ( $d > 0$ )、最大ランが  $k$  であり、基本符号語長が  $n$  ビットの可変長符号 ( $d, k; m, n; r$ ) (最大拘束長  $r > 1$ ) を、基本データ長が  $m$  ビットのデータに変換する復調装置において、

基礎符号パターンとそれに対応付けられた基礎データパターンとを含む第 1 の復調テーブルに従って、入力された符号語列をデータ列に変換する第 1 の変換手段と、

前記最小ランの連続を  $N$  ( $N > 0$ ) 回以下に制限するように決定されている最小ラン連続制限パターンの符号パターンとして、拘束長が第 1 の値である場合における複数の異なる第 1 の前記符号パターン及び拘束長が前記第 1 の値よりも小さい第 2 の値である場合における单一の第 2 の前記符号パターン、複数の異なる前記第 1 の符号パターンにそれぞれ対応付けられた同一のデータパターン、並びに单一の前記第 2 の符号パターンに対応付けられたデータパターンを含む第 2 の復調テーブルに従って、入力された符号語列をデータ列に変換する第 2 の変換手段と、

20

前記最小ラン連続制限パターンの符号パターンを検出する第 1 の検出手段と、

前記最小ラン連続制限パターンが検出された場合、前記第 2 の復調テーブルに従って変換されたデータ列を選択する選択手段と

を備え、

前記第 1 の復調テーブルは、前記最大ランを  $M$  ( $M > 0$ ) に制限するように決定されている符号パターンとそれに対応付けられたデータパターンをさらに有し、

30

$d = 1, k = 7, m = 2, n = 3$  であり、前記最小ランの連続が 5 回以下に制限されている

復調装置。

【請求項 5】

少なくとも 1 つの前記最小ラン連続制限パターンの符号パターンを一部に含む符号パターンを検出する第 2 の検出手段をさらに備え、

前記選択手段は、1 つの前記最小ラン連続制限パターンの符号パターンを一部に含む符号パターンが検出されたかどうかの結果を用いて、前記第 1 の復調テーブルの第 1 の部分または第 2 の部分に従って変換されたデータ列のいずれかを選択する

請求項 4 に記載の復調装置。

40

【請求項 6】

前記選択手段は、最小単位の基礎符号パターンとそれに対応付けられた基礎データパターンに従って変換されたデータ列を選択する

請求項 4 に記載の復調装置。

【請求項 7】

前記選択手段により選択されたデータ列から、所定の位置に挿入されている同期パターンまたは DSV 制御ビットを取り除き、データビットを取り出す取出手段をさらに備える

請求項 4 乃至 6 に記載の復調装置。

【請求項 8】

入力された信号から前記符号語列を作成する符号語列化手段をさらに備える

50

請求項4乃至7に記載の復調装置。

【請求項 9】

入力された前記符号語列から、所定の位置に挿入されている同期パターンを検出する同期パターン検出手段をさらに備える

請求項4乃至8に記載の復調装置。

【請求項 10】

最小ランが  $d$  ( $d > 0$ )、最大ランが  $k$  であり、基本符号語長が  $n$  ビットの可変長符号  $(d, k; m, n; r)$  (最大拘束長  $r > 1$ ) を、基本データ長が  $m$  ビットのデータに変換する復調装置の復調方法において、

基礎符号パターンとそれに対応付けられた基礎データパターンとを含む第1の復調テーブルに従って、入力された符号語列をデータ列に変換する第1の変換ステップと、

前記最小ランの連続を  $N$  ( $N > 0$ ) 回以下に制限するように決定されている最小ラン連続制限パターンの符号パターンとして、拘束長が第1の値である場合における複数の異なる第1の前記符号パターン及び拘束長が前記第1の値よりも小さい第2の値である場合における单一の第2の前記符号パターン、複数の異なる前記第1の符号パターンにそれぞれ対応付けられた同一のデータパターン、並びに单一の前記第2の符号パターンに対応付けられたデータパターンを含む第2の復調テーブルに従って、入力された符号語列をデータ列に変換する第2の変換ステップと、

前記最小ラン連続制限パターンの符号パターンを検出する検出ステップと、

前記最小ラン連続制限パターンの符号パターンが検出された場合、前記第2の復調テーブルに従って変換されたデータ列を選択する選択ステップと

を含み、

前記第1の復調テーブルは、前記最大ランを  $M$  ( $M > 0$ ) に制限するように決定されている符号パターンとそれに対応付けられたデータパターンをさらに有し、

$d = 1, k = 7, m = 2, n = 3$  であり、前記最小ランの連続が5回以下に制限されている

復調方法。

【請求項 11】

最小ランが  $d$  ( $d > 0$ )、最大ランが  $k$  であり、基本符号語長が  $n$  ビットの可変長符号  $(d, k; m, n; r)$  (最大拘束長  $r > 1$ ) を、基本データ長が  $m$  ビットのデータに変換する処理をコンピュータに実行させるプログラムにおいて、

基礎符号パターンとそれに対応付けられた基礎データパターンとを含む第1の復調テーブルに従って、入力された符号語列をデータ列に変換する第1の変換ステップと、

前記最小ランの連続を  $N$  ( $N > 0$ ) 回以下に制限するように決定されている最小ラン連続制限パターンの符号パターンとして、拘束長が第1の値である場合における複数の異なる第1の前記符号パターン及び拘束長が前記第1の値よりも小さい第2の値である場合における单一の第2の前記符号パターン、複数の異なる前記第1の符号パターンにそれぞれ対応付けられた同一のデータパターン、並びに单一の前記第2の符号パターンに対応付けられたデータパターンを含む第2の復調テーブルに従って、入力された符号語列をデータ列に変換する第2の変換ステップと、

前記最小ラン連続制限パターンの符号パターンを検出する検出ステップと、

前記最小ラン連続制限パターンの符号パターンが検出された場合、前記第2の復調テーブルに従って変換されたデータ列を選択する選択ステップと

をコンピュータに実行させるプログラムであり、

前記第1の復調テーブルは、前記最大ランを  $M$  ( $M > 0$ ) に制限するように決定されている符号パターンとそれに対応付けられたデータパターンをさらに有し、

$d = 1, k = 7, m = 2, n = 3$  であり、前記最小ランの連続が5回以下に制限されている

プログラム。

【請求項 12】

10

20

30

40

50

請求項 1 1 に記載のプログラムが記録されている記録媒体。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、復調テーブル、復調装置および復調方法、プログラム、並びに記録媒体に関し、特に最小ランの連続回数がより少なくなるようにした復調テーブル、復調装置および復調方法、プログラム、並びに記録媒体に関する。

【背景技術】

【0 0 0 2】

データを所定の伝送路に伝送したり、または例えば磁気ディスク、光ディスク、光磁気ディスク等の記録媒体に記録する際、伝送路や記録媒体に適するように、データの変調が行われる。このような変調方法の1つとして、ブロック符号が知られている。ブロック符号とは、データ列を  $m \times i$  ビットからなる単位（以下データ語という）にブロック化し、このデータ語を適当な符号則に従って、 $n \times i$  ビットからなる符号語に変換するものである。そしてこの符号は、 $i = 1$  のときには固定長符号となり、また  $i$  が複数個選べるとき、すなわち、1乃至  $i_{\max}$ （最大の  $i$ ）の範囲の所定の  $i$  を選択して変換したときには可変長符号となる。このブロック符号化された符号は可変長符号  $(d, k; m, n; r)$  と表される。

【0 0 0 3】

ここで  $i$  は拘束長と称され、 $i_{\max}$  は  $r$ （最大拘束長）となる。また  $d$  は、例えば、連続する“1”の間に入る、“0”の最小連続個数である“0”の最小ランを示し、 $k$  は連続する“1”の間に入る、“0”の最大連続個数である“0”の最大ランを示している。

【0 0 0 4】

ところで上述のようにして得られる符号語を、光ディスクや光磁気ディスク等に記録する場合、例えばコンパクトディスク(CD)やミニディスク(MD)（登録商標）では、可変長符号列は、“1”を反転とし、“0”を無反転とするNRZI(Non Return to Zero Inverted)変調され、NRZI変調された可変長符号（以下、記録波形列と称する）に基づき記録が行なわれている。これはマークエッジ記録とも称される。これに対して、ISO規格の3.5inch・230MB容量の光磁気ディスク等では、記録変調された符号列がNRZI変調せずにそのまま記録される。これはマークポジション記録と言われる。現在のように高記録密度化された記録メディアでは、マークエッジ記録が多く用いられている。

【0 0 0 5】

記録波形列の最小反転間隔を  $T_{\min}$  とし、最大反転間隔を  $T_{\max}$  とするとき、線速方向に高密度記録を行うためには、最小反転間隔  $T_{\min}$  は長い方が、即ち最小ラン  $d$  は大きい方が良く、またクロックの再生の面からは、最大反転間隔  $T_{\max}$  は短い方が、即ち最大ラン  $k$  は小さい方が望ましい。またオーバーライト特性を考慮する場合には  $T_{\max}/T_{\min}$  の小さい方が望ましい。さらには、JitterやS/Nの点から検出窓幅  $T_w=m/n$  が大きいことが重要になるなど、メディアの条件と照らし合わせながら種々の変調方法が提案され、実用化されている。

【0 0 0 6】

ここで具体的に、光ディスク、磁気ディスク、または光磁気ディスク等において、提案されたり、あるいは実際に使用されている変調方式をあげてみる。CDやMDで用いられるEFM符号  $((2, 10; 8, 17; 1)$  とも表記される)やDVDで用いられる8-16符号  $((2, 10; 1, 2; 1)$  とも表記される)、そしてPD(120mm650MB容量)で用いられるRLL(2,7)  $((2, 7; m, n; r)$  とも表記される)は、最小ラン  $d=2$  のRLL符号である。また、MD - DATA 2 あるいはISO規格の3.5inchMO(640MB容量)で用いられるRLL(1,7)  $((1, 7; 2, 3; r)$  とも表記される)は、最小ラン  $d=1$  のRLL符号である。この他、現在開発研究されている、記録密度の高い光ディスクや光磁気ディスク等の記録再生ディスク装置においては、最小マークの大きさや、変換効率のバランスの取れた、最小ラン  $d=1$  のRLL符号 (Run Length Limited code) がよく用いられている。

【0 0 0 7】

可変長のRLL(1,7)符号の変換テーブルとしては、例えば以下のようなテーブルが知られ

10

20

30

40

50

ている。

<表1>

RLL(1,7) : (d,k;m,n;r) = (1,7;2,3;2)

データパターン 符号パターン

|       |      |         |

|-------|------|---------|

| i = 1 | 11   | 00x     |

|       | 10   | 010     |

|       | 01   | 10x     |

| i = 2 | 0011 | 000 00x |

|       | 0010 | 000 010 |

|       | 0001 | 100 00x |

|       | 0000 | 100 010 |

#### 【0008】

ここで変換テーブル内の記号xは、次に続くチャネルビットが“0”であるときに“1”とされ、また次に続くチャネルビットが“1”であるときに“0”とされる。最大拘束長rは2である。

#### 【0009】

可変長RLL(1,7)のパラメータは(1,7;2,3,2)であり、記録波形列のビット間隔をTとすると、 $(d+1)T$ で表される最小反転間隔T<sub>min</sub>は $2(=1+1)T$ となる。データ列のビット間隔をT<sub>data</sub>とすると、この $(m/n) \times 2$ で表される最小反転間隔T<sub>min</sub>は $1.33(=2/3) \times 2T$ となる。また $(k+1)T$ で表される最大反転間隔T<sub>max</sub>は、 $T_{max}=8(=7+1)T(=(m/n) \times 8T$   $T_{data}=(2/3) \times 8T$  $T_{data}=5.33T$ となる。さらに検出窓幅Twは $(m/n) \times T_{data}$ で表され、その値は、 $T_w=0.67(=2/3)T_{data}$ となる。

#### 【0010】

ところで、表1のRLL(1,7)による変調を行ったチャネルビット列においては、発生頻度としてはT<sub>min</sub>である2Tが一番多く、以下、3T, 4T, 5T, 6T, …の順に多い。そして最小ランである2Tが繰り返した場合、即ちエッジ情報が早い周期で多く発生することは、クロック再生には有利となる場合が多い。

#### 【0011】

ところが、例えば光ディスクの記録再生において、さらに記録線密度を高くしていった場合、最小ランは、エラーが発生しやすい部位となる。なぜなら、ディスク再生時において、最小ランの波形出力は、他のランよりも小さく、例えばデフォーカスやタンジェンシャル・チルト等による影響を受けやすいからである。またさらに、高記録線密度における、最小マークの連続した記録再生は、ノイズ等の外乱の影響も受けやすく、従ってデータ再生誤りを起こしやすくなる。この時のデータ再生誤りのパターンとしては、連続する最小マークの先頭のエッジから最後のエッジまでが、一斉にシフトして誤るという場合がある。即ち発生するビットエラー長は、最小ランの連続する区間の、先頭から最後まで伝搬することになる。従ってエラー伝搬は長くなってしまうという問題が現れる。

#### 【0012】

以上より高線密度にデータを安定して記録再生するには、最小ランの連続を制限することが効果的である。

#### 【0013】

一方、記録媒体へのデータの記録、あるいはデータの伝送の際には、記録媒体あるいは伝送路に適した符号化変調が行われるが、これら変調符号に低域成分が含まれていると、例えば、ディスク装置のサーボ制御におけるトラッキングエラーなどの、各種のエラー信号に変動が生じ易くなったり、あるいはジッターが発生し易くなったりする。従って変調符号は、低域成分がなるべく抑制されている方が望ましい。

#### 【0014】

低域成分を抑制する方法として、DSV(Digital Sum Value)制御がある。DSVとは、チャネルビット列をNRZI化(すなわちレベル符号化)して記録符号列とし、そのビット列(データのシンボル)の“1”を「+1」、「0」を「-1」として、符号を加算していく

10

20

30

40

50

ときのその総和を意味する。DSVは記録符号列の低域成分の目安となる。DSVの正負のゆれの絶対値を小さくすること、すなわちDSV制御を行うことは、記録符号列の直流成分を除き、低域成分を抑制することになる。

【0015】

上記表1に示した、可変長RLL(1,7)テーブルによる変調符号はDSV制御が行われていない。このような場合のDSV制御は、変調後の符号化列（チャネルビット列）において、所定の間隔でDSV計算を行い、所定のDSV制御ビットを符号化列（チャネルビット列）内に挿入することで実現する（例えば、特許文献1）。

【0016】

チャネルビット列内に挿入するDSV制御ビット数は、最小ランdによって決まる。d = 1の時、最小ランを守るように、符号語内の任意の位置にDSV制御ビットを挿入する場合、必要なビット数は $2 (= d + 1)$ チャネルビットである。また最大ランを守るように、符号語内の任意の位置にDSV制御ビットを挿入する場合に必要となるビット数は $4 (= 2 \times (d + 1))$ チャネルビットである。これらよりも少ないチャネルビットでDSV制御を行うと、挟まれる前後のパターンによって、DSV制御できない場合が発生する。

【0017】

(d, k; m, n)=(1,7;2,3)であるRLL(1,7)符号において、上記DSV制御ビットを、変換率と合わせて、データに換算すると、

$$4 \text{ チャネルビット} \times 2 / 3 = 8 / 3 = 2.67 \text{ データ相当 (2.67 T data)}$$

になる。

【0018】

ところで、DSV制御ビットは基本的には冗長ビットである。従って符号変換の効率から考えれば、DSV制御ビットはなるべく少ないほうが良い。

【0019】

またさらに、挿入されるDSV制御ビットによって、最小ランdおよび最大ランkは、変化しないほうが良い。(d, k)が変化すると、記録再生特性に影響を及ぼしてしまうからである。

【0020】

ただし、実際のRLL符号においては、最小ランは記録再生特性への影響が大きいために、必ず守られる必要があるが、最大ランについては必ずしも守られてはいない。場合によつては最大ランを破るパターンを同期信号に用いるフォーマットも存在する。例えば、DVD (Digital Versatile Disk) の8-16符号における最大ランは11Tだが、同期パターン部分においては最大ランを超える14Tが与られており、これにより同期信号の検出能力を上げている。

【0021】

以上を踏まえて本発明者らは、(d, k)=(1,7)でさらに高記録密度に対応した変調方式として、表2の1,7PP符号を先に提案した（例えば、特許文献2）。

<表2>

$$1,7PP : (d, k; m, n; r) = (1,7; 2,3; 4)$$

データパターン 符号パターン

11 \*0\*

10 001

01 010

0011 010 100

0010 010 000

0001 000 100

000011 000 100 100

000010 000 100 000

10

20

30

40

50

|          |                      |

|----------|----------------------|

| 000001   | 010 100 100          |

| 000000   | 010 100 000          |

| 110111   | 001 000 000(next010) |

| 00001000 | 000 100 100 100      |

| 00000000 | 010 100 100 100      |

if xx1 then \*0\* = 000

xx0 then \*0\* = 101

#### 【0 0 2 2】

10

表2の変換テーブルは、変換パターンとして、それがないと変換処理ができない基礎パターン（（11）から（000000）までのデータパターン）、それがなくても変換処理は可能であるが、それを行うことによって、より効果的な変換処理が実現する置換パターン（（110111），（00001000），（00000000）のデータパターン）、および、データ列を任意の位置で終端させるための終端パターン（（00），（0000）のデータパターン）を持っている。

#### 【0 0 2 3】

20

また、表2は、最小ランd = 1、最大ランk = 7で、基礎パターンの要素に不確定符号（\*）を含んでいる。不確定符号\*は、直前および直後の符号語列の如何によらず、最小ランdと最大ランkを守るように、“0”か“1”に決定される。すなわち表2において、変換する2データが（11）であったとき、その直前の符号語列（チャネルビット列）によって、“000”または“101”が選択され、そのいずれかに変換される。例えば、直前の符号語列の1チャネルビットが“1”である場合、最小ランdを守るために、2データ（11）は、符号語“000”に変換され、直前の符号語列の1チャネルビットが“0”である場合、最大ランkが守られるように、2データ（11）は、符号語“101”に変換される。

#### 【0 0 2 4】

30

表2の変換テーブルの基礎パターンは可変長構造を有している。すなわち、拘束長i = 1における基礎パターンは、必要数の4つ（ $2^m=2^2=4$ ）よりも少ない3つ（\*0\*，001，010の3つ）で構成されている。その結果、データ列を変換する際に、拘束長i = 1だけでは変換出来ないデータ列が存在することになる。結局、表2において、全てのデータ列を変換するには（変換テーブルとして成り立つためには）、拘束長i = 3までの基礎パターンを参照する必要がある。

#### 【0 0 2 5】

40

また、表2の変換テーブルは、最小ランdの連續を制限する置換パターンを持っているため、データ列が（110111）である場合、さらに後ろに続く符号語列が参照され、それが“010”であるとき、この6データは符号語“001 000 000”に置換される。また、このデータ列は、後ろに続く符号語列が“010”以外である場合、2データ単位（（11），（01），（11））で符号語に変換されるので、符号語“\*0\* 010 \*0\*”に変換される。これによって、データを変換した符号語列は、最小ランの連續が制限され、最大でも6回までの最小ラン繰り返しとなる。

#### 【0 0 2 6】

そして表2の変換テーブルは、最大拘束長r = 4である。拘束長i = 4の変換パターンは、最大ランk = 7を実現するための置換パターン（最大ラン保証パターン）で構成されている。すなわち、データパターン（00001000）は、符号パターン“000 100 100 100”に変換され、データパターン（00000000）は、符号パターン“010 100 100 100”に変換されるように構成されている。そしてこの場合においても、最小ランd = 1は守られている。

#### 【0 0 2 7】

50

さらに表2は、同期パターンを挟むために、データ列の任意の位置において終端させる場合、データ列が（00）または（0000）で終端位置となる際には、終端パターンが用いら

れる。挿入される同期パターンは、先頭の 1 符号語が終端パターン使用識別ビットとなつてあり、終端パターンが用いられた時は、直後の同期パターン列の先頭符号語が“ 1 ”とされる。また終端パターンが用いられなかった時は、“ 0 ”とされる。なお、表 2 における同期パターンは、上述の終端パターン使用識別ビットと、同期パターン検出のために、最大ラン  $k = 7$  を超える  $k = 8$  の符号語の 2 回の繰り返しの合計 24 符号語で構成されている。

#### 【 0 0 2 8 】

ところで、表 2 の変換パターンは、データパターンの要素内の“ 1 ”の個数を 2 で割った時の余りと、符号パターンの要素内の“ 1 ”の個数を 2 で割った時の余りが、どちらも 1 あるいは 0 で同一（対応するいずれの要素も、“ 1 ”の個数が奇数または偶数）となるような変換規則を持っている。例えば、変換パターンのうちのデータパターン（000001）は“ 010 100 100 ”の符号パターンに対応しているが、それぞれの要素の“ 1 ”の個数はデータパターンでは 1 個、対応する符号パターンでは 3 個であり、どちらも 2 で割ったときの余りが 1（奇数）で一致している。同様にして、変換パターンのうちのデータパターン（000000）は“ 010 100 000 ”の符号パターンに対応しているが、それぞれ“ 1 ”の個数はデータパターンでは 0 個、対応する符号パターンでは 2 個であり、どちらも 2 で割ったときの余りが 0（偶数）で一致している。

#### 【 0 0 2 9 】

次に、DSV 制御を行う方法について述べる。表 1 の RLL(1,7) 符号のような、変換テーブルに DSV 制御が行われていない場合における DSV 制御は、データ列を変調した後、変調後のチャネルビット列に、所定の間隔で、DSV 制御ビットを少なくとも  $(d + 1)$  ビットだけ付加することで行われる。これに対して、表 2 のような変換テーブルにおいては、表 1 の場合と同様の DSV 制御を行うこともできるが、表 2 におけるデータパターンと変換される符号パターンの関係を生かして、さらに効率良く DSV 制御を行うことができる。即ち、変換テーブルが、データパターン内の“ 1 ”の個数と、符号パターン内の“ 1 ”の個数を、2 で割った時の余りが、どちらも 1 あるいは 0 で同一となるような変換規則を持っている時、上記のようにチャネルビット列内に、「反転」を表す“ 1 ”、あるいは「非反転」を表す“ 0 ”の DSV 制御ビットを挿入することは、データビット列内に、「反転」するならば（1）の、「非反転」ならば（0）の、それぞれ DSV 制御ビットを挿入することと等価となる。

#### 【 0 0 3 0 】

例えば表 2 において、データ変換する 3 ビットが（001）と続いたときに、その後ろにおいて DSV 制御ビットを挿入すると、データは、（001-x）（x は 1 ビットで、「0」または「1」）となる。ここで x に「0」を与えれば、表 2 の変換テーブルで、

データパターン 符号パターン

0010 010 000

の変換が行われ、また、「1」を与えれば、

データパターン 符号パターン

0011 010 100

の変換が行われる。符号語列を NRZI 化して、レベル符号列を生成すると、これらは

データパターン 符号パターン レベル符号列

0010 010 000 011 111

0011 010 100 011 000

となり、レベル符号列の最後の 3 ビットが相互に反転している。このことは、DSV 制御ビット x の（1）と（0）を選択することによって、データ列内においても、DSV 制御が行えることを意味する。

#### 【 0 0 3 1 】

DSV 制御による冗長度を考えると、データ列内の 1 ビットで DSV 制御を行うということは、チャネルビット列で表現すれば、表 2 の変換率（m:n=2:3）より、1.5 チャネルビットで DSV 制御を行っていることに相当する。一方、表 1 のような RLL(1,7) テーブルにおいて DSV 制

10

20

30

40

50

御を行うためには、チャネルビット列においてDSV制御を行う必要があるが、この時最小ランを守るためには、少なくとも2チャネルビットが必要であり、表2のDSV制御と比較すると、冗長度がより大きくなってしまう。換言すれば、表2のテーブル構造を持つ時、データ列内でDSV制御を行うことで、効率よくDSV制御を行うことができる。

【0032】

そしてさらに、本発明者らは、表2の1,7PP符号に対する逆変換テーブル（復調テーブル）として、次の表3を提案した（例えば、特許文献2）。

【0033】

<表3>

1,7PP\_DEM : (d, k; m, n; r) = (1, 7; 2, 3; 4)

符号パターン データパターン

|       |     |    |

|-------|-----|----|

| i = 1 | 101 | 11 |

|       | 000 | 11 |

|       | 001 | 10 |

|       | 010 | 01 |

|       |                  |      |

|-------|------------------|------|

| i = 2 | 010 100          | 0011 |

|       | 010 000(not 100) | 0010 |

|       | 000 100          | 0001 |

|       |                      |        |

|-------|----------------------|--------|

| i = 3 | 000 100 100          | 000011 |

|       | 000 100 000(not 100) | 000010 |

|       | 010 100 100          | 000001 |

|       | 010 100 000(not 100) | 000000 |

|       |                                                  |        |

|-------|--------------------------------------------------|--------|

| i = 3 | : Prohibit Repeated Minimum Transition Runlength |        |

|       | 001 000 000(not 100)                             | 110111 |

|       |                 |          |

|-------|-----------------|----------|

| i = 4 | : limits k to 7 |          |

|       | 000 100 100 100 | 00001000 |

|       | 010 100 100 100 | 00000000 |

【0034】

上記表3の逆変換テーブルは、例えば拘束長の大きい方から順に入力符号語列との一致比較・変換をすることで復調処理が行われ、元のデータ列を得ることが出来る。この表3の逆変換テーブルは、最小ランの連続を6回までに制限するように、拘束長i=3において、置換パターンとして1つの最小ラン連続制限パターン（逆変換パターン）を持っている。また同期パターンは、表2に示されている場合と同様であり、検出された位置を基準として表3にあるような逆変換テーブルに従って、復調処理が行われる。

【0035】

以上に説明した(d, k)=(1, 7)の最小ランと最大ランを持った、高記録密度に対応した表2の変調テーブルとそれに対応する表3の復調テーブルは、高密度光ディスクであるBlu-ray Disc ReWritablever1.0（登録商標）におけるフォーマットとして採用されている。

【特許文献1】特開平6-197024号公報

【特許文献2】特開平11-346154号公報

【発明の開示】

【発明が解決しようとする課題】

【0036】

今後さらなる高記録密度に対して、具体的には、高密度光ディスクに対するさらなる高密度規格に対して、さらに安定した変復調方式が要求されている。

【0037】

10

20

30

40

50

その際、既に商品化されているBlu-ray Disc ReWritable ver1.0に対し、従来の1,7PP符号と同様なテーブルの構成で、より安定したシステムを実現する復調方式が実現すれば、従来の設計技術を流用することが出来ることより、ハードウェア設計時の設計リスクを低減することができる。

【0038】

さらに、従来の1,7PP符号テーブルを全て含んだ復調構成とすれば、従来の1,7PP符号によって変調され、記録されたデータの復調を行うことも可能となる。

【0039】

しかし、RLL符号を高線密度にディスクに記録再生する場合、最小ランdの連続したパターンがあると、長いエラーが発生し易かった。また(1,7;2,3)符号においてDSV制御を行うには冗長ビットを挟む必要があり、なるべくこの冗長ビットを少なくする必要があった。そして、このような状況から開発された、最小ランd=1のRLL符号(d,k;m,n)=(1,7;2,3)において、最小ランの連続する回数を制限し、さらに最小ランおよび最大ランを守りながら、効率の良い制御ビットでDSV制御を行うことができる等の特徴を持つ、1,7PP符号に対し、さらに安定した符号列を発生する変調テーブルに対応した復調テーブル、および復調装置が望まれている。具体的には、エッジシフトによるエラーの発生を、さらに少なくする復調方式が要求されている。

10

【0040】

さらに、従来との再生互換のために、またハードウェア共通化とハードウェア設計を容易にするために、従来の1,7PPテーブルを含み、かつ同様なテーブル構成であることが望まれる。

20

【0041】

本発明は、このような状況に鑑みてなされたものであり、基本構成を1,7PP符号と同様にした上で、従来1,7PP符号と再生互換性を考慮し、さらに、最小ランの連続する回数を、従来よりもさらに減らすようにし、記録再生時における、長いエラーの発生を改善するものである。

【課題を解決するための手段】

【0042】

本発明の側面は、最小ランがd (d > 0)、最大ランがkであり、基本符号語長がnビットの可変長符号(d,k;m,n;r) (最大拘束長r > 1)を、基本データ長がmビットのデータに変換する復調テーブルにおいて、基本符号語長がnビットの基礎符号からなる符号パターンを、基本データ長がmビットの基礎データからなるデータパターンに変換する基礎テーブルと、前記最小ランの連続をN (N > 0)回以下に制限するように決定されている最小ラン連続制限パターンの符号パターンを、対応するデータパターンに変換する第1の置換テーブルと、前記最大ランをM (M > 0)に制限するように決定されている符号パターンを、対応するデータパターンに変換する第2の置換テーブルとを有し、前記第1の置換テーブルは、拘束長が第1の値である場合における複数の異なる前記最小ラン連続制限パターンの符号パターンを、対応する同一のデータパターンに変換し、拘束長が前記第1の値よりも小さな第2の値である場合における单一の前記最小ラン連続制限パターンの符号パターンを、対応するデータパターンに変換するものであり、d = 1, k = 7, m = 2, n = 3であり、前記最小ランの連続が5回以下に制限されている復調テーブルである。

30

【0043】

拘束長が前記第1の値である場合における複数の異なる前記最小ラン連続制限パターンの符号パターンに対応するデータパターンは、その一部に、拘束長が前記第2の値である場合における单一の前記最小ラン連続制限パターンの符号パターンに対応するデータパターンを含むことができる。

40

【0044】

前記符号パターン内の“1”的個数と、前記データパターン内の“1”的個数が、2で割った際の余りが、どちらも1あるいは0で一致するような変換規則を有することができる。

50

## 【0047】

本発明の他の側面は、最小ランが  $d$  ( $d > 0$ )、最大ランが  $k$  であり、基本符号語長が  $n$  ビットの可変長符号( $d, k; m, n; r$ ) (最大拘束長  $r > 1$ )を、基本データ長が  $m$  ビットのデータに変換する復調装置において、基礎符号パターンとそれに対応付けられた基礎データパターンとを含む第1の復調テーブルに従って、入力された符号語列をデータ列に変換する第1の変換手段と、前記最小ランの連続を  $N$  ( $N > 0$ )回以下に制限するように決定されている最小ラン連続制限パターンの符号パターンとして、拘束長が第1の値である場合における複数の異なる第1の前記符号パターン及び拘束長が前記第1の値よりも小さい第2の値である場合における单一の第2の前記符号パターン、複数の異なる前記第1の符号パターンにそれぞれ対応付けられた同一のデータパターン、並びに单一の前記第2の符号パターンに対応付けられたデータパターンを含む第2の復調テーブルに従って、入力された符号語列をデータ列に変換する第2の変換手段と、前記最小ラン連続制限パターンの符号パターンを検出する第1の検出手段と、前記最小ラン連続制限パターンが検出された場合、前記第2の復調テーブルに従って変換されたデータ列を選択する選択手段とを備え、前記第1の復調テーブルは、前記最大ランを  $M$  ( $M > 0$ ) に制限するように決定されている符号パターンとそれに対応付けられたデータパターンをさらに有し、 $d = 1, k = 7, m = 2, n = 3$  であり、前記最小ランの連続が5回以下に制限されている復調装置である。10

## 【0048】

少なくとも1つの前記最小ラン連続制限パターンの符号パターンを一部に含む符号パターンを検出する第2の検出手段をさらに備え、前記選択手段は、1つの前記最小ラン連続制限パターンの符号パターンを一部に含む符号パターンが検出されたかどうかの結果を用いて、前記第1の復調テーブルの第1の部分または第2の部分に従って変換されたデータ列のいずれかを選択することができる。20

## 【0049】

前記選択手段は、最小単位の基礎符号パターンとそれに対応付けられた基礎データパターンに従って変換されたデータ列を選択することができる。

## 【0050】

前記選択手段により選択されたデータ列から、所定の位置に挿入されている同期パターンまたはDSV制御ビットを取り除き、データビットを取り出す取出手段をさらに備えることができる。30

## 【0051】

入力された信号から前記符号語列を作成する符号語列化手段をさらに備えることができる。

## 【0052】

入力された前記符号語列から、所定の位置に挿入されている同期パターンを検出する同期パターン検出手段をさらに備えることができる。

## 【0054】

また本発明の他の側面は、最小ランが  $d$  ( $d > 0$ )、最大ランが  $k$  であり、基本符号語長が  $n$  ビットの可変長符号( $d, k; m, n; r$ ) (最大拘束長  $r > 1$ )を、基本データ長が  $m$  ビットのデータに変換する復調方法、プログラム、またはプログラムが記録された記録媒体において、基礎符号パターンとそれに対応付けられた基礎データパターンとを含む第1の復調テーブルに従って、入力された符号語列をデータ列に変換する第1の変換ステップと、前記最小ランの連続を  $N$  ( $N > 0$ )回以下に制限するように決定されている最小ラン連続制限パターンの符号パターンとして、拘束長が第1の値である場合における複数の異なる第1の前記符号パターン及び拘束長が前記第1の値よりも小さい第2の値である場合における单一の第2の前記符号パターン、複数の異なる前記第1の符号パターンにそれぞれ対応付けられた同一のデータパターン、並びに单一の前記第2の符号パターンに対応付けられたデータパターンを含む第2の復調テーブルに従って、入力された符号語列をデータ列に変換する第2の変換ステップと、前記最小ラン連続制限パターンの符号パターンを検出40

する検出ステップと、前記最小ラン連続制限パターンの符号パターンが検出された場合、前記第2の復調テーブルに従って変換されたデータ列を選択する選択ステップとを含み、前記第1の復調テーブルは、前記最大ランをM( $M > 0$ )に制限するように決定されている符号パターンとそれに対応付けられたデータパターンをさらに有し、 $d = 1$ ,  $k = 7$ ,  $m = 2$ ,  $n = 3$ であり、前記最小ランの連続が5回以下に制限されている復調方法、それらのステップをコンピュータに実行させるプログラム、またはプログラムが記録された記録媒体である。

【0055】

本発明の側面においては、復調テーブルが、基本符号語長がnビットの基礎符号からなる符号パターンを、基本データ長がmビットの基礎データからなるデータパターンに変換する基礎テーブルと、最小ランの連続をN( $N > 0$ )回以下に制限するように決定されている複数の異なる最小ラン連続制限パターンの符号パターンを、対応するデータパターンに変換する第1の置換テーブルと、最大ランをM( $M > 0$ )に制限するように決定されている符号パターンを、対応するデータパターンに変換する第2の置換テーブルとにより構成されている。

【0056】

本発明の他の側面においては、第1の復調テーブルと第2の復調テーブルに従って、入力された符号語列がデータ列に変換される。最小ラン連続制限パターンの符号パターンが検出された場合、第2の復調テーブルに従って変換されたデータ列が選択される。

【発明の効果】

【0057】

本発明の側面によれば、最小ランが連続する回数をより少なくすることができる。また、本発明の側面によれば、エラーの発生をより少なくすることができる。

【発明を実施するための最良の形態】

【0058】

以下に本発明の実施の形態を説明するが、本発明の構成要件と、明細書または図面に記載の実施の形態との対応関係を例示すると、次のようになる。この記載は、本発明をサポートする実施の形態が、明細書または図面に記載されていることを確認するためのものである。従って、明細書または図面には記載されているが、本発明の構成要件に対応する実施の形態として、ここには記載されていない実施の形態があったとしても、そのことは、その実施の形態が、その構成要件に対応するものではないことを意味するものではない。逆に、実施の形態が構成要件に対応するものとしてここに記載されていたとしても、そのことは、その実施の形態が、その構成要件以外の構成要件には対応しないものであることを意味するものでもない。

【0059】

本発明の側面は、最小ランがd( $d > 0$ )、最大ランがkであり、基本符号語長がnビットの可変長符号( $d, k; m, n; r$ ) (最大拘束長 $r > 1$ )を、基本データ長がmビットのデータに変換する復調テーブルにおいて、基本符号語長がnビットの基礎符号からなる符号パターンを、基本データ長がmビットの基礎データからなるデータパターンに変換する基礎テーブル (例えば、表4の基礎テーブル) と、前記最小ランの連続をN( $N > 0$ )回以下に制限するように決定されている最小ラン連続制限パターンの符号パターンを、対応するデータパターンに変換する第1の置換テーブル (例えば、表4の置換テーブル) と、前記最大ランをM( $M > 0$ )に制限するように決定されている符号パターン (例えば、表4の符号パターン “000 100 100 100”, “010 100 100 100”) を、対応するデータパターン (例えば、表4のデータパターン (00001000), (00000000)) に変換する第2の置換テーブル (例えば、表4の置換テーブル) とを有し、前記第1の置換テーブルは、拘束長が第1の値 (例えば、 $i=5$ ) である場合における複数の異なる前記最小ラン連続制限パターンの符号パターン (例えば、表4の符号パターン “101 010 000 000 101”, “000 010 000 00 101”) を、対応する同一のデータパターン (例えば、表4のデータパターン (100111 0111)) に変換し、拘束長が前記第1の値よりも小さな第2の値 (例えば、 $i=3$ ) である

10

20

30

40

50

場合における单一の前記最小ラン連続制限パターンの符号パターン（例えば、表4の符号パターン“001 000 000(not 100)”）を、対応するデータパターン（例えば、表4のデータパターン（110111））に変換するものであり、 $d = 1$ ， $k = 7$ ， $m = 2$ ， $n = 3$ であり、前記最小ランの連続が5回以下に制限されている復調テーブル（例えば、表4の復調テーブル）である。

【0060】

拘束長が前記第1の値である場合における複数の異なる前記最小ラン連続制限パターンの符号パターン（例えば、表4の符号パターン“101 010 000 000 101”）に対応するデータパターン（例えば、表4のデータパターン（1001110111））は、その一部に、拘束長が前記第2の値である場合における单一の前記最小ラン連続制限パターンの符号パターン（例えば、表4の符号パターン“001 000 000”）に対応するデータパターン（例えば、データパターン（110111））を含むことができる。

【0062】

本発明の他の側面は、基礎符号パターンとそれに対応付けられた基礎データパターン（例えば、表4の基礎テーブル）とを含む第1の復調テーブル（例えば、図4の逆変換テーブル82A乃至82C）に従って、入力された符号語列をデータ列に変換する第1の変換手段（例えば、図3の逆変換パターン処理部41）と、前記最小ランの連続を $N$ （ $N > 0$ ）回以下に制限するように決定されている最小ラン連続制限パターンの符号パターンとして、拘束長が第1の値である場合における複数の異なる第1の前記符号パターン及び拘束長が前記第1の値よりも小さい第2の値である場合における单一の第2の前記符号パターン、複数の異なる前記第1の符号パターンにそれぞれ対応付けられた同一のデータパターン、並びに单一の前記第2の符号パターンに対応付けられたデータパターンを含む第2の復調テーブル（例えば、表4の拘束長 $i = 3$ の変換パターン、及び拘束長 $i = 5$ の変換パターン）に従って、入力された符号語列をデータ列に変換する第2の変換手段（例えば、図4の最小ラン連続制限逆変換テーブル72B）と、前記最小ラン連続制限パターン（例えば、表4の符号パターン“000 010 000 000 101”，“101 010 000 000 101”）の符号パターンを検出する第1の検出手段（例えば、図4の最小ラン連続制限逆変換パターン検出部71）と、前記最小ラン連続制限パターンが検出された場合（例えば、図11のステップS231で最小ラン連続制限逆変換パターン検出フラグ（15cbit）がonであると判定された場合）、前記第2の復調テーブルに従って変換されたデータ列を選択する選択手段（例えば、図11のステップS232の処理を実行する図3の逆変換パターン決定部44）とを備え、前記第1の復調テーブルは、前記最大ランを $M$ （ $M > 0$ ）に制限するように決定されている符号パターンとそれに対応付けられたデータパターン（例えば、図4の逆変換テーブル82D）をさらに有し、 $d = 1$ ， $k = 7$ ， $m = 2$ ， $n = 3$ であり、前記最小ランの連続が5回以下に制限されている復調装置（例えば、図1の復調装置1）である。

【0063】

少なくとも1つの前記最小ラン連続制限パターン（例えば、表4の符号パターン“000 010 000 000 101”）の符号パターンを一部に含む符号パターン（例えば、図6のステップS31の符号パターン“xxx 000 010 000 000 101”）を検出する第2の検出手段（例えば、図3のパターン検出予想処理部43）をさらに備え、前記選択手段は、1つの前記最小ラン連続制限パターンの符号パターンを一部に含む符号パターンが検出されたかどうかの結果（例えば、図11のステップS241で予想フラグがonかどうかの結果）を用いて、前記第1の復調テーブルの第1の部分（例えば、図4の逆変換テーブル82A）または第2の部分（例えば、図4の逆変換テーブル82B）に従って変換されたデータ列のいずれかを選択する（例えば、図11のステップS242, S243, S244の処理）ことができる。

【0064】

前記選択手段は、最小単位（例えば、表4の拘束長 $i = 1$ ）の基礎符号パターンとそれに対応付けられた基礎データパターンに従って変換されたデータ列を選択することができる。

【0065】

10

20

30

40

50

前記選択手段により選択されたデータ列から、所定の位置に挿入されている同期パターンまたはDSV制御ビットを取り除き、データビットを取り出す取出手段（例えば、図1のデータビット取出部24）をさらに備えることができる。

【0066】

入力された信号から前記符号語列を作成する符号語列化手段（例えば、図1のチャネルビット列化部21）をさらに備えることができる。

【0067】

入力された前記符号語列から、所定の位置に挿入されている同期パターンを検出する同期パターン検出手段（例えば、図1の同期パターン検出処理部22）をさらに備えることができる。

10

【0068】

本発明の側面は、基礎符号パターンとそれに対応付けられた基礎データパターン（例えば、表4の基礎テーブル）とを含む第1の復調テーブル（例えば、図4の逆変換テーブル82A乃至82C）に従って、入力された符号語列をデータ列に変換する第1の変換ステップ（例えば、図5のステップS6）と、前記最小ランの連續をN（N > 0）回以下に制限するよう決してある最小ラン連続制限パターンの符号パターンとして、拘束長が第1の値である場合における複数の異なる第1の前記符号パターン及び拘束長が前記第1の値よりも小さい第2の値である場合における単一の第2の前記符号パターン、複数の異なる前記第1の符号パターンにそれぞれ対応付けられた同一のデータパターン、並びに単一の前記第2の符号パターンに対応付けられたデータパターンを含む第2の復調テーブル（例えば、表4の拘束長i = 3の変換パターン、及び拘束長i = 5の変換パターン）に従って、入力された符号語列をデータ列に変換する第2の変換ステップ（例えば、図7のステップS54）と、前記最小ラン連続制限パターン（例えば、表4の符号パターン“000 010 000 000 101”，“101 010 000 000 101”）の符号パターンを検出する検出ステップ（例えば、図7のステップS52）と、前記最小ラン連続制限パターンが検出された場合（例えば、図11のステップS231で最小ラン連続制限逆変換パターン検出フラグ（15cbit）がonであると判定された場合）、前記第2の復調テーブルに従って変換されたデータ列を選択する選択ステップ（例えば、図5のステップS232）とを含み、前記第1の復調テーブルは、前記最大ランをM（M > 0）に制限するよう決してある最小ラン連続制限パターンとそれに対応付けられたデータパターン（例えば、図4の逆変換テーブル82D）をさらに有し、d = 1, k = 7, m = 2, n = 3であり、前記最小ランの連續が5回以下に制限されている復調方法（例えば、図1の復調装置1の復調方法）である。

20

30

30

【0070】

以下、図を参照して本発明の実施の形態について説明する。以下、復調後のデータ列を（000011）のように（ ）で区切って表し、復調前のチャネルビット列を、“000 100 100”のように“ ”で区切って表す。また、最小ランd = 1、最大ランk = 7、かつ変換率(m:n)=(2:3)である可変長符号であり、さらに、最小ランの連續する回数を制限し、かつ、最小ランおよび最大ランを守りながら、効率の良いDSV制御ビットで、完全なDSV制御を行う変換テーブルを持つ符号を、1,7PP符号（PP:Parity-preserve Prohibit-repeated-minimum-transition-runlength）と称する。

40

【0071】

以下の表4は、本発明の実施の形態としての復調テーブル（逆変換テーブル）の例を表す。

【0072】

なお、本明細書において、データパターンを符号パターンに変換する場合を変換すると表現し、逆に符号パターンをデータパターンに変換する場合を逆変換すると表現する。そして、データパターンを符号パターンに変換する変換パターンが記述されているテーブルを変調テーブル（変換テーブル）と表現し、符号パターンをデータパターンに変換する変換パターン（逆変換パターン）が記述されているテーブルを復調テーブル（逆変換テーブル）という。

50

## 【 0 0 7 3 】

&lt; 表 4 &gt;

1,7PP- rmtr5\_DEM RLL(1,7;2,3;5)

| 符号パターン<br>( 符号語列 )                             | データパターン<br>( 復調データ列 ) |    |

|------------------------------------------------|-----------------------|----|

| i = 1 101                                      | 11                    |    |

| 000                                            | 11                    |    |

| 001                                            | 10                    |    |

| 010                                            | 01                    |    |

|                                                |                       | 10 |

| i = 2 010 100                                  | 0011                  |    |

| 010 000(not 100)                               | 0010                  |    |

| 000 100                                        | 0001                  |    |

|                                                |                       |    |

| i = 3 000 100 100                              | 000011                |    |

| 000 100 000(not 100)                           | 000010                |    |

| 010 100 100                                    | 000001                |    |

| 010 100 000(not 100)                           | 000000                |    |

|                                                |                       | 20 |

| i = 4 : limits k to 7                          |                       |    |

| 000 100 100 100                                | 00001000              |    |

| 010 100 100 100                                | 00000000              |    |

|                                                |                       |    |

| Prohibit Repeated Minimum Transition Runlength |                       |    |

| i = 3 001 000 000(not 100)                     | 110111                |    |

| i = 5 101 010 000 000 101                      | 1001110111            |    |

| 000 010 000 000 101                            | 1001110111            |    |

## Termination table

| 符号パターン        | データパターン |  |

|---------------|---------|--|

| i = 1 000     | 00      |  |

| i = 2 010 100 | 0000    |  |

## SYNC &amp; Termination

```

#01 010 000 000 010 000 000 010 (24 cbits)

#= 0 not terminate case

#= 1 terminate case

```

## 【 0 0 7 4 】

表 4 の復調テーブル（逆変換テーブル）は、可変長符号( $d, k; m, n; r$ )=(1,7;2,3;5)である1,7PP符号で、最小ランの連続が5回までに制限されている符号語列に対して、データ復調を行う逆変換テーブルである。

## 【 0 0 7 5 】

表 4 の逆変換テーブルは1,7PP符号であり、さらに基本構成が表 3 と同様でありながら、最小ランの連続を制限する逆変換パターンを複数通り持っている。即ち、表 4 の逆変換テーブルは、逆変換パターン（符号パターン（符号語列））とデータパターン（復調データ列）として、それがないと変換処理ができない基礎パターンを有する基礎テーブル、それがなくても変換処理は可能であるが、それを行うことによってより効果的な変換処理が実現する置換パターンを有する置換テーブル、および符号を任意の位置で終端させるための終端パターンを有する終端テーブルを含んでいる。

## 【 0 0 7 6 】

10

20

30

40

50

基礎テーブルの逆変換パターンは、拘束長  $i = 1$  の“101”から拘束長  $i = 3$  の“010 100 000 (not 100)”までの符号パターン（基礎符号パターン）と、それに対応する(11)から(000000)までのデータパターン（基礎データパターン）により構成される。

#### 【0077】

置換テーブルの逆変換パターンは、最大ランを制限する逆変換パターンと最小ランの連続を制限する逆変換パターンとで構成される。なお、以下においては、置換テーブルの逆変換パターンは置換パターンとも称する。

#### 【0078】

最大ランを制限する逆変換パターン（置換パターン）は、拘束長  $i = 4$  の符号パターン“000 100 100 100”，“010 100 100 100”と、それに対応するデータパターン（00001000），（00000000）により構成される。not 100は、次の3チャネルビットが“100”ではないことを意味する。

10

#### 【0079】

最小ランの連続を制限する逆変換パターン（置換パターン）は、拘束長  $i = 3$  の符号パターン“001 000 000 (not 100)”，並びに拘束長  $i = 5$  の符号パターン“101 010 000 000 101”，“000 010 000 000 101”と、それに対応するデータパターン（110111），（1001110111）により構成される。

#### 【0080】

終端テーブルの逆変換パターンは、符号パターン“000”，“010 100”からなる終端符号パターンと、それに対応するデータパターン（00），（0000）からなる終端データパターンとにより構成される。

20

#### 【0081】

なお、入力されたデータがデータパターンと一致する場合、そのデータパターンと一致する部分を対応する符号パターンに変換するためにデータパターンと符号パターンの対応関係を記述するのが変調テーブル（変換テーブル）であるのに対して、入力された符号列が符号パターンと一致する場合、その符号パターンと一致する部分を対応するデータパターンに逆変換するために符号パターンとデータパターンとの対応関係を記述するのが復調テーブル（逆変換テーブル）であり、以下においては、表4の一部のことも必要に応じて復調テーブル（逆変換テーブル）と記述する。

30

表4において、符号パターン“101”，“000”的いずれもがデータパターン（11）に逆変換されるのは、対応する変換テーブル（変調テーブル）（図示せず）において、最小ラン  $d = 1$ 、最大ラン  $k = 7$  で、データパターン（11）に対して不確定符号“\*”を含む符号パターン“\*0\*”が対応付けられていたからである。同様に、符号パターン“101 010 000 000 101”，“000 010 000 000 101”的いずれもが、データパターン（1001110111）に逆変換されるのは、拘束長  $i = 5$  において、最小ラン  $d$  の連続を制限するために、変換テーブル（変調テーブル）においてデータ（1001110111）に対して不確定符号“\$”を含む符号パターン“\$0\$ 010 000 000 101”が対応付けられていたからである。

#### 【0082】

表4の逆変換テーブルは可変長構造を有しているので、 $i = 1$  から  $i = 3$  までの基礎パターンを持つ。基礎パターンでは、それぞれの拘束長  $i$  において変換する符号パターンと一致したとき、復調データ列として変換される。

40

#### 【0083】

また、表4の逆変換テーブルは、拘束長  $i = 3$  において、最小ラン  $d$  の連続を制限する置換パターンを持っている。9符号語が符号パターン“001 000 000”と一致し、さらに続く3符号語が符号パターン“010”と一致するとき、復調データ列としてデータパターン（110111）に変換される。なお、9符号語が符号パターン“001 000 000”と一致した場合、さらに続く3符号語が符号パターン“100”以外の符号であったとき、データパターン（110111）に変換するようにしてもよい。このようにすれば、“010”的場合だけではなく、再生エラーのために“101”，“000”，“001”となった場合にもデータパー

50

ン(110111)への変換が行われる。

【0085】

そして表4の逆変換テーブルは、拘束長*i* = 4のパターンにおいて、最大ラン*k* = 7を実現するための置換パターン(最大ラン保証パターン)を持っている。すなわち、12符号語は符号パターン“000 100 100 100”と一致するとき、データパターン(00001000)に変換される。また、12符号語は符号パターン“010 100 100 100”と一致するとき、データパターン(00000000)に変換される。

【0086】

表4の逆変換テーブルは、最小ランの連続を制限する逆変換パターン(置換パターン)としてさらに、拘束長*i* = 5の符号パターン“101 010 000 000 101”，“000 010 000 000 101”を有している。符号パターン“101 010 000 000 101”，“000 010 000 000 101”は、いずれも同一のデータパターン(1001110111)に対応付けられている。これは、表4の復調テーブルに対応する変調テーブルにおいて、データパターン(1001110111)が、不確定符号“\$”を含む符号パターン“\$0\$ 010 000 000 101”に対応付けられていたことに起因するものである。

【0087】

さらに表4は、同期パターンを挟むため利用される終端パターンを持っている。同期パターン列の先頭の1符号語が、終端パターン使用識別情報とされている。同期パターン列の先頭符号語が“1”であるとき、同期パターンの直前の符号は終端パターンを用いて復調データ列に変換され、また同期パターン列の先頭符号語が“0”であるとき、同期パターンの直前の符号は終端パターン以外を用いて(基礎テーブルまたは置換テーブルを用いて)復調データ列に変換される。

【0088】

以上のようにして、表4によって、 $(d, k; m, n; r) = (1, 7; 2, 3; 5)$ であり、さらに、最小ランの連続が5回までに制限された符号語列を元のデータ列に復調することができる。

【0089】

なお、表4の逆変換テーブルは、表3の逆変換テーブル要素を全て持っている構造となっている。

【0090】

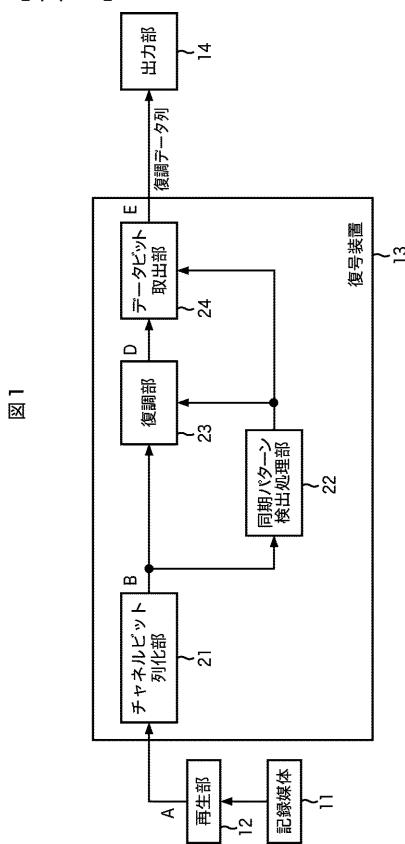

次に、図を参照して、本発明に係る復調装置の実施の形態を図面を参照しながら説明する。図1は、本発明の復調装置の全体の構成を示すブロック図である。

【0091】

復調装置1は、図1に示されるように、伝送路より伝送されてきた信号、または、記録媒体11に記録されている信号を出力する再生部12、再生部12からの出力信号を復号する復号装置13、復号装置13からの信号を出力する出力部14により構成されている。

【0092】

復号装置13は、再生部12より入力された信号を2値化し、また必要であれば(信号がNRZI化されている場合には)、逆NRZI化するチャネルビット列化部21、チャネルビット列化部21より出力されるチャネルビット列から所定の位置に所定の間隔で挿入されている同期パターンを検出することで、後段の復調処理の開始位置の同期を取る同期パターン検出処理部22、チャネルビット列化部21より出力されるチャネルビット列を復調しデータ列化する復調部23、並びに、復調部23の出力から冗長ビットとして残っている所定の間隔で挿入されている同期パターンとDSV制御ビットを取り除き、データビットを取り出すデータビット取出部24により構成されている。

【0093】

また、図示しないが、タイミング信号を生成し、各部に供給してタイミングを管理するタイミング管理部が設けられている。

【0094】

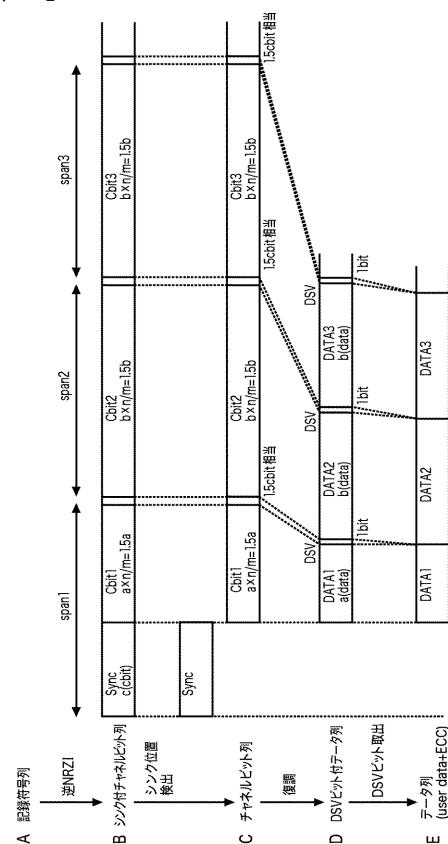

図2は、図1の復調装置1の各部におけるデータフォーマットを示す図である。再生部12により記録媒体11より再生された再生信号列(図2A)はチャネルビット列化部21に入力

10

20

30

40

50

され、シンク付チャネルビット列（同期パターンを含むチャネルビット列）（図2B）として出力される。同期パターン検出処理部22は、チャネルビット列化部21より出力されたシンク付チャネルビット列からシンク（同期パターン）を検出し、そのタイミング信号を復調部23とデータビット取出部24に出力する。

#### 【0095】

シンク（同期パターン）はcチャネルビットで構成されている。復調部23は、チャネルビット列化部21より入力されたシンク付チャネルビット列を復調し、DSVビット付データ列を出力する（図2D）。データ列のDSV区間(DATA1, DATA2, およびDATA3)をそれぞれa比特データ、b比特データ、およびb比特データとすると、変調テーブルの変換率m:nは2:3であるから、各DSV区間(DATA1, DATA2, およびDATA3)の変調後のチャネルビット区間は、 $(a \times 3/2) = (1.5a)$ あるいは、 $(b \times 3/2) = (1.5b)$ となっている。これが復調（復号）されるため、DSVビット付データ列のDSV区間（DATA1, DATA2, およびDATA3）は、それぞれa比特データ、b比特データ、およびb比特データとなる。

10

#### 【0096】

またこの例の場合、所定の位置（この例ではDATA1位置の前の先頭位置）に、シンク（SYNC）が挿入されるため、SYNCのチャネルビット数をc(cbit)とすれば、a,b,cの間には  $1.5a + c = 1.5b$  の関係が成立している。すなわち、各DSV区間の長さを表すspan1, span2, span3, ...は、同じ長さとされており、等しい間隔でDSV制御が行われている。

#### 【0097】

図2におけるチャネルビット内のDSV制御ビットは、1.5チャネルビット相当である。すなわち、データ列内にDSV制御ビットは1ビット挿入されるから、チャネルビット相当では変換率分だけ増加し、 $1 \text{ビット} \times n/m = 1 \times 3/2 = 1.5$ チャネルビットとなる。これを従来の方式と比較すると例えば、チャネルビット内でDSV制御を行う場合では、最小ランd=1を守って行うためには、2チャネルビットが必要であり、あるいは最小ラン・最大ランとも守って行うためには、4チャネルビットが必要である。これより、従来のDSV制御方式と較べると、本方式であるデータ列内DSV制御ビット挿入は、DSV制御のための冗長チャネルビットが少なく行えることがわかる。

20

#### 【0098】

データビット取出部24は、復調部23より出力されたDSVビット付データ列からシンク（同期パターン）とDSV制御ビットを除去することで、データビット（図2E）を取り出す。この復調データ列が出力部14に供給される。

30

#### 【0099】

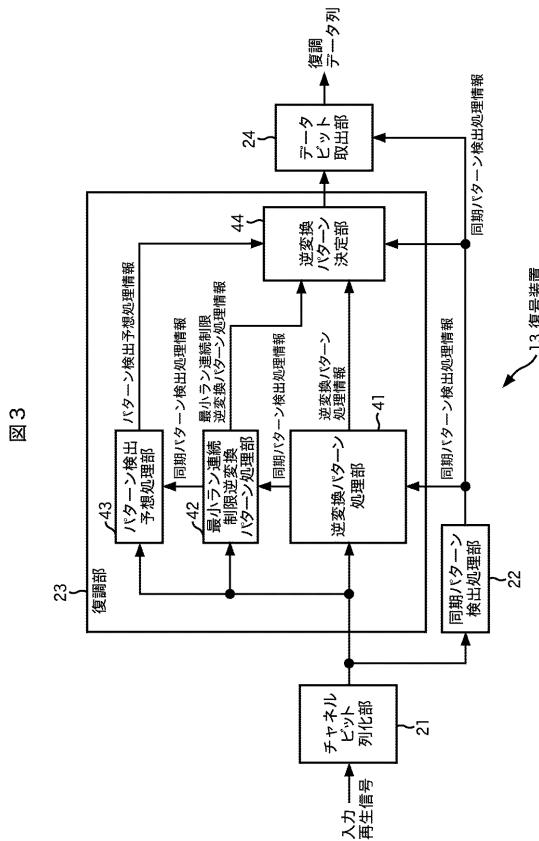

図3は、図1の復号装置13の主要部の構成の詳細を示すブロック図である。同図に示されるように、復調部23は、逆変換パターン処理部41、最小ラン連続制限逆変換パターン処理部42、パターン検出予想処理部43、および逆変換パターン決定部44により構成されている。

#### 【0100】

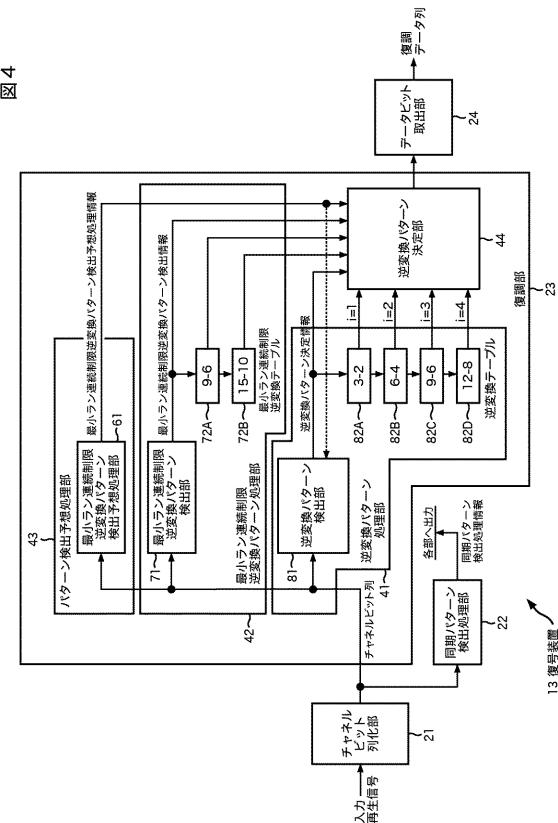

図4は、図3の復号装置13のさらにより詳細な構成を表している。図4に示されるように、逆変換パターン処理部41は、逆変換パターン検出部81と逆変換テーブル82A乃至82Dにより構成されている。最小ラン連続制限逆変換パターン処理部42は、最小ラン連続制限逆変換パターン検出部71、並びに最小ラン連続制限逆変換テーブル72A, 72Bにより構成されている。パターン検出予想処理部43は、最小ラン連続制限逆変換パターン検出予想処理部61により構成されている。

40

#### 【0101】

図4において、入力された再生信号は再生部12により記録媒体11から再生された記録符号列（あるいは伝送路より入力された場合は伝送符号列）であり、2値化された状態では“111 100 110 000 00...”のように、レベル符号となっている時、チャネルビット列化部21は、入力値の“1”と“0”が反転した位置に対して“1”を出力することで逆NRZI化を行い、チャネルビット列に変換して出力する。チャネルビット列化部21からの出力は、同期パターン検出処理部22、逆変換パターン検出部81、最小ラン連続制限逆変換パターン

50

検出部71、並びに最小ラン連続制限逆変換パターン検出予想処理部61へ供給される。

【0102】

同期パターン検出処理部22は、チャネルビット列化部21より供給されたチャネルビット列より、所定の位置に所定の間隔で挿入されている同期パターンを検出し、後段の復調処理を開始する位置を示すとともに、復調処理のために必要な情報を、逆変換パターン検出部81、最小ラン連続制限逆変換パターン検出部71、最小ラン連続制限逆変換パターン検出予想処理部61、逆変換パターン決定部44、並びにデータビット取出部24へ供給する。各部は、この情報をそれぞれ処理を開始する位置情報として用いる。

【0103】

逆変換パターン検出部81は、チャネルビット列よりRLL規則を守るためのパターンの逆変換パターン検出を行い、その結果情報としての逆変換パターン決定情報を逆変換パターン決定部44へ出力するとともに、各逆変換テーブル82A乃至82Dへも出力する。各逆変換テーブル82A乃至82Dは検出された逆変換パターン（変換データ列）を、逆変換パターン決定部44に供給する。また、逆変換パターン処理部41は、同期パターンを挿入するために必要に応じて用いられた終端テーブルの逆変換テーブルを持っており、直後にある同期パターンの先頭ビットを参照してデータビットを決定し、以下同様の処理を行う。

10

【0104】

最小ラン連続制限逆変換パターン検出部71は、チャネルビット列より、最小ランの連続回数を制限するための逆変換パターンを検出した時、その情報を最小ラン連続制限逆変換パターン検出情報として逆変換パターン決定部44へ出力するとともに、各最小ラン連続制限逆変換テーブル72A, 72Bへも出力する。各逆変換テーブル72A, 72Bは検出した逆変換パターン（変換データ列）を逆変換パターン決定部44に供給する。

20

【0105】

最小ラン連続制限逆変換パターン検出予想処理部61は、チャネルビット列の先頭ではない所定位置において、最小ランの連続回数を制限するための逆変換パターンのうちの所定の逆変換パターンを検出した時、その情報を最小ラン連続制限逆変換パターン検出予想処理情報として逆変換パターン決定部44へ出力する。

【0106】

逆変換パターン決定部44は、逆変換パターン検出部81、最小ラン連続制限逆変換パターン検出部71、そして最小ラン連続制限逆変換パターン検出予想処理部61からの情報を用いて、逆変換テーブル82A乃至82Dおよび最小ラン連続制限逆変換テーブル72A, 72Bからの逆変換データ列出力から採用する逆変換パターンを決定、選択し、データビット取出部24に出力する。そして、データビット取出部24は、冗長ビットとして残っている所定の間隔で挿入されている同期パターンあるいはDSV制御ビットを取り除くことでデータビットを取り出し、復調データ列として出力する。

30

【0107】

このほか各部の動作のタイミングは、図示しないタイミング管理部から供給されるタイミング信号に同期して管理されている。

【0108】

なお、図3と図4において、同期パターンを除去する手段については、同図の限りではなく、例えば、逆変換パターン決定部44で、例外処理として同期パターンを除去する構成としてもよく、その場合は、データビット取出部24においては、所定の間隔で挿入されたDSV制御ビットだけを取り除けばよい。

40

【0109】

図4と表4の間での対応を示すと次のようになる。すなわち、最小ラン連続制限逆変換パターン検出部71は、表4において、入力チャネルビット列が“001 000 000”であり、さらに続くチャネルビット列が“010”である時（“100”ではない時）、または“101 01 0 000 000 101”である時、若しくは、“000 010 000 000 101”である時動作する。最小ラン連続制限逆変換パターン検出予想処理部61は、表4において、入力チャネルビット列の4ビット目以降が“000 010 000 000 101”である時、動作する。

50

## 【0110】

逆変換パターン決定部44は、逆変換テーブル82A乃至82Dからの出力と、最小ラン連続制限逆変換テーブル72A, 72Bからの出力が重複する場合、逆変換パターン検出部81、最小ラン連続制限逆変換パターン検出部71、そして最小ラン連続制限逆変換パターン検出予想処理部61からの情報を用いて、いずれかの出力を選択する。表4において、例えば、拘束長  $i = 1$  の“001”と拘束長  $i = 3$  の“001 000 000”+“010”とが重複する場合は、拘束長の大きい最小ラン連続制限逆変換テーブル72Aからの出力（後者）が選択される。また、表4において、例えば、拘束長  $i = 1$  の“101”と拘束長  $i = 5$  の“101 010 000 000 101”とが重複するか、または拘束長  $i = 1$  の“000”と拘束長  $i = 5$  の“000 010 000 000 101”とが重複する場合は、拘束長の大きい最小ラン連続制限逆変換テーブル72Bからの出力（後者）が選択される。さらにまた、表4において例えば、拘束長  $i = 2$  の“010 000”と“010 000 010 000 000 101”とが重複する場合（拘束長  $i = 5$  の“000 010 000 000 101”的直前の符号が“010”である場合（後述する図10のステップS169でYesと判定された場合、すなわち、図11のステップS241でYesと判定された場合））は、最小ラン連続制限逆変換パターン検出予想処理部61からの出力に基づいて、3チャネルビットの“010”が出力される。10

## 【0111】

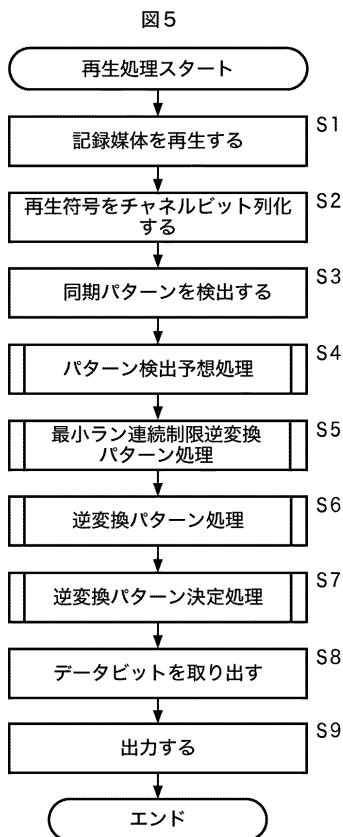

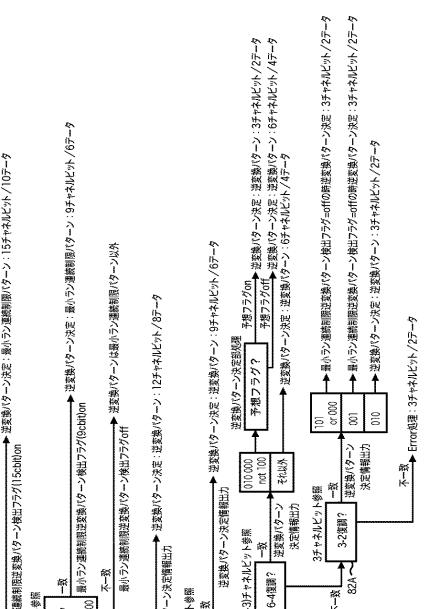

次に、図5のフローチャートを参照して復調装置1の動作について説明する。ステップS1において、再生部12は記録媒体11を再生する。ステップS2において、チャネルビット列化部21は、再生部12より供給された再生符号をチャネルビット列化する。ステップS3において、同期パターン検出処理部22は同期パターンを検出する。検出した結果に基づく情報は各部へ出力される。20

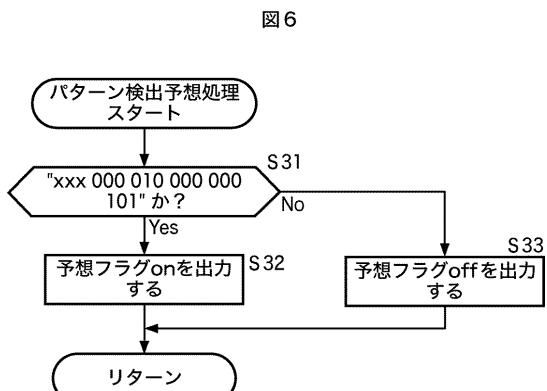

## 【0112】

ステップS4において、パターン検出予想処理部43はパターン検出予想処理を実行する。その詳細は図6のフローチャートを参照して後述するが、これにより所定の符号パターン“xxx 000 010 000 000 101”が検出された場合、予想フラグonが出力される。

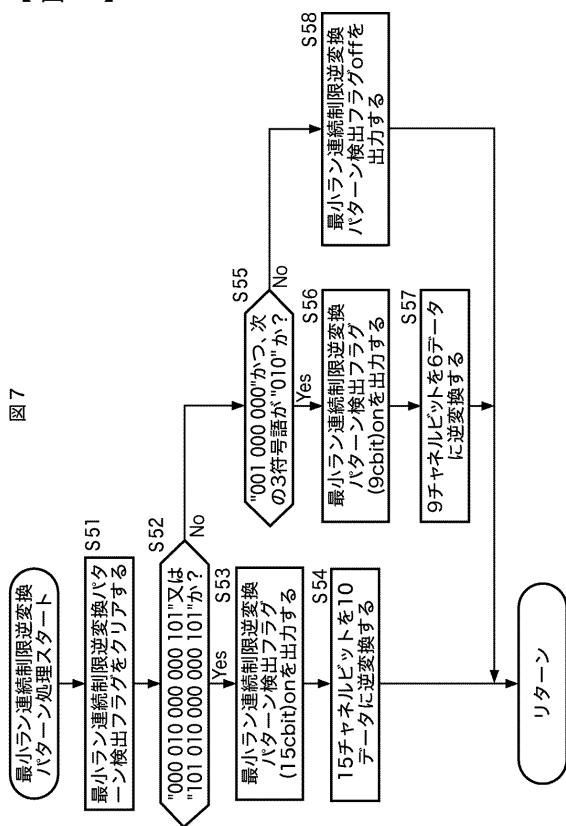

## 【0113】

ステップS5において、最小ラン連続制限逆変換パターン処理部42は最小ラン連続制限逆変換パターン処理を実行する。その詳細は図7のフローチャートを参照して後述するが、これにより、例えば符号パターン“000 010 000 000 101”または符号パターン“101 010 000 000 101”が検出された場合、最小ラン連続制限逆変換パターン検出フラグ（15cbit）onが出力される。また、符号パターン“001 000 000 010”が検出された場合、最小ラン連続制限逆変換パターン検出フラグ（9cbit）onが出力される。30

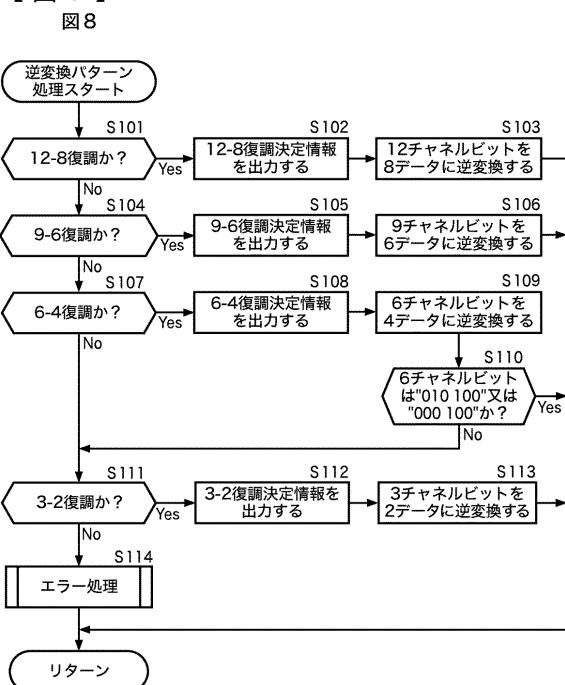

## 【0114】

ステップS6において、逆変換パターン処理部41は逆変換パターン処理を実行する。その処理の詳細は図8を参照して後述するが、これにより逆変換テーブル82A乃至82Dにより逆変換が実行される。

## 【0115】

なお、ステップS4乃至ステップS6の処理は実際には並行に実行される。

## 【0116】

ステップS7において、逆変換パターン決定部44は逆変換パターン決定処理を実行する。その処理の詳細は図11のフローチャートを参照して後述するが、これにより逆変換テーブル82A乃至82Dより供給されたデータパターン、または最小ラン連続制限逆変換テーブル72A, 72Bより供給されたデータパターンのいずれかが選択され、データビット取出部24に供給される。

## 【0117】

ステップS8において、データビット取出部24は、データビットを取り出す。すなわち、同期パターンとDSV制御ビットを除去することによりデータビットが取り出される。ステップS9において、出力部14はデータビット取出部24より入力された復調データ列をデスクランプルしたり、ECCでエラー訂正したりする。このようにして画像データ、音声データ4050

などの意味を有するデータ列が生成され、LCD, CRTなどの表示部、あるいはスピーカなどに出力される。あるいは、必要に応じてさらに所定のフォーマットでエンコードされ、各種のデバイス、伝送路に供給されたり、記録媒体に記録される。

【0118】

図6は、図5のステップS4のパターン検出予想処理の詳細を表している。

【0119】

ステップS31において、パターン検出予想処理部43の最小ラン連続制限逆変換パターン検出予想処理部61は、チャネルビット列化部21より入力されたチャネルビット列が、符号パターン“xxx 000 010 000 000 101”かを判定する。符号語列がこの符号パターンに一致する場合には、ステップS32において最小ラン連続制限逆変換パターン検出予想処理部61は、最小ラン連続制限逆変換パターン検出予想フラグonを出力する。

10

【0120】

ステップS31において、入力されたチャネルビット列が符号パターン“xxx 000 010 000 000 101”と一致しないと判定された場合、ステップS33において最小ラン連続制限逆変換パターン検出予想処理部61は、最小ラン連続制限逆変換パターン検出予想フラグoffを出力する。

【0121】

この最小ラン連続制限逆変換パターン検出予想フラグは、図10のステップS169、図11のステップS241において利用される。

20

【0122】

図7は、図5のステップS5の最小ラン連続制限逆変換パターン処理の詳細を表している。

【0123】

ステップS51において、最小ラン連続制限逆変換パターン処理部42の最小ラン連続制限逆変換パターン検出部71は、検出フラグをクリアする。即ち、後述するステップS53, S56で出力される最小ラン連続制限逆変換パターン検出フラグ(15cbit)と最小ラン連続制限逆変換パターン検出フラグ(9cbit)がクリアされる。ステップS52において、最小ラン連続制限逆変換パターン処理部42の最小ラン連続制限逆変換パターン検出部71は、入力されたチャネルビット列が符号パターン“000 010 000 000 101”、または符号パターン“101 010 000 000 101”かを判定する。入力されたチャネルビット列がこれらの符号パターンに一致する場合には、ステップS53において最小ラン連続制限逆変換パターン検出部71は、最小ラン連続制限逆変換パターン検出フラグ(15cbit)onを出力する。このフラグは、逆変換パターン決定部44と最小ラン連続制限逆変換テーブル72A, 72Bに出力される。

30

【0124】

ステップS54において最小ラン連続制限逆変換テーブル72Bは、15チャネルビットを10データに逆変換する。すなわち、表4に示されるように、符号パターン“101 010 000 000 101”が入力された場合、並びにチャネルビット列“000 010 000 000 101”が入力された場合、データパターン(1001110111)が出力される。

【0125】

ステップS53で出力されたフラグは図11のステップS231で利用され、ステップS54で変換されたデータパターンは図11のステップS232において選択、出力される。

40

【0126】

ステップS52において、入力されたチャネルビット列があらかじめ定められた符号パターン“000 010 000 000 101”, “101 010 000 000 101”と一致しないと判定された場合、ステップS55において最小ラン連続制限逆変換パターン検出部71は、チャネルビット列が符号パターン“001 000 000”と一致し、かつ、次の3符号語が“010”かを判定する。換言すれば、チャネルビット列が符号パターン“001 000 000 010”と一致するがを判定される。チャネルビット列がこのパターンと一致する場合には、ステップS56において、最小ラン連続制限逆変換パターン検出部71は最小ラン連続制限逆変換パターン検出フラグ(9cbit)onを出力する。このフラグは、逆変換パターン決定部44と最小ラン連続逆変換

50

テーブル72A, 72Bに出力される。

【0127】

ステップS57において最小ラン連続制限逆変換テーブル72Aは、9チャネルビットを6データに逆変換する。すなわち、符号語列“001 000 000”がデータパターン(110111)に変換される。

【0128】

ステップS56で出力されたフラグは図11のステップS233において利用され、ステップS57で変換されたデータは図11のステップS234に選択、出力される。

【0129】

ステップS55において、チャネルビット列が符号パターン“001 000 000”と一致しないか、または次の3符号語が符号パターン“010”と一致しないと判定された場合、すなわち、符号語列が符号パターン“001 000 000”と一致しないか、または一致したとしても次の符号が符号パターン“010”と一致しない場合には、ステップS58において最小ラン連続逆変換パターン検出部71は、最小ラン連続制限逆変換パターン検出フラグoffを出力する。この最小ラン連続制限逆変換パターン検出フラグoffは、ステップS53の最小ラン連続制限逆変換パターン検出フラグ(15cbit)のoffを意味するとともに、ステップS56の最小ラン連続制限逆変換パターン検出フラグ(9cbit)のoffを意味する。

【0130】

次に、図8のフローチャートを参照して、図5のステップS6の逆変換パターン処理の詳細について説明する。

20

【0131】

ステップS101において、逆変換パターン処理部41の逆変換パターン検出部81は、入力されたチャネルビット列が12-8復調かを判定する。具体的には、符号列が表4における拘束長*i* = 4の符号パターン“000 100 100 100”, “010 100 100 100”と一致するかが判定される(他の拘束長の場合も同様である)。12-8復調であると判定された場合、ステップS102において逆変換パターン検出部81は、12-8復調決定情報を出力する。この12-8復調決定情報は、逆変換パターン決定部44と逆変換テーブル82A乃至82Dに供給される。ステップS103において逆変換テーブル82Dは、12チャネルビットを8データに逆変換する。すなわち、チャネルビット列の符号パターン“000 100 100 100”がデータパターン(00001000)に変換されるか、あるいは符号パターン“010 100 100 100”がデータパターン(00000000)に変換される。

30

【0132】

ステップS102で出力された情報は図11のステップS235で利用され、ステップS103で変換されたデータは図11のステップS236で選択、出力される。

【0133】

ステップS101において、チャネルビット列が12-8復調ではないと判定された場合、ステップS104において、逆変換パターン検出部81は、チャネルビット列が9-6復調かを判定する。すなわち、チャネルビット列が表4における拘束長*i* = 3の符号パターン“000 100 100”, “000 100 000”, “010 100 100”, “010 100 000”と一致するかがここで判定される。チャネルビット列が9-6復調であると判定された場合、ステップS105において逆変換パターン検出部81は、9-6復調決定情報を出力する。この決定情報は、逆変換パターン決定部44と逆変換テーブル82A乃至82Dに供給される。ステップS106において逆変換テーブル82Cは、9チャネルビットを6データに逆変換する。具体的には、逆変換テーブル82Cは、符号パターン“000 100 100”, “000 100 000”(次のチャネルビットが“100”ではない場合), “010 100 100”, “010 100 000”(次のチャネルビットが“100”ではない場合)をそれぞれデータパターン(000011), (000010), (000001), (000000)に変換する。

40

【0134】

ステップS105で出力された情報は図11のステップS237で利用され、ステップS106で変換されたデータは図11のステップS238で選択、出力される。

50

## 【0135】

ステップS104において、チャネルビット列が9-6復調ではないと判定された場合、ステップS107において、逆変換パターン検出部81は、チャネルビット列が6-4復調かを判定する。すなわち、チャネルビット列が表4の拘束長  $i = 2$  の符号パターン“010 100”，“010 000”，“000 100”と一致するかが判定される。チャネルビット列が6-4復調であると判定された場合、ステップS108において逆変換パターン検出部81は、6-4復調決定情報を出力する。この決定情報は、逆変換パターン決定部44と逆変換テーブル82A乃至82Dに出力される。ステップS109において逆変換テーブル82Bは、6チャネルビットを4データに逆変換する。具体的には、表4における拘束長  $i = 2$  における逆変換が行われる。すなわち、符号パターン“010 100”，“010 000”（次のチャネルビットが“100”ではない場合），“000 100”は、データパターン（0011），（0010），（0001）にそれぞれ変換される。

## 【0136】

ステップS110において逆変換パターン検出部81は、6チャネルビットは符号パターン“010 100”または“000 100”かを判定する。6チャネルビットがこれらの符号パターンと一致する場合、逆変換パターン処理は終了される。これに対して、6チャネルビットがこれらの符号パターンと一致しない場合（符号パターン“010 000”である場合）には、処理はステップS111に進む。ステップS107において、チャネルビット列が6-4復調ではないと判定された場合にも、処理はステップS111に進む。

## 【0137】

ステップS111において、逆変換パターン検出部81はチャネルビット列が3-2復調かを判定する。すなわち、チャネルビット列が表4における拘束長  $i = 1$  の符号パターン“101”，“000”，“001”，“010”と一致するかが判定される。チャネルビット列が3-2復調である場合には、ステップS112において逆変換パターン検出部81は、3-2復調決定情報を出力する。この決定情報は、逆変換パターン決定部44と逆変換テーブル82A乃至82Dに出力される。この情報は、図11のステップS243において利用される。ステップS113において逆変換テーブル82Aは、3チャネルビットを2データに逆変換する。具体的には、表4の拘束長  $i = 1$  における場合に示されているように、符号パターン“101”，“000”，“001”，“010”は、データパターン（11），（11），（10），（01）にそれぞれ変換される。これらのデータは、図11のステップS244において選択、出力される。

## 【0138】

ステップS111において、チャネルビット列が3-2復調ではないと判定された場合、ステップS114において逆変換パターン検出部81はエラー処理を実行する。

## 【0139】

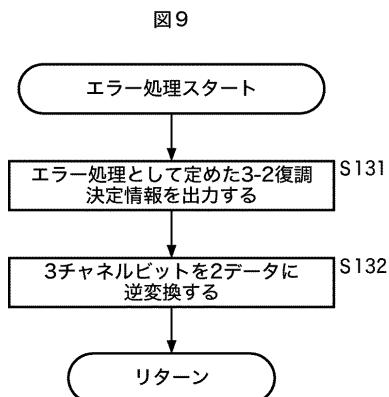

すなわち、表4に記述されていないパターンが出現した場合、最小処理単位である3-2逆変換処理が行われる。このエラー処理の詳細は図9のフローチャートに示されている。

## 【0140】

すなわち、図9に示されるように、ステップS131において逆変換パターン検出部81は、予めエラー処理として定めた3-2復調決定情報を出力する。この決定情報は、逆変換パターン決定部44と逆変換テーブル82A乃至82Dに出力される。ステップS132において、変換テーブル82Aは予めエラー処理用として定められている3チャネルビットを2データに逆変換する。すなわち、符号パターン“101”，“000”，“001”，“010”的うちのいずれか1つがエラー処理用の符号パターンとされ、それが対応するデータパターンに変換される。

## 【0141】

あるいは、エラー専用のデータパターンを用意し、例えば、エラー処理用として3チャネルビットを2データ（00）に逆変換するようにしてもよい。

## 【0142】

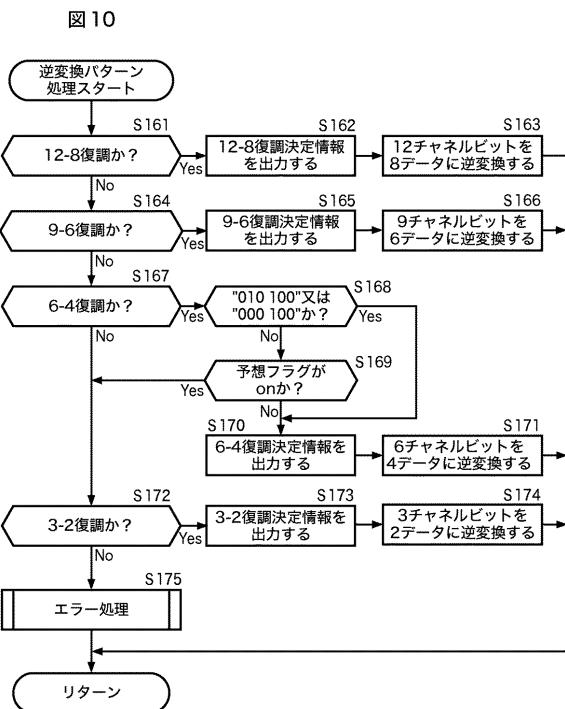

図10のフローチャートは、図5のステップS6の逆変換パターン処理の他の実施の形態を表している。但し、図10の逆変換パターン処理を実行する場合には、図4において点線で

10

20

30

40

50

示されるように、最小ラン連続制限逆変換パターン検出予想処理部61が出力する最小ラン連続制限逆変換パターン検出予想処理情報が逆変換パターン検出部81に供給される。

#### 【0143】

ステップS161乃至ステップS175の処理は、図8のステップS101乃至ステップS114の処理と基本的に同様の処理であるが、図10のステップS167における6-4復調かの判定処理でYesと判定された場合のステップS168乃至S171の処理が、図8のステップS107における6-4復調かの判定処理でYesと判定された場合のステップS108乃至S110の処理と異なっている。

#### 【0144】

すなわち、図10の処理においては、ステップS161乃至S166で、図8のステップS101乃至S106と同様の処理が行われている。そして、図8のステップS107に対応する図10のステップS167でチャネルビット列が6-4復調であると判定された場合、ステップS168において逆変換パターン検出部81は、チャネルビット列は“010 100”または“000 100”的符号パターンと一致するかを判定する。チャネルビット列がこれらの符号パターンと一致しない場合（符号パターン“010 000”と一致する場合）には、ステップS169において逆変換パターン検出部81は、最小ラン連続制限逆変換パターン検出予想フラグがonかを判定する。上述したようにこの実施の形態の場合、逆変換パターン検出部81に最小ラン連続制限逆変換パターン検出予想処理部61から最小ラン連続制限逆変換パターン検出部予想処理情報が供給されている。

#### 【0145】

ステップS169において、最小ラン連続制限逆変換パターン検出予想フラグがonではない（offである）と判定された場合（チャネルビットが、符号パターン“xxx 000 010 000 00 101”と一致しない場合）、ステップS170において逆変換パターン検出部81は、6-4復調決定情報を出力する。この決定情報は、逆変換パターン決定部44と逆変換テーブル82A乃至82Dに供給される。この情報は、図11のステップS239で利用される。次に、ステップS171において、逆変換テーブル82Bは、6チャネルビットを4データに逆変換する。具体的には、表4の拘束長  $i = 2$  における符号パターン“010 100”，“010 000”（次のチャネルビットが“100”ではない場合），“000 100”が、データパターン（0011），（0010），（0001）にそれぞれ変換される。この変換データは、図11のステップS242で選択、出力される。

#### 【0146】

ステップS168において、符号パターンが“010 100”、または“000 100”であると判定された場合には、ステップS169の処理はスキップされ、ステップS170，S171の処理が実行される。

#### 【0147】

ステップS171の処理が終了した場合、処理は図5のステップS7に戻る。

#### 【0148】

ステップS169において、最小ラン連続制限逆変換パターン検出予想フラグがonであると判定された場合、処理はステップS172に進み、チャネルビット列は3-2復調かが判定される。以下の処理は、図8のステップS111乃至S114の処理と同様の処理となる。

#### 【0149】

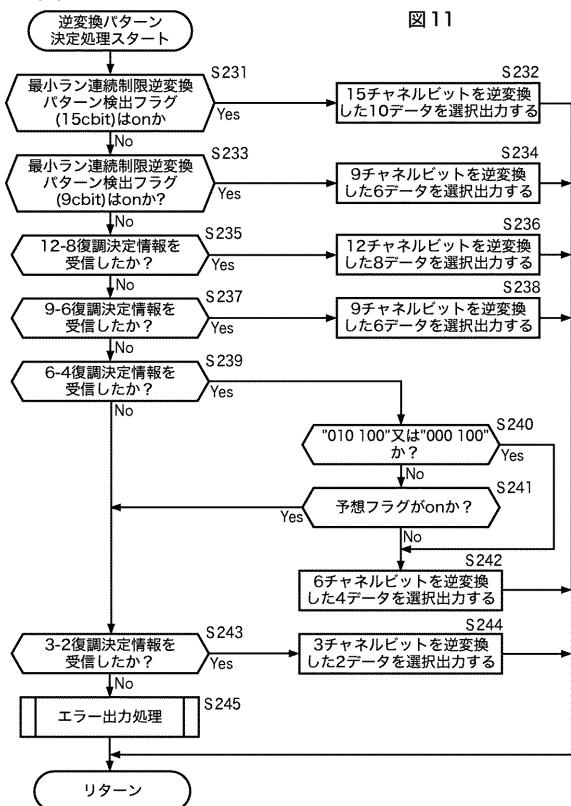

次に、図11のフローチャートを参照して、図5のステップS7における逆変換パターン決定処理の詳細について説明する。

#### 【0150】

ステップS231において、逆変換パターン決定部44は、最小ラン連続制限逆変換パターン検出フラグ（15cbit）はonかを判定する。このフラグは、図7のステップS53，S58で出力されたフラグである。このフラグがonである場合（チャネルビット列が符号パターン“00 0 010 000 000 101”または“101 010 000 000 101”と一致する場合）には、ステップS232において逆変換パターン決定部44は、15チャネルビットを逆変換した10データを選択、出力する。すなわち、図7のステップS54で逆変換されたデータがここで選択、出力されることになる。

10

20

30

40

50

## 【0151】

ステップS231において、最小ラン連続制限逆変換パターン検出フラグ(15cbit)はonではない(offである)と判定された場合、ステップS233において逆変換パターン決定部44は、最小ラン連続制限逆変換パターン検出フラグ(9cbit)はonかを判定する。このフラグは、図7のステップS56,S58で出力されたものである。このフラグがonである場合(チャネルビット列が符号パターン“001 000 000 010”と一致する場合)には、ステップS234において逆変換パターン決定部44は、9チャネルビットを逆変換した6データを選択、出力する。このデータは、図7のステップS57で逆変換されたものである。

## 【0152】

ステップS233において、最小ラン連続制限逆変換パターン検出フラグ(9cbit)がonではない(offである)と判定された場合、ステップS235において逆変換パターン決定部44は、12-8復調決定情報を受信したかを判定する。この情報は、図8のステップS102において出力されたものである。

10

## 【0153】

ステップS235において12-8復調決定情報を受信したと判定された場合(チャネルビット列が拘束長*i* = 4の符号パターンと一致する場合)、ステップS236において逆変換パターン決定部44は、12チャネルビットを逆変換した8データを選択、出力する。このデータは、図8のステップS103で逆変換されたものである。

## 【0154】

ステップS235において、12-8復調決定情報を受信していないと判定された場合、ステップS237において逆変換パターン決定部44は、9-6復調決定情報を受信したかを判定する。この情報は、図8のステップS105で出力されたものである、9-6復調決定情報を受信している場合(チャネルビット列が拘束長*i* = 3の符号パターンと一致する場合)には、ステップS238において逆変換パターン決定部44は、9チャネルビットを逆変換した6データを選択、出力する。このデータは、図8のステップS106で逆変換されたものである。

20

## 【0155】

ステップS237において、9-6復調決定情報を受信していないと判定された場合、ステップS239において逆変換パターン決定部44は、6-4復調決定情報を受信したかを判定する。この情報は、図8のステップS108で出力されたものである。6-4復調決定情報を受信している場合(チャネルビット列が拘束長*i* = 2の符号パターンと一致する場合)には、ステップS240において逆変換パターン決定部44は、チャネルビット列が“010 100”または“00 100”的符号パターンと一致するかを判定する。

30

## 【0156】

チャネルビット列がこれらの符号パターン“010 100”, “000 100”と一致しない場合(“010 000”と一致する場合)、ステップS241において逆変換パターン決定部44は、最小ラン連続制限逆変換パターン検出予想フラグがonかを判定する。この予想フラグは、最小ラン連続制限逆変換パターン検出予想処理部61より供給されるものである。予想フラグがonではない(offである)場合(チャネルビット列が符号パターン“xxx 000 010 000 00 101”と一致しない場合)、ステップS242において逆変換パターン決定部44は、6チャネルビットで逆変換した4データを選択、出力する。このデータは、図8のステップS109で出力されたものである。

40

## 【0157】

ステップS240において、チャネルビット列が“010 100”または“000 100”的符号パターンと一致すると判定された場合には、ステップS241の処理はスキップされ、ステップS242の処理が実行される。

## 【0158】

ステップS239において、6-4復調決定情報を受信していないと判定された場合、または、ステップS241で予想フラグがonであると判定された場合(チャネルビット列が符号パターン“xxx 000 010 000 000 101”と一致すると判定された場合であるが、ステップS240で符号パターン“010 000”と一致する(符号パターン“010 100”または“000 100”と

50

一致しない)とも判定されているので、結局、符号パターン“010 000 010 000 000 101”と一致する場合)ステップS243において逆変換パターン決定部44は、3-2復調決定情報を受信したかを判定する。この情報は、図8のステップS112で出力されたものである。3-2復調決定情報を受信している場合には、ステップS244において逆変換パターン決定部44は、3チャネルビットを逆変換した2データを選択、出力する。このデータは、図8のステップS113で逆変換されたものである。

#### 【0159】

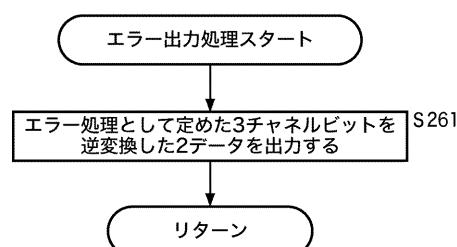

ステップS243において、3-2復調決定情報を受信していないと判定された場合、ステップS245において逆変換パターン決定部44はエラー出力処理を実行する。

#### 【0160】

ステップS245のエラー出力処理の詳細は、図12に示されている。すなわち、ステップS261において逆変換パターン決定部44は、エラー処理として定めた3チャネルビットを逆変換した2データを出力する。具体的には、符号パターン“101”, “000”, “001”, “010”的いずれかがエラー処理用として予め定められており、データパターン(11), (11), (10), (01)のうちそれに対応するデータパターンが出力されることになる。

#### 【0161】

このエラー出力処理においては、エラー専用にデータパターンが個別に与えられている場合には、そのデータパターン(例えば、データパターン(00))を出力するようにしてもよい。

#### 【0162】

最小ラン連続制限逆変換パターン検出予想処理部61、最小ラン連続制限逆変換パターン検出部71、最小ラン連続制限逆変換テーブル72A, 72B、逆変換パターン検出部81、逆変換テーブル82A乃至82D、並びに逆変換パターン決定部44の処理をまとめると、図13に示されるようになる。

#### 【0163】

すなわち、最小ラン連続制限逆変換パターン検出予想処理部61は、チャネルビット列が符号パターン“xxx 000 010 000 000 101”と一致するかを判定する。一致する場合には最小ラン連続制限逆変換パターン検出予想フラグonが出力され、一致しない場合には最小ラン連続制限逆変換パターン検出予想フラグoffが出力される。ここで“xxx”は、検出時にこれら3ビットを無視することを意味する。一致したかどうかが最小ラン連続制限逆変換パターン検出予想情報として出力される。

#### 【0164】

最小ラン連続制限逆変換パターン検出部71は、チャネルビット列が15-10復調であるか、すなわち符号パターン“000 010 000 000 101”または“101 010 000 000 101”と一致するかを判定する。一致する場合には、最小ラン連続制限逆変換パターン検出フラグ(15cbit)onが出力される。さらに、“000 010 000 000 101”または“101 010 000 000 101”から(1001110111)へのデータ変換が行われる。これに対して、一致しない場合には9-6復調かが判定される。すなわち、符号パターン“001 000 000 010”である場合、あるいは別の例として“001 000 000”であり次の符号語が“100”ではない場合には、最小ラン連続制限逆変換パターン検出フラグ(9cbit)onが出力される。さらに、“001 000 000”から(110111)へのデータ変換が行われる。これに対して、チャネルビット列が9-6復調でもないと判定された場合には、最小ラン連続制限逆変換パターン検出フラグoffが出力される。

#### 【0165】

一方、逆変換パターン検出部81においては、チャネルビット列が12-8復調かが判定され、そうである場合には逆変換パターン検出決定情報が出力され、逆変換テーブル82Dにより12チャネルビットが8データに逆変換される。

#### 【0166】

これに対して、チャネルビット列が12-8復調ではないと判定された場合、チャネルビット列が9-6復調かが判定される。9-6復調である場合には、9チャネルビットが6データに

10

20

30

40

50

逆変換テーブル82Cにより逆変換される。

【0167】

チャネルビット列が9-6復調ではないと判定された場合は、チャネルビット列が6-4復調であるかが判定される。そうである場合には、さらに符号パターン“010 000”であり、次のチャネルビットが“100”ではないかが判定され、そうである場合には、さらに最小ラン連続制限逆変換パターン検出予想フラグがonであるかoffであるかが判定される。予想フラグがonである場合には3チャネルビットが2データに逆変換テーブル82Aにより逆変換され、予想フラグがoffである場合には6チャネルビットが4データに逆変換テーブル82Bにより逆変換される。

【0168】

チャネルビット列が6-4復調であり符号パターンが“010 000”+not“100”と一致しない場合には、6チャネルビット（“010 000”）が4データに逆変換テーブル82Bにより逆変換される。最小ラン連続制限逆変換パターン検出予想処理部61からの情報は、6-4復調において用いられる。

【0169】

チャネルビット列が6-4復調ではない場合には、チャネルビット列が3-2復調であるかが判定され、3-2復調である場合には3チャネルビットを2データに逆変換テーブル82Aにより逆変換する処理が実行される。チャネルビット列が3-2復調ではないと判定された場合には、エラー処理により予め定められている3チャネルビットを2データに逆変換する処理が実行される。変換される2データは任意（例えば、（00））に予め決定しておく。

【0170】

そして、逆変換パターンの決定が行われると入力チャネルビット列は、それぞれ決定した分だけシフトレジスタ内において進められたタイミングで、次の検出処理が再度繰り返される。

【0171】

なお本発明は、例えば表2において最大ラン $k = 7$ を実現する置換パターンである、拘束長 $i = 4$ の変換パターンが省略されたテーブルによって発生された、最小ラン $d = 1$ 、最大ラン $k = 8$ のRLL符号列に対しても、表4の復調テーブルを適用することができる。この場合においては、表4の復調テーブルはさらに、表5のように変更することができる。

【0172】

<表5>

| 1,8PP-rmtr5_DEM  |                      | RLL(1,8;2,3;5)      |

|------------------|----------------------|---------------------|

| 符号パターン<br>(符号語列) |                      | データパターン<br>(復調データ列) |

| i = 1            | 101                  | 11                  |

|                  | 000                  | 11                  |

|                  | 001                  | 10                  |

|                  | 010                  | 01                  |

| i = 2            | 010 100              | 0011                |

|                  | 010 000(not 100)     | 0010                |

|                  | 000 100              | 0001                |

| i = 3            | 000 100 100          | 000011              |

|                  | 000 100 000(not 100) | 000010              |

|                  | 010 100 100          | 000001              |

|                  | 010 100 000(not 100) | 000000              |

Prohibit Repeated Minimum Transition Runlength

|       |                      |            |

|-------|----------------------|------------|

| i = 3 | 001 000 000(not 100) | 110111     |

| i = 5 | 101 010 000 000 101  | 1001110111 |

10

20

30

40

50

000 010 000 000 101 1001110111

【 0 1 7 3 】

このように、表 5 の逆変換テーブルは、基礎パターンの  $i = 1$  から  $i = 3$  までによって最小ラン  $d = 1$ 、最大ラン  $k = 8$  のRLL符号が実現され、さらに  $i = 3$  及び  $i = 5$  の最小ランの連續を制限する置換パターンによって最小ランの連續が最大でも 5 回までに制限されているようなチャネルビット列の、逆変換テーブルであり、表 5 においても本発明と同様な構成で復調装置を実現することができる。

【 0 1 7 4 】

以上のようにして、復調装置 1 に内蔵されている表 4 の逆変換テーブルは、1,7PP符号であり、さらに、基本構成が従来の逆変換テーブルである表 3 と同様でありながら、最小ランの連續を制限する逆変換パターンを複数通り持っているので、最小ランの連續する回数が、5 回までに制限され、エラー伝播特性を改善することができる。

【 0 1 7 5 】

表 4 の逆変換テーブルは、最小ラン  $d = 1$ 、最大ラン  $k = 7$ 、変換率( $m:n$ )=(2:3)の逆変換テーブルにおいて、最小ラン長の繰り返し回数を制限する置換パターンを設けるようにしたので、

( 1 ) 高線密度での記録再生、および、タンジェンシャル・チルトに対する許容度が向上する。

( 2 ) 信号レベルが小さい部分が減少し、AGC ( Auto Gain Control ) やPLL ( Phase-Locked Loop ) 等の波形処理の精度が向上し、総合特性を高めることができる。

( 3 ) 従来と比較して、ビタビ復号等の際のバスメモリ長を短く設計することができ、回路規模を小さくすることができる。

また、逆変換テーブルの符号語列内の「1」の個数と、復調データ列内の「1」の個数を、2で割った時の余りが、どちらも1あるいは0で一致するようにしたので、

( 4 ) DSVの制御のための冗長ビットを少なくすることができる。

( 5 ) 最小ラン  $d = 1$  かつ( $m,n$ )=(2,3)においては、1.5符号語でDSV制御を行うことができる。

( 6 ) 冗長度が少ない上に、最小ランと最大ランを守ることができる。さらに本テーブルは、表 3 の1,7PP符号と較べて、最小ランの連續回数制限を6回から5回へと少なくしたので、データ記録再生時のエラー伝播を、より少なくすることができる。

【 0 1 7 6 】

一般的に、データ再生誤りのパターンとしては、連續する最小マークの先頭のエッジから最後のエッジまでが、一齊にシフトして誤るという場合がある。即ち発生するビットエラー長は、最小ランの連續する区間の、先頭から最後まで伝搬することになる。従ってエラー伝搬は長くなってしまうという問題が現れる。しかしながら、最小ランの連續を5回に制限することによって、上記のエラーの発生を少なくすることができ、より安定したデータの記録再生を実現することができる。

【 0 1 7 7 】

表 4 の逆変換テーブルは、さらに表 3 の逆変換テーブルを含んでいるので、表 2 の1,7PP符号で作成されたチャネルビット列は、完全にデータ列への復調を行うことができる。

【 0 1 7 8 】

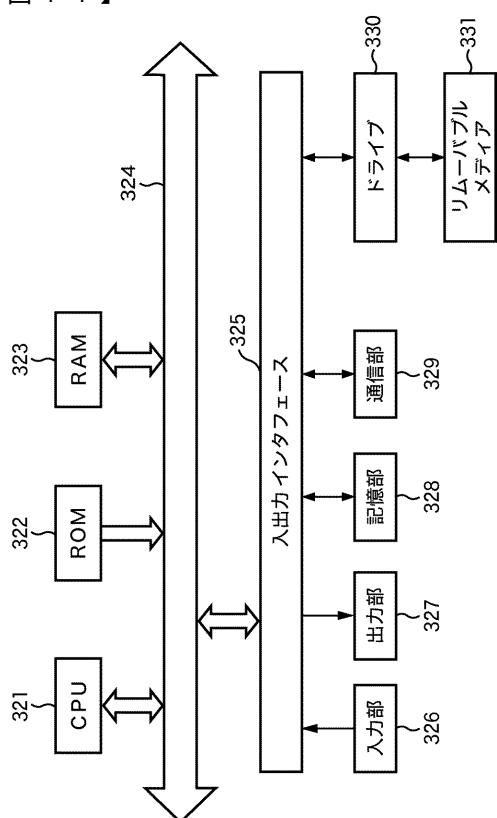

図14は、上述した一連の処理をプログラムにより実行するパーソナルコンピュータの構成の例を示すブロック図である。CPU ( Central Processing Unit ) 321は、ROM ( Read Only Memory ) 322、または記憶部328に記憶されているプログラムに従って各種の処理を実行する。RAM ( Random Access Memory ) 323には、CPU321が実行するプログラムやデータなどが適宜記憶される。これらのCPU321、ROM322、およびRAM323は、バス324により相互に接続されている。

【 0 1 7 9 】

CPU321にはまた、バス324を介して入出力インターフェース325が接続されている。入出力インターフェース325には、キーボード、マウス、マイクロホンなどよりなる入力部326

10

20

30

40

50

、ディスプレイ、スピーカなどによる出力部327が接続されている。CPU321は、入力部326から入力される指令に対応して各種の処理を実行する。そして、CPU321は、処理の結果を出力部327に出力する。

【0180】

出入力インターフェース325に接続されている記憶部328は、例えばハードディスクからなり、CPU321が実行するプログラムや各種のデータを記憶する。通信部329は、インターネットやローカルエリアネットワークなどのネットワークを介して外部の装置と通信する。また、通信部329を介してプログラムを取得し、記憶部328に記憶してもよい。

【0181】

出入力インターフェース325に接続されているドライブ330は、磁気ディスク、光ディスク、光磁気ディスク、或いは半導体メモリなどのリムーバブルメディア331が装着されたとき、それらを駆動し、そこに記録されているプログラムやデータなどを取得する。取得されたプログラムやデータは、必要に応じて記憶部328に転送され、記憶される。

【0182】

上述した一連の処理は、ハードウェアにより実行させることもできるし、ソフトウェアにより実行させることもできる。一連の処理をソフトウェアにより実行させる場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータ、または、各種のプログラムをインストールすることで、各種の機能を実行することが可能な、例えば汎用のパーソナルコンピュータなどに、プログラム格納媒体からインストールされる。

10

【0183】

コンピュータにインストールされ、コンピュータによって実行可能な状態とされるプログラムを格納するプログラム格納媒体は、図14に示すように、磁気ディスク（フレキシブルディスクを含む）、光ディスク（CD-ROM(Compact Disc-Read Only Memory),DVD(Digital Versatile Disc)を含む）、光磁気ディスク（MD（Mini-Disc）（登録商標）を含む）、もしくは半導体メモリなどによるパッケージメディアであるリムーバブルメディア331、または、プログラムが一時的もしくは永続的に格納されるROM322や、記憶部328を構成するハードディスクなどにより構成される。プログラム格納媒体へのプログラムの格納は、必要に応じてルータ、モデムなどのインターフェースである通信部329を介して、ローカルエリアネットワーク、インターネット、デジタル衛星放送といった、有線または無線の通信媒体を利用して行われる。

20

【0184】

なお、本明細書において、プログラム格納媒体に格納されるプログラムを記述するステップは、記載された順序に沿って時系列的に行われる処理はもちろん、必ずしも時系列的に処理されなくとも、並列的あるいは個別に実行される処理をも含むものである。

30

【0185】

なお、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

【図面の簡単な説明】

【0186】

40

【図1】本発明の一実施の形態の復調装置の構成を示すブロック図である。

【図2】データフォーマットを説明する図である。

【図3】図1の復号装置のより詳細な構成を示すブロック図である。

【図4】図3の復号装置のさらにより詳細な構成を示すブロック図である。

【図5】図1の復調装置の再生処理を説明するフローチャートである。

【図6】図5のステップS4のパターン検出予想処理を説明するフローチャートである。

【図7】図5のステップS5の最小ラン連続制限逆変換パターン処理を説明するフローチャートである。

【図8】図5のステップS6の逆変換パターン処理を説明するフローチャートである。

【図9】図8のステップS114のエラー処理を説明するフローチャートである。

50

【図10】図5のステップS6の逆変換パターン処理の他の実施の形態を説明するフローチャートである。

【図11】図5のステップS7の逆変換パターン決定処理を説明するフローチャートである。

【図12】図11のステップS245のエラー出力処理を説明するフローチャートである。

【図13】最小ラン連続制限逆変換パターン検出予想部、最小ラン連続制限逆変換パターン検出部、および逆変換パターン検出部の処理を説明する図である。

【図14】パーソナルコンピュータの構成を示すブロック図である。

【符号の説明】

【0187】

10

1 復調装置， 13 復号装置， 21 チャネルビット列化部， 22 同期パターン検出処理部， 23 復調部， 24 データビット取出部， 41 逆変換パターン処理部， 42 最小ラン連続制限逆変換パターン処理部， 43 パターン検出予想処理部， 44 逆変換パターン決定部， 61 最小ラン連続制限逆変換パターン検出予想処理部， 71 最小ラン連続制限逆変換パターン検出部， 81 逆変換パターン検出部， 72A, 72B 最小ラン連続制限逆変換テーブル， 82A乃至82D 逆変換テーブル

【図1】

【図2】

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

【図9】

図9

【図10】

リターン

【図11】

【 図 1 2 】

【図 1.3】

13

【図 1-4】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

G 11 B 20 / 14

H 03 M 7 / 14