(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7595246号**

**(P7595246)**

(45)発行日 令和6年12月6日(2024.12.6)

(24)登録日 令和6年11月28日(2024.11.28)

(51)国際特許分類

|        |                  |     |        |        |         |

|--------|------------------|-----|--------|--------|---------|

| H 01 L | 21/363 (2006.01) | F I | H 01 L | 21/363 |         |

| C 23 C | 14/08 (2006.01)  |     | C 23 C | 14/08  | K       |

| C 23 C | 14/34 (2006.01)  |     | C 23 C | 14/34  | N       |

| H 01 L | 21/336 (2006.01) |     | H 01 L | 29/78  | 6 1 8 A |

| H 01 L | 29/786 (2006.01) |     | H 01 L | 29/78  | 6 1 8 B |

請求項の数 10 (全13頁) 最終頁に続く

(21)出願番号 特願2020-210353(P2020-210353)

(22)出願日 令和2年12月18日(2020.12.18)

(65)公開番号 特開2022-97013(P2022-97013A)

(43)公開日 令和4年6月30日(2022.6.30)

審査請求日 令和5年11月28日(2023.11.28)

(73)特許権者 000003942

日新電機株式会社

京都府京都市右京区梅津高畠町47番地

(74)代理人 100121441

弁理士 西村 竜平

(74)代理人 100154704

弁理士 齊藤 真大

(74)代理人 100129702

弁理士 上村 喜永

(74)代理人 100206151

弁理士 中村 慎志

(74)代理人 100218187

弁理士 前田 治子

(72)発明者 松尾 大輔

京都府京都市右京区梅津高畠町47番地

最終頁に続く

(54)【発明の名称】 酸化物半導体の成膜方法及び薄膜トランジスタの製造方法

**(57)【特許請求の範囲】****【請求項1】**

プラズマを用いてターゲットをスパッタリングすることにより酸化物半導体膜を基板上に成膜する方法であって、

前記基板と前記ターゲットとの間の距離を変更することにより前記酸化物半導体膜の結晶性を制御して、非晶質の前記酸化物半導体膜と、結晶質の前記酸化物半導体膜を作り分ける、成膜方法。

**【請求項2】**

前記基板と前記ターゲットとの間を所定の第1距離にしてスパッタリングを行うことと、非晶質の前記酸化物半導体膜を成膜する第1成膜工程と、

前記基板と前記ターゲットとの間を前記第1距離よりも短い第2距離にしてスパッタリングを行うことで、結晶質の前記酸化物半導体膜を成膜する第2成膜工程と、を含む請求項1に記載の成膜方法。

**【請求項3】**

アルゴンガスと酸素ガスとの混合ガスをスパッタリングガスとして用いてスパッタリングを行う請求項1又は2に記載の成膜方法。

**【請求項4】**

前記第1成膜工程と前記第2成膜工程において、前記スパッタリングガス中の酸素分圧が同一である請求項2を引用する請求項3に記載の成膜方法。

**【請求項5】**

前記スパッタリングガス中の前記酸素ガスの分圧が2.5%以上である請求項4に記載の成膜方法。

【請求項6】

前記プラズマを維持したまま前記基板と前記ターゲットとの間の距離を変更することと、前記酸化物半導体膜の結晶性を制御する請求項1～5のいずれか一項に記載の成膜方法。

【請求項7】

前記酸化物半導体膜がIn-Ga-Zn-Oにより構成されている請求項1～6のいずれか一項に記載の成膜方法。

【請求項8】

前記ターゲットに印加するターゲットバイアス電圧を-1.0kV以上の負電圧にしてスパッタリングを行う、請求項1～7のいずれか一項に記載の成膜方法。

10

【請求項9】

前記ターゲットに印加するターゲットバイアス電圧と、プラズマを発生させるアンテナに供給する高周波電力とを独立に制御可能なスパッタリング装置を用いてスパッタリングを行う請求項1～8のいずれか一項に記載の成膜方法。

【請求項10】

ゲート電極と、ゲート絶縁層と、酸化物半導体層と、ソース電極及びドレイン電極とが基板上に積層された薄膜トランジスタの製造方法であって、

請求項1～9のいずれか一項に記載の成膜方法により前記酸化物半導体層を形成する薄膜トランジスタの製造方法。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、プラズマを用いてターゲットをスパッタリングして酸化物半導体膜を成膜する成膜方法、及び当該成膜方法を用いた薄膜トランジスタの製造方法に関するものである。

【背景技術】

【0002】

近年、In-Ga-Zn-O系(IGZO)等の酸化物半導体をチャネル層に用いた薄膜トランジスタの開発が活発に行われている。このような半導体層を有する薄膜トランジスタの製造工程においては、半導体層中に酸素欠損等の欠陥が多く存在すると、その電気伝導度が変化し、薄膜トランジスタの電気的特性を劣化する恐れがある。そのため半導体層中の酸素欠損等の欠陥を低減するべく、従来種々の試みが行われている。

30

【0003】

例えば特許文献1には、酸化物半導体層を、非晶質の酸化物半導体膜からなる第1半導体層と、結晶質の酸化物半導体膜からなる第2半導体層とを積層する多層構造としたものが記載されている。特許文献1には、非晶質である第1半導体層の上に結晶質である第2半導体層を積層することで、この上に成膜される絶縁層との界面における酸素欠陥を低減でき、薄膜トランジスタのゲート閾値電圧を大きくできることが記載されている。

【先行技術文献】

【特許文献】

40

【0004】

【文献】国際公開WO2019/181095号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで上記特許文献1には、スパッタリングガス中の酸素ガスの分圧を変更することにより、酸化物半導体膜の結晶性を制御することが記載されている。具体的には、酸素ガスの分圧を低くすることにより非晶質の酸化物半導体膜を成膜し、酸素ガスの分圧を高くすることにより結晶質の酸化物半導体膜を成膜することが記載されている。しかしながら、このような酸素ガスの分圧を変更することにより酸化物半導体膜の結晶性を制御する方

50

法では、高い酸素ガス分圧で成膜した結晶質の酸化物半導体膜に比べて、低い酸素ガス分圧で成膜した非晶質の酸化物半導体膜の膜密度が大きく低下してしまうという問題がある。

#### 【 0 0 0 6 】

本発明はこのような問題に鑑みてなされたものであり、膜密度を大きく変化させることなく結晶性が異なる酸化物半導体膜を作り分けられる成膜方法を提供することを主たる課題とするものである。

#### 【課題を解決するための手段】

#### 【 0 0 0 7 】

上記課題を解決すべく本願発明者が鋭意検討を重ねた結果、プラズマを用いてターゲットをスパッタリングして酸化物半導体膜を成膜する成膜方法において、ターゲットと基板の間の距離と、酸化物半導体膜の結晶性との間に相関性があることを見出した。本願発明者は、さらに鋭意検討した結果、ターゲットと基板との間の距離を短くしてスパッタリングを行うことで、結晶質の酸化物半導体膜を成膜でき、ターゲットと基板との間の距離を長くしてスパッタリングを行うことで、非晶質の酸化物半導体膜を成膜できることを見出した。

10

#### 【 0 0 0 8 】

すなわち本発明に係る成膜方法は、プラズマを用いてターゲットをスパッタリングすることにより酸化物半導体膜を基板上に成膜する方法であって、前記基板と前記ターゲットとの間の距離を変更することにより前記酸化物半導体膜の結晶性を制御することを特徴とする。

20

#### 【 0 0 0 9 】

このような成膜方法であれば、基板とターゲットとの間の距離を変更することにより酸化物半導体膜の結晶性を制御できるので、結晶性の異なる複数の酸化物半導体膜を成膜する際に、スパッタリング中の酸素ガスの分圧を変更する必要がない。これにより、膜密度を大きく変化させることなく結晶性が異なる酸化物半導体膜を作り分けることができる。

なお“酸化物半導体膜を基板上に成膜する”とは、酸化物半導体膜を基板の表面に直接成膜するだけでなく、酸化物半導体膜と基板との間に他の成分からなる膜が介在しているものを含む意味である。

#### 【 0 0 1 0 】

前記成膜方法は、前記基板と前記ターゲットとの間を所定の第1距離にしてスパッタリングを行うことで、非晶質の前記酸化物半導体膜を成膜する第1成膜工程と、前記基板と前記ターゲットとの間を前記第1距離よりも短い第2距離にしてスパッタリングを行うことで、結晶質の酸化物半導体膜を成膜する第2成膜工程と、を含むことが好ましい。

30

このようにすれば、基板とターゲットとの間の距離を変更してスパッタリングを行うことにより、非晶質の酸化物半導体膜と結晶質の酸化物半導体膜とを作り分けることができる。

#### 【 0 0 1 1 】

前記成膜方法は、アルゴンガスと酸素ガスとの混合ガスをスパッタリングガスとして用いてスパッタリングを行うことが好ましい。

このようにすれば、スパッタリングガス中に酸素ガスを含むことで、酸化物半導体膜中の酸素欠損をより低減し、膜密度を向上することができる。

40

#### 【 0 0 1 2 】

前記成膜方法は、前記第1成膜工程と前記第2成膜工程において、前記スパッタリングガス中の酸素分圧が同一であることが好ましい。

このようにすれば、第1成膜工程と第2成膜工程とでスパッタリングガス中の酸素分圧を変更する必要がないので、プラズマを安定的に維持した状態で第1成膜工程と第2成膜工程との間を移行することができる。これによりタクトタイムを短くでき、製造コストを低減できる。また各成膜工程で酸素分圧が同一であるので、膜密度が大きく変化することがない。

#### 【 0 0 1 3 】

50

前記成膜方法は、前記スパッタリングガス中の前記酸素ガスの分圧が2.5%以上であることが好ましい。

このようにすれば、酸化物半導体層中の酸素欠損をより低減するとともに、第2成膜工程において形成する酸化物半導体膜の結晶性をより高めることができる。

#### 【0014】

前記成膜方法の具体的な態様として、前記プラズマを維持したまま前記基板と前記ターゲットとの間の距離を変更することで、前記酸化物半導体膜の結晶性を制御するものが挙げられる。

#### 【0015】

前記酸化物半導体膜の具体的な態様としては、例えばIn-Ga-Zn-O(IGZO)等が挙げられる。

#### 【0016】

前記第1成膜工程及び第2成膜工程では、前記ターゲットに印加するターゲットバイアス電圧を-1.0kV以上の負電圧にしてスパッタリングを行うことが好ましい。

このようにすれば、ターゲットバイアス電圧の絶対値が1.0kV以下と小さいので、酸素が脱離したスパッタ粒子の生成を抑制できる。その結果、基板には、ターゲット材料と同じ酸化物状態を維持した膜が形成され、より膜密度が高い高品質の酸化物半導体層を形成することができる。

#### 【0017】

前記成膜方法は、前記ターゲットに印加するターゲットバイアス電圧と、前記アンテナに供給する高周波電力とを独立に制御可能なスパッタリング装置を用いてスパッタリングを行うことが好ましい。

このようなスパッタリング装置を用いれば、プラズマの生成とは独立してターゲットに印加するバイアス電圧の値を設定できるので、バイアス電圧をプラズマ中のイオンをターゲットに引き込んでスパッタさせる程度の低電圧に設定することができる。そのため、スパッタリング時にターゲットに印加する負のバイアス電圧を-1kV以上の小さな値に設定することが可能になる。

#### 【0018】

また、本発明の薄膜トランジスタの製造方法は、ゲート電極と、ゲート絶縁層と、酸化物半導体層と、ソース電極及びドレイン電極とが基板上に積層された薄膜トランジスタの製造方法であって、前記した成膜方法により前記酸化物半導体層を形成することを特徴とする。

このような製造法であれば、上記した本発明の成膜方法と同様の作用効果を奏し得る。

#### 【発明の効果】

#### 【0019】

このように構成した本発明によれば、膜密度を大きく変化させることなく結晶性が異なる酸化物半導体膜を作り分けられる成膜方法を提供することができる。

#### 【図面の簡単な説明】

#### 【0020】

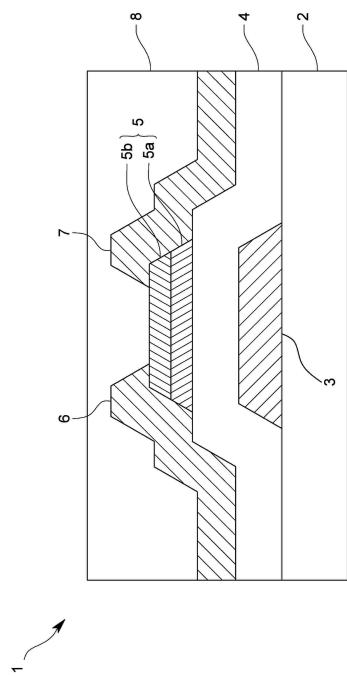

【図1】本実施形態の薄膜トランジスタの構成を模式的に示す図。

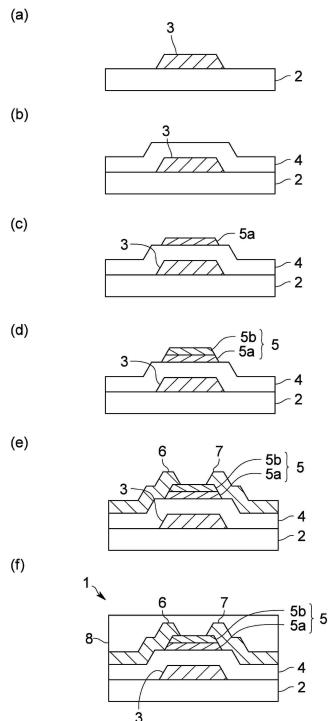

【図2】同実施形態の薄膜トランジスタの製造工程を模式的に示す図。

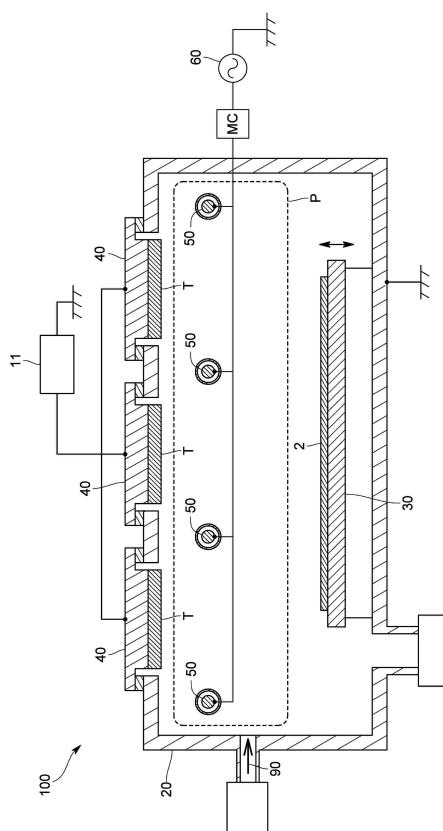

【図3】同実施形態の薄膜トランジスタの半導体層形成工程で用いられるスパッタリング装置の構成を模式的に示す図。

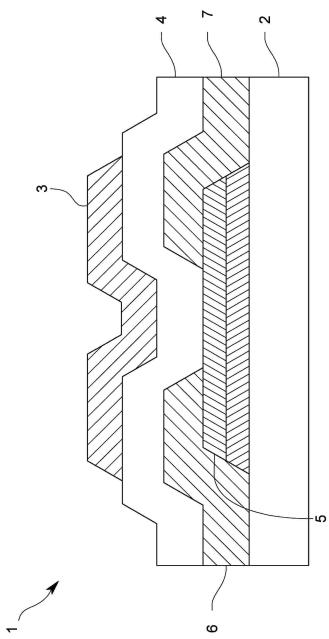

【図4】別の実施形態の薄膜トランジスタの構成を模式的に示す図。

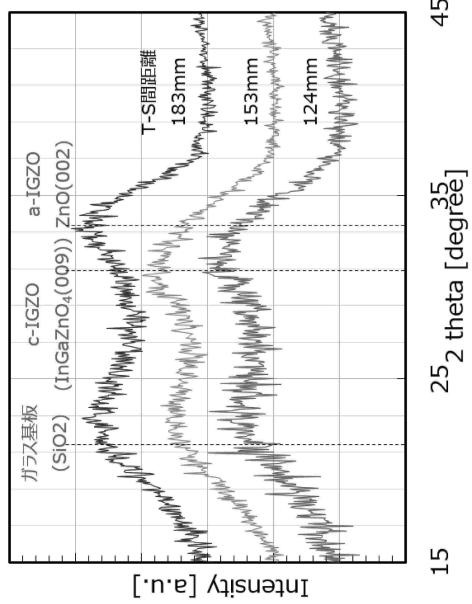

【図5】実験例における、成膜距離と酸化物半導体膜の結晶性との関係を示すグラフ。

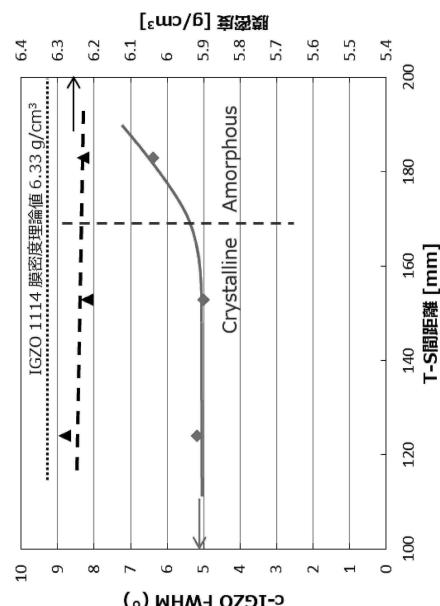

【図6】実験例における、成膜距離と、酸化物半導体膜の結晶性及び膜密度との関係を示すグラフ。

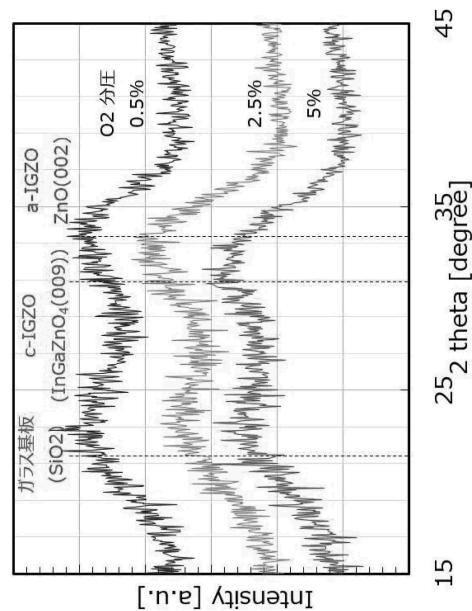

【図7】比較例における、酸素ガスの分圧と酸化物半導体膜の結晶性との関係を示すグラフ。

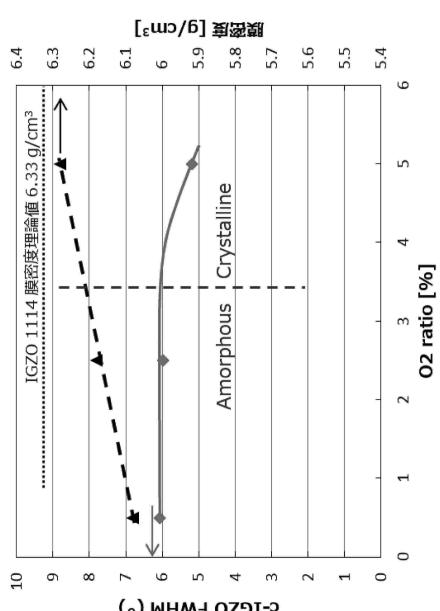

【図8】比較例における、酸素ガスの分圧と、酸化物半導体膜の結晶性及び膜密度との関

10

20

30

40

50

係を示すグラフ。

**【発明を実施するための形態】**

**【0021】**

以下に、本発明の一実施形態に係る薄膜トランジスタおよびその製造方法について説明する。

**【0022】**

<1. 薄膜トランジスタ>

本実施形態の薄膜トランジスタ1は所謂ボトムゲート型のものである。具体的には図1に示すように、基板2と、ゲート電極3と、ゲート絶縁層4と、チャネル層である酸化物半導体層5と、ソース電極6及びドレイン電極7と、保護層8を有しており、基板2側からこの順に配置(形成)されている。以下、各部について詳述する。

10

**【0023】**

基板2は光を透過できるような材料から構成されており、例えば、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)、アクリル、ポリイミド等の樹脂材料やガラス等によって構成されてよい。

**【0024】**

基板2の表面にはゲート電極3が設けられている。ゲート電極3は高い導電性を有する材料から構成されており、例えばSi、Al、Mo、Cr、Ta、Ti、Pt、Au、Ag等から選択される1種以上の金属から構成されてよい。また、Al-Nd、Ag合金、酸化錫、酸化亜鉛、酸化インジウム、酸化インジウム錫(ITO)、酸化亜鉛インジウム(IZO)、In-Ga-Zn-O(IGZO)等の金属酸化物の導電性膜から構成されてよい。ゲート電極3は、これらの導電性膜の単層構造又は2層以上の積層構造から構成されてもよい。

20

**【0025】**

ゲート電極3の上にはゲート絶縁層4が配置されている。ゲート絶縁層4は高い絶縁性を有する材料から構成されており、例えば、 $\text{SiO}_2$ 、 $\text{SiN}_x$ 、 $\text{SiON}$ 、 $\text{Al}_2\text{O}_3$ 、 $\text{Y}_2\text{O}_3$ 、 $\text{Ta}_2\text{O}_5$ 、 $\text{Hf}_2$ 等から選択される1つ以上の酸化物を含む絶縁膜であってよい。ゲート絶縁層4は、これらの導電性膜を単層構造又は2層以上の積層構造としたものであってよい。

30

**【0026】**

ゲート絶縁層4の上には酸化物半導体層5が配置されている。本実施形態の酸化物半導体層5は、第1半導体層5aと第2半導体層5bが基板2側から順に配置された多層構造を成している。第1半導体層5aと第2半導体層5bはいずれも、Inを含む酸化物を主成分とする酸化物半導体層からなり、例えば、In-Ga-Zn-O、In-Al-Mg-O、In-Al-Zn-O又はIn-Hf-Zn-O等から成ることが好ましい。第1半導体層5aは非晶質(アモルファス)の酸化物半導体膜からなる層であり、第2半導体層5bは結晶質の酸化物半導体膜からなる層である。

**【0027】**

第1半導体層5aが非晶質の酸化物半導体膜であることは、第1半導体層5aがIn-Ga-Zn-O(IGZO)からなる酸化物半導体膜である場合、Cu光源(Cu-K線)を用いた2法によるXRD(X線回折)による測定において、 $2 = 31^\circ$ 近傍に急峻なピークが現れることにより確認できる。

40

**【0028】**

第2半導体層5bの結晶性が高いほど、界面における酸素欠陥を低減でき、薄膜トランジスタ1のゲート閾値電圧 $V_{th}$ (ドレイン電流 $I_d = 1\text{nA}$ におけるゲート電圧 $V_g$ )を大きくすることができる。そのため第2半導体層5bの結晶性は高い方が好ましい。第2半導体層5bの結晶性の高さは、第2半導体層5bがIn-Ga-Zn-O(IGZO)からなる酸化物半導体膜である場合、前記したXRD(X線回折)による測定において $2 = 31^\circ$ 近傍で確認できるピークの半値全幅の大きさにより評価することができる。具体的には、当該ピークの半値全幅が小さいほど、第2半導体層5bの結晶性が高いと評価

50

できる。

#### 【0029】

酸化物半導体層5の上には、ソース電極6およびドレイン電極7が配置されている。ソース電極6及びドレイン電極7は、半導体層5の表面を部分的に覆うように、互いに離間して形成されている。ソース電極6及びドレイン電極7はそれぞれ、電極として機能するように高い導電性を有する材料から構成されている。例えばゲート電極2と同様の材料により構成されてもよく、異なる材料により構成されてもよい。ソース電極6及びドレイン電極7は、金属や導電性酸化物の単層構造から構成されてもよく、2層以上の積層構造から構成されてもよい。

#### 【0030】

酸化物半導体5、ソース電極6およびドレイン電極7の上には、これらを保護するための保護層(パッシベーション層)8が配置されている。保護層8は、絶縁性の材料により構成されており、例えばフッ素含有シリコン窒化膜(SiN:F)、フッ素含有シリコン酸化膜(SiO:F)、シリコン窒化膜(SiNx)、シリコン酸化膜(SiOx)等により構成されてよい。

10

#### 【0031】

##### <2. 薄膜トランジスタの製造方法>

次に、上述した構造の薄膜トランジスタ1の製造方法を、図2を参照して説明する。

本実施形態の薄膜トランジスタ1の製造方法は、ゲート電極形成工程、ゲート絶縁層形成工程、半導体層形成工程、ソース・ドレイン電極形成工程、保護層形成工程を含む。以下、各工程について説明する。

20

#### 【0032】

##### (1) ゲート電極形成工程

まず図2(a)に示すように、例えばPET等の樹脂材料からなる基板2を準備し、基板2の表面にゲート電極3を形成する。ゲート電極3の形成方法は特に制限されず、例えば真空蒸着法、DCスパッタリング法等の既知の方法により形成してよい。

#### 【0033】

##### (2) ゲート絶縁層形成工程

次に、図2(b)に示すように、基板2及びゲート電極3の表面を覆うようにゲート絶縁層4を形成する。ゲート絶縁層4の形成方法は特に限定されず、既知の方法により形成してよい。

30

#### 【0034】

##### (3) 半導体層形成工程

次に、図2(c)に示すように、ゲート絶縁層4上にチャネル層である酸化物半導体層5を成膜する。この半導体層形成工程は、第1半導体層5aを形成する第1成膜工程と、第2半導体層5bを形成する第2成膜工程とを含む。

#### 【0035】

##### (3-1) スパッタリング装置

この半導体層形成工程では、図3に示すような、誘導結合型のプラズマPを用いてターゲットTをスパッタリングするスパッタリング装置100が用いられる。スパッタリング装置100は、真空容器20と、真空容器20内において基板2を保持する基板保持部30と、真空容器20内において基板2と対向してターゲットTを保持するターゲット保持部40と、基板保持部30に保持された基板2の表面に沿って配列され、プラズマPを発生させる複数のアンテナ50と、真空容器20内に誘導結合型のプラズマPを生成するための高周波を複数のアンテナ50に印加する高周波電源60(周波数13.56MHz)と、ターゲットTにターゲットバイアス電圧を印加するターゲットバイアス電源11とを備える。このようなスパッタリング装置100を使用することにより、プラズマPを発生させるためにアンテナ50に供給する高周波電圧と、ターゲットTに印加するターゲットバイアス電圧とを独立して制御することができる。そのため、プラズマPの生成とは独立して、バイアス電圧をプラズマP中のイオンをターゲットTに引き込んでスパッタさせる

40

50

程度の低電圧に設定することができ、スパッタリング時にターゲット T に印加する負のバイアス電圧を -1 kV 以上（すなわち絶対値が 1 kV 以下）の負電圧に設定することが可能になる。さらには、プラズマ P の生成とは独立して、ターゲット T に印加するバイアス電圧の値をスパッタリング中に任意に変更することができる。スパッタリング装置 100 のターゲット保持部 40 にターゲット T（例えば I G Z O）を配置し、基板保持部 30 に基板 2 を配置してスパッタリングが行われる。なおこのスパッタリング装置 100 は、基板保持部 30 又はターゲット保持部 40 の上下方向に沿った高さ位置が可変であり、これによりターゲット T と基板との間の距離をプラズマ処理中に変更することができる。

#### 【0036】

##### (3-2) 第1成膜工程

上記したスパッタリング装置 100 を用いて、まずゲート絶縁層 4 上に非晶質の第1半導体層 5a を形成する。具体的には、スパッタリング装置 100 の真空容器 20 を例えれば  $3 \times 10^{-6}$  Torr 以下に真空排気した後、スパッタリングガスを 50 sccm 以上 200 sccm 以下の流量で導入しつつ、真空容器内 20 の圧力を例えば 0.5 Pa 以上 3.1 Pa 以下となるように調整する。そして高周波電源 60 から複数のアンテナ 50 に高周波電力を供給し、誘導結合型のプラズマ P を生成及び維持する。ターゲットバイアス電源 11 からターゲット T に直流電圧パルスを印加して、ターゲット T のスパッタリングを行う。第1半導体層 5a 中の酸素欠損を少なくする観点から、ターゲット T に印加する電圧を -1 kV 以上の負電圧とすることが好ましく、-600 V 以上の負電圧にすることがより好ましい。これにより、図 2 (c) に示すように、ゲート絶縁層 4 上に第1半導体層 5a を形成する。なお、真空容器 20 内の圧力、スパッタリングガスの流量、高周波電力密度等は適宜変更されてもよい。

#### 【0037】

##### (3-3) 第2成膜工程

第1成膜工程の後、スパッタリング装置 100 を用いてスパッタリングを行うことで、第1半導体層 5a 上に結晶質の第2半導体層 5b を形成する。第2成膜工程における真空容器内の圧力、スパッタリングガスの流量、高周波電力密度、ターゲット T に印加する負電圧値は等の条件は第1成膜工程と同様であってもよく、適宜変更されてもよい。

#### 【0038】

##### (3-4) 基板 - ターゲット間の距離

ここで、本実施形態の半導体層形成工程では、スパッタリング装置 100 内における基板とターゲット T との間の距離（以下、成膜距離）を変更することにより酸化物半導体膜の結晶性を制御し、非晶質である第1半導体層 5a と、結晶質である第2半導体層 5b とを作り分けるようにしている。具体的にこの半導体層形成工程では、第1成膜工程と第2成膜工程とで成膜距離を異ならせており、第2成膜工程における成膜距離（第2成膜距離という）が、第1成膜工程における成膜距離（第1成膜距離という）よりも短くなるようにしている。より詳細に説明すると、第1成膜工程において、真空容器 20 内にプラズマ P を発生させ、第1成膜距離でスパッタリングを行うことでゲート絶縁層上に所定の膜厚の第1半導体層 5a を成膜する。そして、その後真空容器 20 内に生じたプラズマ P を維持したまま、基板とターゲット T との間の距離を狭め、第2成膜距離でスパッタリングを行うことで第1半導体層 5a 上に第2半導体層 5b を成膜する。なおこの成膜距離とは、スパッタリング装置 100 の基板保持部 30 における基板 2 の載置面と、これに対向するターゲット T の表面との間の距離を意味する。

#### 【0039】

##### (3-5) スパッタリングガス中の酸素分圧

第1成膜工程及び第2成膜工程において、供給するスパッタリングガスは、アルゴンガス単体でもよく、アルゴンガスと酸素ガスの混合ガスであってもよい。半導体層 5 中の酸素欠損を低減して膜密度を向上する観点から、供給するスパッタリングガスはアルゴンガスと酸素ガスの混合ガスであることが好ましい。この場合、第2成膜工程においてより結晶性の高い第2半導体層 5b を成膜する観点から、混合ガスにおける酸素ガスの分圧が 2

10

20

30

40

50

. 5 %以上であることが好ましく、5 %以上であることがより好ましい。また第1成膜工程と第2成膜工程とで、混合ガス中の酸素ガスの分圧を変更してもよいし、同一であってもよい。

#### 【0040】

##### (4) ソース・ドレイン電極形成工程

次に、図2(e)に示すように、酸化物半導体層5の上にソース電極6およびドレイン電極7を形成する。ソース電極6およびドレイン電極7の形成は、例えば、RFマグネットロンスパッタリング等を用いた既知の方法により形成することができる。ソース電極6及びドレイン電極7は、半導体層5の表面上で互いに離間し、半導体層5の表面の一部を露出させるように形成される。

10

#### 【0041】

##### (5) 保護層形成工程

その後、図2(f)に示すように、形成された酸化物半導体層5、ソース電極6及びドレイン電極7の上面を覆うように、例えばプラズマCVD法を用いて保護膜8を形成する。

#### 【0042】

以上により、本実施形態の薄膜トランジスタ1を得ることができる。

#### 【0043】

##### <3. 本実施形態の効果>

このように構成した本実施形態の薄膜トランジスタ1の製造方法であれば、半導体層形成工程において、スパッタリング中の酸素ガス分圧を変更することなく成膜距離を変更することにより結晶性を制御することができるので、非晶質の酸化物半導体膜と結晶質の酸化物半導体膜とをいずれも優れた膜密度で成膜することができる。これにより、ゲート絶縁層4や保護層8と、酸化物半導体層5との間の界面における欠損密度を低下させることができるために、高い信頼性を有する優れた薄膜トランジスタを製造することができる。

20

#### 【0044】

##### <4. その他の変形実施形態>

なお、本発明は前記実施形態に限られるものではない。

#### 【0045】

例えば、前記実施形態の薄膜トランジスタ1は、ゲート電極3、ゲート絶縁層4及び酸化物半導体層5が基板2側から順に積層されたボトムゲート型のものであったがこれに限らない。他の実施形態では、薄膜トランジスタ1は、図4に示すように、酸化物半導体層5、ゲート絶縁層4、及びゲート電極3が基板2側から順に積層されたトップゲート型のものであってもよい。

30

#### 【0046】

また前記実施形態の薄膜トランジスタ1は、酸化物半導体層5は、非晶質の第1半導体層5aと、結晶質の第2半導体層5bを積層した2層構造であったが、これに限らない。他の実施形態では、酸化物半導体層5は例えば3層以上の構造を有してもよい。

#### 【0047】

また、前記実施形態の製造方法は、非晶質の第1半導体層5aを成膜した後、結晶質の第2半導体層5bを成膜していたがこれに限らない。他の実施形態では、結晶質の第2半導体層5bを成膜した後、非晶質の第1半導体層5aを成膜してもよい。

40

#### 【0048】

前記実施形態の製造方法では、第1成膜工程で真空容器20内に生成したプラズマPを維持したまま成膜距離を変更することにより第2成膜工程に移行したが、これに限らない。他の実施形態では、第1成膜工程と第2成膜工程との間で、プラズマPの生成を停止するようにしてもよい。

#### 【0049】

その他、本発明は前記実施形態に限られず、その趣旨を逸脱しない範囲で種々の変形が可能であるのは言うまでもない。

#### 【実施例】

50

### 【0050】

以下、実施例を挙げて本発明をより具体的に説明する。本発明は以下の実施例によって制限を受けるものではなく、前記、後記の趣旨に適合し得る範囲で適当に変更を加えて実施することが勿論可能であり、それらはいずれも本発明の技術的範囲に包含される。

### 【0051】

#### < 1 . 成膜距離と酸化物半導体膜の結晶性及び膜密度との関係 >

本発明の効果を示す実験例として、上記した本実施形態のスパッタリング装置 100 を用いて、スパッタリング中の成膜距離と、形成される酸化物半導体膜の結晶性及び膜密度との関係性を評価した。

### 【0052】

#### (サンプルの作製)

具体的には、スパッタリング装置 100 の真空容器 20 を  $4.0 \times 10^{-4}$  Pa 以下に真空排気した後、スパッタリングガスとしてアルゴンと酸素の混合ガス（酸素分圧：5%）を 5 sccm の流量で供給して、真空容器内 20 内の圧力を 0.9 Pa に調整した。そして複数のアンテナ 50 に高周波電源 60 から高周波電力を供給して誘導結合型のプラズマを生成し、これを維持した。ターゲット T として I G Z O (11114) を使用し、ターゲット T に直流電圧パルス (-400 V, 75 kHz, Duty 95.7%) を印加してスパッタリングを行い、ガラス基板 (SiO<sub>2</sub>) 上に酸化物半導体膜 (I G Z O 膜) を成膜した。ここでは、成膜距離を変えて (124 mm, 153 mm, 183 mm) 成膜を行うことで、成膜条件の異なる 3 つの酸化物半導体膜を成膜した。

10

### 【0053】

#### (結晶性の評価)

そして、作製した 3 つのサンプルに対して、Cu 光源 (Cu - K 線) を使用したブルカーラー・エイエックスエス社製の X 線回折装置（型番：D 8 DISCOVER）を用いて X 線回折 (XRD) を行った。その結果を図 5 に示す。図 5 に示すスペクトルに現れている回折ピークは、I G Z O 膜中の In に由来するものである。ここから分かるように、成膜距離が 183 mm であるサンプルでは、 $2\theta = 31^\circ$  近傍に回折ピークが現れず、 $2\theta = 33^\circ$  近傍で回折ピークが現れており、非晶質の I G Z O 膜 (a-I G Z O) が主に成膜されていることが分かった。一方で、成膜距離が比較的短いサンプル (153 mm, 124 mm) では、 $2\theta = 33^\circ$  近傍に回折ピークが現れず、 $2\theta = 31^\circ$  近傍で急峻な回折ピークが現れており、結晶質の I G Z O 膜 (c-I G Z O) が主に成膜されていることが分かった。この結果から、基板とターゲットとの間の距離を変えてスパッタリングすることにより、酸化物半導体膜の結晶性を制御できることを確認できた。

20

成膜距離が最も遠いサンプルでは、他のサンプルに比べて、ターゲットから飛び出したスパッタ粒子が基板に到達するまでに互いに衝突する回数が増えてしまい、これにより結晶性が低下して非晶質の I G Z O 膜が主に成膜されるものと考えられる。逆に、成膜距離が比較的短いサンプルでは、ターゲットから飛び出したスパッタ粒子が基板に到達するまでに互いに衝突する回数が減少し、これにより結晶質の I G Z O 膜が主に成膜されるものと考えられる。

30

### 【0054】

#### (膜密度の評価)

次に、作製した各サンプルの膜密度を測定した。膜密度の測定は、X 線反射率法 (XRR 法、測定機器：Bruker 社 D 8 DISCOVER) により行った。その結果を図 6 に示す。図 6 には、成膜距離毎の膜密度と、前記した X 線回折で得られるスペクトルに現れている回折ピーク (I G Z O 膜中の In に由来する回折ピーク) の半値全幅とを示している。図 6 から分かるように、成膜距離を変更して成膜を行うことにより、膜密度を大きく低下させることなく I G Z O 膜の結晶性を制御でき、結晶質の I G Z O 膜と非晶質の I G Z O 膜とを作り分けできることを確認できた。

40

### 【0055】

#### < 2 . 酸素分圧と酸化物半導体膜の結晶性及び膜密度との関係 >

50

次に比較例として、上記した本実施形態のスパッタリング装置 100 を用いて、スパッタリングガス中の酸素分圧と、形成される酸化物半導体膜の結晶性及び膜密度との関係性を評価した。

#### 【0056】

##### (サンプルの作製)

具体的には、スパッタリング装置 100 の真空容器 20 を  $4.0 \times 10^{-4}$  Pa 以下に真空排気した後、スパッタリングガスとしてアルゴンと酸素の混合ガスを 5 sccm の流量で供給して、真空容器内 20 内の圧力を 0.9 Pa に調整した。そして複数のアンテナ 50 に高周波電源 60 から高周波電力を供給して誘導結合型のプラズマを生成し、これを維持した。ターゲット T として I G Z O (1114) を使用し、ターゲット T に直流電圧パルス (-400 V, 75 kHz, Duty 95.7%) を印加してスパッタリングを行い、ガラス基板 (SiO<sub>2</sub>) 上に酸化物半導体膜 (I G Z O 膜) を成膜した。スパッタリングは、成膜距離を 124 mm に固定して行った。ここでは、スパッタリングガス中の酸素分圧を変えて (0.5%、2.5%、5%) 成膜を行うことで、成膜条件の異なる 3 つの酸化物半導体膜を成膜した。

#### 【0057】

##### (結晶性の評価)

そして、作製した 3 つのサンプルに対して、前記した X 線回折装置を用いて X 線回折 (XRD) を行った。その結果を図 7 に示す。ここから分かるように、酸素分圧が 0.5% であるサンプルでは、 $2\theta = 31^\circ$  近傍に回折ピークが現れず、 $2\theta = 33^\circ$  近傍で回折ピークが現れており、非晶質の I G Z O 膜 (a - I G Z O) が主に成膜されていることが分かった。一方、酸素分圧が比較的高いサンプル (5%) では、 $2\theta = 31^\circ$  近傍で急峻な回折ピークが現れており、結晶質の I G Z O 膜 (c - I G Z O) が主に成膜されていることが分かった。酸素分圧が 2.5% のサンプルでは、 $2\theta = 33^\circ$  近傍と  $2\theta = 31^\circ$  近傍で回折ピークが現れており、非晶質の I G Z O 膜 (a - I G Z O) と結晶質の I G Z O 膜 (c - I G Z O) の両方が成膜されていることが分かった。この結果から、スパッタリングガス中の酸素分圧を変えることで、酸化物半導体膜の結晶性を制御できることを確認した。

#### 【0058】

##### (膜密度の評価)

次に、作製した各サンプルの膜密度を、前記した X 線反射率法により測定した。その結果を図 8 に示す。図 8 には、酸素分圧毎の膜密度と、前記した X 線回折で得られるスペクトルに現れている回折ピークの半値全幅とを示している。図 8 から分かるように、酸素分圧を変更して成膜を行うことにより、酸化物半導体膜の結晶性を制御し、結晶質の I G Z O 膜と非晶質の I G Z O 膜とを作り分けできるが、非晶質の I G Z O 膜を成膜する場合に膜密度が大きく低下してしまうことを確認できた。

#### 【符号の説明】

#### 【0059】

2 … 基板

5 … 酸化物半導体層

100 … スパッタリング装置

20 … 真空容器

50 … アンテナ

T … ターゲット

P … プラズマ

10

20

30

40

50

【図面】

【図1】

【図2】

【図3】

【図4】

【図 5】

【図 6】

10

20

30

40

【図 7】

【図 8】

50

---

フロントページの続き

(51)国際特許分類

F I

H 01 L      29/78      6 1 8 E

日新電機株式会社内

審査官 長谷川 直也

(56)参考文献

特開2013-021308 (JP, A)

特開2020-092222 (JP, A)

特開2018-170488 (JP, A)

特開2008-198705 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 01 L      2 1 / 3 6 3

C 23 C      1 4 / 0 8

C 23 C      1 4 / 3 4

H 01 L      2 1 / 3 3 6

H 01 L      2 9 / 7 8 6