(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5888990号

(P5888990)

(45) 発行日 平成28年3月22日(2016.3.22)

(24) 登録日 平成28年2月26日(2016.2.26)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 618B |

| HO1L 21/336  | (2006.01) | HO1L 29/78 | 618A |

| HO1L 21/8242 | (2006.01) | HO1L 29/78 | 616M |

| HO1L 27/108  | (2006.01) | HO1L 29/78 | 619A |

| HO1L 21/8247 | (2006.01) | HO1L 29/78 | 626C |

請求項の数 7 (全 46 頁) 最終頁に続く

(21) 出願番号

特願2012-1728 (P2012-1728)

(22) 出願日

平成24年1月9日(2012.1.9)

(65) 公開番号

特開2012-160716 (P2012-160716A)

(43) 公開日

平成24年8月23日(2012.8.23)

審査請求日 平成27年1月6日(2015.1.6)

(31) 優先権主張番号 特願2011-4421 (P2011-4421)

(32) 優先日 平成23年1月12日(2011.1.12)

(33) 優先権主張国 日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

(57) 【特許請求の範囲】

【請求項 1】

基板上に下地絶縁層を形成し、

前記下地絶縁層上に第1の導電膜を形成し、

前記第1の導電膜上に第1のエッティングマスクを形成し、

前記第1のエッティングマスクを用いて前記第1の導電膜を加工して、第1の導電層を形成し、

前記第1のエッティングマスクを除去し、

前記第1の導電層上に第1の酸化物半導体膜を形成し、

前記基板に対して第1の加熱処理を行って、前記第1の酸化物半導体膜を第2の酸化物半導体膜とし、 10

前記第2の酸化物半導体膜上に第2のエッティングマスクを形成し、

前記第2のエッティングマスクを用いて前記第2の酸化物半導体膜を加工して、第1の酸化物半導体層を形成し、

前記第2のエッティングマスクを除去し、

少なくとも前記第1の酸化物半導体層を覆ってサイドウォール絶縁膜を形成し、

前記基板に対して第2の加熱処理を行い、

前記サイドウォール絶縁膜上に第3のエッティングマスクを形成し、

前記第3のエッティングマスクを用いて前記サイドウォール絶縁膜を加工して、少なくとも前記第1の酸化物半導体層の側壁を覆うサイドウォール絶縁層を形成し、 20

前記第3のエッティングマスクを除去し、

少なくとも前記第1の酸化物半導体層上にゲート絶縁層を形成し、

前記ゲート絶縁層上に第2の導電膜を形成し、

前記第2の導電膜上に第4のエッティングマスクを形成し、

前記第4のエッティングマスクを用いて前記第2の導電膜を加工して、第2の導電層を形成し、

前記第4のエッティングマスクを除去し、

前記第2の導電層をマスクとして前記第1の酸化物半導体層にイオンインプランテーションを行って、ソース領域及びドレイン領域を有する第2の酸化物半導体層を形成することを特徴とする半導体装置の作製方法。 10

【請求項2】

請求項1において、

前記第2の酸化物半導体層が設けられた状態で前記基板に対して第3の加熱処理を行うことを特徴とする半導体装置の作製方法。

【請求項3】

請求項2において、

前記第3の加熱処理の前に、前記ゲート絶縁層及び前記第2の導電層を覆ってパッシベーション膜を形成することを特徴とする半導体装置の作製方法。

【請求項4】

請求項1乃至請求項3のいずれか一において、

前記下地絶縁層は、化学量論比よりも多くの酸素を含む絶縁性酸化物を有することを特徴とする半導体装置の作製方法。 20

【請求項5】

請求項1乃至請求項4のいずれか一において、

前記サイドウォール絶縁膜は、化学量論比よりも多くの酸素を含む絶縁性酸化物を有することを特徴とする半導体装置の作製方法。

【請求項6】

請求項4または請求項5において、

前記絶縁性酸化物は酸化シリコンであることを特徴とする半導体装置の作製方法。

【請求項7】

請求項1乃至請求項6のいずれか一において、

前記下地絶縁層と前記サイドウォール絶縁膜は、同じ方法及び同じ材料を用いて設けられることを特徴とする半導体装置の作製方法。 30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置とその作製方法に関する。なお、本明細書において、半導体装置とは、半導体素子自体または半導体素子を含むものをいい、このような半導体素子として、例えばトランジスタ（薄膜トランジスタなど）が挙げられる。また、液晶表示装置などの表示装置も半導体装置に含まれる。 40

【背景技術】

【0002】

半導体装置は、人間の生活に欠かせないものとなっている。従来、半導体装置に適用される半導体材料はシリコンが主流であった。しかし、近年、半導体装置に適用される半導体として、酸化物半導体が注目されている。酸化物半導体として、Zn-O系金属酸化物またはIn-Ga-Zn-O系金属酸化物を適用した半導体装置が、特許文献1及び特許文献2に開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2007-123861号公報

【特許文献 2】特開 2007-96055号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

酸化物半導体を適用した半導体装置を作製するに際し、酸化物半導体層の側面を所望の形状に加工すると、該酸化物半導体層の側面が活性な状態で反応室の真空（減圧雰囲気または還元性雰囲気）に曝される。そのため、酸化物半導体層の側面から反応室へと酸素が引き抜かれ、欠陥（酸素欠損）を生じることになる。このような欠陥（酸素欠損）は、ドナーとして欠陥（酸素欠損）の存在する領域を低抵抗化させ、ソースとドレインの間にリーキ電流を生じさせる原因となる。 10

【0005】

本発明の一態様は、酸化物半導体層の側面に酸素を十分に存在させつつ作製することができる半導体装置の作製方法を提供することを課題とする。

【0006】

本発明の一態様は、酸化物半導体層中の欠陥（酸素欠損）が十分に少なく、ソースとドレインの間のリーキ電流が抑制された半導体装置を提供することを課題とする。

【課題を解決するための手段】

【0007】

本発明の一態様は、酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥（酸素欠損）を少なくする半導体装置の作製方法である。前記酸化物半導体層の側壁を覆って設けられた絶縁層はサイドウォール絶縁層である。該サイドウォール絶縁層の形成は、サイドウォール絶縁膜を全面に形成し、該サイドウォール絶縁膜を加工することで形成する。そして、サイドウォール絶縁膜を形成した後サイドウォール絶縁層を形成する前に更なる加熱処理を行うとよい。 20

【0008】

なお、本発明の一態様において、半導体装置は、T G B C ( T o p G a t e B o t t o m C o n t a c t ) 構造とする。 30

【0009】

なお、本明細書において、「膜」とは、CVD法（プラズマCVD法などを含む。）またはスパッタリング法などにより、被形成面の全面に形成されたものをいう。一方で、「層」とは、「膜」が加工されたもの、または被形成面の全面に形成された状態で加工を要しないものをいう。ただし、「膜」と「層」を特に区別することなく用いることがあるものとする。

【発明の効果】

【0010】

本発明の一態様によれば、酸化物半導体層の側面に酸素を十分に存在させつつ半導体装置を作製することができる。 40

【0011】

本発明の一態様によれば、半導体装置の酸化物半導体層中の欠陥（酸素欠損）を十分に少なくし、ソースとドレインの間のリーキ電流を小さくすることができる。

【図面の簡単な説明】

【0012】

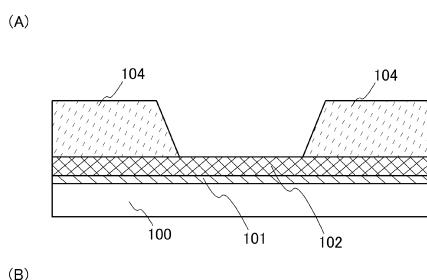

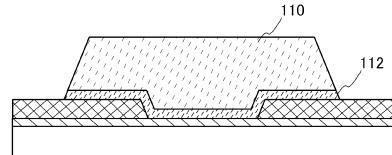

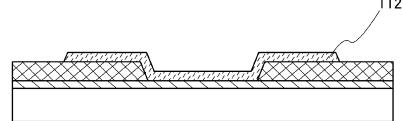

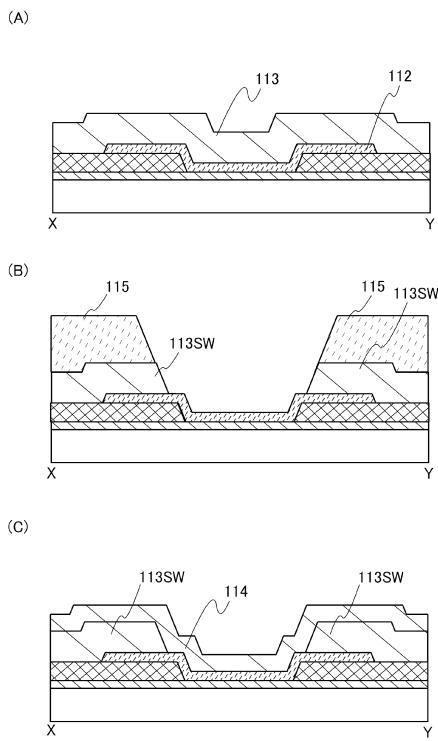

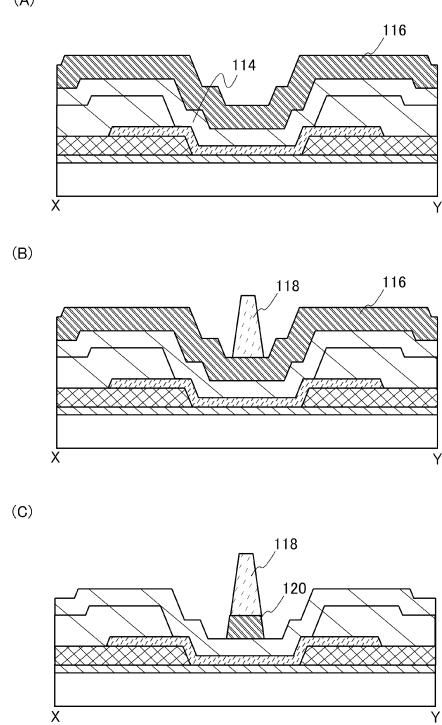

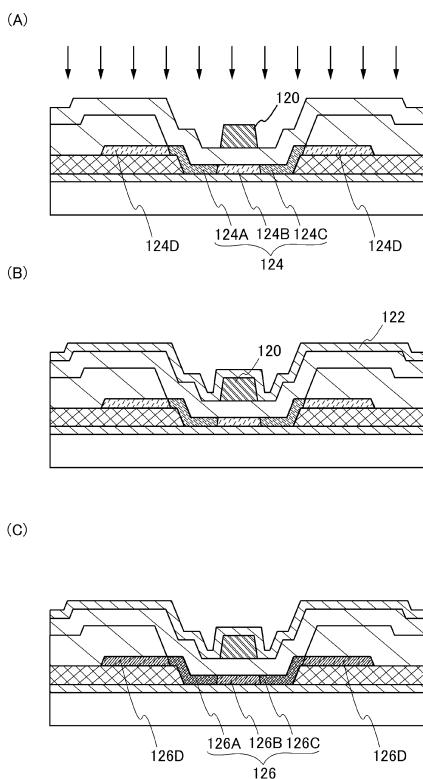

【図1】本発明の一態様である半導体装置の作製方法を説明する図。

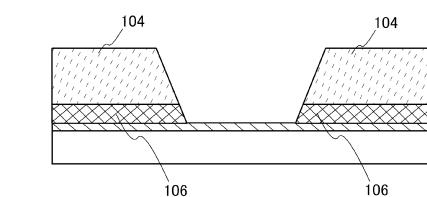

【図2】本発明の一態様である半導体装置の作製方法を説明する図。

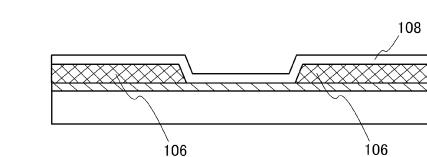

【図3】本発明の一態様である半導体装置の作製方法を説明する図。

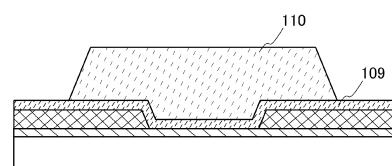

【図4】本発明の一態様である半導体装置の作製方法を説明する図。

【図5】本発明の一態様である半導体装置の作製方法を説明する図。 50

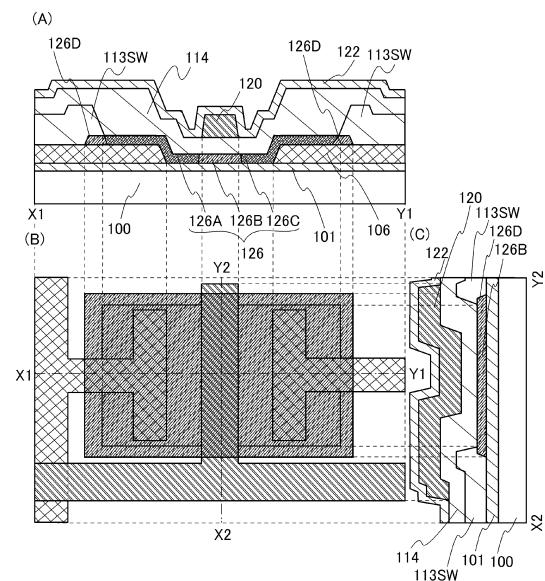

【図6】本発明の一態様である半導体装置を説明する図。

【図7】本発明の一態様である半導体装置を説明する図。

【図8】本発明の一態様である半導体装置を説明する図。

【図9】本発明の一態様である半導体装置を説明する図。

【図10】本発明の一態様である半導体装置を説明する図。

【図11】本発明の一態様である半導体装置を説明する図。

【図12】本発明の一態様である半導体装置を説明する図。

【図13】本発明の一態様である半導体装置を説明する図。

【図14】本発明の一態様である半導体装置を説明する図。

【図15】本発明の一態様である半導体装置を説明する図。

【図16】本発明の一態様である半導体装置を説明する図。

【図17】本発明の一態様である半導体装置を説明する図。

【図18】本発明の一態様である半導体装置を説明する図。

【図19】本発明の一態様である半導体装置を説明する図。

【図20】本発明の一態様である半導体装置を説明する図。

【図21】計算結果を説明する図。

【図22】計算結果を説明する図。

【発明を実施するための形態】

【0013】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、上面図において、絶縁膜及び絶縁層は図示しないことがある。

【0014】

(実施の形態1)

本実施の形態では、本発明の一態様である半導体装置の作製方法について説明する。具体的には、トランジスタの作製方法について説明する。

【0015】

本実施の形態のトランジスタの作製方法では、基板100上に下地絶縁層101及び第1の導電膜102を形成し、第1の導電膜102上に第1のエッチングマスク104を形成し、第1のエッチングマスク104を用いて第1の導電膜102を加工することで第1の導電層106を形成し、第1のエッチングマスク104を除去し、第1の導電層106上に第1の酸化物半導体膜108を形成し、基板100に対して少なくとも第1の加熱処理を行って第2の酸化物半導体膜109とし、第2の酸化物半導体膜109上に第2のエッチングマスク110を形成し、第2のエッチングマスク110を用いて第2の酸化物半導体膜109を加工することで、第1の酸化物半導体層112を形成し、第2のエッチングマスク110を除去し、少なくとも第1の酸化物半導体層112を覆ってサイドウォール絶縁膜113を形成し、基板100に対して第2の加熱処理を行い、サイドウォール絶縁膜113上に第3のエッチングマスク115を形成し、第3のエッチングマスク115を用いてサイドウォール絶縁膜113を加工することで、少なくとも第1の酸化物半導体層112の側壁を覆うサイドウォール絶縁層113SWを形成し、第3のエッチングマスク115を除去し、少なくとも第1の酸化物半導体層112上に第1の絶縁層114を形成し、第4の導電膜116上に第4のエッチングマスク118を形成し、第4のエッチングマスク118を用いて第2の導電膜116を加工することで第2の導電層120を形成し、第4のエッチングマスク118を除去し、第2の導電層120をマスクとして第1の酸化物半導体層112にイオンインプランテーションを行ってソース領域及びドレイン領域を有する第2の酸化物半導体層124を形成し、好ましくは第1の絶縁層114上及び第2の導電層120を覆って第2の絶縁層122を形成することを特徴とする。更に、第2の酸化物半導体層124が設け

10

20

30

40

50

られた状態で基板 100 に対して第 3 の加熱処理を行うことが好ましい。

【0016】

なお、前記第 1 の加熱処理は、以下では好ましい形態を説明しているため、前記第 1 の加熱処理よりも前に二の加熱処理を行い、前記第 2 の加熱処理と前記第 3 の加熱処理の間に一の加熱処理を行うため、前記第 1 の加熱処理は「第 3 の加熱処理」と表記され、前記第 2 の加熱処理は「第 4 の加熱処理」と表記され、前記第 3 の加熱処理は「第 6 の加熱処理」と表記されている。

【0017】

まず、基板 100 上に下地絶縁層 101 及び第 1 の導電膜 102 を形成し、第 1 の導電膜 102 上に第 1 のエッティングマスク 104 を形成する(図 1 (A))。

10

【0018】

基板 100 は、ガラス基板(好ましくは無アルカリガラス基板)、石英基板、セラミック基板またはプラスチック基板などを適宜用いることができる。または、基板 100 として、可撓性を有するガラス基板または可撓性を有するプラスチック基板を用いることができる。プラスチック基板の材料としては、屈折率異方性の小さい材料を用いることが好ましい。例えば、ポリエーテルサルфон(PES)、ポリイミド、ポリエチレンナフタレート(PEN)、PVF(ポリビニルフルオライド)、ポリエステル、ポリカーボネート(PC)、アクリル樹脂または半硬化した有機樹脂中に纖維体を含むプリプレグなどを用いることができる。

【0019】

下地絶縁層 101 は、少なくとも表面に酸素を含み、該酸素の一部が加熱処理により脱離する絶縁性酸化物により形成する。酸素の一部が加熱処理により脱離する絶縁性酸化物としては、化学量論比よりも多くの酸素を含むものを用いることが好ましい。これは、加熱処理により、下地絶縁層 101 に接する酸化物半導体膜(または層)に酸素を拡散させることができるためである。

20

【0020】

絶縁性酸化物が化学量論比よりも多くの酸素を含む場合として、例えば、酸化シリコン SiO<sub>x</sub>において x > 2 である場合が挙げられる。ただし、これに限定されず、下地絶縁層 101 は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化ハフニウム、酸化イットリウムなどで形成してもよい。

30

【0021】

なお、「窒化酸化シリコン」とは、その組成として、酸素よりも窒素の含有量が多いものをいう。

【0022】

なお、「酸化窒化シリコン」とは、その組成として、窒素よりも酸素の含有量が多いものをいう。

【0023】

なお、下地絶縁層 101 は、複数の層を積層して形成してもよい。下地絶縁層 101 は、例えば、窒化シリコン層上に酸化シリコン層が設けられた積層構造であってもよい。

40

【0024】

ところで、化学量論比よりも多くの酸素を含む絶縁性酸化物では、該酸素の一部が加熱処理により脱離しやすい。酸素の一部が加熱処理により脱離しやすいときの TDS 分析による酸素の脱離量(酸素原子に換算した値)は、1.0 × 10<sup>18</sup> atoms/cm<sup>3</sup> 以上、好ましくは 1.0 × 10<sup>20</sup> atoms/cm<sup>3</sup> 以上、より好ましくは 3.0 × 10<sup>20</sup> atoms/cm<sup>3</sup> 以上であるとよい。

【0025】

ここで、前記 TDS 分析の測定方法について説明する。TDS 分析における気体の脱離量は、TDS スペクトルの積分値に比例する。このため、絶縁性酸化物における TDS スペクトルの積分値と、標準試料の基準値から、気体の脱離量を計算することができる。標

50

準試料の基準値は、ある特定の原子を含む試料（標準試料）におけるスペクトルの積分値に対する原子密度の割合である。

【0026】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDSスペクトル及び絶縁性酸化物のTDSスペクトルから、絶縁性酸化物の酸素分子（O<sub>2</sub>）の脱離量（N<sub>O<sub>2</sub></sub>）は、以下の式（1）で求めることができる。

【0027】

【数1】

$$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times \alpha \quad (1)$$

10

【0028】

N<sub>H<sub>2</sub></sub>は、標準試料から脱離した水素分子（H<sub>2</sub>）を密度に換算した値である。S<sub>H<sub>2</sub></sub>は、標準試料の水素分子（H<sub>2</sub>）のTDSスペクトルの積分値である。すなわち、N<sub>H<sub>2</sub></sub> / S<sub>H<sub>2</sub></sub>を標準試料の基準値とする。S<sub>O<sub>2</sub></sub>は、絶縁性酸化物の酸素分子（O<sub>2</sub>）のTDSスペクトルの積分値である。αは、TDSスペクトル強度に影響する係数である。数式1の詳細に関しては、特開平06-275697号公報を参照されたい。

【0029】

なお、TDS分析による前記酸素の脱離量（酸素原子に換算した値）は、電子科学株式会社製の昇温脱離分析装置EMD-WA1000S/Wを用い、標準試料として1×10<sup>16</sup> atoms/cm<sup>3</sup>の水素原子を含むシリコンウェハを用いて測定した場合の値を示している。

20

【0030】

なお、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、前記係数αは酸素分子のイオン化率を含んでいるため、酸素分子の放出量を評価することで、酸素原子の放出量についても算出することができる。

【0031】

なお、N<sub>O<sub>2</sub></sub>は酸素分子（O<sub>2</sub>）の脱離量である。そのため、酸素原子で換算した酸素の脱離量は、酸素分子（O<sub>2</sub>）の脱離量の2倍である。

【0032】

30

下地絶縁層101は、スパッタリング法またはCVD法などにより形成すればよい。CVD法を用いる場合には、下地絶縁層101を形成した後に加熱処理を行って下地絶縁層101に含まれる水素などを脱離させて除去することが好ましい。なお、下地絶縁層101が酸素の一部が加熱処理により脱離する絶縁性酸化物により形成される場合には、スパッタリング法による形成が行いやすいため好ましい。下地絶縁層101として、酸化シリコン膜を形成する場合には、ターゲットとして石英（好ましくは合成石英）ターゲット、スパッタリングガスとしてアルゴンガスを用いてもよいし、ターゲットとしてシリコンターゲット、スパッタリングガスとして酸素を含むガスを用いてもよい。なお、酸素を含むガスとしては、アルゴンガスと酸素ガスの混合ガスでもよいし、酸素ガスのみを用いてもよい。

40

【0033】

下地絶縁層101が、酸素を含み、該酸素の一部が加熱処理により脱離する絶縁性酸化物により形成される場合、下地絶縁層101の厚さは、50nm以上、好ましくは200nm以上500nm以下とするよい。特に、前記範囲内で厚くすると、加熱処理により下地絶縁層101に接する酸化物半導体膜（または層）に多くの酸素を拡散させることができ、下地絶縁層101と酸化物半導体膜（または層）の界面における欠陥（酸素欠損）を低減することができるため、好ましい。

【0034】

第1の導電膜102は、導電性材料により単層で、または積層して形成すればよい。ここで、導電性材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン

50

、タングステン、マンガン、マグネシウム、ベリリウム若しくはジルコニウムなどの金属、または前記金属の一種または複数種を成分として含む合金を挙げることができる。例えば、シリコンを含むアルミニウム膜の単層膜、アルミニウム膜上にチタン膜が設けられた二層の積層膜、窒化チタン膜上にチタン膜が設けられた二層の積層膜、窒化チタン膜上にタングステン膜が設けられた二層の積層膜、窒化タンタル膜上にタングステン膜が設けられた二層の積層膜、または、アルミニウム膜をチタン膜で挟持した三層の積層膜などが挙げられる。

## 【0035】

なお、第1の導電膜102を銅により形成すると、第1の導電膜102を加工して形成される配線を低抵抗にすることができるため、好ましい。ここで、第1の導電膜102が積層構造である場合には、第1の導電膜102のうち少なくとも一層が銅により形成されていればよい。

10

## 【0036】

または、第1の導電膜102は、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物または酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料により形成してもよい。

## 【0037】

または、第1の導電膜102は、前記透光性を有する導電性材料膜と、前記金属膜を積層して形成してもよい。

20

## 【0038】

なお、第1の導電膜102の形成方法及び厚さは特に限定されず、作製するトランジスタのサイズなどに応じて決めればよい。第1の導電膜102の形成方法としては、例えば、スパッタリング法またはCVD法などが挙げられる。第1の導電膜102の厚さは、例えば100nm以上300nm以下とすればよい。

## 【0039】

第1のエッチングマスク104は、レジスト材料により形成すればよい。ただし、これに限定されず、第1の導電膜102を加工する際にマスクとして機能するものであればよい。

30

## 【0040】

次に、第1のエッチングマスク104を用いて第1の導電膜102を加工することで第1の導電層106を形成する(図1(B))。

## 【0041】

なお、ここで、加工は、ドライエッチングにより行えばよい。ドライエッチングに用いるエッチングガスとしては、例えば塩素ガス、または三塩化ホウ素ガスと塩素ガスの混合ガスを用いればよい。ただし、これに限定されず、ウエットエッチングを用いてもよいし、第1の導電膜102を加工することができる他の手段を用いてもよい。

## 【0042】

第1の導電層106は、少なくともソース電極及びドレイン電極を構成する。

40

## 【0043】

次に、第1のエッチングマスク104を除去し、第1の導電層106上に第1の酸化物半導体膜108を形成する(図1(C))。

## 【0044】

なお、第1のエッチングマスク104がレジスト材料により形成されている場合には、第1のエッチングマスク104をアッシングのみで除去してもよい。

## 【0045】

第1の酸化物半導体膜108は、金属酸化物を用いて形成すればよく、四元系金属酸化物であるIn-Sn-Ga-Zn-O系金属酸化物、三元系金属酸化物であるIn-Ga-Zn-O系金属酸化物、In-Sn-Zn-O系金属酸化物、In-Al-Zn-O系

50

金属酸化物、Sn-Ga-Zn-O系金属酸化物、Al-Ga-Zn-O系金属酸化物若しくはSn-Al-Zn-O系金属酸化物、または二元系金属酸化物であるIn-Zn-O系金属酸化物、Sn-Zn-O系金属酸化物、Al-Zn-O系金属酸化物、Zn-Mg-O系金属酸化物、Sn-Mg-O系金属酸化物、In-Mg-O系金属酸化物若しくはIn-Ga-O系金属酸化物などを用いて形成すればよい。または、In-O系金属酸化物、Sn-O系金属酸化物、Zn-O系金属酸化物などを用いてもよい。なお、n元系金属酸化物はn種類の金属酸化物で構成されるものとする。ここで、例えば、In-Ga-Zn-O系金属酸化物は、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。

10

#### 【0046】

なお、前記金属酸化物では、これらの化学量論比に対し、酸素(O)を過剰に含ませることが好ましい。酸素(O)を過剰に含ませると、形成される第1の酸化物半導体膜108の欠陥(酸素欠損)によるキャリアの生成を抑制することができる。

#### 【0047】

なお、一例として、第1の酸化物半導体膜108をIn-Zn-O系金属酸化物により形成する場合には、ターゲットの組成を原子数比で、In/Zn=1~100、好ましくはIn/Zn=1~20、さらに好ましくはIn/Zn=1~10とする。Znに対するInの原子数比を好ましい前記範囲とすることで、トランジスタの電界効果移動度を向上させることができる。ここで、酸素(O)を過剰に含ませるためには、化合物の原子数比In:Zn:O=X:Y:Zを、Z>1.5X+Yとすることが好ましい。

20

#### 【0048】

なお、第1の酸化物半導体膜108に適用することができる金属酸化物は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、更に好ましくは3eV以上であるとい。このように、バンドギャップの広い金属酸化物を用いると、トランジスタのオフ電流を低減することができる。

#### 【0049】

なお、第1の酸化物半導体膜108には、水素が含まれる。この水素は、水素原子の他、水素分子、水、水酸基、または水素化物として含まれる場合もある。第1の酸化物半導体膜108に含まれる水素は、極力少ないことが好ましい。

30

#### 【0050】

なお、第1の酸化物半導体膜108のアルカリ金属及びアルカリ土類金属の濃度は小さくすることが好ましく、これらの濃度は、好ましくは $1 \times 10^{-8}$ atoms/cm<sup>3</sup>以下、更に好ましくは $2 \times 10^{-6}$ atoms/cm<sup>3</sup>以下とする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアが生成されることがあり、トランジスタのオフ電流を上昇させる原因となるからである。

#### 【0051】

前記アルカリ金属の一種として、例えば、ナトリウムは、酸化物半導体層に接して絶縁性酸化物が設けられている場合には、当該絶縁性酸化物中に拡散してNa<sup>+</sup>となることが多い。また、ナトリウムは、酸化物半導体膜中において、酸化物半導体を構成する金属と酸素の結合を分断し、更にはこれらの結合中に入り込む場合もある。その結果、トランジスタのしきい値電圧をマイナス方向にシフトさせ、電界効果移動度を低下させる原因となり、トランジスタの特性を劣化させるのみならず、基板面内における個々のトランジスタの特性を不均一なものとする。

40

#### 【0052】

このようなナトリウムが原因となるトランジスタの特性の劣化及び不均一化は、酸化物半導体膜中の水素濃度が十分に低い場合に、特に顕著である。従って、(完成した)トランジスタが有する酸化物半導体層中の水素濃度が $1 \times 10^{-8}$ atoms/cm<sup>3</sup>以下、特に $1 \times 10^{-7}$ atoms/cm<sup>3</sup>以下である場合には、特に、アルカリ金属及びアルカリ土類金属の濃度を少なくすることが好ましい。SIMS法によるNa濃度の測定値は

50

、 $5 \times 10^{16}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以下、更に好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以下とするといい。同様に、SIMS法によるLi濃度の測定値は、 $5 \times 10^{15}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以下とするといい。同様に、SIMS法によるK濃度の測定値は、 $5 \times 10^{15}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以下とするといい。

#### 【0053】

なお、第1の酸化物半導体膜108の形成方法及び厚さは特に限定されず、作製するトランジスタのサイズなどに応じて決めればよい。第1の酸化物半導体膜108の形成方法としては、例えば、スパッタリング法、塗布法、印刷法またはパルスレーザー蒸着法などが挙げられる。第1の酸化物半導体膜108の厚さは、3nm以上50nm以下とすることが好ましい。

#### 【0054】

ここでは、好ましい一例として、In-Ga-Zn-O系金属酸化物ターゲットを用いたスパッタリング法により第1の酸化物半導体膜108を形成する。ここで、スパッタリングガスとしては、希ガス（例えばアルゴン）、酸素ガスまたは希ガスと酸素ガスの混合ガスを用いればよい。

#### 【0055】

なお、第1の酸化物半導体膜108を形成する際に用いるスパッタリングガスとしては、水素、水、水酸基または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。また、基板100を高温に保持した状態で第1の酸化物半導体膜108を形成すると第1の酸化物半導体膜108に含まれる不純物濃度を低減することができる。ここで、基板100の温度は、100以上600以下、好ましくは200以上400以下とすればよい。

#### 【0056】

なお、第1の酸化物半導体膜108は、非晶質構造であってもよいし、結晶構造を有していてもよい。第1の酸化物半導体膜108が結晶構造を有する場合には、c軸方向に配向した結晶性の（C Axis Aligned Crystalline：CAAC）酸化物半導体膜とすることが好ましい。第1の酸化物半導体膜108をCAAC酸化物半導体膜とすることで、トランジスタの信頼性を高めることができる。

#### 【0057】

なお、CAAC酸化物半導体膜とは、c軸配向し、且つab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては、金属原子が層状に配列し、または金属原子と酸素原子が層状に配列し、ab面（あるいは表面または界面）においては、a軸またはb軸の向きが異なる（c軸を中心に回転した）結晶を含む酸化物半導体膜のことである。

#### 【0058】

なお、広義には、CAAC酸化物半導体膜とは、非単結晶であって、そのab面に垂直な方向から見て、三角形もしくは六角形、または正三角形もしくは正六角形の原子配列を有し、かつc軸に垂直な方向から見て金属原子が層状に配列した相、または金属原子と酸素原子が層状に配列した相を含む材料をいう。

#### 【0059】

なお、CAAC酸化物半導体膜は単結晶ではないが、非晶質のみから形成されているものでもない。また、CAAC酸化物半導体膜は結晶化した部分（結晶部分）を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できない場合もある。

#### 【0060】

また、CAAC酸化物半導体膜を構成する酸素の一部または全部が窒素で置換されてもよい。また、CAAC酸化物半導体膜を構成する個々の結晶部分のc軸は一定の方向（例えば、CAAC酸化物半導体膜が形成される基板面、CAAC酸化物半導体膜の表面または界面などに垂直な方向）に揃っていてもよい。または、CAAC酸化物半導体膜を

10

20

30

40

50

構成する個々の結晶部分の a b 面の法線は一定の方向（例えば、基板面、膜の表面または界面などに垂直な方向）であってもよい。

【 0 0 6 1 】

なお、 C A A C 酸化物半導体膜は、その組成などに応じて、導体であってもよいし、半導体であってもよいし、絶縁体であってもよい。また、 C A A C 酸化物半導体膜は、その組成などに応じて、可視光に対して透明であってもよいし、不透明であってもよい。

【 0 0 6 2 】

ここで、 C A A C 酸化物半導体膜の形成方法について説明する。

【 0 0 6 3 】

まず、酸化物半導体膜をスパッタリング法、分子線エピタキシー法、原子層堆積法またはパルスレーザー蒸着法によって形成する。なお、基板 100 を高温に保持しつつ酸化物半導体膜の形成を行うことで、非晶質部分よりも結晶部分の占める割合を大きくすることができる。このとき、基板 100 の温度は、例えば、 150 以上 450 以下とすればよく、好ましくは 200 以上 350 以下とする。

10

【 0 0 6 4 】

次に、酸化物半導体膜に対して加熱処理（この加熱処理を第 1 の加熱処理と表記する。）を行ってもよい。第 1 の加熱処理によって、非晶質部分よりも結晶部分の占める割合を大きくすることができる。第 1 の加熱処理時の基板 100 の温度は、例えば、 200 以上基板 100 の歪み点未満とすればよく、好ましくは 250 以上 450 以下とすればよく、第 1 の加熱処理の時間は 3 分以上とすればよい。第 1 の加熱処理の時間を長くすると非晶質部分よりも結晶部分の占める割合を大きくすることができるが、生産性の低下を招くことになる。そのため、第 1 の加熱処理の時間を 24 時間以下とすることが好ましい。なお、第 1 の加熱処理は、酸化性雰囲気または不活性雰囲気で行えばよいが、これらに限定されるものではない。また、第 1 の加熱処理は減圧下で行ってもよい。

20

【 0 0 6 5 】

本実施の形態において、酸化性雰囲気は、酸化性ガスを含む雰囲気である。酸化性ガスとしては、例えば、酸素、オゾンまたは亜酸化窒素などを例示することができる。該酸化性雰囲気には、酸化物半導体膜に含まれないことが好ましい成分（水及び水素など）が極力除去されていることが好ましい。例えば、酸素、オゾン、亜酸化窒素の純度を、 8 N ( 99.999999 % ) 以上、好ましくは 9 N ( 99.9999999 % ) 以上とする。

30

【 0 0 6 6 】

なお、前記酸化性雰囲気には、希ガスなどの不活性ガスが含まれていてもよい。ただし、前記酸化性雰囲気には、 10 ppm 以上の酸化性ガスが含まれているものとする。

【 0 0 6 7 】

なお、本実施の形態において、不活性雰囲気には、不活性ガス（窒素または希ガスなど）が含まれ、酸化性ガスなどの反応性ガスが 10 ppm 未満で含まれているものとする。

【 0 0 6 8 】

なお、第 1 の加熱処理は、 R T A ( R a p i d T h e r m a l A n n e a l ) 装置を用いて行えばよい。 R T A 装置を用いることで、短時間に限り、基板 100 の歪み点以上の温度で熱処理を行うことができる。そのため、短時間で非晶質部分よりも結晶部分の占める割合の大きい酸化物半導体膜を形成することができ、生産性の低下を抑制できるため好ましい。

40

【 0 0 6 9 】

ただし、第 1 の加熱処理に用いる装置は R T A 装置に限定されず、例えば、抵抗発熱体などからの熱伝導または熱輻射によって、被処理物を加熱する機構を備えた装置を用いればよい。第 1 の加熱処理に用いる加熱処理装置として、例えば、電気炉や、 G R T A ( G a s R a p i d T h e r m a l A n n e a l ) 装置、 L R T A ( L a m p R a p i d T h e r m a l A n n e a l ) 装置などの R T A ( R a p i d T h e r m a l A n n e a l ) 装置などを挙げることができる。なお、 L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリ

50

ウムランプまたは高圧水銀ランプなどのランプから発せられる光(電磁波)の輻射により、被処理物を加熱する装置である。また、G R T A 装置は、高温のガスを熱媒体として用いて被処理物を加熱する装置である。ここで、高温のガスは、被処理物の加熱温度よりも高くすることが好ましい。

【0070】

なお、本実施の形態における他の加熱処理においても、前記加熱処理装置を用いることができる。

【0071】

なお、ここで、酸化物半導体膜の材料としては、例示した前記金属酸化物を用いればよい。

10

【0072】

なお、窒素の濃度が  $1 \times 10^{17}$  atoms/cm<sup>3</sup> 以上  $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下である In-Ga-Zn-O 系金属酸化物を用いると、c 軸配向した六方晶の結晶構造を含む金属酸化物膜が形成され、一または複数の Ga 及び Zn を有する層が、二層の In-O の結晶面(インジウムと酸素を含む結晶面)の間に配される。

【0073】

ここで、第1の加熱処理後に更に二層目の酸化物半導体膜を形成してもよい。二層目の酸化物半導体膜は、一層目の酸化物半導体膜と同様の方法で形成することができる。

【0074】

二層目の酸化物半導体膜の形成は、基板 100 を高温(第1の加熱処理と同程度の温度)に保持しつつ行ってもよい。基板 100 を高温(第1の加熱処理と同程度の温度)に保持しつつ二層目の酸化物半導体膜を形成することで、一層目の酸化物半導体膜を種結晶として結晶成長させて二層目の酸化物半導体膜を形成することができる。このとき、一層目の酸化物半導体膜と二層目の酸化物半導体膜が同一の元素から構成されている場合には、当該結晶成長はホモ成長であり、一層目の酸化物半導体膜と二層目の酸化物半導体膜のいずれかに異なる元素が含まれている場合には、当該結晶成長はヘテロ成長である。

20

【0075】

なお、二層目の酸化物半導体膜を形成した後に更に第2の加熱処理を行ってもよい。第2の加熱処理は、一層目の酸化物半導体膜を形成後に行った第1の加熱処理と同様に行えばよい。第2の加熱処理により、残存した非晶質部分も結晶成長させることができるのであり、非晶質部分よりも結晶部分の占める割合を大きくすることができる。該結晶成長は、ホモ成長であってもよいし、ヘテロ成長であってもよい。

30

【0076】

以上説明したように C A A C 酸化物半導体膜を形成することができる。

【0077】

C A A C 酸化物半導体膜は、非晶質構造の酸化物半導体膜と比較して、金属と酸素の結合の秩序性が高い。すなわち、酸化物半導体膜が非晶質構造の場合には、隣接する金属によって金属原子に配位している酸素原子の数が異なるが、C A A C 酸化物半導体膜では金属原子に配位している酸素原子の数はほぼ一定となる。そのため、微視的なレベルにおいても欠陥(酸素欠損)がほぼ見られず、水素原子(水素イオンを含む)やアルカリ金属原子などによる電荷の移動や電気伝導性の不安定さを抑制することができる。

40

【0078】

従って、C A A C 酸化物半導体を用いてトランジスタを作製すると、トランジスタへの光照射またはバイアス・熱ストレス(B T)の付加を行った後に生じる、トランジスタのしきい値電圧の変化を抑制することができ、安定した電気的特性を有するトランジスタを作製することができる。

【0079】

次に、基板 100 に対して第3の加熱処理を行って第2の酸化物半導体膜 109 を形成する。

【0080】

50

なお、ここで行う第3の加熱処理により、第1の酸化物半導体膜108に含まれる水素を脱離させ、絶縁性酸化膜である下地絶縁層101を供給源として第1の酸化物半導体膜108に酸素を供給する。第3の加熱処理の温度は、150以上基板100の歪み点(基板100がガラス基板以外の基板である場合には、基板100を変質させる温度)未満とし、好ましくは250以上450以下とし、更に好ましくは300以上450以下とする。また、第1の酸化物半導体膜108をCACC酸化物半導体膜とする場合には、基板100の温度は第1の酸化物半導体膜108の形成時よりも高い温度とすることが好ましい。

#### 【0081】

なお、ここで、第1の酸化物半導体膜108に供給された酸素は、少なくとも絶縁性酸化膜である下地絶縁層101と第1の酸化物半導体膜108の界面近傍に拡散する。

10

#### 【0082】

なお、第3の加熱処理は、不活性ガス雰囲気中で行うことが好ましい。

#### 【0083】

なお、第3の加熱処理により、第1の酸化物半導体膜108に含まれる水素を脱離させ、絶縁性酸化膜である下地絶縁層101を供給源として第1の酸化物半導体膜108(膜中及び界面近傍の少なくともいずれか一方)に酸素を供給することができる。そのため、第1の酸化物半導体膜108(膜中及び界面近傍の少なくともいずれか一方)の欠陥(酸素欠損)を少なくすることができる。

#### 【0084】

このように、第1の酸化物半導体膜108の加工前に第3の加熱処理を行うため、酸素を脱離させて欠陥(酸素欠損)を生成しやすい酸化物半導体層の側面を露出させず、酸化物半導体層に含まれる欠陥(酸素欠損)を低減することができる。

20

#### 【0085】

これは、例えばドライエッティングにおいてエッティングされた酸化物半導体膜(酸化物半導体層)の側面が塩素ラジカルまたはフッ素ラジカルなどを含むプラズマに曝されると、エッティングされた酸化物半導体膜(酸化物半導体層)の側面に露出する金属原子と塩素ラジカルまたはフッ素ラジカルなどが結合する。このとき、金属原子と塩素原子またはフッ素原子が結合して脱離するため、酸化物半導体層中に当該金属原子と結合していた酸素原子が活性となる。このように活性となった酸素原子は容易に反応し、脱離しやすい。そのため、酸化物半導体層の側面には欠陥(酸素欠損)を生じやすい。

30

#### 【0086】

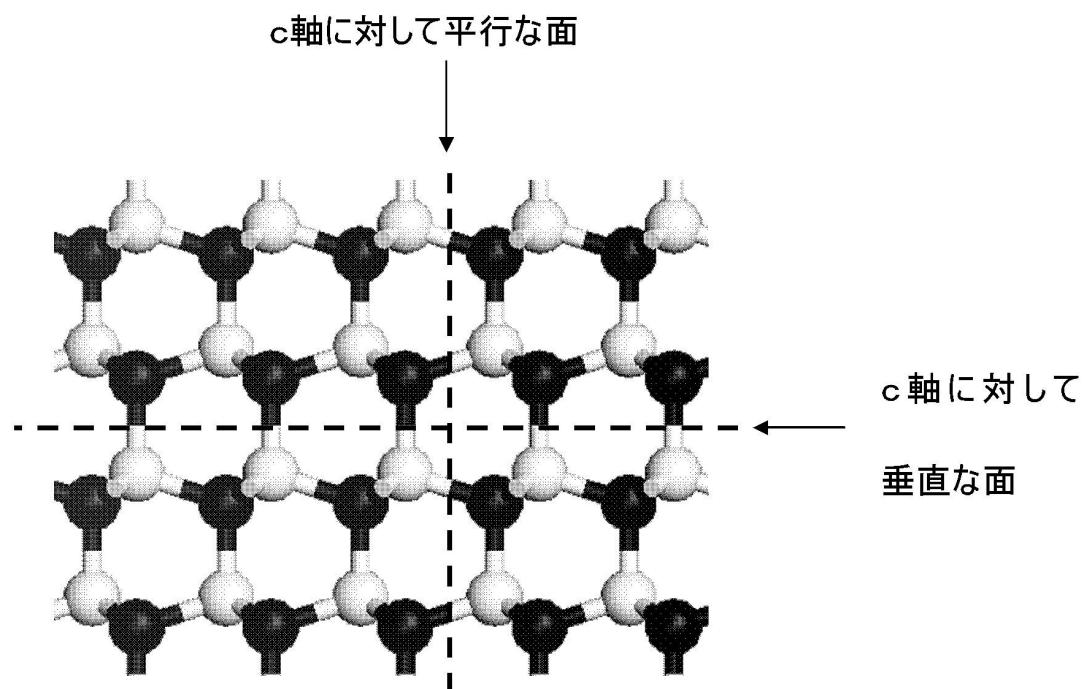

ここで、酸化物半導体膜の表面と側面における酸素の欠損しやすさについて、以下のモデルを用いて計算を行い検証した結果について説明する。なお、CACC酸化物半導体は、一側面に複数の結晶面を有することから計算が複雑になる。そのため、ここではc軸に配向したウルツ鉱構造であるZnO単結晶を用いて計算を行った。結晶のモデルとしては、図21に示すように、c軸に平行な面と垂直な面でそれぞれ切断し、(001)表面、(100)表面、及び(110)表面を用いた。

#### 【0087】

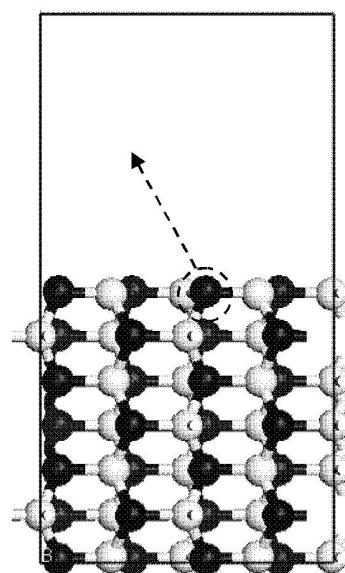

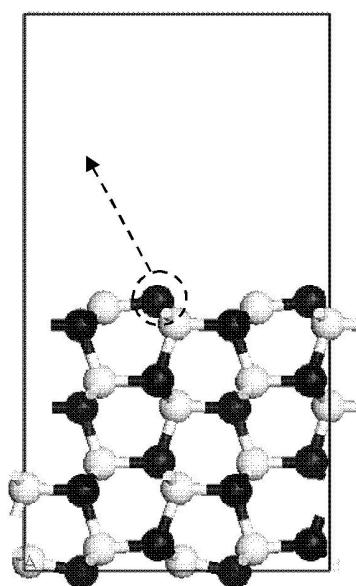

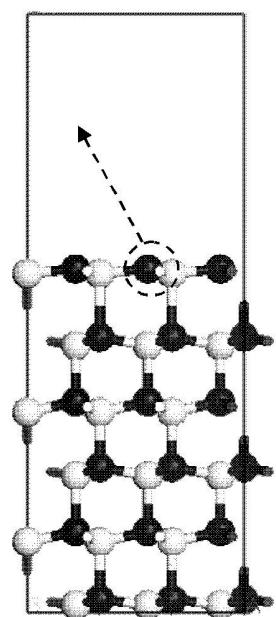

表面構造を作製した後、図22(A)乃至図22(C)に示すように(100)表面、(110)表面及び(001)表面から酸素が抜ける場合の計算を行い、その抜けやすさを各表面で比較した。

40

#### 【0088】

まず、(001)面が表面になるように切断したモデルを用いた。ただし、計算は3次元周期構造で行うため、(001)表面が2つ存在する真空領域の厚さが1nmのスラブモデルを用いた。同様にして、側面は(001)面と垂直な面と想定されるため、側面の一例として(100)面と(110)面が表面に出たスラブモデルを用いた。この2つの面を計算することで、(001)に垂直な面における酸素の抜けやすさの傾向を見ることができる。この場合も真空領域の厚さは1nmである。原子数は(100)表面モデル、(110)表面モデル、(001)表面モデルでそれぞれ、64、108、108原子と

50

した。また、前記 3 構造の表面から酸素を抜いた構造を用いた。

【0089】

計算には密度汎関数法のプログラムである C A S T E P を用いた。密度汎関数の方法として平面波基底擬ポテンシャル法を用い、汎関数は G G A P B E を用いた。始めにウルツ構造の 4 原子のユニットセルにおいて、格子定数を含めた構造最適化を行った。次に、最適化された構造をもとにして、表面構造を決定した。その後、作製した表面構造の酸素が欠損有りの構造と欠損無しの構造において、格子定数を固定した構造最適化を行った。エネルギーは構造最適化後のものを使用している。

【0090】

カットオフエネルギーとして、ユニットセルの計算では 380 eV、表面構造の計算では 300 eV を用いた。k 点として、ユニットセルの計算では  $9 \times 9 \times 6$ 、(100) 表面モデルの計算では  $3 \times 2 \times 1$ 、(110) 表面モデルの計算では  $1 \times 2 \times 2$ 、(001) 表面モデルの計算では  $2 \times 2 \times 1$  を用いた。

【0091】

上記の表面構造に、酸素欠損有りの構造のエネルギーと酸素分子のエネルギーの半分を足した値から、酸素欠損無しの構造のエネルギーを引いたエネルギー差（ここでは、束縛エネルギーと表記する。）を計算した。束縛エネルギーの小さい表面で酸素が抜けやすいといえる。

【0092】

【数 2】

$$\begin{aligned}

\text{(束縛エネルギー)} &= \text{(酸素欠損有りの構造のエネルギー)} \\

&+ \text{(酸素分子のエネルギーの半分)} \\

&- \text{(酸素欠損無しの構造のエネルギー)}

\end{aligned}$$

【0093】

前記式 2 により得られた各表面の束縛エネルギーを表 1 に示す。

【0094】

【表 1】

|             | 束縛エネルギー |

|-------------|---------|

| (100) 表面モデル | 2.89    |

| (110) 表面モデル | 2.64    |

| (001) 表面モデル | 3.38    |

【0095】

表 1 に示す結果より、(001) 表面と比べ、(100) 表面及び(110) 表面は束縛エネルギーが小さく、酸素が抜けやすいといえる。即ち、表面に垂直な方向に c 軸を有し、該 c 軸に配向した ZnO 膜は表面よりも側面の方が、酸素が抜けやすいことが分かる。CAC 酸化物半導体である ZnO についても、様々な結晶面が混ざり合っているが、ZnO 単結晶と同種の結晶面を側面に有している。そのため、ZnO 単結晶における酸素の抜けやすさと同様の傾向があるといえる。

【0096】

なお、このように第 1 の酸化物半導体膜 108 に第 3 の加熱処理を施すと、第 3 の加熱処理を施す前の第 1 の酸化物半導体膜 108 とは大きく異なるものとなるため、第 3 の加熱処理を施した後のものを第 2 の酸化物半導体膜 109 と表記する。

【0097】

次に、第 2 の酸化物半導体膜 109 上に第 2 のエッチングマスク 110 を形成する（図 2 (A)）。

【0098】

10

20

30

40

50

第2のエッティングマスク110は、レジスト材料により形成すればよい。ただし、これに限定されず、第2の酸化物半導体膜109を加工する際にマスクとして機能するものであればよい。

【0099】

次に、第2のエッティングマスク110を用いて第2の酸化物半導体膜109を加工することで、第1の酸化物半導体層112を形成する(図2(B))。

【0100】

なお、ここで、加工は、ドライエッティングにより行えばよい。ドライエッティングに用いるエッティングガスとしては、例えば塩素ガス、または三塩化ホウ素ガスと塩素ガスの混合ガスを用いればよい。ただし、これに限定されず、ウェットエッティングを用いてもよいし、第2の酸化物半導体膜109を加工することができる他の手段を用いてもよい。

10

【0101】

次に、第2のエッティングマスク110を除去する(図2(C))。

【0102】

なお、第2のエッティングマスク110がレジスト材料により形成されている場合には、第2のエッティングマスク110をアッシングのみで除去してもよい。

【0103】

その後、少なくとも第1の酸化物半導体層112を覆ってサイドウォール絶縁膜113を形成する(図3(A))。

【0104】

20

サイドウォール絶縁膜113は、下地絶縁層101と同様の方法及び同様の材料により形成することが好ましい。

【0105】

従って、サイドウォール絶縁膜113は、少なくとも第1の酸化物半導体層112と接する面に酸素を含み、該酸素の一部が加熱処理により脱離する絶縁性酸化物により形成する。酸素の一部が加熱処理により脱離する絶縁性酸化物としては、化学量論比よりも多くの酸素を含むものを用いることが好ましい。これは、加熱処理により、下地絶縁層101に接する酸化物半導体膜(または層)に酸素を拡散させることができるためである。

【0106】

なお、ここで第4の加熱処理を行うとよい。第4の加熱処理により、絶縁性酸化膜であるサイドウォール絶縁膜113を供給源として、第1の酸化物半導体層112に酸素が供給される。第4の加熱処理の温度は、150以上450以下とし、好ましくは250

30

以上325以下とする。第4の加熱処理は、前記温度まで徐々に温度を上昇させて行ってもよいし、前記温度まで段階的に温度を上昇させてもよい。第4の加熱処理は、酸化性雰囲気または不活性雰囲気で行えばよいが、これらに限定されるものではない。また、第4の加熱処理は減圧下で行ってもよい。

【0107】

次に、サイドウォール絶縁膜113上に第3のエッティングマスク115を形成し、第3のエッティングマスク115を用いてサイドウォール絶縁膜113を加工することで、少なくとも第1の酸化物半導体層112の側壁を覆うサイドウォール絶縁層113SWを形成する(図3(B))。その後、第3のエッティングマスクを除去する。

40

【0108】

次に、少なくとも第1の酸化物半導体層112上に第1の絶縁層114を形成する。ここでは、第1の酸化物半導体層112及びサイドウォール絶縁層113SWを覆って第1の絶縁層114を形成する(図3(C))。

【0109】

第1の絶縁層114は、少なくとも第1の酸化物半導体層112に接する部分に酸素を含み、該酸素の一部が加熱により脱離する絶縁性酸化物により形成することが好ましい。すなわち、下地絶縁層101の材料として例示列挙したものを用いることが好ましい。第1の絶縁層114の第1の酸化物半導体層112と接する部分を酸化シリコンにより形成

50

すると、第1の酸化物半導体層112に酸素を拡散させることができ、トランジスタの低抵抗化を防止することができる。

【0110】

なお、第1の絶縁層114として、ハフニウムシリケート( $HfSiO_x$ )、窒素が添加されたハフニウムシリケート( $HfSi_xO_yN_z$ )、窒素が添加されたハフニウムアルミネート( $HfAl_xO_yN_z$ )、酸化ハフニウム、酸化イットリウムなどの $hig h-k$ 材料を用いると、ゲートリーク電流を低減することができる。ここで、ゲートリーク電流とは、ゲート電極とソース電極またはドレイン電極の間に流れるリーク電流をいう。更には、前記 $hig h-k$ 材料により形成される層と、酸化シリコン、酸化窒化シリコン、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化窒化アルミニウム及び酸化ガリウムにより形成される層を積層してもよい。ただし、第1の絶縁層114を積層構造とする場合であっても、第1の酸化物半導体層112に接する部分は、絶縁性酸化物であることが好ましい。10

【0111】

第1の絶縁層114は、スパッタリング法により形成すればよい。また、第1の絶縁層114の厚さは、1nm以上300nm以下、好ましくは5nm以上50nm以下とするとい。第1の絶縁層114の厚さを5nm以上とすると、ゲートリーク電流を特に小さくすることができる。

【0112】

なお、第1の絶縁層114を形成する前に、第1の酸化物半導体層112の表面を酸化性ガスのプラズマに曝して第1の酸化物半導体層112の表面の欠陥(酸素欠損)を少なくすることができる。20

【0113】

第1の絶縁層114は、少なくともゲート絶縁層を構成する。

【0114】

なお、ここで第5の加熱処理を行ってもよい。第5の加熱処理により、絶縁性酸化膜である第2の絶縁層122を供給源として、第2の酸化物半導体層124に酸素が供給されてもよい。第5の加熱処理の温度は、150以上450以下とし、好ましくは250以上325以下とする。第5の加熱処理は、前記温度まで徐々に温度を上昇させて行ってもよいし、前記温度まで段階的に温度を上昇させてもよい。第5の加熱処理は、酸化性雰囲気または不活性雰囲気で行えばよいが、これらに限定されるものではない。また、第5の加熱処理は減圧下で行ってもよい。30

【0115】

次に、第1の絶縁層114上に第2の導電膜116を形成する(図4(A))。

【0116】

第2の導電膜116は、第1の導電膜102と同様の材料及び同様の方法により形成すればよい。

【0117】

なお、第2の導電膜116を銅により形成すると、第2の導電膜116を加工して形成される配線を低抵抗にすることができるため、好ましい。ここで、第2の導電膜116が積層構造である場合には、第2の導電膜116のうち少なくとも一層が銅により形成されなければよい。40

【0118】

次に、第2の導電膜116上に第4のエッチングマスク118を形成する(図4(B))。

【0119】

第4のエッチングマスク118は、レジスト材料により形成すればよい。ただし、これに限定されず、第2の導電膜116を加工する際にマスクとして機能するものであればよい。

【0120】

次に、第4のエッティングマスク118を用いて第2の導電膜116を加工することで第2の導電層120を形成する(図4(C))。

【0121】

なお、ここで、加工は、ドライエッティングにより行えばよい。ドライエッティングに用いるエッティングガスとしては、例えば塩素ガス、または三塩化ホウ素ガスと塩素ガスの混合ガスを用いればよい。ただし、これに限定されず、ウエットエッティングを用いてもよいし、第2の導電膜116を加工することができる他の手段を用いてもよい。

【0122】

第2の導電層120は、少なくともゲート電極を構成する。

【0123】

なお、第1の絶縁層114と第2の導電層120の間に、In-Ga-Zn-O系金属酸化物によりバッファ層が設けられていることが好ましい。第1の絶縁層114と第2の導電層120の間に、In-Ga-Zn-O系金属酸化物によりバッファ層が設けられていることで、しきい値電圧をプラス側にシフトさせることができる。

【0124】

次に、第4のエッティングマスク118を除去し、第2の導電層120をマスクとして、第1の酸化物半導体層112にドーパントを添加してソース領域及びドレイン領域を有する第2の酸化物半導体層124を形成する(図5(A))。第2の酸化物半導体層124は、ソース領域及びドレイン領域の一方である領域124Aと、チャネル形成領域となる領域124Bと、ソース領域及びドレイン領域の他方である領域124Cと、高抵抗な領域124Dと、を有する。

【0125】

なお、第2の酸化物半導体層124において、サイドウォール絶縁層113SWと重畠する領域124Dにはドーパントが添加されない。領域124Dは、領域124Bと同様、低抵抗化されず、高抵抗領域となる。また、第2の酸化物半導体層124の周辺領域にサイドウォール絶縁層113SWが設けられることで、第2の酸化物半導体層124の領域124D(側壁部を含む。)における欠陥(酸素欠損)の生成を防止し、当該高抵抗領域を維持することができる。これにより、第2の酸化物半導体層124の領域124D(側壁部を含む。)が低抵抗化して、ソース領域とドレイン領域がゲート電圧によらず導通してしまうことを防ぐことができる。

【0126】

なお、第4のエッティングマスク118がレジスト材料により形成されている場合には、第4のエッティングマスク118をアッシングのみで除去してもよい。

【0127】

なお、ここで、ドーパントの添加は、イオンインプランテーション法またはイオンドーピング法により行えばよい。または、ドーパントを含むガス雰囲気中でプラズマ処理を行うことでドーパントの添加を行ってもよい。また、添加するドーパントとしては、水素、希ガス、窒素、リンまたはヒ素などを用いればよい。

【0128】

次に、第1の絶縁層114上及び第2の導電層120を覆って第2の絶縁層122を形成する(図5(B))。

【0129】

第2の絶縁層122は、下地絶縁層101及び第1の絶縁層114と同様の材料及び同様の方法により形成すればよく、絶縁性酸化膜であることが好ましい。

【0130】

第2の絶縁層122は、少なくともパッシベーション膜(保護絶縁層)として機能する。なお、第2の絶縁層122は設けられていなくてもよい。

【0131】

次に、基板100に対して第6の加熱処理を行って第3の酸化物半導体層126を形成する。第3の酸化物半導体層126は、ソース領域及びドレイン領域の一方である領域1

10

20

30

40

50

26Aと、チャネル形成領域となる領域126Bと、ソース領域及びドレイン領域の他方である領域126Cと、を有する(図5(C))。

【0132】

なお、ここで行う第6の加熱処理により、絶縁性酸化膜である第2の絶縁層122を供給源として、第2の酸化物半導体層124に酸素が供給されてもよい。第6の加熱処理の温度は、150以上450以下とし、好ましくは250以上325以下とする。第6の加熱処理は、前記温度まで徐々に温度を上昇させて行ってもよいし、前記温度まで段階的に温度を上昇させててもよい。

【0133】

なお、第6の加熱処理は、不活性ガス雰囲気中で行うことが好ましい。

10

【0134】

なお、第6の加熱処理が施された後の第3の酸化物半導体層126の水素濃度は、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、更に好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下、更に好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以下であるとよい。

【0135】

なお、第6の加熱処理が施された後の第3の酸化物半導体層126の窒素濃度は、領域126A及び領域126Cでは、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{22}$  atoms/cm<sup>3</sup>以下であるとよく、領域126Bでは、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満であるとよい。

20

【0136】

以上説明したように、トランジスタを作製することができる。本実施の形態のトランジスタの作製方法によれば、酸化物半導体層(特に、側壁)の低抵抗化を防止し、トランジスタに設けられる酸化物半導体層の欠陥(酸素欠損)を少なくすることができる。

【0137】

なお、本実施の形態にて作製したトランジスタの完成図の一例を図6に示す。図6(A)は、図6(B)のX1-Y1における断面図を示し、図6(C)は、図6(B)のX2-Y2における断面図を示す。

【0138】

図6に示すトランジスタでは、基板100上に第1の導電層106によりソース電極及びドレイン電極が設けられ、該ソース電極と該ドレイン電極の間には第3の酸化物半導体層126が設けられ、第3の酸化物半導体層の側壁にはサイドウォール絶縁層113SWが設けられ、第3の酸化物半導体層126及び前記サイドウォール絶縁層113SWを覆つて第1の絶縁層114によりゲート絶縁層が設けられ、第1の絶縁層114上のチャネル形成領域となる領域126Bと重畳する部分に第2の導電層120によりゲート電極が設けられ、第1の絶縁層114及び第2の導電層120上には第2の絶縁層122が設けられている。すなわち、図6に示すトランジスタはTGC構造である。図6に示すトランジスタはオフ電流がきわめて小さいトランジスタとすることができる。

30

【0139】

なお、図6に示すように、第3の酸化物半導体層126において、サイドウォール絶縁層113SWと重畳する領域126Dにはドーパントが添加されていない。領域126Dは、領域124Bと同様、低抵抗化されず、高抵抗な状態が維持されている。また、第3の酸化物半導体層126の領域126D(側壁部を含む。)にサイドウォール絶縁層113SWが設けられることで、第3の酸化物半導体層126の領域126Dにおける欠陥(酸素欠損)の生成を防止し、当該高抵抗領域を維持することができる。これにより、第3の酸化物半導体層126の領域126D(側壁部を含む。)が低抵抗化して、ソース領域とドレイン領域がゲート電圧によらず導通してしまうことを防ぐことができる。

40

【0140】

(実施の形態2)

本実施の形態では、実施の形態1で説明したトランジスタの応用例について説明する。

50

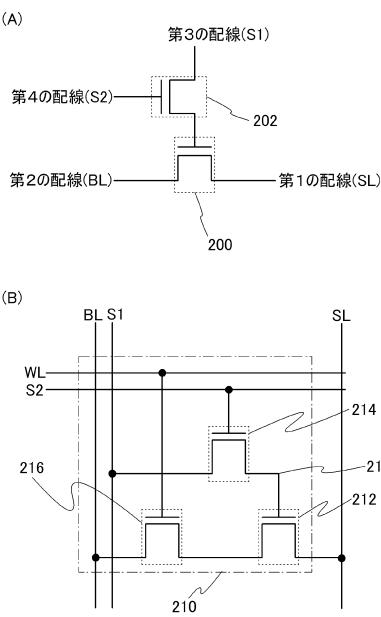

## 【0141】

図7(A)は、半導体装置を構成する記憶素子(以下、メモリセルと表記する。)の回路図の一例を示す。図7(A)に示すメモリセルは、酸化物半導体以外の材料(例えば、シリコン、ゲルマニウム、炭化シリコン、ガリウムヒ素、窒化ガリウムまたは有機化合物など)をチャネル形成領域に用いたトランジスタ200と酸化物半導体をチャネル形成領域に用いたトランジスタ202を有する。

## 【0142】

酸化物半導体をチャネル形成領域に用いたトランジスタ202は、実施の形態1にて説明した本発明の一態様である半導体装置の作製方法を適用して作製したものである。

## 【0143】

図7(A)に示すように、トランジスタ200のゲートと、トランジスタ202のソース及びドレインの一方は、電気的に接続されている。また、第1の配線S<sub>L</sub>(1<sub>s</sub>t L<sub>i</sub>ne:ソース線)と、トランジスタ200のソースは、電気的に接続されている。第2の配線B<sub>L</sub>(2<sub>n</sub>d L<sub>i</sub>ne:ビット線)と、トランジスタ200のドレインは、電気的に接続されている。そして、第3の配線S<sub>1</sub>(3<sub>r</sub>d L<sub>i</sub>ne:第1信号線)と、トランジスタ202のソース及びドレインの他方は、電気的に接続されている。第4の配線S<sub>2</sub>(4<sub>t</sub>h L<sub>i</sub>ne:第2信号線とも呼ぶ。)と、トランジスタ202のゲートは、電気的に接続されている。

## 【0144】

酸化物半導体以外の材料として、例えば単結晶シリコンをチャネル形成領域に用いたトランジスタ200は十分な高速動作が可能なため、トランジスタ200を用いることにより、記憶内容の読み出しなどを高速に行うことが可能である。また、酸化物半導体をチャネル形成領域に用いたトランジスタ202は、オフ電流が小さい。このため、トランジスタ202をオフ状態とすることで、トランジスタ200のゲートの電位を極めて長時間にわたって保持することが可能である。

## 【0145】

ゲートの電位を極めて長時間にわたって保持することが可能という特徴を活かして、次のように、情報の書き込み、保持及び読み出しが可能である。

## 【0146】

はじめに、情報の書き込み及び保持について説明する。まず、第4の配線S<sub>2</sub>の電位を、トランジスタ202がオン状態となる電位として、トランジスタ202をオン状態とする。これにより、第3の配線S<sub>1</sub>の電位が、トランジスタ200のゲートに与えられる(書き込み)。その後、第4の配線S<sub>2</sub>の電位を、トランジスタ202がオフ状態となる電位としてトランジスタ202をオフ状態とすることにより、トランジスタ200のゲートの電位が保持される(保持)。

## 【0147】

トランジスタ202のオフ電流は小さいので、トランジスタ200のゲートの電位は長時間にわたって保持される。例えば、トランジスタ200のゲートの電位がトランジスタ200をオン状態とする電位であれば、トランジスタ200のオン状態が長時間にわたって保持されることになる。また、トランジスタ200のゲートの電位がトランジスタ200をオフ状態とする電位であれば、トランジスタ200のオフ状態が長時間にわたって保持される。

## 【0148】

次に、情報の読み出しについて説明する。トランジスタ200のオン状態またはオフ状態が保持された状態において、第1の配線S<sub>L</sub>に所定の電位(定電位)が与えられると、トランジスタ200のオン状態またはオフ状態に応じて、第2の配線B<sub>L</sub>の電位は異なる値をとる。例えば、トランジスタ200がオン状態の場合には、第2の配線B<sub>L</sub>の電位が第1の配線S<sub>L</sub>の電位に近いものとなる。また、トランジスタ200がオフ状態の場合には、第2の配線B<sub>L</sub>の電位は変化しない。

## 【0149】

10

20

30

40

50

このように、情報が保持された状態において、第2の配線B Lの電位と、所定の電位とを比較することで、情報を読み出すことができる。

【0150】

次に、情報の書き換えについて説明する。情報の書き換えは、情報の書き込み及び保持と同様に行われる。つまり、第4の配線S 2の電位を、トランジスタ2 0 2がオン状態となる電位として、トランジスタ2 0 2をオン状態とする。これにより、第3の配線S 1の電位（新たな情報に係る電位）が、トランジスタ2 0 0のゲートに与えられる。その後、第4の配線S 2の電位をトランジスタ2 0 2がオフ状態となる電位として、トランジスタ2 0 2をオフ状態とすることにより、新たな情報が保持される。

【0151】

このように、本実施の形態のメモリセルは、再度の情報の書き込みによって直接的に情報を書き換えることが可能である。このためフラッシュメモリなどにおいて必要とされる消去動作が不要であり、消去動作に起因する動作速度の低下を抑制することができる。つまり、メモリセルを有する半導体装置の高速動作が実現される。

【0152】

図7（B）は、図7（A）のメモリセルを変形させた回路図の一例を示す。

【0153】

図7（B）に示すメモリセル2 1 0は、第1の配線S L（ソース線）と、第2の配線B L（ビット線）と、第3の配線S 1（第1信号線）と、第4の配線S 2（第2信号線）と、第5の配線W L（ワード線）と、トランジスタ2 1 2（第1のトランジスタ）と、トランジスタ2 1 4（第2のトランジスタ）と、トランジスタ2 1 6（第3のトランジスタ）と、から構成されている。トランジスタ2 1 2及びトランジスタ2 1 6は、酸化物半導体以外の材料をチャネル形成領域に用いており、トランジスタ2 1 4は酸化物半導体をチャネル形成領域に用いている。

【0154】

ここで、トランジスタ2 1 2のゲートと、トランジスタ2 1 4のソース及びドレインの一方は、電気的に接続されている。また、第1の配線S Lと、トランジスタ2 1 2のソースは電気的に接続されている。トランジスタ2 1 2のドレインと、トランジスタ2 1 6のソースは、電気的に接続されている。そして、第2の配線B Lと、トランジスタ2 1 6のドレインは、電気的に接続されている。第3の配線S 1と、トランジスタ2 1 4のソース及びドレインの他方は、電気的に接続されている。第4の配線S 2と、トランジスタ2 1 4のゲートは、電気的に接続されている。第5の配線W Lと、トランジスタ2 1 6のゲートは、電気的に接続されている。

【0155】

次に、回路の具体的な動作の一例について説明する。なお、以下の説明で使用する電位、電圧などの数値は適宜変更してもよい。

【0156】

メモリセル2 1 0に書き込みを行う場合には、第1の配線S Lを0 Vとし、第5の配線W Lを0 Vとし、第2の配線B Lを0 Vとし、第4の配線S 2を2 Vとする。データ”1”を書き込む場合には第3の配線S 1を2 Vとし、データ”0”を書き込む場合には第3の配線S 1を0 Vとする。このとき、トランジスタ2 1 6はオフ状態、トランジスタ2 1 4はオン状態となる。なお、書き込み終了時には、第3の配線S 1の電位を変化させる前に、第4の配線S 2を0 Vとして、トランジスタ2 1 4をオフ状態にする。

【0157】

その結果、データ”1”書き込み後にはトランジスタ2 1 2のゲートに電気的に接続されたノード（以下、ノード2 1 8）の電位が約2 Vとなり、データ”0”書き込み後にはノード2 1 8の電位が約0 Vとなる。ノード2 1 8には、第3の配線S 1の電位に応じた電荷が蓄積されるが、トランジスタ2 1 4のオフ電流は小さいため、トランジスタ2 1 2のゲートの電位は長時間にわたって保持される。

【0158】

10

20

30

40

50

次に、メモリセルの読み出しを行う場合には、第1の配線 S L を 0 V とし、第5の配線 W L を 2 V とし、第4の配線 S 2 を 0 V とし、第3の配線 S 1 を 0 V とし、第2の配線 B L に電気的に接続された読み出し回路を動作状態とする。このとき、トランジスタ 216 はオン状態、トランジスタ 214 はオフ状態となる。

【0159】

データ "0" (ノード 218 が約 0 V の状態) であればトランジスタ 212 はオフ状態であるから、第2の配線 B L と第1の配線 S L 間の抵抗は高い。一方で、データ "1" (ノード 218 が約 2 V の状態) であればトランジスタ 212 がオン状態であるから、第2の配線 B L と第1の配線 S L 間の抵抗は低い。読み出し回路は、メモリセルの抵抗状態の違いから、データ "0", "1" を読み出すことができる。なお、書き込み時の第2の配線 B L は 0 V としたが、フローティング状態や 0 V 以上の電位であってもよい。読み出し時の第3の配線 S 1 は 0 V としたが、フローティング状態や 0 V 以上の電位に充電されてもよい。

【0160】

なお、データ "1" とデータ "0" は便宜上の定義であって、逆であってもよい。動作電圧は、データ "0" の場合にトランジスタ 212 がオフ状態となり、データ "1" の場合にトランジスタ 212 がオン状態となるように、また、書き込み時にトランジスタ 214 がオン状態、書き込み時以外にはオフ状態となるように、また、読み出し時にトランジスタ 216 がオン状態となるように設定すればよい。

【0161】

本実施の形態では、便宜上、最小記憶単位 (1 ビット) のメモリセルについて説明したが、メモリセルの構成はこれに限定されず、前記メモリセルを複数組み合わせてもよい。例えば、前記メモリセルを複数組み合わせて、NAND 型メモリセル及び NOR 型メモリセルを構成することができる。

【0162】

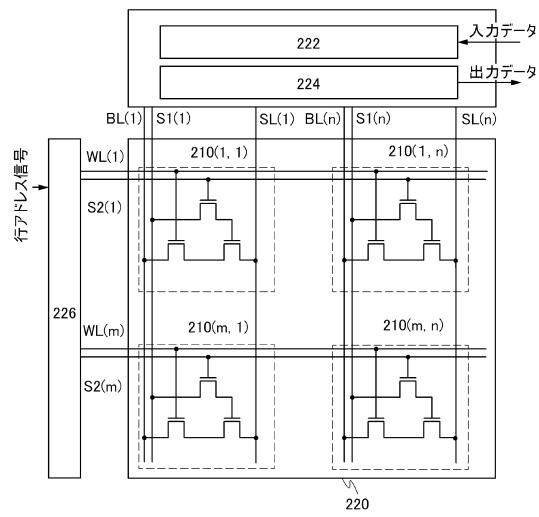

図 8 は、 $m \times n$  ビットの記憶容量を有する本発明の一態様に係る半導体装置のブロック回路図を示す。

【0163】

図 8 に示す半導体装置は、メモリセルアレイ 220 と、第2の配線 B L 及び第3の配線 S 1 が電気的に接続された駆動回路 222 と、読み出し回路 224 と、第4の配線 S 2 及び第5の配線 W L が電気的に接続された駆動回路 226 と、を有する。メモリセルアレイ 220 は、 $m$  本の第5の配線 W L 及び  $m$  本の第4の配線 S 2 と、 $n$  本の第2の配線 B L 及び  $n$  本の第3の配線 S 1 と、マトリクス状に配置された縦  $m$  個 (行) × 横  $n$  個 (列) ( $m$ 、 $n$  は自然数) のメモリセル 210 と、を有する。なお、これらの他にリフレッシュ回路などが設けられていてもよい。

【0164】

各メモリセルの代表として、メモリセル 210 ( $i, j$ ) に注目して説明する。ここで、メモリセル 210 ( $i, j$ ) ( $i$  は 1 以上  $m$  以下の整数、 $j$  は 1 以上  $n$  以下の整数) は、第2の配線 B L ( $j$ )、第3の配線 S 1 ( $j$ )、第5の配線 W L ( $i$ )、第4の配線 S 2 ( $i$ ) 及び第1の配線 S L ( $j$ ) にそれぞれ電気的に接続されている。第1の配線 S L ( $j$ ) には電位  $V_s$  が与えられている。また、第2の配線 B L (1) ~ B L ( $n$ ) 及び第3の配線 S 1 (1) ~ S 1 ( $n$ ) は、駆動回路 222 及び読み出し回路 224 にそれぞれ電気的に接続されている。第5の配線 W L (1) ~ W L ( $m$ ) 及び第4の配線 S 2 (1) ~ S 2 ( $m$ ) は、駆動回路 226 にそれぞれ電気的に接続されている。

【0165】

図 8 に示した半導体装置の動作について説明する。ここでは、行ごとの書き込み及び読み出しを行う。

【0166】

第  $i$  行のメモリセル 210 ( $i, 1$ ) ~ 210 ( $i, n$ ) に書き込みを行う場合には、第1の配線 S L (1) ~ S L ( $n$ ) の電位  $V_s$  を 0 V とし、第5の配線 W L ( $i$ ) を 0 V

10

20

30

40

50

とし、第2の配線B L (1) ~ B L (n)を0 Vとし、第4の配線S 2 (i)を2 Vとする。このときトランジスタ2 1 4は、オン状態となる。第3の配線S 1 (1) ~ S 1 (n)は、データ”1”を書き込む列は2 Vとし、データ”0”を書き込む列は0 Vとする。なお、書き込み終了にあたっては、第3の配線S 1 (1) ~ S 1 (n)の電位を変化させる前に、第4の配線S 2 (i)を0 Vとして、トランジスタ2 1 4をオフ状態にする。また、第5の配線W L (i)以外の第5の配線W Lも0 Vとし、第4の配線S 2 (i)以外の第4の配線S 2 は0 Vとする。

#### 【0167】

その結果、データ”1”の書き込みを行ったメモリセルのトランジスタ2 1 2のゲートに接続されたノード2 1 8の電位は約2 Vとなり、データ”0”の書き込みを行ったメモリセルのノード2 1 8の電位は約0 Vとなる。また、非選択メモリセルのノード2 1 8の電位は変わらない。

#### 【0168】

第1行のメモリセル2 1 0 (i, 1) ~ 2 1 0 (i, n)の読み出しを行う場合には、第1の配線S L (1) ~ S L (n)の電位V sを0 Vとし、第5の配線W L (i)を2 Vとし、第4の配線S 2 (i)を0 Vとし、第3の配線S 1 (1) ~ S 1 (n)を0 Vとし、第2の配線B L (1) ~ B L (n)に接続された読み出し回路2 2 4を動作状態とする。読み出し回路2 2 4では、例えば、メモリセルの抵抗状態の違いから、データ”0”, ”1”を読み出すことができる。なお、第5の配線W L (i)以外の第5の配線W Lも0 Vとし、第4の配線S 2 (i)以外の第4の配線S 2 は0 Vとする。なお、書き込み時の第2の配線B Lは0 Vとしたが、フローティング状態や0 V以上の電位であってもよい。読み出し時の第3の配線S 1 は0 Vとしたが、フローティング状態や0 V以上の電位であってもよい。

#### 【0169】

なお、本実施の形態において、電位の数値として使用した値は、接地電位を0 Vとして算出される値である。

#### 【0170】

本実施の形態にて説明したように、実施の形態1を適用したトランジスタ（酸化物半導体をチャネル領域に用いたトランジスタ）のソースまたはドレインと接続されたノードの電位を極めて長時間にわたって保持することが可能であるため、小さい消費電力にて、情報の書き込み、保持、読み出しが可能なメモリセルを作製することができる。

#### 【0171】

##### （実施の形態3）

本実施の形態では、実施の形態1で説明したトランジスタの応用例であって実施の形態2とは異なるものについて説明する。

#### 【0172】

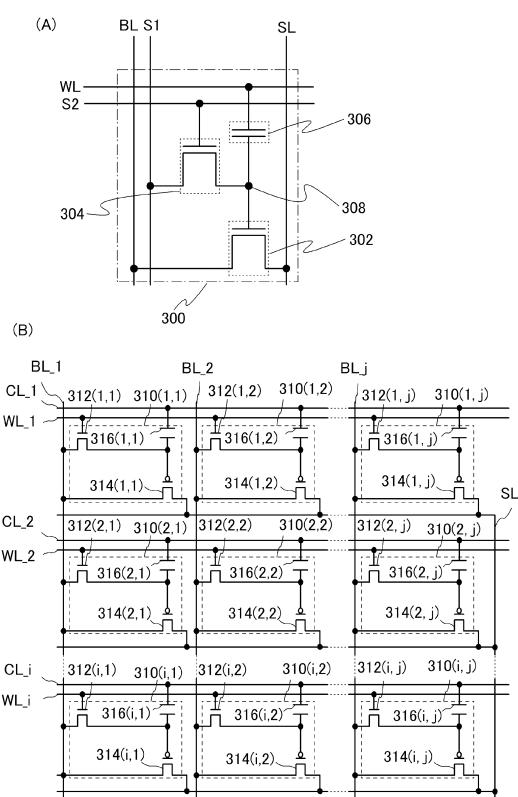

本実施の形態では、容量素子を有するメモリセル及び半導体記憶装置について説明する。図9 (A)に示すメモリセル3 0 0は、第1の配線S Lと、第2の配線B Lと、第3の配線S 1と、第4の配線S 2と、第5の配線W Lと、トランジスタ3 0 2（第1のトランジスタ）と、トランジスタ3 0 4（第2のトランジスタ）と、容量素子3 0 6と、を有する。トランジスタ3 0 2は、酸化物半導体以外の材料をチャネル形成領域に用いており、トランジスタ3 0 4はチャネル形成領域に酸化物半導体を用いている。

#### 【0173】

酸化物半導体をチャネル形成領域に用いたトランジスタ3 0 4は、実施の形態1にて説明した本発明の一態様である半導体装置の作製方法を適用して作製したものである。

#### 【0174】

ここで、トランジスタ3 0 2のゲートと、トランジスタ3 0 4のソース及びドレインの一方と、容量素子3 0 6の一方の電極は、電気的に接続されている。また、第1の配線S Lと、トランジスタ3 0 2のソースは、電気的に接続されている。第2の配線B Lと、トランジスタ3 0 2のドレインは、電気的に接続されている。第3の配線S 1と、トランジ

10

20

30

40

50

スタ304のソース及びドレインの他方は、電気的に接続されている。第4の配線S2と、トランジスタ304のゲートは、電気的に接続されている。第5の配線WLと、容量素子306の他方の電極は、電気的に接続されている。

【0175】

次に、回路の具体的な動作の一例について説明する。なお、以下の説明で使用する電位、電圧などの数値は適宜変更してもよい。

【0176】

メモリセル300に書き込みを行う場合には第1の配線SLを0Vとし、第5の配線WLを0Vとし、第2の配線BLを0Vとし、第4の配線S2を2Vとする。データ"1"を書き込む場合には第3の配線S1を2Vとし、データ"0"を書き込む場合には第3の配線S1を0Vとする。このとき、トランジスタ304はオン状態となる。なお、書き込み終了時には、第3の配線S1の電位を変化させる前に、第4の配線S2を0Vとして、トランジスタ304をオフ状態にする。

【0177】

その結果、データ"1"の書き込み後にはトランジスタ302のゲートに電気的に接続されたノード308の電位が約2Vとなり、データ"0"の書き込み後にはノード308の電位が約0Vとなる。

【0178】

メモリセル300の読み出しを行う場合には、第1の配線SLを0Vとし、第5の配線WLを2Vとし、第4の配線S2を0Vとし、第3の配線S1を0Vとし、第2の配線BLに電気的に接続された読み出し回路を動作状態とする。このとき、トランジスタ304は、オフ状態となる。

【0179】

第5の配線WLを2Vとした場合のトランジスタ302の状態について説明する。トランジスタ302の状態を決めるノード308の電位は、第5の配線WL - ノード308間の容量C1と、トランジスタ302のゲート - ソースとドレイン間の容量C2に依存する。

【0180】

なお、読み出し時の第3の配線S1は0Vとしたが、フローティング状態や0V以上としてもよい。データ"1"とデータ"0"は便宜上の定義であって、逆であってもよい。

【0181】

書き込み時の第3の配線S1の電位は、書き込み後にトランジスタ304がオフ状態となり、第5の配線WLの電位が0Vの場合にはトランジスタ302がオフ状態である範囲で、データ"0"、"1"の電位をそれぞれ選べばよい。読み出し時の第5の配線WLの電位は、データ"0"の場合にはトランジスタ302がオフ状態となり、データ"1"の場合にはトランジスタ302がオン状態となるようにすればよい。また、トランジスタ302のしきい値電圧は、トランジスタ302の状態を変えない範囲で適宜設定すればよい。

【0182】

次に、第1のゲート及び第2のゲートを有する選択トランジスタと、容量素子を有するメモリセルを用いるNOR型の半導体装置(半導体記憶装置)の一例について説明する。

【0183】

図9(B)に示すメモリセルアレイは、i行(iは3以上の自然数)j列(jは3以上の自然数)にマトリクス状に配列された複数のメモリセル310と、i本のワード線WL(ワード線WL\_1 ~ WL\_i)と、i本の容量線CL(容量線CL\_1 ~ CL\_i)と、i本のゲート線BGL(ゲート線BGL\_1 ~ BGL\_i)と、ソース線SLと、を有する。ここで、i及びjは便宜上3以上の自然数としているが、本実施の形態に示すメモリセルアレイの行数及び列数は、それぞれ3以上に限定されない。1行または1列のメモリセルアレイとしてもよいし、2行または2列のメモリセルアレイとしてもよい。

【0184】

更には、複数のメモリセル310のそれぞれ(メモリセル310(M, N))(ただし、

10

20

30

40

50

$N$  は 1 以上  $j$  以下の自然数、 $M$  は 1 以上  $i$  以下の自然数 ) ) は、トランジスタ 312 ( $M$ ,  $N$ ) と、容量素子 316 ( $M$ ,  $N$ ) と、トランジスタ 314 ( $M$ ,  $N$ ) と、を有する。

【0185】

なお、ここで、容量素子は、第 1 の容量電極、第 2 の容量電極及び該第 1 の容量電極と該第 2 の容量電極の間に設けられた誘電体層により構成されていればよい。容量素子は、第 1 の容量電極と第 2 の容量電極の間の電位差に応じて電荷が蓄積される。

【0186】

トランジスタ 312 ( $M$ ,  $N$ ) は、 $n$  チャネル型トランジスタであり、ソース、ドレイン及びゲートを有する。なお、本実施の形態の半導体装置（半導体記憶装置）において、必ずしもトランジスタ 312 を  $n$  チャネル型トランジスタにしなくてもよい。

10

【0187】

トランジスタ 312 ( $M$ ,  $N$ ) のソース及びドレインの一方は、ビット線  $B_L_N$  に電気的に接続され、トランジスタ 312 ( $M$ ,  $N$ ) のゲートは、ワード線  $W_L_M$  に電気的に接続されている。トランジスタ 312 ( $M$ ,  $N$ ) のソース及びドレインの一方がビット線  $B_L_N$  に電気的に接続された構成にすることにより、メモリセルごとに選択的にデータを読み出すことができる。

【0188】

トランジスタ 312 ( $M$ ,  $N$ ) は、メモリセル 310 ( $M$ ,  $N$ ) において選択トランジスタとしての機能を有する。

【0189】

トランジスタ 312 ( $M$ ,  $N$ ) としては、酸化物半導体をチャネル形成領域に用いたトランジスタを用いることができる。

20

【0190】

トランジスタ 314 ( $M$ ,  $N$ ) は、 $p$  チャネル型トランジスタである。なお、本実施の形態の半導体装置（半導体記憶装置）において、必ずしもトランジスタ 314 を  $p$  チャネル型トランジスタにしなくてもよい。

【0191】

トランジスタ 314 ( $M$ ,  $N$ ) のソース及びドレインの一方は、ソース線  $S_L$  に電気的に接続され、トランジスタ 314 ( $M$ ,  $N$ ) のソース及びドレインの他方は、ビット線  $B_L_N$  に電気的に接続され、トランジスタ 314 ( $M$ ,  $N$ ) のゲートは、トランジスタ 312 ( $M$ ,  $N$ ) のソース及びドレインの他方に電気的に接続されている。

30

【0192】

トランジスタ 314 ( $M$ ,  $N$ ) は、メモリセル 310 ( $M$ ,  $N$ ) において、出力トランジスタとしての機能を有する。トランジスタ 314 ( $M$ ,  $N$ ) としては、例えば単結晶シリコンをチャネル形成領域に用いるトランジスタを用いることができる。

【0193】

容量素子 316 ( $M$ ,  $N$ ) の第 1 の容量電極は、容量線  $C_L_M$  に電気的に接続され、容量素子 316 ( $M$ ,  $N$ ) の第 2 の容量電極は、トランジスタ 312 ( $M$ ,  $N$ ) のソース及びドレインの他方に電気的に接続されている。なお、容量素子 316 ( $M$ ,  $N$ ) は、保持容量としての機能を有する。

40

【0194】

ワード線  $W_L_1 \sim W_L_i$  のそれぞれの電位は、例えばデコーダを用いた駆動回路により制御すればよい。

【0195】

ビット線  $B_L_1 \sim B_L_j$  のそれぞれの電位は、例えばデコーダを用いた駆動回路により制御すればよい。

【0196】

容量線  $C_L_1 \sim C_L_i$  のそれぞれの電位は、例えばデコーダを用いた駆動回路により制御すればよい。

【0197】

50

ゲート線駆動回路は、例えばダイオード及び第1の容量電極がダイオードのアノードに電気的に接続された容量素子を有する回路により構成されている。

【0198】

なお、本実施の形態において、電位の数値として使用した値は、接地電位を0Vとして算出される値である。

【0199】

本実施の形態にて説明したように、実施の形態1を適用したトランジスタ（酸化物半導体をチャネル領域に用いたトランジスタ）のソースまたはドレインと接続されたノードの電位を極めて長時間にわたって保持することが可能であるため、小さい消費電力にて、情報の書き込み、保持、読み出しが可能なメモリセルを作製することができる。

10

【0200】

（実施の形態4）

本実施の形態では、実施の形態1で説明したトランジスタの応用例であって実施の形態2及び実施の形態3とは異なるものについて説明する。

【0201】

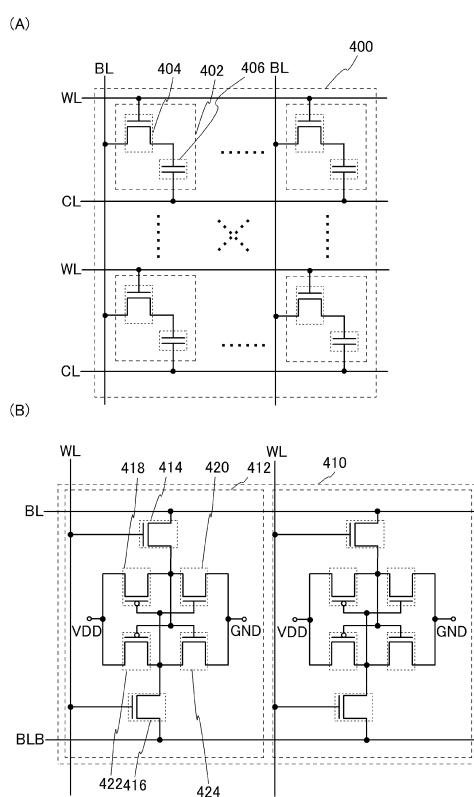

図10(A)は、いわゆるDRAM(Dynamic Random Access Memory)に相当する構成の半導体装置の一例を示す。図10(A)に示すメモリセルアレイ400には、複数のメモリセル402がマトリクス状に配列されている。また、メモリセルアレイ400は、m本の第1の配線BL及びn本の第2の配線WLを有する。なお、本実施の形態においては、第1の配線をBL(ビット線)と表記し、第2の配線をWL(ワード線)と表記する。

20

【0202】

メモリセル402は、トランジスタ404及び容量素子406を有する。トランジスタ404のゲートは、第2の配線WLに電気的に接続されている。また、トランジスタ404のソース及びドレインの一方は、第1の配線BLに電気的に接続されており、トランジスタ404のソース及びドレインの他方は、容量素子406の電極の一方に電気的に接続されている。また、容量素子406の電極の他方は容量線CLに電気的に接続され、一定の電位が与えられている。

【0203】

酸化物半導体をチャネル形成領域に用いたトランジスタ404は、実施の形態1にて説明した本発明の一態様である半導体装置の作製方法を適用して作製したものである。

30

【0204】

実施の形態1にて説明した本発明の一態様である半導体装置の作製方法を適用して作製したトランジスタは、オフ電流が小さいという特徴を有する。このため、いわゆるDRAMとして認識されている図10(A)に示す半導体装置に当該トランジスタを適用する場合には、実質的な不揮発性メモリを得ることが可能である。

【0205】

図10(B)は、いわゆるSRAM(Static Random Access Memory)に相当する構成の半導体装置の一例を示す。図10(B)に示すメモリセルアレイ410は、複数のメモリセル412がマトリクス状に配列されている。また、メモリセルアレイ410は、第1の配線BL、第2の配線BLB及び第3の配線WLをそれぞれ複数本有する。そして、所定の位置が電源電位VDD及び接地電位GNDに接続されている。

40

【0206】

メモリセル412は、第1のトランジスタ414、第2のトランジスタ416、第3のトランジスタ418、第4のトランジスタ420、第5のトランジスタ422及び第6のトランジスタ424を有する。第1のトランジスタ414及び第2のトランジスタ416は、選択トランジスタとして機能する。また、第3のトランジスタ418と第4のトランジスタ420のうち、一方はnチャネル型トランジスタ（ここでは、第4のトランジスタ420）であり、他方はpチャネル型トランジスタ（ここでは、第3のトランジスタ41

50

8)とする。つまり、第3のトランジスタ418と第4のトランジスタ420によってCMOS回路が構成されている。同様に、第5のトランジスタ422と第6のトランジスタ424によってCMOS回路が構成されている。

#### 【0207】

第1のトランジスタ414、第2のトランジスタ416、第4のトランジスタ420及び第6のトランジスタ424は、nチャネル型トランジスタであり、実施の形態1のトランジスタを適用すればよい。第3のトランジスタ418と第5のトランジスタ422は、pチャネル型トランジスタであり、酸化物半導体以外の材料をチャネル形成領域に用いればよい。なお、これに限定されず、第1のトランジスタ乃至第6のトランジスタはpチャネル型とした実施の形態1のトランジスタであってもよいし、nチャネル型とした酸化物半導体以外の材料をチャネル形成領域に用いたトランジスタであってもよい。

10

#### 【0208】

##### (実施の形態5)

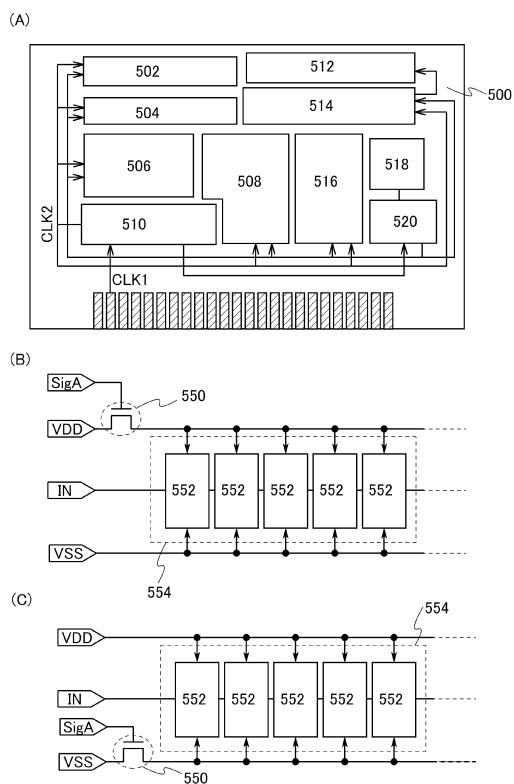

本実施の形態では、実施の形態1で説明したトランジスタの応用例であって実施の形態2乃至実施の形態4とは異なるものについて説明する。本実施の形態では、実施の形態1で説明したトランジスタを少なくとも一部に適用したCPU(Central Processing Unit)について説明する。

#### 【0209】

図11(A)は、CPUの具体的な構成を示すブロック図である。図11(A)に示すCPUは、基板500上に、演算回路(ALU: Arithmetic logic unit)502、ALUコントローラ504、インストラクションデコーダ506、インターフェースコントローラ508、タイミングコントローラ510、レジスタ512、レジスタコントローラ514、バスインターフェース(Bus I/F)516、書き換え可能なROM518及びROMインターフェース(ROM I/F)520を有する。基板500としては、半導体基板、SOI基板またはガラス基板などを用いることができる。ROM518及びROMインターフェース520は、別チップに設けられていてもよい。もちろん、図11(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

20

#### 【0210】

バスインターフェース516を介してCPUに入力された命令は、インストラクションデコーダ506に入力され、デコードされた後に、ALUコントローラ504、インターフェースコントローラ508、レジスタコントローラ514及びタイミングコントローラ510に入力される。

30

#### 【0211】

ALUコントローラ504、インターフェースコントローラ508、レジスタコントローラ514及びタイミングコントローラ510は、デコードされた命令に基づき、各種制御を行う。具体的にALUコントローラ504は、ALU502の動作を制御するための信号を生成する。また、インターフェースコントローラ508は、CPUのプログラム実行中に、外部の入出力装置または周辺回路からの割り込み要求を、その優先度やマスク状態から判断して処理する。レジスタコントローラ514は、レジスタ512のアドレスを生成し、CPUの状態に応じてレジスタ512の読み出し及び書き込みを行なう。

40

#### 【0212】

また、タイミングコントローラ510は、ALU502、ALUコントローラ504、インストラクションデコーダ506、インターフェースコントローラ508及びレジスタコントローラ514の動作のタイミングを制御する信号を生成する。例えば、タイミングコントローラ510は、基準クロック信号CLK1を基にして、内部クロック信号CLK2を生成する内部クロック生成部を有し、クロック信号CLK2を前記各種回路に供給する。

#### 【0213】

図11(A)に示すCPUでは、レジスタ512に、メモリセルが設けられている。レジスタ512のメモリセルには、実施の形態2乃至実施の形態4にて説明したメモリセル

50

のいずれかを用いることができる。

【0214】

図11(A)に示すCPUにおいて、レジスタコントローラ514は、ALU502からの指示に従い、レジスタ512における保持動作の選択を行う。すなわち、レジスタ512が有する記憶素子において、位相反転素子によるデータの保持を行うか、容量素子によるデータの保持を行うかを選択する。位相反転素子によるデータの保持が選択されている場合には、レジスタ512内の記憶素子に電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合には、容量素子へのデータの書き換えが行われ、レジスタ512内の記憶素子への電源電圧の供給を停止することができる。

【0215】

電源の停止は、図11(B)または図11(C)に示すように、記憶素子群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を配することにより行うことができる。

【0216】

図11(B)及び図11(C)では、記憶素子への電源電位の供給を制御するスイッチング素子に、実施の形態1のトランジスタを適用した記憶回路の構成の一例を示す。

【0217】

図11(B)に示す記憶装置は、スイッチング素子550と、記憶素子552を複数有する記憶素子群554と、を有する。具体的に、各記憶素子552には、実施の形態2乃至実施の形態4の記憶素子を用いることができる。記憶素子群554が有する各記憶素子552には、スイッチング素子550を介して、ハイレベルの電源電位VDDが供給されている。さらに、記憶素子群554が有する各記憶素子552には、信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。

【0218】

図11(B)では、スイッチング素子550として、実施の形態1のトランジスタを用いており、該トランジスタは、そのゲート電極に与えられる信号SigAによりスイッチングが制御される。

【0219】

なお、図11(B)では、スイッチング素子550がトランジスタを一つだけ有する構成を示しているが、トランジスタを複数有していてもよい。スイッチング素子550がスイッチング素子として機能するトランジスタを複数有している場合には、前記複数のトランジスタは並列に接続されてもよいし、直列に接続されてもよいし、直列に接続された部分と並列に接続された部分が組み合わせられてもよい。

【0220】

また、図11(B)では、スイッチング素子550により、記憶素子群554が有する各記憶素子552への、ハイレベルの電源電位VDDの供給が制御されているが、スイッチング素子550により、ローレベルの電源電位VSSの供給が制御されてもよい。

【0221】

図11(C)には、記憶素子群554が有する各記憶素子552に、スイッチング素子550を介して、ローレベルの電源電位VSSが供給されている記憶装置の一例を示す。スイッチング素子550により、記憶素子群554が有する各記憶素子552へのローレベルの電源電位VSSの供給を制御することができる。

【0222】

記憶素子群554と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を配することで、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。

【0223】

ここでは、CPUを例に挙げて説明したが、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)など

10

20

30

40

50

l e G a t e A r r a y ) などの L S I にも応用可能である。

【 0 2 2 4 】

( 実施の形態 6 )

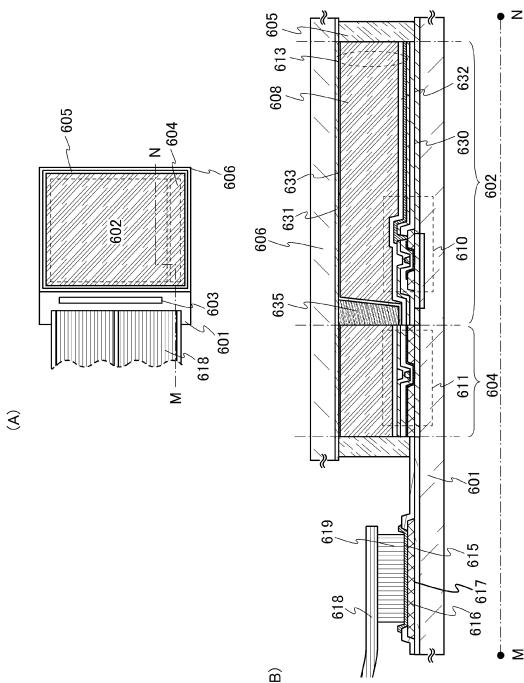

本実施の形態では、実施の形態 1 のトランジスタを適用した表示装置について説明する。

【 0 2 2 5 】

図 12 ( A ) 及び図 12 ( B ) は、実施の形態 1 のトランジスタを適用した液晶表示装置を示す。図 12 ( B ) は、図 12 ( A ) の M - N における断面図に相当する。図 12 ( A ) において、第 1 の基板 601 上に設けられた画素部 602 と、走査線駆動回路 604 とを囲むようにして、シール材 605 が設けられている。また画素部 602 と、走査線駆動回路 604 とは、第 1 の基板 601 とシール材 605 と第 2 の基板 606 とによって、液晶素子などの表示素子と共に封止されている。図 12 ( A ) においては、第 1 の基板 601 上のシール材 605 によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜または多結晶半導体膜で形成された信号線駆動回路 603 が実装されている。図 12 ( A ) においては、別途設けられた信号線駆動回路 603 と、走査線駆動回路 604 または画素部 602 に与えられる各種信号及び電位は、F P C ( F l e x i b l e p r i n t e d c i r c u i t ) である F P C 618 から供給されている。

【 0 2 2 6 】

また、図 12 ( A ) においては、走査線駆動回路 604 を第 1 の基板 601 上に設け、かつ信号線駆動回路 603 を別途設けて第 1 の基板 601 に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途設けて実装してもよいし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途設けて実装してもよい。

【 0 2 2 7 】

なお、別途設けた駆動回路の接続方法は、特に限定されるものではなく、C O G ( C h i p O n G l a s s ) 法、ワイヤボンディング法、或いは T A B ( T a p e A u t o m a t e d B o n d i n g ) 法などを用いてもよい。図 12 ( A ) は、C O G 法により信号線駆動回路 603 を実装する例である。

【 0 2 2 8 】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含む I C などを実装した状態にあるモジュールとを含む。

【 0 2 2 9 】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源（照明装置含む）を指す。また、コネクター、例えば F P C もしくは T A B テープもしくは T C P が取り付けられたモジュール、T A B テープや T C P の先にプリント配線板が設けられたモジュールまたは表示素子に C O G 方式により I C ( 集積回路 ) が直接実装されたモジュールも全て表示装置に含むものとする。

【 0 2 3 0 】

また、第 1 の基板上に設けられた画素部及び走査線駆動回路は、トランジスタを複数有しており、実施の形態 1 のトランジスタを適用することができる。

【 0 2 3 1 】

表示装置に設けられる表示素子としては液晶素子（液晶表示素子ともいう。）、発光素子（発光表示素子ともいう。）を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機 E L ( E l e c t r o L u m i n e s c e n c e ) 、有機 E L などを含む。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

【 0 2 3 2 】

図 12 ( B ) に示すように、半導体装置は接続端子電極 615 及び端子電極 616 を有しており、接続端子電極 615 及び端子電極 616 は F P C 618 が有する端子と異方性導電膜 619 を介して、電気的に接続されている。なお、端子電極 616 の下部には酸化

10

20

30

40

50

物半導体膜 617 が残置している。

【0233】

接続端子電極 615 は、第1の電極 630 と同じ導電膜から形成され、端子電極 616 は、トランジスタ 610、トランジスタ 611 のソース電極及びドレイン電極と同じ導電膜から形成されている。

【0234】

また、第1の基板 601 上に設けられた画素部 602 と、走査線駆動回路 604 は、トランジスタを複数有しており、図 12 (B) では、画素部 602 に含まれるトランジスタ 610 と、走査線駆動回路 604 に含まれるトランジスタ 611 とを例示している。

【0235】

本実施の形態では、トランジスタ 610、トランジスタ 611 として、実施の形態 1 のトランジスタを適用することができる。

【0236】

画素部 602 に設けられたトランジスタ 610 は、表示素子と電気的に接続し、表示パネルを構成する。表示素子は特に限定されず、様々な表示素子を用いることができる。

【0237】

図 12 (B) に表示素子として液晶素子を用いた液晶表示装置の例を示す。図 12 (B) において、表示素子である液晶素子 613 は、第1の電極 630、第2の電極 631、及び液晶層 608 を含む。なお、液晶層 608 を挟持するように配向層として機能する絶縁膜 632 及び絶縁膜 633 が設けられている。第2の電極 631 は第2の基板 606 側に設けられ、第1の電極 630 と第2の電極 631 とは液晶層 608 を介して積層する構成となっている。

【0238】

また、スペーサ 635 は絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、液晶層 608 の厚さ (セルギャップ) を調整するために設けられている。なお球状のスペーサを用いていてもよい。

【0239】

表示素子として、液晶素子を用いる場合、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶などを用いる。これらの液晶材料は、条件により、コレステリック相、スマクチック相、キュービック相、カイラルネマチック相、等方相などを示す。

【0240】

また、液晶材料の固有抵抗率は、 $1 \times 10^9 \cdot \text{cm}$  以上であり、好ましくは $1 \times 10^{11} \cdot \text{cm}$  以上であり、さらに好ましくは $1 \times 10^{12} \cdot \text{cm}$  以上である。なお、本明細書における固有抵抗率の値は、20 で測定した値とする。

【0241】

液晶表示装置に設けられる保持容量の大きさは、画素部に配置されるトランジスタのリーケ電流などを考慮して、所定の期間の間電荷を保持できるように設定される。高純度の酸化物半導体膜を有するトランジスタを用いることにより、各画素における液晶容量に対して 1/3 以下または 1/5 以下の容量の大きさを有する保持容量を設ければ充分である。

【0242】

本実施の形態で用いる実施の形態 1 のトランジスタは、オフ電流を小さくすることができる。よって、画像信号などの電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくできるため、消費電力を抑制する効果を奏する。

【0243】

また、本実施の形態で用いる実施の形態 1 のトランジスタは、比較的高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に上記トランジスタを用いることで、高画質な画像を提供することができる。また、上記トランジスタ

10

20

30

40

50

は、同一基板上に駆動回路部または画素部を作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

【0244】

ここで、本実施の形態の液晶表示装置に適用可能な液晶の駆動方法などについて説明する。液晶の駆動方法には、基板に対して直交に電圧を印加する縦電界方式、基板に対して平行に電圧を印加する横電界方式がある。

【0245】

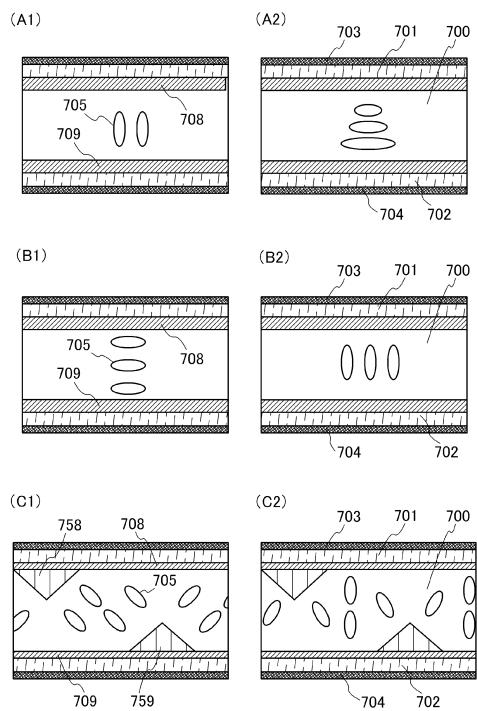

まず、図13(A1)及び(A2)に、TNモードの液晶表示装置の画素構成を説明する断面模式図を示す。

【0246】

互いに対向するように配置された第1の基板701及び第2の基板702に、表示素子を有する層700が挟持されている。また、第1の基板701側に第1の偏光板703が形成され、第2の基板702側に第2の偏光板704が形成されている。第1の偏光板703の吸収軸と、第2の偏光板704の吸収軸は、クロスニコルの状態で配置されている。

【0247】

なお、図示しないが、バックライトなどは、第2の偏光板704の外側に配置される。第1の基板701、及び第2の基板702上には、それぞれ第1の電極708、第2の電極709が設けられている。そして、少なくともバックライトと反対側、つまり視認側の電極である第1の電極708は、透光性を有するように形成する。

【0248】

このような構成を有する液晶表示装置において、ノーマリホワイトモードの場合、第1の電極708及び第2の電極709に電圧が印加(縦電界方式と表記する。)されると、図13(A1)に示すように、液晶分子705は縦に並んだ状態となる。すると、バックライトからの光は第1の偏光板703の外側に到達することができず、黒色表示となる。

【0249】

そして、図13(A2)に示すように、第1の電極708及び第2の電極709の間に電圧が印加されていないときは、液晶分子705は横に並び、平面内で揺れている状態となる。その結果、バックライトからの光は第1の偏光板703の外側に到達することができ、白色表示となる。また、第1の電極708及び第2の電極709に印加する電圧を調節することにより、階調を表現することができる。このようにして、所定の映像表示が行われる。

【0250】

このとき、カラーフィルタを設けることにより、フルカラー表示を行うことができる。カラーフィルタは、第1の基板701側、または第2の基板702側のどちらに設けることもできる。

【0251】

TNモードに使用される液晶材料は、公知のものを使用すればよい。

【0252】

図13(B1)及び(B2)に、VAモードの液晶表示装置の画素構成を説明する断面模式図を示す。VAモードは、無電界の時に液晶分子705が基板に垂直となるように配向されているモードである。

【0253】

図13(A1)及び(A2)と同様に、第1の基板701、及び第2の基板702上には、それぞれ第1の電極708、第2の電極709が設けられている。そして、バックライトと反対側、つまり視認側の電極である第1の電極708は、透光性を有するように形成する。そして第1の基板701側には、第1の偏光板703が形成され、第2の基板702側に第2の偏光板704が形成されている。また、第1の偏光板703の吸収軸と、第2の偏光板704の吸収軸は、クロスニコルの状態で配置されている。

【0254】

10

20

30

40

50

このような構成を有する液晶表示装置において、第1の電極708及び第2の電極709に電圧が印加される（縦電界方式）と、図13（B1）に示すように液晶分子705は横に並んだ状態となる。すると、バックライトからの光は、第1の偏光板703の外側に到達することができ、白色表示となる。

【0255】

そして、図13（B2）に示すように、第1の電極708及び第2の電極709の間に電圧が印加されていないときは、液晶分子705は縦に並んだ状態となる。その結果、第2の偏光板704により偏光されたバックライトからの光は、液晶分子705の複屈折の影響を受けることなくセル内を通過する。すると、偏光されたバックライトからの光は、第1の偏光板703の外側に到達することができず、黒色表示となる。また、第1の電極708及び第2の電極709に印加する電圧を調節することにより、階調を表現することができる。このようにして、所定の映像表示が行われる。

10

【0256】

このとき、カラーフィルタを設けることにより、フルカラー表示を行うことができる。カラーフィルタは、第1の基板701側、または第2の基板702側のどちらに設けることもできる。

【0257】

図13（C1）及び（C2）に、MVAモードの液晶表示装置の画素構成を説明する断面模式図を示す。MVAモードは一画素を複数に分割し、それぞれの部分の配向方向を異ならせて、視野角依存性を互いに補償する方法である。図13（C1）に示すように、MVAモードでは、第1の電極708及び第2の電極709上に配向制御用に断面が三角の突起物758及び突起物759が設けられている。なお、他の構成はVAモードと同等である。

20

【0258】

第1の電極708及び第2の電極709に電圧が印加される（縦電界方式）と、図13（C1）に示すように液晶分子705は突起物758及び759の面に対して液晶分子705の長軸が概ね垂直となるように配向する。すると、バックライトからの光は、第1の偏光板703の外側に到達することができ、白色表示となる。

【0259】

そして、図13（C2）に示すように、第1の電極708及び第2の電極709の間に電圧が印加されていないときは、液晶分子705は縦に並んだ状態となる。その結果、バックライトからの光は、第1の偏光板703の外側に到達することができず、黒色表示となる。また、第1の電極708及び第2の電極709に印加する電圧を調節することにより、階調を表現することができる。このようにして、所定の映像表示が行われる。

30

【0260】

このとき、カラーフィルタを設けることにより、フルカラー表示を行うことができる。カラーフィルタは、第1の基板701側、または第2の基板702側のどちらに設けることもできる。

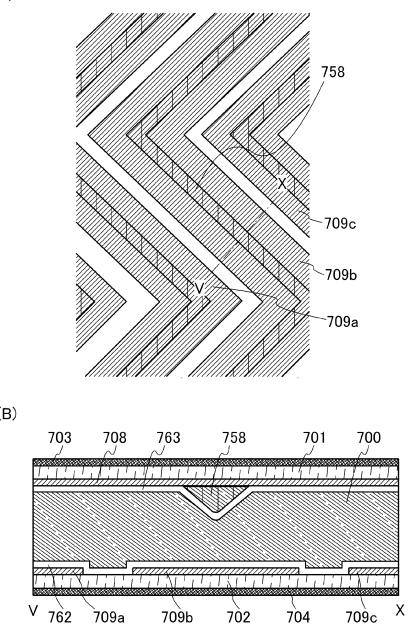

【0261】

MVAモードの他の例を上面図及び断面図を図16に示す。図16（A）において、第2の電極は、くの字型のよう屈曲したパターンに形成されており、第2の電極709a、第2の電極709b、第2の電極709cとなっている。図16（B）で示す様に、第2の電極709a、709b、709c上に配向膜である絶縁層762が形成されている。第1の電極708上には突起物758が第2の電極709bと重畳するように形成されている。第1の電極708及び突起物758上に配向膜である絶縁層763が形成されている。

40

【0262】

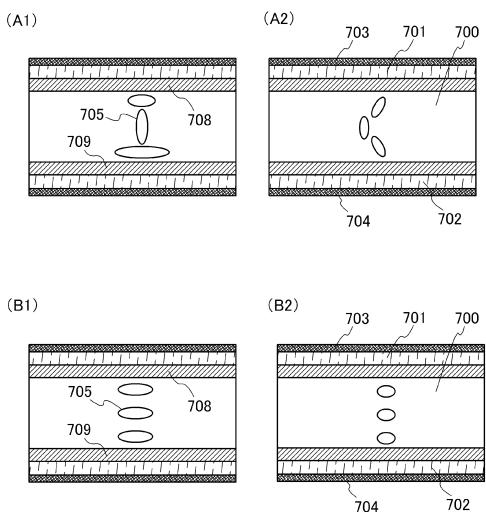

図14（A1）及び（A2）に、OCBモードの液晶表示装置の画素構成を説明する断面模式図を示す。OCBモードは、液晶層内で液晶分子705の配列が光学的に補償状態を形成している（バンド配向）。

## 【0263】

図13と同様に、第1の基板701、及び第2の基板702上には、それぞれ第1の電極708、第2の電極709が設けられている。そして、バックライトと反対側、つまり視認側の電極である第1の電極708は、透光性を有するように形成する。そして第1の基板701側には、第1の偏光板703が形成され、第2の基板702側に第2の偏光板704が形成されている。また、第1の偏光板703の吸収軸と、第2の偏光板704の吸収軸は、クロスニコルの状態で配置されている。

## 【0264】

このような構成を有する液晶表示装置において、第1の電極708及び第2の電極709に電圧が印加される（縦電界方式）と、黒色表示が行われる。このとき液晶分子705は、図14（A1）に示すように縦に並んだ状態となる。すると、バックライトからの光は、第1の偏光板703の外側に到達することができず、黒色表示となる。

10

## 【0265】

そして、図14（A2）に示すように、第1の電極708及び第2の電極709の間に一定の電圧が印加されていないときは、液晶分子705はペンド配向の状態となる。その結果、バックライトからの光は、第1の偏光板703の外側に到達することができ、白色表示となる。また、第1の電極708及び第2の電極709に印加する電圧を調節することにより、階調を表現することができる。このようにして、所定の映像表示が行われる。

## 【0266】

このとき、カラーフィルタを設けることにより、フルカラー表示を行うことができる。カラーフィルタは、第1の基板701側、または第2の基板702側のどちらに設けることもできる。

20

## 【0267】

このようなOCBモードでは、液晶層内の液晶分子705の配列により視野角依存性を補償できる。さらに、一対の積層された偏光子を含む層によりコントラスト比を高めることができる。

## 【0268】

図14（B1）及び（B2）に、FLCモード及びALCモードの液晶表示装置の画素構成を説明する断面模式図を示す。

## 【0269】

30

図13と同様に、第1の基板701、及び第2の基板702上には、それぞれ第1の電極708、第2の電極709が設けられている。そして、少なくともバックライトと反対側、つまり視認側の電極である第1の電極708は、透光性を有するように形成する。そして第1の基板701側には、第1の偏光板703が形成され、第2の基板702側に第2の偏光板704が形成されている。また、第1の偏光板703の吸収軸と、第2の偏光板704の吸収軸は、クロスニコルの状態で配置されている。

## 【0270】

このような構成を有する液晶表示装置において、第1の電極708及び第2の電極709に電圧が印加（縦電界方式と表記する。）されると、液晶分子705はラビング方向からずれた方向で横に並んでいる状態となる。その結果、バックライトからの光は、第1の偏光板703の外側に到達することができ、白色表示となる。

40

## 【0271】

そして、図14（B2）に示すように、第1の電極708及び第2の電極709の間に電圧が印加されていないときは、液晶分子705はラビング方向に沿って横に並んだ状態となる。すると、バックライトからの光は、第1の偏光板703の外側に到達することができず、黒色表示となる。また、第1の電極708及び第2の電極709に印加する電圧を調節することにより、階調を表現することができる。このようにして、所定の映像表示が行われる。

## 【0272】

このとき、カラーフィルタを設けることにより、フルカラー表示を行うことができる。

50

カラーフィルタは、第1の基板701側、または第2の基板702側のどちらに設けることもできる。

【0273】

FLCモード及びALCモードに使用される液晶材料は、公知のものを使用すればよい。

【0274】

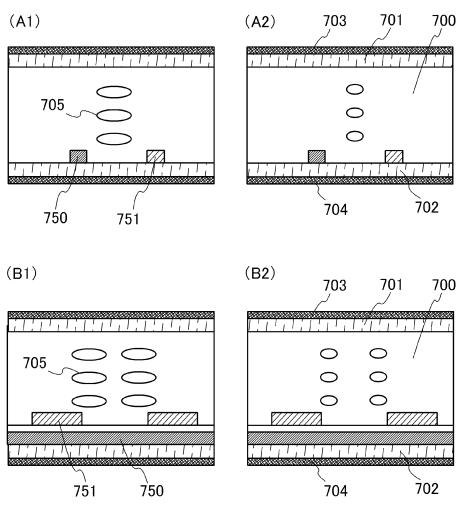

図15(A1)及び(A2)に、IPSモードの液晶表示装置の画素構成を説明する断面模式図を示す。IPSモードは、液晶分子705を基板に対して常に平面内で回転させるモードであり、電極は一方の基板側のみに設けた横電界方式をとる。

【0275】

IPSモードは一方の基板に設けられた一対の電極により液晶を制御することを特徴とする。そのため、第2の基板702上に一対の電極750、電極751が設けられている。一対の電極750、電極751は、それぞれ透光性を有するとよい。そして第1の基板701側には、第1の偏光板703が形成され、第2の基板702側に第2の偏光板704が形成されている。また、第1の偏光板703の吸収軸と、第2の偏光板704の吸収軸は、クロスニコルの状態で配置されている。

【0276】

このような構成を有する液晶表示装置において、一対の電極750、電極751に電圧が印加されると、図15(A1)に示すように液晶分子705はラビング方向からずれた電気力線に沿って配向する。すると、バックライトからの光は、第1の偏光板703の外側に到達することができ、白色表示となる。

【0277】

そして、図15(A2)に示すように、一対の電極750、電極751の間に電圧が印加されていないとき、液晶分子705は、ラビング方向に沿って横に並んだ状態となる。その結果、バックライトからの光は、第1の偏光板703の外側に到達することができず、黒色表示となる。また、一対の電極750、電極751の間に印加する電圧を調節することにより、階調を表現することができる。このようにして、所定の映像表示が行われる。

【0278】

このとき、カラーフィルタを設けることにより、フルカラー表示を行うことができる。カラーフィルタは、第1の基板701側、または第2の基板702側のどちらに設けることもできる。

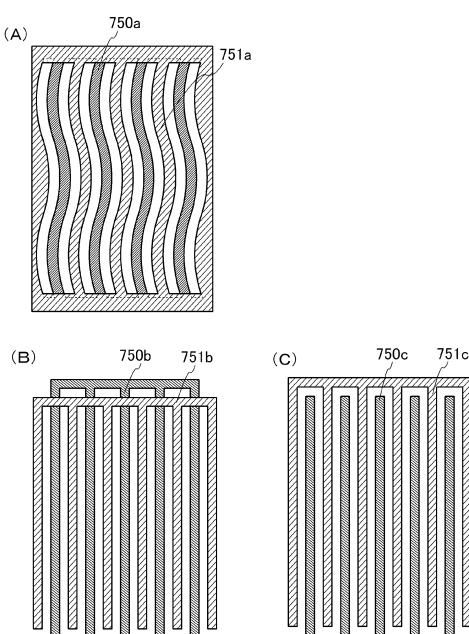

【0279】

IPSモードで用いることできる一対の電極750及び751の例を図17に示す。図17(A)乃至(C)の上面図に示すように、一対の電極750及び751が互い違いとなるように形成されており、図17(A)では電極750a及び電極751aはうねりを有する波状形状であり、図17(B)では電極750b及び電極751bは櫛歯状であり一部重なっている形状であり、図17(C)では電極750c及び電極751cは櫛歯状であり電極同士がかみ合うような形状である。

【0280】

図15(B1)及び(B2)に、FFSモードの液晶表示装置の画素構成を説明する断面模式図を示す。FFSモードはIPSモードと同じ横電界方式であるが、図15(B1)及び(B2)に示すように、電極750上に絶縁膜を介して電極751が形成される構造である。

【0281】

一対の電極750、電極751は、それぞれ透光性を有するとよい。そして第1の基板701側には、第1の偏光板703が形成され、第2の基板702側に第2の偏光板704が形成されている。また、第1の偏光板703の吸収軸と、第2の偏光板704の吸収軸は、クロスニコルの状態で配置されている。

【0282】

10

20

30

40

50

このような構成を有する液晶表示装置において、一対の電極 750、電極 751 に電圧が印加されると、図 15 (B1) に示すように液晶分子 705 はラビング方向からずれた電気力線に沿って配向する。すると、バックライトからの光は、第 1 の偏光板 703 の外側に到達することができ、白色表示となる。

【0283】

そして、図 15 (B2) に示すように、一対の電極 750、電極 751 の間に電圧が印加されていないとき、液晶分子 705 は、ラビング方向に沿って横に並んだ状態となる。その結果、バックライトからの光は、第 1 の偏光板 703 の外側に到達することができず、黒色表示となる。また、一対の電極 750、電極 751 の間に印加する電圧を調節することにより、階調を表現することができる。このようにして、所定の映像表示が行われる

10

。

【0284】

このとき、カラーフィルタを設けることにより、フルカラー表示を行うことができる。カラーフィルタは、第 1 の基板 701 側、または第 2 の基板 702 側のどちらに設けることもできる。

【0285】

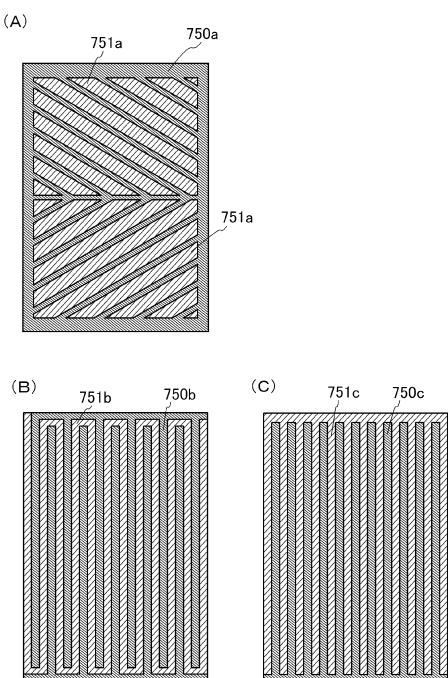

FFS モードで用いることできる一対の電極 750 及び 751 の例を図 18 に示す。図 18 (A) 乃至 (C) の上面図に示すように、電極 750 上に様々なパターンに形成された電極 751 が形成されており、図 18 (A) では電極 750a 上の電極 751a は屈曲したくの字形状であり、図 18 (B) では電極 750b 上の電極 751b は櫛歯状で電極同士がかみ合うような形状であり、図 18 (C) では電極 750c 上の電極 751c は櫛歯状の形状である。

20

【0286】

IPS モード及び FFS モードに使用される液晶材料は、公知のものを使用すればよい。または、ブルー相を示す液晶を用いてもよい。

【0287】

また、これら以外にも、PVA モード、ASM モード、TBA モードなどの動作モードを適用することが可能である。

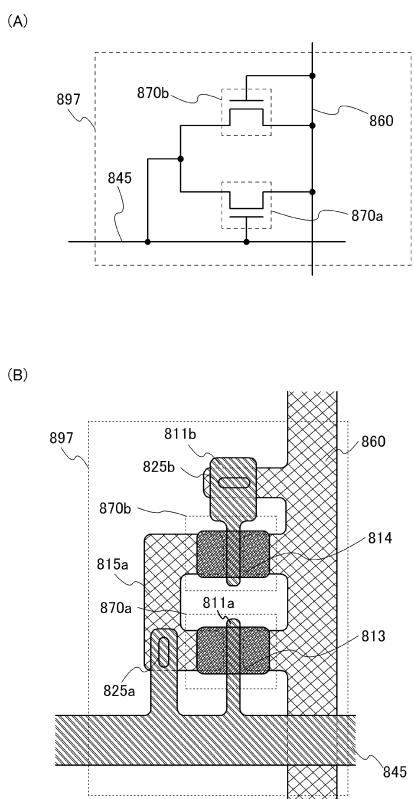

【0288】

ところで、本実施の形態の液晶表示装置には、保護回路が設けられていることが好ましい。保護回路に適用可能な回路の一例を図 19 (A) に示す。保護回路 897 は n 型のトランジスタ 870a 及び 870b によって構成されており、それぞれダイオードと同様の特性を示すように、ゲート端子がドレイン端子に電気的に接続されている。なお、トランジスタ 870a 及び 870b として、実施の形態 1 で示したトランジスタを用いるとよい。

30

【0289】

トランジスタ 870a の第 1 端子 (ゲート) と第 3 端子 (ドレイン) は第 1 の配線 845 に電気的に接続され、第 2 端子 (ソース) は第 2 の配線 860 に電気的に接続されている。また、トランジスタ 870b の第 1 端子 (ゲート) と第 3 端子 (ドレイン) は第 2 の配線 860 に電気的に接続され、第 2 端子 (ソース) は第 1 の配線 845 に電気的に接続されている。すなわち、図 19 (A) で示す保護回路は、二つのトランジスタのそれぞれが整流方向を逆向きにして、第 1 の配線 845 と第 2 の配線 860 が電気的に接続されている。言い換えると、整流方向が第 1 の配線 845 から第 2 の配線 860 に向かうトランジスタと、整流方向が第 2 の配線 860 から第 1 の配線 845 に向かうトランジスタを、第 1 の配線 845 と第 2 の配線 860 の間に有する。

40

【0290】

保護回路 897 が設けられていることで、第 2 の配線 860 が静電気などによりプラスまたはマイナスに帯電した場合、その電荷を打ち消す方向に電流が流れる。例えば、第 2 の配線 860 がプラスに帯電した場合は、そのプラスの電荷を第 1 の配線 845 に逃がす方向に電流が流れる。この動作により、帯電した第 2 の配線 860 に電気的に接続してい

50

る回路や素子の静電破壊または誤動作を防止することができる。また、帯電した第2の配線860と他の配線が絶縁層を介して交差する構成において、該絶縁層が絶縁破壊される現象を防止することができる。

【0291】

なお、保護回路は上記構成に限定されない。例えば、整流方向が第1の配線845から第2の配線860に向かう複数のトランジスタと、整流方向が第2の配線860から第1の配線845に向かう複数のトランジスタを有する構成であってもよい。また、奇数個のトランジスタを使って保護回路を構成することもできる。

【0292】

なお、図19(A)に例示した保護回路は様々な用途に適用することができる。例えば、第1の配線845を表示装置の共通配線とし、第2の配線860を複数の信号線の一とし、その間に当該保護回路を適用することができる。保護回路が設けられた信号線に電気的に接続された画素トランジスタは、配線の帯電による静電破壊やしきい値電圧のシフトなどの不具合から保護される。該保護回路は表示回路の他の部位にも適用できるのはもちろんのこと、他の用途、例えば実施の形態2の読み出し回路などにも用いることができる。

【0293】

次に、基板上に保護回路897を構成する例を説明する。保護回路897の上面図の一例を図19(B)に示す。

【0294】

トランジスタ870aはゲート電極811aを有し、ゲート電極811aは第1の配線845と電気的に接続されている。トランジスタ870aのソース電極は第2の配線860と電気的に接続され、ドレイン電極は第1の電極815aを介して第1の配線845と電気的に接続されている。また、トランジスタ870aはソース電極とドレイン電極の間にゲート電極811aと重畳する半導体層813を備える。

【0295】

トランジスタ870bはゲート電極811bを有し、ゲート電極811bはコンタクトホール825bを介して第2の配線860と電気的に接続されている。トランジスタ870bのドレイン電極は第2の配線860と電気的に接続され、ソース電極は第1の電極815aとコンタクトホール825aを介して第1の配線845と電気的に接続されている。また、トランジスタ870bはソース電極とドレイン電極の間にゲート電極811bと重畳する半導体層814を有する。

【0296】

本実施の形態にて説明したように、実施の形態1のトランジスタは液晶表示装置に適用することができる。

【0297】

ただし、本発明の一態様である半導体装置の表示装置は、液晶表示装置に限定されず、表示素子として発光素子が設けられたEL表示装置であってもよい。

【0298】

また、表示素子として発光素子を用いる場合には、発光素子の発光、非発光をトランジスタで制御するような画素構成とすればよい。例えば、一画素に駆動用トランジスタと電流制御用トランジスタが設けられた構成とすればよい。このとき、駆動用トランジスタと電流制御用トランジスタの双方に実施の形態1のトランジスタを適用してもよいし、一方にのみ実施の形態1のトランジスタを適用してもよい。なお、駆動用トランジスタと電流制御用トランジスタの一方にのみ実施の形態1のトランジスタを適用する場合には、他方には、酸化物半導体以外の材料をチャネル形成領域に用いたトランジスタを適用してもよい。

【0299】

(実施の形態7)

次に、本発明の一態様である電子機器について説明する。本発明の一態様である電子機

10

20

30

40

50

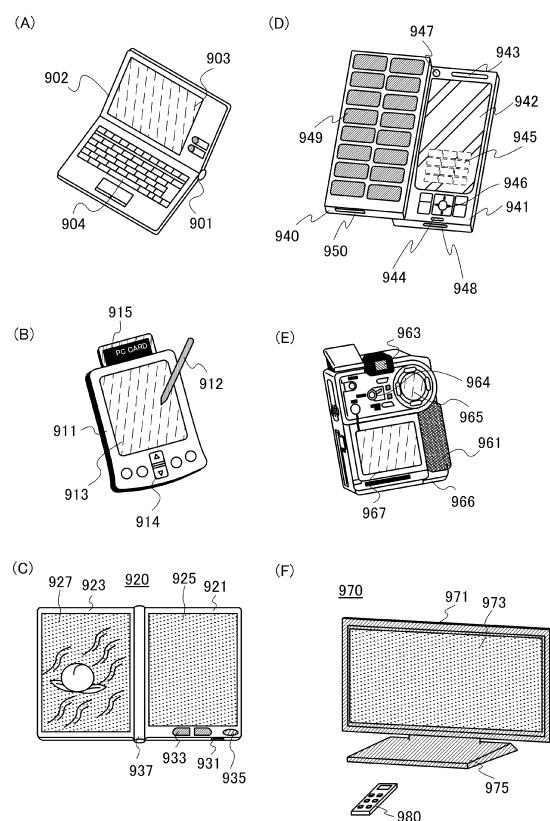

器は、実施の形態1のトランジスタを少なくとも一部に有する。本発明の一態様である電子機器として、例えば、コンピュータ、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯情報端末（携帯型ゲーム機、音響再生装置なども含む）、デジタルカメラ、デジタルビデオカメラ、電子ペーパー、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）などが挙げられる。例えば、このような電子機器の表示部を構成する画素トランジスタに実施の形態6で説明した表示装置を適用すればよい。

【0300】

図20(A)は、ノート型のパーソナルコンピュータであり、筐体901、筐体902、表示部903、キーボード904などによって構成されている。筐体901と筐体902内には、実施の形態1のトランジスタが設けられている。図20(A)に示すノート型のパーソナルコンピュータに実施の形態1のトランジスタを搭載することで、表示部の表示むらを低減し、信頼性を向上させることができる。

【0301】

図20(B)は、携帯情報端末(PDA)であり、本体911には、表示部913と、外部インターフェース915と、操作ボタン914などが設けられている。更には、携帯情報端末を操作するスタイルス912などを備えている。本体911内には、実施の形態1のトランジスタが設けられている。図20(B)に示すPDAに上記の実施の形態1のトランジスタを搭載することで、表示部の表示むらを低減し、信頼性を向上させることができる。

【0302】

図20(C)は、電子ペーパーを実装した電子書籍920であり、筐体921と筐体923の2つの筐体で構成されている。筐体921及び筐体923には、それぞれ表示部925及び表示部927が設けられている。筐体921と筐体923は、軸部937により物理的に接続されており、軸部937を軸として開閉動作を行うことができる。そして、筐体921は、電源931、操作キー933、スピーカー935などを備えている。筐体921、筐体923の少なくとも一には、実施の形態1のトランジスタが設けられている。図20(C)に示す電子書籍に実施の形態1のトランジスタを搭載することで、表示部の表示むらを低減し、信頼性を向上させることができる。

【0303】

図20(D)は、携帯電話機であり、筐体940と筐体941の2つの筐体で構成されている。さらに、筐体940と筐体941は、スライドし、図20(D)のように展開している状態から重なり合った状態とすることができる、携帯に適した小型化が可能である。そして、筐体941は、表示パネル942、スピーカー943、マイクロフォン944、ポインティングデバイス946、カメラ用レンズ947、外部接続端子948などを備えている。そして、筐体940は、携帯電話機の充電を行う太陽電池セル949、外部メモリスロット950などを備えている。なお、アンテナは、筐体941に内蔵されている。筐体940と筐体941の少なくとも一には、実施の形態1のトランジスタが設けられている。図20(D)に示す携帯電話機に実施の形態1のトランジスタを搭載することで、表示部の表示むらを低減し、信頼性を向上させることができる。

【0304】

図20(E)は、デジタルカメラであり、本体961、表示部967、接眼部963、操作スイッチ964、表示部965、バッテリー966などによって構成されている。本体961内には、実施の形態1のトランジスタが設けられている。図20(E)に示すデジタルカメラに実施の形態1のトランジスタを搭載することで、表示部の表示むらを低減し、信頼性を向上させることができる。

【0305】

図20(F)は、テレビジョン装置970であり、筐体971、表示部973、ストップ975などで構成されている。テレビジョン装置970の操作は、筐体971が備えるスイッチや、リモコン操作機980により行うことができる。筐体971及びリモコン操作機980には、実施の形態1のトランジスタが搭載されている。図20(F)に示すテ

10

20

30

40

50

レビジョン装置に実施の形態1のトランジスタを搭載することで、表示部の表示むらを低減し、信頼性を向上させることができる。

【符号の説明】

【0 3 0 6】

|           |              |    |

|-----------|--------------|----|

| 1 0 0     | 基板           |    |

| 1 0 1     | 下地絶縁層        |    |

| 1 0 2     | 第1の導電膜       |    |

| 1 0 4     | 第1のエッティングマスク |    |

| 1 0 6     | 第1の導電層       |    |

| 1 0 8     | 第1の酸化物半導体膜   | 10 |

| 1 0 9     | 第2の酸化物半導体膜   |    |

| 1 1 0     | 第2のエッティングマスク |    |

| 1 1 2     | 第1の酸化物半導体層   |    |

| 1 1 3     | サイドウォール絶縁膜   |    |

| 1 1 3 S W | サイドウォール絶縁層   |    |

| 1 1 4     | 第1の絶縁層       |    |

| 1 1 5     | 第3のエッティングマスク |    |

| 1 1 6     | 第2の導電膜       |    |

| 1 1 8     | 第4のエッティングマスク |    |

| 1 2 0     | 第2の導電層       | 20 |

| 1 2 2     | 第2の絶縁層       |    |

| 1 2 4     | 第2の酸化物半導体層   |    |

| 1 2 4 A   | 領域           |    |

| 1 2 4 B   | 領域           |    |

| 1 2 4 C   | 領域           |    |

| 1 2 4 D   | 領域           |    |

| 1 2 6     | 第3の酸化物半導体層   |    |

| 1 2 6 A   | 領域           |    |

| 1 2 6 B   | 領域           |    |

| 1 2 6 C   | 領域           | 30 |

| 1 2 6 D   | 領域           |    |

| 2 0 0     | トランジスタ       |    |

| 2 0 2     | トランジスタ       |    |

| 2 1 0     | メモリセル        |    |

| 2 1 2     | トランジスタ       |    |

| 2 1 4     | トランジスタ       |    |

| 2 1 6     | トランジスタ       |    |

| 2 1 8     | ノード          |    |

| 2 2 0     | メモリセルアレイ     |    |

| 2 2 2     | 駆動回路         | 40 |

| 2 2 4     | 読み出し回路       |    |

| 2 2 6     | 駆動回路         |    |

| 3 0 0     | メモリセル        |    |

| 3 0 2     | トランジスタ       |    |

| 3 0 4     | トランジスタ       |    |

| 3 0 6     | 容量素子         |    |

| 3 0 8     | ノード          |    |

| 3 1 0     | メモリセル        |    |

| 3 1 2     | トランジスタ       |    |

| 3 1 4     | トランジスタ       | 50 |

|       |               |    |

|-------|---------------|----|

| 3 1 6 | 容量素子          |    |

| 4 0 0 | メモリセルアレイ      |    |

| 4 0 2 | メモリセル         |    |

| 4 0 4 | トランジスタ        |    |

| 4 0 6 | 容量素子          |    |

| 4 1 0 | メモリセルアレイ      | 10 |

| 4 1 2 | メモリセル         |    |

| 4 1 4 | トランジスタ        |    |

| 4 1 6 | トランジスタ        |    |

| 4 1 8 | トランジスタ        |    |

| 4 2 0 | トランジスタ        |    |

| 4 2 2 | トランジスタ        |    |

| 4 2 4 | トランジスタ        |    |

| 5 0 0 | 基板            |    |

| 5 0 2 | ALU           |    |

| 5 0 4 | ALUコントローラ     |    |

| 5 0 6 | インストラクションデコーダ |    |

| 5 0 8 | インターラプトコントローラ |    |

| 5 1 0 | タイミングコントローラ   |    |

| 5 1 2 | レジスタ          | 20 |

| 5 1 4 | レジスタコントローラ    |    |

| 5 1 6 | バスインターフェース    |    |

| 5 1 8 | ROM           |    |

| 5 2 0 | ROMインターフェース   |    |

| 5 5 0 | スイッチング素子      |    |

| 5 5 2 | 記憶素子          |    |

| 5 5 4 | 記憶素子群         |    |

| 6 0 1 | 第1の基板         |    |

| 6 0 2 | 画素部           |    |

| 6 0 3 | 信号線駆動回路       | 30 |

| 6 0 4 | 走査線駆動回路       |    |

| 6 0 5 | シール材          |    |

| 6 0 6 | 第2の基板         |    |

| 6 0 8 | 液晶層           |    |

| 6 1 0 | トランジスタ        |    |

| 6 1 1 | トランジスタ        |    |

| 6 1 3 | 液晶素子          |    |

| 6 1 5 | 接続端子電極        |    |

| 6 1 6 | 端子電極          |    |

| 6 1 7 | 酸化物半導体膜       | 40 |

| 6 1 8 | FPC           |    |

| 6 1 9 | 異方性導電膜        |    |

| 6 3 0 | 第1の電極         |    |

| 6 3 1 | 第2の電極         |    |

| 6 3 2 | 絶縁膜           |    |

| 6 3 3 | 絶縁膜           |    |

| 6 3 5 | スペーサ          |    |

| 7 0 0 | 表示素子を有する層     |    |

| 7 0 1 | 第1の基板         |    |

| 7 0 2 | 第2の基板         | 50 |

|         |            |    |

|---------|------------|----|

| 7 0 3   | 第 1 の偏光板   |    |

| 7 0 4   | 第 2 の偏光板   |    |

| 7 0 5   | 液晶分子       |    |

| 7 0 8   | 第 1 の電極    |    |

| 7 0 9   | 第 2 の電極    |    |

| 7 0 9 a | 第 2 の電極    | 10 |

| 7 0 9 b | 第 2 の電極    |    |

| 7 0 9 c | 第 2 の電極    |    |

| 7 5 0   | 電極         |    |

| 7 5 0 a | 電極         |    |

| 7 5 0 b | 電極         |    |

| 7 5 0 c | 電極         |    |

| 7 5 1   | 電極         |    |

| 7 5 1 a | 電極         |    |

| 7 5 1 b | 電極         |    |

| 7 5 1 c | 電極         |    |

| 7 5 8   | 突起物        |    |

| 7 5 9   | 突起物        |    |

| 7 6 2   | 絶縁層        |    |

| 7 6 3   | 絶縁層        | 20 |

| 8 1 1 a | ゲート電極      |    |

| 8 1 1 b | ゲート電極      |    |

| 8 1 3   | 半導体層       |    |

| 8 1 4   | 半導体層       |    |

| 8 1 5 a | 第 1 の電極    |    |

| 8 2 5 a | コンタクトホール   |    |

| 8 2 5 b | コンタクトホール   |    |

| 8 4 5   | 第 1 の配線    |    |

| 8 6 0   | 第 2 の配線    |    |

| 8 7 0 a | トランジスタ     | 30 |

| 8 7 0 b | トランジスタ     |    |

| 8 9 7   | 保護回路       |    |

| 9 0 1   | 筐体         |    |

| 9 0 2   | 筐体         |    |

| 9 0 3   | 表示部        |    |

| 9 0 4   | キーボード      |    |

| 9 1 1   | 本体         |    |

| 9 1 2   | スタイルス      |    |

| 9 1 3   | 表示部        |    |

| 9 1 4   | 操作ボタン      | 40 |

| 9 1 5   | 外部インターフェース |    |

| 9 2 0   | 電子書籍       |    |

| 9 2 1   | 筐体         |    |

| 9 2 3   | 筐体         |    |

| 9 2 5   | 表示部        |    |

| 9 2 7   | 表示部        |    |

| 9 3 1   | 電源         |    |

| 9 3 3   | 操作キー       |    |

| 9 3 5   | スピーカー      |    |

| 9 3 7   | 軸部         | 50 |

|       |             |    |

|-------|-------------|----|

| 9 4 0 | 筐体          |    |

| 9 4 1 | 筐体          |    |

| 9 4 2 | 表示パネル       |    |

| 9 4 3 | スピーカー       |    |

| 9 4 4 | マイクロフォン     |    |

| 9 4 6 | ポインティングデバイス |    |

| 9 4 7 | カメラ用レンズ     |    |

| 9 4 8 | 外部接続端子      |    |

| 9 4 9 | 太陽電池セル      |    |

| 9 5 0 | 外部メモリスロット   | 10 |

| 9 6 1 | 本体          |    |

| 9 6 3 | 接眼部         |    |

| 9 6 4 | 操作スイッチ      |    |

| 9 6 5 | 表示部         |    |

| 9 6 6 | バッテリー       |    |

| 9 6 7 | 表示部         |    |

| 9 7 0 | テレビジョン装置    |    |

| 9 7 1 | 筐体          |    |

| 9 7 3 | 表示部         |    |

| 9 7 5 | スタンド        | 20 |

| 9 8 0 | リモコン操作機     |    |

【図1】

(A)

(B)

(C)

【図2】

(A)

(B)

(C)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

(A) (100) (B) (110)

(C) (001)

---

フロントページの続き

| (51)Int.Cl.              | F I                  |

|--------------------------|----------------------|

| H 01 L 27/115 (2006.01)  | H 01 L 29/78 6 2 1   |

| H 01 L 27/105 (2006.01)  | H 01 L 27/10 3 2 1   |

| H 01 L 21/8244 (2006.01) | H 01 L 27/10 4 3 4   |

| H 01 L 27/11 (2006.01)   | H 01 L 27/10 4 4 1   |

| H 01 L 29/788 (2006.01)  | H 01 L 27/10 3 8 1   |

| H 01 L 29/792 (2006.01)  | H 01 L 27/10 6 7 1 C |

| G 02 F 1/1368 (2006.01)  | H 01 L 27/10 6 7 1 Z |

|                          | H 01 L 29/78 3 7 1   |

|                          | G 02 F 1/1368        |

(56)参考文献 特開2009-152633(JP, A)

特開2010-114432(JP, A)

特開2007-220818(JP, A)

特開2010-016163(JP, A)

米国特許出願公開第2008/0277663(US, A1)

米国特許出願公開第2010/0233847(US, A1)

特開2010-166030(JP, A)

## (58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 786

H 01 L 21 / 336