(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6766427号

(P6766427)

(45) 発行日 令和2年10月14日(2020.10.14)

(24) 登録日 令和2年9月23日(2020.9.23)

(51) Int.Cl.

F 1

|             |              |                  |             |              |

|-------------|--------------|------------------|-------------|--------------|

| <b>H03L</b> | <b>7/093</b> | <b>(2006.01)</b> | <b>H03L</b> | <b>7/093</b> |

| <b>H03B</b> | <b>5/32</b>  | <b>(2006.01)</b> | <b>H03B</b> | <b>5/32</b>  |

| <b>H03L</b> | <b>1/02</b>  | <b>(2006.01)</b> | <b>H03L</b> | <b>1/02</b>  |

| <b>H03L</b> | <b>7/085</b> | <b>(2006.01)</b> | <b>H03L</b> | <b>7/085</b> |

A

請求項の数 13 (全 40 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2016-86657 (P2016-86657)    |

| (22) 出願日  | 平成28年4月25日 (2016.4.25)        |

| (65) 公開番号 | 特開2017-199947 (P2017-199947A) |

| (43) 公開日  | 平成29年11月2日 (2017.11.2)        |

| 審査請求日     | 平成31年4月17日 (2019.4.17)        |

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区新宿四丁目1番6号 |

| (74) 代理人  | 100104710<br>弁理士 竹腰 昇                        |

| (74) 代理人  | 100090479<br>弁理士 井上 一                        |

| (74) 代理人  | 100124682<br>弁理士 黒田 泰                        |

| (72) 発明者  | 中島 克仁<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内       |

| (72) 発明者  | 瀬尾 顯太郎<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内      |

最終頁に続く

(54) 【発明の名称】回路装置、発振器、電子機器及び移動体

## (57) 【特許請求の範囲】

## 【請求項 1】

発振信号に基づく入力信号と基準信号との位相比較を行う位相比較部と、

前記位相比較の結果に基づく周波数制御データに対して信号処理を行う処理部と、

前記処理部からの前記信号処理後の前記周波数制御データにより設定される発振周波数

の前記発振信号を生成する発振信号生成回路と、

レジスター部と、

を含み、

前記位相比較の後の位相比較結果データに対してオフセット調整が行われ、

前記レジスター部は、

前記位相比較結果データをモニターデータとして記憶する第1のレジスターを含み、

テストモードにおいて、前記位相比較結果データを模擬するテストデータがオフセット

調整データとして入力され、

前記第1のレジスターには、前記位相比較部による前記位相比較の後の前記位相比較結果

データが前記モニターデータとして記憶されることを特徴とする回路装置。

## 【請求項 2】

請求項1において、

前記レジスター部は、

G P S (Global Positioning System) 用又は U T C (Coordinated Universal Time)

用のいずれか一方のオフセット調整データである第1のオフセット調整データが設定され

10

20

る第 2 のレジスターと、

前記基準信号と前記発振信号の位相差を調整するための第 2 のオフセット調整データが設定される第 3 のレジスターと、

の少なくとも 1 つを含むことを特徴とする回路装置。

【請求項 3】

請求項 2 に記載された回路装置において、

前記処理部は、

前記第 1 のオフセット調整データ及び前記第 2 のオフセット調整データの少なくとも一方に基づいて前記位相比較結果データに対する前記オフセット調整を行い、前記オフセット調整された前記位相比較結果データに基づいて前記周波数制御データを生成することを特徴とする回路装置。 10

【請求項 4】

請求項 2 又は 3 に記載された回路装置において、

前記第 2 のレジスターには、前記 GPS 用と前記 UTC 用で異なるオフセット調整データが前記第 1 のオフセット調整データとして設定されることを特徴とする回路装置。

【請求項 5】

請求項 4 に記載された回路装置において、

前記 GPS 用のオフセット調整データは、前記基準信号と前記入力信号の間の位相差を GPS 用の所定値に調整するオフセット調整データであり、

前記 UTC 用のオフセット調整データは、前記基準信号と前記入力信号の間の位相差を UTC 用の所定値に調整するオフセット調整データであることを特徴とする回路装置。 20

【請求項 6】

請求項 1 乃至 5 のいずれか一項に記載された回路装置において、

前記位相比較部は、

前記入力信号でカウント動作を行うカウンターを含み、前記基準信号の n 周期 (n は 1 以上の整数) における前記カウンターのカウント値と前記カウント値の期待値とを整数で比較する前記位相比較を行うことを特徴とする回路装置。

【請求項 7】

請求項 1 乃至 6 のいずれか一項に記載された回路装置において、

前記処理部は、

前記信号処理として、温度補償処理、エージング補正処理、及び前記発振信号生成回路が有する可変容量キャパシターの容量特性の補正処理の少なくとも 1 つを行うと共に、前記オフセット調整を行うことを特徴とする回路装置。 30

【請求項 8】

請求項 7 に記載された回路装置において、

前記処理部は、

前記位相比較の結果である位相誤差データに対するデジタルフィルター処理を行うことを特徴とする回路装置。

【請求項 9】

請求項 1 乃至 7 のいずれか一項に記載された回路装置において、

デジタルインターフェース部を含み、

前記発振信号生成回路は、

第 1 のモードでは、前記位相比較の結果に基づく前記周波数制御データで前記発振信号を生成し、

第 2 のモードでは、前記デジタルインターフェース部を介して入力される外部生成周波数制御データに基づく前記周波数制御データで前記発振信号を生成することを特徴とする回路装置。 40

【請求項 10】

請求項 1 乃至 9 のいずれか一項に記載された回路装置において、

前記発振信号を生成するための振動子が接続される端子を含み、 50

前記発振信号は、前記端子から出力される信号であることを特徴とする回路装置。

**【請求項 1 1】**

請求項 1 乃至 9 のいずれか一項に記載された回路装置と、

前記発振信号を生成するための振動子と、

を含むことを特徴とする発振器。

**【請求項 1 2】**

請求項 1 乃至 10 のいずれか一項に記載の回路装置を含むことを特徴とする電子機器。

**【請求項 1 3】**

請求項 1 乃至 10 のいずれか一項に記載の回路装置を含むことを特徴とする移動体。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

本発明は、回路装置、発振器、電子機器及び移動体等に関する。

**【背景技術】**

**【0002】**

従来より、O C X O (oven controlled crystal oscillator)、T C X O (temperature compensated crystal oscillator) 等の発振器が知られている。このような発振器を基準信号源として用いる基地局、ネットワークルーター、測定機器等では、発振器を含むPLL (Phase Locked Loop) 回路を構成し、G P S 信号等の基準信号に対して発振器の発振信号を同期させている。

20

**【0003】**

PLL 回路の従来技術が、例えば特許文献 1 に開示されている。特許文献 1 では、位相比較器が基準信号とフィードバック信号の位相差に対応する位相差パルスを出力し、T D C (Time to Digital Converter) が位相差パルスをデジタル値に変換し、そのデジタル値に基づいてD C O (Digitally Controlled Oscillator) が発振する。このような構成では、位相差パルスを生成する前段の回路のスルーレートが低い場合に、ゼロ近傍の微小な位相差に対応する細い位相差パルスがT D C に伝達されない可能性がある。特許文献 1 では、ループのいずれかの位置にオフセット値を加算し、ロック時でもゼロでない位相差の基準信号とフィードバック信号がT D C に入力されるようにして、確実に位相差パルスを伝達できるようにしている。

30

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献 1】特開 2009 - 268047 号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

上記特許文献 1 のように、位相差パルスを生成する前段の回路のスルーレートが低い場合であっても確実に位相差パルスを伝達できるようにするだけでなく、基準信号と発振信号との位相差を所望の値に設定したい場合がある。或いは、オフセット調整を利用した動作テストを行いたい場合がある。具体的には、オフセット調整データとしてテストデータを入力し、その場合のPLL 回路の動作を検査したい場合がある。

40

**【0006】**

本発明の幾つかの態様によれば、基準信号と発振信号との位相差を所望の値に設定できる、又はオフセット調整を利用した動作テストが可能な回路装置、発振器、電子機器及び移動体等を提供できる。

**【課題を解決するための手段】**

**【0007】**

本発明は、上記の課題の少なくとも一部を解決するためになされたものであり、以下の形態又は態様として実現することが可能である。

50

**【 0 0 0 8 】**

本発明の一態様は、発振信号に基づく入力信号と基準信号との位相比較を行う位相比較部と、前記位相比較の結果に基づく周波数制御データに対して信号処理を行う処理部と、前記処理部からの前記信号処理後の前記周波数制御データにより設定される発振周波数の前記発振信号を生成する発振信号生成回路と、レジスター部と、を含み、前記位相比較の後の位相比較結果データに対してオフセット調整が行われ、前記レジスター部は、前記位相比較結果データをモニターデータとして記憶する第1のレジスターと、G P S (Global Positioning System)用又はU T C (Coordinated Universal Time)用のいずれか一方のオフセット調整データである第1のオフセット調整データが設定される第2のレジスターと、前記基準信号と前記発振信号の位相差を調整するための第2のオフセット調整データが設定される第3のレジスターと、の少なくとも1つを含む回路装置に関係する。

**【 0 0 0 9 】**

このようにすれば、第2のレジスターにG P S用又はU T C用のいずれか一方のオフセット調整データが設定されることで、基準信号と発振信号の位相差を、基準信号の種類に応じた所望の値に設定できる。また、第3のレジスターに基準信号と発振信号の位相差を調整するためのオフセット調整データが設定されることで、基準信号と発振信号の位相差を任意の所望の値に設定できる。また、第1のレジスターが位相比較結果データをモニターデータとして記憶することで、そのモニターデータを外部装置に出力可能になる。これにより、P L L回路の動作を検査できるようになる。

**【 0 0 1 0 】**

また本発明の一態様では、回路装置は、前記発振信号を生成するための振動子が接続可能な端子を含み、前記発振信号は、前記端子から出力される信号であってもよい。

**【 0 0 1 1 】**

例えば発振信号生成回路から位相比較部へのフィードバック経路での遅延等により、回路装置の端子から出力される発振信号と基準信号との間に位相差が発生する可能性がある。この点、本発明の一態様によれば、第3のレジスターに設定されるオフセット調整データにより、その位相差を調整できる。

**【 0 0 1 2 】**

また本発明の一態様では、テストモードにおいて、前記位相比較結果データを模擬するテストデータがオフセット調整データとして入力され、前記第1のレジスターには、前記位相比較部による前記位相比較の後の前記位相比較結果データが前記モニターデータとして記憶されてもよい。

**【 0 0 1 3 】**

このようにすれば、オフセット調整データの代わりに位相比較結果データを模擬するテストデータを入力し、その場合の位相比較結果データをモニターすることが可能となる。例えばテスト装置等の外部装置が位相比較結果データをモニターし、P L L回路の動作を検査することができる。

**【 0 0 1 4 】**

また本発明の一態様では、前記処理部は、前記第1のオフセット調整データ及び前記第2のオフセット調整データの少なくとも一方に基づいて前記位相比較結果データに対する前記オフセット調整を行い、前記オフセット調整された前記位相比較結果データに基づいて前記周波数制御データを生成してもよい。

**【 0 0 1 5 】**

このように、処理部がオフセット調整データに基づいて位相比較結果データに対するオフセット調整を行うことで、処理部が生成した周波数制御データに基づく発振信号と基準信号との間に、オフセット調整データに対応する位相差が付加される。このようにして、オフセット調整データによる位相差の調整が実現される。

**【 0 0 1 6 】**

また本発明の一態様では、前記第2のレジスターには、前記G P S用と前記U T C用で異なるオフセット調整データが前記第1のオフセット調整データとして設定されてもよい

10

20

30

40

50

。

### 【 0 0 1 7 】

G P S の時刻パルスと U T C の時刻パルスの間には時間差がある。本発明の一態様によれば、G P S 用と U T C 用で異なるオフセット調整データが設定されることで、この時間差に相当する位相差を意図的に発振信号に付加できる。これにより、G P S 、 U T C のいずれの時刻パルスを基準信号として用いた場合であっても、精密な時刻同期が可能となる。

。

### 【 0 0 1 8 】

また本発明の一態様では、前記 G P S 用のオフセット調整データは、前記基準信号と前記入力信号の間の位相差を G P S 用の所定値に調整するオフセット調整データであり、前記 U T C 用のオフセット調整データは、前記基準信号と前記入力信号の間の位相差を U T C 用の所定値に調整するオフセット調整データであってもよい。

10

### 【 0 0 1 9 】

このように、G P S 用の所定値に対応する G P S 用のオフセット調整データ、 U T C 用の所定値に対応する U T C 用のオフセット調整データが設定されることで、G P S 、 U T C のいずれの時刻パルスを基準信号として用いた場合であっても、精密な時刻同期が可能となる。

### 【 0 0 2 0 】

また本発明の一態様では、前記位相比較部は、前記入力信号でカウント動作を行うカウンターを含み、前記基準信号の n 周期（ n は 1 以上の整数）における前記カウンターのカウント値と前記カウント値の期待値とを整数で比較する前記位相比較を行ってもよい。

20

### 【 0 0 2 1 】

本発明の一態様によれば、位相比較部が、カウンターのカウント値と期待値とを整数で比較する位相比較を行ことで、簡素な構成で位相比較部を構成できる。これにより、回路装置を小規模化できる。また本発明の一態様によれば、位相比較部が、基準信号の n 周期におけるカウンターのカウント値とカウント値の期待値とを整数で比較する。そして n は 2 以上に設定可能である。これにより、位相比較部により検出される位相誤差の時間分解能を小さくできる。即ち、位相比較部を含む P L L 回路のロック状態における位相誤差を抑制できる。

### 【 0 0 2 2 】

30

また本発明の一態様では、前記処理部は、前記信号処理として、温度補償処理、エージング補正処理、及び前記発振信号を生成するための振動子に接続される可変容量キャパシターの容量特性の補正処理の少なくとも 1 つを行うと共に、前記オフセット調整を行ってもよい。

### 【 0 0 2 3 】

このように処理部がオフセット調整を行うことで、基準信号に対して発振信号に所望の位相差を付加できる。また、そのオフセット調整と共に、処理部は温度補償処理、エージング補正処理、容量特性補正処理等を実行する。例えば、D S P 等のハードウェアを共用して複数の処理を実行することが可能である。これにより、各処理を個別のハードウェアで構成する場合に比べて処理部の回路を小規模化できる。

40

### 【 0 0 2 4 】

また本発明の一態様では、前記処理部は、前記位相比較の結果である位相誤差データに対するデジタルフィルター処理を行ってもよい。

### 【 0 0 2 5 】

このように処理部が位相誤差データに対するデジタルフィルター処理を行うことで、処理部が位相誤差データから周波数制御データを生成できる。

### 【 0 0 2 6 】

また本発明の一態様では、回路装置は、デジタルインターフェース部を含み、前記発振信号生成回路は、第 1 のモードでは、前記位相比較の結果に基づく前記周波数制御データで前記発振信号を生成し、第 2 のモードでは、前記デジタルインターフェース部を介して

50

入力される外部生成周波数制御データに基づく前記周波数制御データで前記発振信号を生成してもよい。

**【0027】**

このようにすれば、例えばユーザーの所望の使い方に応じてモードを選択し、内部PLLによる発振周波数の制御と、外部PLLによる発振周波数の制御とを切り替えることが可能となる。

**【0028】**

また本発明の他の態様は、上記のいずれかに記載された回路装置と、前記発振信号を生成するための振動子と、を含む発振器に関係する。

**【0029】**

また本発明の更に他の態様は、上記のいずれかに記載された回路装置を含む電子機器に関係する。

**【0030】**

また本発明の更に他の態様は、上記のいずれかに記載された回路装置を含む移動体に関係する。

**【図面の簡単な説明】**

**【0031】**

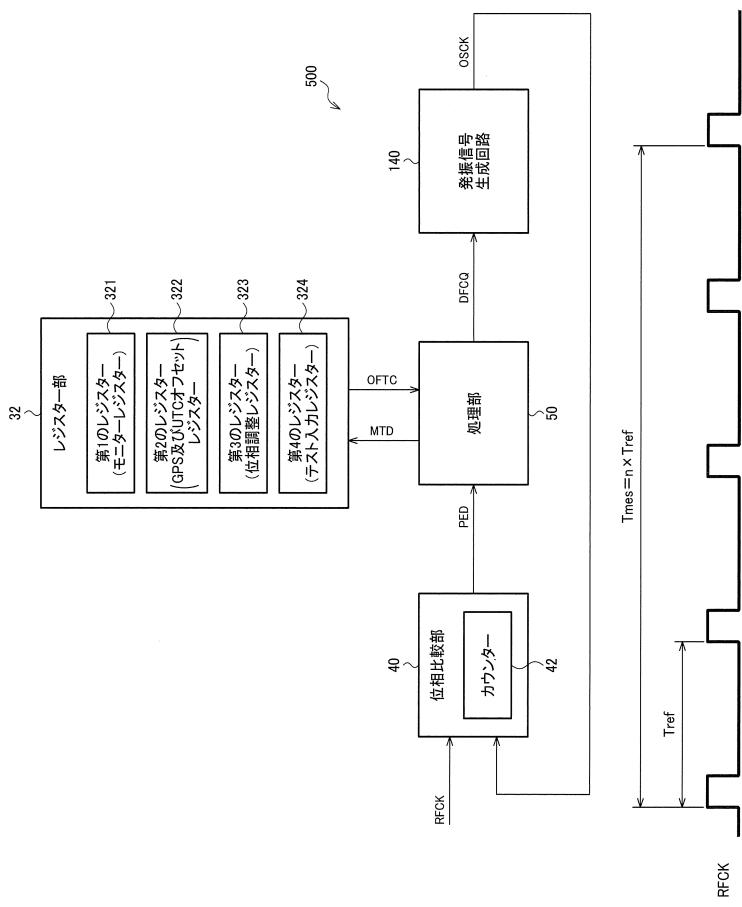

【図1】図1は、本実施形態の回路装置の構成例である。

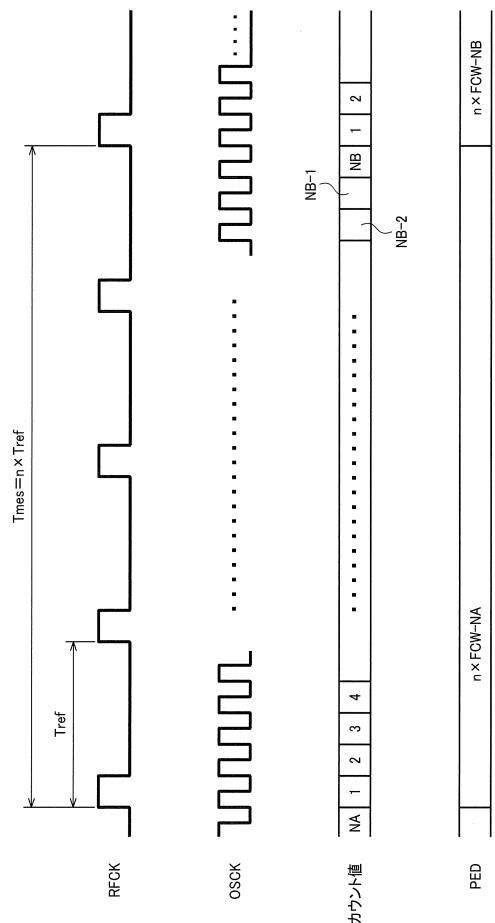

【図2】図2は、位相比較部の動作を説明するタイミングチャートである。

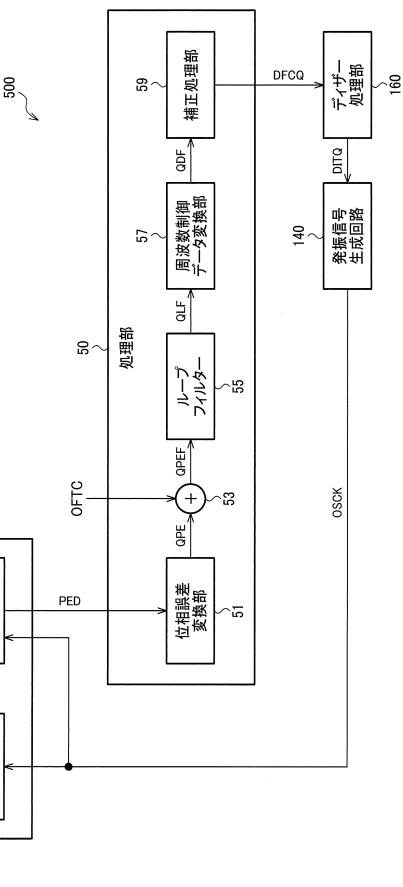

【図3】図3は、計測時間と時間分解能の関係を示す図である。

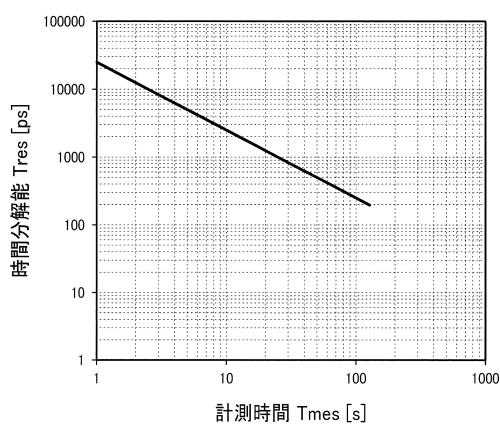

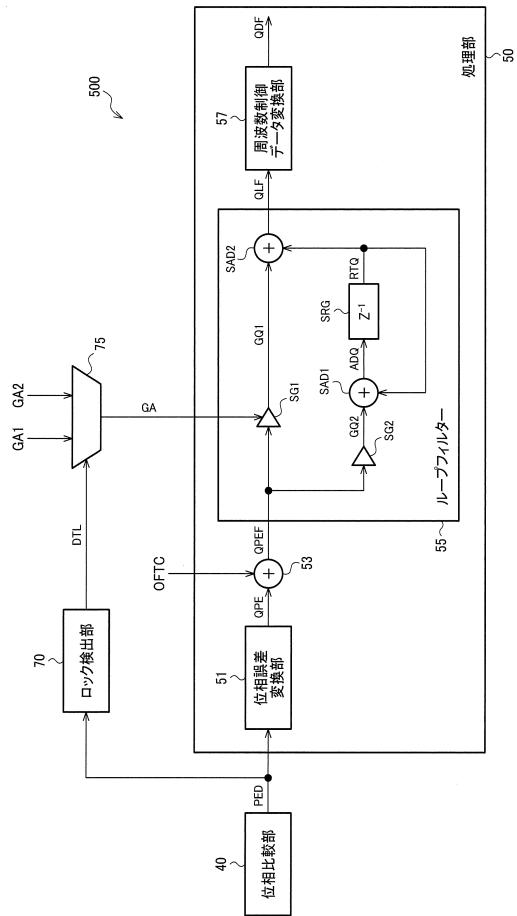

【図4】図4は、本実施形態の回路装置の第1の詳細な構成例、位相比較部の詳細な構成例、処理部の第1の詳細な構成例である。

【図5】図5は、PLL回路の動作テストを行うテストモードでの動作を説明する図である。

【図6】図6は、本実施形態の回路装置の第2の詳細な構成例、ループフィルターの詳細な構成例である。

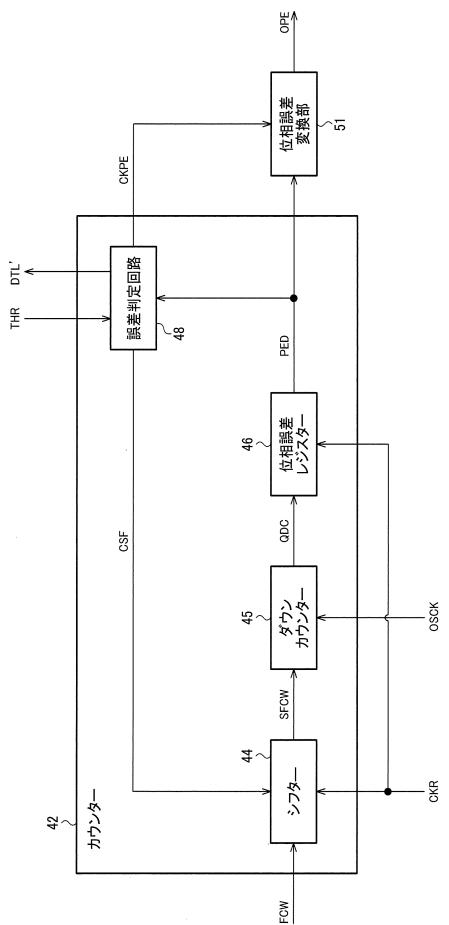

【図7】図7は、カウンターの変形構成例である。

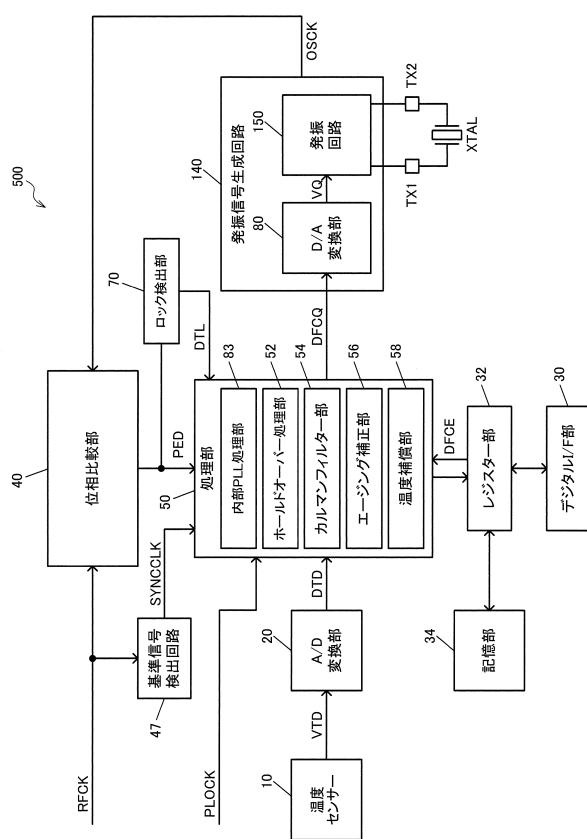

【図8】図8は、本実施形態の回路装置の第3の詳細な構成例である。

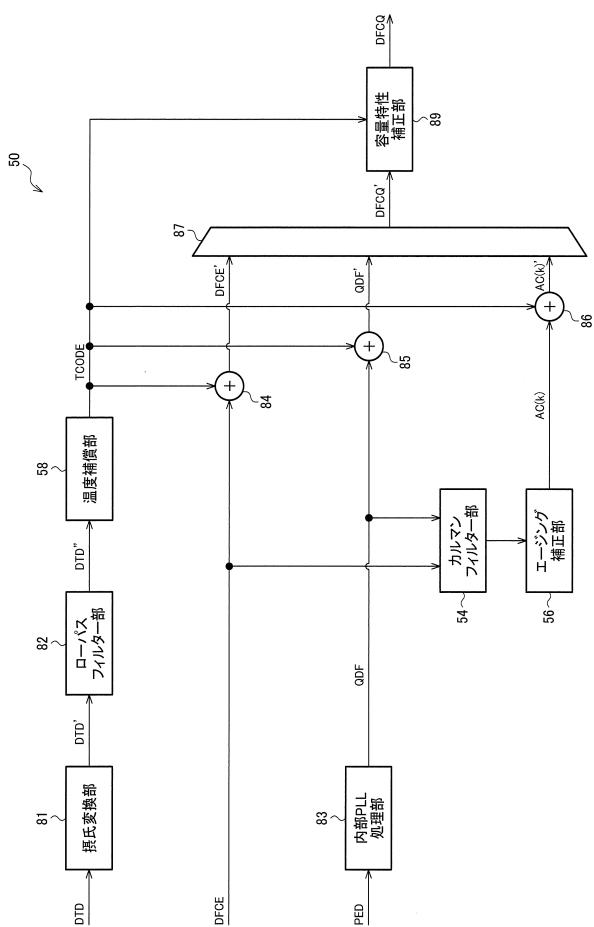

【図9】図9は、処理部の第2の詳細な構成例である。

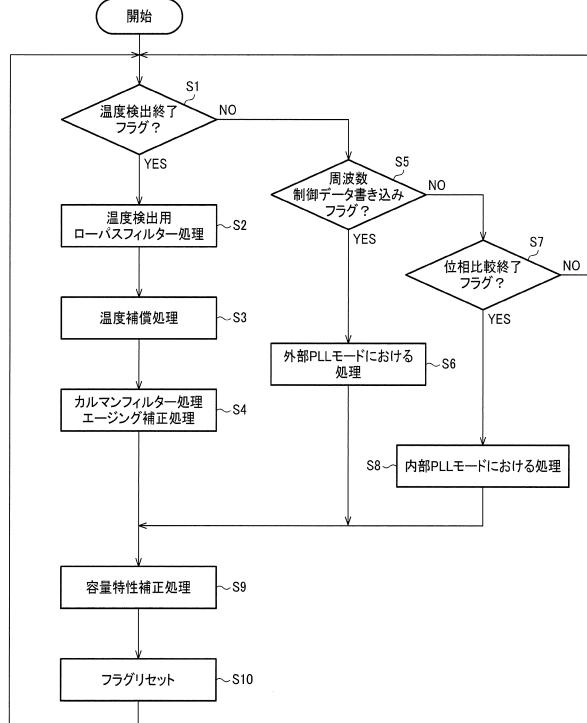

【図10】図10は、処理部が行う処理のフローチャートである。

【図11】図11は、温度検出用ローパスフィルター処理の詳細なフローチャートである。

【図12】図12は、カルマンフィルター処理及びエージング補正処理の詳細なフローチャートである。

【図13】図13は、外部PLLモードにおける処理の詳細なフローチャートである。

【図14】図14は、内部PLLモードにおける処理の詳細なフローチャートである。

【図15】図15は、処理部の第3の詳細な構成例である。

【図16】図16は、エージングによる発振周波数の変動の測定結果の例を示す図である。

【図17】図17は、エージング補正部の詳細な構成例である。

【図18】図18は、発振回路の構成例である。

【図19】図19は、本実施形態の変形例の回路装置の構成例である。

【図20】図20は、ダイレクト・デジタル・シンセサイザー方式の場合の回路構成例である。

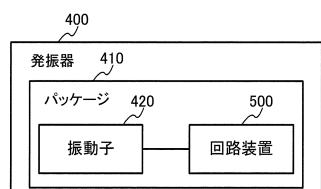

【図21】図21は、本実施形態の回路装置を含む発振器の構成例である。

【図22】図22は、本実施形態の回路装置を含む電子機器の構成例である。

【図23】図23は、本実施形態の回路装置を含む移動体の例である。

【図24】図24は、電子機器の1つである基地局の構成例である。

**【発明を実施するための形態】**

**【0032】**

10

20

30

40

50

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

### 【0033】

例えば以下では位相比較部が整数での位相比較を行うカウント方式である場合を例に説明するが、本発明はカウント方式以外（小数での位相比較を行う方式。例えばTDCを用いた方式）の位相比較部を用いるPLL回路にも適用できる。

### 【0034】

#### 1. 構成

図1は、本実施形態の回路装置500の構成例である。回路装置500は、レジスター部32（レジスター回路）、位相比較部40（位相比較回路）、処理部50（処理回路）、発振信号生成回路140を含む。10

### 【0035】

位相比較部40は、発振信号生成回路140が生成する発振信号OSCKの位相と基準信号RFCKの位相とを比較し、その結果を位相誤差データPEDとして出力する。具体的には、位相比較部40は、発振信号OSCKのクロック数をカウントするカウンター42を含み、そのカウンター42のカウント値に基づいて位相誤差データPEDを出力する。ここで、基準信号RFCKは、所定タイミング或いは所定間隔で入力されるパルス信号であり、例えば時刻等の基準となる信号である。例えば、基準信号RFCKは、GPS受信器が出力する基準信号（時刻パルス）や、ネットワークの物理層回路が出力する基準信号（クロック信号）である。20

### 【0036】

図2は、位相比較部40の動作を説明するタイミングチャートである。図2に示すように、基準信号RFCKの周期をTrefとする。例えばGPSの基準信号ではTref=1秒である。カウンター42は、例えば基準信号RFCKの立ち上がりエッジでカウント値がリセットされ、そのエッジから計測時間Tmes（計測期間）の間、発振信号OSCKのクロック数をカウントする。計測時間Tmesは位相比較を行う周期であり、基準信号RFCKのn周期である。即ち、計測時間Tmesの間に蓄積された位相誤差を検出することになる。後述するように、nは2以上に設定可能な整数である。計測時間Tmesが終了したときのカウント値をNBとした場合、期待値n×FCWとカウント値NBとの差分（n×FCW-NB）が位相誤差データPEDとして出力される。FCWは、発振信号OSCKの周波数を設定するための周波数設定データである。30

### 【0037】

なお、ここではカウンター42が初期値「0」からカウントアップする場合を例に説明したが、これに限定されない。例えば後述するように、期待値n×FCWを初期値としてカウントダウンし、計測時間Tmesが終了したときのカウント値が（n×FCW-NB）となるように構成してもよい。

### 【0038】

処理部50は種々のデジタル信号処理を行う。具体的には処理部50は、位相比較部40からの位相誤差データPEDをデジタル信号処理して、発振信号OSCKの周波数を制御するための周波数制御データDFCQを生成する。例えば処理部50は、カウント値と期待値n×FCWとの差である位相誤差データPEDを、時間を単位とする位相誤差データに変換する処理や、位相誤差データに対するループフィルター処理（デジタルフィルター処理）を行う。また処理部50は、位相誤差データに対するオフセット調整処理（基準信号RFCKと発振信号OSCKとの間のオフセット調整処理）や、ループフィルター処理後の周波数制御データに対する種々の補正処理等を行ってもよい。補正処理は、例えば振動子の発振周波数の温度依存性を補償する処理（温度補償処理）や、発振周波数を制御するための可変容量キャパシター（バリキャップ等）の容量特性を補正する処理（容量特性補正処理）である。或いは、補正処理として、ホールドオーバー時に発振器が自走発振している状態での発振周波数の経時変化を補正する処理（エージング補正処理）等を行つ4050

てもよい。処理部 50 は、ゲートアレイ等の ASIC 回路により実現してもよいし、プロセッサー（例えば CPU (Central Processing Unit)、DSP (Digital Signal Processor) 等）とプロセッサー上で動作するプログラム（プログラムモジュール）により実現してもよい。

#### 【0039】

発振信号生成回路 140 は、周波数制御データ DFCQ により設定される発振周波数の発振信号 OSCK を生成する。例えば発振信号生成回路 140 は、処理部 50 からの周波数制御データ DFCQ と振動子を用いて、周波数制御データ DFCQ により設定される発振周波数の発振信号 OSCK を生成する。一例としては、発振信号生成回路 140 は、周波数制御データ DFCQ により設定される発振周波数で振動子を発振させて、発振信号 OSCK を生成する。10

#### 【0040】

なお発振信号生成回路 140 は、ダイレクト・デジタル・シンセサイザー方式で発振信号 OSCK を生成する回路であってもよい。例えば振動子（固定発振周波数の発振源）の発振信号をリファレンス信号として、周波数制御データ DFCQ で設定される発振周波数の発振信号 OSCK をデジタル的に生成してもよい。或いは発振信号生成回路 140 は、振動子を用いずに、周波数制御データ DFCQ により設定される発振周波数の発振信号 OSCK を生成する回路であってもよい。例えば発振信号生成回路 140 は、周波数制御データ DFCQ を制御電圧に変換する D/A 変換回路と、その制御電圧で設定される発振周波数で発振する電圧制御発振回路（VCO）で構成されてもよい。或いは、周波数制御データ DFCQ で容量が可変に制御される可変容量を含む CR 発振回路で構成されてもよい。この CR 発振回路は、可変容量の容量により設定される発振周波数で発振する。20

#### 【0041】

以上の位相比較部 40、処理部 50、発振信号生成回路 140 により PLL 回路が構成され、基準信号 RFCK に同期した発振信号 OSCK が生成される。即ち、処理部 50 は PI (Proportional-Integral) 制御等によって位相誤差データ PED に対して負帰還制御を行い、位相誤差を小さくする（ゼロに近づける）周波数制御データ DFCQ を生成する。そして、その周波数制御データ DFCQ に基づいて発振信号生成回路 140 が発振信号 OSCK を生成することで、基準信号 RFCK に同期した発振信号 OSCK が生成される。30

#### 【0042】

レジスター部 32 は、第 1 のレジスター 321（モニターレジスター）、第 2 のレジスター 322（GPS 及び UTC オフセットレジスター）、第 3 のレジスター 323（位相調整レジスター）、第 4 のレジスター 324（テスト入力レジスター）を含む。

#### 【0043】

まず第 2 のレジスター 322 について説明する。基準信号 RFCK が GPS (Global Positioning System) 受信器から入力される時刻パルスである場合には、GPS 用のオフセット調整データが第 2 のレジスター 322 に記憶される。また基準信号 RFCK がネットワーク等から入力される UTC (Coordinated Universal Time) の時刻パルスである場合には、UTC 用のオフセット調整データが第 2 のレジスター 322 に記憶される。処理部 50 は、第 2 のレジスター 322 に記憶されたオフセット調整データを位相比較結果データ（例えば図 4 では QPE）に加算処理する。これにより、基準信号 RFCK と発振信号 OSCK の間には、GPS 用又は UTC 用のオフセット調整データに対応する位相差（オフセット）が付加されることになる。40

#### 【0044】

GPS の時刻パルスと UTC の時刻パルスの間には所定の時間差（例えば 20 ナノ秒）がある。そのため、GPS の時刻パルスに同期させた発振器と、UTC の時刻パルスに同期させた発振器の間には、その時間差に相当する時刻の誤差が生じることになる。本実施形態では、基準信号 RFCK の種類に応じて基準信号 RFCK と発振信号 OSCK の位相差を調整できるので、複数の発振器の間で高精度な時刻同期を行うことが可能となる。例50

えば、G P S用又のオフセット調整データは、位相差ゼロに対応したオフセット調整データであり、U T C用のオフセット調整データは、上記所定の時間差に対応したオフセット調整データである。

#### 【 0 0 4 5 】

第3のレジスター323には、基準信号R F C Kと発振信号O S C Kの位相差を調整するためのオフセット調整データが記憶される。処理部50は、第3のレジスター323に記憶されたオフセット調整データを位相比較結果データに加算処理する。これにより、基準信号R F C Kと発振信号O S C Kの間に、任意の位相差（オフセット）を付加することができる。

#### 【 0 0 4 6 】

位相比較部40の入力ノードに到達する発振信号O S C Kの位相は、発振信号生成回路140が出力する発振信号O S C Kの位相と異なっている可能性がある。例えば、バッファーハウスを通過することによる遅延や、信号線の寄生容量及び寄生抵抗による遅延等により、位相が変化する。そのため位相比較部40の入力ノードに到達する発振信号O S C Kと基準信号R F C Kの位相差がゼロになったとしても、発振信号生成回路140が出力する発振信号O S C Kと基準信号R F C Kとの間には位相差が生じる可能性がある。本実施形態では、基準信号R F C Kと発振信号O S C Kの位相差を任意に調整できるので、このような位相差を微調整できる。

#### 【 0 0 4 7 】

第4のレジスター324には、位相比較結果データを模擬するテストデータが記憶される。処理部50は、位相比較結果データに変えて、第4のレジスター324に記憶されたテストデータに対して信号処理を行う。これにより、テストデータを位相比較結果データとしてPLL回路を動作させた場合の位相誤差データP E Dが位相比較部40から出力されることになる。第1のレジスター321には、処理部50からの位相比較結果データがモニターデータM T Dとして記憶される。なお、第1のレジスター321には、位相比較部40からの位相誤差データP E DがモニターデータM T Dとして記憶されてもよい。なお、第3のレジスター323が第4のレジスター324を兼ね、テストモード時にテストデータを記憶してもよい。この場合、第4のレジスター324は省略される。

#### 【 0 0 4 8 】

例えば回路装置500の出荷前検査等における検査項目の1つとして、PLL回路の動作テストが考えられる。本実施形態では、位相比較結果データを模擬するテストデータを入力することが可能であり、そのテストデータに対して期待した位相誤差データP E Dが得られるか否かを検査できる。

#### 【 0 0 4 9 】

なお、位相比較結果データは、位相比較部40による位相比較の後のデータのことである。位相比較結果データは、位相比較の後にループ内で生成されるデータであればよい。例えば位相比較結果データは、位相比較部40が出力する位相誤差データP E Dに対して何らかの処理（例えば変換処理、乗算処理、加算処理、フィルター処理等）がされたデータである。或いは、位相比較結果データは、位相比較部40が出力する位相誤差データP E Dであってもよい。第2のレジスター322、第3のレジスター323、第4のレジスター324には、基準信号R F C Kと発振信号O S C Kの位相差を、それに相当する位相比較結果データに換算したオフセット調整データが記憶される。

#### 【 0 0 5 0 】

レジスター部32から処理部50に入力されるオフセット調整データO F T Cは、第2のレジスター322、第3のレジスター323、第4のレジスター324に記憶されたオフセット調整データの少なくとも1つである。例えば、オフセット調整データO F T Cは、3つのレジスター値のいずれかである。或いは、複数のレジスター値がオフセット調整データO F T Cとして処理部50に入力され、それら複数のレジスター値が位相比較結果データに加算されてもよい。

#### 【 0 0 5 1 】

10

20

30

40

50

第2のレジスター322、第3のレジスター323、第4のレジスター324には、例えば図8のデジタルインターフェース部30を介して外部装置（例えばCPU、テスト装置等）からデータが書き込まれる。或いは、図8の記憶部34等にデータが予め記憶されており、そのデータが第2のレジスター322、第3のレジスター323、第4のレジスター324に読み出されてもよい。また第1のレジスター321は、例えば図8のデジタルインターフェース部30を介して外部装置からアクセス可能となっており、外部装置から位相誤差データP E Dを読み出される。

#### 【0052】

以上の実施形態では、回路装置500は、発振信号O S C Kに基づく入力信号と基準信号R F C Kとの位相比較を行う位相比較部40と、位相比較の結果に基づく周波数制御データに対して信号処理を行う処理部50と、処理部50からの信号処理後の周波数制御データD F C Qにより設定される発振周波数の発振信号O S C Kを生成する発振信号生成回路140と、レジスター部32と、を含む。そして、位相比較の後の位相比較結果データに対してオフセット調整が行われる。レジスター部32は、位相比較結果データをモニターデータM T Dとして記憶する第1のレジスター321と、G P S用又はU T C用のいずれか一方のオフセット調整データである第1のオフセット調整データが設定される第2のレジスター322と、基準信号R F C Kと発振信号O S C Kの位相差を調整するための第2のオフセット調整データが設定される第3のレジスター323と、の少なくとも1つを含む。

#### 【0053】

このようにすれば、基準信号R F C Kと発振信号O S C Kとの位相差を所望の値に設定できる。また、オフセット調整を利用した動作テストが可能となる。具体的には、第2のレジスター322にG P S用又はU T C用のいずれか一方のオフセット調整データが設定されることで、基準信号R F C Kと発振信号O S C Kの位相差を、基準信号R F C Kの種類に応じた所望の値に設定できる。上述したように、異なる基準信号を用いる複数の発振器の間で高精度に時刻を同期できるようになる。また、第3のレジスター323に基準信号R F C Kと発振信号O S C Kの位相差を調整するためのオフセット調整データが設定されることで、基準信号R F C Kと発振信号O S C Kの位相差を任意の所望の値に設定できる。上述したように、発振信号O S C Kの伝達経路における遅延を含めた位相誤差を微調整できるようになる。また、第1のレジスター321が位相比較結果データをモニターデータM T Dとして記憶することで、そのモニターデータM T Dをテスト装置等の外部装置に出力可能になる。これにより、P L L回路の動作を検査できるようになる。

#### 【0054】

ここで発振信号O S C Kに基づく入力信号は、例えば図1で説明したように発振信号O S C Kそのものである。但しこれに限定されず、入力信号は発振信号O S C Kをバッファリングした信号であってもよいし、発振信号O S C Kを分周した信号であってもよい。図1では処理部50がオフセット調整を行う場合を例に説明したが、これに限定されない。例えば、位相比較部40がオフセット調整データを位相誤差データP E Dに加算し、オフセット調整を行ってもよい。また図1ではレジスター部32が第1のレジスター321、第2のレジスター322、第3のレジスター323の全てを含む場合を例に説明したが、これに限定されない。例えばレジスター部32が第1のレジスター321、第2のレジスター322、第3のレジスター323のいずれか1つ又はいずれか2つを含んでもよい。また位相比較の結果に基づく周波数制御データに対して信号処理を行うとは、例えば図1で説明したように、処理部50が位相比較部40からの位相誤差データP E Dをループフィルター処理して周波数制御データ（位相比較の結果に基づく周波数制御データ）を生成し、その周波数制御データに対して信号処理を行うことである。なお、これに限定されず、位相比較部40が位相誤差データP E Dを周波数制御データ（位相比較の結果に基づく周波数制御データ）に変換し、その周波数制御データに対して処理部50が信号処理を行ってもよい。

#### 【0055】

10

20

30

40

50

また本実施形態では、回路装置 500 は、発振信号 OSCK を生成するための振動子が接続可能な端子を含んでもよい。そして発振信号 OSCK は、その端子から出力される信号であってもよい。

#### 【 0056 】

例えば図 8 で後述するように、発振信号生成回路 140 が発振回路 150 (VCO) を含み、その発振回路 150 と振動子 X T A L が端子 TX1、TX2 を介して接続される。この場合、端子 TX1 又は端子 TX2 から出力される信号が発振信号 OSCK である。

#### 【 0057 】

位相比較部 40 は、発振信号 OSCK に基づく入力信号と基準信号 RFCK との位相比較を行っている。即ち、位相差がゼロとなるように制御されるのは、位相比較部 40 の入力信号である。一方、発振器が組み込まれた基地局等では、回路装置 500 の端子から出力された発振信号 OSCK をクロック信号として用いることになる。そのため、位相比較部 40 へのフィードバック経路での遅延等により発振信号 OSCK と基準信号 RFCK の間に位相差が発生する可能性がある。この点、本実施形態によれば、第 3 のレジスター 323 に設定されるオフセット調整データにより、基準信号 RFCK と、回路装置 500 の端子から出力される発振信号 OSCK との間の位相差を調整（微調整）できる。10

#### 【 0058 】

また本実施形態では、テストモードにおいて、位相比較結果データを模擬するテストデータがオフセット調整データとして回路装置 500 に入力される。そして、第 1 のレジスター 321 には、位相比較部 40 による位相比較の後の位相比較結果データがモニターデータ MTD として記憶される。20

#### 【 0059 】

このようにすれば、オフセット調整データの代わりに位相比較結果データを模擬するテストデータを入力し、その場合の位相比較結果データをモニターすることが可能となる。例えばテスト装置等の外部装置が位相比較結果データをモニターし、PLL 回路の動作を検査することができる。

#### 【 0060 】

ここで、位相比較結果データを模擬するテストデータとは、位相比較部 40 による位相比較の結果として生成される位相比較結果データに相当するテストデータであり、テストモードにおいて位相比較結果データを代替するデータとして入力されるデータのことである。テストデータとしては、任意の位相比較結果データ（固定データ、時系列データ）に相当するデータを入力できる。テストモードは、例えば回路装置 500 の出荷前検査或いは回路装置 500 を組み込んだ電子機器等の出荷前検査等において回路装置 500 の動作を検査する際に設定されるモードである。例えばテスター等の外部装置からレジスター部（例えば図 8 のレジスター部 32）にテストモードが設定される。30

#### 【 0061 】

また本実施形態では、処理部 50 は、第 1 のオフセット調整データ及び第 2 のオフセット調整データの少なくとも一方に基づいて、位相比較結果データに対するオフセット調整を行い、オフセット調整された位相比較結果データに基づいて周波数制御データ DFCQ を生成する。40

#### 【 0062 】

例えば図 4 で後述するように、処理部 50 は、位相比較部 40 からの位相誤差データ PEQ を位相誤差データ QPE に変換する。この位相誤差データ QPE が位相比較結果データに対応する。そして、処理部 50 は位相誤差データ QPE にオフセット調整データ OFTC を加算し、その結果である位相誤差データ QPEF にループフィルター処理等を行つて周波数制御データ DFCQ を生成する。この周波数制御データ DFCQ に基づいて生成される発振信号 OSCK と基準信号 RFCK の間には、オフセット調整データ OFTC に対応する（例えば逆符号の）位相差が生じる。このとき、位相誤差データ QPE は、オフセット調整データ OFTC の逆符号のデータとなり、位相誤差データ QPE とオフセット調整データ OFTC が加算されることによって、位相誤差データ QPEF は（理想的には50

) ゼロとなる。

**【 0 0 6 3 】**

このように、処理部 50 がオフセット調整データに基づいて位相比較結果データに対するオフセット調整を行うことで、処理部 50 が生成した周波数制御データ DFCQ に基づく発振信号 OSCK と基準信号 RFCK との間に、オフセット調整データに対応する位相差が付加される。このようにして、オフセット調整データによる位相差の調整が実現される。

**【 0 0 6 4 】**

また本実施形態では、第 2 のレジスター 322 には、GPS 用と UTC 用で異なるオフセット調整データが第 1 のオフセット調整データとして設定される。

10

**【 0 0 6 5 】**

上述したように、GPS の時刻パルスと UTC の時刻パルスの間には時間差がある。本実施形態によれば、GPS 用と UTC 用で異なるオフセット調整データが設定されることで、この時間差に相当する位相差を意図的に発振信号 OSCK に付加できる。これにより、GPS、UTC のいずれの時刻パルスを基準信号 RFCK として用いた場合であっても、精密な時刻同期が可能となる。

**【 0 0 6 6 】**

具体的には、GPS 用のオフセット調整データは、基準信号 RFCK と発振信号 OSCK に基づく入力信号の間の位相差を GPS 用の所定値に調整するオフセット調整データである。UTC 用のオフセット調整データは、基準信号 RFCK と発振信号 OSCK に基づく入力信号の間の位相差を UTC 用の所定値に調整するオフセット調整データである。

20

**【 0 0 6 7 】**

GPS 用の所定値、UTC 用の所定値は、GPS 及び UTC の規格に応じた値である。或いは、実測値に基づく値であってもよい。例えば GPS の時刻パルスと UTC の時刻パルスの相対的な時間差に基づいて所定値が設定される。例えば、同一時刻を表す GPS の時刻パルスと UTC の時刻パルスの間に 20 ナノ秒の差がある場合、GPS 用の所定値をゼロに設定し、UTC 用の所定値を 20 ナノ秒に設定する。

**【 0 0 6 8 】**

このように、GPS 用の所定値に対応する GPS 用のオフセット調整データ、UTC 用の所定値に対応する UTC 用のオフセット調整データが設定されることで、GPS、UTC のいずれの時刻パルスを基準信号 RFCK として用いた場合であっても、精密な時刻同期が可能となる。

30

**【 0 0 6 9 】**

また本実施形態では、位相比較部 40 は、発振信号 OSCK に基づく入力信号でカウント動作を行うカウンター 42 を含み、基準信号 RFCK の n 周期 (n は 2 以上に設定可能な整数である) におけるカウンター 42 のカウント値とカウント値の期待値  $n \times FCW$  を整数で比較する位相比較を行う。

**【 0 0 7 0 】**

ここで、n は 2 以上に設定可能な整数であるとは、n が固定か可変かに関わらず n が 2 以上の整数に設定できることができるということである。即ち、n が固定である場合、n は 2 以上の整数のいずれかに固定に設定されている。n が可変に設定される場合には、n は 2 以上の整数を含む複数の整数のいずれかに可変に設定される。その設定可能な複数の整数には更に 1 が含まれていてもよい。n は回路装置 500 の外部からレジスター部 (例えば図 8 のレジスター部 32) に設定されてもよいし、或いは図 7 等で後述するように回路装置 500 が自ら設定してもよい。或いは n は不揮発性メモリー (例えば図 8 のレジスター部 32) に記憶された設定値やヒューズ等によって設定されてもよい。

40

**【 0 0 7 1 】**

本実施形態によれば、位相比較部 40 が、カウンター 42 のカウント値と期待値とを整数で比較する位相比較を行ことで、簡素な構成で位相比較部 40 を構成できる。また位相比較の結果が整数となるので位相誤差に対する処理を簡素化できる。

50

**【 0 0 7 2 】**

しかしながら、カウント値と期待値とを整数で比較する場合には小数精度での位相誤差を検出できないので、カウント値と期待値とを小数で比較する場合に比べて位相誤差の時間分解能（検出可能な最小の位相誤差）が大きくなってしまう。この点、本実施形態によれば、位相比較部 4 0 が、基準信号 R F C K の n 周期におけるカウンター 4 2 のカウント値とカウント値の期待値  $n \times F C W$  を整数で比較する。そして n は 2 以上に設定可能である。これにより、位相誤差の時間分解能を小さくできる。

**【 0 0 7 3 】**

具体的には、位相誤差の時間分解能  $T r e s$  は下式（1）で表される。 $T o u t$  は発振信号 O S C K の周期である。図 3 は、計測時間  $T m e s$  と時間分解能  $T r e s$  の関係を示す図である。図 3 には、基準信号 R F C K の周期  $T r e f$  が 1 秒であり、発振周波数（ $1 / T o u t$ ）が 4 0 M H z である場合の例を示す。

**【 数 1 】**

$$T r e s = \frac{T o u t}{T m e s / T r e f} = \frac{T o u t}{n} \quad \cdots (1)$$

**【 0 0 7 4 】**

上式（1）、図 3 から、n を 2 以上に設定して計測時間  $T m e s$  を大きくすることによって時間分解能  $T r e s$  を小さくできることが分かる。即ち、本実施形態では n が 2 以上に設定可能であることによって、基準信号 R F C K に対して発振信号を高精度に同期させることができるとなり、発振周波数を高精度化できる。

**【 0 0 7 5 】**

また本実施形態では、位相比較部 4 0 を含む P L L 回路の少なくともロック状態において、n が k 1（k 1 は 2 以上の整数）に設定されてもよい。

**【 0 0 7 6 】**

このように、ロック状態において n が 2 以上の整数に設定されることで、ロック状態において位相誤差の時間分解能を小さくなり、基準信号 R F C K に対して高精度に同期した発振信号を生成することができる。

**【 0 0 7 7 】**

また本実施形態では、P L L 回路の起動時に、n が k 2（k 2 は 1 以上で k 1 より小さい整数）に設定されてもよい。P L L 回路の起動時とは、P L L 回路が基準信号 R F C K に対して発振信号 O S C K を同期させる動作を開始してから、基準信号 R F C K に対して発振信号 O S C K が同期するまでの間（いわゆる引き込み状態）である。

**【 0 0 7 8 】**

また本実施形態では、テストモードにおいて、n が k 3（k 3 は 1 以上で k 1 より小さい整数）に設定される。

**【 0 0 7 9 】**

このように、P L L 回路の起動時或いはテストモードにおいて、ロック状態での  $n = k 1$  よりも小さい n（k 2、k 3）が設定されることで、計測時間  $T m e s$ （即ち位相比較の周期）が短くなり、同期動作を開始してからロック状態となるまでの時間を短縮できる。即ち、図 6 で後述するいわゆるギアシフトと同様の効果を得ることが可能となる。

**【 0 0 8 0 】**

また本実施形態では、n が可変に設定されてもよい。例えば図 7 で後述するように、回路装置 5 0 0 が自ら n を可変に設定してもよい。或いは、回路装置 5 0 0 の外部からレジスター部等を介して n が可変に設定されてもよい。

**【 0 0 8 1 】**

n が可変に設定されることで、ロック状態においては発振周波数の高精度化のために n を 2 以上の大きな整数に設定できる。一方、起動時やテストモードでの引き込み時間を短縮するために n をロック状態よりも小さい整数に設定できる。

10

20

30

40

50

**【 0 0 8 2 】**

また本実施形態では、処理部 50 は、信号処理（デジタル信号処理）として、温度補償処理、エージング補正処理、及び発振信号 O S C K を生成するための振動子に接続される可変容量キャパシターの容量特性の補正処理の少なくとも 1 つを行うと共に、オフセット調整を行う。なお、温度補償処理、エージング補正処理、容量特性補正処理の詳細は後述する。

**【 0 0 8 3 】**

このように処理部 50 がオフセット調整を行うことで、基準信号 R F C K に対して発振信号 O S C K に所望の位相差を付加できる。また、そのオフセット調整と共に、処理部 50 は温度補償処理、エージング補正処理、容量特性補正処理等を時分割に実行する。例えば、図 15 で後述するような D S P によって、各処理の内容を記述したプログラムを実行することによって、1 体のハードウェアを共用して複数の処理を実行することが可能となる。これにより、各処理を個別のハードウェアで構成する場合に比べて処理部 50 の回路を小規模化できる。10

**【 0 0 8 4 】**

また本実施形態では、処理部 50 は、位相比較の結果である位相誤差データ P E D に対するデジタルフィルター処理（ループフィルター処理）を行う。

**【 0 0 8 5 】**

このように処理部 50 が位相誤差データ P E D に対するデジタルフィルター処理を行うことで、処理部 50 が位相誤差データ P E D から周波数制御データを生成できる。この周波数制御データの生成の詳細については図 6 等で後述する。20

**【 0 0 8 6 】**

また図 8 で後述するように、回路装置 500 はデジタルインターフェース部 30 を含んでもよい。発振信号生成回路 140 は、第 1 のモード（内部 P L L モード）では、位相比較の結果に基づく周波数制御データ D F C Q で発振信号 O S C K を生成し、第 2 のモード（外部 P L L モード）では、デジタルインターフェース部 30 を介して入力される外部生成周波数制御データ（図 8 の D F C E ）に基づく周波数制御データ D F C Q で発振信号 O S C K を生成する。

**【 0 0 8 7 】**

このようにすれば、例えばユーザーの所望の使い方に応じてモードを選択し、内部 P L L による発振周波数の制御と、外部 P L L による発振周波数の制御とを切り替えることが可能となる。例えば小型基地局等の安価に同期クロックを得たいユーザーは、第 1 のモードで回路装置 500 を使用することで、低コストで同期クロックを得ることができる。一方、同期クロックの生成手法等においてノウハウがあるユーザーは、外部 P L L を組み第 1 のモードで回路装置 500 を使用することで、ノウハウを活かすことができる。30

**【 0 0 8 8 】****2 . 回路装置の第 1 詳細構成**

図 4 は、本実施形態の回路装置 500 の第 1 の詳細な構成例、位相比較部 40 の詳細な構成例、処理部 50 の第 1 の詳細な構成例である。回路装置 500 は、位相比較部 40 、処理部 50 、ディザイナー処理部 160 、発振信号生成回路 140 を含む。位相比較部 40 は、同期回路 41 、カウンター 42 を含む。処理部 50 は、位相誤差変換部 51 、加算部 53 、ループフィルター 55 、周波数制御データ変換部 57 、補正処理部 59 を含む。40

**【 0 0 8 9 】**

同期回路 41 は、基準信号 R F C K を発振信号 O S C K に同期させる回路である。具体的には、同期回路 41 は、基準信号 R F C K を発振信号 O S C K で取り込むフリップフロップ回路等で構成される。即ち同期回路 41 は、フリップフロップ回路により基準信号 R F C K の論理レベルを発振信号 O S C K のエッジで取り込み、発振信号 O S C K のエッジに同期して論理レベルが変わるクロック信号 C K R （或いはパルス信号）を出力する。

**【 0 0 9 0 】**

カウンター 42 は、クロック信号 C K R の立ち上がりエッジ（又は立ち下がりエッジ）50

でカウント値を期待値  $n \times F C W$  にセットし、その期待値  $n \times F C W$  から発振信号 O S C K のクロック数をダウンカウントする。そして、クロック信号 C K R の  $n$  周期後の立ち上がりエッジ（又は立ち下がりエッジ）におけるカウント値を位相誤差データ P E D として出力する。ここで F C W は周波数設定データであり、例えば図 8 のレジスター部 3 2 等から入力される。例えば周波数設定データ F C W は外部装置からデジタルインターフェース部 3 0 を介してレジスター部 3 2 に書き込まれる。或いは、記憶部 3 4 に記憶された周波数設定データ F C W がレジスター部 3 2 に読み出されてもよい。

#### 【 0 0 9 1 】

位相誤差変換部 5 1 は、基準信号 R F C K の  $n$  周期におけるカウント値と期待値  $n \times F C W$ との差である位相誤差データ P E D を、1 秒間における基準信号 R F C K と発振信号 O S C K の位相の時間差に変換し、変換後の位相誤差データ Q P E を出力する。具体的には下式(2)、(3)に示す演算を行う。ここで  $K_{pe}$  は変換係数であり、 $f_{ref}$  は基準信号 R F C K の周波数であり、 $f_{out}$  は発振信号 O S C K の周波数である。

#### 【 数 2 】

$$QPE = K_{pe} \times PED \quad \dots (2)$$

$$K_{pe} = \frac{f_{ref}}{n \times f_{out}} \quad \dots (3)$$

#### 【 0 0 9 2 】

加算部 5 3 は、位相誤差データ Q P E にオフセット調整データ O F T C を加算処理し、加算処理後（オフセット調整後）の位相誤差データ Q P E F を出力する。即ち図 4 では位相誤差データ Q P E が図 1 での位相比較結果データに対応している。オフセット調整後の位相誤差がゼロとなるように負帰還制御されるので、ロック状態では、基準信号 R F C K と発振信号 O S C K の間にはオフセット調整データ O F T C に相当する位相誤差が付与されることになる。なお、オフセット調整機能はイネーブルとディセーブルを選択可能であってもよく、オフセット調整機能がディセーブルに設定された場合には加算部 5 3 は位相誤差データ Q P E を位相誤差データ Q P E F として出力する。

#### 【 0 0 9 3 】

ループフィルター 5 5 は、オフセット調整後の位相誤差データ Q P E F に対してデジタルフィルター処理を行い、その結果を出力データ Q L F として出力する。デジタルフィルター処理は、例えばローパス特性或いはバンドパス特性を有する。例えばループフィルター 5 5 は、位相誤差データ Q P E F に係数を乗じる比例処理と位相誤差データ Q P E F を積分する積分処理とを組み合わせた処理を行う。なお、ループフィルター 5 5 が行う処理はこれに限定されず、位相誤差データ Q P E F をゼロに近づけるような出力データ Q L F を演算する（即ち P L L 回路がロックしたときの出力データ Q L F に収束させる）処理であればよい。

#### 【 0 0 9 4 】

周波数制御データ変換部 5 7 は、ループフィルター 5 5 の出力データ Q L F を周波数制御データ Q D F に変換する。具体的には下式(4)、(5)に示す演算を行う。ここで  $K_{dc0}$  は変換係数である。 $2^{16}-1$  は、発振信号生成回路 1 4 0 に入力される周波数制御データ D I T Q の値の範囲（即ち D I T Q は 16 ビットデータ）である。 $f_{max}$  は、発振信号 O S C K の周波数変化範囲の上限周波数であり、 $f_{min}$  は、発振信号 O S C K の周波数変化範囲の下限周波数である。例えば周波数制御データ D I T Q の最大値  $2^{16}-1$  が発振信号生成回路 1 4 0 に入力された場合の発振信号 O S C K の周波数が  $f_{max}$  であり、周波数制御データ D I T Q の最小値 0 が発振信号生成回路 1 4 0 に入力された場合の発振信号 O S C K の周波数が  $f_{min}$  である。なお、これに限定されず、例えばマージンを設け、周波数制御データ D I T Q の値の範囲に対応した実際の発振周波数の変化範囲よりも、 $f_{max}$ 、 $f_{min}$  を外側に設定してもよい。例えば、振動子等の個体ばらつ

10

20

30

40

50

き等を測定し、それに基づいて  $f_{max}$ 、 $f_{min}$  を設定すればよい。なお、ここでは周波数制御データ DITQ を 16 ビットとしたが、周波数制御データ DITQ は 16 ビットに限定されない。

【数 3】

$$QDF = Kdco \times QLF \quad \dots \quad (4)$$

$$Kdco = \frac{(2^{16} - 1) \times fout}{fmax - fmin} \quad \dots \quad (5)$$

10

【0095】

補正処理部 59 は、周波数制御データ QDF に対して種々の補正処理を行い、補正処理後の周波数制御データ DFCQ を出力する。上述のように、補正処理は例えば温度補償処理、容量特性補正処理等である。またホールドオーバー時において補正処理部 59 がエンジニアリング補正処理を行い、周波数制御データ DFCQ を生成してもよい。

【0096】

なお処理部 50 の各部は、個別のハードウェアで構成されてもよいし、プロセッサー上で動作するプログラムとして構成されてもよい。プログラムとして構成される場合、例えば処理部 50 の各部がそれに対応するプログラムモジュールとして構成される。プログラムは ROM 等にデータとして記憶されたものであってもよいし、プログラムに相当するデータを出力するゲートアレイ等のハードウェアとして実現されたものであってもよい。

20

【0097】

ディザイナー処理部 160 は、周波数制御データ DFCQ に対してディザイナー処理を行い、ディザイナー処理後の周波数制御データ DITQ を出力する。発振信号生成回路 140 は、周波数制御データ DITQ により設定される発振周波数の発振信号 OSCK を生成する。例えば処理部 50 は 32 ビットの浮動小数点データを用いて演算を行う。ディザイナー処理部 160 は、32 ビットの浮動小数点データである周波数制御データ DFCQ を、16 ビットの整数データである周波数制御データ DITQ に変換し、その変換の際のディザイナー処理を行う。例えばディザイナー処理は端数の丸め処理において量子化誤差を低減する又はランダム化する処理である。

30

【0098】

図 5 は、PLL 回路の動作テストを行うテストモードでの動作を説明する図である。図 5 に示すように、テストモードでは位相誤差変換部 51 とループフィルター 55 の間でループが切れている。そして、第 4 のレジスター 324 からループフィルター 55 にテストデータ QPEF' が入力される。

【0099】

このテストデータ QPEF' は、位相誤差変換部 51 が出力する位相誤差データ QPE を模擬したデータである。即ち、1 秒間ににおける基準信号 RFCK と発振信号 OSCK の位相の時間差を模擬したデータである。テストデータ QPEF' は図 4 のオフセット調整データ OFTC に対応しているが、加算部 53 は加算処理を行わずにテストデータ QPEF' を通過させてループフィルター 55 に出力する。

40

【0100】

第 4 のレジスター 324 には、一定の或いは時系列に変化するテストデータ QPEF' がテスト装置等から書き込まれる。そして、ループフィルター 55、周波数制御データ変換部 57、補正処理部 59 がテストデータ QPEF' から周波数制御データ DFCQ を生成し、ディザイナー処理部 160、発振信号生成回路 140 が周波数制御データ DFCQ により設定される周波数の発振信号 OSCK を生成する。位相比較部 40、位相誤差変換部 51 が、基準信号 RFCK と発振信号 OSCK の位相誤差データ QPE を生成し、その位相誤差データ QPE が第 1 のレジスター 321 に記憶される。即ち、図 5 では位相誤差データ

50

タ Q P E が図 1 でのモニターデータ M T D に対応している。

【 0 1 0 1 】

3 . 回路装置の第 2 詳細構成

図 6 は、本実施形態の回路装置 5 0 0 の第 2 の詳細な構成例、ループフィルター 5 5 の詳細な構成例である。なお、図 6 では補正処理部 5 9、ディザー処理部 1 6 0、発振信号生成回路 1 4 0 を省略している。

【 0 1 0 2 】

回路装置 5 0 0 は、位相比較部 4 0、処理部 5 0、ロック検出部 7 0（ロック検出回路）、セレクター 7 5 を含む。また図 6 ではループフィルター 5 5 が乗算部 S G 1、S G 2、加算部 S A D 1、S A D 2、レジスター S R G を含む。

10

【 0 1 0 3 】

ロック検出部 7 0 は、位相誤差データ P E D に基づいて P L L 回路がロック状態であるか否かを検出し、ロック状態でない場合にはロック検出信号 D T L を非アクティブ（第 1 論理レベル、例えばローレベル）にし、ロック状態である場合にはロック検出信号 D T L をアクティブ（第 2 論理レベル、例えばハイレベル）にする。例えばロック検出部 7 0 は、位相誤差データ P E D が所定範囲内である場合にロック状態であると判定する。例えばロック状態において位相誤差データ P E D が「0」になる場合、- 1 P E D + 1 の場合にロック状態であると判定する。ロック検出部 7 0 は例えばロジック回路で構成される。なおロック検出部 7 0 は処理部 5 0 に含まれてもよい。

【 0 1 0 4 】

20

セレクター 7 5 は、ロック検出信号 D T L に基づいてループフィルター 5 5 の比例処理の係数を選択する。具体的にはセレクター 7 5 は、ロック検出信号 D T L が非アクティブである場合には係数 G A 1 を選択し、ロック検出信号 D T L がアクティブである場合には係数 G A 2 を選択する。セレクター 7 5 は、選択した係数を係数 G A として出力する。係数 G A 2 を下式（6）に示す。係数 G A 1 は下式（7）に示す範囲を満たす係数である。f c はループフィルター 5 5 のカットオフ周波数である。係数 G A 1、G A 2 は例えば図 8 のレジスター部 3 2 等から入力される。

【 数 4 】

$$GA2 = \frac{2\pi f c}{f ref} \quad \dots (6)$$

30

$$GA2 \leq GA1 \leq 1 \quad \dots (7)$$

【 0 1 0 5 】

ループフィルター 5 5 の乗算部 S G 1 は、位相誤差データ Q P E F に比例処理の係数 G A を乗算処理し、その結果を出力データ G Q 1 として出力する。

【 0 1 0 6 】

乗算部 S G 2 は、位相誤差データ Q P E F に積分処理の係数 G R H を乗算処理し、その結果を出力データ G Q 2 として出力する。係数 G R H は下式（8）に示す範囲を満たす係数である。係数 G R H は例えば図 8 のレジスター部 3 2 等から入力される。

40

【 数 5 】

$$0 \leq GRH \leq \frac{(GA2)^2}{2} \quad \dots (8)$$

【 0 1 0 7 】

加算部 S A D 1、レジスター S R G は積分器を構成する。即ち、加算部 S A D 1 は出力

50

データ G Q 2 とレジスター S R G の出力データ R T Q を加算処理し、その結果を出力データ A D Q として出力する。レジスター S R G は出力データ A D Q を保持し、保持したデータを出力データ R T Q として出力する。

#### 【 0 1 0 8 】

加算部 S A D 2 は、比例処理の結果である出力データ G Q 1 と積分処理の結果である出力データ R T Q を加算処理し、その結果を出力データ Q L F として出力する。ループフィルター 5 5 の伝達関数 H ( z ) は下式 ( 9 ) のようになる。

#### 【 数 6 】

$$H(z) = \frac{GA2 + (GRH - GA2)z^{-1}}{1 - z^{-1}} \quad \dots (9)$$

10

#### 【 0 1 0 9 】

上述した非ロック状態において選択される比例処理の係数 G A 1 は、非ロック状態においてロック状態までの収束時間を短縮する機能（以下、ギアシフトと呼ぶ）に用いられる。即ち上式 ( 7 ) に示すように、非ロック状態では、ロック状態での係数 G A 2 以上の係数 G A 1 で比例処理を行う。これにより、位相誤差を収束させようとする効果（位相誤差に対する負帰還）がロック状態よりも強く働くことになり、ギアシフトを用いない場合に比べてロック状態までの収束時間が短縮される。

20

#### 【 0 1 1 0 】

##### 4 . カウンターの変形例

図 7 は、カウンター 4 2 の変形構成例である。カウンター 4 2 は、シフター 4 4 、ダウンカウンター 4 5 、位相誤差レジスター 4 6 、誤差判定回路 4 8 を含む。

#### 【 0 1 1 1 】

この変形構成例では計測時間 T m e s を可変に制御することによってギアシフトと同等の機能を実現するものである。この変形構成例を採用した場合、図 6 のギアシフトに関わる構成（ロック検出部 7 0 、セレクター 7 5 ）を省略してもよい。

#### 【 0 1 1 2 】

シフター 4 4 は、シフト量制御信号 C S F に対応したシフト量で周波数設定データ F C W をビットシフトする。具体的には計測時間 T m e s = n × T r e f の n が 2<sup>j</sup> ( j は 0 以上の整数 ) に設定可能であり、その j がシフト量に相当する。シフター 4 4 は、 j ビットだけ周波数設定データ F C W を M S B 側にシフトさせ、その結果を期待値 S F C W (= n × F C W ) として出力する。シフター 4 4 は、期待値 S F C W をクロック信号 C K R の立ち上がりエッジ（又は立ち下がりエッジ）で更新する。

30

#### 【 0 1 1 3 】

ダウンカウンター 4 5 は、クロック信号 C K R の立ち上がりエッジ（又は立ち下がりエッジ）でカウント値を期待値 S F C W に初期化する。そしてダウンカウンター 4 5 は、計測時間 T m e s の間、クロック信号 C K R の立ち上がりエッジ（又は立ち下がりエッジ）まで発振信号 O S C K でダウンカウントを行い、そのカウント値 Q D C を出力する。

40

#### 【 0 1 1 4 】

位相誤差レジスター 4 6 は、ダウンカウンター 4 5 のカウント値 Q D C を、計測時間 T m e s 終了時のクロック信号 C K R の立ち上がりエッジ（又は立ち下がりエッジ）で取り込み、その取り込んだカウント値を位相誤差データ P E D として出力する。

#### 【 0 1 1 5 】

誤差判定回路 4 8 は、位相誤差データ P E D の絶対値が閾値 T H R 以下であるか否かを判定し、その判定結果に基づいてシフト量制御信号 C S F を出力する。具体的には、誤差判定回路 4 8 は、位相誤差データ P E D の絶対値が閾値 T H R 以下となった場合にシフト量（ビット数 j ）を 1 段階大きくする。例えば j = 0, 1, 2, ..., j m a x と 1 ずつ増加させる。j m a x はシフト量の最大値であり、ロック状態でのシフト量（即ちロック

50

状態では  $n = 2^{j \max}$  )である。なお、 $j$  の初期値は 1 以上の整数であってもよい。また  $j$  は 2 以上の整数ずつ増加させてもよい。閾値 THR は例えば図 8 のレジスター部 32 等から入力される。

#### 【0116】

また誤差判定回路 48 は、上記判定結果に基づいて変換係数 Kpe の制御信号 CKPE を位相誤差変換部 51 に出力する。具体的には、上式(3)のように変換係数 Kpe は  $n$  に依存している。誤差判定回路 48 は、シフト量である  $j$  と連動して  $n = 2^j$  の場合の変換係数 Kpe を指定する制御信号 CKPE を出力する。例えば  $j$  の各値に対応した変換係数が予め図 8 のレジスター部 32 等に記憶されており、位相誤差変換部 51 が制御信号 CKPE に応じて変換係数 Kpe を選択してもよい。或いは、基準となるシフト量(例えば  $j = 0$ )での変換係数が図 8 のレジスター部 32 等に記憶されており、位相誤差変換部 51 が、レジスター部 32 等から読み出した変換係数に対して制御信号 CKPE に応じた演算を行って、変換係数 Kpe を求めてよい。

#### 【0117】

また誤差判定回路 48 は、 $j = j_{\max}$ において位相誤差データ P E D の絶対値が閾値 THR 以下となったか否かの判定結果に基づいてロック検出信号 DTL' を出力にする。即ち、位相誤差データ P E D の絶対値が閾値 THR 以下となった場合にロック検出信号 DTL' をアクティブにする。

#### 【0118】

##### 5. 回路装置の第 3 詳細構成

図 8 は、本実施形態の回路装置 500 の第 3 の詳細な構成例である。

#### 【0119】

回路装置 500 は、温度センサー 10、A/D 変換部 20 (A/D 変換回路)、デジタルインターフェース部 30 (デジタルインターフェース回路)、レジスター部 32 (レジスター回路)、記憶部 34 (メモリー)、位相比較部 40、処理部 50、ロック検出部 70、基準信号検出回路 110、発振信号生成回路 140 を含む。

#### 【0120】

温度センサー 10 は、温度検出電圧 VTD を出力する。具体的には、環境(回路装置 500)の温度に応じて変化する温度依存電圧を、温度検出電圧 VTD として出力する。例えば温度センサー 10 は、ダイオードやバイポーラトランジスター等で構成できる。そして、ダイオードやバイポーラトランジスター等に含まれる PN 接合の順方向電圧が温度検出電圧 VTD に相当する。

#### 【0121】

A/D 変換部 20 は、温度センサー 10 からの温度検出電圧 VTD の A/D 変換を行つて、温度検出データ DTD を出力する。例えば温度検出電圧 VTD の A/D 変換結果に対応するデジタルの温度検出データ DTD (A/D 結果データ) を出力する。A/D 変換部 20 の A/D 変換方式としては、例えば逐次比較方式や逐次比較方式に類似する方式などを採用できる。なお A/D 変換方式はこのような方式には限定されず、種々の方式(計数型、並列比較型又は直並列型等)を採用できる。

#### 【0122】

振動子 X T A L は、回路装置 500 の外部に設けられ、例えば AT カットタイプや SC カットタイプなどの厚みすべり振動タイプの水晶振動子等や屈曲振動タイプなどの圧電振動子である。振動子 X T A L は共振器(電気機械的な共振子又は電気的な共振回路)であつてもよい。なお振動子 X T A L としては、圧電振動子として、S A W (Surface Acoustic Wave) 共振子、シリコン製振動子としての M E M S (Micro Electro Mechanical Systems) 振動子等を採用できる。振動子 X T A L の基板材料としては、水晶、タンタル酸リチウム、ニオブ酸リチウム等の圧電単結晶や、ジルコン酸チタン酸鉛等の圧電セラミックス等の圧電材料、又はシリコン半導体材料等を用いることができる。振動子 X T A L の励振手段としては、圧電効果によるものを用いてよいし、クーロン力による静電駆動を用いてよい。

10

20

30

40

50

## 【0123】

発振信号生成回路140は、D/A変換部80と発振回路150を含む。D/A変換部80は、処理部50からの周波数制御データDFCQのD/A変換を行う。D/A変換部80のD/A変換方式としては例えば抵抗ストリング型（抵抗分割型）を採用できる。但し、D/A変換方式はこれには限定されず、抵抗ラダー型（R-2Rラダー型等）、容量アレイ型、又はパルス幅変調型などの種々の方式を採用できる。またD/A変換部80は、D/A変換器以外にも、その制御回路や変調回路（PWM変調等）やフィルター回路などを含むことができる。発振回路150は、D/A変換部80の出力電圧VQと振動子XTALを用いて、発振信号OSCKを生成する。発振回路150は、振動子XTAL（圧電振動子、共振子等）を発振させることで、発振信号OSCKを生成する。具体的には、振動子XTALの一端が回路装置500の第1の振動子用端子TX1を介して発振回路150に接続され、振動子XTALの他端が回路装置500の第2の振動子用端子TX2を介して発振回路150に接続される。そして発振回路150は、D/A変換部80の出力電圧VQを周波数制御電圧（発振制御電圧）とした発振周波数で、振動子XTALを発振させる。例えば発振回路150が、電圧制御により振動子XTALの発振を制御する回路（VCO）である場合には、発振回路150は、周波数制御電圧に応じて容量値が変化する可変容量キャパシター（バリキャップ等）を含むことできる。10

## 【0124】

基準信号検出回路47は、基準信号RFCKが消失又は異常となったか否かを検出し、その検出結果に基づいて基準信号検出信号SYNCCLKを出力する。基準信号RFCKが存在する又は正常であると検出された場合、検出信号SYNCCLKはアクティブ（第2論理レベル）になる。基準信号RFCKが消失した又は異常となったことが検出された場合、検出信号SYNCCLKは非アクティブ（第1論理レベル）になる。例えば、基準信号検出回路47は、基準信号RFCKのパルス（又は周波数）を監視して基準信号RFCKが消失した又は異常となったか否かを検出する。例えば、基準信号RFCKのパルス間隔をカウンター等により測定し、そのカウント値に基づいてパルスが所定期間入力されなかったと判断した場合に、基準信号RFCKが消失又は異常となったと判定する。或いは、カウント値に基づいてパルスの入力間隔が所定期間続いたと判断した場合に、基準信号RFCKが消失又は異常となったと判定する。20

## 【0125】

記憶部34は、回路装置500の各種の処理や動作に必要な各種の情報を記憶するものである。この記憶部34は、例えば不揮発性メモリーにより実現できる。不揮発性メモリーとしては、例えばEEPROMなどを用いることができる。EEPROMとしては例えばMONOS（Metal-Oxide-Nitride-Oxide-Silicon）型のメモリーなどを用いることができる。或いはEEPROMとして、フローティングゲート型などの他のタイプのメモリーを用いてもよい。なお記憶部34は、電源が非供給でも情報を保持して記憶できるものであればよく、例えばヒューズ回路等により実現することも可能である。30

## 【0126】

レジスター部32は、ステータスレジスター、コマンドレジスター、データレジスターなどの複数のレジスターで構成される回路である。回路装置500の外部装置（例えばCPUやMPU等のプロセッサー等）は、デジタルインターフェース部30を介してレジスター部32の各レジスターにアクセスする。そして外部装置は、レジスター部32のレジスターを用いて、回路装置500のステータスを確認したり、回路装置500に対してコマンドを発行したり、回路装置500に対してデータを転送したり、回路装置500からデータを読み出すことなどが可能になる。またレジスター部32には、記憶部34から読み出された情報が格納される。例えば上述した変換係数Kpe、Kdc0やオフセット調整データOTC、係数GA1、GA2、GRH等のパラメーターが記憶部34に記憶されている。これらのパラメーターは例えば回路装置500の起動時等にレジスター部32に読み出される（初期ロードされる）。そして、処理部50はレジスター部32を参照して上記パラメーターを用いた処理を実行する。4050

## 【0127】

処理部50は、内部PLL処理部83、ホールドオーバー処理部52、カルマンフィルター部54、エージング補正部56（エージング補正処理の回路又はプログラムモジュール）、温度補償部58を有する。なお、カルマンフィルター部54、エージング補正部56、温度補償部58が図4の補正処理部59に対応する。内部PLL処理部83は図4等で説明した位相誤差変換部51、加算部53、ループフィルター55、周波数制御データ変換部57に対応する。以下では、内部PLL処理部83が行う処理を内部PLL処理と呼ぶ。ホールドオーバー処理部52は、ホールドオーバーに関する種々の処理を行う。カルマンフィルター部54は、周波数制御データの観測値に対する真値を推定する処理を行う。エージング補正部56は、ホールドオーバー時においてエージングによる周波数変動を補償するためのエージング補正を行う。温度補償部58は、A/D変換部20からの温度検出データDTDに基づいて発振周波数の温度補償処理を行う。10

## 【0128】

デジタルインターフェース部30は、回路装置500と外部装置（例えばマイクロコンピューター、コントローラー等）との間でデジタルデータを入出力するためのインターフェースである。例えばシリアルクロック線とシリアルデータ線を用いた同期式のシリアル通信方式により実現できる。具体的には、I2C（Inter-Integrated Circuit）方式や、3線又は4線のSPI（Serial Peripheral Interface）方式などにより実現できる。I2C方式は、シリアルクロック線SCLと、双方向のシリアルデータ線SDAの2本の信号線で通信を行う同期式のシリアル通信方式である。SPI方式は、シリアルクロック線SCKと、単方向の2本のシリアルデータ線SDI、SDOで通信する同期式のシリアル通信方式である。デジタルインターフェース部30は、これらの通信方式を実現する入出力バッファー回路や制御回路などにより構成される。20

## 【0129】

基準信号RFCKは、回路装置500の接続端子（パッド）を介して回路装置500に入力される。外部PLL回路がロック状態となっているか否かを通知する信号PLOCKは、回路装置500の接続端子（パッド）を介して回路装置500に入力される。なお、信号PLOCKはデジタルインターフェース部30を介して回路装置500に入力されてもよい。例えば信号PLOCKは、ロック状態でない場合には非アクティブとなり、ロック状態である場合にはアクティブとなる。30

## 【0130】

本実施形態では、例えば、外部装置がデジタルインターフェース部30を介してレジスター部32にモード設定情報を書き込むことで、内部PLLモード（第1のモード）と外部PLLモード（第2のモード）のいずれかが設定される。

## 【0131】

内部PLLモードでは、処理部50は位相比較部40からの位相誤差データPEDに基づいて内部PLL処理を行い、周波数制御データ（図4のQDF）を生成する。そして処理部50は、周波数制御データQDFに対して、例えば温度補償処理等の信号処理を行い、信号処理後の周波数制御データDFCQを発振信号生成回路140に出力する。発振信号生成回路140は周波数制御データDFCQと振動子XTALを用いて、発振信号OSCKを生成して、位相比較部40に出力する。これにより、位相比較部40、発振信号生成回路140等によるPLL回路（内部PLL回路）のループが形成される。40

## 【0132】

外部PLLモードでは、外部周波数制御データ生成部からの周波数制御データDFCE（外部生成周波数制御データ）がデジタルインターフェース部30を介して処理部50に入力される。そして処理部50は、周波数制御データDFCEに対して、例えば温度補償処理等の信号処理を行い、信号処理後の周波数制御データDFCQを発振信号生成回路140に出力する。発振信号生成回路140は周波数制御データDFCQと振動子XTALを用いて、発振信号OSCKを生成して、外部周波数制御データ生成部に出力する。これにより、外部周波数制御データ生成部、発振信号生成回路140等によるPLL回路（外50

部 P L L 回路 ) のループが形成される。

**【 0 1 3 3 】**

なお、外部周波数制御データ生成部は、発振信号 O S C K に基づく入力信号と基準信号 R F C K とを比較して周波数制御データ D F C E を生成する。例えば外部周波数制御データ生成部は、発振信号 O S C K と基準信号 R F C K との比較演算を行う比較演算部と、位相誤差データの平滑化処理を行うデジタルフィルター部とを含むことができる。或いは、アナログ回路の位相比較器と、アナログ回路のフィルター部(ループフィルター)と A / D 変換器とを含むことができる。

**【 0 1 3 4 】**

6 . 処理部の第 2 詳細構成

10

図 9 は、処理部 5 0 の第 2 の詳細な構成例である。処理部 5 0 は、摂氏変換部 8 1 、ローパスフィルター部 8 2 、温度補償部 5 8 、内部 P L L 処理部 8 3 、カルマンフィルター部 5 4 、エージング補正部 5 6 、容量特性補正部 8 9 、加算部 8 4 、8 5 、8 6 、セレクター 8 7 を含む。なお、カルマンフィルター部 5 4 、エージング補正部 5 6 、温度補償部 5 8 、容量特性補正部 8 9 が図 4 の補正処理部 5 9 に対応する。

**【 0 1 3 5 】**

摂氏変換部 8 1 は、温度検出データ D T D を、摂氏温度を表す(広義には摂氏温度に対応する)温度検出データ D T D ' に変換する。例えば摂氏温度に対して非線形な特性の温度検出データ D T D を、摂氏温度に対して線形な特性の温度検出データ D T D ' に変換する。

20

**【 0 1 3 6 】**

ローパスフィルター部 8 2 は、温度検出データ D T D ' の時間変化を平滑化するデジタルフィルター処理を行い、デジタルフィルター処理後の温度検出データ D T D " を出力する。

**【 0 1 3 7 】**

温度補償部 5 8 は、温度検出データ D T D " に基づいて温度補償処理を行い、温度変動に対して発振周波数を一定に保つための温度補償データ T C O D E ( 温度補償コード ) を生成する。具体的には、下式(10)の多項式(近似関数)の係数 A 0 ~ A 5 の情報が、図 8 の記憶部 3 4 に記憶されている。X は温度検出データ D T D " に相当する。温度補償部 5 8 は、記憶部 3 4 から係数 A 0 ~ A 5 の情報を読み出し、この係数 A 0 ~ A 5 と、温度検出データ D T D " (= X ) とに基づいて、下式(10)の演算処理を行って、温度補償データ T C O D E を生成する。

30

**【 数 7 】**

$$TCODE = A_5 \cdot X^5 + A_4 \cdot X^4 + A_3 \cdot X^3 + A_2 \cdot X^2 + A_1 \cdot X + A_0 \quad \dots \quad (10)$$

**【 0 1 3 8 】**

加算部 8 4 は、外部 P L L モードにおいて外部周波数制御データ生成部から入力された周波数制御データ D F C E に対して温度補償データ T C O D E を加算処理し、その結果を周波数制御データ D F C E ' として出力する。なお周波数制御データ D F C E をそのまま周波数制御データ D F C E ' として出力してもよい。

40

**【 0 1 3 9 】**

内部 P L L 処理部 8 3 は、内部 P L L モードにおいて位相比較部 4 0 から入力された位相誤差データ P E D に基づいて内部 P L L 処理を行い、周波数制御データ Q D F を出力する。

**【 0 1 4 0 】**

加算部 8 5 は、周波数制御データ Q D F に対して温度補償データ T C O D E を加算処理し、その結果を周波数制御データ Q D F ' として出力する。なお周波数制御データ Q D F をそのまま周波数制御データ Q D F ' として出力してもよい。

**【 0 1 4 1 】**

50

カルマンフィルター部 54 は、基準信号 R F C K の消失又は異常によるホールドオーバーが検出される前の期間（通常動作期間）において、周波数制御データ（D F C E、Q D F）の観測値に対する真値を、カルマンフィルター処理により推定する処理を行う。この真値は、カルマンフィルター処理により推定された真値であり、本当の真の値であるとは限らない。なお、ホールドオーバーの検出による制御処理は、図 8 のホールドオーバー処理部 52 により実行される。カルマンフィルター処理の詳細は後述する。

#### 【 0 1 4 2 】

エージング補正部 56 は、ホールドオーバーが検出された場合に、ホールドオーバーの検出タイミングに対応するタイミングでの真値を保持する。この真値を保持するタイミングは、ホールドオーバーの検出タイミングそのものであってもよいし、当該タイミングの前のタイミング等であってもよい。そしてエージング補正部 56 は、保持された真値に基づく演算処理を行うことで、エージング補正された周波数制御データ A C ( k ) を生成する。エージング補正処理の詳細は後述する。10

#### 【 0 1 4 3 】

加算部 85 は、周波数制御データ A C ( k ) に対して温度補償データ T C O D E を加算処理し、その結果を周波数制御データ A C ( k ) ' として出力する。なお周波数制御データ A C ( k ) をそのまま周波数制御データ A C ( k ) ' として出力してもよい。

#### 【 0 1 4 4 】

セレクター 87 は、非ホールドオーバー（通常動作）時の外部 P L L モードでは周波数制御データ D F C E ' を選択し、非ホールドオーバー時の内部 P L L モードでは周波数制御データ Q D F ' を選択し、ホールドオーバー時には周波数制御データ A C ( k ) ' を選択する。セレクター 87 は、選択した周波数制御データを周波数制御データ D F C Q ' として出力する。20

#### 【 0 1 4 5 】

容量特性補正部 89 は、周波数制御データ D F C Q ' と発振周波数とが一意に対応する（同一の周波数制御データ D F C Q ' に対して同一の発振周波数が得られる）ように周波数制御データ D F C Q ' に対して補正処理を行い、その結果を周波数制御データ D F C Q として出力する。具体的には、発振回路 150 の可変容量キャパシター（例えば図 18 の C X 1 ）は、例えば個体ばらつきや温度変化により、制御電圧に対する容量が変動する。容量特性補正部 89 は、このような容量特性の変動をキャンセル（低減）する補正を行う。例えば、容量特性補正部 89 は、容量特性の個体ばらつきをキャンセル（低減）する第 1 補正処理、容量特性の温度変化を温度補償データ T C O D E に基づいてキャンセル（低減）する第 2 補正処理、容量特性の非線形性をキャンセル（低減）する（周波数制御データ D F C Q ' に対する容量特性を線形にする）第 3 補正処理を行う。第 1 ~ 第 3 補正処理は、各補正処理に対応した補正式の演算によって実現される。補正式に用いるパラメーター（係数等）は、例えば図 8 の記憶部 34 に記憶される。そしてパラメーターは記憶部 34 からレジスター部 32 に読み出され、レジスター部 32 から処理部 50 に入力される。なお、第 1 ~ 第 3 補正処理の各補正処理は、イネーブルとディセーブルを選択可能であつてもよい。30

#### 【 0 1 4 6 】

##### 7 . 処理フロー

図 10 は、処理部 50 が行う処理のフローチャートである。

#### 【 0 1 4 7 】

処理が開始されると、処理部 50 は温度検出終了フラグがアクティブとなったか否かを判定する（S1）。温度検出終了フラグは、A / D 変換部 20 が温度検出データ D T D を出力（更新）した場合にアクティブになるフラグである。

#### 【 0 1 4 8 】

温度検出終了フラグがアクティブである場合、処理部 50 は温度検出用ローパスフィルター処理を行う（S2）。即ち、摂氏変換部 81 が温度検出データ D T D を摂氏変換し、その温度検出データ D T D ' をローパスフィルター部 82 がローパスフィルター処理する50

。次に、温度補償部 5 8 が、ローパスフィルター処理後の温度検出データ D T D ”に基づいて温度補償処理を行い、温度補償データ T C O D E を生成する ( S 3 )。次に、カルマンフィルター部 5 4 が、周波数制御データ D F C E 又は Q D F に基づいてカルマンフィルター処理を行う。またホールドオーバー時にはエージング補正部 5 6 がエージング補正処理を行う ( S 4 )。次に、ステップ S 9 に進む。

#### 【 0 1 4 9 】

ステップ S 1 において温度検出終了フラグが非アクティブである場合、周波数制御データ書き込みフラグがアクティブであるか否かを判定する ( S 5 )。周波数制御データ書き込みフラグは、外部周波数制御データ生成部からデジタルインターフェース部 3 0 を介して周波数制御データ D F C E が入力された ( 例えばレジスター部 3 2 に書き込まれた ) 場合にアクティブになるフラグである。

10

#### 【 0 1 5 0 】

周波数制御データ書き込みフラグがアクティブである場合、処理部 5 0 は外部 P L L モードにおける処理を行う ( S 6 )。具体的には、加算部 8 4 、セレクター 8 7 が、この処理を実行する。次に、ステップ S 9 に進む。

#### 【 0 1 5 1 】

周波数制御データ書き込みフラグが非アクティブである場合、位相比較終了フラグがアクティブであるか否かを判定する ( S 7 )。位相比較終了フラグは、位相比較部 4 0 が位相誤差データ P E D を出力 ( 更新 ) した場合にアクティブになるフラグである。具体的には、基準信号 R F C K の n 周期毎に位相比較終了フラグがアクティブになる。或いは、基準信号 R F C K の 1 周期毎に位相比較部 4 0 が位相誤差データ P E D を出力すると共に位相比較終了フラグがアクティブとなってもよい。この場合、例えば n 回同じ位相誤差データ P E D が出力され、位相誤差データ P E D の値が変化するのは基準信号 R F C K の n 周期毎である。

20

#### 【 0 1 5 2 】

位相比較終了フラグがアクティブである場合、処理部 5 0 は内部 P L L モードにおける処理を行う ( S 8 )。具体的には、内部 P L L 処理部 8 3 、加算部 8 5 、セレクター 8 7 が、この処理を実行する。次に、ステップ S 9 に進む。

#### 【 0 1 5 3 】

位相比較終了フラグが非アクティブである場合、ステップ S 1 に戻り、温度検出終了フラグ、周波数制御データ書き込みフラグ、位相比較終了フラグのいずれかがアクティブになるまでループを繰り返し、フラグ待ちを行う。

30

#### 【 0 1 5 4 】

ステップ S 9 では、容量特性補正部 8 9 が、ステップ S 4 、 S 6 、 S 8 のいずれかのステップの処理結果である周波数制御データ D F C Q ' に対して容量特性補正処理を行い、周波数制御データ D F C Q を発振信号生成回路 1 4 0 ( 又はディザー処理部 1 6 0 ) に出力する ( S 9 )。次に、処理部 5 0 はフラグリセットを行う ( S 1 0 )。具体的には、温度検出終了フラグ、周波数制御データ書き込みフラグ、位相比較終了フラグのうちアクティブとなっているフラグを非アクティブにリセットする。次に、ステップ S 1 に戻り、フラグ待ちを行う。

40

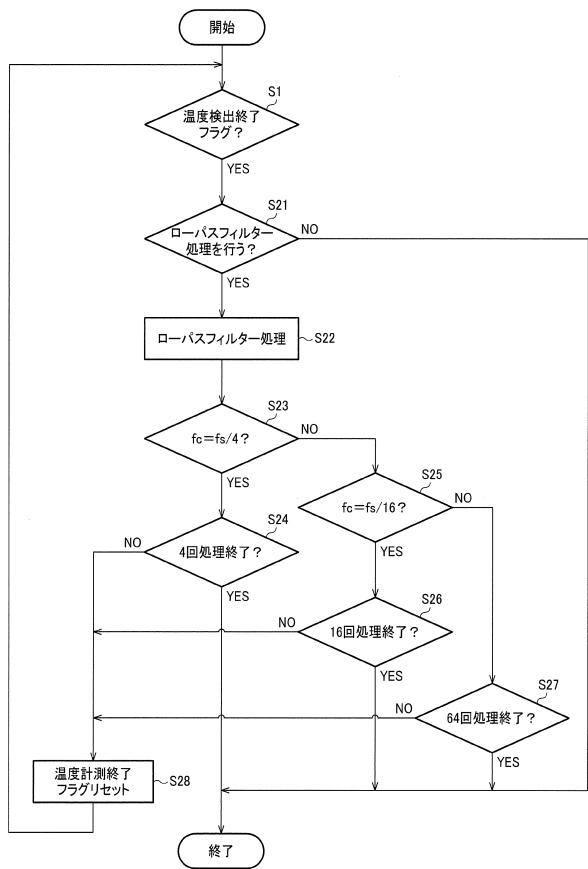

#### 【 0 1 5 5 】

図 1 1 は、温度検出用ローパスフィルター処理 ( S 2 ) の詳細なフローチャートである。

#### 【 0 1 5 6 】

処理部 5 0 はローパスフィルター処理がイネーブルに設定されているか否かを判定する ( S 2 1 )。ローパスフィルター処理がディセーブルに設定されている場合にはローパスフィルター処理を行わずに処理を終了する。なお、摂氏変換処理は例えばステップ S 2 1 の前に行われる。

#### 【 0 1 5 7 】

ローパスフィルター処理がイネーブルに設定されている場合には、ローパスフィルター

50

部 8 2 が温度検出データ D T D' に対してローパスフィルター処理を行う ( S 2 2 )。次に、ローパスフィルター処理のカットオフ周波数  $f_c$  が  $f_s / 4$  に設定されている否かを判定する ( S 2 3 )。  $f_s$  はローパスフィルター処理の動作周波数である。即ち、 $f_s$  は温度検出データ D T D のサンプリング周波数 ( A / D 変換部 2 0 が温度検出データ D T D を出力する周波数) である。

#### 【 0 1 5 8 】

カットオフ周波数  $f_c$  が  $f_s / 4$  に設定されている場合、処理部 5 0 はローパスフィルター処理を 4 回行ったか ( 4 入力分の温度検出データ D T D に対するローパスフィルター処理を行ったか ) 否かを判定する ( S 2 4 )。 4 回行った場合は処理を終了する。 4 回行って以内場合は温度計測終了フラグを非アクティブにリセットし ( S 2 8 )、ステップ S 1 に戻る。

#### 【 0 1 5 9 】

カットオフ周波数  $f_c$  が  $f_s / 4$  に設定されていない場合、ローパスフィルター処理のカットオフ周波数  $f_c$  が  $f_s / 16$  に設定されているか否かを判定する ( S 2 5 )。

#### 【 0 1 6 0 】

カットオフ周波数  $f_c$  が  $f_s / 16$  に設定されている場合、処理部 5 0 はローパスフィルター処理を 16 回行ったか ( 16 入力分の温度検出データ D T D に対するローパスフィルター処理を行ったか ) 否かを判定する ( S 2 6 )。 16 回行った場合は処理を終了する。 16 回行って以内場合は温度計測終了フラグを非アクティブにリセットし ( S 2 8 )、ステップ S 1 に戻る。

#### 【 0 1 6 1 】

カットオフ周波数  $f_c$  が  $f_s / 16$  に設定されていない場合、カットオフ周波数  $f_c$  は  $f_s / 64$  に設定されているので、処理部 5 0 はローパスフィルター処理を 64 回行ったか ( 64 入力分の温度検出データ D T D に対するローパスフィルター処理を行ったか ) 否かを判定する ( S 2 7 )。 64 回行った場合は処理を終了する。 64 回行って以内場合は温度計測終了フラグを非アクティブにリセットし ( S 2 8 )、ステップ S 1 に戻る。

#### 【 0 1 6 2 】

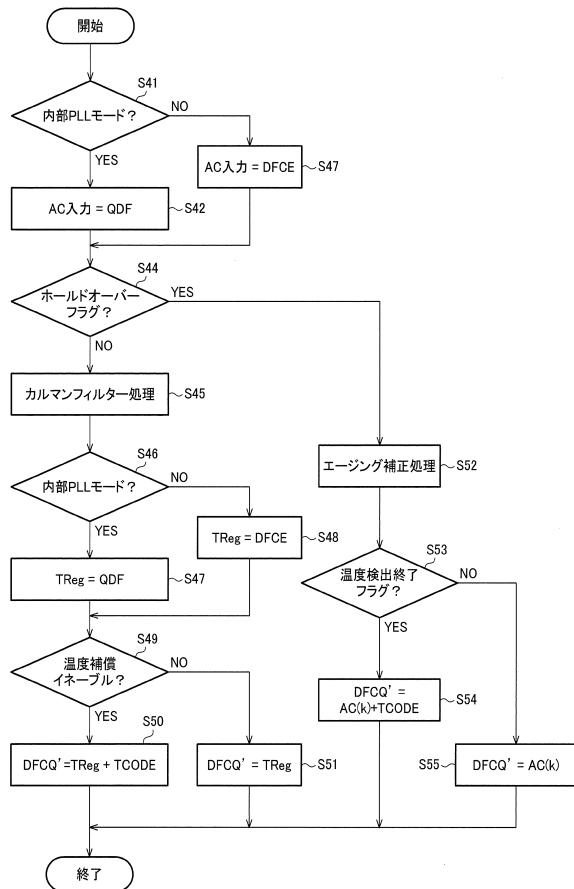

図 1 2 は、カルマンフィルター処理及びエージング補正処理 ( S 4 ) の詳細なフローチャートである。

#### 【 0 1 6 3 】

処理部 5 0 は、内部 P L L モードに設定されているか否かを判定する ( S 4 1 )。 内部 P L L モードに設定されている場合には、カルマンフィルター処理の入力レジスター ( A C 入力 ) に周波数制御データ Q D F を記憶させる ( S 4 2 )。 外部 P L L モードに設定されている ( 内部 P L L モードに設定されていない ) 場合には、カルマンフィルター処理の入力レジスターに周波数制御データ D F C E を記憶させる ( S 4 3 )。

#### 【 0 1 6 4 】

次に処理部 5 0 は、ホールドオーバーフラグ ( 図 1 7 の信号 H O L D O V E R ) がアクティブか否かを判定する ( S 4 4 )。ホールドオーバーフラグは、ホールドオーバー処理部 5 2 がホールドオーバー状態であると判断した場合にアクティブになるフラグである。

#### 【 0 1 6 5 】

ホールドオーバーフラグが非アクティブの場合には、カルマンフィルター部 5 4 が、ステップ S 4 2 、 S 4 7 で選択された入力に対してカルマンフィルター処理を行う ( S 4 5 )。 次に、処理部 5 0 は、内部 P L L モードに設定されているか否かを判定する ( S 4 6 )。 内部 P L L モードに設定されている場合には、変数 T R e g のレジスターに周波数制御データ Q D F を記憶させる ( S 4 7 )。 外部 P L L モードに設定されている場合には、変数 T R e g のレジスターに周波数制御データ D F C E を記憶させる ( S 4 8 )。

#### 【 0 1 6 6 】

次に、処理部 5 0 は温度補償処理がイネーブルに設定されているか否かを判定する ( S 4 9 )。 温度補償処理がイネーブルに設定されている場合には、変数 T R e g と温度補償データ T C O D E との加算値を周波数制御データ D F C Q' のレジスターに記憶させる (

10

20

30

40

50

S 5 0 )。温度補償処理がディセーブルに設定されている場合には、変数 T R e g を周波数制御データ D F C Q ' のレジスターに記憶させる ( S 5 1 )。なお、ステップ S 4 9 ~ S 4 9 の処理は、加算部 8 4 、 8 5 、セレクター 8 7 が行う処理に対応している。

#### 【 0 1 6 7 】

ステップ S 4 4 においてホールドオーバーフラグがアクティブである場合、エージング補正部 5 6 がエージング補正処理を行う ( S 5 2 )。次に、処理部 5 0 は温度検出終了フラグがアクティブであるか否かを判定する ( S 5 3 )。温度検出終了フラグがアクティブである場合、周波数制御データ A C ( k ) と温度補償データ T C O D E との加算値を周波数制御データ D F C Q ' のレジスターに記憶させる ( S 5 4 )。温度検出終了フラグが非アクティブである場合、周波数制御データ A C ( k ) を周波数制御データ D F C Q ' のレジスターに記憶させる ( S 5 5 )。なお、ステップ S 5 3 ~ S 5 5 の処理は、加算部 8 6 、セレクター 8 7 が行う処理に対応している。10

#### 【 0 1 6 8 】

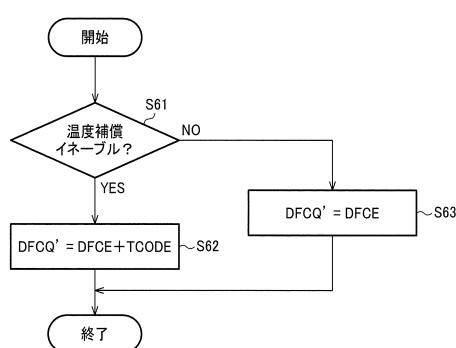

図 1 3 は、外部 P L L モードにおける処理 ( S 6 ) の詳細なフローチャートである。

#### 【 0 1 6 9 】

処理部 5 0 は、温度補償処理がイネーブルに設定されているか否かを判定する ( S 6 1 )。温度補償処理がイネーブルに設定されている場合には、周波数制御データ D F C E と温度補償データ T C O D E との加算値を周波数制御データ D F C Q ' のレジスターに記憶させる ( S 6 2 )。温度補償処理がディセーブルに設定されている場合には、周波数制御データ D F C E を周波数制御データ D F C Q ' のレジスターに記憶させる ( S 6 3 )。なお、ステップ S 6 1 ~ S 6 3 の処理は、加算部 8 4 、セレクター 8 7 が行う処理に対応している。20

#### 【 0 1 7 0 】

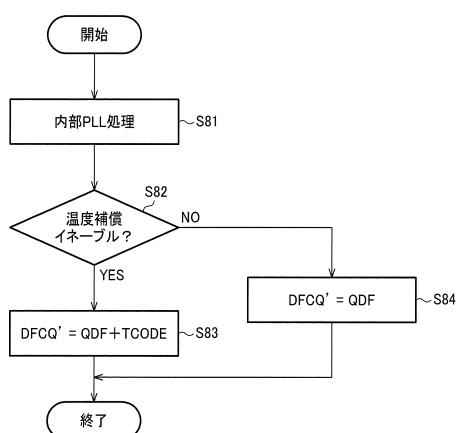

図 1 4 は、内部 P L L モードにおける処理 ( S 8 ) の詳細なフローチャートである。

#### 【 0 1 7 1 】

内部 P L L 処理部 8 3 は、位相誤差データ P E D に対して内部 P L L 処理を行い、周波数制御データ Q D F を生成する ( S 8 1 )。次に、処理部 5 0 は、温度補償処理がイネーブルに設定されているか否かを判定する ( S 8 2 )。温度補償処理がイネーブルに設定されている場合には、周波数制御データ Q D F と温度補償データ T C O D E との加算値を周波数制御データ D F C Q ' のレジスターに記憶させる ( S 8 3 )。温度補償処理がディセーブルに設定されている場合には、周波数制御データ Q D F を周波数制御データ D F C Q ' のレジスターに記憶させる ( S 8 4 )。なお、ステップ S 8 2 ~ S 8 4 の処理は、加算部 8 5 、セレクター 8 7 が行う処理に対応している。30

#### 【 0 1 7 2 】

##### 8 . 処理部の第 3 詳細構成

図 1 5 は、処理部 5 0 の第 3 の詳細な構成例である。図 1 5 は、処理部 5 0 を D S P で構成する場合の構成例である。即ち、この D S P がプログラムに記述された命令を実行することにより、図 9 の機能ブロック図で説明した処理や、図 1 0 ~ 図 1 4 のフローチャートで説明した処理が実現される。

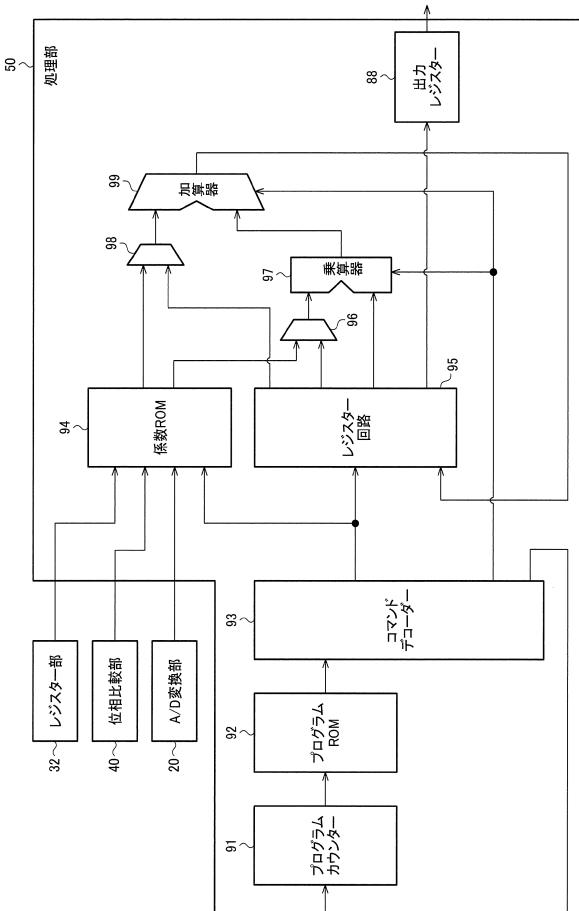

#### 【 0 1 7 3 】

処理部 5 0 は、プログラムカウンター 9 1 、プログラム R O M 9 2 、コマンドデコーダー 9 3 、係数 R O M 9 4 、レジスター回路 9 5 、セレクター 9 6 、乗算器 9 7 、セレクター 9 8 、加算器 9 9 、出力レジスター 8 8 を含む。

#### 【 0 1 7 4 】

プログラム R O M 9 2 は、プログラムを記憶する R O M ( Read Only Memory ) である。なお、プログラムデータをロジック回路 ( 組み合わせ回路等 ) として構成したものであってもよい。例えば、プログラムは行ナンバーと、その行ナンバーに対応する命令 ( コマンド ) 、その命令によって操作されるオペランドで構成される。

#### 【 0 1 7 5 】

プログラムカウンター 9 1 は、プログラムの行ナンバーを出力するカウンターである。

プログラムROM92は、プログラムカウンター91のカウント値によって指定される行ナンバーの命令とオペランドを出力する。

#### 【0176】

コマンドデコーダー93は、命令とオペランドを解釈し、命令とオペランドに対応した処理を乗算器97や加算器99等に実行させる制御信号を出力する。具体的には、コマンドデコーダー93は、乗算器97の入力データを指示する乗算器入力アドレス、乗算器97の入力データの符号を示す乗算器入力データ符号、加算器99の入力データを指示する加算器入力アドレス、加算器99の入力データの符号を示す加算器入力データ符号、加算器99の出力データを記憶するレジスター アドレスを指示する書き込みアドレスを出力する。

10

#### 【0177】

係数ROM94は、ROMとセレクターとを含む。処理部50が行う演算に用いられる種々の係数の一部はROMに記憶されている。係数の残りの一部は記憶部34に記憶されており、記憶部34から読み出されてレジスター部32に記憶されている。セレクターには、ROM及びレジスター部32からの係数と、処理部50への入力データとが入力される。入力データは、例えばレジスター部32からの周波数制御データDFCE、位相比較部40からの位相誤差データPED、A/D変換部20からの温度検出データDTDである。セレクターは、コマンドデコーダー93からの乗算器入力アドレスに対応する係数又は入力データを選択し、セレクター96に出力する。またセレクターは、コマンドデコーダー93からの加算器入力アドレスに対応する係数又は入力データを選択し、セレクター98に出力する。

20

#### 【0178】

レジスター回路95は、レジスターとセレクターとを含む。レジスターは、演算により生成されるデータ（中間生成データを含む）を一時記憶するレジスターである。例えば、変数Treg、温度補償データTCODE、周波数制御データQDF、DFCQ'、AC(k)等を記憶するレジスターである。セレクターは、コマンドデコーダー93からの乗算器入力アドレスに対応するデータを選択し、セレクター96又は乗算器97に出力する。またセレクターは、コマンドデコーダー93からの加算器入力アドレスに対応するデータを選択し、セレクター98に出力する。

30

#### 【0179】

セレクター96は、係数ROMからの係数又は入力データと、レジスター回路95からのデータとのいずれかを選択し、乗算器97に出力する。セレクター98は、係数ROMからの係数又は入力データと、レジスター回路95からのデータとのいずれかを選択し、加算器99に出力する。

#### 【0180】

乗算器97は、セレクター96の出力とレジスター回路95からのデータとを乗算し、その結果を加算器99に出力する。加算器99は、セレクター98の出力と乗算器97の出力とを加算し、その結果をレジスター回路95に出力する。レジスター回路95は、コマンドデコーダー93からの書き込みアドレスに対応するレジスター回路95内のレジスターに乗算器97の出力を記憶させる。

40

#### 【0181】

出力レジスター88は、処理部50が出力するデータを記憶し、そのデータを処理部50の外部へ出力する。例えば、出力レジスター88は、発振信号生成回路140（又はディザイナー処理部160）へ出力される周波数制御データDFCQが記憶される。

#### 【0182】

##### 9. カルマンフィルター処理を用いたエージング補正

本実施形態では、カルマンフィルター処理を用いたエージング補正手法を採用している。以下、この手法について説明する。

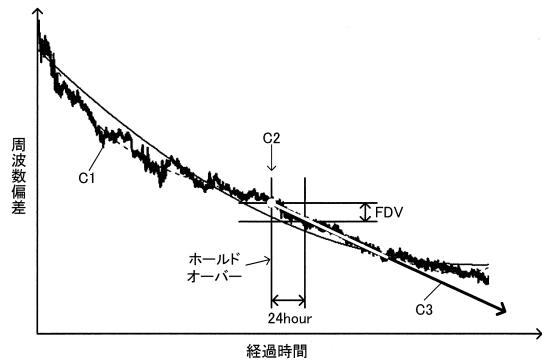

#### 【0183】

図16は、エージングによる発振周波数の変動の測定結果の例を示す図である。横軸は

50

経過時間（エージング時間）であり、縦軸は発振周波数の周波数偏差（ $f / f_0$ ）である。図16のC1に示すように観測値である測定値には、システムノイズや観測ノイズに起因する大きなばらつきが存在する。このばらつきには、環境温度に起因するばらつきも含まれる。このように測定値に大きなばらつきがある状況において、真値を正しく求めるために、本実施形態では、カルマンフィルター処理（例えば線形カルマンフィルター処理）による状態推定を行う。

#### 【0184】

時系列の状態空間モデルの離散時間状態方程式は、下式(11)、(12)の状態方程式、観測方程式により与えられる。

【数8】

10

$$x(k+1) = A \cdot x(k) + v(k) \quad \cdots (11)$$

$$y(k) = x(k) + w(k) \quad \cdots (12)$$

#### 【0185】

$x(k)$ は時刻kにおける状態であり、 $y(k)$ は観測値（周波数制御データ）である。 $v(k)$ はシステムノイズであり、 $w(k)$ は観測ノイズであり、Aはシステム行列である。 $x(k)$ が発振周波数（周波数制御データ）である場合に、Aは例えばエージングレート（エージング係数）に相当する。エージングレートは経過期間に対する発振周波数の変化率を表すものである。

20

#### 【0186】

例えば図16のC2に示すタイミングでホールドオーバーが発生したとする。この場合に、基準信号RFCKが途絶えたC2の時点での真の状態 $x(k)$ と、図16のC3に示す傾きに相当するエージングレート(A)に基づいて、エージング補正を実行する。具体的には、C2の時点での発振周波数（周波数制御データ）の真値 $x(k)$ を、C3に示すエージングレートによる周波数変化を小さくするための補償（補正）として、例えば当該周波数変化をキャンセル（相殺）する補正值で、順次に変化させるエージング補正を行う。

#### 【0187】

30

本実施形態のカルマンフィルター処理の詳細について説明する。本実施形態のカルマンフィルター処理では、下式(13)～(18)の処理を行って、真値を推定する。なお本明細書では、推定値であることを表すハットの記号「^」を、適宜、2文字に並べて記載する。

## 【数9】

$$\hat{x}^-(k) = \hat{x}(k-1) + D(k-1) \quad \dots (13)$$

$$P^-(k) = P(k-1) + v(k) \quad \dots (14)$$

$$G(k) = \frac{P^-(k)}{P^-(k) + w(k)} \quad \dots (15)$$

$$\hat{x}(k) = \hat{x}^-(k) + G(k) \cdot (y(k) - \hat{x}^-(k)) \quad \dots (16)$$

$$P(k) = (1 - G(k)) \cdot P^-(k) \quad \dots (17)$$

$$D(k) = D(k-1) + E \cdot (y(k) - \hat{x}^-(k)) \quad \dots (18)$$

$\hat{x}(k)$ : 事後推定値

$\hat{x}^-(k)$ : 事前推定値

$P(k)$ : 事後共分散

$P^-(k)$ : 事前共分散

$G(k)$ : カルマンゲイン

## 【0188】

観測更新（観測過程）において、上式（15）によりカルマンゲイン  $G(k)$  が求められる。また観測値  $y(k)$  に基づいて上式（16）により、事後推定値  $\hat{x}^-(k)$  が更新される。また上式（17）により、誤差の事後共分散  $P(k)$  が更新される。

## 【0189】

時間更新（予測過程）において、上式（13）に示すように、タイムステップ  $k-1$  の事後推定値  $\hat{x}^-(k-1)$  と補正值  $D(k-1)$  の加算処理により、次のタイムステップ  $k$  での事前推定値  $\hat{x}^-(k)$  を予測する。また上式（14）に示すように、タイムステップ  $k-1$  での事後共分散  $P(k-1)$  と、システムノイズ  $v(k)$  に基づいて、次のタイムステップ  $k$  での事前共分散  $P^-(k)$  を予測する。また上式（18）に示すように、タイムステップ  $k-1$  での補正值  $D(k-1)$  と定数  $E$  を乗じた観測残差  $y(k) - \hat{x}^-(k)$  との加算処理により、次のタイムステップ  $k$  での補正值  $D(k)$  を求める。本実施形態では、上式（13）のように、システム行列  $A$  を事後推定値  $\hat{x}^-(k-1)$  に乘じる代わりに、事後推定値  $\hat{x}^-(k-1)$  と補正值  $D(k-1)$  の加算処理を行っている。即ち、補正值  $D(k)$  がエージングレートの予測値に対応している。

## 【0190】

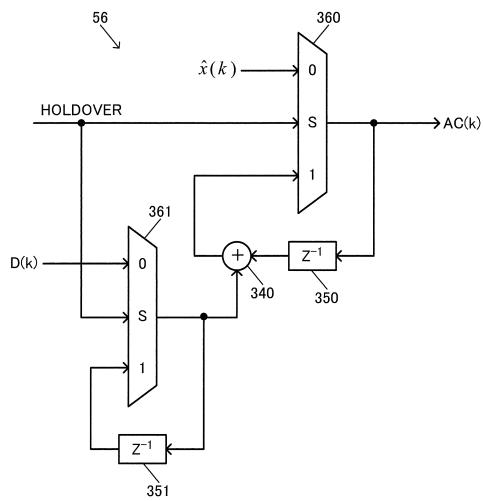

図17は、エージング補正部56の詳細な構成例である。

## 【0191】

信号HOLDOVERはホールドオーバーが検出されたホールドオーバー期間において論理レベル「1」（アクティブ、以下単に「1」と記載）になる信号である。具体的には、外部PLLモードでのロック検出信号である信号LOCK又は内部PLLモードでのロック検出信号である信号DTLを、信号PLLLOCKとする。信号PLLLOCKが論理レベル「0」（非アクティブ、以下単に「0」と記載）且つ信号SYNCCLKが「0」の場合に信号HOLDOVERが「1」になり、信号PLLLOCKが「1」又は信号SYNCCLKが「1」の場合に信号HOLDOVERが「0」になる。

## 【0192】

通常動作期間では、信号HOLDOVERが「0」になるため、セレクター360、3

10

20

30

40

50

61は「0」端子側を選択する。これにより、通常動作期間においてカルマンフィルタ部54により演算された事後推定値 $x^k$ 、補正值D(k)が、各々、レジスター350、351に保持される。

#### 【0193】

ホールドオーバーが検出されて、信号HOLDOVERが「1」になると、セレクター360、361は「1」端子側を選択する。これによりセレクター361は、ホールドオーバーの検出タイミングでレジスター351に保持された補正值D(k)を、ホールドオーバー期間中は出力し続けることになる。

#### 【0194】

そして、加算部340は、ホールドオーバーの検出タイミングでレジスター350に保持された事後推定値 $x^k$ に対して、レジスター351に保持されてセレクター361から出力された補正值D(k)(補正值)を、各タイムステップごとに順次に加算する処理を行う。これにより下式(19)に示すようなエージング補正が実現される。

#### 【数10】

$$AC(k+1) = AC(k) + D(k) \quad \dots (19)$$

#### 【0195】

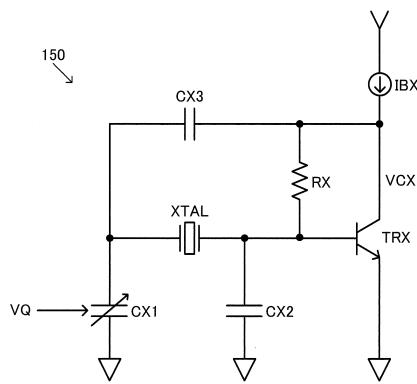

##### 10. 発振回路

図18は、発振回路150の構成例である。この発振回路150は、電流源IBX、バイポーラートランジスターTRX、抵抗RX、可変容量キャパシターCX1、キャパシタ-CX2、CX3を有する。

#### 【0196】

電流源IBXは、バイポーラートランジスターTRXのコレクターにバイアス電流を供給する。抵抗RXは、バイポーラートランジスターTRXのコレクターとベースの間に設けられる。

#### 【0197】

容量が可変である可変容量キャパシターCX1の一端は、振動子XTALの一端に接続される。具体的には、可変容量キャパシターCX1の一端は、回路装置500の第1の振動子用端子(振動子用パッド)を介して振動子XTALの一端に接続される。キャパシタ-CX2の一端は、振動子XTALの他端に接続される。具体的には、キャパシターCX2の一端は、回路装置500の第2の振動子用端子(振動子用パッド)を介して振動子XTALの他端に接続される。キャパシターCX3は、その一端が振動子XTALの一端に接続され、その他端がバイポーラートランジスターTRXのコレクターに接続される。

#### 【0198】

バイポーラートランジスターTRXには、振動子XTALの発振により生じたベース・エミッター間電流が流れる。そしてベース・エミッター間電流が増加すると、バイポーラートランジスターTRXのコレクター・エミッター間電流が増加し、電流源IBXから抵抗RXに分岐するバイアス電流が減少するので、コレクター電圧VCXが低下する。一方、バイポーラートランジスターTRXのベース・エミッター間電流が減少すると、コレクター・エミッター間電流が減少し、電流源IBXから抵抗RXに分岐するバイアス電流が増加するので、コレクター電圧VCXが上昇する。このコレクター電圧VCXはキャパシターCX3を介して振動子XTALにフィードバックされる。

#### 【0199】

振動子XTALの発振周波数は温度特性を有しており、この温度特性は、D/A変換部80の出力電圧VQ(周波数制御電圧)により補償される。即ち、出力電圧VQは可変容量キャパシターCX1に入力され、出力電圧VQにより可変容量キャパシターCX1の容量値が制御される。可変容量キャパシターCX1の容量値が変化すると、発振ループの共振周波数が変化するので、振動子XTALの温度特性による発振周波数の変動が補償され

10

20

30

40

50

る。可変容量キャパシター CX1 は、例えば可変容量ダイオード（バラクター）などにより実現される。

#### 【0200】

##### 11. 変形例

次に本実施形態の種々の変形例について説明する。図19は、本実施形態の変形例の回路装置の構成例である。

#### 【0201】

図19では、図8とは異なり、発振信号生成回路140にD/A変換部80が設けられていない。そして発振信号生成回路140により生成される発振信号OSCKの発振周波数が、処理部50からの周波数制御データDFCQに基づいて、直接に制御される。即ち D/A変換部を介さずに発振信号OSCKの発振周波数が制御される。

10

#### 【0202】

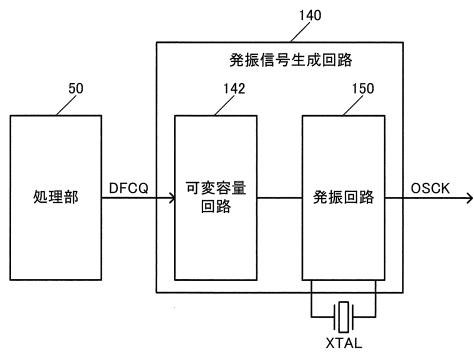

例えば図19では、発振信号生成回路140が、可変容量回路142と発振回路150を有する。そして図18の可変容量キャパシターCX1の代わりに、この可変容量回路142が設けられ、可変容量回路142の一端が振動子XTALの一端に接続される。

#### 【0203】

この可変容量回路142は、処理部50からの周波数制御データDFCQに基づいて、その容量値が制御される。例えば可変容量回路142は、複数のキャパシター（キャパシターアレイ）と、周波数制御データDFCQに基づき各スイッチ素子のオン、オフが制御される複数のスイッチ素子（スイッチアレイ）を有する。これらの複数のスイッチ素子の各スイッチ素子は、複数のキャパシターの各キャパシターに電気的に接続される。そして、これらの複数のスイッチ素子がオン又はオフされることで、複数のキャパシターのうち、振動子XTALの一端に、その一端が接続されるキャパシターの個数が変化する。これにより、可変容量回路142の容量値が制御されて、振動子XTALの一端の容量値が変化する。従って、周波数制御データDFCQにより、可変容量回路142の容量値が直接に制御されて、発振信号OSCKの発振周波数を制御できるようになる。

20

#### 【0204】

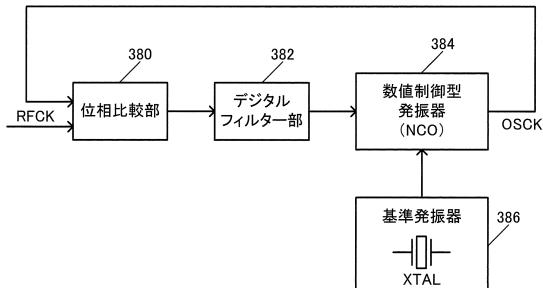

また本実施形態の回路装置を用いてPLL回路を構成する場合に、ダイレクト・デジタル・シンセサイザー方式のPLL回路とすることも可能である。図20は、ダイレクト・デジタル・シンセサイザー方式の場合の回路構成例である。

30

#### 【0205】

位相比較部380は、基準信号RFCKと発振信号OSCK（発振信号に基づく入力信号）の比較演算を行う。デジタルフィルター部382は、位相誤差の平滑化処理を行う。位相比較部380の構成、動作は図1等の位相比較部40と同様であり、カウンター42等を含むことができる。デジタルフィルター部382は図4の位相誤差変換部51、ループフィルター55、周波数制御データ変換部57等に相当するものである。数値制御型発振器384は、振動子XTALを有する基準発振器386からの基準発振信号を用いて、任意の周波数や波形をデジタル的に合成する回路である。即ちVCOのようにD/A変換器からの制御電圧に基づいて発振周波数を制御するのではなく、デジタルの周波数制御データと基準発振器386（振動子XTAL）を用いて、デジタル演算処理により任意の発振周波数の発振信号OSCKを生成する。

40

#### 【0206】

##### 12. 発振器、電子機器、移動体

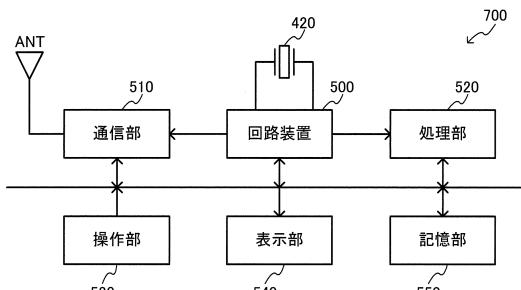

図21は、本実施形態の回路装置500を含む発振器400の構成例である。図21に示すように、発振器400は、振動子420と回路装置500を含む。振動子420と回路装置500は、発振器400のパッケージ410内に実装される。そして振動子420の端子と、回路装置500（IC（集積回路装置））の端子（パッド）は、パッケージ410の内部配線により電気的に接続される。

#### 【0207】

図22は、本実施形態の回路装置500を含む電子機器700の構成例である。この電

50

子機器 700 は、本実施形態の回路装置 500、水晶振動子等の振動子 420、アンテナ A N T、通信部 510、処理部 520 を含む。また操作部 530、表示部 540、記憶部 550 を含むことができる。振動子 420 と回路装置 500 により発振器 400 が構成される。なお電子機器は図 22 の構成に限定されず、これらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【 0 2 0 8 】

図 22 の電子機器 700 としては、例えば基地局又はルーター等のネットワーク関連機器や、高精度の計測機器や、G P S 内蔵時計、生体情報測定機器（脈波計、歩数計等）又は頭部装着型表示装置等のウェアラブル機器や、スマートフォン、携帯電話機、携帯型ゲーム装置、ノート P C 又はタブレット P C 等の携帯情報端末（移動端末）や、コンテンツを配信するコンテンツ提供端末や、デジタルカメラ又はビデオカメラ等の映像機器などの種々の機器を想定できる。10

#### 【 0 2 0 9 】

通信部 510（無線回路）は、アンテナ A N T を介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部 520 は、電子機器 700 の制御処理や、通信部 510 を介して送受信されるデータの種々のデジタル処理などを行う。この処理部 520 の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現できる。

#### 【 0 2 1 0 】

操作部 530 は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイをなどにより実現できる。表示部 540 は、各種の情報を表示するものであり、液晶や有機 E L などのディスプレイにより実現できる。なお操作部 530 としてタッチパネルディスプレイを用いる場合には、このタッチパネルディスプレイが操作部 530 及び表示部 540 の機能を兼ねることになる。記憶部 550 は、データを記憶するものであり、その機能は R A M や R O M などの半導体メモリーや H D D（ハードディスクドライブ）などにより実現できる。20

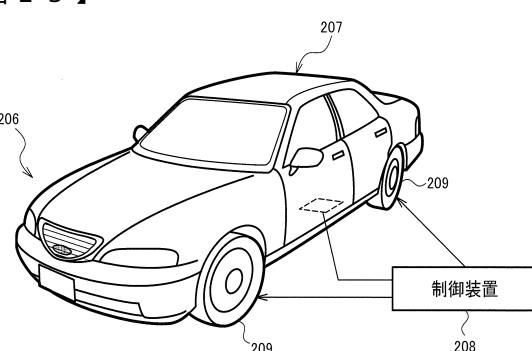

#### 【 0 2 1 1 】

図 23 は、本実施形態の回路装置 500 を含む移動体の例である。本実施形態の回路装置 500（回路装置 500 を含む発振器 400）は、例えば、車、飛行機、バイク、自転車、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器（車載機器）を備えて、地上や空や海上を移動する機器・装置である。図 23 は移動体の具体例としての自動車 206 を概略的に示している。自動車 206 には、本実施形態の回路装置と振動子を有する発振器（不図示）が組み込まれる。制御装置 208 は、この発振器により生成されたクロック信号により動作する。制御装置 208 は、例えば車体 207 の姿勢に応じてサスペンションの硬軟を制御したり、個々の車輪 209 のブレーキを制御する。例えば制御装置 208 により、自動車 206 の自動運転を実現してもよい。なお本実施形態の回路装置や発振器が組み込まれる機器は、このような制御装置 208 には限定されず、自動車 206 等の移動体に設けられる種々の機器（車載機器）に組み込むことが可能である。30

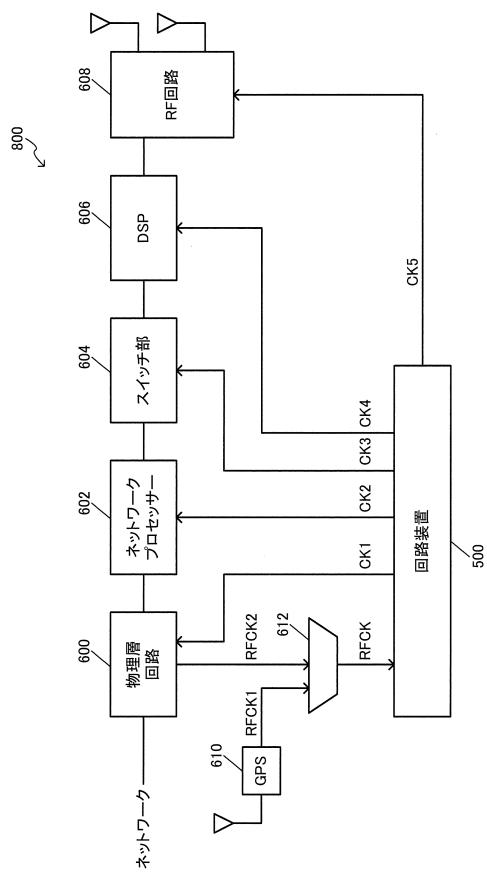

#### 【 0 2 1 2 】

図 24 は、電子機器の 1 つである基地局 800（基地局装置）の構成例である。物理層回路 600 はネットワークを介した通信処理における物理層の処理を行う。ネットワークプロセッサー 602 は、物理層よりも上位層の処理（リンク層等）を行う。スイッチ部 604 は通信処理の各種の切り替え処理を行う。D S P 608 は、通信処理に必要な各種のデジタル信号処理を行う。R F 回路 608 は、ローノイズアンプ（L N A）により構成される受信回路、や、パワーアンプにより構成される送信回路や、D / A 変換器、A / D 変換器などを含む。40

#### 【 0 2 1 3 】

セレクター 612 は、G P S 610 からの基準信号 R F C K 1、物理層回路 600 からの基準信号 R F C K 2（ネットワークからクロック信号）のいずれかを、基準信号 R F C K として、本実施形態の回路装置 500 に出力する。回路装置 500 は、基準信号 R F C K として、本実施形態の回路装置 500 に出力する。50

Kに対して発振信号（発振信号に基づく入力信号）を同期させる処理を行う。そして周波数が異なる各種のクロック信号CK1、CK2、CK3、CK4、CK5を生成して、物理層回路600、ネットワークプロセッサー602、スイッチ部604、DSP606、RF回路608に供給する。

#### 【0214】

本実施形態の回路装置500によれば、図24に示すような基地局において、基準信号RFCRに発振信号を同期させ、当該発振信号に基づいて生成された周波数安定度の高いクロック信号CK1～CK5を、基地局の各回路に供給できるようになる。

#### 【0215】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。また位相比較部、処理部、発振信号生成回路、回路装置、発振器、電子機器、移動体の構成・動作等も、本実施形態で説明したものに限定されず、種々の変形実施が可能である。

#### 【符号の説明】

#### 【0216】

10

10 ... 温度センサー、20 ... A / D 変換部、30 ... デジタルインターフェース部、

32 ... レジスター部、34 ... 記憶部、40 ... 位相比較部、41 ... 同期回路、

42 ... カウンター、44 ... シフター、45 ... ダウンカウンター、

46 ... 位相誤差レジスター、47 ... 基準信号検出回路、48 ... 誤差判定回路、

50 ... 処理部、51 ... 位相誤差変換部、52 ... ホールドオーバー処理部、

53 ... 加算部、54 ... カルマンフィルター部、55 ... ループフィルター、

56 ... エージング補正部、57 ... 周波数制御データ変換部、58 ... 温度補償部、

59 ... 補正処理部、70 ... ロック検出部、75 ... セレクター、80 ... D / A 変換部、

81 ... 摂氏変換部、82 ... ローパスフィルター部、83 ... 内部PLL処理部、

84 ... 加算部、85 ... 加算部、86 ... 加算部、87 ... セレクター、

88 ... 出力レジスター、89 ... 容量特性補正部、91 ... プログラムカウンター、

92 ... プログラムROM、93 ... コマンドデコーダー、94 ... 係数ROM、

95 ... レジスター回路、96 ... セレクター、97 ... 乗算器、98 ... セレクター、

99 ... 加算器、110 ... 基準信号検出回路、140 ... 発振信号生成回路、

142 ... 可変容量回路、150 ... 発振回路、160 ... ディザイナー処理部、

206 ... 自動車（移動体）、207 ... 車体、208 ... 制御装置、209 ... 車輪、

321 ... 第1のレジスター、322 ... 第2のレジスター、

323 ... 第3のレジスター、324 ... 第4のレジスター、340 ... 加算部、

350 ... レジスター、351 ... レジスター、360 ... セレクター、

361 ... セレクター、380 ... 位相比較部、382 ... デジタルフィルター部、

384 ... 数値制御型発振器、386 ... 基準発振器、400 ... 発振器、

410 ... パッケージ、420 ... 振動子、500 ... 回路装置、510 ... 通信部、

520 ... 処理部、530 ... 操作部、540 ... 表示部、550 ... 記憶部、

600 ... 物理層回路、602 ... ネットワークプロセッサー、604 ... スイッチ部、

608 ... RF回路、610 ... GPS、612 ... セレクター、700 ... 電子機器、

800 ... 基地局、

CX1 ... 可変容量キャパシター、DFCQ ... 周波数制御データ、

FCW ... 周波数設定データ、MTD ... モニターデータ、

OFTC ... オフセット調整データ、OSCK ... 発振信号、PED ... 位相誤差データ、

QPEF' ... テストデータ、RFCR ... 基準信号、SFCW ... 期待値、

10

20

30

40

50

T m e s ... 計測時間、 T r e f ... 基準信号の周期、 T r e s ... 時間分解能、

X T A L ... 振動子

【 义 1 】

【図2】

【図3】

【図4】

【図5】

【図6】

【四七】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13】

【図15】

【図14】

【図 1 6】

【図 1 8】

【図 1 7】

【図 1 9】

【図 2 0】

【図 2 2】

【図 2 1】

【図 2 3】

【図24】

---

フロントページの続き

審査官 石田 昌敏

(56)参考文献 特開平04-373214(JP,A)

特開2015-128220(JP,A)

特開平08-146166(JP,A)

特開2015-082815(JP,A)

特開2016-019269(JP,A)

特開2002-026724(JP,A)

特開2008-219513(JP,A)

特開平07-095069(JP,A)

特開2002-076888(JP,A)

特開2006-060570(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03L 1/00 - 7/26