(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3579903号

(P3579903)

(45) 発行日 平成16年10月20日(2004.10.20)

(24) 登録日 平成16年7月30日(2004.7.30)

(51) Int.CI.<sup>7</sup>

F 1

H 01 L 21/60

G 02 F 1/1345H 01 L 21/60 311 S

G 02 F 1/1345

請求項の数 10 (全 19 頁)

(21) 出願番号 特願平7-513716

(86) (22) 出願日 平成6年11月9日(1994.11.9)

(86) 国際出願番号 PCT/JP1994/001887

(87) 国際公開番号 WO1995/013625

(87) 国際公開日 平成7年5月18日(1995.5.18)

審査請求日 平成13年2月8日(2001.2.8)

(31) 優先権主張番号 特願平5-283694

(32) 優先日 平成5年11月12日(1993.11.12)

(33) 優先権主張国 日本国(JP)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107076

弁理士 藤綱 英吉

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 村松 永至

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 田中 永一

最終頁に続く

(54) 【発明の名称】半導体素子の実装構造及び半導体装置の実装構造並びに液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項1】

半導体素子を実装するための構造であつて、

前記半導体素子を搭載した複数の回路基板を備え、

前記各回路基板が、前記半導体素子に接続された入力配線及び出力配線と、

前記入力配線に接続された入力端子と、前記出力配線に接続された出力端子と、

前記入力端子に接続された入力バス配線と、

を有し、

前記出力配線、前記出力端子及び前記入力配線が、前記各回路基板の前記半導体素子を実装した面に設けられ、

前記入力端子及び前記入力バス配線が、前記各回路基板の前記半導体素子実装面と反対側の面に設けられ、

前記入力バス配線は前記入力端子間を相互に接続してなり、

前記入力端子と前記入力配線とが前記各回路基板に形成されたバイアホールにより接続され、

前記各回路基板の前記入力バス配線により相互に接続された前記入力端子と、当該回路基板に隣接する回路基板の入力端子との間が、ワイヤボンディングにより接続されていること、

を特徴とする半導体素子の実装構造。

## 【請求項2】

半導体素子を実装するための構造であって、

複数の前記半導体素子を搭載した複数の回路基板を備え、

前記各回路基板が、前記各半導体素子に接続された各入力配線及び各出力配線と、

前記各出力配線に接続された各出力端子と、を有し、前記入力配線に接続された入力端子

と、前記入力端子に接続された入力バス配線と、を有し、

前記各出力配線、前記各出力端子及び前記各入力配線が、前記回路基板の前記各半導体素

子を実装した面に形成され、

前記入力端子及び前記入力バス配線が、前記各回路基板の前記各半導体素子実装面と反対

側の面に形成され、

前記入力バス配線は前記入力端子間を相互に接続してなり、 10

前記各半導体素子の前記各入力配線が、前記入力端子または前記入力バス配線と、前記各

回路基板に形成されたバイアホールを介して接続され、

前記各回路基板の前記入力バス配線により相互に接続された前記入力端子と、当該回路基

板に隣接する回路基板の入力端子との間が、ワイヤボンディングにより接続されているこ

と、

を特徴とする半導体素子の実装構造。

【請求項3】

半導体素子を実装するための構造であって、

前記半導体素子を搭載した複数の回路基板を備え、

前記回路基板が、前記半導体素子に接続された入力配線及び出力配線と、 20

前記入力配線に接続された入力端子と、前記出力配線に接続された出力端子と、前記入力

端子に接続された第1の入力バス配線と、前記半導体素子を介して前記入力配線を相互に

接続してなる第2の入力バス配線と、を有し、

前記出力配線、前記出力端子、前記入力配線及び前記第2の入力バス配線が、前記回路基

板の前記半導体素子を実装した面に設けられ、

前記入力端子及び前記第1の入力バス配線が、前記回路基板の前記半導体素子実装面と反

対側の面に設けられ、

前記第1の入力バス配線は前記入力端子間を相互に接続してなり、

前記入力端子と前記入力配線とが前記回路基板に形成されたバイアホールにより接続され

、 30

前記各回路基板の前記第1の入力バス配線により相互に接続された前記入力端子と、当該

回路基板に隣接する回路基板の入力端子との間が、ワイヤボンディングにより接続されて

いること、

を特徴とする半導体素子の実装構造。

【請求項4】

半導体素子を実装するための構造であって、

複数の前記半導体素子を搭載した複数の回路基板を備え、

前記各回路基板が、前記各半導体素子に接続された各入力配線及び各出力配線と、

前記各出力配線に接続された各出力端子と、を有し、前記入力配線に接続された入力端子

と、前記入力端子に接続された第1の入力バス配線と、前記各半導体素子を介して前記入

力配線を相互に接続してなる第2の入力バス配線と、を有し、 40

前記各出力配線、前記各出力端子、前記各入力配線及び前記第2の入力バス配線が、前記

回路基板の前記各半導体素子を実装した面に形成され、

前記入力端子及び前記第1の入力バス配線が、前記各回路基板の前記各半導体素子実装面

と反対側の面に形成され、

前記第1の入力バス配線は前記入力端子間を相互に接続してなり、

前記各半導体素子の前記各入力配線が、前記入力端子または前記第1の入力バス配線と、

前記各回路基板に形成されたバイアホールを介して接続され、

前記各回路基板の前記第1の入力バス配線により相互に接続された前記入力端子と、当該

回路基板に隣接する回路基板の入力端子との間が、ワイヤボンディングにより接続されて

いること、 50

いること、

を特徴とする半導体素子の実装構造

【請求項 5】

前記回路基板の前記出力端子が、該出力端子に対応する電子装置の端子と接続されることにより電子装置に実装されることを特徴とする請求項 1 乃至 4 のいずれかに記載の半導体素子の実装構造。

【請求項 6】

前記回路基板の前記出力端子が、異方性導電膜を介して電子装置の対応する端子に接続されていることを特徴とする請求項 1 乃至 5 のいずれかに記載の半導体素子の実装構造。

【請求項 7】

請求項 1 乃至 6 のいずれかに記載の前記半導体素子の実装構造を備えることを特徴とする液晶表示装置。

【請求項 8】

電子装置に、半導体素子を実装する半導体装置の実装構造であって、

前記半導体素子を搭載した複数の回路基板を備え、

前記各回路基板が、前記半導体素子に接続された入力配線及び出力配線と、前記入力配線に接続された入力端子と、前記出力配線に接続された出力端子と、前記入力端子に接続された入力バス配線と、を有し、

前記出力配線、前記出力端子及び前記入力配線が、前記各回路基板の前記半導体素子を実装した面に設けられ、

前記入力端子及び前記入力バス配線が、前記各回路基板の前記半導体素子実装面と反対側の面に設けられ、

前記入力バス配線は前記入力端子間を相互に接続してなり、

前記入力端子と前記入力配線とが前記各回路基板に形成されたバイアホールにより接続され、

前記各回路基板の前記入力バス配線により相互に接続された前記入力端子と、当該回路基板に隣接する回路基板の入力端子との間が、ワイヤボンディングにより接続されていること、

を特徴とする半導体装置の実装構造。

【請求項 9】

電子装置に、半導体素子を実装する半導体装置の実装構造であって、

複数の前記半導体素子を搭載した複数の回路基板を備え、

前記各回路基板が、前記各半導体素子に接続された各入力配線及び各出力配線と、前記各出力配線に接続された各出力端子と、を有し、前記入力配線に接続された入力端子と、前記入力端子に接続された入力バス配線と、を有し、

前記各出力配線、前記各出力端子及び前記各入力配線が、前記回路基板の前記各半導体素子を実装した面に形成され、

前記入力端子及び前記入力バス配線が、前記各回路基板の前記各半導体素子実装面と反対側の面に形成され、

前記入力バス配線は前記入力端子間を相互に接続してなり、

前記各半導体素子の前記各入力配線が、前記入力端子または前記入力バス配線と、前記各回路基板に形成されたバイアホールを介して接続され、

前記各回路基板の前記入力バス配線により相互に接続された前記入力端子と、当該回路基板に隣接する回路基板の入力端子との間が、ワイヤボンディングにより接続されていること、

を特徴とする半導体装置の実装構造。

【請求項 10】

前記回路基板の前記出力端子が、異方性導電膜を介して電子装置の対応する端子に接続されることを特徴とする請求項 8 または 9 のいずれかに記載の半導体装置の実装構造。

【発明の詳細な説明】

10

20

30

40

50

## 技術分野

本発明は、半導体素子を実装するための構造及び方法に関し、特に液晶表示装置等の電子装置に回路基板を用いて半導体素子を実装するのに適した構造及び方法に関する。また、本発明は、かかる実装構造及び方法を用いてその駆動用半導体素子を実装した液晶表示装置に関する。

## 背景技術

従来より、電子装置に半導体素子と実装するために、所謂TAB ( Tape Automated Bonding ) 技術を用いて半導体素子を搭載したテープキャリアパッケージを一括接続するTAB方式や、ガラス基板の表面にパターン形成された配線に半導体素子を直接接続するCOG ( Chip - on - Glass ) 方式等が知られている。

液晶表示装置では、マトリクス構造のXY電極からなる液晶ディスプレイのパネル周辺部に、上述したTAB方式により駆動用半導体チップを接続するのが一般的である。しかしながら、この場合には、半導体素子の入力及び出力配線がTABパッケージの同一面に形成され、かつ各TABパッケージが液晶パネルの外側に装着されるため、実装面積が非常に大きくなり、液晶表示部の周辺に大きな所謂額縁部分即ちデスエリアが形成されて、液晶表示装置全体が大型化し、相対的に表示面積が小さくなるという問題があった。

更に、各TABパッケージの半導体素子に入力信号及び電源等を供給するために入力バス配線を設けた別個の駆動回路基板が必要であり、そのためにデスエリアが一層拡大されると共に、コストが増大するという問題があった。

また、COG方式により駆動用半導体素子を液晶パネルの表面に直接実装する場合には、液晶パネル周辺部の表面に入力配線、出力配線等をパターニングするため、液晶パネルの実装面積が大きくなり、TAB方式の場合と同様にデスエリアが非常に大きくなる。更に、入力・出力配線と入力バス配線とを同一面上でクロス配線処理するため、製造コストが非常に高くなるという問題があった。

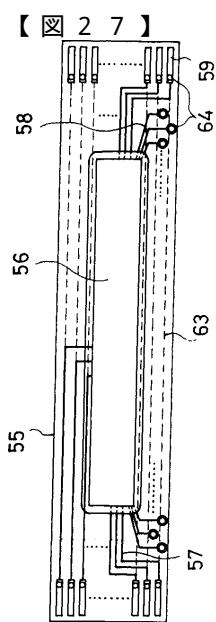

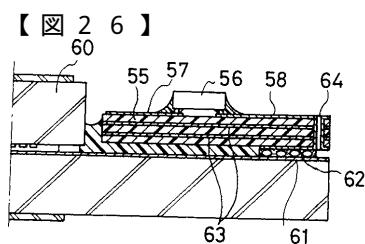

そこで、本願出願人は、特願平5 - 223523号明細書に記載されるように、多層構造の回路基板を介して液晶駆動用LSIを液晶表示装置に実装する構造を提案した。第26図及び第27図に示すように、この積層回路基板55は、その所定位置に駆動用LSI56を接続した表面に、入力配線57、出力配線58及び入力端子59を形成し、その裏面に液晶パネル60の接続端子61に接続するための出力端子62を形成し、かつ中間層に入力バス配線63等を設けると共に、出力配線と出力端子とを、及び入力配線とバス配線とをそれぞれバイアホール64を介して層間接続している。

これによって、TAB基板に接続される駆動回路基板が不要になるので実装面積が小さくなり、液晶表示装置全体を小型化かつ薄型化できると共に、接続点数を少なくして信頼性の向上を図ることができる。

しかしながら、通常半導体素子1個当たり80~数百もある多数の出力配線と出力端子とをバイアホールにより層間接続するために、製造コストが高くなり、かつ多数のバイアホールを形成するので回路基板の実装面積が大きくなるという問題があった。更に、少なくとも3層以上の多層構造となるために製造工程が複雑になって製造コストが増大するだけでなく、実装後の液晶表示装置の薄型化を十分に図れない。また、加工上の困難性から、出力配線のピッチを例えば $150\text{ }\mu\text{m}$ 以下にまでファイン化することが困難である。このため、電子機器のダウンサイジング化の要請に十分対応することができない虞がある。

そこで、本発明の目的は、半導体素子を搭載した回路基板においてバイアホールによる層間接続を少なくしましたは完全に排除して、実装面積を小さくし、また回路基板から入出力線、バス配線のための中間導電層を排除して薄型化を図り、コンパクトでダウンサイジング化の要請に対応できると共に、製造工程を簡単にし、かつ製造コストを低減させることができる半導体素子の実装構造及び実装方法を提供することにある。

また、本発明の別の目的は、液晶表示装置にその駆動用LSIを実装する場合に、液晶パネルの額縁面積即ちデスエリアを最小にして、実質的に表示面積を拡大し、ダウンサイジング化の要請に対応して装置全体の小型化・薄型化を図ることができる液晶表示装置を提供することにある。

## 発明の開示

本発明によれば、半導体素子を実装するための構造であって、前記半導体素子を搭載した回路基板を備え、前記回路基板が、前記半導体素子に接続された入力配線及び出力配線と、前記入力配線に接続された入力端子と、前記出力配線に接続された出力端子と、前記入力端子に接続された入力バス配線と、を有し、前記出力配線、前記出力端子及び前記入力配線が、前記回路基板の前記半導体素子を実装した面に設けられ、前記入力端子及び前記入力バス配線が、前記回路基板の前記半導体素子実装面と反対側の面に設けられ、かつ、前記入力バス配線は、前記回路基板の前記半導体素子が実装される領域と重なる裏面を通過して延在され、前記入力端子と前記入力配線とが前記回路基板に形成されたバイアホールにより接続されることを特徴とする半導体素子の実装構造が提供される。

10

本発明の第1実施例によれば、各回路基板は、出力配線、出力端子及び入力配線が、半導体素子を実装した面に形成され、入力端子及び入力バス配線が、半導体実装面と反対側の面に形成され、かつ各入力端子と対応する各入力配線とを接続するためのバイアホールが回路基板に設けられると共に、入力バス配線によって隣接する回路基板の各半導体素子を連絡するバス配線経路が構成されるようになっている。

この場合、前記入力バス配線に加えて、半導体素子の端子を経由して入力配線を互いに接続することによって、第2の入力バス配線が半導体実装面に形成される。また、半導体素子の内部が複数にブロック分けされる場合には、同じ信号を各ブロックの入力配線及び入力端子から別個に供給することができる。また、一方の入力配線から入力した信号に対する半導体素子の出力が、他方の入力配線を介して別の回路基板の半導体素子に送られ、該半導体素子から出力されるようなカスケード接続も可能である。更に、このような半導体素子と入力端子及び入力配線との接続は、必要に応じて適当に組み合わせができる。

20

半導体素子を実装するための構造であって、前記半導体素子を搭載した複数の回路基板を備え、前記各回路基板が、前記半導体素子に接続された入力配線及び出力配線と、前記入力配線に接続された入力端子と、前記出力配線に接続された出力端子と、前記入力端子に接続された入力バス配線と、を有し、前記出力配線、前記出力端子及び前記入力配線が、前記各回路基板の前記半導体素子を実装した面に設けられ、前記入力端子及び前記入力バス配線が、前記各回路基板の前記半導体素子実装面と反対側の面に設けられ、前記入力バス配線は前記入力端子間を相互に接続してなり、前記入力配線が、前記入力端子または前記入力バス配線と、前記各回路基板に形成されたバイアホールを介して接続され、前記各回路基板の前記入力バス配線により相互に接続された前記入力端子と、当該回路基板に隣接する前記回路基板の入力端子との間が、ワイヤボンディングにより接続されていることを特徴とする半導体素子の実装構造。

30

更に、半導体素子を実装するための構造であって、前記半導体素子を搭載した複数の回路基板を備え、前記入力配線に接続された入力端子と、前記出力配線に接続された出力端子と、前記入力端子に接続された第1の入力バス配線と、前記半導体素子を介して前記入力配線を相互に接続してなる第2の入力バス配線と、を有し、前記出力配線、前記出力端子、前記入力配線及び前記第2の入力バス配線が、前記回路基板の前記半導体素子を実装した面に設けられ、前記入力端子及び前記第1の入力バス配線が、前記回路基板の前記半導体素子実装面と反対側の面に設けられ、前記第1の入力バス配線は前記入力端子間を相互に接続してなり、前記入力配線が、前記入力端子または前記第1の入力バス配線と、前記各回路基板に形成されたバイアホールを介して接続され、前記各回路基板の前記第1の入力バス配線により相互に接続された前記入力端子と、当該回路基板に隣接する回路基板の入力端子との間が、ワイヤボンディングにより接続されていること、を特徴とする半導体素子の実装構造。

40

本発明によれば、このように構成することによって、回路基板に形成されるバイアホールの数を削減し、またはバイアホールを排除することができ、回路基板の実装面積を小さくしつつ薄型化することができる。

また、本発明の別の実施例によれば、上述した各回路基板に複数の半導体素子を搭載する

50

ことができ、これを電子装置に実装することによって、一回の接続工程で複数の半導体素子を同時に接続することができる。

また、本発明の半導体装置の実装方法は、電子装置に、半導体素子を実装するための方法であって、一方の面に前記半導体素子を実装し、前記一方の面に前記半導体素子の入力配線及び出力配線、並びに出力端子を有し、他方の面上に前記入力端子を有し、前記入力端子と前記一方の面の対応する前記入力配線とをバイアホールを介して接続し、かつ前記入力端子と同一面上に入力バス配線を有する回路基板を用意し、前記出力端子を前記電子装置の対応する端子に接続することによって、前記回路基板を前記電子装置に実装することを特徴とする。

特に、本発明による半導体素子の実装構造を液晶表示装置に適用した場合、それぞれ液晶駆動用半導体素子を搭載し、半導体素子に接続された2組の入力配線及び1組の出力配線と、各組の入力配線にそれぞれ接続された2組の入力端子と、出力配線に接続された1組の出力端子と、各組間の入力端子を相互に接続する入力バス配線とを有する複数の回路基板を備え、これらの回路基板において、出力配線、出力端子及び入力配線が、半導体素子を実装した面に形成され、入力端子及び入力バス配線が、半導体素子実装面と反対側の面に形成され、各入力端子と対応する各入力配線とを接続するためのバイアホールが設けられ、かつ各回路基板の出力端子を液晶表示装置の電極端子に接続すると共に、各回路基板がその各組の入力端子を互いに隣接する別の回路基板の1組の入力端子と電気的に接続することにより、相互に連結されていることを特徴とする液晶表示装置が提供される。

これによって、液晶表示パネルの表示部分の外側に形成される額縁部分を縮小することができ、実質的に表示部分を拡大して、ダウンサイジング化に適したコンパクトな液晶表示装置を得ることができる。

#### 【図面の簡単な説明】

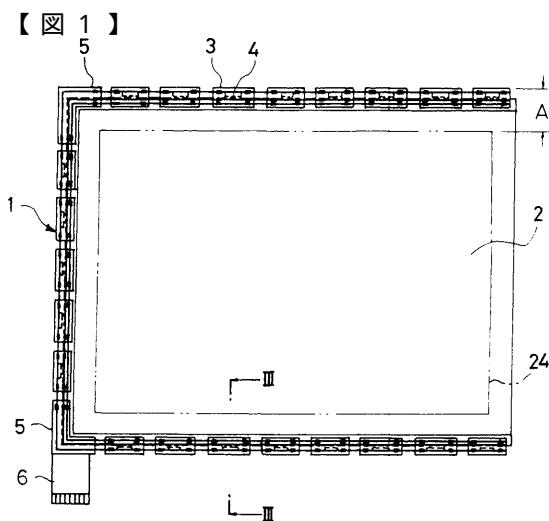

第1図は、本発明による第1実施例の半導体素子の実装構造を適用した液晶表示装置の平面図である。

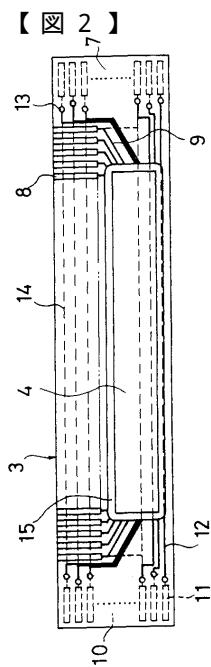

第2図は、第1図の液晶表示装置に使用される回路基板を示す平面図である。

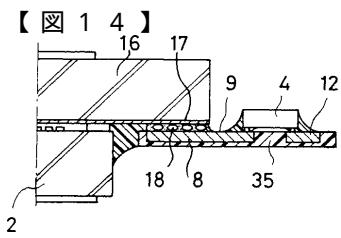

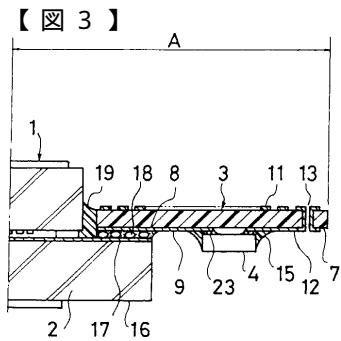

第3図は、第1実施例の回路基板をLCDセルに接続した状態を示す第1図のIII-III線に於ける部分拡大断面図である。

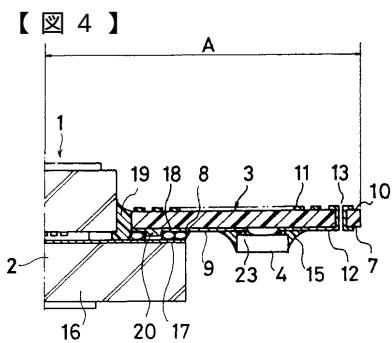

第4図は、第1実施例の回路基板の変形例を示す第3図と同様の断面図である。

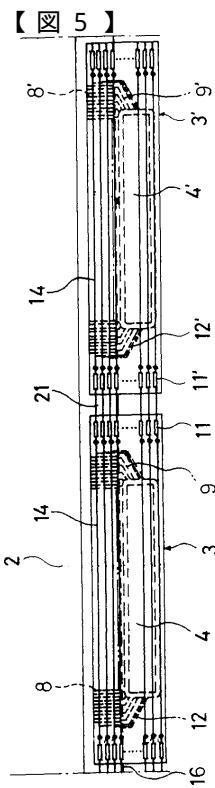

第5図は、第1図の液晶表示装置に於いて隣接する回路基板同士の接続状態を示す部分拡大図である。

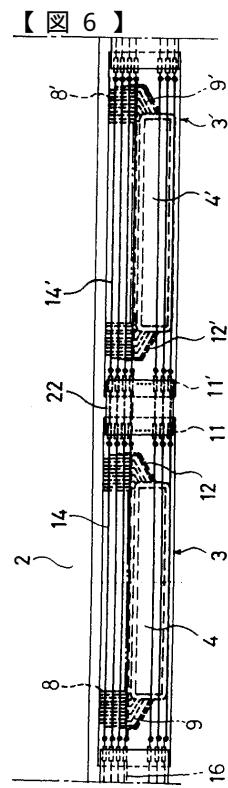

第6図は、FPC(フレキシブル配線板)を用いて隣接する回路基板同士を接続する別の実施例を示す図5と同様の部分拡大図である。

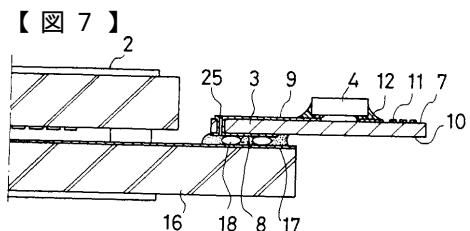

第7図は、本発明の参考例による回路をLCDセルに接続した状態を示す第3図と同様の断面図である。

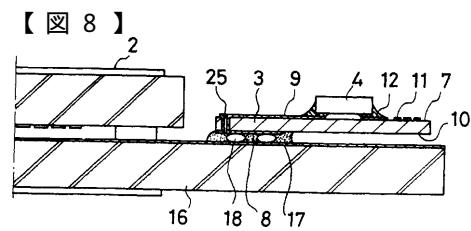

第8図は、参考例の変形例を示す断面図である。

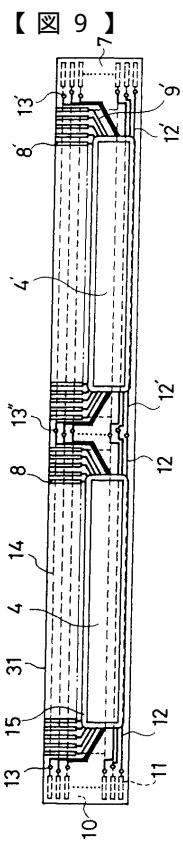

第9図は、2個のLCD駆動用LSIを搭載した本発明の他の実施例による回路基板を示す平面図である。

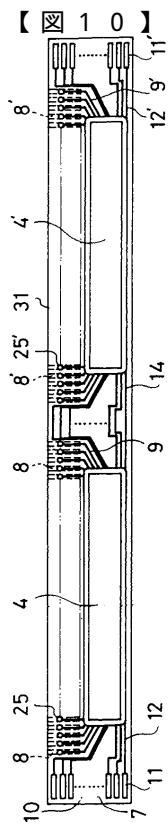

第10図は、第9図の変形例である参考例を示す回路基板の平面図である。

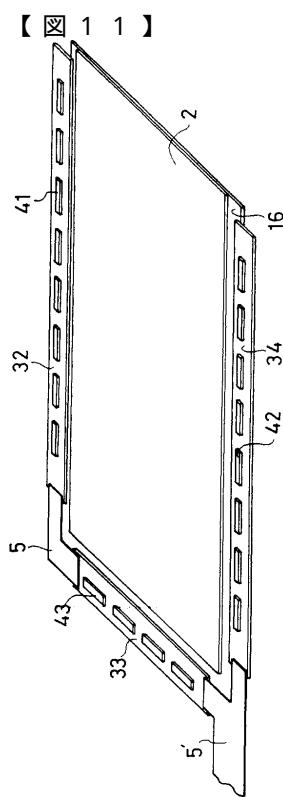

第11図は、多数のLCD駆動用LSIを搭載した回路基板をLCDセルの周辺に接続した液晶表示装置を示す斜視図である。

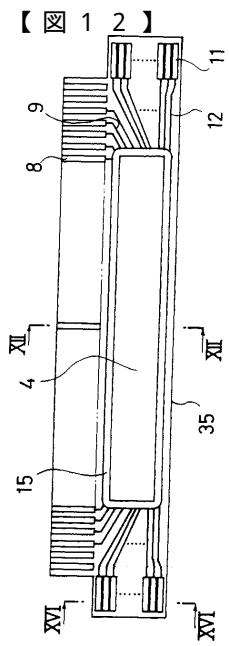

第12図は、本発明の参考例による半導体素子の実装構造に使用する回路基板の平面図である。

第13図は、第12図のXII-XII線に於ける回路基板の断面図である。

第14図は、参考例の回路基板をLCDセルに接続した状態を示す断面図である。

第15図は、参考例の回路基板の変形例を示す第13図と同様の断面図である。

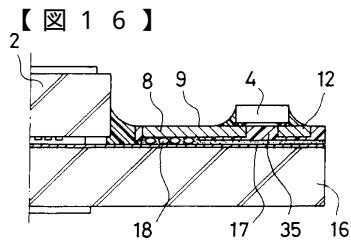

第16図は、第15図の回路基板をLCDセルに接続した状態を示す断面図である。

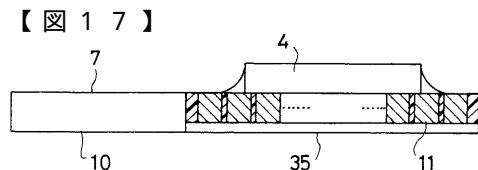

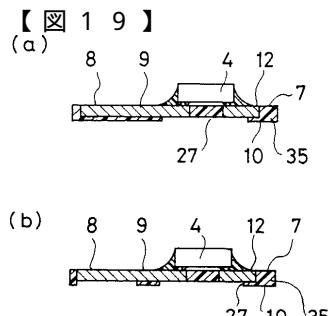

第17図は、参考例の別の変形例による回路基板を示す第12図のXVI-XVI線に於ける断面図である。

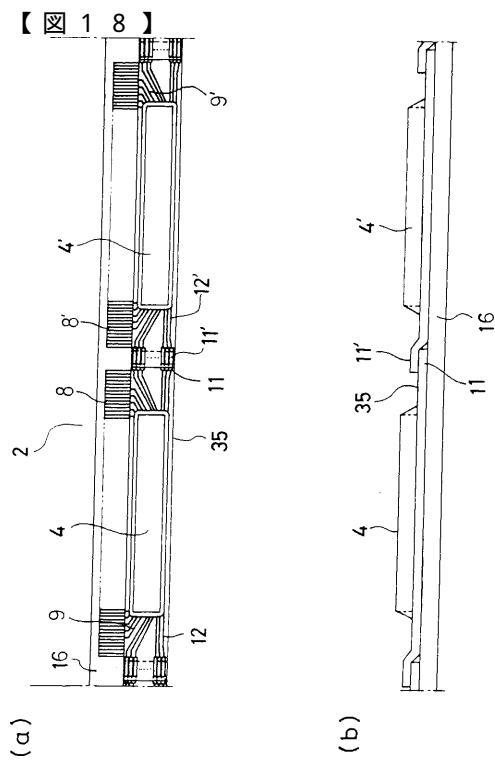

第18図(a)(b)は、第17図の変形例による複数の回路基板をLCDセルに接続する際に

10

20

30

40

50

隣接する回路基板同士の接続状態をそれぞれ示す平面図及び側面図である。

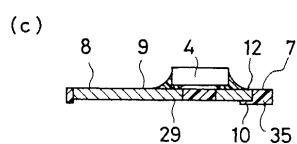

第19図( a )～( c )は、それぞれ参考例による回路基板の更に別の変形例を示す断面図である。

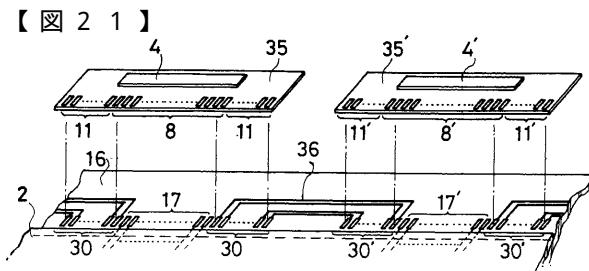

第20図は、複数の回路基板をLCDセルに接続するための別参考例を示す斜視図である。

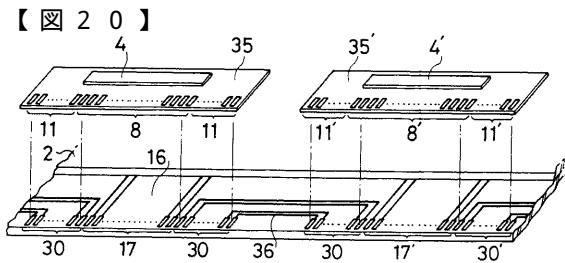

第21図は、第20図の参考例の変形例を示す斜視図である。

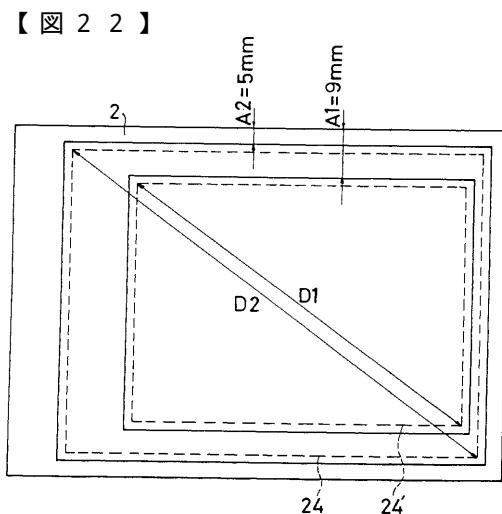

第22図は、液晶表示装置の表示部及びデスエリアを示す平面図である。

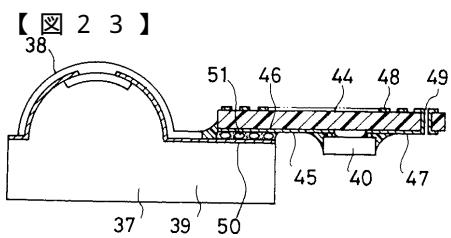

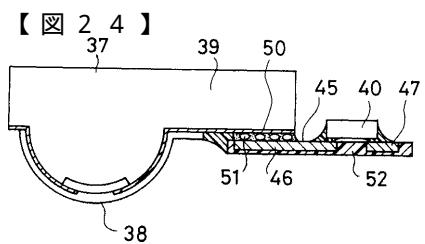

第23図は、本発明の第1実施例を適用して駆動用LSIを実装した電子印字装置を示す断面図である。

第24図は、参考例の回路基板を用いた電子印字装置を示す第23図と同様の断面図である。

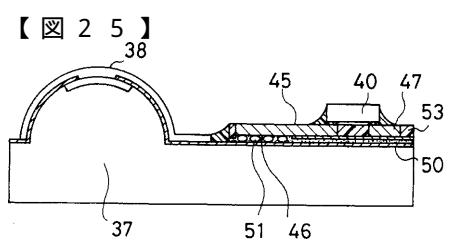

第25図は、参考例の変形例による第15図の回路基板を用いた電子印字装置を示す断面図である。

第26図は、従来技術による多層構造の回路基板を用いた半導体素子の実装構造を示す断面図である。

第27図は、第26図の回路基板を示す平面図である。

#### 発明を実施するための最良の形態

第1図に於いて、本発明による半導体素子の実装構造を適用した液晶表示装置1は、通常のXYマトリックス電極構造を有するLCDセル2の周辺部に、その上辺、下辺及び左辺に沿ってそれぞれ多数の回路基板3が直線状に連続して接続されている。LCDセル2の上辺及び下辺に接続された回路基板3にはX側の液晶駆動用LSI4が、前記LCDセルの左辺に接続された回路基板3にはY側の液晶駆動用LSI4が、それぞれ1個ずつ後述するように実装されている。また、LCDセル2の左上角部及び左下角部には、X側の前記回路基板の入力バス配線とY側の前記回路基板の入力バス配線とを連絡接続するための中継基板5がそれぞれ配設されている。更に、LCDセル2の左下角部の中継基板5には、前記各回路基板に電源及び電力信号を供給するためのケーブル6が接続されている。

回路基板3は、例えばセラミックス、ガラスエポキシ樹脂、ポリイミド樹脂等通常の比較的硬質な基板材料を用いて、図2に示されるように長手方向に細長い長方形に形成されている。回路基板3の一方の面7には、その下半分の略中央位置に、同様に細長い長方形をなす1個の液晶駆動用LSI4が長手方向に沿ってフェイスダウンボンディングにより実装されている。当然ながら、別の実施例では、必要に応じて長方形以外の異なる形状例えば正方形に近い外形のLSIを用いることができ、それに応じて回路基板3の外形を変更することができる。また、使用条件や必要に応じて、例えば液晶表示装置1の表示内容が増大して周波数が高くなる場合等に、回路基板3に電気的グランド層を設ける必要が生じる。このような場合には、回路基板3の内部にグランド層として導電層を設けることができる。回路基板3のLSI実装面即ち表面7の上半分には、その上辺に沿って長手方向にLSI4の出力端子と同数の1組の出力端子8が、一定のピッチで直線状に形成され、かつそれぞれLSI4との間に配設された対応する出力配線9に接続されている。通常、出力端子8のピッチは約100～200μm程度であるが、その材料や成膜プロセスを適当に選択することによって、50μm以下の狭ピッチに形成することも可能である。

回路基板3のLSI実装面7と反対側の面即ち裏面10には、その左右両辺に沿ってそれぞれLSI4の入力端子と同数の各1組の入力端子11が、一定のピッチで直線状に並設されている。本実施例に於いて、入力端子11のピッチは約100～300μm程度である。更に回路基板3の表面7には、入力配線12が、LSI4から前記回路基板の左右各辺に向けて対応する入力端子11の位置まで延長するようにパターン形成されている。各入力端子11は、対応する入力配線12とそれぞれバイアホール13を介して接続され、これによりLSI4に接続されている。本実施例に於いて、バイアホール13の直径は100μmであるが、必要に応じて適当に変更することができる。更に、回路基板3の裏面10には、左辺の入力端子11と右辺の入力端子11とを相互に接続する入力バス配線14がパターン形成されている。

本実施例では、図示されるように、左右2組の入力端子11が、それぞれ入力配線12を介して前記LSIの入力端子に接続されている。従って、回路基板3の左辺の入力端子11と右辺の入力端子11とが、前記各LSIの入力端子を経由して入力配線12によって相互に接続され

10

20

30

40

50

るので、裏面10の入力バス配線14に加えて、それと並行に入力配線12からなる第2の入力バス配線がLSI実装面7に設けられることになる。これにより、回路基板3全体として入力バス配線の抵抗値を小さくすることができる。

また、LSI4が特に第2図のように細長いスリムタイプの場合には、内部が複数に例えれば左右にブロック分けされ、かつブロック毎に別個にLSI入力端子を設けることがある。このような場合、各ブロックの前記LSI入力端子は、左右いずれか近い方の入力端子11と入力配線12を介して接続され、従って同じ信号が左右から別個に供給される。また、本実施例によれば、左辺の入力端子11から左辺側の入力配線12を介してLSI4に接続し、かつその出力を右辺側の入力配線12を介して右辺の入力端子11に接続することによって、隣接する左右の回路基板のLSIを直列に連結するカスケード接続に適用することができる。 10

実際には、これらの実施例を、使用する回路基板やLSIの構成等要求に応じて適当に組み合わせることができる。例えば、LSI4の内部が部分的に例えば電源系統がブロック分けされて、一部の信号が左右の入力端子及び入力配線から別個に入力され、他の一部の信号は上述したカスケード接続により、例えは右側の入力端子及び入力配線を介して隣接する回路基板のLSIに送信され、かつ残りの信号が、LSIの入力端子を経由して接続される左右の入力配線からなる入力バス配線を介して送信されるように構成することも可能である。

これらの配線9、12、14及び端子8、11は、Au単体により、またはAgPd、Ag、Cuをベース材料として必要に応じてNi・AuまたはSn等をめっきすることにより形成され、かつ必要に応じてその表面にソルダレジスト等を塗布することによって、腐食及び損傷の防止を図ることができる。バイアホール13は、前記各配線及び端子と同様にAu等の金属材料により、またはAgPd、Ag、Cuをベース材料に必要に応じてNi・AuまたはSn等をめっきすることにより形成され、かつ必要に応じてソルダレジスト等が塗布される。回路基板3に実装されたLSI4は、必要に応じて紫外線硬化型、熱硬化型エポキシ系等の接着剤からなるモールド材15で被覆することにより、耐湿性、絶縁性を高めて信頼性の向上を図ることができる。 20

第3図には、回路基板3をLCDセル2に接続することによって、駆動用LSI4を液晶表示装置1に実装した構造が示されている。LCDセル2の電極パターンを形成した下側の透明電極基板16の周辺部上面には、前記電極に接続されたLCD端子17が、回路基板3の出力端子8に対応させて所定ピッチで直線状に形成されている。各LCD端子17は、通常ITO(酸化インジウムスズ)透明電極からなり、必要に応じてCr、Ni、Au、Cu等の金属又はそれらを組み合わせてめっき処理することができる。 30

回路基板3は、各出力端子8を対応するLCD端子17と位置合わせしつつ、それらの間にACF即ち異方性導電膜18を配設して、所定の加圧・加熱ツールにより熱圧着することによって、一括して電気的かつ機械的に接続される。本実施例では、ACF18として日立化成工業(株)製のAC6000番系または7000番系の熱硬化型のものを使用した。また、ACFには、例えばUV硬化性のものや、ペースト状の異方性導電接着剤を用いることができる。更に、LCDセル2と回路基板3との接続部分には、防湿等を目的としてモールド材19を施すことができる。

別の実施例では、第4図に示すように回路基板3の出力端子8にAu、Cu等のバンプ20が形成されている。これに、第3図と同様にACF18を用いて接続することによって、出力端子8とLCD端子17とをより確実かつ良好に電気的に接続することができる。 40

第5図に示すように、隣接させてLCDセル2に接続された回路基板3、3'同士は、互いに隣接する入力端子11、11'同士が、Au、Al、Cu等の金属又はそれらの合金からなるワイヤ21を用いてワイヤボンディングにより相互に接続されている。これによって、LCDセル2の周辺に連続して実装された全回路基板3の入力バス配線14が相互に連絡される。実際上、隣接する前記回路基板の入力端子同士をワイヤボンディングする際には、回路基板3、3'の下側に適当な支持部材を配設すると好都合である。また、別の実施例では、第6図に示すように、その表面に配線をパターン形成したFPC22を用いて、隣接する回路基板3、3'の入力端子11、11'間を接続することができる。

また、上述した実施例では、LSI4がAu等のバンプ付き入力・出力端子23を有し、フェイスダウン方式で回路基板3の入力及び出力配線11、9に直接接続されている。しかしながら 50

、フェイスアップ方式を採用して回路基板3上に上向きに固定したLSI4の各入力・出力端子を対応する入力及び出力配線とワイヤボンディングすることもできる。

このように、本発明の半導体素子の実装構造によれば、回路基板3の出力端子8をLSI4の実装面7と同一面上に設けてLCDセル2の端子17と接続することによって、上述した特願平5-223523号明細書記載の実装構造のように、出力配線と出力端子とを接続するためのバイアホールを回路基板に設ける必要がない。特に出力端子の数は入力端子の数よりも非常に多く、上述したように半導体素子1個当たり80～数百個であるから、出力端子のためのバイアホールをなくすことによって、回路基板をコンパクトかつ安価に形成でき、かつその面積を有効に利用でき、配線の自由度を高めることができる。また反対側の面10に入力端子11及び入力バス配線14を形成することによって、回路基板3の外形をよく小さくし、かつ中間導電層をなくしてその厚さを薄くすることができる。10

これによって、LCDセル2の周囲に存在する額縁部分、即ち第1図に於いて液晶表示装置1の表示部24の周囲に寸法Aで示される実装領域を、非常に小さくすることができます。更に、回路基板3の薄型化によって、該回路基板をLCDセル2に実装した際にその厚さの範囲内にLSI4を収めることができる。従って、実装構造をコンパクト化して、液晶表示装置1全体を小型化することができる。また、別の実施例では、LCDセル2のいずれか1辺にのみ、2辺又は4辺全部に本発明による半導体素子の実装構造を用いることができ、その場合にも同様の作用効果が得られる。

第7図には、本発明による半導体素子の実装構造の参考例が示されている。本実施例の回路基板3は、第2図に示す第1実施例の回路基板と概ね同じ細長い長方形をなし、かつその略中央にLCD駆動用LSI4が実装されている。LSI実装面7には、出力配線9、入力配線12に加えて、その左右両辺に沿って各1組の、それぞれLSI4の入力端子と同数の入力端子11が形成されている。左辺の入力端子11と右辺の入力端子11とは、それぞれ対応する左右の入力配線12を介してLSI4の入力端子に接続されている。即ち、LSI4の前記入力端子を経由して左右両辺の入力端子11同士を接続する左右の入力配線12が、同時に入力バス配線14を構成する。更に、本参考例では、左辺の入力配線12から入力した信号に対する前記LSIの出力が、右辺の入力配線12を介して別の回路基板のLSIに送られ、該LSIから出力されるようなカスケード接続を組み合わせることも可能である。20

回路基板3のLSI実装面7と反対側の面10には、第1実施例の回路基板と同様にその上辺に沿って長手方向に1組の出力端子8が形成され、かつ回路基板3を貫通するバイアホール25によってそれぞれ対応する出力配線9と相互に接続されている。回路基板3は、出力端子8を電極基板16上のLCD端子17と位置合わせしつつ、その間にACF18を配置して熱圧着することにより、同様にLCDセル2に電気的かつ機械的に接続される。本参考例の場合にも、隣接する回路基板3同士は、第1実施例と同様に入力端子11同士をワイヤ又はFPCを用いることによって相互に接続される。30

本参考例の場合、LSI実装面7では入力配線12即ち入力バス配線を設計する際に、電力基板16との接着面積を必要とする反対側の面10と比較して、そのピッチをより大きく設定できるので有利である。また、入力端子11と接続するためのバイアホールを設ける必要がないので、上述した第1実施例程度ではないが、回路基板3のコンパクト化、コストの低減化及び基板面積の有効利用を図ることができる。40

第8図には、上述した参考例の変形例が示されており、電極基板16の周辺部が、その平面に於いて回路基板3全体を含む領域まで拡大されている。これにより、回路基板3を、出力端子8の部分だけでなくその下面10全体で電極パネル16上に接着することができ、LCDセル2に回路基板3を機械的に強固にかつ確実に接続することができる。

第9図には、1個の回路基板に2個のLCD駆動用LSIを実装した本発明の第3他の実施例による半導体素子の実装構造が示されている。この回路基板31は、第2図に示す第1実施例の回路基板3と同様の構成を有し、かつそれよりも左右に細長い帯板状に形成され、その一方の面7に2個のLSI4、4'が、長手方向に一方の側辺に沿って直列にフェイスダウンボンディングにより実装されている。

LSI実装面7には、各LSI4、4'の出力端子に対応する同数の各1組の出力端子8、8'には、各LSI4、4'の出力端子に対応する同数の各1組の出力端子8、8'。50

が、それぞれ長手方向の他方の側辺に沿って一定ピッチで直線状に配置されている。前記各組の出力端子は、それぞれ対応する各LSI4、4'から延長するようにパターン形成された出力配線9、9'と接続されている。回路基板3の裏面10には、左右各辺にそれぞれ1組の、LSI4、4'の入力端子と同数の入力端子11、11'が、一定ピッチで配置されている。前記左右各組の入力端子同士は、前記回路基板裏面を長手方向に延長するようにパターン形成された入力バス配線14によって、相互に接続されている。

更にLSI実装面7には、各LSI4、4'の入力配線12、12'がそれぞれパターン形成されている。前記各LSIから回路基板3の左辺または右辺に向けて延長する入力配線12、12'は、バイアホール13、13'を介して対応する各入力端子11、11'と相互に接続されている。更に前記両LSI4、4'間を延長する入力配線12、12'が、相互に接続されると共に、共通のバイアホール13'を介して入力バス配線14と接続されている。10

従って、第1実施例の回路基板3の場合と同様に、回路基板31の左辺の入力端子11と右辺の入力端子11'とが、前記両LSIの入力端子を経由して入力配線12及び12'によって相互に接続される。これにより、上述した入力バス配線14に加えて、第2の入力バス配線がLSI実装面7に設けられることになり、全体として入力バス配線の抵抗値を小さくすることができます。

更に第1実施例の場合と同様に、LSI4、4'が細長いシリムタイプで内部が左右にブロック分けされている場合には、前記各LSIの左側または右側ブロックの入力端子が、左辺または右辺の近い方の入力端子11、11'と入力配線12、12'を介して接続され、かつ前記各LSIの他方のブロックの入力端子が、両LSI間の入力配線12、12'及び共通のバイアホール13'を介して入力バス配線14と接続されて、同じ信号が左右ブロックに別個に供給される。また、左辺の入力端子11から左辺側の入力配線12を介して左側のLSI4に接続し、その出力を前記両LSI間の入力配線12、12'を介して右側のLSI4'に接続し、かつその出力を右辺側の入力配線12'を介して右辺の入力端子11'に接続するカスケード接続を含むよう<sup>20</sup>または組み合わせて配線を構成することも可能である。

回路基板31は、第3の場合と同様に各出力端子8、8'を対応する電力基板のLCD端子に位置合わせしつつ、ACFを用いてLCDセルに一括接続される。このように、本実施例によれば、2個の液晶駆動用LSIを1回の接続工程でLCDセルに実装することができる。また、隣接する回路基板31の入力端子間は、ワイヤボンディング又はFPCにより相互に接続される。これによって、隣接する回路基板同士を連絡するためのバス配線経路が形成される。30

また、回路基板31を、図7の参考例と同様にLSI実装面に出力端子を設けた構成にすることができる。図10には、このような変形例の参考例による半導体素子の実装構造が示されている。同図の回路基板31も同様に細長い帯板状をなし、かつその一方の面7に2個のLSI4、4'が、長手方向に沿って直列にフェイスダウンボンディングされている。

LSI実装面7には、左右各辺にそれぞれ1組の入力端子11、11'が一定ピッチで配置され、かつ前記各入力端子から各LSI4、4'に向けて入力配線12、12'がパターン形成されている。更にLSI実装面7の上辺に向けて各LSI4、4'の出力配線9、9'がパターン形成されている。回路基板3の裏面10には、LCDセルに接続するための各1組の出力端子8、8'が、それぞれ長手方向の側辺に沿って出力配線9、9'に対応する位置に直線状に配置され、かつ回路基板3を貫通するバイアホール25、25'を介して相互に接続されている40。

また、回路基板3のLSI実装面7には、LSI4、4'の入力端子が接続されるランド同士を接続する入力バス配線14がパターン形成されている。これによって、入力端子11、11'同士が入力配線12、12'及び入力バス配線を介して相互に接続され、隣接する回路基板同士を連絡するためのバス配線経路を形成している。

更に本発明によれば、1個の回路基板に3個又はそれ以上の半導体素子を実装して、1度の接続工程で多数の半導体素子を同時に実装することができる。このような本発明の好適な実施例が第11図に示されている、同図に示すように、LCDセル2には、その周辺部に沿って上辺、下辺及び左辺にそれぞれ1個の細長い帯板状の回路基板32~34が接続されている。回路基板32、34にはそれぞれ8個のX側駆動用LSI41、42が、及び回路基板33には4

個のY側駆動用LSI43が、それぞれ一方の面に長手方向に沿って直線状に連続して実装されている。

各回路基板32～34は、第10図示の参考例と略同様の構成を有し、LSI実装面には、左右両辺に設けられた各1組の入力端子に接続された入力配線、及び隣接するLSI同士を連絡するための入力バス配線がパターン形成されている。前記LSI実装面と反対側の面には、各LSIの出力端子が長手方向の一方の側辺に沿って形成されている。従って、各回路基板32～34は、前記出力端子と電極基板16との間にACFを用いることによって、容易に電極基板16に一括接続される。

更に、LCDセル2の左上角部には、中継基板5が配設されて、X側の回路基板32とY側の回路基板33とを前記入力端子を介して相互に接続している。LCDセル2の左下角部には、

外部へのケーブルを一体化した中継基板5'が配設され、下側のX側回路基板34とY側回路基板33を接続すると共に、前記各回路基板に外部から電源、入力信号等を供給することができる。また、当然ながら、X側回路基板32、34は、Y側回路基板の接続されない右辺又は左辺には、前記入力端子を設けなくてもよい。

本発明によれば、このようにLCDセルの各辺に沿ってそれぞれ1個の回路基板を接続することにより多数の液晶駆動用LSIを実装することによって、工数を少なくし、かつ作業を容易にして生産性の向上を図り、製造コストを低減させることができる。同時に、上述した各実施例と同様に、液晶表示装置の実装面積を従来より大幅に少なくすることができる。例えば、第22図に示すように、本発明による実装構造を用いて20cm(8インチ)サイズの液晶表示パネルを製造した場合、同一の外形寸法に対して表示部24の周囲に形成される額縁部分即ちデスエリアの大きさを、同図に示す寸法Aに於いて従来のA1=9mmからA2=5mmに削減することができた。これによって、同一外形寸法の液晶表示パネルに於いて、表示部のサイズをD1=20cmからD2=22cm(8.7インチ)のものに変更することができ、表示面積を実質的に拡大することができた。

また、本実施例においても、回路基板35を、第2図の第1実施例の回路基板3と同様にLSI実装面に出力端子を設けた構成にすることができ、その場合にも同様に2個の液晶駆動用LSIを搭載することができる。

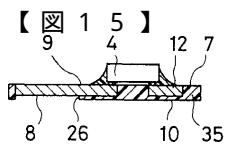

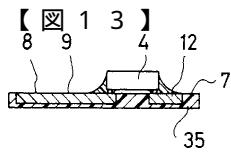

第12図及び第13図には、本発明の参考例による半導体素子の実装構造の回路基板35が示されている。本参考例の回路基板35は、上述した第1乃至第3実施例の回路基板と同様に細長い長方形をなすが、LCD駆動用LSI4の実装面7上に出力端子8、出力配線9、入力端子11、及び入力配線12がパターン形成され、そのためにバイアホールを全く有しない点で異なる。このように、出力端子又は入力端子と出力配線又は入力配線を接続するバイアホールを全く用いないことによって、回路基板35自体の構成を極めて簡単にすことができ、製造コストをより一層低減させることができる。

更に、回路基板35の左右各辺には、それぞれ1組のLSI4の入力端子と同数の入力端子11が配設され、かつそれぞれ入力配線12を介して前記LSI4入力端子と接続されている。このように左辺及び右辺の入力端子11同士を接続する入力配線12によって、同時に隣接する別の回路基板を連絡するための入力バス配線が形成される。また、本参考例においても上述した各実施例又は各参考例と同様に、左辺の入力配線12から入力した信号に対する前記LSI4の出力が、右辺の入力配線12を介して別の回路基板のLSI4に送られて出力されるカスケード接続を組み合わせることが可能である。

本参考例の回路基板35は、第14図に示すように、上述した各実施例と同様にACF18を用いて、出力端子8が電極基板16のLCD端子17に電気的かつ機械的に接続される。このようにして薄型化し、かつLSI4と出力端子8とを同一面上に設けた回路基板35をLCDセル2に接続することによって、LSI4が、電極基板16の側方にかつその厚みの範囲内に配置されるので、液晶表示装置全体を薄型化することができる。

また、本参考例の回路基板35は、第13図に示されるように、入力端子8、出力配線9、入力配線12及び入力端子11が回路基板35のLSI実装面7から内部に埋設するように形成されている。従って、例えば第15図のように、回路基板35の裏面10を部分的に削除して窓部26を開設することによって、出力端子8を裏面10側に露出させることができる。

10

20

30

40

50

このように出力端子8を回路基板35の両面に露出させることによって、回路基板35は、第16図に示すように裏面10側から電極基板16のLCD端子17に接続することができる。この場合、回路基板35をその全面に亘って電極基板16に接着できるので、より確実かつ安定的に固定することができる。回路基板35の窓部26は、例えばエキシマレーザ加工等により裏面10を選択的に除去することによって容易に形成することができる。

窓部を開設した回路基板35の別の参考例が、第17図に示されている。参考例の回路基板35は、第12図に示すように、入力端子11を設けて左右各側辺部分が、外方に幾分突出している。第17図の変形例では、前記左右側辺部分の裏面10を削除して、入力端子11を裏面10側に露出させている。このように入力端子11を回路基板35の両面に露出させることによって、複数の回路基板35をLCDセル2の周辺部に隣接させて実装する場合、第18図に示すように回路基板35の隣接する入力端子11部分を相互に重ね合わせて、ACFや半田付け等によって相互に接続することができる。この場合、上述した第1及び第2実施例のようにワイヤボンディングやFPCを用いる必要がないので接続作業が容易であり、かつ接続部分の信頼性が向上し、しかも部品点数が少なくなってコストの低減化を図ることができる。10

第19図(a)～(c)には、参考例の回路基板の更に別の変形例がそれぞれ示されている。第19図(a)の回路基板35は、回路基板裏面10のLS14に対応する領域に窓部27が設けられている。また、第19図(b)には、第19図(a)の窓部27に加えて、第14図と同様に出力端子8を露出させる窓部28が開設形成されている。更に、第19図(c)の回路基板35には、出力端子8、出力配線9、入力配線12を含む回路基板裏面10の略全体を露出させる窓部29が設けられている。これらの変形例では、回路基板35の裏面10にLS14の実装領域に対応する窓部を設けることによって、LS14を回路基板35に実装する際に、加熱ツールを入力配線12及び出力配線9に直接当てることができる。このため、LS14の各入出力端子を入力及び出力配線12、9により容易にギャングボンディングすることによって接続することができる。20

第20図及び第21図には、参考例の回路基板35をLCDセル2に接続するための別の構成がそれぞれ示されている。第20図の実施例では、入力端子11が、回路基板35の左右両側辺ではなく、長手方向の一方の側辺に沿って出力端子8の配列の左右両側に配置されている。回路基板35のLSI実装面7と反対側の裏面には、図示していないが第17図と同様に出力端子8及び入力端子11を露出させる窓部が開設されている。

LCDセル2の電極基板16の周辺部には、そのX電極又はY電極に接続されたLCD端子17に加えて、それらと同様に電極基板16の周縁に沿って、回路基板35の入力端子11に対応する位置にパネル接続端子30がパターン形成されている。更に、電極基板16には、前記回路基板に隣接させて別の回路基板35'を接続するために、同様にLCD端子17'及びパネル接続端子30'が、電極基板16の周縁に沿ってパターン形成されている。30

回路基板35のパネル接続端子17と隣接する回路基板35'のパネル接続端子17とは、それぞれ電極基板16上にパターン形成されたバス配線36によって相互に接続されている。従って、回路基板35、35'を、その出力端子8、8'及び入力端子11、11'をそれぞれ対応するLCD端子17、17'及びパネル接続端子30、30'に位置合わせして、例えばACFを用いて熱圧着することによって電極基板16に接続すると、同時に前記両回路基板の入力端子11、11'同士が相互に接続される。40

このように本参考例では、ワイヤボンディングやFPCを用いることなく、各回路基板を電極基板に実装するだけで、隣接する前記回路基板同士が接続されて、入力バス配線が相互に連絡される。従って、接続作業が容易で工数を少なくできる利点がある。更に本参考例では、回路基板35の出力端子8及び入力端子11が一直線状に配置されるので、加圧ヘッドを直線状の簡単な形状にすることができ、ボンディング装置を簡単に構成することができる。

また、第20図の参考例では、回路基板裏面に窓部を開設して入出力端子を露出させた第17図と同じ構成を有する回路基板を使用したが、少なくとも出力端子及び入力端子が同一面上に配設されれば、他の構成の回路基板を用いることができる。例えば、第12図に示される回路基板裏面に窓部を有しない構造のものを使用することができる。この場合、回50

路基板35は、第14図の場合と同様にLSI4が電極基板16の側方に、かつその厚さの範囲内に位置するように接続される。

第21図の参考例では、各LCD端子17及びパネル接続端子30が電極基板16の内側に配置され、その外側にバス配線36がパターン形成されている。回路基板35は、第20図の参考例と同じ構成のものであり、同様にACF等を用いて電極基板16に一括に接続される。

本実施例では、LCD端子17からLCDセル2のX電極又はY電極への配線長が、第20図の参考例の場合よりも短くなるので、その配線抵抗値が小さくなる利点が得られる。また、LCD端子17等を形成する電極基板16の周辺部を、第20図の参考例の場合よりも小さくすることができます。但し、本参考例では、電極基板16の周辺部にLCD端子17及びパネル接続端子30の外側にバス配線36を設ける領域を確保する必要となるので、第20図の参考例のように、裏面に窓部を有しない第13図の回路基板を接続することは困難である。10

以上、本発明による半導体素子の実装構造を、電子装置として液晶表示装置に適用した場合について説明したが、本発明は、EL(エレクトロルミネセンス)ディスプレイ、プラズマディスプレイ等の他の電子表示装置や、サーマルプリンタ等の電子印字装置にも同様に適用することができる。

第23図乃至第25図には、電子印字装置としてサーマルプリンタヘッドに駆動用LSIを実装する構造の実施例が示されている。第23図に於いて、サーマルプリンタヘッド37には、発熱部38を形成したセラミック基板39上に、駆動用LSI40を搭載した回路基板44が接続されている。回路基板44は、第1図の回路基板3と同様の構成を有し、駆動用LSI40を搭載した面に出力配線45、出力端子46、入力配線47が形成され、かつ反対側の面には、入力端子48と隣接する回路基板のLSIに接続するための入力バス配線が形成されると共に、入力端子48がバイアホール49により入力配線47と相互に接続されている。回路基板44は、サーマルプリンタヘッド37の基板39上に形成されたサーマルプリンタヘッド端子50と出力端子46を位置合わせして、ACF51を用いて熱圧着により電気的かつ機械的に接続されている。20

第24図の参考例では、回路基板52が第12図の回路基板35と同様の構成を有し、かつ第14図の場合と同様にしてサーマルプリンタヘッド37の基板39に接続されている。また、第25図の参考例では、回路基板53が第15図の回路基板35と同様の構成を有し、かつ第16図の場合と同様にしてサーマルプリンタヘッド37の基板39に接続されている。

このように本発明の半導体素子の実装構造によれば、電子表示装置だけでなく、電子印字装置その他の様々な電子装置に使用した場合にも、実装面積を非常に小さくしあつ装置全体を薄型化することができ、ダウンサイジング化の要請に対応していわゆるデスエリアの少ないコンパクトな電子装置を実現することができる。30

---

フロントページの続き

(56)参考文献 特開平4 - 147221 (JP, A)

特開平4 - 212495 (JP, A)

特開平4 - 274413 (JP, A)

特開平4 - 329648 (JP, A)

実開平5 - 46033 (JP, U)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 21/60 311

G02F 1/1345