(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6232038号

(P6232038)

(45) 発行日 平成29年11月15日(2017.11.15)

(24) 登録日 平成29年10月27日(2017.10.27)

(51) Int.Cl.

H03K 19/177 (2006.01)

G09G 3/30 (2006.01)

F 1

H03K 19/177

G09G 3/30

J

請求項の数 4 (全 37 頁)

(21) 出願番号 特願2015-239187 (P2015-239187)

(22) 出願日 平成27年12月8日 (2015.12.8)

(62) 分割の表示 特願2014-243897 (P2014-243897)

分割

原出願日 平成23年1月19日 (2011.1.19)

(65) 公開番号 特開2016-86422 (P2016-86422A)

(43) 公開日 平成28年5月19日 (2016.5.19)

審査請求日 平成27年12月9日 (2015.12.9)

(31) 優先権主張番号 特願2010-9569 (P2010-9569)

(32) 優先日 平成22年1月20日 (2010.1.20)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 竹村 保彦

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 緒方 寿彦

最終頁に続く

(54) 【発明の名称】プログラマブル回路、及び、FPGA

## (57) 【特許請求の範囲】

## 【請求項1】

チャネル形成領域を酸化物半導体層に有する第2のトランジスタによって、チャネル形成領域をシリコン半導体層に有する第1のトランジスタのゲートへの電位の供給を制御し、基本ブロック間の接続を制御して回路を構築し、

前記第1のトランジスタ上に前記第2のトランジスタを有することを特徴とするプログラマブル回路。

## 【請求項2】

チャネル形成領域を酸化物半導体層に有する第2のトランジスタによって、チャネル形成領域をシリコン半導体層に有する第1のトランジスタのゲートへの電位の供給を制御し、基本ブロック間の接続を制御してコンフィギュレーション処理を行い、

前記第1のトランジスタ上に前記第2のトランジスタを有することを特徴とするプログラマブル回路。

## 【請求項3】

チャネル形成領域を酸化物半導体層に有する第2のトランジスタによって、チャネル形成領域をシリコン半導体層に有する第1のトランジスタのゲートへの電位の供給を制御し、基本ブロック間の接続を制御して回路を構築し、

前記第1のトランジスタ上に前記第2のトランジスタを有することを特徴とするFPGA。

## 【請求項4】

10

20

チャネル形成領域を酸化物半導体層に有する第2のトランジスタによって、チャネル形成領域をシリコン半導体層に有する第1のトランジスタのゲートへの電位の供給を制御し、基本ブロック間の接続を制御してコンフィギュレーション処理を行い、

前記第1のトランジスタ上に前記第2のトランジスタを有することを特徴とするFPG

A。

【発明の詳細な説明】

【技術分野】

【0001】

酸化物半導体を用いた半導体素子を有する、半導体装置に関する。

【背景技術】

10

【0002】

近年、アモルファスシリコンよりも高い移動度と、高い信頼性が得られ、なおかつ、均一な素子特性をも有する新たな半導体材料として、酸化物半導体と呼ばれる半導体特性を示す金属酸化物に注目が集まっている。金属酸化物は様々な用途に用いられており、例えば、よく知られた金属酸化物である酸化インジウムは、液晶表示装置などで透明電極材料として用いられている。半導体特性を示す金属酸化物としては、例えば、酸化タンゲステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような半導体特性を示す金属酸化物をチャネル形成領域に用いる薄膜トランジスタが、既に知られている（特許文献1及び特許文献2）。

【先行技術文献】

20

【特許文献】

【0003】

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、通常の中央演算処理装置（CPU：Central Processing Unit）等の半導体集積回路は、あらかじめ回路設計された構成を製造後に変更することができない。これに対し、プログラマブル論理回路（PLD：Programmable Logic Device）と呼ばれる半導体集積回路は、適当な規模の基本ブロック単位で論理回路が構成されており、各基本ブロック間の接続構造を製造後において変更できることを特徴とする。よって、PLDは、ユーザーの手による回路構成の変更が可能であるため汎用性が高く、また、回路の設計、開発に費やされる期間やコストを大幅に低減させることができる。

30

【0005】

PLDには、CPLD（Complex PLD）、FPGA（Field Programmable Gate Array）などが含まれるが、いずれも、回路構成のプログラムを無制限に書き換えられるタイプの場合、EEPROMやSRAM等の半導体メモリに記憶されている基本ブロックの接続構造に従って、その回路構成が定まる。そして、プログラムされた回路構成によっては、その回路を構成するのに寄与しない基本ブロックが存在する場合もあり得る。特に、規模が大きく汎用性の高いPLDほど、基本ブロック数が増加するため、特殊な用途向けに回路構成をカスタマイズすることで、回路構成に寄与しない基本ブロックの数が増加する。

40

【0006】

ところが、PLDでは、回路構成に寄与しない基本ブロックにも電源電圧の供給が行われている。そのため、当該基本ブロックにおいて、寄生容量を含む各種容量が無駄に充放電され、電力が消費されてしまう。また、電源電圧の供給が行われることで、リーク電流やオフ電流により、当該基本ブロックにおいて不要な消費電力が生じる。例えば、CMOSで構成されているインバータの場合、定常状態において理想的には電力を消費しないが、

50

実際には、ゲート絶縁膜に流れるリーク電流や、ソース電極とドレイン電極間に流れるオフ電流により、電力を消費する。バルクのシリコンを用いて作製されたCMOSのインバータの場合、室温下、電源電圧が約3Vの状態にて、1pA程度のオフ電流が生じる。PLDの高集積化がさらに進むと、半導体素子の微細化や、素子数の増加などにより、上記消費電力はさらに大きくなることが見込まれる。

#### 【0007】

また、書き換え可能なPLDの場合、接続構造を記憶するためのプログラム素子として、EEPROMやSRAMが一般的に用いられている。しかし、EEPROMは、原理上、トンネル電流を利用してデータの書き込みと消去を行っているため、絶縁膜の劣化が生じやすい。よって、実際には、データの書き換え回数は無限ではなく、数万から数十万回程度が限度である。また、データの書き込み時と消去時にEEPROMに印加される電圧の絶対値が、20V前後と高い。よって、データの書き込み時と消去時に消費電力が嵩みやすい。また、上記動作電圧の大きさをカバーするための冗長な回路設計が必要となる。10

#### 【0008】

一方、SRAMは、データを保持するために、常時電源電圧の供給を必要とする。よって、電源電圧が供給されている間は、上述したように、定常状態においても電力を消費するため、高集積化に伴いSRAMを用いたプログラム素子の数が増加すると、半導体装置の消費電力が嵩んでしまう。

#### 【0009】

上述の課題に鑑み、本発明は、消費電力を抑えることができる半導体装置の提供を、目的の一とする。また、本発明は、信頼性の高いプログラム素子を用いた半導体装置の提供を、目的の一とする。20

#### 【課題を解決するための手段】

#### 【0010】

本発明の一態様に係る半導体装置では、基本ブロック間の接続構造を変更するのに合わせて、基本ブロックへの電源電圧の供給の有無も変更する。すなわち、基本ブロック間の接続構造を変更することで回路構成に寄与しない基本ブロックが生じた場合に、当該基本ブロックへの電源電圧の供給を停止することを特徴とする。

#### 【0011】

また、本発明の一態様では、基本ブロックへの電源電圧の供給を、オフ電流またはリーク電流が極めて低い絶縁ゲート電界効果型トランジスタ（以下、単にトランジスタとする）を用いたプログラム素子によって、制御することを特徴とする。上記トランジスタは、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含むことを特徴とするものである。上述したような特性を有する半導体材料をチャネル形成領域に含むことで、オフ電流が極めて低いトランジスタを実現することができる。このような半導体材料としては、例えば、シリコンの約3倍程度の大きなバンドギャップを有する、酸化物半導体が挙げられる。30

#### 【0012】

また、本発明の一態様では、基本ブロック間の接続を制御するためのプログラム素子に、上述したオフ電流またはリーク電流が極めて低いトランジスタを用いる。40

#### 【0013】

なお、特に断りがない限り、本明細書では、オフ電流とは、nチャネル型トランジスタにおいては、ドレイン電極をソース電極とゲート電極よりも高い電位とした状態において、ソース電極の電位を基準としたときのゲート電極の電位が0以下であるときに、ソース電極とドレイン電極の間に流れる電流のことを意味する。或いは、本明細書でオフ電流とは、pチャネル型トランジスタにおいては、ドレイン電極をソース電極とゲート電極よりも低い電位とした状態において、ソース電極の電位を基準としたときのゲート電極の電位が0以上であるときに、ソース電極とドレイン電極の間に流れる電流のことを意味する。

#### 【0014】

具体的に、上記プログラム素子は、2つのノード間の接続を制御するためのスイッチング50

素子として機能する第1のトランジスタと、上記第1のトランジスタが有するゲート電極への、電位の供給を制御するための第2のトランジスタとを、少なくとも有する。そして、第2のトランジスタは、シリコンの約3倍程度の大きなバンドギャップを有する酸化物半導体などの半導体材料をチャネル形成領域に有しており、オフ電流またはリーク電流が極めて低いことを特徴とする。よって、第1のトランジスタのゲート電極とソース電極間の電圧（ゲート電圧）は、オフ電流またはリーク電流が極めて低い第2のトランジスタによって、長期間に渡り保持される。

#### 【0015】

なお、酸化物半導体は、微結晶シリコンまたは多結晶シリコンによって得られるのと同程度の高い移動度と、非晶質シリコンによって得られるのと同程度の均一な素子特性とを兼ね備えた、半導体特性を示す金属酸化物である。そして、電子供与体（ドナー）となる水分または水素などの不純物が低減されて高純度化された酸化物半導体（purified OS）は、i型（真性半導体）又はi型に限りなく近い。そのため、上記酸化物半導体を用いたトランジスタは、オフ電流またはリーク電流が著しく低いという特性を有する。

具体的に、高純度化された酸化物半導体は、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectrometry）による水素濃度の測定値が、 $5 \times 10^{-9} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{-8} / \text{cm}^3$ 以下、より好ましくは $5 \times 10^{-7} / \text{cm}^3$ 以下、さらに好ましくは $1 \times 10^{-6} / \text{cm}^3$ 以下とする。また、ホール効果測定により測定できる酸化物半導体膜のキャリア密度は、 $1 \times 10^{14} / \text{cm}^3$ 未満、好ましくは $1 \times 10^{12} / \text{cm}^3$ 未満、さらに好ましくは $1 \times 10^{11} / \text{cm}^3$ 未満とする。また、酸化物半導体のバンドギャップは、2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。水分または水素などの不純物濃度が十分に低減されて高純度化された酸化物半導体膜を用いることにより、トランジスタのオフ電流、リーク電流を低くすることができる。

#### 【0016】

ここで、酸化物半導体膜中の、水素濃度の分析について触れておく。SIMSは、その原理上、試料表面近傍や、材質が異なる膜との積層界面近傍のデータを正確に得ることが困難であることが知られている。そこで、膜中における水素濃度の厚さ方向の分布をSIMSで分析する場合、対象となる膜が存在する範囲において、値に極端な変動が無く、ほぼ一定の値が得られる領域における平均値を、水素濃度として採用する。また、測定の対象となる膜の厚さが小さい場合、隣接する膜内の水素濃度の影響を受けて、ほぼ一定の値が得られる領域を見いだせない場合がある。この場合、当該膜が存在する領域における、水素濃度の極大値または極小値を、当該膜中の水素濃度として採用する。さらに、当該膜の存在する領域において、極大値を有する山型のピーク、極小値を有する谷型のピークが存在しない場合、変曲点の値を水素濃度として採用する。

#### 【0017】

具体的に、高純度化された酸化物半導体膜を活性層として用いたトランジスタのオフ電流が低いことは、いろいろな実験により証明できる。例えば、チャネル幅が $1 \times 10^6 \mu\text{m}$ でチャネル長が $10 \mu\text{m}$ の素子であっても、ソース電極とドレイン電極間の電圧（ドレン電圧）が1Vから10Vの範囲において、オフ電流（ゲート電極とソース電極間の電圧を0V以下としたときのドレン電流）が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13} \text{ A}$ 以下という特性を得ることができる。この場合、オフ電流をトランジスタのチャネル幅で除した数値に相当するオフ電流密度は、 $100 \text{ zA} / \mu\text{m}$ 以下であることが分かる。また、容量素子とトランジスタ（ゲート絶縁膜の厚さは $100 \text{ nm}$ ）とを接続して、容量素子に流入または流出する電荷を当該トランジスタで制御する回路を用いた実験において、当該トランジスタとして高純度化された酸化物半導体膜をチャネル形成領域に用いた場合、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定したところ、トランジスタのソース電極とドレン電極間の電圧が3Vの場合に、 $10 \text{ zA} / \mu\text{m}$ 乃至 $100 \text{ zA} / \mu\text{m}$ という、さらに低いオフ電流が得られることが分かった。したがって、本発明の一態様に係る半導体装置では、高純度化され

10

20

30

40

50

た酸化物半導体膜を活性層として用いたトランジスタのオフ電流密度を、ソース電極とドレイン電極間の電圧によっては、 $100 \text{ zA} / \mu\text{m}$ 以下、好ましくは $10 \text{ zA} / \mu\text{m}$ 以下、更に好ましくは $1 \text{ zA} / \mu\text{m}$ 以下にすることができる。従って、高純度化された酸化物半導体膜を活性層として用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく低い。

#### 【0018】

また、高純度化された酸化物半導体を用いたトランジスタは、オフ電流の温度依存性がほとんど現れない。これは、酸化物半導体中で電子供与体（ドナー）となる不純物を除去して、酸化物半導体が高純度化することによって、導電型が限りなく真性型に近づき、フェルミ準位が禁制帯の中央に位置するためと言える。また、これは、酸化物半導体のエネルギーギャップが $3 \text{ eV}$ 以上であり、熱励起キャリアが極めて少ないとても起因する。また、ソース電極及びドレイン電極が縮退した状態にあることも、温度依存性が現れない要因となっている。トランジスタの動作は、縮退したソース電極から酸化物半導体に注入されたキャリアによるものがほとんどであり、キャリア密度には温度依存性がないことから、オフ電流の温度依存性がみられないことを説明することができる。

#### 【0019】

なお、酸化物半導体は、四元系金属酸化物である $\text{In-Sn-Ga-Zn-O}$ 系酸化物半導体や、三元系金属酸化物である $\text{In-Ga-Zn-O}$ 系酸化物半導体、 $\text{In-Sn-Zn-O}$ 系酸化物半導体、 $\text{In-Al-Zn-O}$ 系酸化物半導体、 $\text{Sn-Ga-Zn-O}$ 系酸化物半導体、 $\text{Al-Ga-Zn-O}$ 系酸化物半導体、 $\text{Sn-Al-Zn-O}$ 系酸化物半導体や、二元系金属酸化物である $\text{In-Zn-O}$ 系酸化物半導体、 $\text{Sn-Zn-O}$ 系酸化物半導体、 $\text{Al-Zn-O}$ 系酸化物半導体、 $\text{Zn-Mg-O}$ 系酸化物半導体、 $\text{Sn-Mg-O}$ 系酸化物半導体、 $\text{In-Mg-O}$ 系酸化物半導体、 $\text{In-Ga-O}$ 系酸化物半導体や、 $\text{In-O}$ 系酸化物半導体、 $\text{Sn-O}$ 系酸化物半導体、 $\text{Zn-O}$ 系酸化物半導体などを用いることができる。なお、本明細書においては、例えば、 $\text{In-Sn-Ga-Zn-O}$ 系酸化物半導体とは、インジウム（ $\text{In}$ ）、錫（ $\text{Sn}$ ）、ガリウム（ $\text{Ga}$ ）、亜鉛（ $\text{Zn}$ ）を有する金属酸化物、という意味であり、その化学量論的組成比は特に問わない。また、上記酸化物半導体は、珪素を含んでいてもよい。

#### 【0020】

或いは、酸化物半導体は、化学式 $\text{InMO}_3(\text{ZnO})_m (m > 0)$ で表記することができる。ここで、Mは、 $\text{Ga}$ 、 $\text{Al}$ 、 $\text{Mn}$ および $\text{Co}$ から選ばれた一または複数の金属元素を示す。

#### 【発明の効果】

#### 【0021】

本発明の一態様では、回路構成に寄与しない基本ブロックへの電源電圧の供給を、プログラム素子により停止することで、半導体集積回路の消費電力を低く抑えることができる。

#### 【0022】

また、上記構成を有するプログラム素子は、トンネル電流によるゲート絶縁膜の劣化を、従来のEEPROMを用いたプログラム素子に比べて抑えることができるので、データの書き換え回数を増やすことができる半導体装置を提供することができる。

#### 【0023】

また、上記構成を有するプログラム素子は、接続状態のデータの書き込みに必要な動作電圧が、第2のトランジスタの動作電圧によりほぼ決まる。よって、従来のEEPROMを用いたプログラム素子に比べて、上記動作電圧を格段に低くすることができ、消費電力を抑えられる半導体装置を提供することができる。

#### 【0024】

また、上記構成を有するプログラム素子は、SRAMを用いたプログラム素子と異なり、オフ電流の著しく低いトランジスタを用いてデータの保持を行っているため、プログラム素子への電源電圧の供給を常時行わなくとも、接続状態をある程度維持することが可能である。そのため、消費電力を抑えられる半導体装置を提供することができる。

10

20

30

40

50

## 【図面の簡単な説明】

## 【0025】

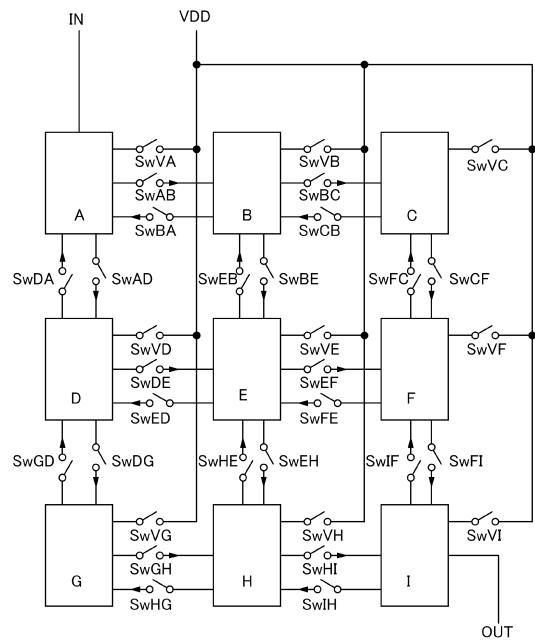

【図1】半導体装置の構成を示す図。

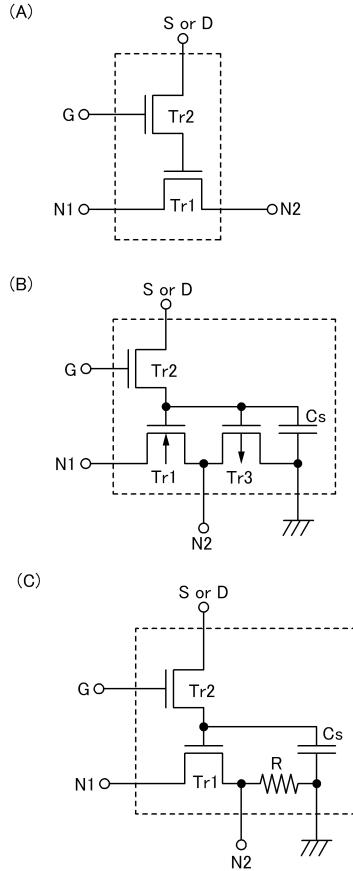

【図2】プログラム素子の回路図。

【図3】半導体装置の動作を示す図。

【図4】半導体装置の動作を示す図。

【図5】半導体装置の動作を示す図。

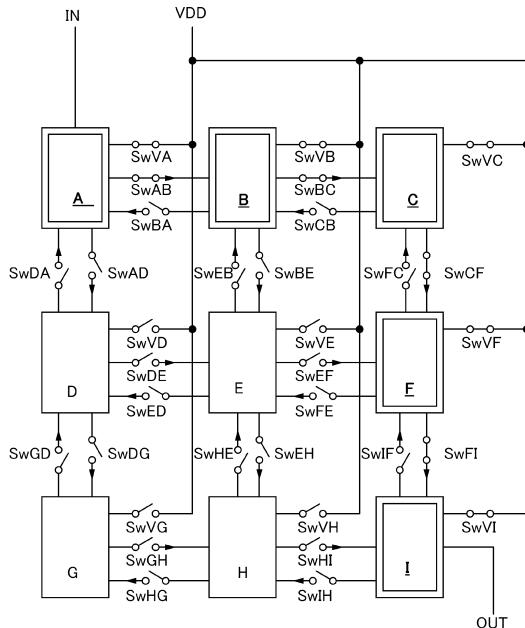

【図6】半導体装置の構成を示す図。

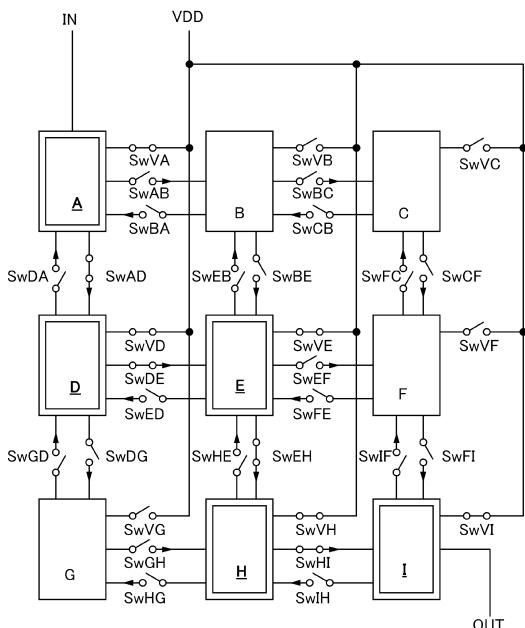

【図7】半導体装置の構成を示す図。

【図8】半導体装置の構成を示す図。

【図9】半導体装置の動作を示すタイミングチャート。

【図10】半導体装置の作製方法を示す図。

【図11】半導体装置の作製方法を示す図。

【図12】半導体装置の作製方法を示す図。

【図13】酸化物半導体を用いた逆スタガ型のトランジスタの縦断面図。

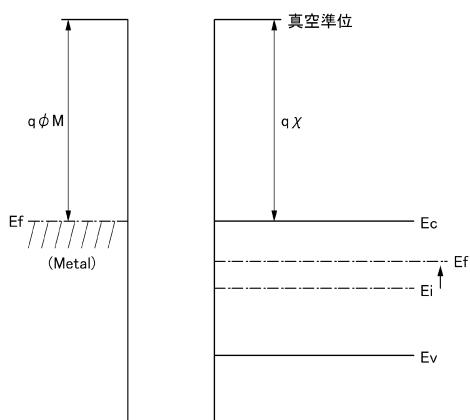

【図14】図13に示すA-A'断面におけるエネルギー・バンド図(模式図)。

【図15】(A)ゲート電極(GE)に正の電圧( $V_G > 0$ )が印加された状態を示し、(B)ゲート電極(GE)に負の電圧( $V_G < 0$ )が印加された状態を示す図。

【図16】真空準位と金属の仕事関数( $\phi_M$ )、酸化物半導体の電子親和力( $\phi_A$ )の関係を示す図。

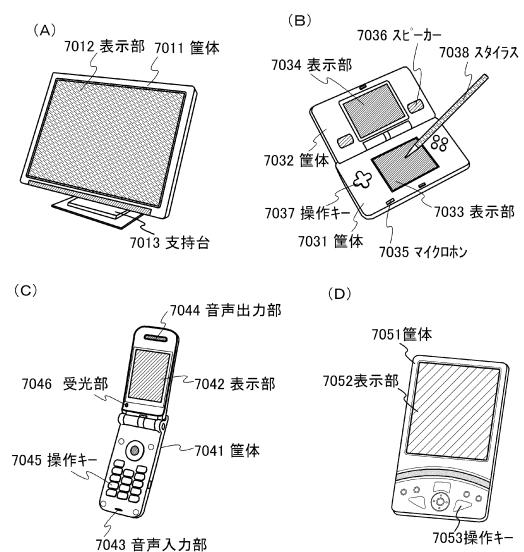

【図17】電子機器の構成を示す図。

## 【発明を実施するための形態】

## 【0026】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

## 【0027】

なお、本発明の半導体装置は、マイクロプロセッサ、画像処理回路、半導体表示装置用のコントローラ、DSP(Digital Signal Processor)、マイクロコントローラなどの、半導体素子を用いた各種半導体集積回路をその範疇に含む。また、本発明の半導体装置は、上記半導体集積回路を用いたRFタグ、半導体表示装置などの各種装置も、その範疇に含む。半導体表示装置には、液晶表示装置、有機発光素子(OLED)に代表される発光素子を各画素に備えた発光装置、電子ペーパー、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)等や、半導体素子を駆動回路に有している他の半導体表示装置が、その範疇に含まれる。

## 【0028】

## (実施の形態1)

本実施の形態では、本発明の一態様に係る半導体装置の構成と、その動作について説明する。

## 【0029】

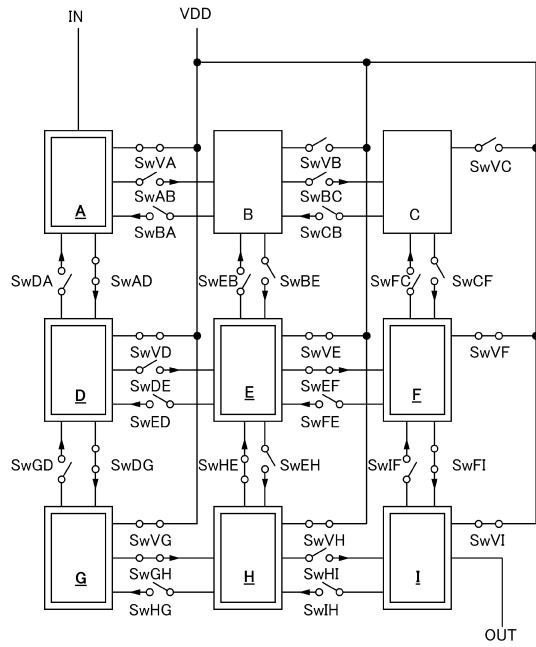

図1に、本発明の一態様に係る半導体装置の構成を、一例として示す。図1に示す半導体装置は、9つの基本ブロックA乃至基本ブロックIと、それら基本ブロックA乃至基本ブロックI間の接続を制御するプログラム素子SwAB乃至プログラム素子SwIHと、各基本ブロックA乃至基本ブロックIへの、電源電位VDDの供給を制御するプログラム素子SwVA乃至プログラム素子SwVIとが設けられている。

## 【0030】

なお、図1では、例えば基本ブロックAの出力端子と基本ブロックBの入力端子の接続を制御するプログラム素子を、SwABと表記する。逆に、基本ブロックBの出力端子と基

10

20

30

40

50

本ブロック A の入力端子の接続を制御するプログラム素子を、 S w B A と表記する。

**【 0 0 3 1 】**

また、図 1 では、説明の煩雑さを避けるために、 9 つの各基本ブロックが左右上下のいずれかの基本ブロックと、プログラム素子を介して接続される場合を例示している。しかし、本発明はこの構成に限定されず、基本ブロックの数とその接続構造は、設計者が適宜定めることができる。

**【 0 0 3 2 】**

また、図 1 では、各基本ブロックが、プログラム素子を介して、電源電位 V D D の与えられているノードと接続されている構成を示しているが、実際には、各基本ブロックは、電源電位 V D D の他に、電源電位 V D D と電位差を有するグラウンドなどの固定電位が与えられている。すなわち、基本ブロックに電源電位 V D D が与えられることで、電源電位 V D D と上記固定電位の電位差が、電源電圧として当該基本ブロックに供給されることとなる。

10

**【 0 0 3 3 】**

また、図 1 では、任意の基本ブロックが有する一の出力端子が、他の基本ブロックが有する一の入力端子に、それぞれプログラム素子を介して接続されている場合を例示している。しかし、本発明はこの構成に限定されず、任意の基本ブロックが有する一の出力端子が、他の基本ブロックが有する複数の入力端子に、それぞれプログラム素子を介して接続されていても良い。

**【 0 0 3 4 】**

20

なお、基本ブロックとして用いる論理回路の構成は、特に限定されない。インバータ、 AND、 NAND、 NOR のような、単純な論理演算を行う論理回路から、加算器、乗算器、メモリ( 例えは、DRAM や SRAM 等 ) 、さらには各種演算装置を、基本ブロックとして用いることができる。

**【 0 0 3 5 】**

また、各プログラム素子は、 2 つのノード間の接続を制御する第 1 のトランジスタ ( T r 1 ) と、当該第 1 のトランジスタが有するゲート電極への、電位の供給を制御する第 2 のトランジスタ ( T r 2 ) とを、少なくとも有している。図 2 に、プログラム素子の構成例を具体的に示す。

**【 0 0 3 6 】**

30

図 2 ( A ) は、最も単純な構造を有するプログラム素子の一例であり、 2 つのノード間の接続を制御する第 1 のトランジスタ ( T r 1 ) と、当該第 1 のトランジスタ ( T r 1 ) が有するゲート電極への、電位の供給を制御する第 2 のトランジスタ ( T r 2 ) とを有する。具体的に、第 1 のトランジスタ ( T r 1 ) が有するソース電極はノード N 1 に、ドレイン電極はノード N 2 に接続されている。そして、第 2 のトランジスタ ( T r 2 ) のソース電極 ( S で示す ) とドレイン電極 ( D で示す ) は、いずれか一方が第 1 のトランジスタ ( T r 1 ) のゲート電極に接続されており、他方には第 1 のトランジスタ ( T r 1 ) のスイッチングを制御するための信号 ( S i g 1 ) の電位が与えられている。

**【 0 0 3 7 】**

なお、第 1 のトランジスタ ( T r 1 ) が有するゲート電極の電位を保持するための容量素子を設けるようにしても良い。

40

**【 0 0 3 8 】**

第 2 のトランジスタ ( T r 2 ) が、そのゲート電極に入力される信号に従ってオンになると、第 1 のトランジスタ ( T r 1 ) のスイッチングを制御するための信号の電位が、第 1 のトランジスタ ( T r 1 ) のゲート電極に与えられる。第 1 のトランジスタ ( T r 1 ) は、そのゲート電極に与えられた電位に従ってスイッチングを行う。第 1 のトランジスタ ( T r 1 ) がオンだと、ノード N 1 とノード N 2 が接続される。逆に、第 1 のトランジスタ ( T r 1 ) がオフだと、ノード N 1 とノード N 2 は接続されず、これらのノードのいずれか一方は、ハイインピーダンスの状態となる。

**【 0 0 3 9 】**

50

次いで、第2のトランジスタ( $T_{r2}$ )が、そのゲート電極に入力される信号に従ってオフになると、第1のトランジスタ( $T_{r1}$ )が有するゲート電極はフローティングの状態となり、その電位が保持される。よって、ノードN1とノードN2の間の接続状態は、保持される。

#### 【0040】

なお、本明細書において接続とは電気的な接続を意味しており、電流、電圧または電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧または電位が、供給可能、或いは伝送可能であるように、配線、抵抗、ダイオード、トランジスタなどの回路素子を介して間接的に接続している状態も、その範疇に含む。

10

#### 【0041】

また、回路図上は独立している構成要素どうしが接続されている場合であっても、実際には、例えば配線の一部が電極としても機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っているだけの場合もある。本明細書において接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

#### 【0042】

また、トランジスタが有するソース電極とドレイン電極は、トランジスタの極性及び各電極に与えられる電位の高低差によって、その呼び方が入れ替わる。一般的に、nチャネル型トランジスタでは、低い電位が与えられる電極がソース電極と呼ばれ、高い電位が与えられる電極がドレイン電極と呼ばれる。また、pチャネル型トランジスタでは、低い電位が与えられる電極がドレイン電極と呼ばれ、高い電位が与えられる電極がソース電極と呼ばれる。本明細書では、便宜上、ソース電極とドレイン電極が固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソース電極とドレイン電極の呼び方が入れ替わる。

20

#### 【0043】

なお、基本ブロック間の接続を制御するプログラム素子の場合、ノードN1とノードN2は、それぞれ互いに異なる基本ブロックの入力端子または出力端子に接続されている。また、基本ブロックへの電源電圧の供給を制御するプログラム素子の場合、ノードN1とノードN2は、一方が基本ブロックに接続されており、他方には電源電位VDDが与えられている。

30

#### 【0044】

次いで、図2(B)に、プログラム素子の別の一例を示す。図2(B)に示すプログラム素子は、2つのノード間の接続を制御する第1のトランジスタ( $T_{r1}$ )と、当該第1のトランジスタ( $T_{r1}$ )が有するゲート電極への、電位の供給を制御する第2のトランジスタ( $T_{r2}$ )と、上記2つのノードのいずれか一つと、固定電位VSSが与えられているノードとの間の接続を制御する第3のトランジスタ( $T_{r3}$ )とを有する。

#### 【0045】

具体的に、第1のトランジスタ( $T_{r1}$ )が有するソース電極はノードN1に、ドレイン電極はノードN2に接続されている。そして、第2のトランジスタ( $T_{r2}$ )のソース電極とドレイン電極は、いずれか一方が第1のトランジスタ( $T_{r1}$ )のゲート電極に接続されており、他方には第1のトランジスタ( $T_{r1}$ )のスイッチングを制御するための信号の電位が与えられている。また、第3のトランジスタ( $T_{r3}$ )が有するソース電極とドレイン電極は、一方がノードN2に接続されており、他方が固定電位VSSの与えられているノードに接続されている。そして、第1のトランジスタ( $T_{r1}$ )のゲート電極と、第3のトランジスタ( $T_{r3}$ )のゲート電極とが接続されている。なお、第1のトランジスタ( $T_{r1}$ )はnチャネル型トランジスタであり、第3のトランジスタ( $T_{r3}$ )はpチャネル型トランジスタである。

40

#### 【0046】

また、図2(B)に示すプログラム素子は、第1のトランジスタ( $T_{r1}$ )が有するゲート電極の電位を保持するための容量素子Csを有している。容量素子Csは必ずしも設け

50

る必要はないが、容量素子 C<sub>s</sub> を設けることで、ノード N<sub>1</sub> とノード N<sub>2</sub> 間の接続状態を、より長い期間に渡って保持することができる。具体的に、容量素子 C<sub>s</sub> が有する一対の電極は、一方が第 1 のトランジスタ (Tr<sub>1</sub>) のゲート電極に接続されており、他方が固定電位 V<sub>SS</sub> の与えられているノードに接続されている。

#### 【0047】

第 2 のトランジスタ (Tr<sub>2</sub>) が、そのゲート電極に入力される信号に従ってオンになると、第 1 のトランジスタ (Tr<sub>1</sub>) のスイッチングを制御するための信号の電位が、第 1 のトランジスタ (Tr<sub>1</sub>) のゲート電極と、第 3 のトランジスタ (Tr<sub>3</sub>) のゲート電極と、容量素子 C<sub>s</sub> の一方の電極に与えられる。第 1 のトランジスタ (Tr<sub>1</sub>) は、そのゲート電極に与えられた信号の電位に従ってスイッチングを行う。そして、第 3 のトランジスタ (Tr<sub>3</sub>) は、第 1 のトランジスタ (Tr<sub>1</sub>) と極性が異なるので、第 1 のトランジスタ (Tr<sub>1</sub>) と逆のスイッチングを行う。10

#### 【0048】

例えば、第 1 のトランジスタ (Tr<sub>1</sub>) がオンになると、第 3 のトランジスタ (Tr<sub>3</sub>) はオフとなる。その結果、ノード N<sub>1</sub> とノード N<sub>2</sub> が接続される。逆に、第 1 のトランジスタ (Tr<sub>1</sub>) がオフになると、第 3 のトランジスタ (Tr<sub>3</sub>) はオンとなる。その結果、ノード N<sub>1</sub> とノード N<sub>2</sub> は接続されず、ノード N<sub>2</sub> が、固定電位 V<sub>SS</sub> の与えられているノードに接続される。

#### 【0049】

次いで、第 2 のトランジスタ (Tr<sub>2</sub>) が、そのゲート電極に入力される信号に従ってオフになると、第 1 のトランジスタ (Tr<sub>1</sub>) が有するゲート電極と、第 3 のトランジスタ (Tr<sub>3</sub>) が有するゲート電極はフロー・ティングの状態となり、その電位が容量 C<sub>s</sub> により保持される。よって、ノード N<sub>1</sub> とノード N<sub>2</sub> の間と、ノード N<sub>2</sub> と固定電位 V<sub>SS</sub> の与えられているノードの間の接続状態は、保持される。20

#### 【0050】

なお、図 2 (B) では、第 3 のトランジスタ (Tr<sub>3</sub>) に、p チャネル型トランジスタを用いたが、酸化物半導体のように一般的に p チャネル型が得られない、あるいは、得られたとしても移動度が非常に低い場合には、図 2 (C) で示すように、p チャネル型トランジスタの代わりに抵抗 R を用いることもできる。

#### 【0051】

そして、本発明の一態様では、図 2 (A) 乃至図 2 (C) に例示したプログラム素子において、第 2 のトランジスタ (Tr<sub>2</sub>) のオフ電流またはリーク電流が極めて低いことを特徴とする。具体的に、第 2 のトランジスタ (Tr<sub>2</sub>) は、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含むことを特徴とするものである。上述したような特性を有する半導体材料をチャネル形成領域に含むことで、オフ電流が極めて低いトランジスタを実現することができる。30

#### 【0052】

シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料の一例として、炭化珪素 (SiC)、窒化ガリウム (GaN) などの化合物半導体、酸化亜鉛 (ZnO) などの金属酸化物である酸化物半導体などを適用することができる。この中でも酸化物半導体は、スパッタリング法や湿式法（印刷法など）により作製可能であり、量産性に優れるといった利点がある。また、炭化珪素や窒化ガリウムは単結晶としなければ十分な特性が得られず、そのための炭化珪素のプロセス温度は約 1500 、窒化ガリウムのプロセス温度は約 1100 であるが、酸化物半導体の成膜温度は、300 ~ 500 （最大でも 700 程度）と低く、単結晶シリコン等の半導体材料を用いた集積回路上に、酸化物半導体による半導体素子を積層させることも可能である。また、基板の大型化にも対応が可能である。よって、上述したワイドギャップ半導体の中でも、特に酸化物半導体は量産性が高いというメリットを有する。また、より優れた性能（例えば電界効果移動度）を有する結晶性の酸化物半導体も、450 から 800 の熱処理によって容易に得ることができる。4050

## 【0053】

酸化物半導体を第2のトランジスタ( $T_{r2}$ )に用いる場合、上記酸化物半導体は、バ

ンドギャップが3eV以上でかつ、キャリア密度が $10^{12} / \text{cm}^3$ 未満、好ましくは $10^{11} / \text{cm}^3$ 未満の特性を有することが望ましい。また、上記酸化物半導体は、SIMSによる水素濃度の測定値が、 $5 \times 10^{19} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{18} / \text{cm}^3$ 以下、より好ましくは $5 \times 10^{17} / \text{cm}^3$ 以下、さらに好ましくは $1 \times 10^{16} / \text{cm}^3$ 以下であることが望ましい。上記特性を有する酸化物半導体を用いることで、第2のトランジスタ( $T_{r2}$ )のオフ電流、リーク電流を低くすることができる。

## 【0054】

また、第2のトランジスタ( $T_{r2}$ )は、ゲート絶縁膜の厚さが、 $10 \text{ nm}$ 以上、好ましくは、 $100 \text{ nm}$ 以上とするのが望ましく、また、チャネル長を $100 \text{ nm}$ 以上、好ましくは $300 \text{ nm}$ 以上とするのが望ましい。上記構造を採用することで、第2のトランジスタ( $T_{r2}$ )のオフ電流、リーク電流を低くすることができる。

10

## 【0055】

このように、オフ電流、リーク電流の著しく低い第2のトランジスタ( $T_{r2}$ )を用いて、第1のトランジスタが有するゲート電極への電位の供給を制御することで、第1のトランジスタのゲート電圧は、長期間に渡って保持される。従って、ノードN1とノードN2の間の接続状態も、長期間に渡り保持することができる。

## 【0056】

なお、接続状態を保持する際ににおいて、第2のトランジスタ( $T_{r2}$ )のオフ電流、リーク電流をさらに低減させるには、第2のトランジスタ( $T_{r2}$ )が有するゲート電極の電位を、プログラム素子の中で最も低くなるように設定すればよい。具体的には、トランジスタ、容量素子、抵抗などの、プログラム素子を構成する全ての回路素子が有する電極や端子の電位のうち、第2のトランジスタ( $T_{r2}$ )が有するゲート電極の電位が、他の全ての電位よりも $3 \text{ V}$ 以上、より好ましくは $5 \text{ V}$ 以上低くなるように設定するのが望ましい。

20

## 【0057】

また、第1のトランジスタ( $T_{r1}$ )または第3のトランジスタ( $T_{r3}$ )は、第2のトランジスタ( $T_{r2}$ )と同様に、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料をチャネル形成領域に有していても良いし、第2のトランジスタ( $T_{r2}$ )とは異なり、移動度のより高い半導体材料をチャネル形成領域に有していても良い。移動度の高い半導体材料として、例えば、多結晶や単結晶などの結晶性を有するゲルマニウム、シリコン、シリコングルマニウムや、単結晶炭化珪素などが適している。また、第1のトランジスタ( $T_{r1}$ )または第3のトランジスタ( $T_{r3}$ )は、薄膜の半導体膜を用いていても良いし、バルクの半導体基板を用いていても良い。

30

## 【0058】

前者の場合、第1のトランジスタ( $T_{r1}$ )または第3のトランジスタ( $T_{r3}$ )も第2のトランジスタ( $T_{r2}$ )と同様に、オフ電流、リーク電流が低いという特性を有することになるので、半導体装置の消費電力をさらに削減することができる。特に、基本ブロックへの電源電位VDDの供給を制御するプログラム素子の場合、第1のトランジスタ( $T_{r1}$ )の電界効果移動度が $10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ 程度であれば十分動作が可能であり、さほど高い動作速度は要求されない。そして、基本ブロックへの電源電位VDDの供給を制御するプログラム素子において生じるオフ電流、リーク電流は、消費電力の増大にそのまま繋がってしまう。そのため、基本ブロックへの電源電位VDDの供給を制御するプログラム素子の場合は、前者の構成を採用することが望ましい。

40

## 【0059】

また、後者の場合、第1のトランジスタ( $T_{r1}$ )の移動度が高くなるので、第1のトランジスタ( $T_{r1}$ )によって接続されるノード間の抵抗を低くすることができる。特に、基本ブロック間の接続を制御するためのプログラム素子の場合、基本ブロックどうしの接続抵抗が高いことは、半導体装置の動作速度の低減につながる。そのため、基本ブロック

50

間の接続を制御するためのプログラム素子の場合は、後者の構成を採用することが望ましい。なお、第1のトランジスタ( $T_{r1}$ )が移動度のより高い半導体材料をチャネル形成領域に有している場合において、オフ電流、リーク電流を低減させるには、そのゲート絶縁膜の厚さを10nm以上とすることが好ましい。

#### 【0060】

なお、第2のトランジスタ( $T_{r2}$ )と、第1のトランジスタ( $T_{r1}$ )及び第3のトランジスタ( $T_{r3}$ )とが、同じ半導体材料をチャネル形成領域に有している場合、第1のトランジスタ( $T_{r1}$ )及び第3のトランジスタ( $T_{r3}$ )を第2のトランジスタ( $T_{r2}$ )と同じ層内に形成してもよい。この場合、第1のトランジスタ( $T_{r1}$ )及び第3のトランジスタ( $T_{r3}$ )と、第2のトランジスタ( $T_{r2}$ )とは、ゲート絶縁膜の膜厚が設計上同じとなるが、チャネル長、またはチャネル幅は、異ならせておいても良い。例えば、第1のトランジスタ( $T_{r1}$ )のチャネル形成領域を低抵抗にしたい場合、そのチャネル幅を、第2のトランジスタ( $T_{r2}$ )の2倍以上、好ましくは5倍以上とすると良い。

10

#### 【0061】

さらに、第1のトランジスタ( $T_{r1}$ )は、ノンセルフアライン方式で作製してもよい。ノンセルフアライン方式では、ゲート電極と、ソース電極またはドレイン電極とのオーバーラップによる寄生容量が生じるが、第1のトランジスタ( $T_{r1}$ )は高速動作をさほど要求されないので、上記寄生容量は問題とならない。むしろ、上記寄生容量は、第1のトランジスタ( $T_{r1}$ )のゲート電極の電位を保持する容量( $C_s$ )として機能する。他方、第2のトランジスタ( $T_{r2}$ )は、スイッチングの際に第1のトランジスタ( $T_{r1}$ )のゲート電極に電位の変化が発生するのを防ぐために、その寄生容量は小さいことが好ましい。

20

#### 【0062】

また、第1のトランジスタ( $T_{r1}$ )に、基本ブロックを構成するトランジスタと同じ半導体材料を用いる場合であっても、第1のトランジスタ( $T_{r1}$ )のリーク電流を低減するために、そのゲート絶縁膜の膜厚は、基本ブロックを構成するトランジスタよりも大きいことが望ましい。この場合、第1のトランジスタ( $T_{r1}$ )は、上述したノンセルフアライン方式で作製し、基本ブロックに用いられるトランジスタとは異なる層に形成された導電膜を、そのゲート電極として用いても良い。

30

#### 【0063】

なお、図2では、第1のトランジスタ( $T_{r1}$ )、第2のトランジスタ( $T_{r2}$ )、第3のトランジスタ( $T_{r3}$ )が、ゲート電極を半導体膜の片側にのみ有している場合を示している。しかし、本発明の一態様はこの構成に限定されず、上記トランジスタが、半導体膜を間に挟んでゲート電極の反対側に存在するバックゲート電極を有していても良い。この場合、バックゲート電極は、電気的に絶縁しているフローティングの状態であっても良いし、電位が他から与えられている状態であっても良い。後者の場合、ゲート電極とバックゲート電極が電気的に接続されていても良いし、バックゲート電極にのみ、常にグラウンドなどの固定電位が与えられていても良い。バックゲート電極に与える電位の高さを制御することで、トランジスタの閾値電圧を制御することができる。

40

#### 【0064】

また、半導体装置に用いることができるプログラム素子は、図2に示した回路構成に限定されず、少なくとも、2つのノード間の接続を制御するための第1のトランジスタと、上記第1のトランジスタが有するゲート電極への、電位の供給を制御するための第2のトランジスタとを有し、なおかつ、第2のトランジスタが、シリコンの約3倍程度の大きなバンドギャップを有する酸化物半導体などの半導体材料をチャネル形成領域に有していれば良い。

#### 【0065】

次いで、上述した構成を有するプログラム素子を用いて、複数の基本ブロックを任意に接続する場合の、半導体装置の動作について説明する。

50

**【 0 0 6 6 】**

図1に示す半導体装置では、全ての基本ブロック間の接続が切断され、また、全ての基本ブロックへの電源電圧の供給が停止している状態である。この図1に示す状態から、プログラム素子の幾つかをオンとして、基本ブロック間が接続された状態を、図3に示す。具体的に、図3では、プログラム素子S w A B、プログラム素子S w B C、プログラム素子S w C F、プログラム素子S w F Iがオンになることで、基本ブロックAの出力端子と基本ブロックBの入力端子が接続され、基本ブロックBの出力端子と基本ブロックCの入力端子が接続され、基本ブロックCの出力端子と基本ブロックFの入力端子が接続され、基本ブロックFの出力端子と基本ブロックIの入力端子が接続されている。また、プログラム素子S w V A、プログラム素子S w V B、プログラム素子S w V C、プログラム素子S w V F、プログラム素子S w V Iがオンになることで、基本ブロックA、基本ブロックB、基本ブロックC、基本ブロックF、基本ブロックIに、電源電位V D Dが与えられている。そして、上記以外の全てのプログラム素子はオフになっている。この結果、図3に示すように、半導体装置の入力端子(IN)から、基本ブロックA - 基本ブロックB - 基本ブロックC - 基本ブロックF - 基本ブロックIという信号の経路が形成される。そして、上記各基本ブロックにおいて第1の信号処理が行われることにより、出力端子(OUT)から信号が出力される。

**【 0 0 6 7 】**

なお、この図3に示した状態で、入力された信号に第1の信号処理を施して出力信号を得た後に、第2の信号処理を行う場合には、基本ブロック間の接続を変更する。基本ブロック間の接続の変更は、一旦、全てのプログラム素子を切断した後に行なうことが望ましい。

**【 0 0 6 8 】**

第2の信号処理を行う際の、基本ブロック間の接続状態の一例を、図4に示す。具体的に、図4では、プログラム素子S w A D、プログラム素子S w D E、プログラム素子S w E H、プログラム素子S w H Iがオンになることで、基本ブロックAの出力端子と基本ブロックDの入力端子が接続され、基本ブロックDの出力端子と基本ブロックEの入力端子が接続され、基本ブロックEの出力端子と基本ブロックHの入力端子が接続され、基本ブロックHの出力端子と基本ブロックIの入力端子が接続されている。また、プログラム素子S w V A、プログラム素子S w V D、プログラム素子S w V E、プログラム素子S w V H、プログラム素子S w V Iがオンになることで、基本ブロックA、基本ブロックD、基本ブロックE、基本ブロックH、基本ブロックIに、電源電位V D Dが与えられている。そして、上記以外の全てのプログラム素子はオフになっている。この結果、図4に示すように、半導体装置の入力端子(IN)から、基本ブロックA - 基本ブロックD - 基本ブロックE - 基本ブロックH - 基本ブロックIという信号の経路が形成される。そして、上記各基本ブロックにおいて第2の信号処理が行われることにより、出力端子(OUT)から信号が出力される。

**【 0 0 6 9 】**

さらに、第3の信号処理を行う場合も、一旦、全てのプログラム素子を切断した後に、基本ブロック間の接続の変更を行なうことが望ましい。第3の信号処理を行う際の、基本ブロック間の接続状態の一例を、図5に示す。具体的に、図5では、プログラム素子S w A D、プログラム素子S w D G、プログラム素子S w G H、プログラム素子S w H E、プログラム素子S w E F、プログラム素子S w F Iがオンになることで、基本ブロックAの出力端子と基本ブロックDの入力端子が接続され、基本ブロックDの出力端子と基本ブロックGの入力端子が接続され、基本ブロックGの出力端子と基本ブロックHの入力端子が接続され、基本ブロックHの出力端子と基本ブロックEの入力端子が接続され、基本ブロックEの出力端子と基本ブロックFの入力端子が接続され、基本ブロックFの出力端子と基本ブロックIの入力端子が接続されている。また、プログラム素子S w V A、プログラム素子S w V D、プログラム素子S w V G、プログラム素子S w V H、プログラム素子S w V E、プログラム素子S w V F、プログラム素子S w V Iがオンになることで、基本ブロックA、基本ブロックD、基本ブロックE、基本ブロックF、基本ブロックG、基本ブロックIに、電源電位V D Dが与えられる。

クH、基本ブロックIに、電源電位VDDが与えられている。そして、上記以外の全てのプログラム素子はオフになっている。この結果、図5に示すように、半導体装置の入力端子(IN)から、基本ブロックA - 基本ブロックD - 基本ブロックG - 基本ブロックH - 基本ブロックE - 基本ブロックF - 基本ブロックIという信号の経路が形成される。そして、上記各基本ブロックにおいて第3の信号処理が行われることにより、出力端子(OUT)から信号が出力される。

#### 【0070】

なお、コンフィギュレーション処理を行う（プログラム素子のスイッチングを制御することで回路を構築する）のに要する時間は、基本ブロックとプログラム素子で構成されるマトリクスの規模にもよるが、図3に示すような回路構成を用いる限りは無視できる程度の短い時間である。例えば、1行の基本ブロックあたりに要する上記時間は100ナノ秒以下である。図1のような、3行の基本ブロックで構成されるマトリクスであれば、1マイクロ秒もかからない。

10

#### 【0071】

本発明の一態様では、回路構成に寄与しない基本ブロックへの電源電圧の供給を停止することにより、半導体装置の消費電力を低く抑えることができる。特に、チャネル長50nm以下の半導体装置においては、ゲート絶縁膜の厚さが数nm以下となり、消費電力の相当部分をゲート絶縁膜におけるリーク電流が占めるため、上記構成は消費電力低減のために有効である。

20

#### 【0072】

また、本発明の一態様では、基本ブロックどうしの接続を、オフ電流又はリーク電流の極めて低いトランジスタにより制御することで、電源電圧が供給されている基本ブロックと、電源電圧が供給されていない基本ブロックの間に流れるリーク電流またはオフ電流を低減し、半導体装置の消費電力を低く抑えることができる。

#### 【0073】

また、上記構成を有するプログラム素子は、トンネル電流によるゲート絶縁膜の劣化を、従来のEEPROMを用いたプログラム素子に比べて抑えることができるので、データの書き換え回数を増やすことができる半導体装置を提供することができる。

#### 【0074】

また、上記構成を有するプログラム素子は、データの書き込みに必要な動作電圧が、第2のトランジスタ( $T_{r2}$ )の動作電圧によりほぼ決まる。よって、従来のEEPROMを用いたプログラム素子に比べて、上記動作電圧を格段に低くすることができ、消費電力を抑えられる半導体装置を提供することができる。

30

#### 【0075】

また、上記構成を有するプログラム素子は、SRAMを用いたプログラム素子と異なり、プログラム素子への電源電圧の供給を常時行わなくとも、接続状態がある程度維持することができる。また、オフ電流の著しく低いトランジスタを用いてデータの保持を行っている。そのため、消費電力を抑えられる半導体装置を提供することができる。

#### 【0076】

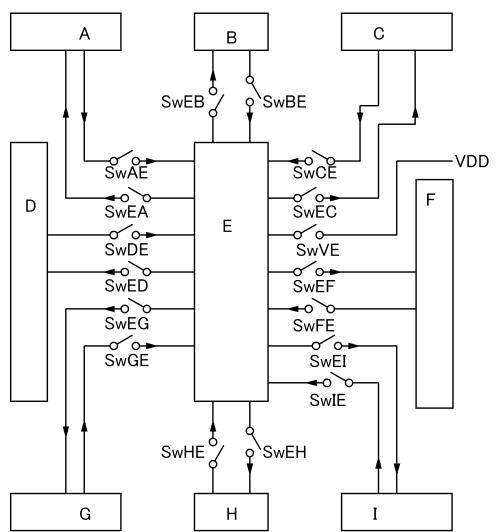

##### (実施の形態2)

40

実施の形態1では、任意の基本ブロックが、多い場合に4つの隣接する基本ブロックと接続できる例を示したが、本実施の形態では、任意の基本ブロックが8つの隣接する基本ブロックと接続する例について説明する。

#### 【0077】

図6に示す半導体装置には、図1と同様に、9つの基本ブロックA乃至基本ブロックIと、それら基本ブロックA乃至基本ブロックI間の接続を制御するプログラム素子と、各基本ブロックA乃至基本ブロックIへの、電源電位VDDの供給を制御するプログラム素子とが設けられている。

#### 【0078】

ただし、図6に示す半導体装置は、図1とは異なり、中央の基本ブロックEと、当該基本

50

ブロック E 以外の全ての基本ブロックとが、プログラム素子 S w A E 乃至プログラム素子 S w I E 、プログラム素子 S w E A 乃至プログラム素子 S w E I により、接続可能である。

#### 【 0 0 7 9 】

なお、図 6 では、中央の基本ブロック E と、その他の基本ブロックの間の接続を制御するプログラム素子 S w A E 乃至プログラム素子 S w I E 、プログラム素子 S w E A 乃至プログラム素子 S w E I と、基本ブロック E への電源電位 V D D の供給を制御するプログラム素子 S w V E のみを示している。しかし、基本ブロック A と基本ブロック B 、基本ブロック B と基本ブロック C 、基本ブロック C と基本ブロック F 、基本ブロック F と基本ブロック I 、基本ブロック I と基本ブロック H 、基本ブロック H と基本ブロック I の間の接続も、図 1 の場合と同様に、プログラム素子により制御することができる。また、基本ブロック A 、基本ブロック B 、基本ブロック C 、基本ブロック D 、基本ブロック F 、基本ブロック G 、基本ブロック H 、基本ブロック I への、電源電位 V D D の供給も、図 1 と同様に、プログラム素子により制御することが可能である。10

#### 【 0 0 8 0 】

なお、プログラム素子は、実施の形態 1 に示した構成を用いることができる。

#### 【 0 0 8 1 】

図 6 に示すように、任意の基本ブロックと接続可能な基本ブロックの数は、設計者が適宜設定することが可能である。20

#### 【 0 0 8 2 】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することができる。

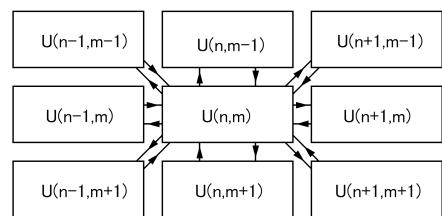

#### 【 0 0 8 3 】

##### ( 実施の形態 3 )

基本ブロックにより大規模なマトリクスが構成されている半導体装置について、より一般化した例を挙げて、説明する。

#### 【 0 0 8 4 】

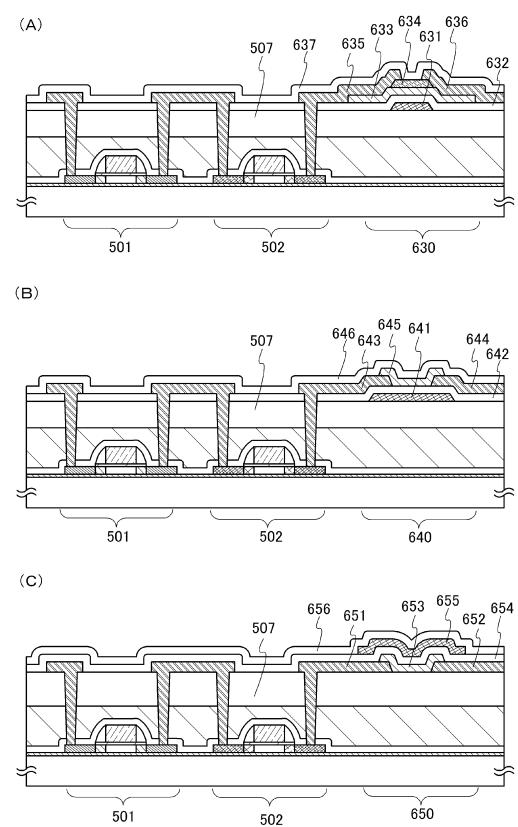

本実施の形態では、半導体装置が有する、第 n 行第 m 列の基本ブロック U ( n , m ) に注目する。図 7 に示すように、基本ブロック U ( n , m ) の周囲には、基本ブロック U ( n - 1 , m - 1 ) 、 U ( n , m - 1 ) 、 U ( n + 1 , m - 1 ) 、 U ( n - 1 , m ) 、 U ( n + 1 , m ) 、 U ( n - 1 , m + 1 ) 、 U ( n , m + 1 ) 、 U ( n + 1 , m + 1 ) という 8 つの基本ブロックが存在している。そして、基本ブロック U ( n , m ) は、これら 8 つの基本ブロックと、プログラム素子を介して、それぞれ信号の授受ができるように接続されている。30

#### 【 0 0 8 5 】

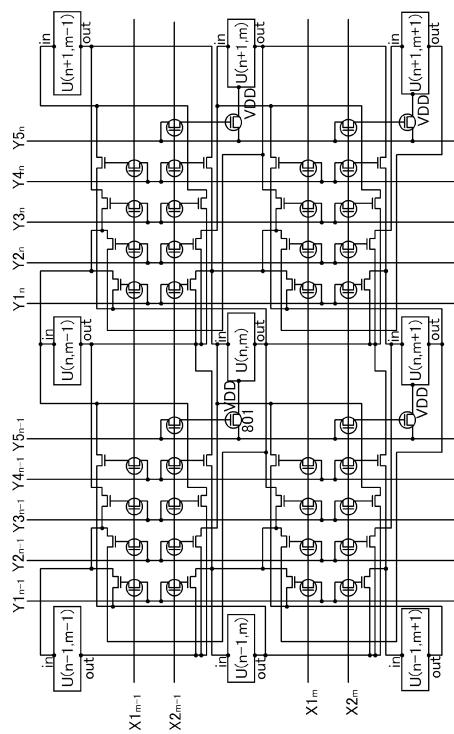

図 8 に、図 7 に示した各基本ブロック間の接続を制御するためのプログラム素子と、各基本ブロックへの電源電位 V D D の供給を制御するためのプログラム素子の、具体的な構成を一例として示す。

#### 【 0 0 8 6 】

なお、図 8 では、図 2 ( A ) で示したプログラム素子を用いた例を示しているが、図 2 ( B ) 、図 2 ( C ) に示したプログラム素子を用いていても良い。また、プログラム素子の構成は図 2 に示した回路構成に限定されず、少なくとも、2 つのノード間の接続を制御するための第 1 のトランジスタと、上記第 1 のトランジスタが有するゲート電極への、電位の供給を制御するための第 2 のトランジスタとを有し、なおかつ、第 2 のトランジスタが、シリコンの約 3 倍程度の大きなバンドギャップを有する酸化物半導体などの半導体材料をチャネル形成領域に有していれば良い。40

#### 【 0 0 8 7 】

また、図 8 では、プログラム素子に用いられている、酸化物半導体などの半導体材料をチャネル形成領域に有しているトランジスタを、他のトランジスタと区別するために、通常のトランジスタに円を重ねた記号で記す。50

**【0088】**

そして、図8に示す半導体装置は、上記基本ブロックに加えて、プログラム素子の動作を制御するための信号線を有している。

**【0089】**

具体的に、図8では、信号線として、マトリクスの1列あたり5本のデータ信号線Y1、Y2、Y3、Y4、Y5と、1行あたり2本の走査信号線X1、X2を用いる例を示しているが、1行あたり1本の走査信号線を用い、代わりに1列あたり9本のデータ信号線を用いる構成としてもよい。走査信号線の数を減らすと、コンフィギュレーション処理を行う時間を短縮できる。

**【0090】**

なお、図8では、n-1列目の5本のデータ信号線をY<sub>1 n-1</sub>、Y<sub>2 n-1</sub>、Y<sub>3 n-1</sub>、Y<sub>4 n-1</sub>、Y<sub>5 n-1</sub>と示し、n列目の5本のデータ信号線をY<sub>1 n</sub>、Y<sub>2 n</sub>、Y<sub>3 n</sub>、Y<sub>4 n</sub>、Y<sub>5 n</sub>と示している。また、m-1行目の2本の走査信号線をX<sub>1 m-1</sub>、X<sub>2 m-1</sub>と示し、m行目の2本の走査信号線をX<sub>1 m</sub>、X<sub>2 m</sub>と示している。

**【0091】**

なお、信号線の総数を抑えるためには、マトリクスを構成している基本ブロックの配置に合わせて、走査信号線とデータ信号線の数を設定すると良い。例えば、図8のように、一列あたり5本のデータ信号線と一行あたり2本の走査信号線を設ける場合、N行M列の基本ブロックを有する半導体装置全体では、(2N+5M)本の信号線があおよそ必要となる。一方、一列あたり9本のデータ信号線と一行あたり1本の走査信号線を用いる場合、N行M列の基本ブロックを有する半導体装置全体では、(N+9M)本の信号線があおよそ必要となる。よって、N < 4Mの半導体装置ならば、後者の構成よりも前者の構成を採用する方が、信号線の総数を抑えることができる。逆に、N > 4Mの半導体装置ならば、前者の構成よりも後者の構成を採用する方が、信号線の総数を抑えることができる。

**【0092】**

本実施の形態で示す半導体装置では、電源電位の供給を、データ信号線Y5を用いて行う点に特徴を有する。データ信号線Y5(Y<sub>5 1</sub>、Y<sub>5 2</sub>、…、Y<sub>5 n-1</sub>、Y<sub>5 n</sub>、…、)は、電源電位の供給を行うためのプログラム素子が有する第1のトランジスタ801に、各基本ブロックが有する当該第1のトランジスタ801のスイッチングを制御するための信号を送る。そして、他のデータ信号線や走査信号線と同様に、コンフィギュレーション処理を行わない期間においては、データ信号線Y5には信号を送る必要がない。よって、その期間において、データ信号線Y5から各基本ブロックに電源電位を供給することができる。

**【0093】**

なお、図8では、各基本ブロックに入力端子と出力端子を各1つしか設けていない例を示したが、複数の入力端子や複数の出力端子を有する基本ブロックを用いていても良い。

**【0094】**

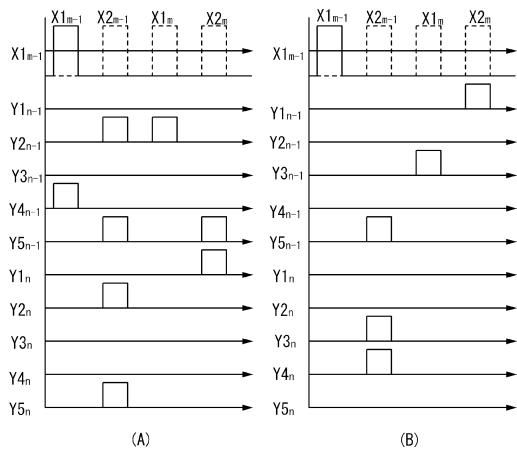

次いで、図8で示す半導体装置の、動作の一例について説明する。図9(A)に、図8に示す半導体装置の各信号線に入力される信号の、タイミングチャートを示す。

**【0095】**

図9(A)に示すように、走査信号線X<sub>1 m-1</sub>、X<sub>2 m-1</sub>、X<sub>1 m</sub>、X<sub>2 m</sub>には、タイミングがずれるように、パルスを有する信号が順次印加される。図9(A)では、走査信号線X<sub>1 m-1</sub>に印加される信号の電位のみを実線で示し、他の走査信号線X<sub>2 m-1</sub>、X<sub>1 m</sub>、X<sub>2 m</sub>に印加される信号の電位を点線で示す。また、図9(A)では、正電位のパルスが印加されている期間以外において、信号の電位は負に保たれる。よって、パルスを有する信号が各走査信号線に印加されると、当該走査信号線にゲート電極が接続された第2のトランジスタが、オンになる。

**【0096】**

そして、各走査信号線にパルスが印加されるタイミングに合わせて、データ信号線Y<sub>1 n</sub>、Y<sub>2 n-1</sub>、Y<sub>3 n-1</sub>、Y<sub>4 n-1</sub>、Y<sub>5 n-1</sub>、Y<sub>1 n</sub>、Y<sub>2 n</sub>、Y<sub>3 n</sub>、Y

10

20

30

40

50

$4_n$ 、 $Y5_n$ に選択信号を印加する。各データ信号線に印加された選択信号は、オンになつた第2のトランジスタを介して、走査信号線とデータ信号線の交点に設けられた第1のトランジスタのゲート電極に入力される。そして、この選択信号の電位に従つて、上記第1のトランジスタのスイッチングが制御される。

#### 【0097】

例えば、図8に示す基本ブロックを、 $U(n-1, m-1)$ 、 $U(n, m)$ 、 $U(n, m+1)$ 、 $U(n-1, m)$ 、 $U(n, m-1)$ 、 $U(n+1, m)$ の順に接続させるには、図9(A)に示したタイミングチャートに従つて、各信号線にパルスを印加すればよい。

#### 【0098】

具体的には、最初に、走査信号線 $X1_{m-1}$ にパルスが印加されるタイミングに合わせて、データ信号線 $Y4_{n-1}$ にパルスを印加する。すると、走査信号線 $X1_{m-1}$ とデータ信号線 $Y4_{n-1}$ の交点にある第1のトランジスタがオンとなる。この第1のトランジスタは、基本ブロック $U(n-1, m)$ の出力端子と、基本ブロック $U(n, m-1)$ の入力端子の接続を制御するスイッチである。よつて、上記第1のトランジスタがオンになることで、基本ブロック $U(n-1, m)$ から基本ブロック $U(n, m-1)$ への信号の経路が形成される。

#### 【0099】

次に、走査信号線 $X2_{m-1}$ にパルスが印加されるタイミングに合わせて、データ信号線 $Y2_{n-1}$ 、 $Y5_{n-1}$ 、 $Y2_n$ 、 $Y5_n$ にパルスを印加する。すると、それぞれの交点にある第1のトランジスタがオンとなる。このうち、走査信号線 $X2_{m-1}$ とデータ信号線 $Y2_{n-1}$ の交点にある第1のトランジスタは、基本ブロック $U(n-1, m-1)$ の出力端子と、基本ブロック $U(n, m)$ の入力端子の接続を制御するスイッチである。また、走査信号線 $X2_{m-1}$ と、データ信号線 $Y5_{n-1}$ 及び $Y5_n$ の交点にある第1のトランジスタは、それぞれ、基本ブロック $U(n, m)$ 、 $U(n+1, m)$ への電源電位の供給を制御するスイッチである。さらに、走査信号線 $X2_{m-1}$ とデータ信号線 $Y2_n$ の交点にある第1のトランジスタは、基本ブロック $U(n, m-1)$ の出力端子と、基本ブロック $U(n+1, m)$ の入力端子の接続を制御するスイッチである。よつて、上記第1のトランジスタがオンになることで、基本ブロック $U(n-1, m-1)$ から基本ブロック $U(n, m)$ への信号の経路と、基本ブロック $U(n, m-1)$ から基本ブロック $U(n+1, m)$ への信号の経路が、形成される。また、基本ブロック $U(n, m)$ 、 $U(n+1, m)$ へ、電源電位が供給される。

#### 【0100】

次に、走査信号線 $X1_m$ にパルスが印加されるタイミングに合わせて、データ信号線 $Y2_{n-1}$ にパルスを印加する。すると、走査信号線 $X1_m$ とデータ信号線 $Y2_{n-1}$ の交点にある第1のトランジスタがオンとなる。この第1のトランジスタは基本ブロック $U(n, m+1)$ の出力端子と、基本ブロック $U(n-1, m)$ の入力端子の接続を制御するスイッチである。よつて、上記第1のトランジスタがオンになることで、基本ブロック $U(n, m+1)$ から基本ブロック $U(n-1, m)$ への信号の経路が形成される。

#### 【0101】

次に、走査信号線 $X2_m$ にパルスが印加されるタイミングに合わせて、データ信号線 $Y5_{n-1}$ 、 $Y1_n$ にパルスを印加する。すると、それぞれの交点にある第1のトランジスタがオンとなる。このうち、走査信号線 $X2_m$ とデータ信号線 $Y1_n$ の交点にある第1のトランジスタは、基本ブロック $U(n, m)$ の出力端子と基本ブロック $U(n, m+1)$ の入力端子の接続を制御するスイッチである。また、走査信号線 $X2_m$ とデータ信号線 $Y5_{n-1}$ の交点にある第1のトランジスタは、基本ブロック $U(n, m+1)$ への電源電位の供給を制御するスイッチである。よつて、上記第1のトランジスタがオンになることで、基本ブロック $U(n, m)$ から基本ブロック $U(n, m+1)$ への信号の経路が形成され、基本ブロック $U(n, m+1)$ への電源電位の供給経路が形成される。

#### 【0102】

10

20

30

40

50

以上の動作により、基本ブロック  $U(n-1, m-1)$  から基本ブロック  $U(n, m)$  への信号の経路、基本ブロック  $U(n, m)$  から基本ブロック  $U(n, m+1)$  への信号の経路、基本ブロック  $U(n, m+1)$  から基本ブロック  $U(n-1, m)$  への信号の経路、基本ブロック  $U(n-1, m)$  から基本ブロック  $U(n, m-1)$  への信号の経路、基本ブロック  $U(n, m-1)$  から基本ブロック  $U(n+1, m)$  への信号の経路が形成され、基本ブロック  $U(n, m+1)$ 、 $U(n, m)$ 、 $U(n+1, m)$  への電源電位の供給経路が形成される。

#### 【0103】

なお、図9(A)のタイミングチャートには図示しなかったが、基本ブロック  $U(n, m+1)$ 、 $U(n, m)$ 、 $U(n+1, m)$  以外に、基本ブロック  $U(n-1, m-1)$ 、 $U(n, m-1)$ 、 $U(n-1, m)$  へも、電源電位の供給経路を形成するようにする。

10

#### 【0104】

上述したように、基本ブロック間の接続や電源電位の供給の設定は、各走査信号線を走査することで行われるため、走査信号線の数が多ければ、設定にも時間を要する。ただし、1本の走査信号線あたりの走査時間、すなわち当該走査信号線にパルスが印加される時間は、100ナノ秒以下である。よって、1000本の走査信号線を有する半導体装置であっても、全ての走査信号線を走査するまでに1ミリ秒もかからない。

#### 【0105】

上述したように、基本ブロック間の接続や電源電位の供給の設定を行った後、データ信号線  $Y_5(Y_{5_1}, Y_{5_2}, \dots, Y_{5_n-1}, Y_{5_n}, \dots)$  に電源電位を供給する。電源電位の供給経路が形成された基本ブロックは、上記データ信号線から、第1のトランジスタを経由して電源電位が供給されるため、演算処理を行うことができる。

20

#### 【0106】

次いで、図8で示す半導体装置の動作について、別の例を挙げて説明する。図9(B)に、図8に示す半導体装置の各信号線に入力される信号の、タイミングチャートを示す。

#### 【0107】

図9(B)に示すように、走査信号線  $X_{1m-1}$ 、 $X_{2m-1}$ 、 $X_{1m}$ 、 $X_{2m}$  には、タイミングがずれるように、パルスを有する信号が順次印加される。なお、図9(B)でも、走査信号線  $X_{1m-1}$  に印加される信号の電位のみを実線で示し、他の走査信号線  $X_{2m-1}$ 、 $X_{1m}$ 、 $X_{2m}$  に印加される信号の電位を点線で示す。また、図9(B)でも、正電位のパルスが印加されている期間以外において、信号の電位は負に保たれる。よって、パルスを有する信号が各走査信号線に印加されると、当該走査信号線にゲート電極が接続された第2のトランジスタが、オンになる。

30

#### 【0108】

そして、図9(B)では、走査信号線  $X_{1m-1}$  にパルスが印加される期間において、データ信号線にはパルスは印加されない。次いで、走査信号線  $X_{2m-1}$  にパルスが印加されるタイミングに合わせて、データ信号線  $Y_{5n-1}$ 、 $Y_{3n}$ 、 $Y_{4n}$  にパルスを印加する。すると、それぞれの交点にある第1のトランジスタがオンとなる。

#### 【0109】

このうち、走査信号線  $X_{2m-1}$  とデータ信号線  $Y_{5n-1}$  の交点にある第1のトランジスタは、基本ブロック  $U(n, m)$  への電源電位の供給を制御するスイッチである。さらに、走査信号線  $X_{2m-1}$  とデータ信号線  $Y_{3n}$  の交点にある第1のトランジスタは、基本ブロック  $U(n, m-1)$  の出力端子と基本ブロック  $U(n+1, m-1)$  の入力端子を接続するスイッチであり、走査信号線  $X_{2m-1}$  とデータ信号線  $Y_{4n}$  の交点にある第1のトランジスタは、基本ブロック  $U(n+1, m-1)$  の出力端子と基本ブロック  $U(n, m)$  の入力端子を接続するスイッチである。上記第1のトランジスタがオンになると、基本ブロック  $U(n, m-1)$  から基本ブロック  $U(n+1, m-1)$  への信号の経路、基本ブロック  $U(n+1, m-1)$  から基本ブロック  $U(n, m)$  への信号の経路が形成され、基本ブロック  $U(n, m)$  への電源電位の供給経路が形成される。

40

#### 【0110】

次に、走査信号線  $X_{1m}$  にパルスが印加されるタイミングに合わせて、データ信号線  $Y_{3n-1}$  にパルスを印加する。すると、走査信号線  $X_{1m}$  とデータ信号線  $Y_{3n-1}$  の交点にある第1のトランジスタがオンとなる。この第1のトランジスタは基本ブロックU( $n, m$ )の出力端子と、基本ブロックU( $n-1, m$ )の入力端子の接続を制御するスイッチである。よって、上記第1のトランジスタがオンになることで、基本ブロックU( $n, m$ )から基本ブロックU( $n-1, m$ )への信号の経路が形成される。

#### 【0111】

次に、走査信号線  $X_{2m}$  にパルスが印加されるタイミングに合わせて、データ信号線  $Y_{1n-1}$  にパルスを印加する。すると、その交点にある第1のトランジスタがオンとなる。走査信号線  $X_{2m}$  とデータ信号線  $Y_{1n-1}$  の交点にある第1のトランジスタは基本ブロックU( $n-1, m$ )の出力端子と基本ブロックU( $n-1, m+1$ )の入力端子の接続を制御するスイッチである。以上により、基本ブロックU( $n-1, m$ )から基本ブロックU( $n-1, m+1$ )への信号の経路が形成される。

#### 【0112】

以上の動作により、基本ブロックU( $n, m-1$ )から、U( $n+1, m-1$ )、U( $n, m$ )、U( $n-1, m$ )、U( $n-1, m+1$ )という順で信号の経路が形成され、また、基本ブロックU( $n, m$ )への電源電位の供給経路が形成される。なお、図9(B)のタイミングチャートには図示しなかったが、基本ブロックU( $n, m$ )以外に、基本ブロックU( $n, m-1$ )、U( $n+1, m-1$ )、U( $n-1, m$ )へも、電源電位の供給経路を形成するようにする。

#### 【0113】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【0114】

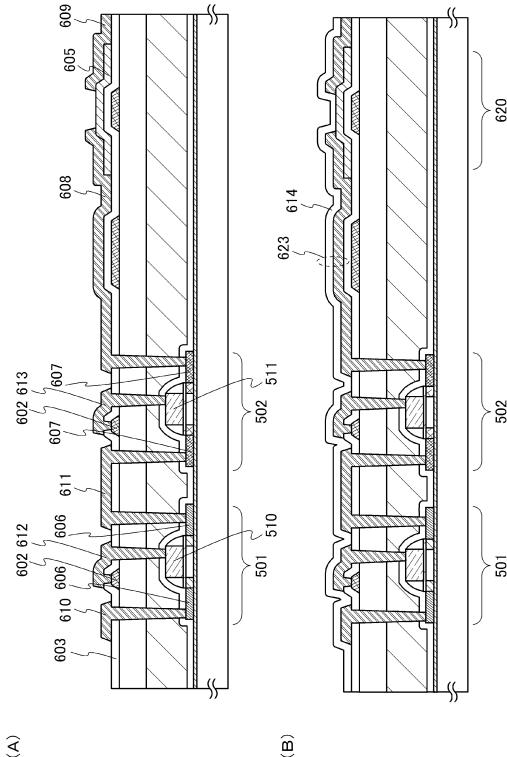

##### (実施の形態4)

本実施の形態では、プログラム素子に用いられている、酸化物半導体を用いた第2のトランジスタの作製方法について説明する。なお、本実施の形態では、図2(B)に示したプログラム素子を例に挙げて、酸化物半導体を用いた第2のトランジスタの作製方法について説明するが、他の回路構成を有するプログラム素子も、本実施の形態において示す作製方法を参考にして、作製することが可能である。

#### 【0115】

また、第1のトランジスタ、第3のトランジスタは、ゲルマニウム、シリコン、シリコンゲルマニウムや、単結晶炭化珪素などを用いた、通常のCMOSプロセスを用いて形成することができる。また、第1のトランジスタ、第3のトランジスタは、薄膜の半導体膜を用いていても良いし、バルクの半導体基板を用いていても良い。本実施の形態では、SOI(Silicon on Insulator)基板を用いて形成された第1のトランジスタ、第3のトランジスタ上に、酸化物半導体を用いた第2のトランジスタを作製する場合を例に挙げて、その作製方法について説明する。

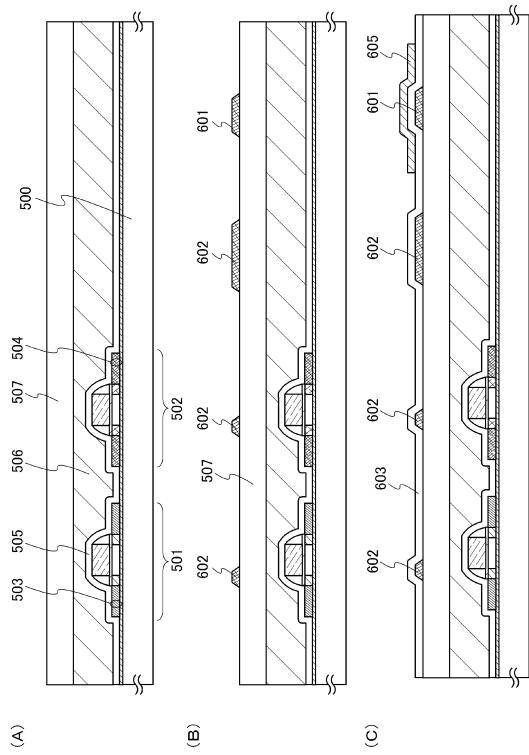

#### 【0116】

まず、図10(A)に示すように、SOI基板を用いて第1のトランジスタ501と、第3のトランジスタ502を形成する。具体的に、第1のトランジスタ501は、絶縁表面を有する基板500上の単結晶シリコン膜503を用いて形成されたnチャネル型トランジスタであり、第3のトランジスタ502は、絶縁表面を有する基板500上の単結晶シリコン膜504を用いて形成されたpチャネル型トランジスタである。また、第1のトランジスタ501および第3のトランジスタ502のゲート絶縁膜の厚さは10nm以上100nm、チャネル長はともに100nm以上500nm以下とする。チャネル長は、第1のトランジスタ501と第3のトランジスタ502で異なった値としてもよい。

#### 【0117】

次いで、第1のトランジスタ501及び第3のトランジスタ502上に、酸化物半導体を用いた第2のトランジスタを作製する。

#### 【0118】

10

20

30

40

50

まず、図10(A)に示すように、第1のトランジスタ501、第3のトランジスタ502を覆うように、絶縁膜505、絶縁膜506、絶縁膜507を順に形成する。なお、本実施の形態では、第1のトランジスタ501及び第3のトランジスタ502を、3層の絶縁膜505、絶縁膜506、絶縁膜507で覆う場合を例示しているが、第1のトランジスタ501及び第3のトランジスタ502と、第2のトランジスタの間に設ける絶縁膜は3層である必要はなく、1層または2層であっても良いし、4層以上であっても良い。

#### 【0119】

絶縁膜505、絶縁膜506、絶縁膜507は、後の作製工程における加熱処理の温度に耐えうる材料を用いる。具体的に、絶縁膜505、絶縁膜506、絶縁膜507として、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、窒化アルミニウム、酸化アルミニウムなどを用いるのが望ましい。なお、本明細書において酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い物質であり、また、窒化酸化物とは、その組成として、酸素よりも窒素の含有量が多い物質を意味する。

#### 【0120】

絶縁膜507は、その表面をCMP(化学的機械研磨)法などにより平坦化させても良い。

#### 【0121】

次いで、図10(B)に示すように、絶縁膜507上に、ゲート電極601、電極602を形成する。

#### 【0122】

ゲート電極601、電極602の材料は、モリブデン、チタン、クロム、タンタル、タンゲステン、ネオジム、スカンジウム等の金属材料、これら金属材料を主成分とする合金材料を用いた導電膜、或いはこれら金属の窒化物を、単層で又は積層で用いることができる。なお、後の工程において行われる加熱処理の温度に耐えうるのであれば、上記金属材料としてアルミニウム、銅を用いることも出来る。アルミニウムまたは銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タンゲステン、ネオジム、スカンジウム等を用いることができる。

#### 【0123】

例えば、二層の積層構造を有するゲート電極601、電極602として、アルミニウム膜上にモリブデン膜が積層された二層の積層構造、銅膜上にモリブデン膜を積層した二層の積層構造、銅膜上に窒化チタン膜若しくは窒化タンタル膜を積層した二層の積層構造、または、窒化チタン膜とモリブデン膜とを積層した二層の積層構造とすることが好ましい。3層の積層構造を有するゲート電極601、電極602としては、アルミニウム膜、アルミニウムとシリコンの合金膜、アルミニウムとチタンの合金膜またはアルミニウムとネオジムの合金膜を中間層とし、タンゲステン膜、窒化タンゲステン膜、窒化チタン膜またはチタン膜を上下層として積層した構造とすることが好ましい。

#### 【0124】

また、ゲート電極601、電極602に酸化インジウム、酸化インジウム酸化スズ合金( $In_2O_3-SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛合金、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、または酸化亜鉛ガリウム等の透光性を有する酸化物導電膜を用いることもできる。

#### 【0125】

ゲート電極601、電極602の膜厚は、10nm~400nm、好ましくは100nm~200nmとする。本実施の形態では、タンゲステンターゲットを用いたスパッタ法により150nmのゲート電極用の導電膜を形成した後、該導電膜をエッチングにより所望の形状に加工(パターニング)することで、ゲート電極601、電極602を形成する。なお、形成されたゲート電極の端部がテーパー形状であると、上に積層するゲート絶縁膜の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため

10

20

30

40

50

、製造コストを低減できる。

#### 【0126】

次いで、図10(C)に示すように、ゲート電極601、電極602上に、ゲート絶縁膜603を形成する。ゲート絶縁膜603は、プラズマCVD法又はスパッタリング法等を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、酸化ハフニウム膜または酸化タンタル膜を単層で又は積層させて形成することができる。ゲート絶縁膜603は、水分や、水素などの不純物を極力含まないことが望ましい。スパッタリング法により酸化珪素膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

10

#### 【0127】

不純物を除去することによりi型化又は実質的にi型化された酸化物半導体(高純度化された酸化物半導体)は界面準位、界面電荷に対して極めて敏感であるため、高純度化された酸化物半導体とゲート絶縁膜603の界面特性は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁膜(GI)は、高品質化が要求される。

#### 【0128】

例えば、μ波(周波数2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体と高品質なゲート絶縁膜とが密接することにより、界面準位密度を低減して界面特性を良好なものとすることができるからである。

20

#### 【0129】

もちろん、ゲート絶縁膜として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によって膜質や、酸化物半導体との界面特性が改善される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、ゲート絶縁膜と酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

#### 【0130】

バリア性の高い材料を用いた絶縁膜と、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜とを積層させた構造を有するゲート絶縁膜603を形成しても良い。この場合、酸化珪素膜、酸化窒化珪素膜などの絶縁膜は、バリア性の高い絶縁膜と酸化物半導体膜の間に形成する。バリア性の高い絶縁膜として、例えば窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などが挙げられる。バリア性の高い絶縁膜を用いることで、水分または水素などの雰囲気中の不純物、或いは基板内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体膜内、ゲート絶縁膜603内、或いは、酸化物半導体膜と他の絶縁膜の界面とその近傍に入り込むのを防ぐことができる。また、酸化物半導体膜に接するよう窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い絶縁膜が直接酸化物半導体膜に接するのを防ぐことができる。

30

#### 【0131】

例えば、第1のゲート絶縁膜としてスパッタリング法により膜厚50nm以上200nm以下の窒化珪素膜(SiN<sub>y</sub>(y>0))を形成し、第1のゲート絶縁膜上に第2のゲート絶縁膜として膜厚5nm以上300nm以下の酸化珪素膜(SiO<sub>x</sub>(x>0))を積層して、膜厚100nmのゲート絶縁膜603としても良い。ゲート絶縁膜603の膜厚は、トランジスタに要求される特性によって適宜設定すればよく350nm乃至400nm程度でもよい。

40

#### 【0132】

本実施の形態では、スパッタ法で形成された膜厚50nmの窒化珪素膜上に、スパッタ法で形成された膜厚100nmの酸化珪素膜を積層させた構造を有する、ゲート絶縁膜603を形成する。

50

## 【0133】

なお、ゲート絶縁膜は酸化物半導体と接する。酸化物半導体に水素が侵入するとトランジスタ特性に悪影響を及ぼすので、ゲート絶縁膜は水素、水酸基および水分が含まれないことが望ましい。ゲート絶縁膜603に水素、水酸基及び水分がなるべく含まれないようにするためにには、成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極601、電極602が形成された基板500を予備加熱し、基板500に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100以上400以下、好ましくは150以上300以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

10

## 【0134】

次いで、ゲート絶縁膜603上に膜厚2nm以上200nm以下、好ましくは膜厚3nm以上50nm以下、さらに好ましくは膜厚3nm以上20nm以下の酸化物半導体膜を形成する。酸化物半導体膜は、酸化物半導体をターゲットとして用い、スパッタ法により成膜する。また、酸化物半導体膜は、希ガス（例えばアルゴン）雰囲気下、酸素雰囲気下、又は希ガス（例えばアルゴン）及び酸素混合雰囲気下においてスパッタ法により形成することができる。

## 【0135】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁膜603の表面に付着している塵埃を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

20

## 【0136】

酸化物半導体膜には、上述したように、四元系金属酸化物であるIn-Sn-Ga-Zn-O系酸化物半導体や、三元系金属酸化物であるIn-Ga-Zn-O系酸化物半導体、In-Sn-Zn-O系酸化物半導体、In-Al-Zn-O系酸化物半導体、Sn-Ga-Zn-O系酸化物半導体、Al-Ga-Zn-O系酸化物半導体、Sn-Al-Zn-O系酸化物半導体や、二元系金属酸化物であるIn-Zn-O系酸化物半導体、Sn-Zn-O系酸化物半導体、Al-Zn-O系酸化物半導体、Zn-Mg-O系酸化物半導体、Sn-Mg-O系酸化物半導体、In-Mg-O系酸化物半導体、In-Ga-O系酸化物半導体や、In-O系酸化物半導体、Sn-O系酸化物半導体、Zn-O系酸化物半導体などを用いることができる。また、上記酸化物半導体は珪素を含んでいてもよい。

30

## 【0137】

或いは、酸化物半導体は、化学式 $InMO_3(ZnO)_m$ ( $m > 0$ )で表記することができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。

40

## 【0138】

本実施の形態では、In(インジウム)、Ga(ガリウム)、及びZn(亜鉛)を含むターゲットを用いたスパッタ法により得られる膜厚30nmのIn-Ga-Zn-O系酸化物半導体の薄膜を、酸化物半導体膜として用いる。上記ターゲットとして、例えば、各金属の組成比がIn:Ga:Zn=1:1:0.5、In:Ga:Zn=1:1:1、またはIn:Ga:Zn=1:1:2であるターゲットを用いることができる。また、SiO<sub>2</sub>を2重量%以上10重量%以下含むターゲットを用いて成膜を行ってもよい。また、In、Ga、及びZnを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

## 【0139】

50

本実施の形態では、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板 500 上に酸化物半導体膜を成膜する。成膜時に、基板温度を 100 以上 600 以下、好ましくは 200 以上 400 以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて成膜室を排気すると、例えば、水素原子、水 ( $H_2O$ ) など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。10

#### 【 0140 】

成膜条件の一例としては、基板とターゲットとの間との距離を 100 mm、圧力 0.6 Pa、直流 (DC) 電源 0.5 kW、酸素（酸素流量比率 100%）雰囲気下の条件が適用される。なお、パルス直流 (DC) 電源を用いると、成膜時に発生する塵埃が軽減でき、膜厚分布も均一となるために好ましい。

#### 【 0141 】

なお、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室でゲート絶縁膜 603 までが形成された基板 500 を予備加熱し、基板 500 に吸着した水分または水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100 以上 400 以下、好ましくは 150 以上 300 以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、後に行われる絶縁膜 614 の成膜前に、ソース電極 608 及びドレイン電極 609、配線 610 乃至配線 613 まで形成した基板 500 にも同様に行ってもよい。20

#### 【 0142 】

次いで、図 10 (C) に示すように、酸化物半導体膜をエッチングなどにより所望の形状に加工（パターニング）し、ゲート絶縁膜 603 上のゲート電極 601 と重なる位置に、島状の酸化物半導体膜 605 を形成する。30

#### 【 0143 】

島状の酸化物半導体膜 605 を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【 0144 】

なお、島状の酸化物半導体膜 605 を形成するためのエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素 ( $Cl_2$ )、三塩化硼素 ( $BCl_3$ )、四塩化珪素 ( $SiCl_4$ )、四塩化炭素 ( $CCl_4$ ) など）が好ましい。また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素 ( $CF_4$ )、六弗化硫黄 ( $SF_6$ )、三弗化窒素 ( $NF_3$ )、トリフルオロメタン ( $CHF_3$ ) など）、臭化水素 ( $HB$ r)、酸素 ( $O_2$ )、これらのガスにヘリウム ( $He$ ) やアルゴン ( $Ar$ ) などの希ガスを添加したガス、などを用いることができる。40

#### 【 0145 】

ドライエッチング法としては、平行平板型 RIE (Reactive Ion Etching) 法や、ICP (Inductively Coupled Plasma: 誘導結合型プラズマ) エッチング法を用いることができる。所望の加工形状にエッチングできるように、エッチング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。

#### 【 0146 】

10

20

30

40

50

ウェットエッティング用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO-07N（関東化学社製）を用いてもよい。また、ウェットエッティング後のエッティング液はエッティングされた材料とともに洗浄によって除去される。その除去された材料を含むエッティング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッティング後の廃液から酸化物半導体膜に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化を図ることができる。

#### 【0147】

なお、次工程の導電膜を形成する前に逆スパッタを行い、島状の酸化物半導体膜605及びゲート絶縁膜603の表面に付着しているレジスト残渣などを除去することが好ましい。

10

#### 【0148】

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水分または水素が多量に含まれていることがある。水分または水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物半導体膜605に対して、窒素、酸素、超乾燥空気（水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気）、または希ガス（アルゴン、ヘリウムなど）の雰囲気下で加熱処理を行う。

#### 【0149】

酸化物半導体膜605に加熱処理を施すことで、酸化物半導体膜605中の水分または水素を脱離させることができる。具体的には、300以上700以下、好ましくは300以上500以下で加熱処理を行えば良い。例えば、500、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

20

#### 【0150】

本実施の形態では、加熱処理装置の一つである電気炉を用いる。

#### 【0151】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA（Gas Rapid Thermal Anneal）装置、LRTA（Lamp Rapid Thermal Anneal）装置等のRTA（Rapid Thermal Anneal）装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

30

#### 【0152】

なお、加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水分または水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N（99.9999%）以上、好ましくは7N（99.9999%）以上、（即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。

40

#### 【0153】

以上の工程により、酸化物半導体膜605中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体膜を形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧性が高く、オンオフ比の高いトランジスタを作製

50

することができる。上記加熱処理は、酸化物半導体膜の成膜以降であれば、いつでも行うことができる。

#### 【0154】

なお、酸化物半導体膜を加熱する場合、酸化物半導体膜の材料や加熱条件にもよるが、その上表面に板状結晶が形成されることがある。板状結晶は、酸化物半導体膜の表面に対して略垂直にc軸配向した単結晶体であることが好ましい。また、単結晶体でなくとも、各結晶が、酸化物半導体膜の表面に対して略垂直にc軸配向した多結晶体であることが好ましい。そして、上記多結晶体は、c軸配向している事に加えて、各結晶のa b面が一致するか、a軸、或いは、b軸が一致していることが好ましい。なお、酸化物半導体膜の下地表面に凹凸がある場合、板状結晶は多結晶体となる。したがって、下地表面は可能な限り平坦であることが望まれる。10

#### 【0155】

次に、絶縁膜505、絶縁膜506、絶縁膜507、ゲート絶縁膜603を部分的にエッチングすることで、第1のトランジスタ501が有する一対の不純物領域606と、第3のトランジスタ502が有する一対の不純物領域607と、第1のトランジスタ501が有するゲート電極510と、第3のトランジスタ502が有するゲート電極511と、電極602に達するコンタクトホールを形成する。

#### 【0156】

なお、第1のトランジスタ501が有する一対の不純物領域606は、一方がソース電極、他方がドレイン電極として機能する。また、第3のトランジスタ502が有する一対の不純物領域607は、一方がソース電極、他方がドレイン電極として機能する。20

#### 【0157】

そして、酸化物半導体膜605を覆うように、ソース電極またはドレイン電極（これと同じ層で形成される配線を含む）として用いる導電膜を、スパッタ法や真空蒸着法で形成したあと、エッチング等により該導電膜をパターニングすることで、図11(A)に示すように、ソース電極608、ドレイン電極609、配線610乃至配線613を形成する。

#### 【0158】

なお、ソース電極608、ドレイン電極609は、酸化物半導体膜605に接している。また、配線610は、一対の不純物領域606の一方に接している。配線611は、一対の不純物領域606の他方と、一対の不純物領域607の一方に接している。また、ソース電極608は、一対の不純物領域607の他方にも、接している。また、配線612は、電極602及びゲート電極510に接している。また、配線613は、電極602及びゲート電極511に接している。30

#### 【0159】

ソース電極608、ドレイン電極609、配線610乃至配線613（加えて、これらと同じ層で形成される他の配線を含む）となる導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、Al、Cuなどの金属膜の下側もしくは上側にCr、Ta、Ti、Mo、Wなどの高融点金属膜を積層させた構成としても良い。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、YなどAl膜に生ずるヒロックやウィスカの発生を防止する元素が添加されているAl材料を用いることで耐熱性を向上させることが可能となる。40

#### 【0160】

また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。

#### 【0161】

また、ソース電極608、ドレイン電極609、配線610乃至配線613（加えて、これらと同じ層で形成される他の配線を含む）となる導電膜としては、導電性の金属酸化物50

で形成しても良い。導電性の金属酸化物としては酸化インジウム ( $In_2O_3$ )、酸化スズ ( $SnO_2$ )、酸化亜鉛 ( $ZnO$ )、酸化インジウム酸化スズ合金、酸化インジウム酸化亜鉛合金 ( $In_2O_3-ZnO$ ) または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

#### 【0162】

導電膜形成後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

#### 【0163】

なお、導電膜のエッティングの際に、酸化物半導体膜 605 がなるべく除去されないようにそれぞれの材料及びエッティング条件を適宜調節する。エッティング条件によっては、島状の酸化物半導体膜 605 の露出した部分が一部エッティングされることで、溝部（凹部）が形成されることもある。

10

#### 【0164】

本実施の形態では、導電膜にチタン膜を用いる。そのため、アンモニアと過酸化水素水を含む溶液（アンモニア過水）を用いて、選択的に導電膜をウェットエッティングすることができるが、酸化物半導体膜 605 も一部エッティングされる場合がある。アンモニア過水を含む溶液は、具体的には、31重量%の過酸化水素水と、28重量%のアンモニア水と水とを、体積比 5 : 2 : 2 で混合した水溶液を用いる。或いは、塩素 ( $Cl_2$ )、塩化硼素 ( $BCl_3$ )などを含むガスを用いて、導電膜をドライエッティングしても良い。

20

#### 【0165】

なお、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッティング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッティングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッティング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

#### 【0166】

次いで、 $N_2O$ 、 $N_2$ 、または  $Ar$  などのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体膜の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

30

#### 【0167】

なお、プラズマ処理を行った後、図 11 (B) に示すように、ソース電極 608 と、ドレン電極 609 と、配線 610 乃至配線 613 と、酸化物半導体膜 605 とを覆うように、絶縁膜 614 を形成する。絶縁膜 614 は、水分や、水素などの不純物を極力含まないことが望ましく、単層の絶縁膜であっても良いし、積層された複数の絶縁膜で構成されていても良い。絶縁膜 614 に水素が含まれると、その水素が酸化物半導体膜へ侵入し、又は水素が酸化物半導体膜中の酸素を引き抜き、酸化物半導体膜のバックチャネル部が低抵抗化 (n型化) してしまい、寄生チャネルが形成されるおそれがある。よって、絶縁膜 614 はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。上記絶縁膜 614 には、バリア性の高い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などを用いることができる。複数の積層された絶縁膜を用いる場合、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を、上記バリア性の高い絶縁膜よりも、酸化物半導体膜 605 に近い側に形成する。そして、窒素の含有比率が低い絶縁膜を間に挟んで、ソース電極 608 及びドレン電極 609 及び酸化物半導体膜 605 と重なるように、バリア性の高い絶縁膜を形成する。バリア性の高い絶縁膜を用いることで、酸化物半導体膜 605 内、ゲート絶縁膜 603 内、或いは、酸化物半導体膜 605 と他の絶縁膜の界面とその近傍に、水分または水素などの不純物が入り込むのを防

40

50

ぐことができる。また、酸化物半導体膜 605 に接するように窒素の比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い材料を用いた絶縁膜が直接酸化物半導体膜 605 に接するのを防ぐことができる。

#### 【0168】

本実施の形態では、スパッタ法で形成された膜厚 200 nm の酸化珪素膜上に、スパッタ法で形成された膜厚 100 nm の窒化珪素膜を積層させた構造を有する、絶縁膜 614 を形成する。成膜時の基板温度は、室温以上 300 以下とすればよく、本実施の形態では 100 とする。

#### 【0169】

なお、絶縁膜 614 を形成した後に、加熱処理を施しても良い。加熱処理は、窒素、酸素、超乾燥空気（水の含有量が 20 ppm 以下、好ましくは 1 ppm 以下、好ましくは 10 ppb 以下の空気）、または希ガス（アルゴン、ヘリウムなど）の雰囲気下において、好ましくは 200 以上 400 以下、例えば 250 以上 350 以下で行う。本実施の形態では、例えば、窒素雰囲気下で 250 、1 時間の加熱処理を行う。或いは、ソース電極 608 及びドレイン電極 609 と、配線 610 乃至配線 613 とを形成する前に、酸化物半導体膜に対して行った先の加熱処理と同様に、高温短時間の RTA 処理を行っても良い。酸化物半導体膜に対して行った先の加熱処理により、酸化物半導体膜 605 に酸素欠損が発生していたとしても、ソース電極 608 とドレイン電極 609 の間に設けられた酸化物半導体膜 605 の露出領域に接して、酸素を含む絶縁膜 614 が設けられた後に、加熱処理が施されることによって、酸化物半導体膜 605 に酸素が供与される。そのため、酸化物半導体膜 605 の絶縁膜 614 と接する領域に酸素が供与されることで、ドナーとなる酸素欠損を低減し、化学量論的組成比を満たすことが可能である。その結果、酸化物半導体膜 605 を i 型化または実質的に i 型化にすることができ、トランジスタの電気特性の向上および、電気特性のばらつきを軽減することができる。この加熱処理を行うタイミングは、絶縁膜 614 の形成後であれば特に限定されない。他の工程における加熱処理、例えば樹脂膜形成時の加熱処理や、透明導電膜を低抵抗化させるための加熱処理が、上記加熱処理を兼ねるようにすることで、工程数を増やすことなく、酸化物半導体膜 605 を i 型化または実質的に i 型化にすることができる。

#### 【0170】

絶縁膜 614 上に導電膜を形成した後、該導電膜をパターニングすることで、酸化物半導体膜 605 と重なる位置にバックゲート電極を形成しても良い。バックゲート電極を形成する場合、バックゲート電極を覆うように絶縁膜を形成する。バックゲート電極は、ゲート電極 601 、電極 602 、或いはソース電極 608 及びドレイン電極 609 、配線 610 乃至配線 613 と同様の材料、構造を用いて形成することが可能である。

#### 【0171】

バックゲート電極の膜厚は、10 nm ~ 400 nm 、好ましくは 100 nm ~ 200 nm とする。例えば、チタン膜、アルミニウム膜、チタン膜が積層された構造を有する導電膜を形成した後、フォトリソグラフィ法などによりレジストマスクを形成し、エッチングにより不要な部分を除去して、該導電膜を所望の形状に加工（パターニング）することで、バックゲート電極を形成すると良い。

#### 【0172】

以上の工程により、第 2 のトランジスタ 620 と、容量素子 623 が形成される。なお、容量素子 623 は、電極 602 とソース電極 608 とが、ゲート絶縁膜 603 を間に挟んで重なり合っている領域に形成される。なお、容量素子 623 は、必ずしも第 2 のトランジスタ 620 と同じ層上に形成する必要はなく、例えば、第 1 のトランジスタ 501 及び第 3 のトランジスタ 502 と同じ層上に形成しても良い。

#### 【0173】

第 2 のトランジスタ 620 は、ゲート電極 601 と、ゲート電極 601 上のゲート絶縁膜 603 と、ゲート絶縁膜 603 上においてゲート電極 601 と重なっている酸化物半導体膜 605 と、酸化物半導体膜 605 上に形成された一対のソース電極 608 またはドレイ

10

20

30

40

50

ン電極 609とを有する。さらに、第2のトランジスタ 620は、酸化物半導体膜 605 上に形成された絶縁膜 614を、その構成要素に含めても良い。図11(B)に示す第2のトランジスタ 620は、ソース電極 608とドレイン電極 609の間ににおいて、酸化物半導体膜 605の一部が露出したチャネルエッチ構造である。

#### 【0174】

なお、第2のトランジスタ 620はシングルゲート構造のトランジスタを用いて説明したが、必要に応じて、電気的に接続された複数のゲート電極 601を有することで、チャネル形成領域を複数有する、マルチゲート構造のトランジスタも形成することができる。

#### 【0175】

次いで、本実施の形態のように酸化物半導体膜中に含まれる水分または水素などの不純物を極力除去し、酸化物半導体膜を高純度化することが、トランジスタの特性にどのように影響を与えるかを以下に説明する。

#### 【0176】

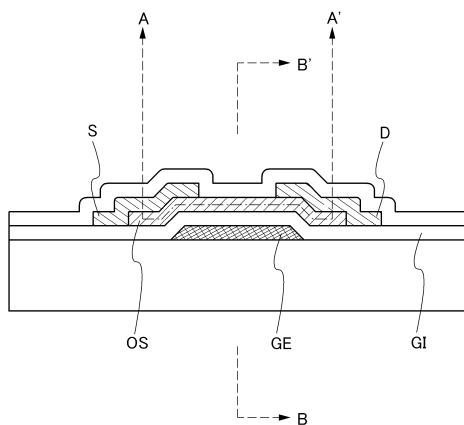

図13は、酸化物半導体を用いたトランジスタの断面図である。ゲート電極(GE)上にゲート絶縁膜(GI)を介して酸化物半導体膜(OS)が設けられ、その上にソース電極(S)及びドレイン電極(D)が設けられ、ソース電極(S)及びドレイン電極(D)上に絶縁膜が設けられている。

#### 【0177】

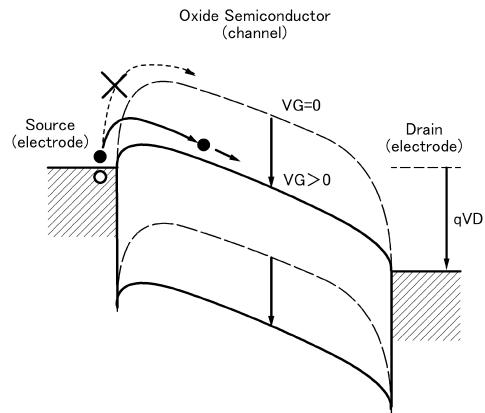

図14に、図13に示すA-A'断面におけるエネルギー-band図(模式図)を示す。また、図14において黒丸( )は電子を示し、白丸( )は正孔を示し、それぞれは電荷-q、電荷+qを有している。ドレイン電極(D)に正の電圧( $V_D > 0$ )を印加した上で、破線はゲート電極(GE)に電圧を印加しない場合( $V_G = 0$ )、実線はゲート電極(GE)に正の電圧( $V_G > 0$ )を印加する場合を示す。ゲート電極(GE)に電圧を印加しない場合は高いポテンシャル障壁のためにソース電極(S)から酸化物半導体膜(OS)側へキャリア(電子)が注入されず、電流を流さないオフ状態を示す。一方、ゲート電極(GE)に正の電圧を印加するとポテンシャル障壁が低下し、酸化物半導体膜(OS)に電流を流すオン状態を示す。

#### 【0178】

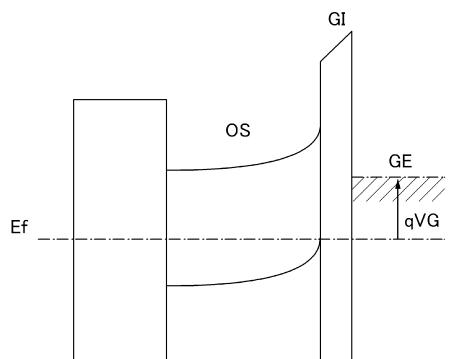

図15は、図13におけるB-B'の断面におけるエネルギー-band図(模式図)である。図15(A)はゲート電極(GE)に正の電圧( $V_G > 0$ )が印加された状態であり、ソース電極とドレイン電極間にキャリア(電子)が流れるオン状態を示している。また、図15(B)は、ゲート電極(GE)に負の電圧( $V_G < 0$ )が印加された状態であり、オフ状態である場合を示す。

#### 【0179】

図16は、真空準位と金属の仕事関数( $\phi_M$ )、酸化物半導体の電子親和力( $\phi$ )の関係を示す。

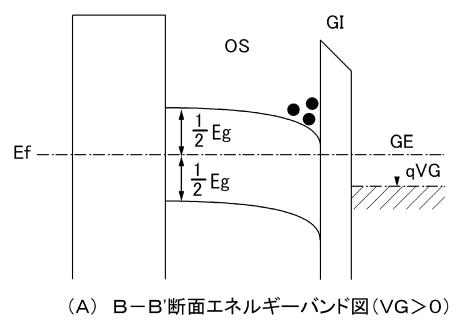

#### 【0180】

常温において金属中の電子は縮退しており、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体は一般にn型であり、その場合のフェルミ準位( $E_F$ )は、バンドギヤップ中央に位置する真性フェルミ準位( $E_i$ )から離れて、伝導帯( $E_c$ )寄りに位置している。なお、酸化物半導体において水素の一部はドナーとなり、酸化物半導体がn型化する一つの要因であることが知られている。また、酸素欠損もn型化する一つの要因であることが知られている。

#### 【0181】

これに対して、本発明の一態様は、n型不純物である水素を酸化物半導体から除去して酸化物半導体の主成分以外の不純物が極力含まれないように高純度化し、かつ、酸素欠損を除去することにより、酸化物半導体を真性(i型)、または限りなく真性に近づけたものである。すなわち、不純物を添加して酸化物半導体をi型化するのではなく、水分または水素等の不純物や酸素欠損を極力除去して高純度化することにより、i型(真性半導体)又はi型(真性半導体)に限りなく近い酸化物半導体を得ることを特徴としている。上記構

10

20

30

40

50

成により、矢印で示すように、フェルミ準位 ( $E_f$ ) は真性フェルミ準位 ( $E_i$ ) と同じレベルに限りなく近づけることができる。

#### 【0182】

酸化物半導体のバンドギャップ ( $E_g$ ) は 3.15 eV で、電子親和力 ( ) は 4.3 V と言われている。ソース電極及びドレイン電極を構成する材料がチタン ( $Ti$ ) である場合の仕事関数は、酸化物半導体の電子親和力 ( ) とほぼ等しい。この場合、金属 - 酸化物半導体界面において、電子に対してショットキー型の障壁は形成されない。チタン以外にもこの条件を満たす材料は存在する。

#### 【0183】

このとき電子は、図 15 (A) で示すようにゲート絶縁膜と高純度化された酸化物半導体との界面における、酸化物半導体側のエネルギー的に安定な最低部を移動する。 10

#### 【0184】

また、図 15 (B) において、ゲート電極 (GE) に負の電圧が印加されると、少数キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

#### 【0185】

このように、酸化物半導体の主成分以外の水分または水素などの不純物が極力含まれないように、酸化物半導体膜を高純度化することにより、トランジスタの動作を良好なものとすることができる。

#### 【0186】

本実施の形態は、上記実施の形態と組み合わせて実施することが可能である。 20

#### 【0187】

##### (実施の形態 5)

本実施の形態では、酸化物半導体膜を用いた第 3 のトランジスタの構造が、実施の形態 4 とは異なる、プログラム素子の構成について説明する。

#### 【0188】

図 12 (A) に示すプログラム素子は、実施の形態 4 と同様に、第 1 のトランジスタ 501 と、第 3 のトランジスタ 502 を有している。そして、図 12 (A) では、第 1 のトランジスタ 501 と、第 3 のトランジスタ 502 上に、酸化物半導体膜を用いたチャネル保護構造の、ボトムゲート型の第 2 のトランジスタ 630 が形成されている。

#### 【0189】

第 2 のトランジスタ 630 は、絶縁膜 507 上に形成されたゲート電極 631 と、ゲート電極 631 上のゲート絶縁膜 632 と、ゲート絶縁膜 632 上においてゲート電極 631 と重なっている酸化物半導体膜 633 と、ゲート電極 631 と重なる位置において酸化物半導体膜 633 上に形成されたチャネル保護膜 634 と、酸化物半導体膜 633 上に形成されたソース電極 635、ドレイン電極 636 と、を有する。さらに、第 2 のトランジスタ 630 は、酸化物半導体膜 633 上に形成された絶縁膜 637 を、その構成要素に含めても良い。

#### 【0190】

チャネル保護膜 634 を設けることによって、酸化物半導体膜 633 のチャネル形成領域となる部分に対する、後の工程時におけるダメージ (エッティング時のプラズマやエッティング剤による膜減りなど) を防ぐことができる。従ってトランジスタの信頼性を向上させることができる。 40

#### 【0191】

チャネル保護膜 634 には、酸素を含む無機材料 (酸化珪素、窒化酸化珪素、酸化窒化珪素、酸化アルミニウム、または酸化窒化アルミニウムなど) を用いることができる。チャネル保護膜 634 は、プラズマ CVD 法や熱 CVD 法などの気相成長法やスパッタリング法を用いて形成することができる。チャネル保護膜 634 は成膜後にエッティングにより形状を加工する。ここでは、スパッタ法により酸化珪素膜を形成し、フォトリソグラフィによるマスクを用いてエッティング加工することでチャネル保護膜 634 を形成する。

#### 【0192】

10

20

30

40

50

酸素を含む無機材料をチャネル保護膜 634 に用いることで、水分または水素を低減させるための加熱処理により酸化物半導体膜 633 中に酸素欠損が発生していたとしても、酸化物半導体膜 633 の少なくともチャネル保護膜 634 と接する領域に酸素を供給し、ドナーとなる酸素欠損を低減して化学量論的組成比を満たす構成とすることが可能である。よって、チャネル形成領域を、i型化または実質的にi型化させることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性の向上を実現することができる。

#### 【0193】

なお、第2のトランジスタ 630 は、絶縁膜 637 上に、バックゲート電極をさらに有していても良い。バックゲート電極は、酸化物半導体膜 633 のチャネル形成領域と重なるように形成する。バックゲート電極は、電気的に絶縁しているフローティングの状態であっても良いし、電位が与えられる状態であっても良い。後者の場合、バックゲート電極には、ゲート電極 631 と同じ高さの電位が与えられていても良いし、グラウンドなどの固定電位が与えられていても良い。バックゲート電極に与える電位の高さを制御することで、第2のトランジスタ 630 の閾値電圧を制御することができる。

10

#### 【0194】

図12(B)に示すプログラム素子は、実施の形態4と同様に、結晶性シリコンを用いた第1のトランジスタ 501 と、第3のトランジスタ 502 を有している。そして、図12(B)では、第1のトランジスタ 501 と、第3のトランジスタ 502 上に、酸化物半導体膜を用いたボトムコンタクト型の第2のトランジスタ 640 が形成されている。

20

#### 【0195】

第2のトランジスタ 640 は、絶縁膜 507 上に形成されたゲート電極 641 と、ゲート電極 641 上のゲート絶縁膜 642 と、ゲート絶縁膜 642 上のソース電極 643、ドレイン電極 644 と、ゲート電極 641 と重なっている酸化物半導体膜 645 とを有する。さらに、第2のトランジスタ 640 は、酸化物半導体膜 645 上に形成された絶縁膜 646 を、その構成要素に含めてても良い。

#### 【0196】

また、図12(B)のタイプのボトムコンタクト型の第2のトランジスタ 640 の場合、ソース電極 643、ドレイン電極 644 の膜厚は、後に形成される酸化物半導体膜 645 が段切れを起こすのを防ぐために、実施の形態4で示したボトムゲート型に比べて薄くするのが望ましい。具体的には、10nm~200nm、好ましくは50nm~75nmとする。

30

#### 【0197】

なお、第2のトランジスタ 640 は、絶縁膜 646 上に、バックゲート電極をさらに有していても良い。バックゲート電極は、酸化物半導体膜 645 のチャネル形成領域と重なるように形成する。バックゲート電極は、電気的に絶縁しているフローティングの状態であっても良いし、電位が与えられる状態であっても良い。後者の場合、バックゲート電極には、ゲート電極 641 と同じ高さの電位が与えられていても良いし、グラウンドなどの固定電位が与えられていても良い。バックゲート電極に与える電位の高さを制御することで、第2のトランジスタ 640 の閾値電圧を制御することができる。

40

#### 【0198】

図12(C)に示すプログラム素子は、実施の形態4と同様に、結晶性シリコンを用いた第1のトランジスタ 501 と、第3のトランジスタ 502 を有している。そして、図12(C)では、第1のトランジスタ 501 と、第3のトランジスタ 502 上に、酸化物半導体膜を用いたトップゲート型の第2のトランジスタ 650 が形成されている。

#### 【0199】

第2のトランジスタ 650 は、絶縁膜 507 上に形成されたソース電極 651、ドレイン電極 652 と、ソース電極 651、ドレイン電極 652 上に形成された酸化物半導体膜 653 と、酸化物半導体膜 653 上のゲート絶縁膜 654 と、ゲート絶縁膜 654 上において酸化物半導体膜 653 と重なっているゲート電極 655 とを有する。さらに、第2のト

50

ランジスタ 650 は、ゲート電極 655 上に形成された絶縁膜 656 を、その構成要素に含めても良い。

#### 【0200】

また、図 12 (C) のタイプのトップゲート型の第 2 のトランジスタ 650 の場合、ソース電極 651、ドレイン電極 652 の膜厚は、後に形成される酸化物半導体膜 653 が段切れを起こすのを防ぐために、実施の形態 4 で示したボトムゲート型に比べて薄くするのが望ましい。具体的には、10 nm ~ 200 nm、好ましくは 50 nm ~ 75 nm とする。

#### 【0201】

本実施の形態は、上記実施の形態と組み合わせて実施することが可能である。

10

#### 【実施例 1】

#### 【0202】

本発明の一態様に係る半導体装置を用いることで、信頼性が高い電子機器、消費電力の低い電子機器を提供することが可能である。特に電力の供給を常時受けることが困難な携帯用の電子機器の場合、本発明の一態様に係る消費電力の低い半導体装置をその構成要素に追加することにより、連続使用時間が長くなるといったメリットが得られる。また、オフ電流が低いトランジスタを用いることで、オフ電流の高さをカバーするための冗長な回路設計が不要となるため、半導体装置に用いられている集積回路の集積度を高めることができ、半導体装置を高機能化させることができる。

#### 【0203】

20

本発明の一態様に係る半導体装置は、表示装置、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的には DVD : D i g i t a l V e r s a t i l e D i s c 等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図 17 に示す。

#### 【0204】

30

図 17 (A) は表示装置であり、筐体 7011、表示部 7012、支持台 7013 等を有する。本発明の一態様に係る半導体装置は、表示装置の駆動を制御するための集積回路に用いることができる。表示装置の駆動を制御するための集積回路に本発明の一態様に係る半導体装置を用いることで、信頼性が高い表示装置、消費電力の低い表示装置を提供することができる。なお、表示装置には、パーソナルコンピュータ用、TV 放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

#### 【0205】

図 17 (B) は携帯型ゲーム機であり、筐体 7031、筐体 7032、表示部 7033、表示部 7034、マイクロホン 7035、スピーカー 7036、操作キー 7037、スタイルス 7038 等を有する。本発明の一態様に係る半導体装置は、携帯型ゲーム機の駆動を制御するための集積回路に用いることができる。携帯型ゲーム機の駆動を制御するための集積回路に本発明の一態様に係る半導体装置を用いることで、信頼性が高い携帯型ゲーム機、消費電力の低い携帯型ゲーム機を提供することができる。なお、図 17 (B) に示した携帯型ゲーム機は、2 つの表示部 7033 と表示部 7034 とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

40

#### 【0206】

図 17 (C) は携帯電話であり、筐体 7041、表示部 7042、音声入力部 7043、音声出力部 7044、操作キー 7045、受光部 7046 等を有する。受光部 7046 において受信した光を電気信号に変換することで、外部の画像を取り込むことができる。本発明の一態様に係る半導体装置は、携帯電話の駆動を制御するための集積回路に用いるこ

50

とができる。携帯電話の駆動を制御するための集積回路に本発明の一態様に係る半導体装置を用いることで、信頼性が高い携帯電話、消費電力の低い携帯電話を提供することができる。

### 【0207】

図17(D)は携帯情報端末であり、筐体7051、表示部7052、操作キー7053等を有する。図17(D)に示す携帯情報端末は、モデムが筐体7051に内蔵されても良い。本発明の一態様に係る半導体装置は、携帯情報端末の駆動を制御するための集積回路に用いることができる。携帯情報端末の駆動を制御するための集積回路に本発明の一態様に係る半導体装置を用いることで、信頼性が高い携帯情報端末、消費電力の低い携帯情報端末を提供することができる。

10

### 【0208】

本実施例は、上記実施の形態と適宜組み合わせて実施することが可能である。

### 【符号の説明】

### 【0209】

|     |           |    |

|-----|-----------|----|

| 500 | 基板        |    |

| 501 | 第1のトランジスタ |    |

| 502 | 第3のトランジスタ |    |

| 503 | 単結晶シリコン膜  |    |

| 504 | 単結晶シリコン膜  |    |

| 505 | 絶縁膜       | 20 |

| 506 | 絶縁膜       |    |

| 507 | 絶縁膜       |    |

| 510 | ゲート電極     |    |

| 511 | ゲート電極     |    |

| 601 | ゲート電極     |    |

| 602 | 電極        |    |

| 603 | ゲート絶縁膜    |    |

| 605 | 酸化物半導体膜   |    |

| 606 | 不純物領域     |    |

| 607 | 不純物領域     | 30 |

| 608 | ソース電極     |    |

| 609 | ドレイン電極    |    |

| 610 | 配線        |    |

| 611 | 配線        |    |

| 612 | 配線        |    |

| 613 | 配線        |    |

| 614 | 絶縁膜       |    |

| 620 | 第2のトランジスタ |    |

| 623 | 容量素子      |    |

| 630 | 第2のトランジスタ | 40 |

| 631 | ゲート電極     |    |

| 632 | ゲート絶縁膜    |    |

| 633 | 酸化物半導体膜   |    |

| 634 | チャネル保護膜   |    |

| 635 | ソース電極     |    |

| 636 | ドレイン電極    |    |

| 637 | 絶縁膜       |    |

| 640 | 第2のトランジスタ |    |

| 641 | ゲート電極     |    |

| 642 | ゲート絶縁膜    | 50 |

|         |           |    |

|---------|-----------|----|

| 6 4 3   | ソース電極     |    |

| 6 4 4   | ドレイン電極    |    |

| 6 4 5   | 酸化物半導体膜   |    |

| 6 4 6   | 絶縁膜       |    |

| 6 5 0   | 第2のトランジスタ |    |

| 6 5 1   | ソース電極     |    |

| 6 5 2   | ドレイン電極    |    |

| 6 5 3   | 酸化物半導体膜   |    |

| 6 5 4   | ゲート絶縁膜    |    |

| 6 5 5   | ゲート電極     | 10 |

| 6 5 6   | 絶縁膜       |    |

| 8 0 1   | 第1のトランジスタ |    |

| 7 0 1 1 | 筐体        |    |

| 7 0 1 2 | 表示部       |    |

| 7 0 1 3 | 支持台       |    |

| 7 0 3 1 | 筐体        |    |

| 7 0 3 2 | 筐体        |    |

| 7 0 3 3 | 表示部       |    |

| 7 0 3 4 | 表示部       |    |

| 7 0 3 5 | マイクロホン    | 20 |

| 7 0 3 6 | スピーカー     |    |

| 7 0 3 7 | 操作キー      |    |

| 7 0 3 8 | スタイラス     |    |

| 7 0 4 1 | 筐体        |    |

| 7 0 4 2 | 表示部       |    |

| 7 0 4 3 | 音声入力部     |    |

| 7 0 4 4 | 音声出力部     |    |

| 7 0 4 5 | 操作キー      |    |

| 7 0 4 6 | 受光部       |    |

| 7 0 5 1 | 筐体        | 30 |

| 7 0 5 2 | 表示部       |    |

| 7 0 5 3 | 操作キー      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(56)参考文献 特許第5 8 5 5 2 1 5 ( J P , B 2 )

特開平0 1 - 1 3 0 3 9 0 ( J P , A )

特開平0 2 - 2 9 1 7 2 0 ( J P , A )

特開2 0 0 7 - 2 7 2 2 2 4 ( J P , A )

特許第5 6 6 0 9 0 2 ( J P , B 2 )

特開平0 9 - 0 7 4 3 5 1 ( J P , A )

特開2 0 0 9 - 0 4 2 6 6 4 ( J P , A )

特開2 0 0 6 - 3 1 3 9 9 9 ( J P , A )

特開2 0 0 7 - 1 2 3 8 6 1 ( J P , A )

(58)調査した分野(Int.Cl. , DB名)

H 0 3 K 1 9 / 1 7 7

G 0 9 G 3 / 3 0