(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5716702号

(P5716702)

(45) 発行日 平成27年5月13日(2015.5.13)

(24) 登録日 平成27年3月27日(2015.3.27)

(51) Int.Cl.

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

F 1

H01L 25/04

C

請求項の数 3 (全 16 頁)

(21) 出願番号 特願2012-96944 (P2012-96944)

(22) 出願日 平成24年4月20日 (2012.4.20)

(65) 公開番号 特開2013-225590 (P2013-225590A)

(43) 公開日 平成25年10月31日 (2013.10.31)

審査請求日 平成26年6月10日 (2014.6.10)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100082175

弁理士 高田 守

(74) 代理人 100106150

弁理士 高橋 英樹

(74) 代理人 100148057

弁理士 久野 淑己

(72) 発明者 王丸 武志

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 小山 和俊

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

制御信号が入力される制御端子並びに前記制御信号により電気的接続がオンオフされる第1端子及び第2端子を有する半導体スイッチング素子と、

一方の端子が前記第1端子と接続し他方の端子が前記第2端子と接続して前記半導体スイッチング素子に並列に接続した第1フリーホイールダイオードと、

一方の端子が前記第1端子と接続し他方の端子が前記第2端子と接続して前記半導体スイッチング素子に並列に接続し、同一の順方向電圧に対する順方向電流が前記第1フリーホイールダイオードよりも低い第2フリーホイールダイオードと、

を備え、

前記半導体スイッチング素子、前記第1フリーホイールダイオード、および前記第2フリーホイールダイオードが、それぞれ表面に電極を有し、

電気伝導性材料で形成され、前記半導体スイッチング素子の前記電極、前記第1フリーホイールダイオードの前記電極および前記第2フリーホイールダイオードの前記電極を接続し、前記第1フリーホイールダイオードの表面電極と接合する面積よりも前記第2フリーホイールダイオードの表面電極と接合する面積が大きい電極板を更に備える半導体装置。

## 【請求項 2】

制御信号が入力される制御端子並びに前記制御信号により電気的接続がオンオフされる第1端子及び第2端子を有する半導体スイッチング素子と、

10

20

一方の端子が前記第1端子と接続し他方の端子が前記第2端子と接続して前記半導体スイッチング素子に並列に接続した第1フリーホイールダイオードと、

一方の端子が前記第1端子と接続し他方の端子が前記第2端子と接続して前記半導体スイッチング素子に並列に接続し、同一の順方向電圧に対する順方向電流が前記第1フリー

ホイールダイオードよりも低い第2フリーホイールダイオードと、

前記半導体スイッチング素子、前記第1フリーホイールダイオード、および前記第2フ

リーホイールダイオードが接続される電極パターンと、

を備え、

前記第1フリーホイールダイオードが表面に第1電極を有し、前記第2フリーホイール

ダイオードが表面に第2電極を有し、前記半導体スイッチング素子が表面に第3電極を有

し、

電気伝導性材料で形成され、前記第1～3電極と接続する電極板を、更に備え、

前記電極板は、前記第1電極に接続する第1部分と前記電極パターンに接続する第2部

分とを有し、前記第1部分と前記第2部分の間に切り欠き部を有する半導体装置。

### 【請求項3】

請求項1または2に記載の半導体装置を有する電力変換装置であって、

前記半導体装置の前記半導体スイッチング素子は、IGBT、MOSFET又はバイポ

ーラトランジスタであり、

2つの前記半導体スイッチング素子が1組となってアーム回路を構成し、

前記アーム回路を1つ以上用いて構成したインバータ回路を備えることを特徴とする電

力変換装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置に関し、特に、半導体スイッチング素子とフリーホイールダイオードを備える半導体装置に関する。

#### 【背景技術】

#### 【0002】

従来、例えば、特開2000-311983号公報に開示されているように、パワー半導体素子およびフリーホイールダイオードを備える半導体装置が知られている。この種の半導体装置は、パワー半導体素子をスイッチング素子として用いる電力変換用の装置として用いられるのが一般的である。

#### 【0003】

上記公報にかかる半導体装置は、複数のパワー半導体素子が並列接続された並列回路を備えている。個々のパワー半導体素子には、それぞれ1つずつフリーホイールダイオードが設けられている。ここで、複数のパワー半導体素子の間で電気的特性のばらつきがあり、複数の並列回路間でインピーダンスの大きさに違いが生じたりすることがある。この場合、複数のパワー半導体素子の間に電流のアンバランスが生じてしまう。

#### 【0004】

そこで、上記従来の技術では、それぞれのフリーホイールダイオードに、バランス制御素子を設けている。このバランス制御素子は酸化物半導体を主材料とし、温度に応じて抵抗値が変化するものである。このバランス制御素子により、半導体素子が高温になった場合に、その半導体素子を含む回路のインピーダンスを高抵抗とすることができます。電流の大きさは半導体素子の発熱に大きく影響するので、上記のバランス制御素子によって電流が集中した回路を高抵抗とことができ、電流のアンバランスを抑制することができる。

#### 【先行技術文献】

#### 【特許文献】

#### 【0005】

【特許文献1】特開2000-311983号公報

10

20

30

40

50

【特許文献2】特開平8-191130号公報

【特許文献3】特開2010-87400号公報

【特許文献4】特開2003-60157号公報

【特許文献5】特開2005-261035号公報

【特許文献6】特開2000-209846号公報

【特許文献7】特開2005-6412号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

ところで、フリー・ホイール・ダイオードが、パワー半導体素子である半導体スイッチング素子ごとに複数個ずつ備えられる場合がある。その目的は、電流定格が比較的大きい場合や、搭載されるフリー・ホイール・ダイオードの熱抵抗を下げたい場合等がある。この場合、それぞれのフリー・ホイール・ダイオードの一方の端子が第1端子（例えばIGBTのコレクタ）と接続し、それぞれのフリー・ホイール・ダイオードの他方の端子が第2端子（例えばIGBTのエミッタ）と接続する。これにより、2つ以上のフリー・ホイール・ダイオードそれぞれが、半導体スイッチング素子に並列に接続される。10

**【0007】**

複数のフリー・ホイール・ダイオードの間でその電気的特性が一致することは稀であり、有る程度の電気的特性のばらつきが存在することが普通である。電気的特性とは、典型的には、電流電圧特性（I-V特性）である。すなわち、フリー・ホイール・ダイオードの順方向通電中の電流IFに対する、アノードカソード間電圧VFの特性である。上記のような1つの半導体スイッチング素子に複数のフリー・ホイール・ダイオードをそれぞれ並列接続する構成において、その複数のフリー・ホイール・ダイオード間に電気的特性のばらつきが存在するのが普通である。20

**【0008】**

このような電気的特性のばらつきにより、フリー・ホイール・ダイオード間での電流のばらつきが生じる。その電流ばらつきにより弊害が予想されるが、その代表的なものはフリー・ホイール・ダイオードの発熱アンバランスである。電流が流れるとフリー・ホイール・ダイオードは発熱するので、半導体装置の設計時には、その発熱を考慮に入れた設計（熱設計）を行う必要がある。しかしながら、上記のような電流アンバランスがあると、一部のフリー・ホイール・ダイオードに電流が相対的に多く流れてしまい、その一部のフリー・ホイール・ダイオードの発熱量が相対的に多くなってしまう。一般にフリー・ホイール・ダイオードの耐熱温度は定格で決められているので、半導体装置の使用中にそれら複数のフリー・ホイール・ダイオードのうち最も発熱量が大きいものが、その定格値以下であることが求められる。このような事情があるため、複数のフリー・ホイール・ダイオードを選定して半導体装置を設計するに当たり、最も発熱量が多いフリー・ホイール・ダイオードを基準とした熱設計を行わざるをえず、設計上の制約が大きかった。30

**【0009】**

本発明は、上述のような課題を解決するためになされたもので、半導体スイッチング素子ごとに接続した複数のフリー・ホイール・ダイオードにそれぞれ流れる電流の差を低減することができる半導体装置を提供することを目的とする。40

**【課題を解決するための手段】**

**【0010】**

第1の発明は、半導体装置であって、

制御信号が入力される制御端子並びに前記制御信号により電気的接続がオンオフされる第1端子及び第2端子を有する半導体スイッチング素子と、

一方の端子が前記第1端子と接続し他方の端子が前記第2端子と接続して前記半導体スイッチング素子に並列に接続した第1フリー・ホイール・ダイオードと、

一方の端子が前記第1端子と接続し他方の端子が前記第2端子と接続して前記半導体スイッチング素子に並列に接続し、同一の順方向電圧に対する順方向電流が前記第1フリー50

ホイールダイオードよりも低い第 2 フリー ホイールダイオードと、

を備え、

前記半導体スイッチング素子、前記第 1 フリー ホイールダイオード、および前記第 2 フリー ホイールダイオードが、それぞれ表面に電極を有し、

電気伝導性材料で形成され、前記半導体スイッチング素子の前記電極、前記第 1 フリー ホイールダイオードの前記電極および前記第 2 フリー ホイールダイオードの前記電極を接続し、前記第 1 フリー ホイールダイオードの表面電極と接合する面積よりも前記第 2 フリー ホイールダイオードの表面電極と接合する面積が大きい電極板を更に備える。

#### 【0011】

第 2 の発明は、半導体装置であって、

制御信号が入力される制御端子並びに前記制御信号により電気的接続がオンオフされる第 1 端子及び第 2 端子を有する半導体スイッチング素子と、

一方の端子が前記第 1 端子と接続し他方の端子が前記第 2 端子と接続して前記半導体スイッチング素子に並列に接続した第 1 フリー ホイールダイオードと、

一方の端子が前記第 1 端子と接続し他方の端子が前記第 2 端子と接続して前記半導体スイッチング素子に並列に接続し、同一の順方向電圧に対する順方向電流が前記第 1 フリー ホイールダイオードよりも低い第 2 フリー ホイールダイオードと、

前記半導体スイッチング素子、前記第 1 フリー ホイールダイオード、および前記第 2 フリー ホイールダイオードが接続される電極パターンと、

を備え、

前記第 1 フリー ホイールダイオードが表面に第 1 電極を有し、前記第 2 フリー ホイールダイオードが表面に第 2 電極を有し、前記半導体スイッチング素子が表面に第 3 電極を有し、

電気伝導性材料で形成され、前記第 1 ~ 3 電極と接続する電極板を、更に備え、

前記電極板は、前記第 1 電極に接続する第 1 部分と前記電極パターンに接続する第 2 部分とを有し、前記第 1 部分と前記第 2 部分の間に切り欠き部を有する。

#### 【発明の効果】

#### 【0012】

第 1 の発明によれば、半導体スイッチング素子に接続した複数のフリー ホイールダイオードにそれぞれ流れる電流の差を低減することができる。

#### 【0013】

第 2 の発明によれば、半導体スイッチング素子に接続した複数のフリー ホイールダイオードにそれぞれ流れる電流の差を低減することができる。

#### 【図面の簡単な説明】

#### 【0014】

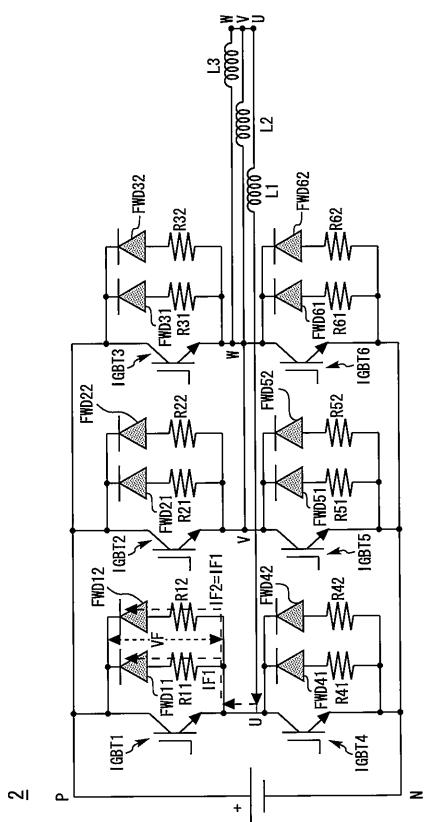

【図 1】フリー ホイールダイオードに流れる電流の差を低減した半導体装置の第 1 構成例としてのパワーモジュール 2 の回路図である。

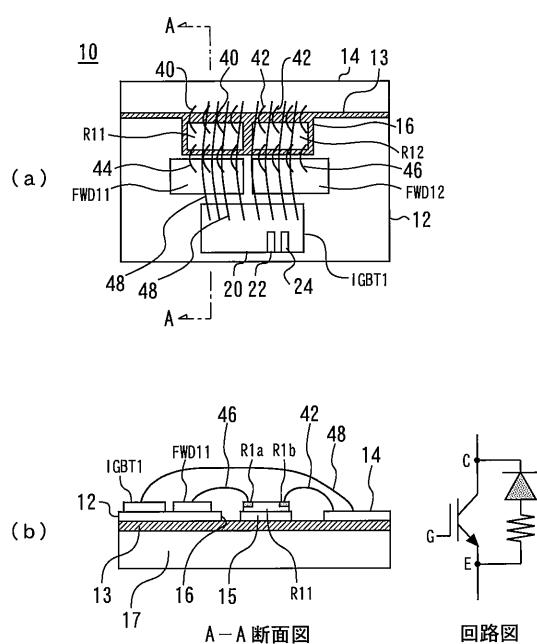

【図 2】パワーモジュール 2において、IGBT 1、FWD 11、FWD 12、R 11、および R 12 を実装した部分の構造を説明する為に、その実装部分を部分的に拡大した模式図である。

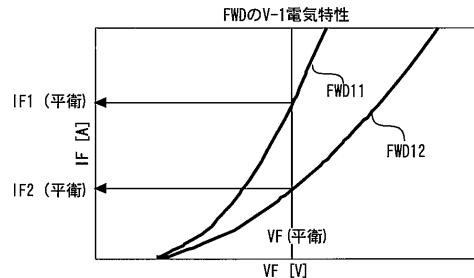

【図 3】パワーモジュール 2が有する FWD 11 および FWD 12 の電流電圧特性を示す図である。

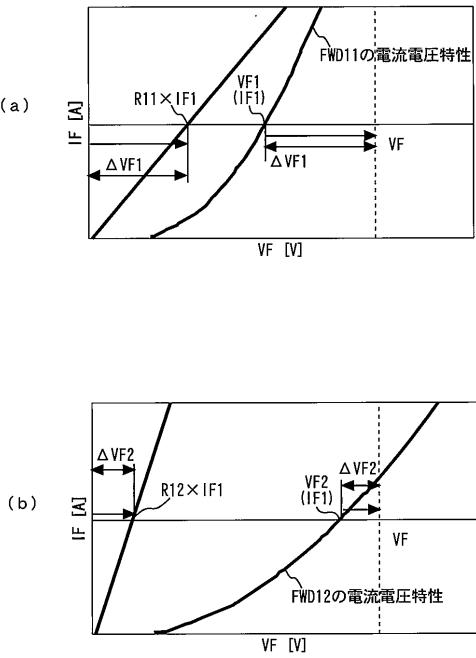

【図 4】パワーモジュール 2にかかる作用効果を説明するための図である。

【図 5】パワーモジュール 2に対する比較例としてのパワーモジュールのチップ実装部分 10 を示す平面図である。

【図 6】フリー ホイールダイオードに流れる電流の差を低減した半導体装置の第 1 構成例としてのパワーモジュールに搭載されるチップ実装部分 200 を示す平面図である。

【図 7】第 2 構成例にかかる半導体装置の変形例としてのパワーモジュールに搭載されるチップ実装部分 210 を示す平面図である。

【図 8】本発明の実施の形態 1にかかる半導体装置としてのパワーモジュールのチップ実

10

20

30

40

50

装部分 300 を示す平面図である。

【図9】本発明の実施の形態<sub>1</sub>に対する比較例としてのパワーモジュールのチップ実装部分 310 を示す平面図である。

【図10】本発明の実施の形態<sub>1</sub>にかかる半導体装置の変形例としてのパワーモジュールに搭載されるチップ実装部分 320 を示す平面図である。

【図11】第3構成例にかかる半導体装置としてのパワーモジュール402 の回路図である。

【図12】パワーモジュール402において実施されるスイッチング動作を示すタイムチャートである。

【発明を実施するための形態】

10

【0015】

フリーホイールダイオードに流れる電流の差を低減した半導体装置の第1構成例 .

[構成]

(回路構成)

図1は、フリーホイールダイオードに流れる電流の差を低減した半導体装置の第1構成例としてのパワーモジュール2の回路図である。パワーモジュール2は、W相、V相、U相を出力する3つのアーム回路を備えた三相インバータ回路を備えており、PN母線間これら3つのアーム回路が並列に接続された回路構成を備えている。

【0016】

20

パワーモジュール2は、6つの半導体スイッチング素子を備えており、半導体スイッチング素子として6個の絶縁ゲートバイポーラトランジスタ(IGBT1～IGBT6)を備えている。各IGBTは、制御信号が入力されるゲート端子、制御信号により電気的接続がオンオフされるエミッタ端子及びコレクタ端子を有するものであり、パワーモジュール2ではNPN-IGBTを用いるものとする。IGBTがオンオフするタイミングで、負荷電流がインダクタL1、L2、L3やFWD11、FWD12等に流れることによって、電力変換が実現される。

【0017】

30

なお、図示しないが、パワーモジュール2は、モールド樹脂によって樹脂封止されたトランシスファー-モールド型半導体パワーモジュールであるものとする。但し、ケース内に回路基板やIGBT、FWDを実装したうえで内部に樹脂を充填したケース型のパワーモジュールであってもよい。

【0018】

各IGBTには、それぞれ、2つのフリーホイールダイオード(以下、単にFWDとも称す)が設けられている。FWD11は、カソードがIGBT1のコレクタと接続し、アノードがIGBT1のエミッタと接続して、IGBT1と並列に接続している。FWD12も、同様に、カソードがIGBT1のコレクタと接続し、アノードがIGBT1のエミッタと接続して、IGBT1と並列に接続している。それぞれのFWDは、電流電圧特性を備えている。ある順方向電圧VFを基準とした時、FWD11は順方向電圧VFに対する順方向電流がIF1であり、その一方で、FWD12は順方向電圧VFに対する順方向電流がIF2である。IF2は、IF1よりも低い。この関係については図3を用いて後ほど説明する。便宜上、図1の回路図中にも、順方向電圧VFと、順方向電流IF1、IF2を模式的に図示している。

40

【0019】

パワーモジュール2は合計で6つのIGBTを備えており、IGBTごとに2つずつFWDを備えている。これらのFWDには電気的特性のばらつきが存在するのが普通であり、パワーモジュール2においてもそのような電気的特性のばらつきが存在するものとする。但し、説明の便宜上、FWD11、FWD21、FWD31、FWD41、FWD51およびFWD61を第一群のFWDとも称する。また、FWD12、FWD22、FWD32、FWD42、FWD52およびFWD62を第二群のFWDとも称する。このように2つのグループに分けて、第一群のFWD同士は実質的に同じ電気的特性(電流電圧特

50

性)を備えるものとし、第二群のFWD同士も実質的に同じ電気的特性(電流電圧特性)を備えるものとする。そして、前述したFWD11とFWD12の間の電流電圧特性の関係(VFにおいて、IF2がIF1より低いという関係)が、第一群のFWDと第二群のFWDとの間で成り立つものとする。例えば、FWD21とFWD22との間には、FWD11とFWD12と同様の関係が成り立つものとする。

#### 【0020】

(抵抗R11およびR12)

パワーモジュール2は、FWD11とIGBT1とを結ぶ回路における電気抵抗が、FWD12とIGBT1とを結ぶ回路における電気抵抗よりも、高いという特徴を有している。つまり、FWD11を介してIGBT1のエミッタ端子とコレクタ端子とを結ぶ経路の電気抵抗(FWD11側経路の電気抵抗)と、FWD12を介してIGBT1のエミッタ端子とコレクタ端子とを結ぶ経路の電気抵抗(FWD12側経路の電気抵抗)とを比較すると、FWD11側経路の電気抵抗のほうがFWD12側経路の電気抵抗よりも高い。

10

#### 【0021】

パワーモジュール2におけるより具体的な回路構成を述べると、パワーモジュール2は、抵抗であるR11およびR12を備えている。R11は、FWD11とIGBT1とを結ぶ回路中において、FWD11と直列に接続されている。R12は、FWD12とIGBT1とを結ぶ回路中においてFWD12と直列に接続されている。R12は、R11の抵抗値よりも低い抵抗値を有するものである。

#### 【0022】

(チップ実装部分10)

図2は、パワーモジュール2において、IGBT1、FWD11、FWD12、R11、およびR12を実装した部分の構造を説明する為に、その実装部分を部分的に拡大した模式図である。実装部分を、便宜上チップ実装部分10と称す。

20

#### 【0023】

なお、チップ実装部分10はIGBT1に関する実装部分であるが、IGBT2~6についても、FWD21~FWD62およびR21~R62が同様の構造で実装されているものとする。

#### 【0024】

図2(a)は、パワーモジュール2の平面図である。図2(b)は、図2(a)のA-A線に沿う断面図およびその回路図である。チップ実装部分10は、電極パターン12、電極パターン14、および電極パターン15を備えている。図2(a)(b)の比較からもわかるように、電極パターン12、14、15は、いずれも絶縁板13上に設けられており、切り欠き部16で互いに絶縁されている。電極パターン12、14、15は、銅またはアルミで形成されることが好ましい。パワーモジュール2は、放熱板17を備えている。放熱板17には絶縁板13が取り付けられており、絶縁板13上には電極パターン12、14、15が設けられ、その電極パターン12、14、15上にIGBT1、FWD11、FWD12、R11、R12が半田付けで固定されている。電極パターン12は、その表面にIGBT1の裏面電極(コレクタ電極)並びにFWD11およびFWD12の裏面電極(カソード電極)が固定される。電極パターン15は、電極パターン12の隣に配置され、電極パターン12と電気的に分離されている。電極パターン15は、電気的に分離された2つの電極パターンからなり、それぞれの上に抵抗R11およびR12が実装されている。抵抗R11、R12は、チップ抵抗であり、それぞれが端子R1a、R1bを有し、各端子R1aとR1bにワイヤ46、42の一端が接続されている。

30

#### 【0025】

IGBT1、FWD11およびR11は、複数本のワイヤでボンディングされることにより電気的に接続されている。ワイヤの材料は、銅またはアルミであることが好ましい。ワイヤ48は、IGBTのエミッタ電極20と、電極パターン14とを電気的に接続する。ワイヤ42は、R11の端子R1bと電極パターン14とを電気的に接続する。ワイヤ46は、FWD11の表面電極(アノード電極)とR11の端子R1aとを接続する。こ

40

50

のような接続関係により、図2(b)の回路図に示すように、R11が、FWD11とIGBT1とを結ぶ回路中においてFWD11と直列に接続される。同様のワイヤ接続がR12についても施されている。また、抵抗R11およびR12を電極パターン15に半田付けすることにより、放熱経路を確保し、効率的に抵抗R11およびR12を冷却することができる。

#### 【0026】

##### [パワーモジュール2にかかる作用効果]

パワーモジュール2では、図1の様に、FWD11とR11の直列回路と、FWD12とR12の直列回路とが、IGBT1に対してそれぞれ並列に接続している。FWD11とFWD12の通電時には、「FWD11の順電圧降下VFの値と抵抗R11の両端に発生する電圧降下の値との和」が、「FWD12の順電圧降下VFの値と抵抗R12の両端に発生する電圧降下の値との和」と一致する。

10

#### 【0027】

FWD11とFWD12の各々の電流電圧特性が異なる場合には、仮にR11とR12の抵抗値が無作為で異なっている場合には、各々の通電電流が異なる。通電電流が異なると、FWD11とFWD12の発熱量も異なる。パワーモジュール2では、この点に対処するために、下記のように抵抗値を定めた抵抗R11、R12をパワーモジュール2に設けることとした。

#### 【0028】

第1構成例では、予めFWD11とFWD12の電流電圧特性を判別しておくものとする。図3は、パワーモジュール2が有するFWD11およびFWD12の電流電圧特性を示す図であり、平衡時の値を図示している。

20

ここで、仮にFWD11およびFWD12とが抵抗R11および抵抗R12を有さずに並列接続された場合には、並列接続の電気的特性からそれら2つのFWDの順方向電圧VFの値は一致する。一方、それら2つのFWDの各々の順方向電流IF(つまりIF1, IF2)は、各FWDの電流電圧特性に従って順方向電圧VFに応じた電流値となる。このとき、FWD11とFWD12の電流電圧特性が異なることに起因してIF1とIF2が相違し、その相違した電流で平衡状態となる。

通電電流IF1に対する順方向電圧VFを比べた場合に、FWD11の順方向電圧は、FWD12の順方向電圧よりも低い。そこで、FWD11には抵抗R11を直列接続する。また、FWD12には、R11よりも低い抵抗値の抵抗R12を直列接続する。このように抵抗R11とR12を挿入することで、2つの異なる電流値を一致させることができとなる。

30

#### 【0029】

特に、パワーモジュール2では、下記に述べる式(1)の関係を成立させることで、FWD11とFWD12とに流れる電流の大きさを一致させることができる。この一致した電流を、便宜上、一致電流IF1とも称す。R11にIF1が、R12にIF2がそれぞれ流れるが、パワーモジュール2では抵抗R11およびR12の抵抗値を適切に選定することで、IF2がIF1と一致することとなる。

#### 【0030】

具体的には、R11の抵抗値およびR12の抵抗値を、下記の関係を有するように設計する。

$$VF = VF_1(IF_1) + R_{11} \times IF_1 = VF_2(IF_1) + R_{12} \times IF_1 \dots (1)$$

VF1は、FWD11の電流電圧特性において、順方向電流(通電電流)IF1の値に応じたFWD11の順方向電圧値を意味している。R11 × IF1は、順方向電流IF1にR11の抵抗値を乗じて求めた電圧値である。これらの和(第1の和)が、VFと一致する。

また、VF2(IF1)は、FWD12の電流電圧特性において、順方向電流値IF1

2 = IF1に応じたFWD12の順方向電圧値を意味している。これらの和(第2の和)

50

も、VFと一致する。つまり、R11とR12の値は、上記第1の和と第2の和とを等しくする値である。

#### 【0031】

仮にIF1 = 100A、VF = 2V、VF1(IF1) = 1.5V、VF2(IF1) = 1.8Vとする。

この場合には、

$$R11 \times 100A = 0.5V, R12 \times 100A = 0.2V \text{ である。}$$

従って、R11 = 5m、R12 = 2m をそれぞれ選択すればよい。

#### 【0032】

図4は、パワーモジュール2の作用効果を説明するための図である。図4(a)には、

10 FWD11の電流電圧特性およびR11の電流電圧特性を記載し、図4(b)には、FWD12の電流電圧特性およびR12の電流電圧特性を記載している。FWD11に関しては、ある順方向電圧VFに対して、通電電流IF1のときの順方向電圧値はVF1(IF1)である。一方、FWD12に関しては、同じ順方向電圧VFに対して、通電電流IF1のときの順方向電圧値はVF2(IF1)である。VF1(IF1)とVFの差と、R11 × IF1による電圧降下の大きさ VF1とを一致させるとともに、VF2(IF1)とVFの差と、R12 × IF1による電圧降下の大きさ VF2とを一致させる。こうすることで、FWD11とR11の直列回路において、通電電流IFが流れるとともに電圧降下の合計はVFとなる。FWD12とR12の直列回路においても、同様に、通電電流IFが流れるとともに電圧降下の合計はVFとなる。このように、パワーモジュール2

20 によれば、FWD11とFWD12に同じ大きさの通電電流を流すことができる。

#### 【0033】

なお、図4に示すように、実際には、抵抗R11、R12の電流電圧特性は線形である。これに対し、FWD11、12の電流電圧特性は非線形である。従って、FWD11とFWD12双方の通電電流を、すべての通電領域において電流IF1で一致させることができるわけではない。しかしながら、この場合においても、パワーモジュール2の最大定格電流値を電流IF1として、R11およびR12の抵抗値を設定すればよい。なぜなら、パワーモジュール2の熱設計を行うにあたっては、最も発熱が大きい定格電流値において、FWDがその耐熱温度以下となるように設計を行わなければならないからである。

#### 【0034】

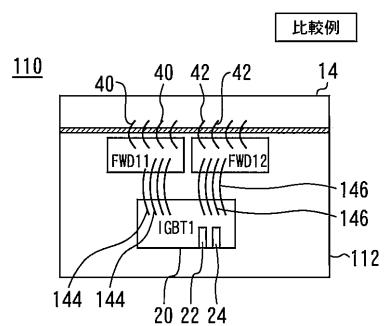

##### [比較例]

図5は、パワーモジュール2に対する比較例としてのパワーモジュールのチップ実装部分110を示す平面図である。比較例であるチップ実装部分110は、R11およびR12を備えておらず、切り欠き部16も備えていない。電極パターン112にFWD11、12およびIGBT1が半田付けされるとともに、FWD11のアノード電極とIGBT1のエミッタ電極20とをワイヤ144、146が接続している。このような構成においては、FWD11とFWD12の電流電圧特性のばらつきがそのままIF1、IF2の大きさに反映されてしまう。その結果、FWD11とFWD12の通電電流の大きさが異なり、発熱量も異なるという問題がある。

#### 【0035】

すなわち、電流定格が比較的大きい場合(例えば定格電流100A以上)や、搭載されるFWDの熱抵抗を下げたい場合には、1相あたり2個以上の複数個FWDを並列接続する構成が考えられる。これが図5の比較例の構成である。FWDを複数個並列接続することで、より多くの電流を流せるようにしたり、また熱抵抗を下げるによってFWDの発熱温度(Tj)を下げてFWDの耐熱温度(例えばシリコン系FWDであれば最大150)に対するマージン確保と信頼性を向上させることができる。

#### 【0036】

しかし、複数個のFWDを単純に並列接続した場合には、搭載されるFWDの電流電圧特性(FWDの順方向通電時の通電電流IFに対するアノードカソード間電圧VF)のばらつきにより、並列接続されたFWDは各々異なる電流が流れる。その理由は、FWDの

50

両端電圧（アノードカソード間電圧）は並列接続のためにどのFWDも同じであるが、電流電圧特性が異なればあるFWDよりも他のFWDに多くのIF電流が流れるという事態が生ずる。従って、IF電流が一番多く流れるFWDの発熱量がより多くなってしまう。

#### 【0037】

FWDの耐熱温度は定格によって決められており、並列接続されたFWDの中で最も発熱の大きいものがその耐熱温度以下でなければならない。そこで、パワーモジュールの設計では、FWDの電流電圧特性の最大ばらつきを計算から求め、この最大ばらつきから予測したFWD最高発熱温度が耐熱温度以下となるように設計を行うことが考えられる。なお、FWDの耐熱温度は、例えばシリコン系FWDであれば最大150°C程度である。予測したFWD最高発熱温度が耐熱温度以下となるように設計を行う場合には、並列接続されたFWDがどれも均一に発熱する場合に比べて、最も高い発熱が生ずるFWDの発熱量を下げるために、より大きなサイズのFWDを選択する必要が生じてしまう。大きなサイズのFWDを選択する理由は、FWDのサイズを大きくすることで相対的な電流密度が下がるため、電流電圧特性の順方向電圧値VFが下がることで損失が小さくなるからである。また、熱抵抗もFWDのチップサイズに反比例して小さくなることから、FWDとしての発熱を小さくすることができるためである。しかしFWDのサイズを大きくすることは、パワーモジュールの体格を大きくせざるをえず、またFWDを含むパワーモジュールの高コスト化も招いてしまう。10

#### 【0038】

この点、パワーモジュール2によれば、FWD11、FWD12について電流アンバランスを抑制するように抵抗値を選定したR11、R12を設け、これと同様にFWD21～FWD62についてもそれぞれ適切な抵抗値を選定した抵抗を設けている。これにより、発熱アンバランスを抑制することができ、上記のようなパワーモジュールの熱設計上の問題を抑制することができる。20

#### 【0039】

##### [パワーモジュール2の変形例]

IGBTに代えて、パワーMOSFETやバイポーラトランジスタ等の半導体スイッチング素子を用いても良い。

#### 【0040】

パワーモジュール2では、図1の回路図に示すとおり、IGBT1のエミッタとFWD11、FWD12のアノードとの間に、抵抗R11、R12がそれぞれ直列に挿入されている。しかしながら本発明はこれに限られず、IGBT1のコレクタとFWD11、FWD12のカソードとの間に、抵抗を直列に挿入してもよい。30

#### 【0041】

パワーモジュール2は2つのFWDの組の両方にFWDを設けたが、これとは異なり2つのFWDの組のうち片方のみに抵抗を設けてもよい。つまり、第一群のFWDに対してのみ直列に抵抗を挿入しても良い。具体的には、例えばIGBT1について、FWD11にのみ直列にR11が挿入され、FWD12には抵抗の挿入がされていなくともよい。IGBT2～IGBT6についても同様に、FWD21、31、41、51、および61にのみ抵抗R21等が挿入されていてもよい。この点を除き、パワーモジュール2と同様の構成を備えるようにしてもよい。このような構成でも、2つのFWD（例えばFWD11とFWD12）の間の電流アンバランスを抑制するように、抵抗を挿入することができる。ただし、電流電圧特性において、同じ順方向電流のときに順方向電圧が小さい側のFWD（例えばFWD11とFWD12のうちFWD11）に対して、抵抗を挿入するものとする。40

#### 【0042】

##### フリーホイールダイオードに流れる電流の差を低減した半導体装置の第2構成例。

##### [構成]

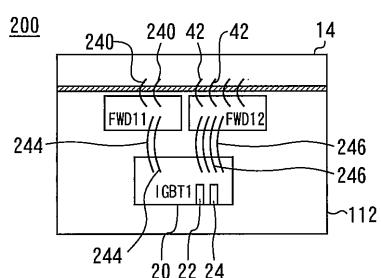

図6は、フリーホイールダイオードに流れる電流の差を低減した半導体装置の第2構成例にかかる半導体装置としてのパワーモジュールに搭載されるチップ実装部分200を示す。

10

20

30

40

50

す平面図である。第2構成例にかかるパワーモジュールは、チップ実装部分10に代えて、チップ実装部分200を備えている点を除き、上述したパワーモジュール2と同様の構成を備えている。

#### 【0043】

このチップ実装部分200は、R11およびR12を備えておらず、切り欠き部16も備えていない点で、上述した第1構成例にかかるチップ実装部分10と相違するとともに、上記の図5の比較例と共に通している。しかしながら、下記の(2-1)および(2-2)に示す特徴的構成を備えている。

(2-1) FWD11と電極パターン14とを接続するワイヤ240の本数が、FWD12と電極パターン14とを接続するワイヤ42の本数よりも少ない。例えばワイヤ240を2本とし、ワイヤ42を4本とする。ワイヤ240とワイヤ42の太さおよび長さは同じとする。

(2-2) FWD11とIGBT1のエミッタ電極20とを接続するワイヤ244の本数が、FWD12とIGBT1のエミッタ電極20とを接続するワイヤ246の本数よりも少ない。例えばワイヤ244を2本とし、ワイヤ246を4本とする。ワイヤ244とワイヤ246の太さおよび長さは同じとする。

#### 【0044】

このような構成においては、FWD11とFWD12との間で、ワイヤが持つ抵抗成分において差を設けることができる。つまり、ボンディングワイヤは金属ではあるものの抵抗値を持っており、ワイヤの抵抗値は抵抗体の長さに比例し、かつ断面積に反比例する。よってワイヤ本数を増やすほど抵抗値が小さくなる。ワイヤ246は、ワイヤ244よりも本数が多くされており、その結果、R12の抵抗値をR11の抵抗値よりも小さくすることができる。なお、第2構成例においては、図1の回路図上において、抵抗R11がワイヤ244であり、抵抗R12がワイヤ246である。

#### 【0045】

ボンディングワイヤの本数を、第1構成例で述べた式(1)を満たすR11、R12が得られるように選定することによって、第1構成例と同様に、FWD11とFWD12の通電電流を均等にすることができます。

#### 【0046】

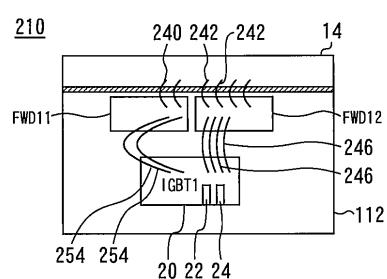

##### [変形例]

図7は、第2構成例にかかる半導体装置の変形例としてのパワーモジュールに搭載されるチップ実装部分210を示す平面図である。ワイヤの抵抗値は抵抗体の長さに比例し、かつ断面積に反比例する。そこで、この変形例では、ワイヤ254をワイヤ246よりも長くして、抵抗値を調節することとした。このような構成によってボンディングワイヤの長さを、式(1)を満たすR11、R12が得られるように選定する。その結果、第1構成例と同様に、FWD11とFWD12の通電電流を均等にすることができます。なお、本変形例ではワイヤの長さ及び本数に差を設けたが、ワイヤの長さのみに差を設けても良い。

#### 【0047】

##### 実施の形態1.

##### [実施の形態1の構成]

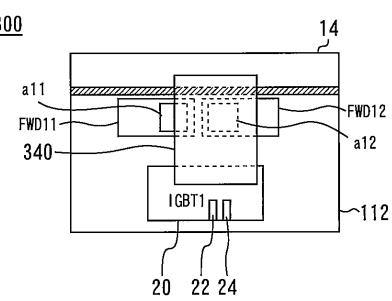

図8は、本発明の実施の形態1にかかる半導体装置としてのパワーモジュールのチップ実装部分300を示す平面図である。実施の形態1にかかるパワーモジュールは、チップ実装部分10に代えて、チップ実装部分300を備えている点を除き、第1構成例にかかるパワーモジュール2と同様の構成を備えている。

#### 【0048】

チップ実装部分300において、電極板であるリードフレーム340が備えられている。リードフレーム340は、電気伝導性材料で形成され、好ましくはアルミニウム又は銅で形成される。リードフレーム340は、IGBT1のエミッタ電極20、FWD11のアノード電極およびFWD12のアノード電極を接続する。リードフレーム340は、FWD1

10

20

30

40

50

1の表面のアノード電極a11と接合する面積よりも、FWD12の表面のアノード電極a12と接合する面積のほうが大きい。つまり、FWD12側の電気抵抗が相対的に低くされている。

#### 【0049】

このような構成においては、FWD11とFWD12との間で、リードフレーム340との電極接触面積において差を設けることができる。つまり、FWD11、12、リードフレーム340およびIGBT1のエミッタ電極20へ至る経路中の電気抵抗値は、リードフレーム340の電極接触面積と相関を有しており、電極接触面積が大きいほど抵抗値が小さくなる。実施の形態1においては、図1の回路図上において、リードフレーム340との電極接触面積の違いによって、抵抗R11と抵抗R12の抵抗値の相違を生じさせることができる。なお、実施の形態1によれば、リードフレーム340を図8紙面左右方向にずらす量は、連続的に変化させることができるとため、ワイヤ本数の変更と比べて連続的な微調整が可能である。また、リードフレーム340とIGBT1との間の接触面積は、リードフレーム340を左右にずらしても均一に保つことができる。さらに、リードフレーム340は平面形状の電極板であり、その取り付け位置をずらすだけで足りるので、個別に複数の形状のリードフレームを準備する必要も無い。

#### 【0050】

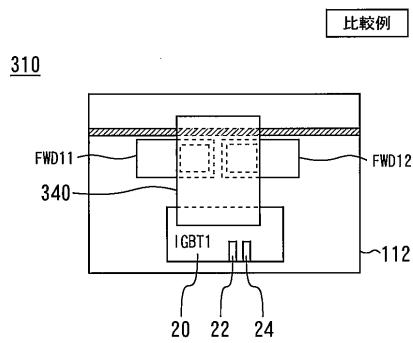

##### [比較例]

図9は、本発明の実施の形態1に対する比較例としてのパワーモジュールのチップ実装部分310を示す平面図である。比較例では、リードフレーム340が、FWD11のアノード電極a11とFWD12のアノード電極a12の両方に、全面接触をしている。このような構成においては、FWD11とFWD12の電流電圧特性のばらつきがそのままIF1、IF2の大きさに反映されてしまう。その結果、FWD11とFWD12の通電電流の大きさが異なり、発熱量も異なるという問題がある。

#### 【0051】

##### [実施の形態1の変形例]

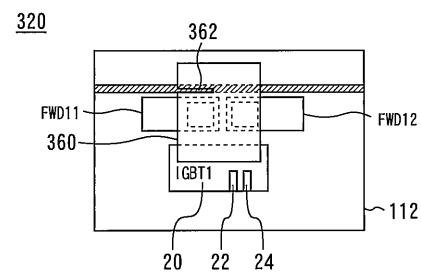

図10は、本発明の実施の形態1にかかる半導体装置の変形例としてのパワーモジュールに搭載されるチップ実装部分320を示す平面図である。チップ実装部分320は、リードフレーム360を有している。リードフレーム360は、FWD11側に切り欠き部362を有している。このようなスリット状の切り欠き部362を設けることで、切り欠き部362を設けたFWD11側の電気抵抗値を、相対的に高くすることができる。なお、切り欠き(スリット)の幅を微小幅で管理することで、抵抗値の微調整が可能となる。

#### 【0052】

##### 切替え可能なスイッチング素子を設けた第3構成例

##### [構成]

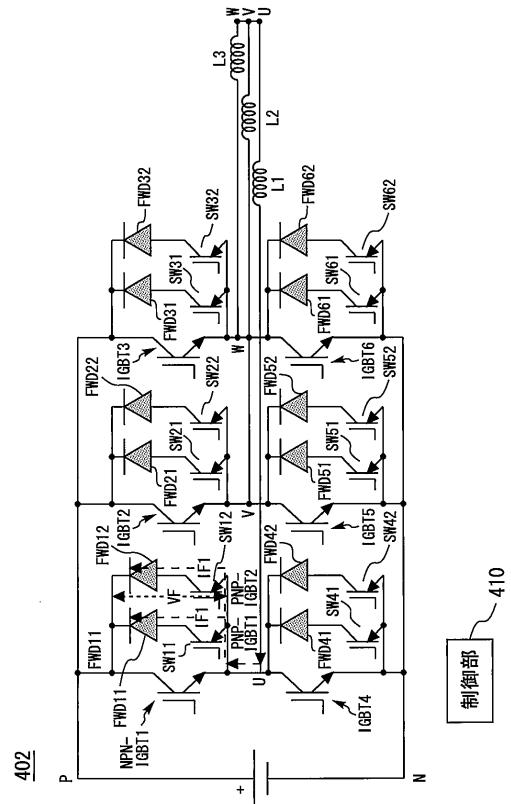

図11は、切替え可能なスイッチング素子を設けた第3構成例にかかる半導体装置としてのパワーモジュール402の回路図である。パワーモジュール402は、抵抗R11、R12、R21、R22、R31、R32、R41、R42、R51、R52、R61、およびR62に代えて、以下に述べる半導体スイッチング素子SW11、SW12、SW21、SW22、SW31、SW32、SW41、SW42、SW51、SW52、SW61、およびSW62を備えている。これらの半導体スイッチング素子SW11等は、いずれもPNP型のIGBTである。また、IGBT1～IGBT6は、いずれも、NPN型のIGBTであるものとする。この点を除き、パワーモジュール402は、パワーモジュール2と同様の構成を備えるものとする。

#### 【0053】

パワーモジュール402には、制御部410が接続される。制御部410は、後述する図12におけるタイムチャートに従って、半導体スイッチング素子SW11、SW12等をオンオフすることができるようにプログラムされている。

#### 【0054】

IGBT1～IGBT6は、それぞれ、制御信号が入力されるゲート端子、並びにその

10

20

30

40

50

制御信号により電気的接続がオンオフされるエミッタ端子及びコレクタ端子を有している。IGBT1～IGBT6には、FWDが2つずつ設けられている。それぞれのFWDは、一方の端子がエミッタ端子と接続し他方の端子がコレクタ端子と接続して、各々のIGBT1～IGBT6に2つずつ、並列に接続している。

#### 【0055】

前述したように、パワーモジュール402は、複数の半導体スイッチング素子SW11～SW62を備えている。図11の回路図からも明らかな通り、各半導体スイッチング素子SW11～SW62は、複数個のフリーホイールダイオードFWD11～FWD62が逐一的にIGBT1～IGBT6と並列接続するように、FWDのそれぞれとIGBT1～IGBT6とを結ぶ回路を切り替えることができる。つまり、例えばIGBT1について言えば、SW11とSW12とを逐一的にオンとすることで、IGBT1に対してFWD11とFWD12のいずれか一方を逐一的に並列接続させることができる。10

#### 【0056】

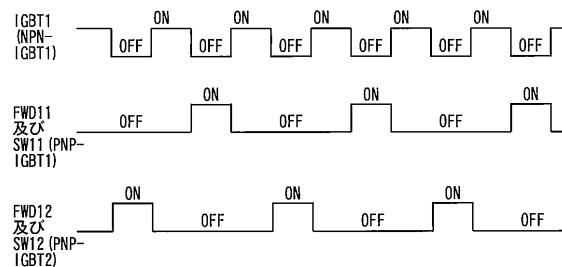

図12は、パワーモジュール402において実施されるスイッチング動作を示すタイムチャートである。制御部410は、このタイムチャートに従って、各IGBT1～IGBT6およびスイッチング素子SW11～SW62をオンオフ制御する。これにより、IGBT1～IGBT6のスイッチング動作ごとに異なるフリーホイールダイオードで電流を流すように、SW11～SW62を制御する。

#### 【0057】

すなわち、異なる電流電圧特性を持つFWDを2つ以上並列接続したときに電流アンバランスが生じるのは、それら2つのFWDの両方に一度に電流が流れるからである。そこで、IGBT1における一回のスイッチング動作に応じてFWD11とFWD12の片方のみをオンさせるようにし、FWD11とFWD12を交互にオンするようにすれば、平均的にはFWDに流れる通電電流を均等にすることができる。具体的には、図12のタイムチャートを用いて説明すると、IGBT1の一回目のオフ動作のときにはFWD12で電流を流すようにSW12をオンとする。一方、IGBT1の二回目のオフ動作のときにはFWD11で電流を流すようにSW11をオンとする。これを交互に繰り返していく、つまりSW11とSW12とをデューティ比50%で駆動させるようにする。これによりFWD11とFWD12の平均電流は同じ値となる。その結果、第1構成例と同様に、FWDの発熱アンバランスを抑制し、熱設計の容易化、最適化が図れる。2030

#### 【符号の説明】

#### 【0058】

2、402 パワーモジュール

10、200、210、300、310、320 チップ実装部分

12 電極パターン

13 絶縁板

14 電極パターン

15 電極パターン

16 切り欠き部

17 放熱板

20 エミッタ電極

42、46、48、144、240、244、246、254 ワイヤ

112 電極パターン

340、360 リードフレーム

362 切り欠き部

410 制御部

a11、a12 アノード電極

FWD11～FWD62 フリーホイールダイオード

IF1 順方向電流

IGBT1～IGBT6 絶縁ゲートバイポーラトランジスタ

20

30

40

50

L 1、L 2、L 3 インダクタ

R 1 1 抵抗

R 1 2 抵抗

R 1 a 端子

R 1 b 端子

S W 1 1 ~ S W 6 2 半導体スイッチング素子 (P N P - I G B T )

V F 順方向電圧

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

---

フロントページの続き

(56)参考文献 特開2012-050176(JP,A)

特開2002-064180(JP,A)

特開2008-187151(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/07

H01L 25/18