(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 602 24 847 T2 2009.02.05

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 488 463 B1

(51) Int Cl.<sup>8</sup>: H01L 29/786 (2006.01)

(21) Deutsches Aktenzeichen: 602 24 847.7

(86) PCT-Aktenzeichen: PCT/US02/40398

(96) Europäisches Aktenzeichen: 02 797 394.0

(87) PCT-Veröffentlichungs-Nr.: WO 2003/081677

(86) PCT-Anmeldetag: 17.12.2002

(87) Veröffentlichungstag

der PCT-Anmeldung: 02.10.2003

(97) Erstveröffentlichung durch das EPA: 22.12.2004

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 23.01.2008

(47) Veröffentlichungstag im Patentblatt: 05.02.2009

(30) Unionspriorität:

104939 21.03.2002 US

(84) Benannte Vertragsstaaten:

DE, FR, GB

(73) Patentinhaber:

Advanced Micro Devices Inc., Sunnyvale, Calif.,

US

(72) Erfinder:

WEI, Andy C., M/S 626 Austin TX 78741, US;

WRISTERS, Derick J., Bee Caves, TX 78738, US;

FUSELIER, Mark B., Austin, TX 78748, US

(74) Vertreter:

Grünecker, Kinkeldey, Stockmair &

Schwanhäusser, 80802 München

(54) Bezeichnung: VORGESPANNTE, TOTAL VERARMTE DREIFACH-WANNEN-SOI-STRUKTUR UND VERSCHIEDENE VERFAHREN ZUR HERSTELLUNG UND FUNKTION DERSELBEN

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung**

## Technisches Gebiet

**[0001]** Diese Erfindung betrifft im Allgemeinen die Halbleiterfertigungstechnologie und betrifft insbesondere eine vorgespannte vollständig verarmte SOI-Struktur mit Dreifach-Wanne und diverse Verfahren zur Herstellung und Betreiben derselben.

## Hintergrund der Erfindung

**[0002]** US-A-5 923 067 offenbart eine dreidimensionale elektrostatische Entladungs-(ESD)CMOS-Struktur auf einem Silizium-auf-Isolator-(SOI)Substrat und ein entsprechendes Verfahren. Das Bauteil umfasst einen Transistor, der über einem SOI-Substrat ausgebildet ist, das eine erste Wanne und eine zweite Wanne aufweist, die in dem Vollsubstrat ausgebildet sind, wobei entsprechende elektrische Kontakte zu den Wannen gemäß dem Oberbegriff des begleitenden Anspruchs 1 vorhanden sind.

**[0003]** Es gibt ein ständiges Bestreben in der Halbleiterindustrie, die Arbeitsgeschwindigkeit integrierter Schaltungsbaulemente, beispielsweise von Mikroprozessoren, Speicherbauelementen und dergleichen zu erhöhen. Dieses Bestreben wird noch durch die Verbrauchernachfrage nach Computern und elektronischen Geräten gefördert, die bei zunehmend größeren Geschwindigkeiten betrieben werden können. Diese Nachfrage nach einer höheren Arbeitsgeschwindigkeit führte zu einer ständigen Verringerung der Größe von Halbleiterbauelementen, beispielsweise von Transistoren. Das heißt, viele Komponenten eines typischen Feldeffekttransistors (FET), beispielsweise die Kanallänge, die Tiefe der PN-Übergänge, die Gate-Isolationsdicke und dergleichen, werden verringert. Wenn beispielsweise alle anderen Faktoren gleich sind, arbeitet ein Transistor mit einer kleineren Kanallänge schneller. Somit gibt es ein ständiges Bestreben, die Größe oder das Maß der Komponenten eines typischen Transistors zu verringern, um damit die Gesamtarbeitsgeschwindigkeit des Transistors, sowie von integrierten Schaltungen, in denen die derartige Transistoren eingebaut sind, zu erhöhen.

**[0004]** Wenn die Transistoren ständig in ihrer Größe verringert werden in dem Bestreben, den Erfordernissen moderner Technologie Rechnung zu tragen, schreibt die Bauteilzuverlässigkeit vor, dass eine entsprechende Verringerung der Versorgungsspannung vorzusehen ist. Folglich steht jede weitere Technologiegeneration häufig im Zusammenhang mit einer Verringerung der Betriebsspannung des Transistors. Es ist bekannt, dass Transistorbauelemente, die auf Silizium-auf-Isolator-(SOI)Substraten hergestellt sind, ein besseres Leistungsverhalten bei geringeren

Betriebsspannungen im Vergleich zu Transistoren mit ähnlichen Abmessungen zeigen, die in Silizium-Vollsubstraten hergestellt sind. Das verbesserte Leistungsverhalten von SOI-Bauelementen bei einer geringen Betriebsspannung steht im Zusammenhang mit der relativ geringen Kapazität der PN-Übergänge, die in einem SOI-Bauelement im Vergleich zu einem Silizium-Vollsubstratbauelement gleicher Abmessungen erreicht werden. Die vergrabene Oxydschicht in einem SOI-Bauelement trennt aktive Transistorgebiete von dem Silizium-Vollsubstrat, so dass die Kapazität der PN-Übergänge verringert wird.

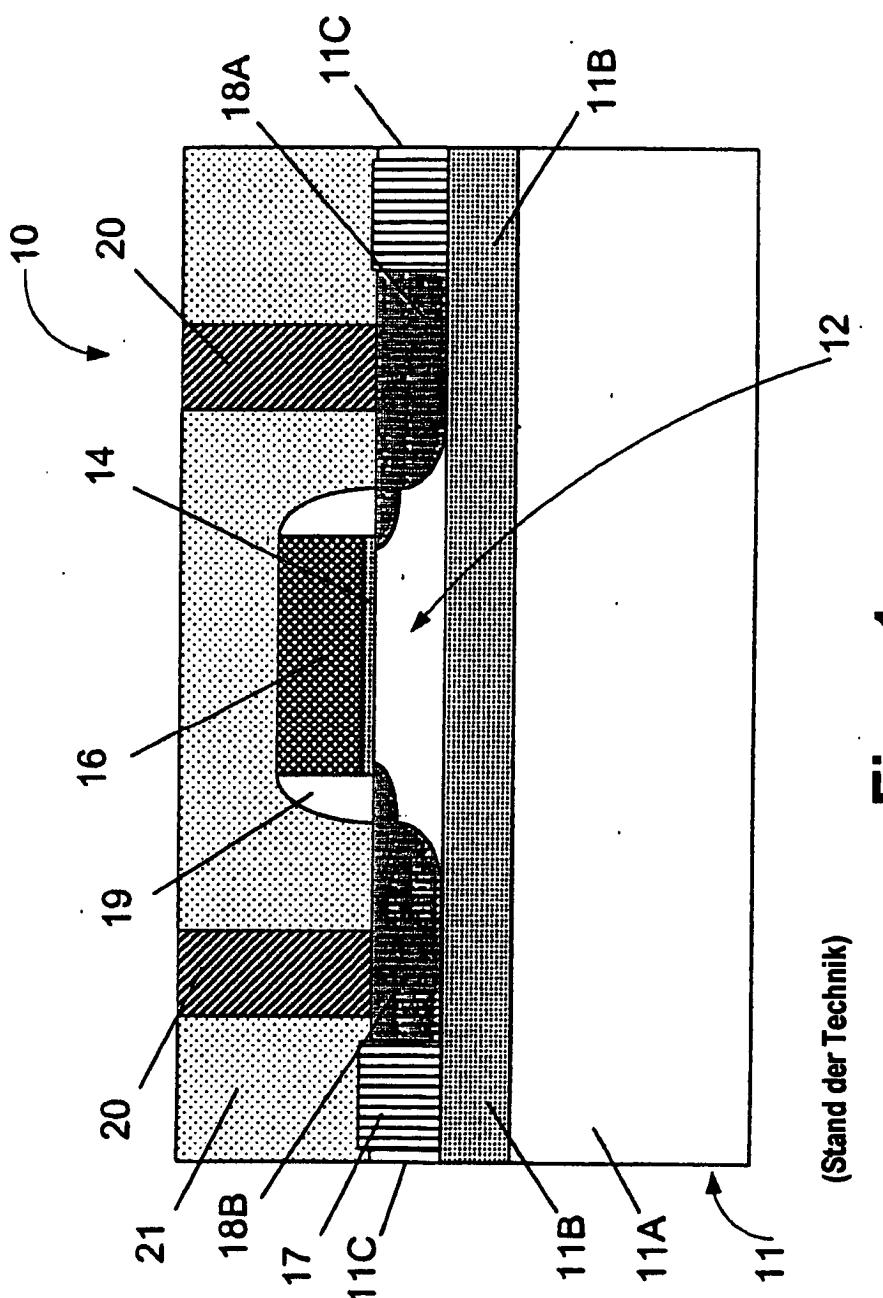

**[0005]** [Fig. 1](#) zeigt ein Beispiel eines anschaulichen Transistors **10**, der auf einem anschaulichen Silizium-auf-Isolator-(SOI)Substrat **11** hergestellt ist. Wie gezeigt ist das SOI-Substrat **11** aus einem Vollsubstrat **11A**, einer vergrabenen Oxydschicht **11B** und einer aktiven Schicht **11C** aufgebaut. Der Transistor **10** ist aus einer Gate-Isolationsschicht **14**, einer Gate-Elektrode **16**, Seitenwandabstandshaltern **19**, einem Drain-Gebiet **18A** und einem Source-Gebiet **18B** aufgebaut. Es sind mehrere Grabenisolationsgebiete **17** in der aktiven Schicht **11C** vorgesehen. Ferner ist in [Fig. 1](#) eine Vielzahl von leitenden Kontakten **20** gezeigt, die in einer Schicht aus isolierendem Material **21** ausgebildet sind. Die leitenden Kontakte **20** stellen elektrische Verbindungen zu den Drain- und Source-Gebieten **18A**, **18B** her. In der gezeigten Struktur bildet der Transistor **10** ein Kanalgebiet **12** in der aktiven Schicht **11C** unterhalb der Gate-Isolationsschicht **14**. Das Vollsubstrat **11A** ist normalerweise mit einem geeigneten Dotiermaterial, d. h., einem P-Dotiermittel, etwa Bor oder Bordifluorid für NMOS-Bauelemente oder einem N-Dotiermittel, etwa Arsen oder Phosphor für PMOS-Bauelemente, dotiert. Typischerweise besitzt das Vollsubstrat **11A** einen Dotierkonzentrationspegel in der Größenordnung von ungefähr  $10^{15}$  Ionen/cm<sup>3</sup>. Die vergrabene Oxydschicht **11D** ist aus Siliziumdioxid aufgebaut und kann eine Dicke von ungefähr 200 bis 360 nm (2000–3600 Å) aufweisen. Die aktive Schicht **11C** ist aus dotiertem Silizium aufgebaut und besitzt eine Dicke von beispielsweise ungefähr 5–30 nm (50–300 Å).

**[0006]** Transistoren, die in SOI-Substraten hergestellt sind, haben einige Verhaltensvorteile gegenüber Transistoren, die in Silizium-Vollsubstraten aufgebaut sind. Beispielsweise sind komplementäre Metall-Oxyd-Halbleiter-(CMOS)Bauelemente, die in SOI-Substraten hergestellt sind, weniger anfällig für den Verlust der kapazitiven Kopplung, was als "ungewolltes Einschalten" bzw. "Latch-up" bezeichnet wird. Des Weiteren besitzen Transistoren, die in SOI-Substraten hergestellt sind, im Allgemeinen größere Durchlassströme und besitzen höhere Transkonduktanz- bzw. Steilheitswerte. Des Weiteren besitzen die SOI-Transistoren im Bereich unter einem Mikrometer eine verbesserte Widerstandsfähigkeit im Hinblick

auf Kurzkanaleffekte im Vergleich zu Vollsubstrattransistoren, die mit ähnlichen Abmessungen hergestellt sind.

**[0007]** Obwohl SOI-Bauelemente Leistungsvorteile gegenüber Vollsubstrat-Bauelementen ähnlicher Abmessungen bieten, zeigen SOI-Bauelemente auch gewisse Probleme im Leistungsverhalten, die sie mit Dünnschicht-Transistoren gemeinsam haben. Beispielsweise werden die aktiven Elemente eines SOI-Transistors in der aktiven Dünnschicht **11C** gebildet. Das Skalieren von Dünnschicht-Transistoren zu immer kleineren Abmessungen erfordert, dass die Dicke der aktiven Schicht **11C** reduziert wird. Wenn die Dicke der aktiven Schicht **11C** verringert wird, steigt jedoch der elektrische Widerstand der aktiven Schicht **11C** entsprechend an. Dies kann eine negative Auswirkung auf das Transistorleistungsverhalten ausüben, da die Herstellung von Transistorelementen in einem leitenden Körper mit einem hohen elektrischen Widerstand den Durchlassstrom des Transistors **10** verringert. Wenn ferner die Dicke der aktiven Schicht **11C** eines SOI-Bauelements ständig abnimmt, können Schwankungen in der Schwellwertspannung ( $V_T$ ) des Bauelements auftreten. Kurz gesagt, wenn die Dicke der aktiven Schicht **11C** abnimmt, wird die Schwellwertspannung des Bauelements instabil. Als Folge davon ist die Verwendung derartiger instabiler Bauelemente in modernen integrierten Schaltungsbauelementen, beispielsweise in Mikroprozessoren, Speicherbauelementen, Logikbauelementen, etc. sehr schwierig, wenn nicht gar unmöglich.

**[0008]** Des Weiteren sind Leckströme im nicht durchgeschalteten Zustand stets ein Problem in integrierten Schaltungen, da derartige Ströme tendenziell unter anderem die Leistungsaufnahme erhöhen. Eine derartig erhöhte Leistungsaufnahme ist insbesondere nachteilig in modernen tragbaren Geräten, in denen integrierte Schaltungen eingesetzt sind, beispielsweise tragbare Computer. Schließlich können bei ständig abnehmenden Bauteilabmessungen in vollständig verarmten SOI-Strukturen erhöhte Kurzkanaleffekte auftreten. Das heißt, in derartigen vollständig verarmten Bauelementen sind zumindest einige der Feldlinien des elektrischen Feldes des Drains **18A** mit dem Kanalgebiet **12** des Transistors **10** durch die relativ dicke (200–360 nm) vergrabene Oxydschicht **11B** gekoppelt. In einigen Fällen kann das elektrische Feld des Drains **18A** so wirken, dass tatsächlich der Transistor **10** eingeschaltet wird. Theoretisch können derartige Probleme verringert werden, indem die Dicke der vergrabenen Oxydschicht **11B** reduziert wird und/oder indem die Dotierstoffkonzentration des Vollsubstrats **11A** erhöht wird. Jedoch würden derartige Maßnahmen zu einer Erhöhung der Kapazität der PN-Übergänge zwischen dem Drain-Gebiet und dem Source-Gebiet **18A**, **18B** und dem Vollsubstrat **11A** führen, wodurch einer der we-

sentlichen Vorteile der SOI-Technologie, d. h. das Reduzieren derartiger Kapazitäten der PN-Übergänge, aufgehoben würde.

**[0009]** Die vorliegenden Erfindung richtet sich an ein Bauteil und diverse Verfahren, die einige oder alle der zuvor genannten Probleme lösen oder zumindest verringern.

### Überblick über die Erfindung

**[0010]** Die vorliegenden Erfindung betrifft im Allgemeinen eine vorgespannte vollständig verarmte SOI-Struktur mit Dreifach-Wanne und diverse Verfahren zur Herstellung und Betreiben derselben. In einer anschaulichen Ausführungsform umfasst das Bauelement einen Transistor, der über einem Silizium-auf-Isolator-(SOI)Substrat hergestellt ist, das ein Vollsubstrat, eine vergrabene isolierende Schicht und eine aktive Schicht besitzt, wobei das Vollsubstrat mit einer ersten Art an Dotiermaterial dotiert ist, und wobei eine erste Wanne bzw. ein erstes Potentialtopfgebiet in dem Vollsubstrat ausgebildet ist und die erste Wanne mit einer zweiten Art an Dotiermaterial dotiert ist, das die entgegengesetzte Leitfähigkeitsart der ersten Art von Dotiermaterial aufweist. Das Bauelement umfasst ferner eine zweite Wanne, die in dem Vollsubstrat innerhalb der ersten Wanne ausgebildet ist, wobei die zweite Wanne mit einem Dotiermaterial dotiert ist, das von der gleichen Art wie die erste Art an Dotiermaterial ist, und wobei der Transistor in der aktiven Schicht über der zweiten Wanne ausgebildet ist, und ein elektrischer Kontakt für die erste Wanne und ein elektrischer Kontakt für die zweite Wanne vorgesehen sind. In weiteren Ausführungsformen umfasst der Transistor ferner mehrere Source/Drain-Gebiete und eine Source/Drain-Wanne ist in dem Vollsubstrat in der zweiten Wanne unter jedem Source/Drain-Gebiet ausgebildet. Die Source/Drain-Wannen sind aus einem Dotiermaterial aufgebaut, das von der gleichen Leitfähigkeitsart wie jene der ersten Art an Dotiermaterial ist, wobei die Source/Drain-Wannen jedoch einen Dotierstoffkonzentrationspegel der ersten Art des Dotierstoffmaterials besitzen, der kleiner ist als ein Dotierstoffkonzentrationspegel der ersten Art an Dotierstoffmaterial in der zweiten Wanne.

**[0011]** In einer anteiligen Ausführungsform ist ein Verfahren offenbart, um einen Transistor über einem Silizium-auf-Isolator-(SOI)Substrat zu bilden, das ein Vollsubstrat, eine vergrabene Oxydschicht und eine aktive Schicht besitzt, wobei das Vollsubstrat mit einer ersten Art an Dotiermaterial dotiert ist. Das Verfahren umfasst: Ausführen eines ersten Ionimplantationsprozesses unter Anwendung einer zweiten Art an Dotierstoffmaterial, das vom entgegengesetzten Leitfähigkeitsyp im Vergleich zur ersten Art an Dotierstoffmaterial ist, um ein erstes Wannengebiet innerhalb des Vollsubstrats zu bilden, Ausführen eines

zweiten Ionenimplantationsprozesses unter Anwendung eines Dotierstoffmaterials, das von der gleichen Leitfähigkeitsart wie die erste Art an Dotierstoffmaterial ist, um ein zweites Wannengebiet in dem Vollsubstrat innerhalb der ersten Wanne zu bilden, wobei der Transistor in der aktiven Schicht über der zweiten Wanne gebildet wird, Bilden eines leitenden Kontakts zu der ersten Wanne und Bilden eines leitenden Kontakts zu der zweiten Wanne. In weiteren Ausführungsformen umfasst das Verfahren ferner Bilden mehrerer Source/Drain-Gebiete, wobei das Verfahren ferner umfasst: Ausführen eines dritten Ionenimplantationsprozesses unter Anwendung von Dotierstoffmaterial, das von entgegengesetzter Leitfähigkeitsart im Vergleich zur ersten Art an Dotierstoffmaterial ist, so dass sich eine Source/Drain-Wanne in dem Vollsubstrat unter jedem der mehreren Source/Drain-Gebiete des Transistors ergibt, wobei die Source/Drain-Wannen einen Dotierstoffkonzentrationspegel der ersten Art an Dotierstoffmaterial aufweisen, der kleiner ist als ein Dotierstoffkonzentrationspegel der ersten Art an Dotierstoffmaterial in der zweiten Wanne.

#### Kurze Beschreibung der Zeichnungen

**[0012]** Die Erfindung kann mit Bezugnahme auf die folgende Beschreibung in Verbindung mit den begleitenden Zeichnungen verstanden werden, in denen gleiche Bezugszeichen gleiche Elemente bezeichnen und in denen:

**[0013]** [Fig. 1](#) eine Querschnittsansicht eines anschaulichen konventionellen Halbleiterbauelementes ist, das über einem SOI-Substrat gebildet ist,

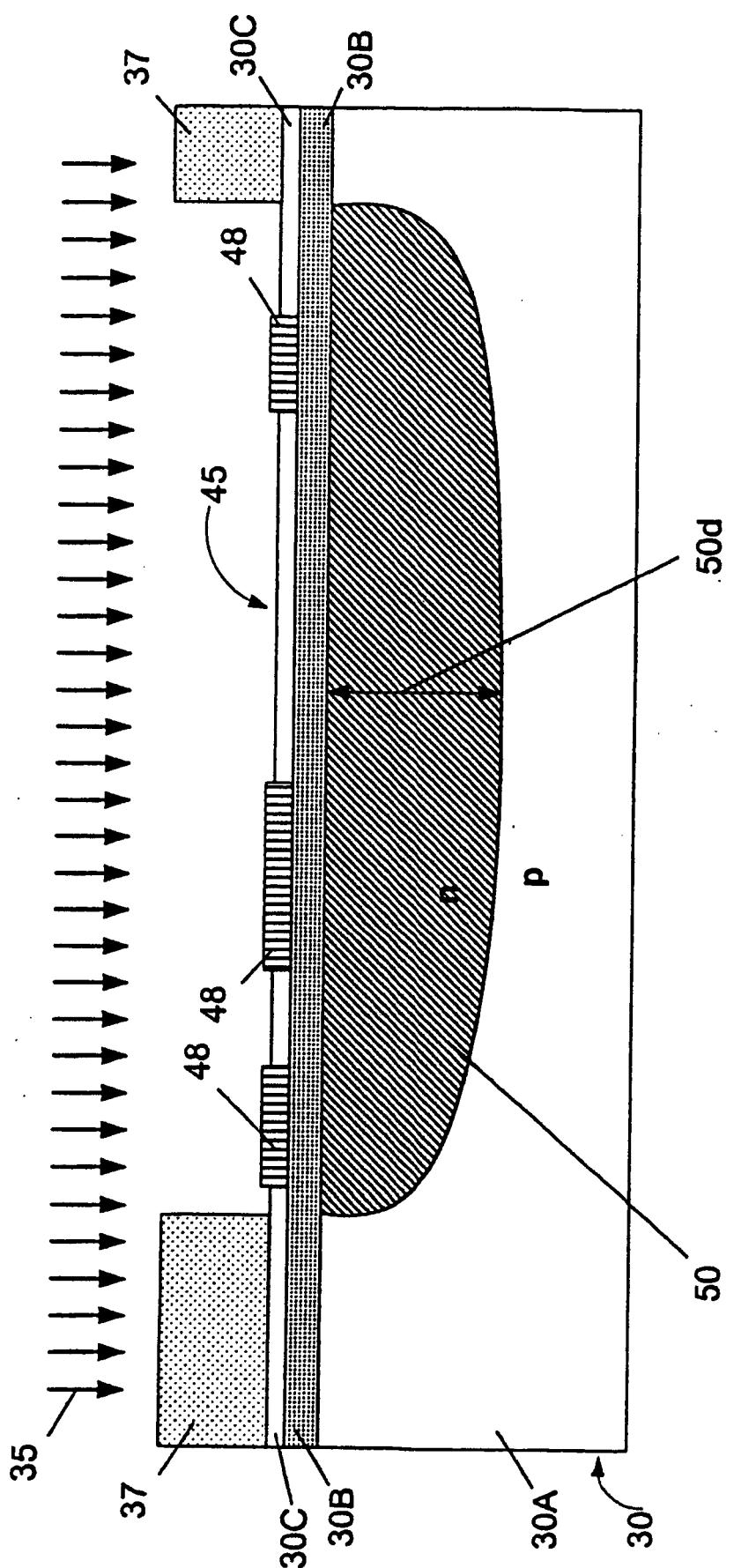

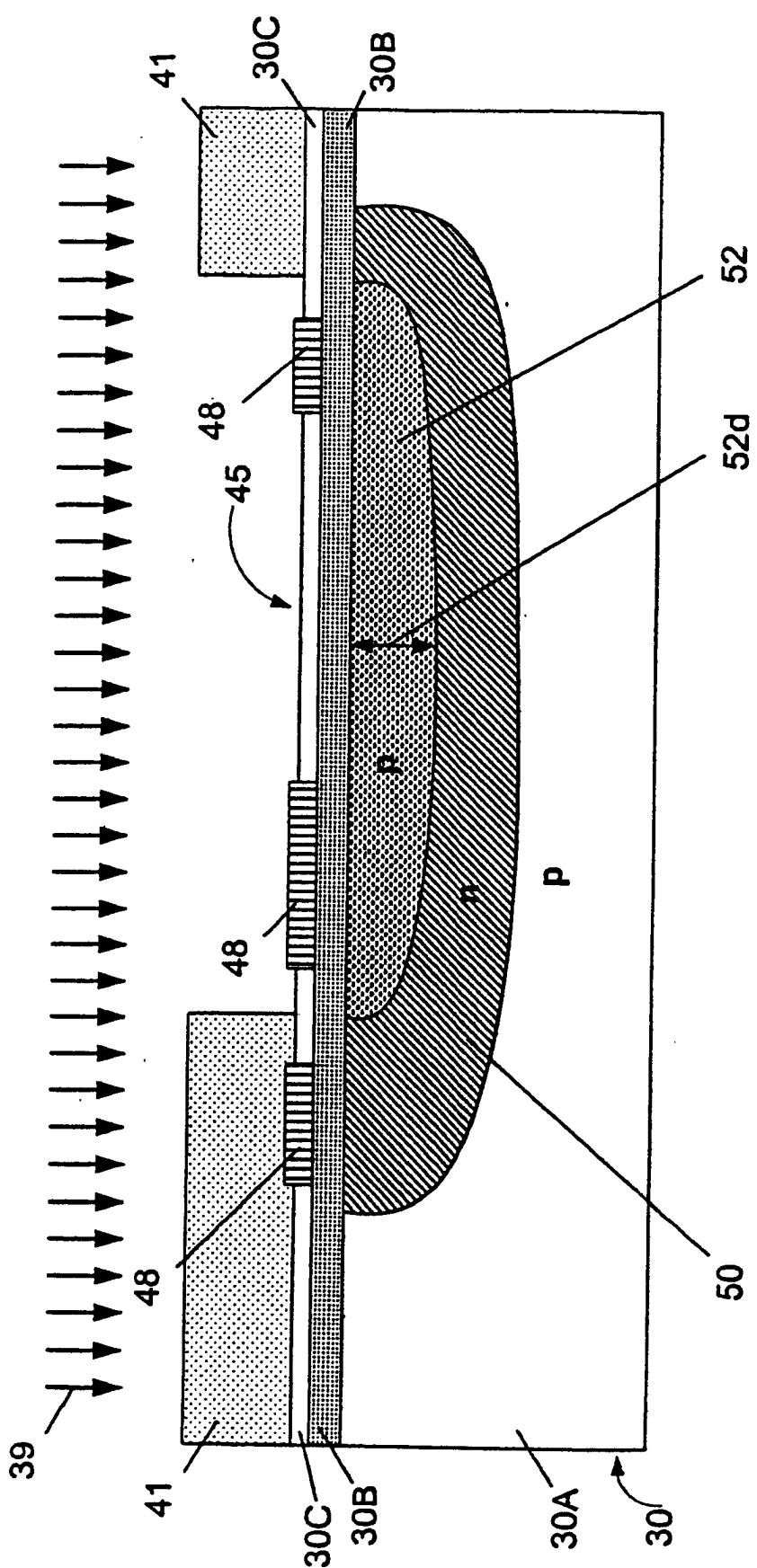

**[0014]** [Fig. 2A](#) bis [Fig. 2F](#) Querschnittsansichten sind, die ein anschauliches Verfahren der vorliegenden Erfindung zur Herstellung von Bereichen eines anschaulichen NMOS-Halbleiterbauelements über einem SOI-Substrat zeigen; und

**[0015]** [Fig. 3A](#) bis [Fig. 3F](#) Querschnittsansichten sind, die ein anschauliches Verfahren der vorliegenden Erfindung zur Herstellung von Bereichen eines anschaulichen PMOS-Halbleiterbauelements über einem SOI-Substrat zeigen.

**[0016]** Obwohl die Erfindung diversen Modifizierungen und alternativen Formen unterliegen kann, sind dennoch spezielle Ausführungsformen hierin beispielhaft in den Zeichnungen gezeigt und detailliert beschrieben. Es sollte jedoch beachtet werden, dass die Beschreibung spezieller Ausführungsformen nicht beabsichtigt, die Erfindung auf die speziellen offenen Formen einzuschränken, sondern die Erfindung beabsichtigt vielmehr, alle Modifizierungen, Äquivalente und Alternativen, die innerhalb des Grundgedankens und Schutzbereichs der Erfindung liegen, wie sie durch die angefügten Patentansprü-

che definiert ist, abzudecken.

#### Art bzw. Arten zum Ausführen der Erfindung

**[0017]** Im Folgenden werden anschauliche Ausführungsformen der Erfindung beschrieben. Im Interesse der Einfachheit halber sind nicht alle Merkmale einer tatsächlichen Implementierung in dieser Beschreibung dargelegt. Es ist jedoch zu beachten, dass bei der Entwicklung einer derartigen tatsächlichen Ausführungsform zahlreiche implementationsspezifische Entscheidungen getroffen werden müssen, um die speziellen Ziele der Entwickler zu erreichen, etwa die Verträglichkeit mit systembezogenen und geschäftsbezogenen Rahmenbedingungen, die sich von einer Implementierung zur anderen unterscheiden können. Des Weiteren ist zu beachten, dass ein derartiger Entwicklungsaufwand komplex und zeitaufwendig sein kann, aber dennoch eine Routinemaßnahme für den Fachmann im Besitze der vorliegenden Offenbarung darstellt.

**[0018]** Die vorliegenden Erfindung wird nunmehr mit Bezug zu den begleitenden Figuren beschrieben. Obwohl diverse Gebiete und Strukturen eines Halbleiterbauelements in den Zeichnungen so dargestellt sind, dass diese genaue und scharfe Konfigurationen und Profile aufweisen, weiß der Fachmann, dass in der Realität diese Gebiete und Strukturen nicht so präzise sind, wie dies in den Zeichnungen dargestellt ist. Des Weiteren sind die relativen Größen der diversen Strukturelemente und dotierten Gebiete, die in den Zeichnungen dargestellt sind, übertrieben oder verkleinert im Vergleich zur Größe dieser Strukturen oder Gebieten in hergestellten Bauelementen. Dennoch sind die beigefügten Zeichnungen hierin enthalten, um anschauliche Beispiele der vorliegenden Erfindung zu beschreiben und zu erläutern. Die Begriffe und Terminologie, die hierin verwendet sind, sollen so verstanden und interpretiert werden, dass sie eine Bedeutung besitzen, die konsistent ist und dem Verständnis dieser Begriffe und Terminologien, wie sie von dem Fachmann angewendet werden. Es soll keine spezielle Definition eines Terms oder eines Begriffes beabsichtigt sein, d. h. eine Definition, die sich von der üblichen und gebräuchlichen Bedeutung, wie sie vom Fachmann verstanden wird, unterscheidet, wenn der Term oder der Begriff hierin konsistent verwendet wird. Wenn ein Term oder ein Begriff eine spezielle Bedeutung haben soll, d. h. eine Bedeutung, die anders ist als sie vom Fachmann verstanden wird, wird eine derartige spezielle Definition ausdrücklich in der Beschreibung in einer definierenden Weise angegeben, so dass sie direkt und eindeutig die spezielle Definition für den Term oder den Begriff erkennen lässt.

**[0019]** Im Allgemeinen richtet sich die vorliegenden Erfindung an eine vorgespannte vollständig verarmte SOI-Struktur mit Dreifach-Wanne und diverse Verfah-

ren zur Herstellung und Betreiben derselben. Obwohl die vorliegenden Erfindung zunächst im Zusammenhang mit der Herstellung eines anschaulichen NMOS-Transistors offenbart ist, erkennt der Fachmann nach einem vollständigen Studium der vorliegenden Anmeldung, dass die vorliegenden Erfindung nicht darauf beschränkt ist. Insbesondere kann die vorliegenden Erfindung im Hinblick auf eine Vielzahl von Technologien, beispielsweise NMOS, PMOS, CMOS, etc. eingesetzt werden, und diese kann im Zusammenhang mit einer Vielzahl unterschiedlicher Bauteiltypen, beispielsweise Speicherbauelementen, Mikroprozessoren, Logikbauelementen, etc. eingesetzt werden.

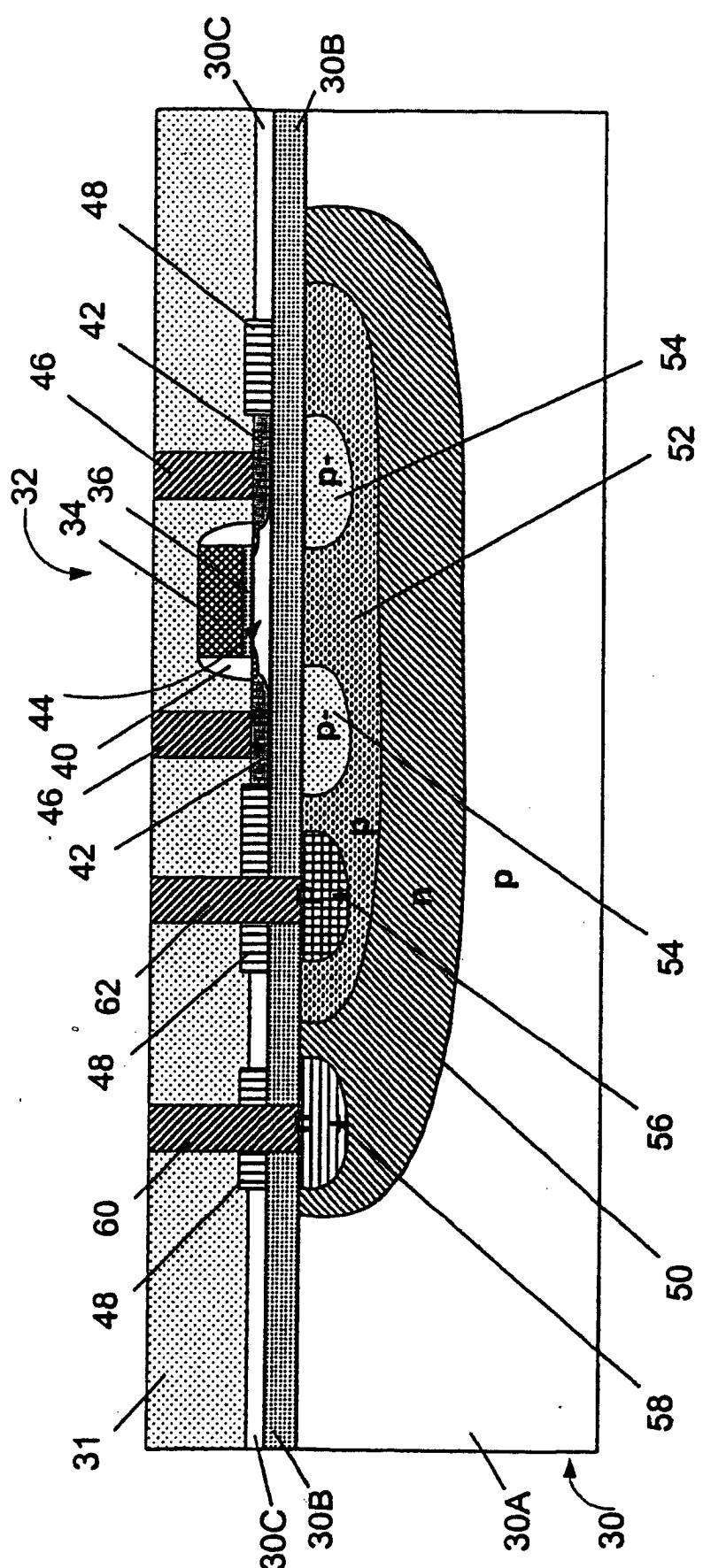

[0020] [Fig. 2A](#) zeigt einen anschaulichen NMOS-Transistor **32**, der gemäß einer Ausführungsform der vorliegenden Erfindung hergestellt ist. Wie gezeigt, ist der Transistor **32** über einem SOI-Substrat **30** gebildet. In einer anschaulichen Ausführungsform ist das SOI-Substrat **30** aus einem Vollsubstrat **30A**, einer vergrabenen isolierenden Schicht **30B** und einer aktiven Schicht **30C** aufgebaut. Selbstverständlich zeigt [Fig. 2A](#) lediglich einen kleinen Teil des gesamten Substrats oder der Scheibe. In der anschaulichen Ausführungsform, in der ein NMOS-Bauelement ausgebildet ist, kann das Vollsubstrat **30A** mit einem P-Dotiermaterial, beispielsweise Bor, Borfluorid, etc. dotiert sein und kann eine Dotierstoffkonzentration von ungefähr  $10^{15}$  Ionen/cm<sup>3</sup> aufweisen. Die vergrabene isolierende Schicht **30B** besitzt eine Dicke, die in einer Ausführungsform von ungefähr 5–50 nm (50–300 Å) variiert, und diese kann beispielsweise aus Siliziumdioxid aufgebaut sein. Die aktive Schicht **30C** besitzt eine Dicke, die von ungefähr 5–30 nm (50–300 Å) reicht und im Falle eines NMOS-Bauelements ist diese mit einem P-Dotiermaterial dotiert. Der Fachmann weiß, dass der Dickenbereich für die vergrabene isolierende Schicht **30B** deutlich kleiner ist als die entsprechende Dicke einer vergrabenen isolierenden Schicht von herkömmlichen SOI-Strukturen, etwa wie sie im Abschnitt "Hintergrund der Erfindung" beschrieben sind. Jedoch sollten die angegebenen Details im Hinblick auf den Aufbau des SOI-Substrats **30** nicht als Einschränkung der vorliegenden Erfindung erachtet werden, sofern derartige Einschränkungen nicht speziell in den angefügten Patentansprüchen festgelegt sind.

[0021] Wie in [Fig. 2A](#) gezeigt ist, ist der Transistor **32** aus einer Gate-Isolationsschicht **36**, der Gate-Elektrode **34**, Seitenwandabstandshaltern **44** und Source/Drain-Gebieten **42** aufgebaut. Des Weiteren sind in [Fig. 2A](#) Isolationsgebiete **48** gezeigt, die in der aktiven Schicht **30C** ausgebildet sind, und ferner sind mehrere leitende Kontakte **46** gezeigt, die in einer Schicht aus isolierendem Material **31** hergestellt sind, und es sind ferner weitere Kontakte **60**, **62** und **63** dargestellt. Wie der Fachmann erkennt, bilden die Kontakte **46** ein Mittel zum Herstellen einer

elektrischen Verbindung zu den Source/Drain-Gebieten **42** des Transistors **32**.

[0022] Gemäß der vorliegenden Erfindung sind mehrere dotierte Wannen, bzw. Potentialtopfgebiete in dem Vollsubstrat **30A** gebildet. Insbesondere, wie in [Fig. 2A](#) gezeigt ist, wird für ein anschauliches CMOS-Bauelement das Vollsubstrat **30A** typischerweise mit einem P-Dotiermaterial, etwa Bor oder Borfluorid, mit einem Konzentrationspegel von ungefähr  $10^{12}$ – $10^{16}$  Ionen/cm<sup>3</sup> hergestellt. Eine erste Wanne **50**, eine zweite Wanne **52** und mehrere Source/Drain-Wannen **54** und mehrere Kontaktwannen **56**, **58** sind in dem Vollsubstrat **30A** gemäß den hierin offenbarten Verfahren ausgebildet. Im Falle eines anschaulichen NMOS-Transistors ist die erste Wanne **50** mit einem N-Dotiermaterial, etwa Arsen oder Phosphor, bei einem Dotierstoff-Konzentrationspegel von ungefähr  $10^{16}$ – $10^{19}$  Ionen/cm<sup>3</sup> dotiert. Wiederum im Falle eines NMOS-Bauelements ist die zweite Wanne **52** mit einem P-Dotiermaterial, beispielsweise Bor oder Borfluorid, bei einer Dotierstoffkonzentration von ungefähr  $10^{17}$ – $10^{20}$  Ionen/cm<sup>3</sup> dotiert. Die Source/Drain-Wannen **54** können durch diverse Gegendotierverfahren hergestellt werden, wie sie hierin noch detaillierter beschrieben sind, wobei die resultierende Konzentration der Source/Drain-Wannen **54** von ungefähr  $10^{14}$ – $10^{17}$  Ionen/cm<sup>3</sup> eines P-Dotiermaterials für ein NMOS-Bauelement reicht. Die Kontaktwanne **56** ist mit einem P-Dotiermaterial mit relativ hoher Konzentration, beispielsweise  $2 \times 10^{20}$  oder mehr Ionen/cm<sup>3</sup> dotiert. In ähnlicher Weise kann die N-Kontaktwanne mit einem ähnlichen Konzentrationspegel von N-Dotieratomen, beispielsweise Arsen, Phosphor, etc. dotiert sein. Wie der Fachmann nach dem vollständigen Studium der vorliegenden Anmeldung erkennt, sind die diversen Komponenten des Transistors, beispielsweise die Gate-Elektrode **34** und die Gate-Isolationsschicht **36** und auch die Art, in der diese hergestellt sind und die Materialien davon, gut bekannt, und diese sollten nicht als Beschränkung der vorliegenden Erfindung erachtet werden, sofern derartige Beschränkungen nicht speziell in den angefügten Patentansprüchen dargelegt sind.

[0023] Ein anschauliches Verfahren zur Herstellung des anschaulichen NMOS-Transistors **32**, der in [Fig. 2A](#) gezeigt ist, wird nunmehr mit Bezug zu den [Fig. 2B](#)–[Fig. 2F](#) beschrieben. Zunächst wird, wie in [Fig. 2B](#) gezeigt ist, eine Maskenschicht **37** über der aktiven Schicht **30C** des Substrats **30** gebildet. Die Maskenschicht **37** kann aus einer Vielzahl von Materialien hergestellt werden, etwa Photolack. Danach wird ein Ionenimplantationsprozess **35** ausgeführt, um die erste Wanne **50** in dem Vollsubstrat zu bilden. Die erste Wanne **50** besitzt eine Tiefe **50d**, die von ungefähr 50–150 nm reicht. Wiederum im Zusammenhang mit der Herstellung eines NMOS-Bauelements kann der Ionenimplantationsprozess **35** unter Anwendung eines N-Dotiermaterials, etwa Arsen,

Phosphor, etc. mit einer Dotierdosis von ungefähr  $5 \times 10^{10}$ – $1,5 \times 10^{14}$  Ionen/cm<sup>2</sup> ausgeführt werden. Die resultierende erste Wanne **50** besitzt einen Dotierstoff-Konzentrationspegel, der im Bereich von ungefähr  $10^{16}$ – $10^{19}$  Ionen/cm<sup>3</sup> liegt. Die während des Ionenimplantationsprozesses **35** angewendete Implantationsenergie kann in Abhängigkeit der Dotierstoffatomsorte, die implantiert wird, variieren. In der anschaulichen Ausführungsform, in der Phosphor als Dotiermaterial verwendet wird, beträgt die Implantationsenergie ungefähr 20–100 keV.

**[0024]** Als nächstes wird die in [Fig. 2B](#) gezeigte Maskenschicht **37** entfernt und es wird eine weitere Maskenschicht **41** über der aktiven Schicht **30C** des Substrats **30** gebildet, wie in [Fig. 2C](#) gezeigt ist. Danach wird ein weiterer Ionenimplantationsprozess ausgeführt, wie dies durch die Pfeile **39** gezeigt ist, um die zweite Wanne **52** in dem Vollsubstrat **30A** zu bilden. Die zweite Wanne **52** ist mit einer zweiten Art an Dotierstoffmaterial dotiert, die von entgegengesetzter Leitfähigkeitsart im Vergleich zu dem Dotiermaterial ist, was in der ersten Wanne **50** verwendet wird. Im Falle eines anschaulichen NMOS-Transistors wird die zweite Wanne **52** mit einem P-Dotiermaterial, etwa Bor, Bordifluorid, etc. dotiert. Die zweite Wanne **52** besitzt eine Dicke **52d**, die von ungefähr 40–100 nm variieren kann. In einer anschaulichen Ausführungsform besitzt die zweite Wanne **52** eine Dotierstoffkonzentration von ungefähr  $10^{17}$ – $10^{20}$  Ionen/cm<sup>3</sup>. Für die Herstellung eines NMOS-Bauelements wird der Ionenimplantationsprozess **39** mit einem P-Dotiermaterial, beispielsweise Bor, Bordifluorid, etc. mit einer Dotierstoffdosis von ungefähr  $4 \times 10^{11}$ – $1 \times 10^{15}$  Ionen/cm<sup>2</sup> ausgeführt. Die während des Implantationsprozesses **39** eingesetzte Implantationsenergie kann dabei in Abhängigkeit von der implantierten Dotierstoffatomsorte variieren. In der dargestellten Ausführungsform, in der Bor als Dotiermaterial verwendet wird, kann die Implantationsenergie von ungefähr 5–30 keV variieren.

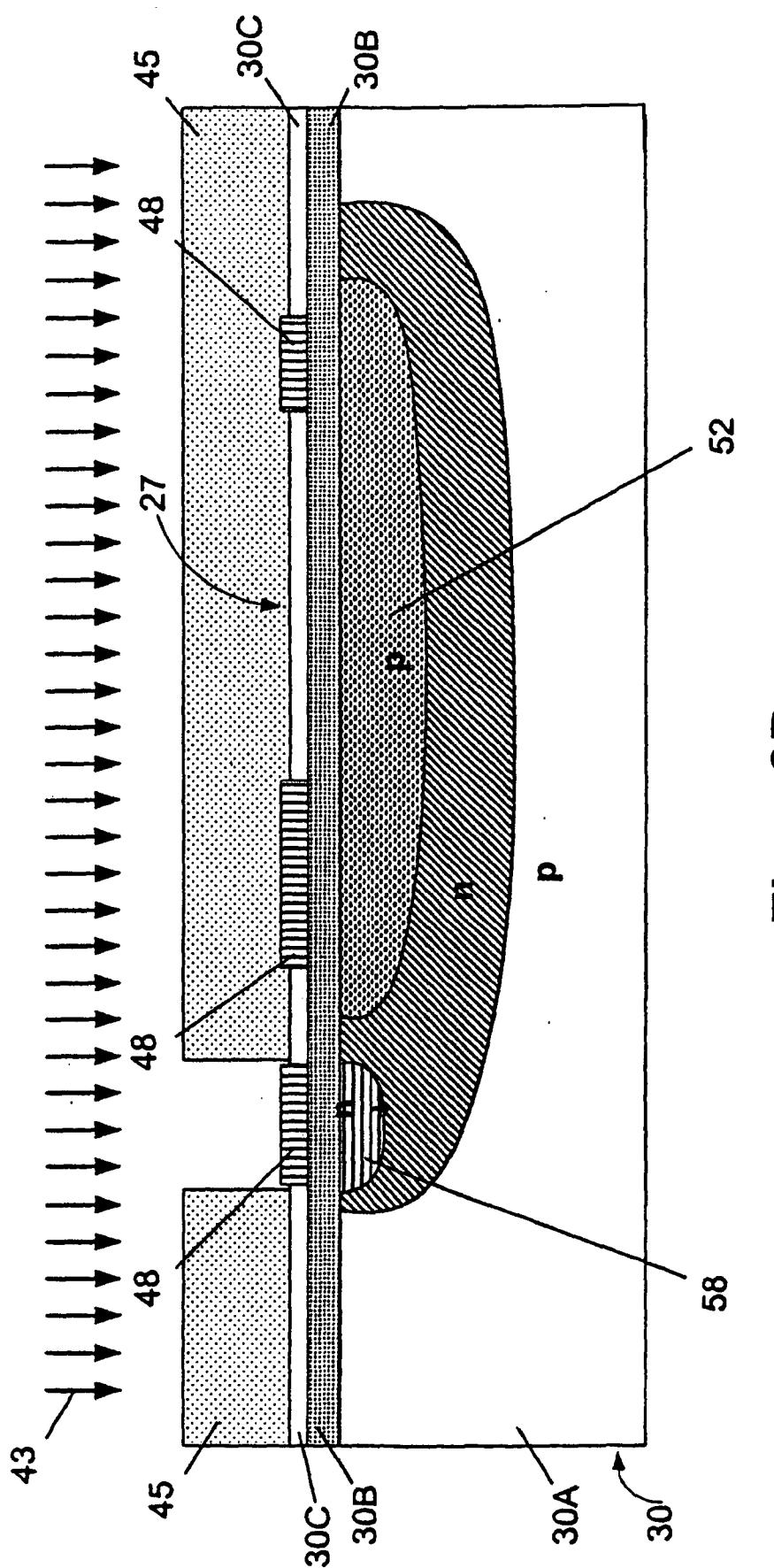

**[0025]** Als nächstes wird die Maskenschicht **41**, die in [Fig. 2C](#) gezeigt ist, entfernt und es wird eine weitere Maskenschicht **45** über dem Substrat **30** gebildet, wie dies in [Fig. 2D](#) gezeigt ist. Wie darin gezeigt ist, wird ein Ionenimplantationsprozess, der durch die Pfeile **43** gekennzeichnet ist, ausgeführt, um eine Kontaktwanne **58** für die erste Wanne **50** zu bilden. In der anschaulichen Ausführungsform eines NMOS-Transistors wird die Kontaktwanne **58** mit einem N-Dotiermaterial, etwa Arsen oder Phosphor dotiert und dies geschieht mit einem relativ hohen Konzentrationspegel, beispielsweise  $2 \times 10^{20}$  Ionen/cm<sup>3</sup>. Dies kann bewerkstelligt werden, indem eine Implantationsdosis von ungefähr  $2 \times 10^{15}$ – $5 \times 10^{15}$  Ionen/cm<sup>2</sup> angewendet wird. Wie bei den anderen Implantationsprozessen variiert gegebenenfalls nur die Implantationsenergie in Abhängigkeit des während des Implantationsprozesses **43** eingebrachten Do-

tiermaterials. In der anschaulichen Ausführungsform, in der Arsen während des Implantationsprozesses **43** implantiert wird, kann die Implantationsenergie von ungefähr 10–20 keV variieren.

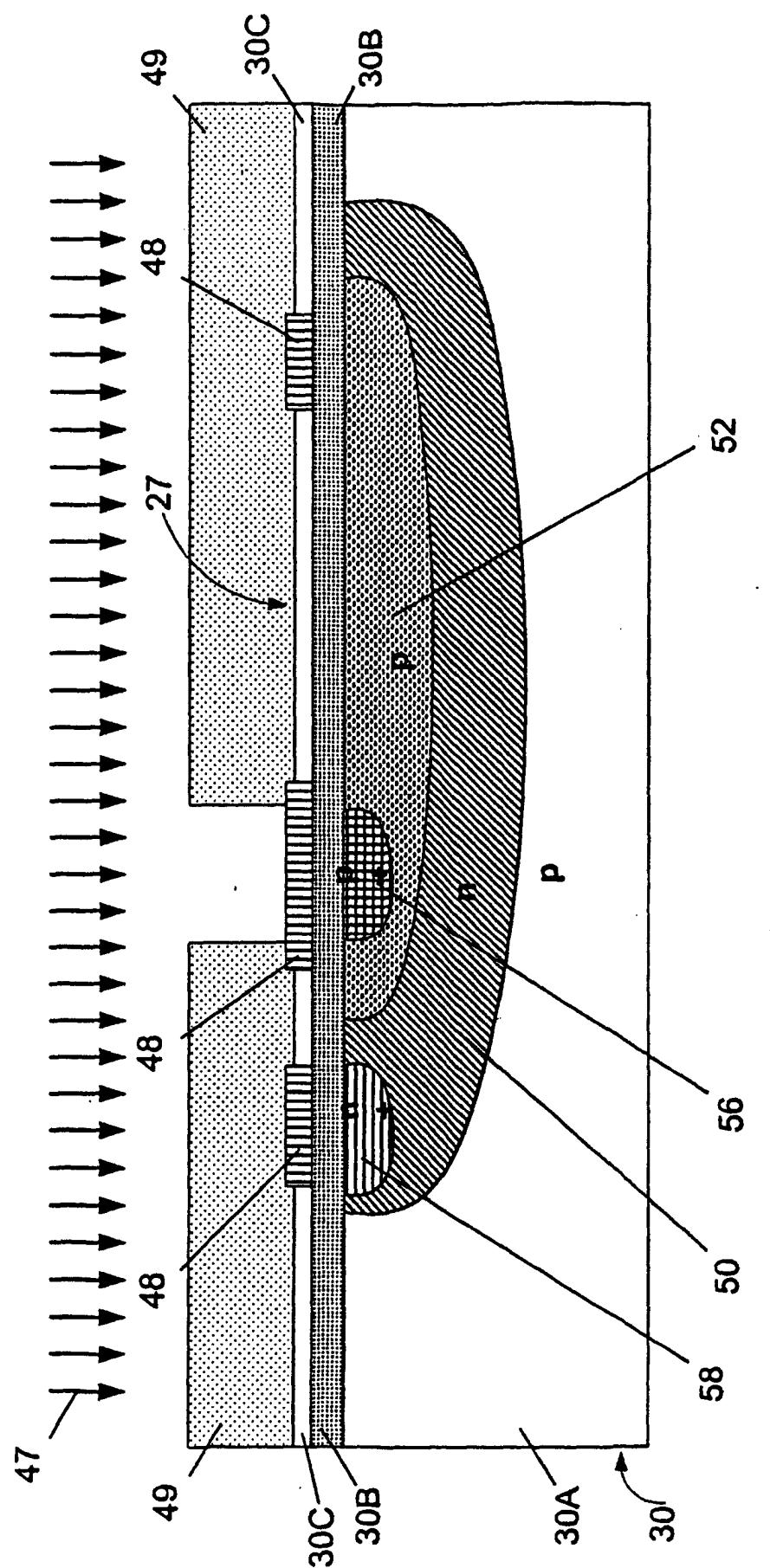

**[0026]** Danach wird die Maskenschicht **45** entfernt und es wird eine weitere Maskenschicht **49** gebildet, wie dies in [Fig. 2E](#) gezeigt ist. Danach wird ein weiterer Ionenimplantationsprozess **47** ausgeführt, um eine Kontaktwanne **56** in der zweiten Wanne **52** zu bilden. Im Falle eines anschaulichen NMOS-Transistors ist die Kontaktwanne **56** aus einem P-Dotiermaterial, etwa Bor, Bordifluorid, etc. aufgebaut. Des Weiteren besitzt die Kontaktwanne **56** einen Dotierstoffkonzentrationspegel von ungefähr  $2 \times 10^{20}$  Ionen/cm<sup>3</sup>. Dies kann unter Anwendung einer Implantationsdosis von ungefähr  $2 \times 10^{15}$ – $5 \times 10^{15}$  Ionen/cm<sup>3</sup> bewerkstelligt werden. Wie bei den anderen Implantationsprozessen kann die Implantationsenergie in Abhängigkeit von dem während des Implantationsprozesses **43** eingebrachten Dotierstoffmaterials variieren. In der anschaulichen Ausführungsform, in der Bor während des Implantationsprozesses **43** eingebracht wird, kann die Implantationsenergie von ungefähr 3–10 keV variieren. Wie der Fachmann nach einem vollständigen Studium der vorliegenden Anmeldung erkennt, können die Kontaktwannen setzen **56**, **58** nach der Herstellung der ersten und der zweiten Wanne gebildet werden und können auch in einer beliebigen Reihenfolge hergestellt werden.

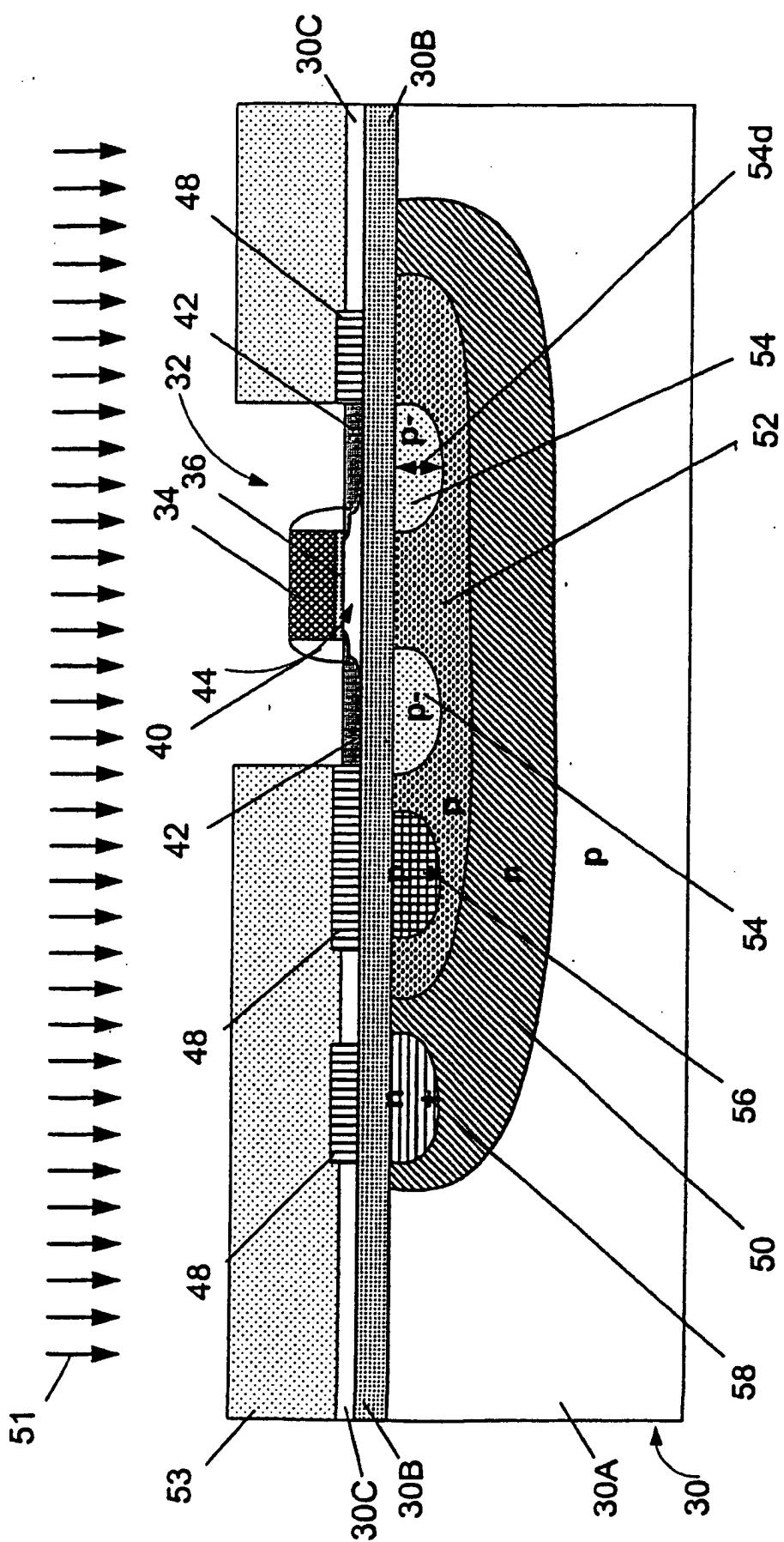

**[0027]** Danach wird, wie in [Fig. 2F](#) gezeigt ist, ein Transistor **32** in der aktiven Schicht **30C** des Substrats **30** gebildet. Der anschauliche Transistor **32**, der in [Fig. 2F](#) gezeigt ist, ist aus einer Gate-Isolationschicht **36**, einer Gate-Elektrode **34**, Seitenwandabstandshaltern **40** und Source/Drain-Gebieten **42** aufgebaut. Es können eine Vielzahl bekannter Techniken und Materialien bei der Herstellung der diversen Komponenten des in [Fig. 2F](#) anschaulich gezeigten Transistors **32** eingesetzt werden. Beispielsweise kann die Gate-Isolationsschicht **36** aus Siliziumdioxid aufgebaut sein, die Gate-Elektrode **34** kann aus einem dotierten Poly-Silizium hergestellt sein und die Seitenwandabstandshalter **40** können aus Siliziumdioxid oder Siliziumnitrid aufgebaut sein. Im Falle eines anschaulichen NMOS-Transistors sind die Source/Drain-Gebiete **42** mit einem geeigneten N-Dotiermaterial, etwa Arsen oder Phosphor dotiert und diese können unter Anwendung konventioneller Erweiterungsimplantationen und Source/Drain-Implantationen hergestellt werden. Daher sollen die speziellen Materialien im Verfahren, die zur Herstellung des anschaulichen Transistors **32** eingesetzt werden, nicht als Einschränkungen der vorliegenden Erfindung verstanden werden, sofern derartige Einschränkungen nicht explizit in den angefügten Patentsprüchen beschrieben sind. Ferner zeigt [Fig. 2F](#) nicht alle Komponenten eines derartigen Transistors. Beispielsweise können die Source/Drain-Gebiete **42**

erhabene Bereiche (nicht gezeigt) aufweisen, die über der aktiven Schicht **30C** ausgebildet sind, und/oder Metallsilizidgebiete **42** können in den Source/Drain-Gebieten **42** und der Gate-Elektrode **34** vorgesehen sein. Jedoch sind der Einfachheit halber derartige Details nicht gezeigt.

**[0028]** Als nächstes wird, wie in [Fig. 2F](#) gezeigt ist, ein Ionenimplantationsprozess, wie dies durch die Pfeile **51** angegeben ist, durch die Maskenschicht **53** ausgeführt, um Source/Drain-Wannen **54** in dem Vollsubstrat **30A** innerhalb der zweiten Wanne **52** zu bilden. Die Source/Drain-Wannen **54** besitzen eine Tiefe **54d**, die von ungefähr 10–90 nm variieren kann. Nach dem Ende des Implantationsprozesses sind die Source/Drain-Wannen **54** aus einem Dotiermaterial aufgebaut, das von der gleichen Leitfähigkeitsart, wie das Dotiermaterial ist, das für die zweite Wanne **54** verwendet wird, wobei der Konzentrationspegel des Dotiermaterials in dem Source/Drain-Wannen **54** kleiner ist als der Konzentrationspegel des Dotiermaterials in der zweiten Wanne **52**. Im Falle eines anschaulichen NMOS-Transistors während die Source/Drain-Wannen **54** durch ein Gegendotierverfahren gebildet werden. Insbesondere werden in einer Ausführungsform die Source/Drain-Wannen **54** durch Implantierung von N-Dotieratome, beispielsweise Arsen oder Phosphor, mit einer Dotierstoffdosis im Bereich von ungefähr  $4 \times 10^{11}$ – $1 \times 10^{15}$  Ionen/cm<sup>2</sup> in die P-dotierte zweite Wanne **52** gebildet.

**[0029]** Die Implantationsenergie für den Implantationsprozess **51** hängt von den speziellen implantierten Dotierstoffsorten ab. In der anschaulichen Ausführungsform, in der Phosphor das Dotiermaterial repräsentiert, beträgt die Implantationsenergie für den Implantationsprozess **51** ungefähr 15–90 keV. Dies ergibt die Source/Drain-Wannen **54** mit einer P-Dotierkonzentration von ungefähr  $10^{15}$ – $10^{17}$  Ionen/cm<sup>3</sup>.

**[0030]** Der Zweck der Source/Drain-Wannen **54** besteht darin, die Dotierstoffkonzentration in dem Vollsubstrat **30A** in den Bereichen unterhalb der Source/Drain-Gebiete **42** des Transistors **32** zu reduzieren, um damit die Kapazität der Übergänge der Source/Drain-Gebiete **42** zu verringern. Der Implantationsprozess **51**, der zur Herstellung der Source/Drain Wannen **54** eingesetzt wird, kann zu jeder Zeit nach der Herstellung der Gate-Elektrode **34** des Transistorelements ausgeführt werden. Jedoch wird typischerweise der Implantationsprozess **51** ausgeführt, nachdem ein oder mehrere Seitenwandabstandshalter **40** benachbart zu der Gate-Elektrode **34** gebildet sind. Das Ausführen des Implantationsprozesses **51** nach der Herstellung der Seitenwandabstandhalter **40** hilft dabei, sicher zu stellen, dass das Vollsubstrat **30A** in dem Bereich unterhalb des Kanalgebiets **44** des Transistors **32** eine relativ hohe Dotierstoffkonzentration beibehält, beispielsweise einen gleichen Pegel, wie die zweite Wanne **52**. Ferner hilft das Aus-

führen des Implantationsprozesses **51** nach der Herstellung der Abstandhalter dabei sicher zu stellen, dass die Source/Drain-Wannen **54**, die eine geringere Dotierstoffkonzentration (im Vergleich zu der zweiten Wanne **52**) besitzen, unter den Source/Drain-Gebieten **42** des Transistors **32** angeordnet werden und einen gewissen Abstand zu dem Kanalgebiet **44** aufweisen. Der Dotierstoffkonzentrationspegel der Source/Drain-Wannen **54** sollte möglichst gering sein, und der Dotierpegel der Wannen **54** kann größer, kleiner oder gleich zu dem Dotierstoffkonzentrationspegel in dem Vollsubstrat **30A** sein.

**[0031]** Danach wird die Maskenschicht **53** der [Fig. 2F](#) entfernt und es werden konventionelle Bearbeitungsverfahren eingesetzt, um die Herstellung des Transistors **32** abzuschließen. Wie beispielsweise in [Fig. 2A](#) gezeigt ist, wird eine Schicht aus isolierenden Material **31** über der aktiven Schicht **32** hergestellt und es werden mehrere Source/Drain-Kontakte **46** gebildet, um eine elektrische Verbindung zu den Source/Drain-Gebieten **42** herzustellen. Ein weiterer Kontakt **60** wird gebildet, um eine elektrische Verbindung zu der ersten Wanne **50** zu schaffen und ein weiterer Kontakt **42** wird gebildet, um eine elektrische Verbindung zu der zweiten Wanne **52** zu schaffen.

**[0032]** Wie hierin beschrieben ist, können einige der diversen dotierten Gebiete mit der gleichen Art an Dotierstoffmaterial, beispielsweise mit N-Leitfähigkeit oder P-Leitfähigkeit, dotiert werden. Für einen anschaulichen NMOS-Transistor werden beispielsweise die zweite Wanne **52**, das Vollsubstrat **30A** und die Source/Drain-Wannen **54** mit einem P-Dotiermaterial dotiert. Jedoch müssen die diversen dotierten Gebiete nicht mit der gleichen Sorte an Dotierstoffmaterial dotiert werden, obwohl in einigen Fällen dies der Fall ist. Beispielsweise kann im Falle eines NMOS-Paarlements das Vollsubstrat **30A** und die zweite Wanne **52** unter Anwendung von Bordiflourid dotiert werden, während die Source/Drain-Wannen **54** mit Bor dotiert werden. Des Weiteren sollte die spezielle Sorte, die bei der Herstellung der diversen gezeigten Implantationsgebiete verwendet wird, nicht als Beschränkung der vorliegenden Erfindung betrachtet werden, sofern derartige Einschränkungen nicht explizit in den angefügten Patentansprüchen aufgenommen sind. Die diversen Implantationsgebiete, die hierin dargestellt sind, werden standardmäßigen Ausheizprozessen nach den Implantationsprozessen unterzogen, oder es wird ein Ausheizprozess bei geringerer Temperatur in dem Bestreben durchgeführt, das Wandern der implantierten Dotierstoffmaterialien zu begrenzen.

**[0033]** Der Aufbau eines Transistors **32** gemäß der vorliegenden Erfindung bietet viele Vorteile. Wenn beispielsweise der Transistor **32** im nicht durchgeschalteten Zustand ist, kann eine negative Spannung

in der Größenordnung von ungefähr –0,1–2,0 Volt an die zweite Wanne **52** über den Kontakt **62** angelegt werden, wodurch Leckströme produziert werden, wenn das Bauelement **32** nicht durchgeschaltet ist. Wenn alternativ der Transistor **32** durchgeschaltet ist, kann die zweite Wanne **52** vorgespannt werden, indem eine Spannung von ungefähr 0,1–1,0 Volt über den Kontakt **62** angelegt wird. Durch Anlegen dieser positiven Vorspannung an die Wanne **52** kann der Durchlassstrom des Transistors **32** erhöht werden, wodurch tendenziell die Gesamtarbeitsgeschwindigkeit des Transistors **32** und der entwickelten Schaltung, die einen derartigen Transistor ausweist, erhöht wird. Diese Möglichkeit, den gleichen Transistor so zu modifizieren, dass dieser einen geringen Leckstrom und einen hohen Durchlassstrom aufweist, ist für die Verwendung in integrierten Schaltungen mit geringer Leistungsaufnahme und großem Leistungsvermögen gut geeignet.

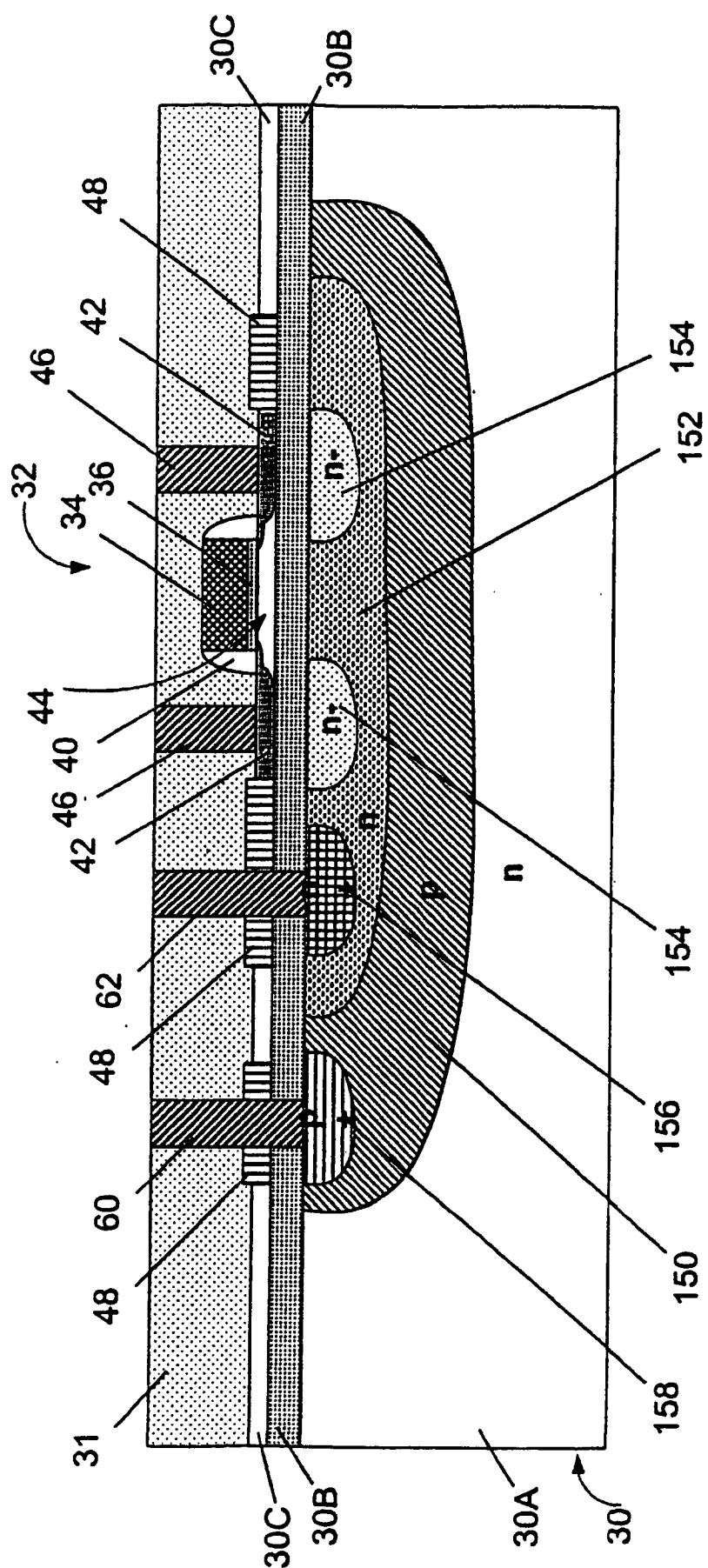

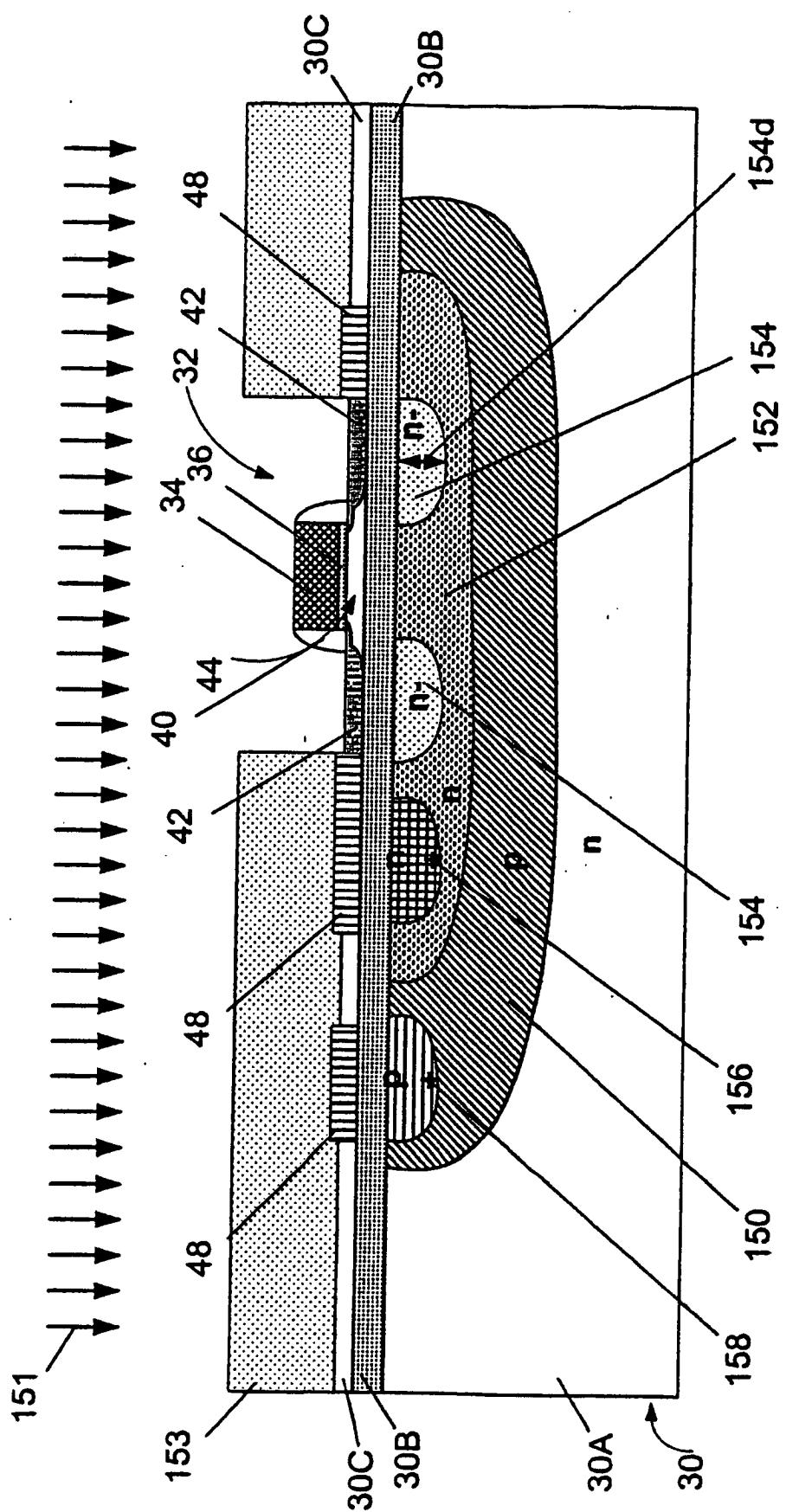

**[0034]** Die [Fig. 3A](#)–[Fig. 3F](#) zeigen die vorliegende Erfindung in der anschaulichen Ausführungsform eines PMOS-Transistors **32**. In der Beschreibung des PMOS-Bauelements werden entsprechende Bezugszeichen für ähnliche Komponenten, wie sie zuvor beschrieben sind, verwendet. Der PMOS-Transistor **32**, der in den [Fig. 3A](#) bis [Fig. 3F](#) dargestellt ist, wird im Allgemeinen durch Ausführen ähnlicher Implantationsprozesse gebildet, wie sie für das NMOS-Bauelement, das in den [Fig. 2A](#) bis [Fig. 2F](#) dargestellt ist, beschrieben sind, wobei entsprechend entgegengesetzte Leitfähigkeitsarten für die Dotierstoffmaterialien verwendet werden. Genauer gesagt, der PMOS-Transistor **32** ist aus einer Gate-Isolationsschicht **36**, der Gate-Elektrode **34**, Seitenwandabstandshaltern **44** und Source/Drain-Gebieten **43** aufgebaut. Ferner sind in [Fig. 3A](#) Isolationsgebiete **48** gezeigt, die in der aktiven Schicht **33** gebildet sind, und es sind mehrere leitende Kontakte **46**, die in einer Schicht aus isolierenden Material **31** hergestellt sind, und weitere Kontakte **60** und **62** dargestellt. Wie in [Fig. 3A](#) gezeigt ist, ist für einen anschaulichen PMOS-Transistor das Vollsubstrat **30A** mit einem N-Dotiermaterial, etwa Arsen oder Phosphor bei einem Konzentrationspegel von ungefähr  $10^{12}$ – $10^{16}$  Ionen/cm<sup>3</sup> dotiert. Eine erste Wanne **150**, eine zweite Wanne **152** Source/Drain-Wannen **154** und Kontaktwannen **156**, **158** sind in dem Vollsubstrat **30A** gemäß den hierin offenbarten Verfahren gebildet. Im Falle eines anschaulichen PMOS-Transistors ist die erste Wanne **150** mit einem P-Dotiermaterial, etwa Bor oder Bordiflourid, bei einem Dotierstoffkonzentrationspegel von ungefähr  $10^{17}$ – $10^{20}$  Ionen/cm<sup>3</sup> dotiert. Im Falle eines PMOS-Bauelements ist die zweite Wanne **152** mit einem N-Dotiermaterial, beispielsweise Arsen oder Phosphor, bei einem Dotierstoffkonzentrationspegel von ungefähr  $10^{16}$ – $10^{19}$  Ionen/cm<sup>3</sup> dotiert. Die Source/Drain-Wannen **154** können durch diverse Gegendorientierverfahren, wie sie nachfolgend detaillierter beschrieben sind, herge-

stellt werden, wobei die resultierende Konzentration der Source/Drain-Wannen **154** im Bereich von ungefähr  $10^{14}$ – $10^{17}$  Ionen/cm<sup>3</sup> eines N-Dotiermaterials für ein PMOS-Bauelement liegt. Die Kontaktwanne **156** ist mit einem N-Dotiermaterial bei relativ hoher Konzentration, beispielsweise  $2 \times 10^{20}$  Ionen/cm<sup>3</sup> oder höher dotiert. In ähnlicher Weise ist die P-Kontaktwanne **158** mit einem ähnlichen Konzentrationspegel von P-Dotierstoffatomen, beispielsweise Bor, Bordiflourid, etc. dotiert. Wie der Fachmann nach dem vollständigen Studium der vorliegenden Anmeldung erkennt, sind die diversen Komponenten des Transistors **32** einschließlich die Art, in der diese gemacht sind und die Materialien des Aufbaus, dem Fachmann gut bekannt und sollten daher nicht als Beschränkung der vorliegenden Erfindung erachtet werden, so werden derartige Beschränkungen nicht speziell in den angefügten Patentansprüchen angegeben sind.

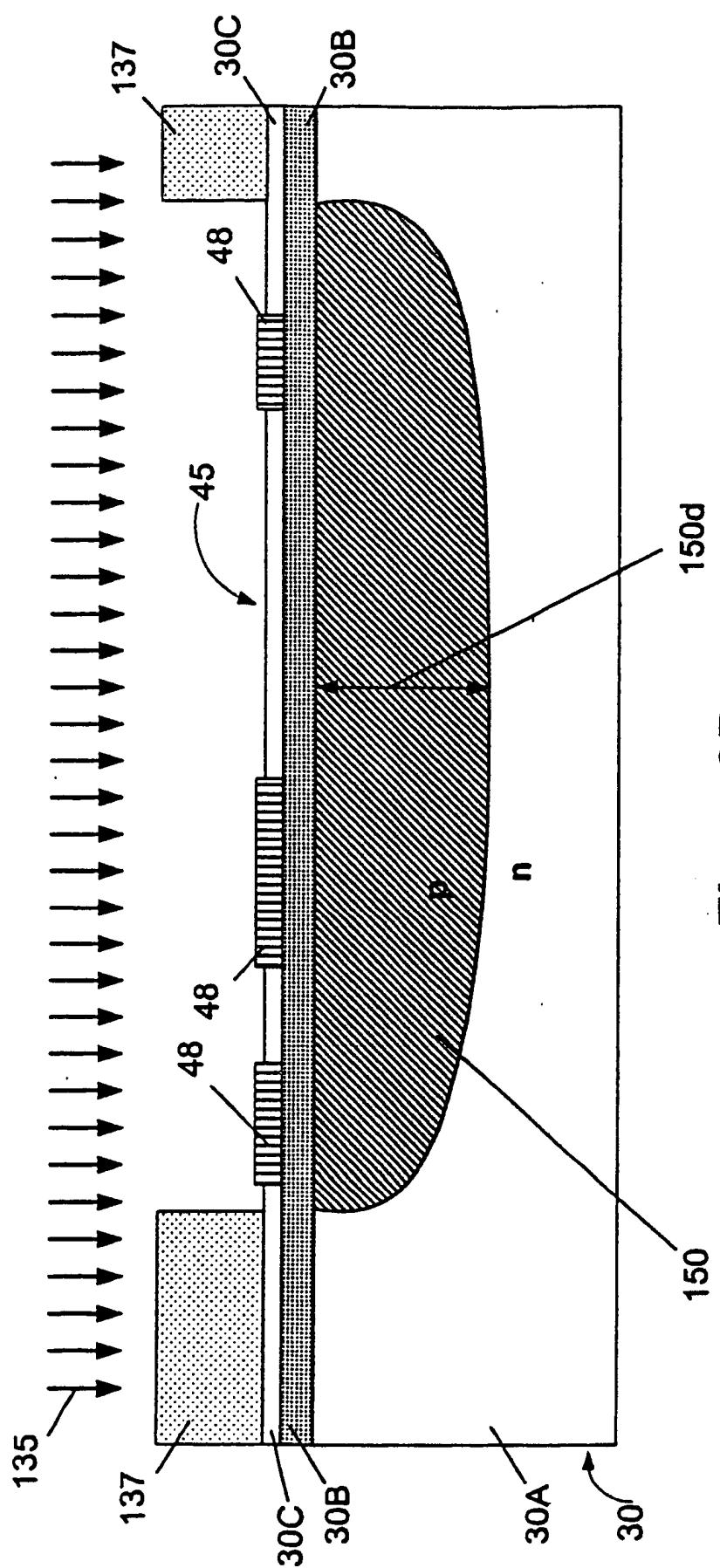

**[0035]** Ein anschauliches Verfahren zur Herstellung des anschaulichen PMOS-Transistors **32**, der in [Fig. 3A](#) gezeigt ist, wird nunmehr mit Bezug zu den [Fig. 3B](#) bis [Fig. 2F](#) beschrieben. Zunächst wird, wie in [Fig. 3B](#) gezeigt ist, eine Maskenschicht **137** über der aktiven Schicht **30C** des Substrats **30** gebildet. Danach wird ein Ionenimplantationsprozess **125** ausgeführt, um die erste Wanne **150** in den Vollsubstrat **30A** zu bilden. Die erste Wanne **150** besitzt eine Tiefe **150d**, die von ungefähr 50–150 nm reichen kann. Im Zusammenhang mit der Herstellung eines PMOS-Bauelements wird der Ionenimplantationsprozess **125** unter Einbindung eines P-Dotiermaterials, etwa Bor, Bordiflourid, etc. bei einer Dotierstoffdosis von ungefähr  $5 \times 10^{10}$ – $1,5 \times 10^{14}$  Ionen/cm<sup>2</sup> ausgeführt. Die sich ergebende erste Wanne **150** besitzt einen Dotierstoffkonzentrationspegel, der von ungefähr  $10^{16}$ – $10^{19}$  Ionen/cm<sup>3</sup> reicht. Die während des Implantationsprozesses **125** verwendete Implantationsenergie kann in Abhängigkeit von der implantierten Dotieratomsorte variieren. In der anschaulichen Ausführungsform, in der Bor das Dotiermaterial ist, kann die Implantationsenergie von ungefähr 10–45 keV variieren.

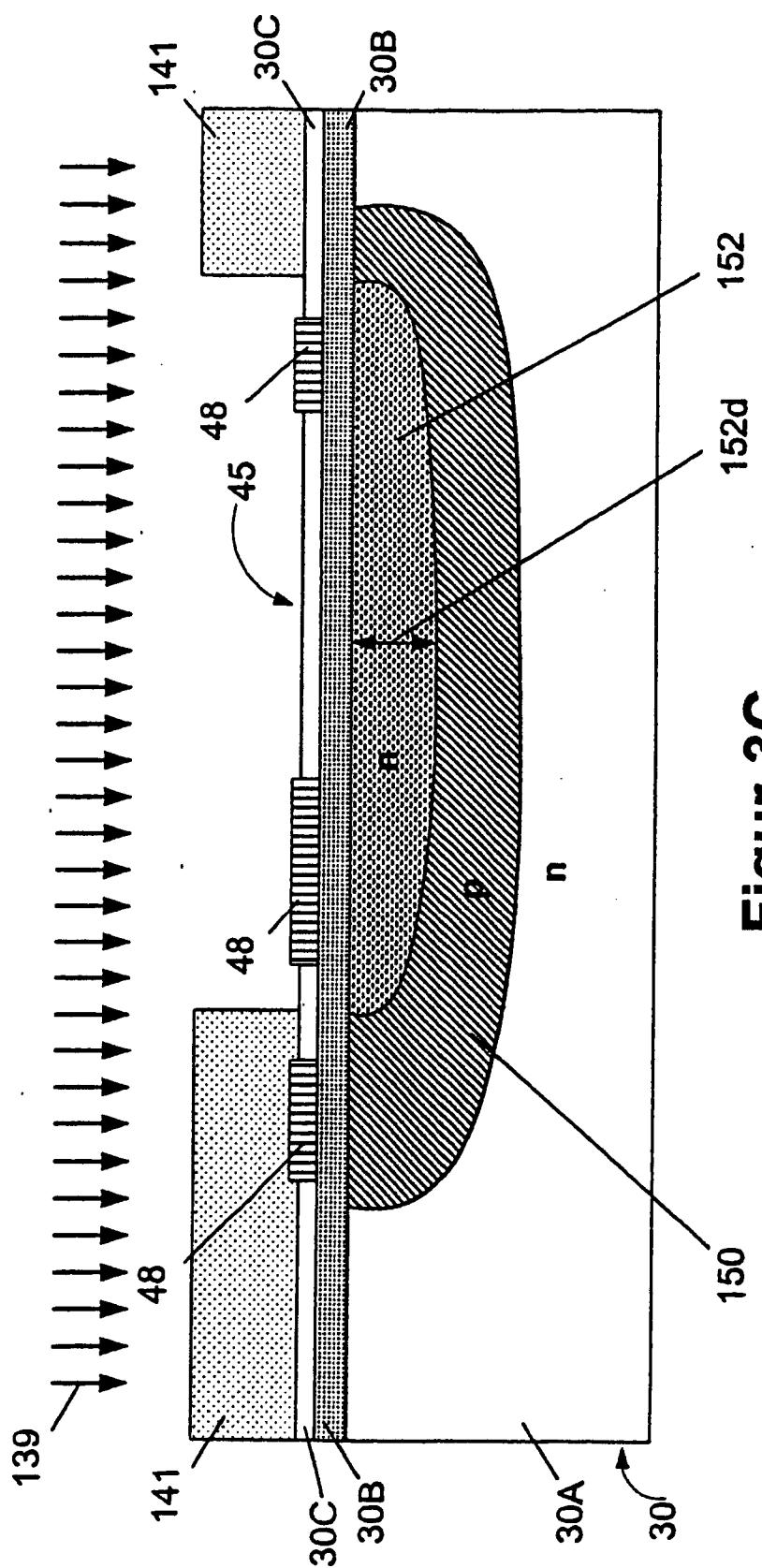

**[0036]** Danach wird, wie in [Fig. 3C](#) gezeigt ist, ein weiterer Ionenimplantationsprozess, der durch die Pfeile **139** bezeichnet ist, durch die Maskenschicht **141** ausgeführt, um die zweite Wanne **152** in dem Vollsubstrat **30A** zu bilden. Die zweite Wanne **152** ist mit einem Dotierstoffmaterial dotiert, das von entgegengesetzter Leitfähigkeitsart im Vergleich zu dem Dotiermaterial ist, das in der ersten Wanne **150** verwendet wird. In dem Falle eines anschaulichen PMOS-Transistors wird die zweite Wanne **152** mit einem N-Dotiermaterial, etwa Arsen, Phosphor, etc. dotiert. Die zweite Wanne **152** besitzt eine Tiefe **152d**, die von ungefähr 40–100 nm variiert. In einer anschaulichen Ausführungsform besitzt die zweite Wanne **152** eine Dotierstoffkonzentration von unge-

fähr  $10^{17}$ – $10^{20}$  Ionen/cm<sup>3</sup>. Im Zusammenhang mit der Herstellung eines PMOS-Bauelements wird der Ionenimplantationsprozess 139 mit einem N-Dotiermaterial ausgeführt, beispielsweise Arsen, Phosphor, etc. bei einer Dotierdosis von ungefähr  $4 \times 10^{11}$ – $1 \times 10^{15}$  Ionen/cm<sup>2</sup>. Die während des Implantationsprozesses 139 verwendete Implantationsenergie hängt von der implantierten Dotierstoffatomsorte ab. In der dargestellten Ausführungsform, in der Arsen das Dotiermaterial ist, variiert die Implantationsenergie von ungefähr 10–35 keV.

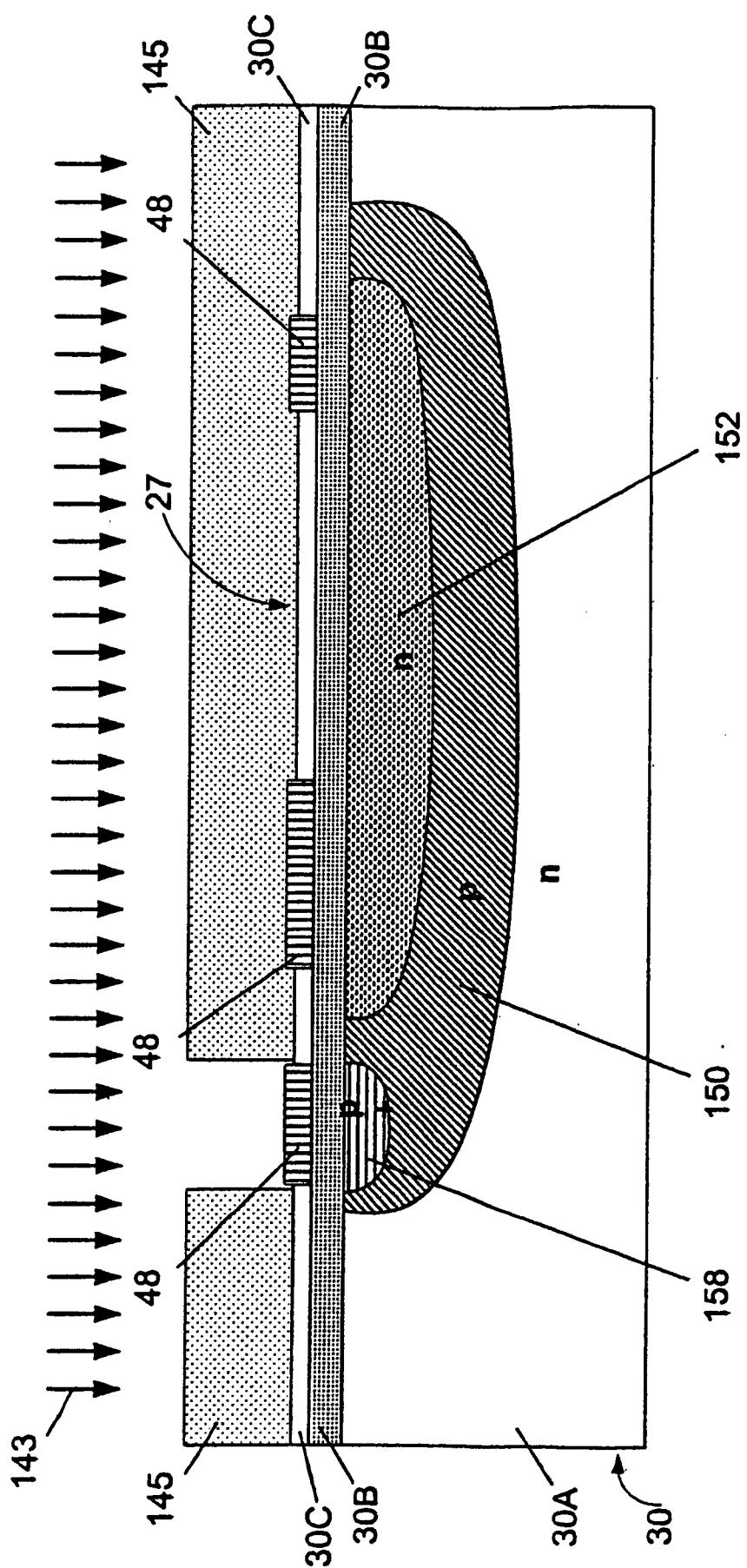

**[0037]** Als nächstes wird, wie in [Fig. 3D](#) gezeigt ist, ein weiterer Ionenimplantationsprozess, der durch die Pfeile 143 gekennzeichnet ist, durch die Maskenschicht 145 durchgeführt, um eine Kontaktwanne 158 für die erste Wanne 150 zu bilden. In dem anschaulichen Beispiel eines PMOS-Transistors wird die Kontaktwanne 158 mit einem P-Dotiermaterial, etwa Bor oder Bordiflourid, dotiert und wird bei einem relativ hohen Konzentrationspegel von ungefähr  $2 \times 10^{20}$  Ionen/cm<sup>3</sup> dotiert. Dies kann erreicht werden, indem eine Implantationsdosis von ungefähr  $2 \times 10^{15}$ – $5 \times 10^{15}$  Ionen/cm<sup>2</sup> angewendet wird. Wie bei den anderen Implantationsprozessen hängt die Implantationsenergie von der während des Implantationsprozesses 143 eingebrachten Dotierstoffsorte ab. In der dargestellten Situation, in der Bor während des Implantationsprozesses 143 eingebracht wird, kann die Implantationsenergie von ungefähr 3–10 keV variieren.

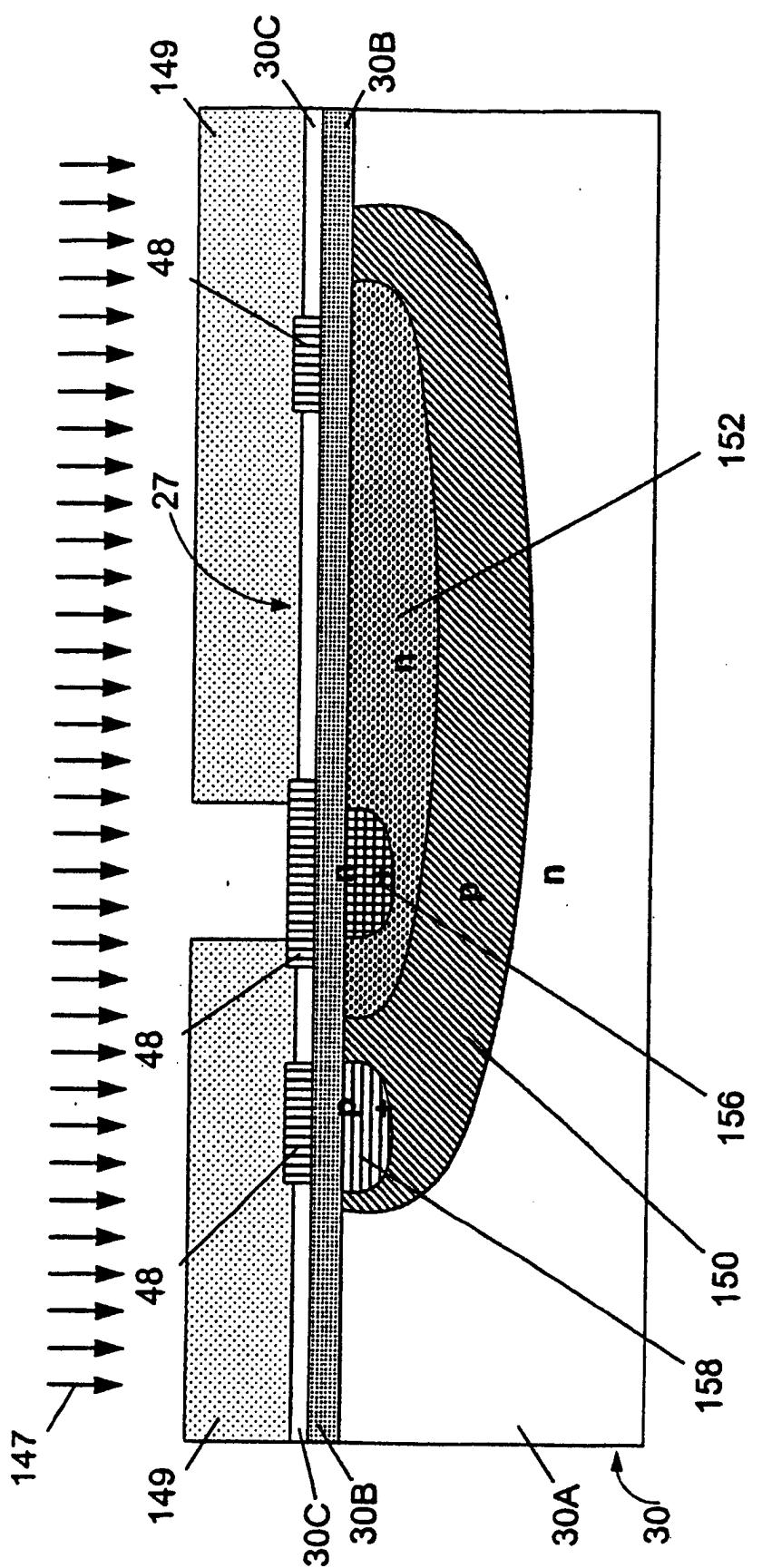

**[0038]** Danach wird, wie in [Fig. 3E](#) gezeigt ist, ein weiterer Ionenimplantationsprozess 147 durch eine Maskenschicht 149 ausgeführt, um eine Kontaktwanne 156 in der zweiten Wanne 152 zu bilden. Im Falle eines anschaulichen PMOS-Transistors ist die Kontaktwanne 156 aus einem N-Dotiermaterial aufgebaut, etwa Arsen, Phosphor, etc. Des Weiteren besitzt die Kontaktwanne 156 einen Dotierstoffkonzentrationspegel von ungefähr  $2 \times 10^{20}$  Ionen/cm<sup>3</sup>. Dies kann erreicht werden, indem eine Implantationsdosis von ungefähr  $2 \times 10^{15}$ – $5 \times 10^{15}$  Ionen/cm<sup>2</sup> angewendet wird. Wie bei den anderen Implantationsprozessen hängt die Implantationsenergie von dem während des Implantationsprozess 143 eingebrachten Dotierstoffmaterial ab. In der anschaulichen Situation, in der Arsen während des Implantationsprozesses 143 eingebracht wird, variiert die Implantationsenergie von ungefähr 10–20 keV. Wie der Fachmann nach dem vollständigen Studium der vorliegenden Anmeldung erkennt, können die Kontaktwannen 156, 158 in einer beliebigen Reihenfolge hergestellt werden.

**[0039]** Anschließend wird, wie in [Fig. 3F](#) gezeigt ist, ein Transistor 32 in der aktiven Schicht 30C des Substrats 30 unter Anwendung üblicher Fertigungsverfahren und Materialien hergestellt. Im Falle eines anschaulichen PMOS-Transistors werden die Source/Drain-Gebiete 42 mit einem geeigneten P-Dotier-

material, etwa Bor oder Bordiflourid, dotiert und werden hergestellt unter Anwendung konventioneller Erweiterungsimplantationsprozesse und Source/Drain-Implantationsprozesse.

**[0040]** Als nächstes wird, wie in [Fig. 3F](#) gezeigt ist, ein Ionenimplantationsprozess, der durch die Pfeile 151 veranschaulicht ist, durch die Maskenschicht 153 ausgeführt, um Source/Drain-Wannen 154 in dem Vollsubstrat 30A in der zweiten Wanne 152 zu bilden. Die Source/Drain-Wannen 154 besitzen eine Tiefe 154d, die von ungefähr 10–90 nm variieren kann. Nach dem Ende des Implantationsprozesses sind die Source/Drain-Wannen 154 aus einem Dotierstoffmaterial der gleichen Leitfähigkeitsart wie das Dotierstoffmaterial, das für die zweite Wanne 154 verwendet wird, aufgebaut, wobei jedoch der Konzentrationspegel des Dotierstoffmaterials in den Source/Drain-Wannen 154 kleiner ist als der Konzentrationspegel des Dotierstoffmaterials in der zweiten Wanne 152. Im Falle eines anschaulichen PMOS-Transistors werden die Source/Drain-Wannen 154 durch eine Gegendotiertechnik hergestellt. Insbesondere werden in einer Ausführungsform die Source/Drain-Wannen 154 durch Implantieren von P-Dotieratomen, beispielsweise Bor oder Bordiflourid, bei einer Dotierstoffdosis im Bereich von ungefähr  $4 \times 10^{11}$ – $1 \times 10^{15}$  Ionen/cm<sup>2</sup> in die N-dotierte zweite Wanne 152 gebildet. Die Implantationsenergie für den Implantationsprozess 151 hängt von der speziellen implantierten Dotierstoffsorte ab. In dem anschaulichen Beispiel, in welchem Bor das Dotierstoffmaterial ist, kann die Implantationsenergie für den Implantationsprozess 151 von ungefähr 10–25 keV variieren. Dies ergibt die Source/Drain-Wannen 154 mit einem N-Dotierkonzentrationspegel von ungefähr  $10^{15}$ – $10^{17}$  Ionen/cm<sup>3</sup>. Ähnlich zu dem NMOS-Bauelement wird der Implantationsprozess 151 angewendet, um die Source/Drain-Wannen 154 zu bilden, wobei dies zu einem beliebigen Zeitpunkt nach der Herstellung der Gate-Elektrode 34 des Bauelements erfolgen kann. Jedoch wird typischerweise der Implantationsprozess ausgeführt, nachdem ein oder mehrere Seitenabstandshalter 40 benachbart zu der Gate-Elektrode 34 hergestellt sind. Danach wird die Maskenschicht 153 aus [Fig. 3F](#) entfernt und übliche Bearbeitungstechniken werden eingesetzt, um die Herstellung des Transistors 32 abzuschließen.

**[0041]** In dieser Ausführungsform wird, wenn der PMOS-Transistor 32 nicht durchgeschaltet ist, eine positive Spannung in der Größenordnung von ungefähr 0,1 bis 2,0 Volt an die zweite Wanne 152 über den Kontakt 162 angelegt, wodurch der Leckstrom des Bauelements 32 im nicht durchgeschalteten Zustand reduziert wird. Wenn alternativ der PMOS-Transistor durchgeschaltet ist, wird die zweite Wanne 152 negativ vorgespannt, indem eine Spannung von ungefähr –0,1 bis –1,0 Volt über den Kontakt 162 angelegt wird. Durch Anlegen dieser negati-

ven Vorspannung an die Wanne **152** kann der Durchlassstrom des PMOS-Transistors **32** erhöht werden, wodurch auch tendenziell die Gesamtarbeitsgeschwindigkeit des PMOS-Transistors **32** und damit einer integrierten Schaltung, in der ein derartiger Transistor eingesetzt ist, erhöht werden kann.

**[0042]** Die vorliegende Erfindung richtet sich im Allgemeinen an eine vorgespannte vollständig verarmte SOI-Struktur mit Dreifachwanne und diverse Verfahren zur Herstellung und Betreiben des selben. In einer anschaulichen Ausführungsform umfasst das Bauelement einen Transistor, der über einem Silizium-auf-Isolator-Substrat ausgebildet ist, das ein Vollsubstrat, ein vergrabende isolierende Schicht und eine aktive Schicht aufweist, wobei das Vollsubstrat mit einer ersten Art an Dotierstoffmaterial dotiert ist und wobei eine erste Wanne in dem Vollsubstrat ausgebildet ist, wobei die erste Wanne mit einer zweiten Art an Dotierstoffmaterial dotiert ist, die von entgegengesetzter Leitfähigkeitsart im Vergleich zu der ersten Art am Dotierstoffmaterial ist. Das Bauteil umfasst ferner eine zweite Wanne, die in dem Vollsubstrat in der ersten Wanne ausgebildet ist, wobei die zweite Wanne mit einem zweiten Dotierstoffmaterial der gleichen Leitfähigkeitart wie das erste Dotierstoffmaterial dotiert ist, wobei der Transistor in der aktiven Schicht über der zweiten Wanne ausgebildet ist, und eine elektrischer Kontakt für die erste Wanne und eine elektrischer Kontakt für die zweite Wanne vorgesehen ist. In weiteren Ausführungsformen umfasst der Transistor ferner mehrere Source/Drain-Gebiete und eine Source/Drain-Wanne ist in dem Vollsubstrat in der zweiten Wanne unter jedem Source/Drain-Gebiet ausgebildet. Die Source/Drain-Wannen sind aus einem Dotierstoffmaterial aufgebaut, das von der gleichen Leitfähigkeitsart wie das erste Dotierstoffmaterial ist, wobei jedoch die Source/Drain-Wannen einen Dotierstoffkonzentrationspegel für das erste Dotierstoffmaterial aufweisen, der geringer ist als ein Dotierstoffkonzentrationspegel des ersten Dotierstoffmaterials in der zweiten Wanne.

**[0043]** In einer anschaulichen Ausführungsform wird ein Verfahren zur Herstellung eines Transistors über einem Silizium-auf-Isolator-Substrat offenbart, das ein Vollsubstrat, eine vergrabene Oxydschicht und eine aktive Schicht umfasst, wobei das Vollsubstrat mit einer ersten Art an Dotierstoffmaterial dotiert ist. Das Verfahren umfasst: Ausführen eines ersten Implantationsprozesses unter Anwendung einer zweiten Art an Dotierstoffmaterial, die von entgegen gesetzter Leitfähigkeitsart zu dem ersten Dotierstoffmaterial ist, um ein erstes Wannengebiet innerhalb des Vollsubstrats zu bilden, Ausführen eines zweiten Ionenimplantationsprozesses unter Anwendung eines Dotierstoffmaterials, das von der gleichen Leitfähigkeitsart wie die erste Art des Dotierstoffmaterials ist, um ein zweites Wannengebiet in dem Vollsubstrat innerhalb der ersten Wanne zu bilden, wobei der

Transistor in der aktiven Schicht über der zweiten Wanne gebildet wird, Bilden eines leitenden Kontakts zu der ersten Wanne und Bilden eines leitenden Kontakts zu der zweiten Wanne. In weiteren Ausführungsformen umfasst das Verfahren ferner mehrere Source/Drain-Gebiete, wobei das Verfahren ferner umfasst: Ausführen eines dritten Ionenimplantationsprozesses unter Anwendung eines Dotierstoffmaterials, das von entgegengesetzter Leitfähigkeitsart im Vergleich zum ersten Dotierstoffmaterial ist, um damit eine Source/Drain-Wanne in dem Vollsubstrat unter jedem der mehreren Source/Drain-Gebiet des Transistors zu erhalten, wobei die Source/Drain-Wannen einen Dotierstoffkonzentrationspegel der ersten Art an Dotierstoffmaterial besitzen, der kleiner ist als ein Dotierstoffkonzentrationspegel der ersten Art eines Dotierstoffmaterials in der zweiten Wanne.

**[0044]** Die speziellen hierin offenbarten Ausführungsformen sind lediglich anschaulicher Natur, da die Erfindung auf unterschiedliche Weisen modifiziert und praktiziert werden kann, wie sich dies dem Fachmann nach dem Studium der technischen Lehre hierin erschließt. Beispielsweise können die Prozessschritte, wie sie zuvor dargestellt sind, in einer anderen Reihenfolge ausgeführt werden. Ferner sind keine Einschränkungen im Hinblick auf die Details des Aufbaus oder der hierin gezeigten Gestaltung beabsichtigt, sofern sie nicht nachfolgend in den Ansprüchen beschrieben sind. Es ist daher selbstverständlich, dass die speziellen zuvor offenbarten Ausführungsformen geändert oder modifiziert werden können und dass alle derartigen Variationen als innerhalb des Schutzbereichs der Erfindung liegend erachtet werden. Folglich ist der hierin angestrebte Schutzbereich durch die nachfolgenden Patentansprüche festgelegt.

## Patentansprüche

1. Vorrichtung mit:

einem Transistor (**32**), der auf einem Silizium-auf-Isolations-Substrat (**30**) ausgebildet ist, das ein Masse-Substrat (**30A**), eine vergrabene Isolationsschicht (**30B**) und eine aktive Schicht (**30C**) aufweist, wobei das Masse-Substrat (**30A**) mit einem Dotierungsma terial eines ersten Typs dotiert ist;

einer ersten Wanne (**50**), die in dem Masse-Substrat (**30A**) ausgebildet ist, wobei die erste Wanne (**50**) mit einem Dotierungsmaterial eines zweiten Typs dotiert ist, der dem ersten Dotierungsmaterial-Typ entgegengesetzt ist;

einer zweiten Wanne (**52**), die in dem Masse-Substrat (**30A**) in der ersten Wanne (**50**) ausgebildet ist, wobei die zweite Wanne (**52**) mit einem Dotierungsmaterial des gleichen Typs wie der erste Dotierungsmaterial-Typ dotiert ist, wobei der Transistor (**32**) in der aktiven Schicht (**30C**) über der zweiten Wanne (**52**) ausgebildet ist;

einem elektrischen Kontakt (**60**) für die erste Wanne

(50); und einem elektrischen Kontakt (62) für die zweite Wanne (52); dadurch gekennzeichnet, dass der Transistor (32) in einem Teil der aktiven Schicht (30C) ausgebildet ist, der über einem durch die zweite Wanne (52) definierten Bereich liegt, derart, dass bei Betrieb der Leckstrom und der Treiberstrom des Transistors (32) durch eine auf den elektrischen Kontakt (62) für die zweite Wanne (52) angelegte Spannung moduliert werden können.

2. Vorrichtung nach Anspruch 1, ferner mit einer Kontakt-Wanne (58), die in dem Masse-Substrat (30A) in der ersten Wanne (50) ausgebildet ist, wobei die Kontakt-Wanne (58) ein Dotierungsmaterial aufweist, das vom gleichen Typ wie der zweite Dotierungsmaterial-Typ ist, wobei die in der ersten Wanne (50) ausgebildete Kontakt-Wanne (58) ein Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des zweiten Typs aufweist, das größer ist als das Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des zweiten Typs in der ersten Wanne (50).

3. Vorrichtung nach Anspruch 1 oder Anspruch 2, ferner mit einer Kontakt-Wanne (56), die in dem Masse-Substrat (30A) in der zweiten Wanne (52) ausgebildet ist, wobei die Kontakt-Wanne (56) ein Dotierungsmaterial aufweist, das vom gleichen Typ wie der erste Dotierungsmaterial-Typ ist, wobei die in der zweiten Wanne (52) ausgebildete Kontakt-Wanne (56) ein Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des ersten Typs aufweist, das größer ist als das Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des ersten Typs in der zweiten Wanne (52).

4. Vorrichtung nach einem der Ansprüche 1 bis 3, bei der der Transistor (32) ferner mehrere Source-/Drain-Bereiche (42) aufweist und die Vorrichtung ferner in dem Masse-Substrat (30A) in der zweiten Wanne (52) unter jedem der Source-/Drain-Bereiche (42) eine Source-/Drain-Wanne (54) aufweist, wobei die Source-/Drain-Wannen (54) ein Dotierungsmaterial aufweisen, das vom gleichen Typ wie der erste Dotierungsmaterial-Typ ist, wobei die Source-/Drain-Wannen (54) ein Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des ersten Typs aufweisen, das kleiner ist als das Dotierungsmaterial-Konzentrationsniveau des in der zweiten Wanne (52) ausgebildeten Dotierungsmaterials des ersten Typs.

5. Vorrichtung nach einem der Ansprüche 1 bis 4, bei der das Masse-Substrat (30A) Silicium aufweist, wobei die vergrabene Isolationsschicht (30B) Siliciumdioxid aufweist und die aktive Schicht (30C) Silicium aufweist.

6. Vorrichtung nach einem der Ansprüche 1 bis 5, bei der das Masse-Substrat (30A) ein Dotierungsmaterial-Konzentrationsniveau im Bereich von ungefähr  $10^{12}$ – $10^{16}$  Ionen/cm<sup>3</sup> aufweist.

7. Vorrichtung nach einem der Ansprüche 1 bis 6, bei der die erste Wanne (50) ein Dotierungsmaterial-Konzentrationsniveau im Bereich von ungefähr  $10^{16}$ – $10^{19}$  Ionen/cm<sup>3</sup> aufweist.

8. Vorrichtung nach einem der Ansprüche 1 bis 7, bei der die zweite Wanne (52) ein Dotierungsmaterial-Konzentrationsniveau im Bereich von ungefähr  $10^{17}$ – $10^{20}$  Ionen/cm<sup>3</sup> aufweist.

9. Vorrichtung nach Anspruch 2, bei der die Kontakt-Wanne (58) in der ersten Wanne (50) ein Dotierungsmaterial-Konzentrationsniveau von ungefähr  $2e^{20}$  Ionen/cm<sup>3</sup> aufweist.

10. Vorrichtung nach Anspruch 3, bei der die Kontakt-Wanne (56) in der zweiten Wanne (52) ein Dotierungsmaterial-Konzentrationsniveau von ungefähr  $2e^{20}$  Ionen/cm<sup>3</sup> aufweist.

11. Vorrichtung nach Anspruch 4, bei der die Source-/Drain-Wannen (54) ein Dotierungsmaterial-Konzentrationsniveau im Bereich von ungefähr  $10^{14}$ – $10^{17}$  Ionen/cm<sup>3</sup> aufweisen.

12. Vorrichtung nach einem der Ansprüche 1 bis 11, bei der die erste Wanne (50) eine Tiefe im Bereich von ungefähr 50–150 nm hat.

13. Vorrichtung nach einem der Ansprüche 1 bis 12, bei der die zweite Wanne (52) eine Tiefe im Bereich von ungefähr 40–100 nm hat.

14. Vorrichtung nach Anspruch 4, bei der die Source-/Drain-Wannen (54) eine Tiefe im Bereich von ungefähr 10–90 nm haben.

15. Verfahren zum Ausbilden einer Vorrichtung in einem Silicium-auf-Isolations-Substrat (30), das ein Masse-Substrat (30A), eine vergrabene Isolations-schicht (30B) und eine aktive Schicht (30C) aufweist, wobei das Masse-Substrat (30A) mit einem Dotierungsmaterial eines ersten Typs dotiert ist, wobei das Verfahren folgende Schritte umfasst:

Durchführen eines ersten Ionenimplantations-Vor-gangs (35) mit einem Dotierungsmaterial eines dem ersten Dotierungsmaterial-Typs entgegengesetzten Typs zum Ausbilden eines ersten Wannenbereichs (50) in dem Masse-Substrat (30A);

Durchführen eines zweiten Ionenimplantations-Vor-gangs (39) mit einem Dotierungsmaterial des gleichen Typs wie der erste Dotierungsmaterial-Typ zum Ausbilden eines zweiten Wannenbereichs (52) in dem Masse-Substrat (30A) in der ersten Wanne (50); Ausbilden eines Transistors (32) in der aktiven

Schicht (**30C**) über der zweiten Wanne (**52**); Ausbilden eines elektrischen Kontakts (**60**) für die erste Wanne (**50**); und Ausbilden eines elektrischen Kontakts (**62**) für die zweite Wanne (**52**); dadurch gekennzeichnet, dass der Transistor (**32**) in einem Teil der aktiven Schicht (**30C**) ausgebildet ist, der über einem durch die zweite Wanne (**52**) definierten Bereich liegt, derart, dass bei Betrieb der Leckstrom und der Treiberstrom des Transistors (**32**) durch eine auf den elektrischen Kontakt (**62**) für die zweite Wanne (**52**) angelegte Spannung moduliert werden können.

16. Verfahren nach Anspruch 15, bei dem der Transistor (**32**) mehrere Source-/Drain-Bereiche (**42**) aufweist, und wobei das Verfahren ferner das Durchführen eines dritten Ionenimplantations-Vorgangs (**51**) mit einem Dotierungsmaterial eines dem ersten Dotierungsmaterial-Typ entgegengesetzten Typs umfasst, derart, dass in dem Masse-Substrat (**30A**) unter jedem der Source-/Drain-Bereiche (**42**) eine Source/Drain-Wanne (**42**) entsteht, wobei die Source-/Drain-Wannen (**54**) ein Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des ersten Typs aufweisen, das kleiner ist als das Dotierungsmaterial-Konzentrationsniveau des in der zweiten Wanne (**52**) ausgebildeten Dotierungsmaterials des ersten Typs.

17. Verfahren nach Anspruch 16, bei dem der Transistor (**32**) ferner eine Gate-Elektrode (**34**) aufweist und bei dem der dritte Ionenimplantations-Vorgang (**51**) nach dem Bilden der Gate-Elektrode (**34**) durchgeführt wird.

18. Verfahren nach Anspruch 16, bei dem der Transistor (**32**) ferner eine Gate-Elektrode (**34**) und einen Seitenwand-Abstandhalter (**40**) aufweist und bei dem der dritte Ionenimplantations-Vorgang (**51**) nach dem Bilden des Seitenwand-Abstandhalter (**40**) durchgeführt wird.

19. Verfahren nach einem der Ansprüche 15 bis 18, ferner mit dem Durchführen eines zusätzlichen Ionenimplantationsvorgangs (**42**) zur Bildung einer Kontakt-Wanne (**58**) in dem Masse-Substrat (**30A**) in der ersten Wanne (**50**), wobei der zusätzliche Ionenimplantationsvorgang (**42**) mit einem Dotierungsmaterial eines zweiten Typs durchgeführt wird, der dem ersten Dotierungsmaterial-Typ entgegengesetzt ist, wobei die Kontakt-Wanne (**58**) ein Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des zweiten Typs aufweist, das größer ist als das Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des zweiten Typs in der ersten Wanne (**50**).

20. Verfahren nach einem der Ansprüche 15 bis 19, ferner mit dem Durchführen eines zusätzlichen

Ionenimplantationsvorgangs (**47**) zur Bildung einer Kontakt-Wanne (**56**) in dem Masse-Substrat (**30A**) in der zweiten Wanne (**52**), wobei der zusätzliche Ionenimplantationsvorgang (**47**) mit einem Dotierungsmaterial des gleichen Typs wie der erste Dotierungsmaterial-Typ durchgeführt wird, wobei die Kontakt-Wanne (**56**) ein Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des ersten Typs aufweist, das größer ist als das Dotierungsmaterial-Konzentrationsniveau des Dotierungsmaterials des ersten Typs in der zweiten Wanne (**52**).

Es folgen 13 Blatt Zeichnungen

**Figur 1**

(Stand der Technik)

**Figur 2A**

Figur 2B

Figure 2C

Figur 2D

Figur 2E

Figure 2F

Figur 3A

**Figur 3B**

**Figur 3C**

**Figur 3D**

Figur 3E

Figur 3F