(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-24657

(P2006-24657A)

(43) 公開日 平成18年1月26日(2006.1.26)

|                      |            |             |

|----------------------|------------|-------------|

| (51) Int.CI.         | F 1        | テーマコード (参考) |

| H01L 23/29 (2006.01) | H01L 23/30 | B 4M109     |

| H01L 23/31 (2006.01) | H01L 23/12 | 501B        |

| H01L 23/12 (2006.01) |            |             |

審査請求 未請求 請求項の数 4 O L (全 10 頁)

|           |                              |          |                                             |

|-----------|------------------------------|----------|---------------------------------------------|

| (21) 出願番号 | 特願2004-199949 (P2004-199949) | (71) 出願人 | 000005821<br>松下電器産業株式会社<br>大阪府門真市大字門真1006番地 |

| (22) 出願日  | 平成16年7月7日 (2004.7.7)         | (74) 代理人 | 100113859<br>弁理士 板垣 孝夫                      |

|           |                              | (74) 代理人 | 100068087<br>弁理士 森本 義弘                      |

|           |                              | (74) 代理人 | 100096437<br>弁理士 笹原 敏司                      |

|           |                              | (74) 代理人 | 100100000<br>弁理士 原田 洋平                      |

|           |                              | (72) 発明者 | 竹村 康司<br>大阪府門真市大字門真1006番地 松下<br>電器産業株式会社内   |

|           |                              |          | F ターム (参考) 4M109 AA02 BA03 CA04             |

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】 層間絶縁膜の機械的強度が弱くても、樹脂硬化時やパッケージ組立時に加わる応力にも耐えうるパッケージ構造となり、信頼性を向上することを目的とする。

【解決手段】 半導体素子とインターポーネント基板の間を低応力樹脂で充填被覆し、チップ周辺部、さらには、チップ上部までを、高剛性樹脂16で被覆することにより、半導体装置の剛性が向上し、層間絶縁膜の機械的強度が弱くても、樹脂硬化時やパッケージ組立時に加わる応力にも耐えうるパッケージ構造となり、信頼性を向上することができる。

【選択図】 図5

**【特許請求の範囲】****【請求項 1】**

インターポーラ基板に半導体素子を搭載して成る半導体装置であって、前記インターポーラ基板と前記半導体素子の間に素子形成層が被覆されるような樹脂フィレットが形成されるように充填被覆される第1の樹脂と、前記第1の樹脂より剛性が高く前記樹脂フィレット上を被覆する第2の樹脂とを有することを特徴とする半導体装置。

**【請求項 2】**

インターポーラ基板に半導体素子を搭載して成る半導体装置であって、前記インターポーラ基板と前記半導体素子の間に素子形成層が被覆されるような樹脂フィレットが形成されるように充填被覆される第1の樹脂と、前記第1の樹脂より熱膨張性が低く前記樹脂フィレット上を被覆する第2の樹脂とを有することを特徴とする半導体装置。

**【請求項 3】**

インターポーラ基板に半導体素子を搭載して成る半導体装置であって、前記インターポーラ基板と前記半導体素子の間に素子形成層が被覆されるような樹脂フィレットが形成されるように充填被覆される第1の樹脂と、前記第1の樹脂より剛性が高く前記樹脂フィレット上および前記半導体素子を被覆する第2の樹脂とを有することを特徴とする半導体装置。

**【請求項 4】**

インターポーラ基板に半導体素子を搭載して成る半導体装置であって、前記インターポーラ基板と前記半導体素子の間に素子形成層が被覆されるような樹脂フィレットが形成されるように充填被覆される第1の樹脂と、前記第1の樹脂より熱膨張性が低く前記樹脂フィレット上および前記半導体素子を被覆する第2の樹脂とを有することを特徴とする半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、樹脂封止構造を有する半導体装置に関するものである。

**【背景技術】****【0002】**

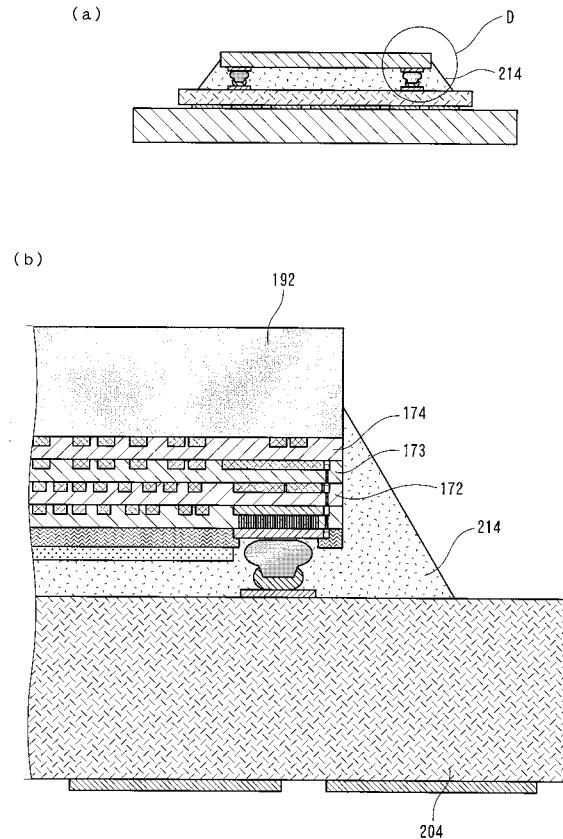

図7、図8、図9、図10を用いて従来の半導体装置について説明する。

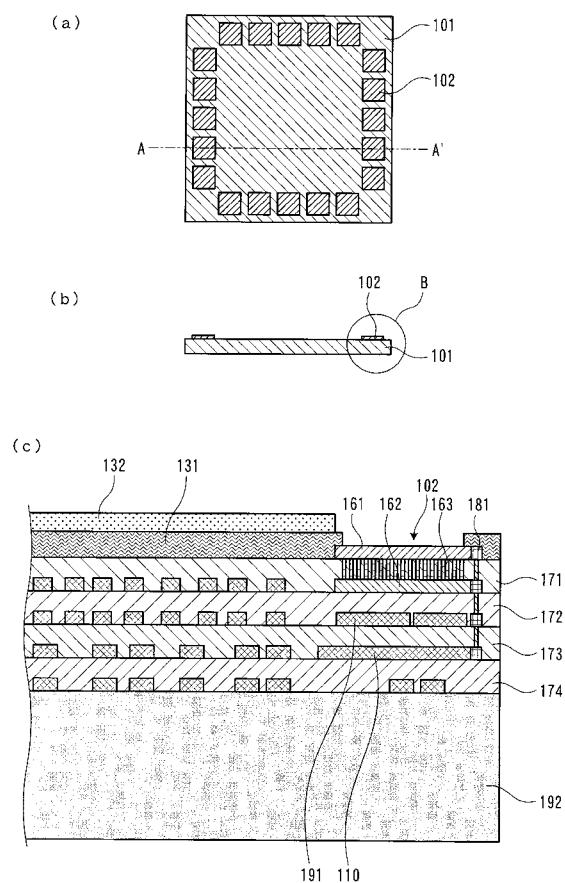

図7(a)は従来の半導体装置の平面図、図7(b)は従来の半導体装置の断面図、図7(c)は従来の半導体装置における入出力回路部分の拡大断面図であり、半導体装置の一般的な入出力回路のレイアウトを示す。また、図7(c)は図7(b)のB部拡大図である。本図面では、5層配線構造の場合を示している。以下、本発明の説明では、入出力回路の素子領域上にパッドを形成した構造を、素子上パッド：P O E (Pad On Element)パッドと称する。

**【0003】**

101は半導体素子、102は周辺P O Eパッドである。131はP S i Nなどの第1の保護膜、132はポリイミドなどの第2の保護膜、171は層間絶縁膜、192はシリコン基板である。また、拡散プロセスの微細化による配線遅延への対応として、層間絶縁膜172、層間絶縁膜173、層間絶縁膜174には、これまでよりも誘電率の低いいわゆるlow-k材料が用いられている。周辺P O Eパッド102は、最上層のパッドメタル161とそのひとつ下の配線層に形成された下層パッドメタル162、およびこれらパッドメタル間を接続するビア163からなる、積層ビア構造を有している。積層ビア構造は、ワイヤボンドなどのボンディング工程で生じるクレタリングを抑制するのに効果がある。これらパッドの下には、電源供給のための、第1の電源層メタル191、さらに下層

10

20

30

40

50

には、入出力回路内への信号供給のための最下層メタル 110 が形成されており、周辺 P O E パッドと最下層メタル 110 は、引出し部メタル 181 のスタック構造により電気的に接続されている。

#### 【 0 0 0 4 】

このような電極パッドを I / O セルの素子形成領域上に配置した構造が、チップサイズの縮小を目的として、各社から提案されている。

例えば、ロジック回路やドライバ回路の上に層間絶縁膜を設け、その上に入力パッド、あるいは出力パッドを形成した半導体集積回路を提案している（特許文献 1 参照）。

#### 【 0 0 0 5 】

次に、従来のチップサイズパッケージ（以下、C S P と称す）と呼ばれる半導体装置およびその製造方法について図面を参照しながら説明する。

10

図 8 は従来の C S P における金属突起を形成する工程を説明する図、図 9 は従来の C S P の製造工程を説明する工程断面図、図 10 は従来の C S P を示す断面図である。

#### 【 0 0 0 6 】

図 8において、半導体素子 101 の周辺 P O E パッド 102 上に（図 8 ( a ) ）、通常のワイヤボンダーを用いて金属突起 208 を以下の方針を用いて形成する。

まず、金属線 141 先端に金属ボール 142 を形成し、キャピラリー 143 を用いて半導体素子 145 上のパッド 144 に超音波振動を加えながら加圧し、クランプ 146 を用いて金属線を固定し、キャピラリー 143 を上方に移動させ金属線 141 を引きちぎる。その後、平坦化ツール 147 を用いて金属突起 208 の高さを規定値に平坦化する（図 8 ( b ) ）。

20

#### 【 0 0 0 7 】

以上のようにして形成された金属突起 208 が（図 9 ( a ) ）、位置合わせを行った後に導電性接続材料 209 によりインターポーヴ基板 204 の電極 210 と接続される（図 9 ( b ) ）。次に、適温に保持した樹脂封止用加熱ステージ 211 上に半導体素子を搭載したインターポーヴ基板 204 を支持し、インターポーヴ基板 204 上の半導体素子の 1 辺から樹脂ノズル 213 を用いて樹脂 212 を一定量塗布する（図 9 ( c ) ）。この際、樹脂封止用加熱ステージは水平でも、樹脂が浸入しやすい方向に傾斜させてもよい。塗布した樹脂が半導体素子とインターポーヴ基板間に注入されたことを確認した後、2 回目の樹脂を適量塗布する。この動作を繰り返し、所定量を塗布した後、樹脂封止用加熱ステージ上で半導体素子周辺部に樹脂フィレット 214 が形成されるまで放置する（図 10 ( a ) ）。図 10 ( b ) は、図 10 ( a ) の D 部分の拡大図である。この際、樹脂フィレット 214 が形成されやすいうように、また形成スピードを上昇させるために樹脂封止用加熱ステージを傾斜させてもよい。最後に、オープン中で樹脂の加熱硬化を行うことにより、半導体装置を完成させる。

30

【特許文献 1】特開平 6 - 244235 号公報

【特許文献 2】特開平 11 - 238745 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【 0 0 0 8 】

しかしながら、上記従来の半導体装置では、封止樹脂硬化工程における封止樹脂硬化収縮が半導体材料の熱収縮よりも大きく、結果として応力がチップ表面付近の層間絶縁膜に直接作用する。また、パッケージ組立後の外部環境温度変化を受け、チップ、封止樹脂、インターポーヴ基板の熱膨張係数差による応力がチップ表面付近の層間絶縁膜に発生する。そして、低誘電率の層間絶縁膜 172、173、174 は従来用いられていた層間絶縁膜よりも機械的強度が格段に弱い。このため、層間絶縁膜が各種応力に耐え切れずに、特にチップ周辺部で破壊、剥離してしまうという課題があり、信頼性上大きな問題となっていた。

#### 【 0 0 0 9 】

本発明は上記従来の問題点を解決するもので、層間絶縁膜の機械的強度が弱くても、樹

40

脂硬化時やパッケージ組立時に加わる応力にも耐えうるパッケージ構造となり、信頼性を向上することを目的とする。

**【課題を解決するための手段】**

**【0010】**

上記目的を達成するために、本発明の請求項1記載の半導体装置は、インターポーザ基板に半導体素子を搭載して成る半導体装置であって、前記インターポーザ基板と前記半導体素子の間に素子形成層が被覆されるような樹脂フィレットが形成されるように充填被覆される第1の樹脂と、前記第1の樹脂より剛性が高く前記樹脂フィレット上を被覆する第2の樹脂とを有することを特徴とする。

**【0011】**

請求項2記載の半導体装置は、インターポーザ基板に半導体素子を搭載して成る半導体装置であって、前記インターポーザ基板と前記半導体素子の間に素子形成層が被覆されるような樹脂フィレットが形成されるように充填被覆される第1の樹脂と、前記第1の樹脂より熱膨張性が低く前記樹脂フィレット上を被覆する第2の樹脂とを有することを特徴とする。

**【0012】**

請求項3記載の半導体装置は、インターポーザ基板に半導体素子を搭載して成る半導体装置であって、前記インターポーザ基板と前記半導体素子の間に素子形成層が被覆されるような樹脂フィレットが形成されるように充填被覆される第1の樹脂と、前記第1の樹脂より剛性が高く前記樹脂フィレット上および前記半導体素子を被覆する第2の樹脂とを有することを特徴とする。

**【0013】**

請求項4記載の半導体装置は、インターポーザ基板に半導体素子を搭載して成る半導体装置であって、前記インターポーザ基板と前記半導体素子の間に素子形成層が被覆されるような樹脂フィレットが形成されるように充填被覆される第1の樹脂と、前記第1の樹脂より熱膨張性が低く前記樹脂フィレット上および前記半導体素子を被覆する第2の樹脂とを有することを特徴とする。

**【0014】**

以上により、層間絶縁膜の機械的強度が弱くても、樹脂硬化時やパッケージ組立時に加わる応力にも耐えうるパッケージ構造となり、信頼性を向上することができる。

**【発明の効果】**

**【0015】**

本発明の半導体装置は、半導体素子とインターポーザ基板の間を低応力樹脂で充填被覆し、チップ周辺部、さらには、チップ上部までを、高剛性樹脂で被覆することにより、半導体装置の剛性が向上し、層間絶縁膜の機械的強度が弱くても、樹脂硬化時やパッケージ組立時に加わる応力にも耐えうるパッケージ構造となり、信頼性を向上することができる。

**【発明を実施するための最良の形態】**

**【0016】**

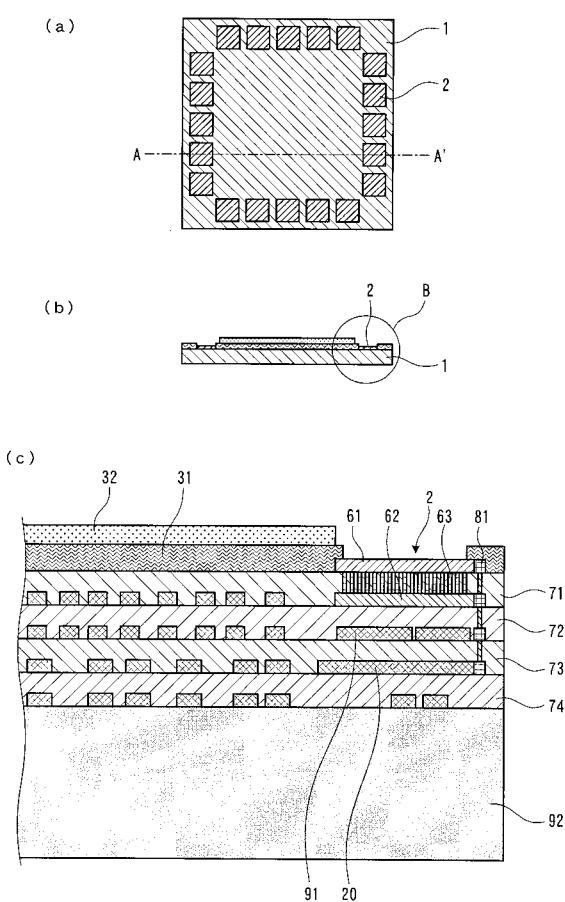

本発明の実施の形態1における半導体装置について、以下図面を参照しながら説明する。

図1(a)は実施の形態1における半導体装置の平面図、図1(b)は実施の形態1における半導体装置の断面図、図1(c)は実施の形態1の半導体装置における入出力回路部分の拡大断面図であり、半導体装置の一般的な入出力回路のレイアウトを示す。また、図1(c)は図1(b)のB部拡大図である。

図1では、5層配線構造の場合を示している。以下、本発明の説明では、従来、入出力回路外側にあった入出力パッドを、入出力回路の素子領域上に形成した構造をとり、素子上パッド：P O E ( P a d O n E l e m e n t )と称する。

**【0017】**

図1において、1は半導体素子、2は周辺P O Eパッドである。31はP S i Nなどの

10

20

30

40

50

第1の保護膜、32はポリイミドなどの第2の保護膜、71は層間絶縁膜、92はシリコン基板である。また、拡散プロセスの微細化による配線遅延への対応として、層間絶縁膜72、層間絶縁膜73、層間絶縁膜74には、これまでよりも誘電率の低いわゆる $\text{LO}_\text{W-K}$ 材料が用いられている。周辺P.O.Eパッド2は、最上層のパッドメタル61とそのひとつ下の配線層に形成された下層パッドメタル62、およびこれらパッドメタル間を接続するビア63からなる、積層ビア構造を有している。積層ビア構造は、ワイヤボンドなどのボンディング工程で生じるクレタリングを抑制するのに効果がある。これらパッドの下には、電源供給のための、第1の電源層メタル91、さらに下層には、入出力回路内への信号供給のための最下層メタル20が形成されており、周辺P.O.Eパッドと最下層メタル20は、引出し部メタル81のスタック構造により電気的に接続されている。

10

## 【0018】

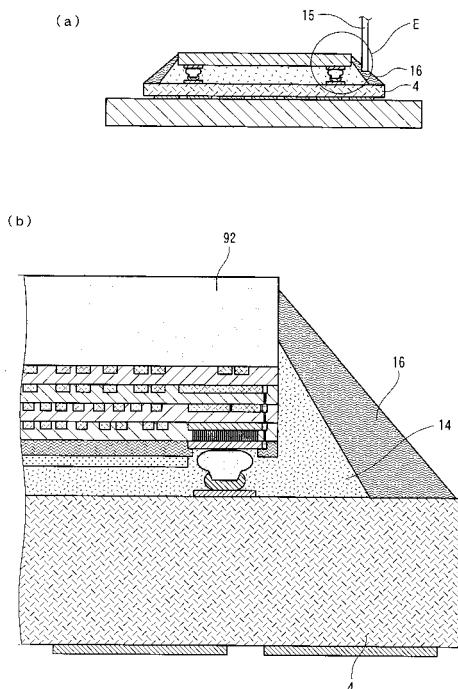

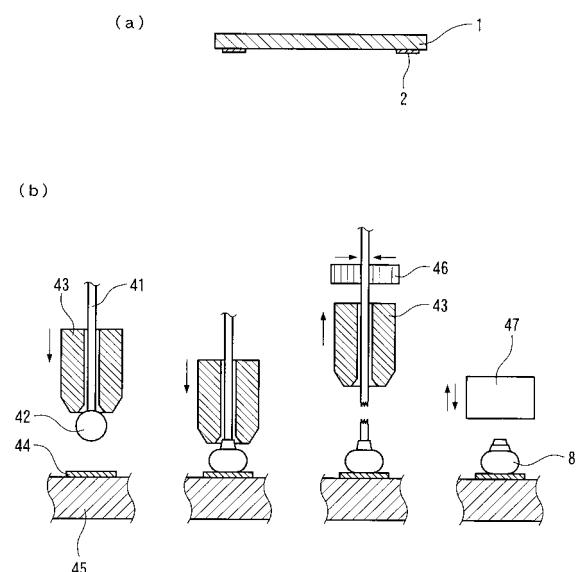

次に、本発明のCSPと呼ばれる半導体装置およびその製造方法について図面を参照しながら説明する。

図2は実施の形態1のCSPにおける金属突起を形成する工程を説明する図、図3は実施の形態1におけるCSPの製造工程を説明する工程断面図、図4は実施の形態1のCSPを示す断面図、図5は実施の形態1の高剛性樹脂を備えるCSPを示す断面図である。

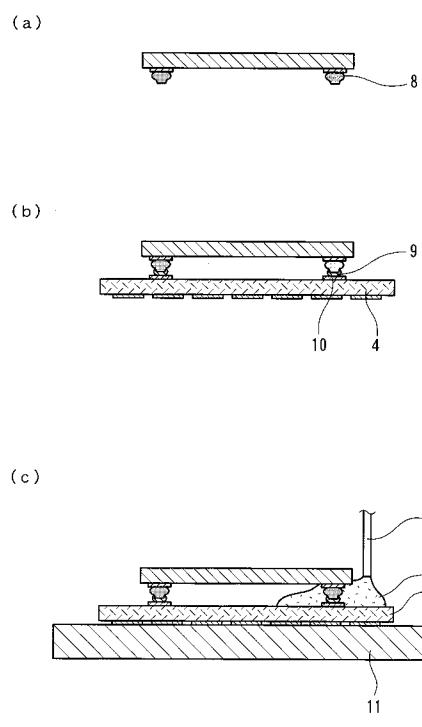

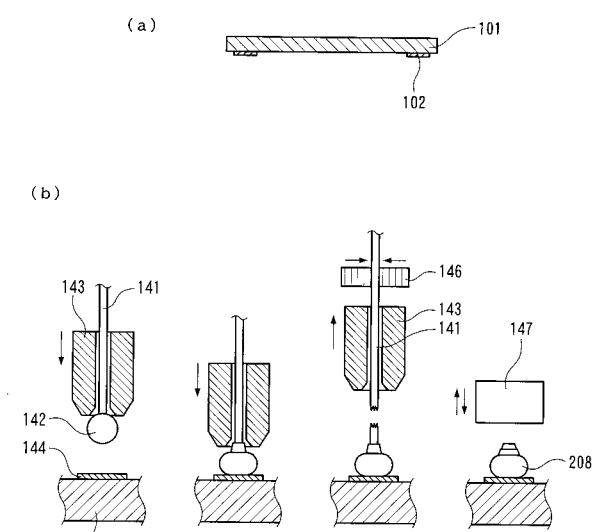

## 【0019】

半導体素子1の周辺P.O.Eパッド2上に(図2(a))、通常のワイヤボンダーを用いて金属突起8を以下の方法を用いて形成する。

まず、金属線41先端に金属ボール42を形成し、キャピラリー43を用いて半導体素子45上のパッド44に超音波振動を加えながら加圧し、クランプ46を用いて金属線を固定し、キャピラリー43を上方に移動させ金属線41を引きちぎる。その後平坦化ツール47を用いて金属突起8の高さを規定値に平坦化する(図2(b))。

## 【0020】

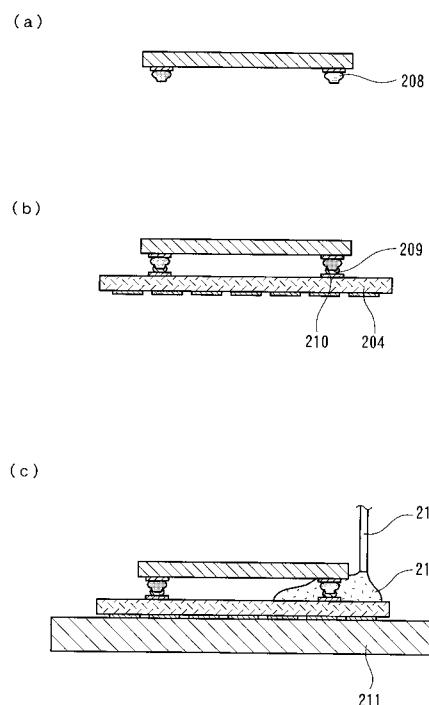

以上のようにして形成された金属突起8が(図3(a))、位置合わせを行った後に導電性接続材料9によりインターポーラ基板4の電極10と接続される(図3(b))。

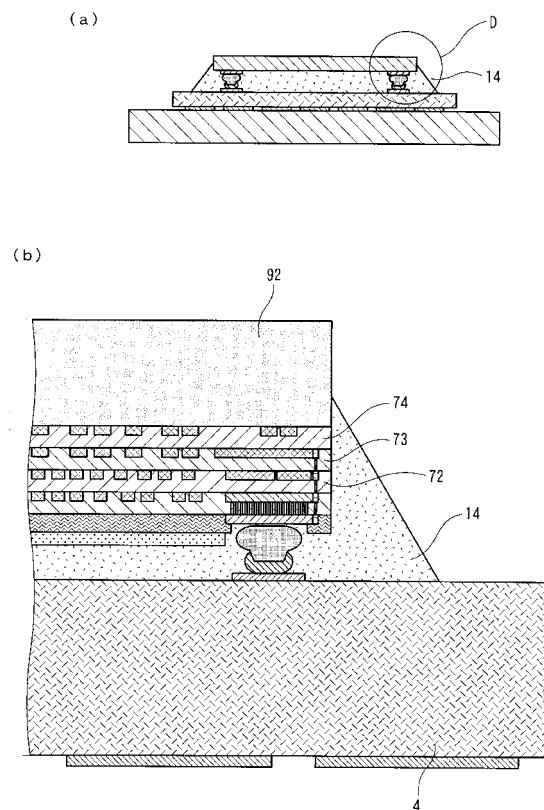

次に、適温に保持した樹脂封止用加熱ステージ11上に半導体素子を搭載したインターポーラ基板4を支持し、インターポーラ基板4上の半導体素子の1辺に樹脂ノズル13を用いて低応力樹脂12を一定量塗布する(図3(c))。この際、樹脂封止用加熱ステージ11は水平でも、樹脂が浸入しやすい方向に傾斜させてもよい。塗布した低応力樹脂12が半導体素子とインターポーラ基板間に注入されたことを確認した後、2回目の樹脂を適量塗布する。この動作を繰り返し、所定量を塗布した後、樹脂封止用加熱ステージ上で半導体素子周辺部に層間絶縁膜74より上方まで樹脂フィレット14が形成されるまで放置する(図4(a))。これにより、半導体素子とインターポーラ基板間、および、素子形成領域である半導体素子周辺部が低応力樹脂12により充填被覆される。

## 【0021】

図4(b)は、図4(a)のD部分の拡大図である。この際、樹脂フィレット14が形成されやすいように、また、形成スピードを上昇させるために樹脂封止用加熱ステージを傾斜させてもよい。その後、オープン中で樹脂の加熱硬化を行う。

## 【0022】

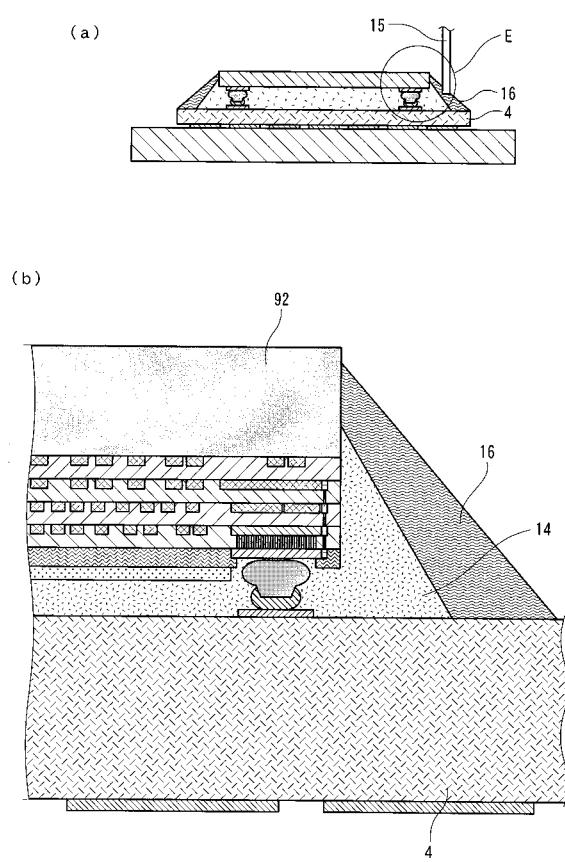

さらに、低応力樹脂12硬化後、樹脂ノズル15により、高剛性樹脂16をチップ周辺部に一定量塗布する(図5(a))。高剛性樹脂16が半導体素子周辺端部と前記インターポーラ基板4と前記低応力樹脂12を被覆するまで放置する(図5(b))。図5(b)は、図5(a)のE部分の拡大図である。その後、オープン中で樹脂の加熱硬化を行い、半導体装置が完成する。

## 【0023】

このように低応力樹脂に加えて高剛性樹脂により半導体装置を被覆して、封止樹脂を二重構造にすることにより、半導体装置の剛性が向上し、層間絶縁膜の機械的強度が弱くても、樹脂硬化時やパッケージ組立時に加わる応力にも耐えうるパッケージ構造となり、信頼性を向上することができる。

20

30

40

50

## 【0024】

また、高剛性樹脂の特性は、低応力樹脂12よりも熱膨張係数が小さいものを使用しても良い。この結果、熱膨張係数の小さい樹脂が熱ストレスに対するパッケージ変形に対し支配的になり、環境変化に対する応力発生を抑え、信頼性を向上することができる。

## 【0025】

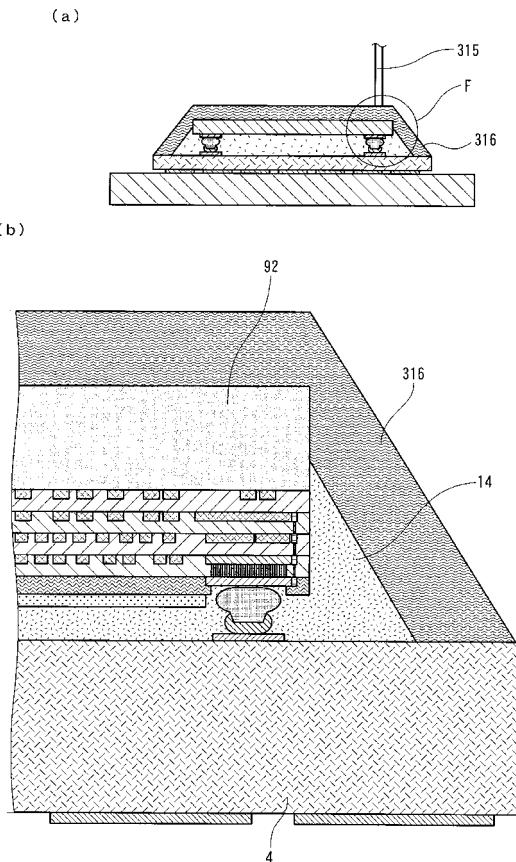

また、高剛性樹脂の構造は以下に示す実施の形態2でも良い。

図6は実施の形態2の高剛性樹脂を備えるCSPを示す断面図である。

低応力樹脂12硬化後、樹脂ノズル315により、高剛性樹脂316をチップ上方より一定量塗布する(図6(a))。高剛性樹脂316が半導体素子上面、周辺端部と前記半導体キヤリアと前記低応力樹脂12を被覆するまで放置する(図6(b))。図6(b)は、図6(a)のF部分の拡大図である。その後、オープン中で樹脂の加熱硬化を行い、半導体装置を完成する。

10

## 【0026】

このように低応力樹脂に加えて高剛性樹脂により半導体装置を被覆して、封止樹脂を二重構造にすることにより、半導体装置の剛性が向上し、層間絶縁膜の機械的強度が弱くても、樹脂硬化時やパッケージ組立時に加わる応力にも耐えうるパッケージ構造となり、信頼性を向上することができる。

## 【0027】

また、高剛性樹脂の特性は、低応力樹脂12よりも熱膨張係数が小さいものを使用しても良い。この結果、熱膨張係数の小さい樹脂が熱ストレスに対するパッケージ変形に対し支配的になり、環境変化に対する応力発生を抑え、信頼性を向上することができる。

20

## 【産業上の利用可能性】

## 【0028】

本発明の半導体装置は、層間絶縁膜の機械的強度が弱くても、樹脂硬化時やパッケージ組立時に加わる応力にも耐えうるパッケージ構造となり、信頼性を向上することができ、樹脂封止構造を有する半導体装置等に有用である。

## 【図面の簡単な説明】

## 【0029】

【図1】(a)実施の形態1における半導体装置の平面図 (b)実施の形態1における半導体装置の断面図 (c)実施の形態1の半導体装置における入出力回路部分の拡大断面図

30

【図2】実施の形態1のCSPにおける金属突起を形成する工程を説明する図

【図3】実施の形態1におけるCSPの製造工程を説明する工程断面図

【図4】実施の形態1のCSPを示す断面図

【図5】実施の形態1の高剛性樹脂を備えるCSPを示す断面図

【図6】実施の形態2の高剛性樹脂を備えるCSPを示す断面図

【図7】(a)従来の半導体装置の平面図 (b)従来の半導体装置の断面図 (c)従来の半導体装置における入出力回路部分の拡大断面図

【図8】従来のCSPにおける金属突起を形成する工程を説明する図

40

【図9】従来のCSPの製造工程を説明する工程断面図

【図10】従来のCSPを示す断面図

## 【符号の説明】

## 【0030】

1 半導体素子

2 周辺POEパッド

4 インターポーザ基板

8 金属突起

9 導電性接続材料

10 電極

11 樹脂封止用加熱ステージ

50

|       |            |    |

|-------|------------|----|

| 1 2   | 低応力樹脂      |    |

| 1 3   | 樹脂ノズル      |    |

| 1 4   | 樹脂フィレット    |    |

| 1 5   | 樹脂ノズル      |    |

| 1 6   | 高剛性樹脂      |    |

| 2 0   | 最下層メタル     | 10 |

| 3 1   | 第1の保護膜     |    |

| 3 2   | 第2の保護膜     |    |

| 4 1   | 金属線        |    |

| 4 2   | 金属ボール      |    |

| 4 3   | キャピラリー     |    |

| 4 4   | パッド        |    |

| 4 5   | 半導体素子      |    |

| 4 6   | クランプ       |    |

| 4 7   | 平坦化ツール     |    |

| 6 1   | パッドメタル     |    |

| 6 2   | パッドメタル     |    |

| 6 3   | ビア         |    |

| 7 1   | 層間絶縁膜      |    |

| 7 2   | 層間絶縁膜      | 20 |

| 7 3   | 層間絶縁膜      |    |

| 7 4   | 層間絶縁膜      |    |

| 8 1   | 引出し部メタル    |    |

| 9 1   | 第1の電源層メタル  |    |

| 9 2   | シリコン基板     |    |

| 1 0 1 | 半導体素子      |    |

| 1 0 2 | 周辺P O Eパッド |    |

| 1 1 0 | 最下層メタル     |    |

| 1 3 1 | 第1の保護膜     |    |

| 1 3 2 | 第2の保護膜     | 30 |

| 1 4 1 | 金属線        |    |

| 1 4 2 | 金属ボール      |    |

| 1 4 3 | キャピラリー     |    |

| 1 4 4 | パッド        |    |

| 1 4 5 | 半導体素子      |    |

| 1 4 6 | クランプ       |    |

| 1 4 7 | 平坦化ツール     |    |

| 1 6 1 | パッドメタル     |    |

| 1 6 2 | パッドメタル     |    |

| 1 6 3 | ビア         |    |

| 1 7 1 | 層間絶縁膜      | 40 |

| 1 7 2 | 層間絶縁膜      |    |

| 1 7 3 | 層間絶縁膜      |    |

| 1 7 4 | 層間絶縁膜      |    |

| 1 8 1 | 引出し部メタル    |    |

| 1 9 1 | 第1の電源層メタル  |    |

| 1 9 2 | シリコン基板     |    |

| 2 0 4 | インターポーザ基板  |    |

| 2 0 8 | 金属突起       |    |

| 2 0 9 | 導電性接続材料    | 50 |

- 2 1 0 電極

2 1 1 樹脂封止用加熱ステージ

2 1 2 樹脂

2 1 3 樹脂ノズル

2 1 4 樹脂フィレット

3 1 5 樹脂ノズル

3 1 6 高剛性樹脂

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】