(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4866745号

(P4866745)

(45) 発行日 平成24年2月1日(2012.2.1)

(24) 登録日 平成23年11月18日(2011.11.18)

(51) Int.Cl.

H03F 1/42 (2006.01)

H03F 3/45 (2006.01)

F 1

H03F 1/42

H03F 3/45

Z

請求項の数 8 外国語出願 (全 39 頁)

(21) 出願番号 特願2007-9334 (P2007-9334)

(22) 出願日 平成19年1月18日 (2007.1.18)

(65) 公開番号 特開2007-195189 (P2007-195189A)

(43) 公開日 平成19年8月2日 (2007.8.2)

審査請求日 平成22年1月8日 (2010.1.8)

(31) 優先権主張番号 60/759899

(32) 優先日 平成18年1月18日 (2006.1.18)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/798567

(32) 優先日 平成18年5月8日 (2006.5.8)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/798480

(32) 優先日 平成18年5月8日 (2006.5.8)

(33) 優先権主張国 米国(US)

(73) 特許権者 502188642

マーベル ワールド トレード リミテッド

バルバドス国 ビービー14027, セントマイケル、ブリトンズ ヒル、ガンサイ

トロード、エル ホライズン

(74) 代理人 100094318

弁理士 山田 行一

(74) 代理人 100123995

弁理士 野田 雅一

(72) 発明者 セハット スタージャ

アメリカ合衆国、カリフォルニア州、ロス アルトス ヒルズ、エレナ ロード

27330

最終頁に続く

(54) 【発明の名称】入れ子状のトランスインピーダンス増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の反転入力、第1の非反転入力、第1の反転出力、及び第1の非反転出力を有する第1の演算増幅器と、

第2の反転入力、第2の非反転入力、第2の反転出力、及び第2の非反転出力を有する第2の演算増幅器であって、前記第2の反転出力が前記第1の非反転入力に接続し、前記第2の非反転出力が前記第1の反転入力に接続する該第2の演算増幅器と、

第3の反転入力、第3の非反転入力、第3の反転出力、及び第3の非反転出力を有する第3の演算増幅器であって、前記第2の反転入力が前記第3の非反転出力に接続し、前記第2の非反転入力が前記第3の反転出力に接続する該第3の演算増幅器と、

第4の反転入力、第4の非反転入力、第4の反転出力、及び第4の非反転出力を有する第4の演算増幅器であって、前記第4の反転出力が前記第3の非反転入力に接続し、前記第4の非反転出力が前記第3の反転入力に接続する該第4の演算増幅器と、

前記第2の非反転入力及び前記第2の反転出力に接続する第1のフィードバック素子と、

前記第2の反転入力及び前記第2の非反転出力に接続する第2のフィードバック素子と、

前記第3の非反転入力及び前記第1の反転出力に接続する第3のフィードバック素子と、

前記第3の反転入力及び前記第1の非反転出力に接続する第4のフィードバック素子と、

前記第3の反転入力及び前記第1の非反転出力に接続する第4のフィードバック素子と、

10

20

、前記第4の反転入力及び前記第1の反転出力に接続する第5のフィードバック素子と、前記第4の非反転入力及び前記第1の非反転出力に接続する第6のフィードバック素子と、

備える、差動トランスインピーダンス増幅器回路。

【請求項2】

前記第1のフィードバック素子が第1の抵抗を備え、前記第2のフィードバック素子が第2の抵抗を備える、請求項1記載の差動トランスインピーダンス増幅器回路。

【請求項3】

前記第3のフィードバック素子が第1の抵抗を備え、前記第4のフィードバック素子が第2の抵抗を備える、請求項1記載の差動トランスインピーダンス増幅器回路。 10

【請求項4】

前記第5のフィードバック素子が第1の抵抗を備え、前記第6のフィードバック素子が第2の抵抗を備える、請求項1記載の差動トランスインピーダンス増幅器回路。

【請求項5】

請求項1記載の差動トランスインピーダンス増幅器を備える、シグマデルタ・アナログ-デジタル変換器。

【請求項6】

入力信号を受ける一方の入力を有する差動増幅器モジュールと、

前記差動増幅器モジュールの出力に接続する積分器モジュールと、

前記積分器モジュールの出力を受ける比較器モジュールと、

前記比較器モジュールの出力及び前記差動増幅器モジュールの他方の入力に接続するデジタル-アナログ変換器モジュールと、

を更に備える、請求項5記載のシグマデルタ・アナログ-デジタル変換器。 20

【請求項7】

前記比較器モジュールの出力を受けるフィルタ及び間引きモジュールを更に備える、請求項6記載のシグマデルタ・アナログ-デジタル変換器。

【請求項8】

前記差動増幅器モジュール、前記積分器モジュール、及び前記比較器モジュールのうち少なくとも一つが、前記差動トランスインピーダンス増幅器を含む、請求項6記載のシグマデルタ・アナログ-デジタル変換器。 30

【発明の詳細な説明】

【関連出願の相互参照】

【0001】

[0001]本出願は、2006年7月28日に出願された米国特許出願第11/495,813号の継続出願であり、当該出願は、2006年6月29日に出願された米国特許仮出願第60/817,268号、2006年5月8日に出願された米国特許仮出願第60/798,480号、2006年5月8日に出願された米国特許仮出願第60/798,567号、2006年1月18日に出願された米国特許仮出願第60/759,899号の利益を主張するものであり、2003年6月11日に出願された米国特許出願第10/459,731号の一部継続出願である。米国特許出願第10/459,731号は、2004年7月13日に発行された米国特許であって2001年3月13日に出願された米国特許仮出願60/275,109号の利益を主張する米国特許第6,762,644号の一部継続出願である。上述の出願を、それらの全体を参照することによって本明細書に援用する。 40

【発明の分野】

【0002】

[0002]本発明は、トランスインピーダンス増幅器に関するものであり、より詳細には、増加した利得帯域幅積を有する入れ子状の(ネステッド)トランスインピーダンス増幅器

10

20

30

40

50

に関するものである。

【発明の背景】

【0003】

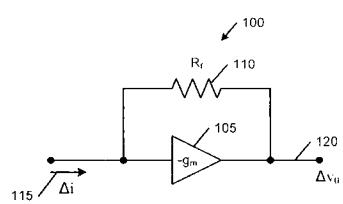

[0003]トランスインピーダンス増幅器(TIA)は、公知のタイプの電子回路である。ここで図1を参照する。TIA100は、利得パラメータ( $-g_m$ )を有する演算増幅器(オペアンプ)105を備えている。演算増幅器105は、抵抗( $R_f$ )110に並列に接続されている。TIA100の入力は、電流( $i$ )115である。TIA100の出力は、電圧( $v_o$ )120である。

【0004】

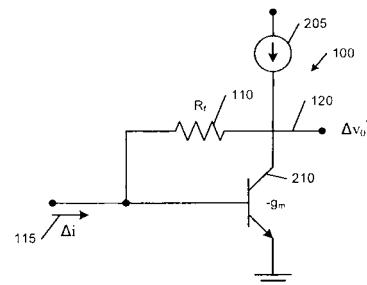

[0004]次に図2を参照する。この図では、TIA100のオペアンプ105が、電流源205と利得 $-g_m$ を有するトランジスタ210とで置き換えられている。図1及び図2におけるTIA100は、相互コンダクタンス増幅器としばしば呼ばれるものである。これは、TIA100が、入力電流*i*を出力電流 $v_o$ に変換するからである。

【0005】

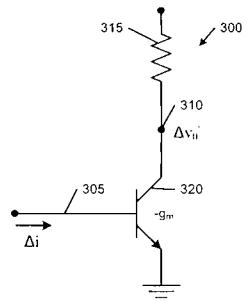

[0005]次に図3を参照する。TIA300は、入力電圧( $v_i$ )305を出力電圧( $v_o$ )310に変換するものである。TIA300はまた、トランジスタ320に接続された抵抗315を備えている。TIA300は、通常、比較的低い帯域幅を必要とする用途に使用される。

【0006】

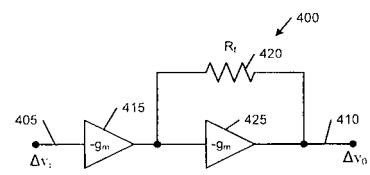

[0006]次に図4を参照する。TIA400は、入力電圧( $v_i$ )405を出力電圧( $v_o$ )410に変換するものである。TIA400は、第2のオペアンプ415を備えており、このオペアンプ415は、抵抗( $R_f$ )420及びオペアンプ425の並列結合体に対して直列に接続されている。TIA400は、通常、TIA300より大きい帯域幅を要件とする用途に使用される。

【0007】

[0007]通常、TIAの帯域幅は、オペアンプに使用されるトランジスタの閾値周波数 $f_T$ のある割合に制限される。ガリウム砒素(GaAs)トランジスタのようなバイポーラ接合トランジスタ(BJT)の場合には、TIAの帯域幅は $f_T$ の10%~20%に略等しい。金属酸化物半導体(MOS)トランジスタの場合には、TIAの帯域幅は、通常、 $f_T$ の数パーセント(即ち、約2~6%)である。

【0008】

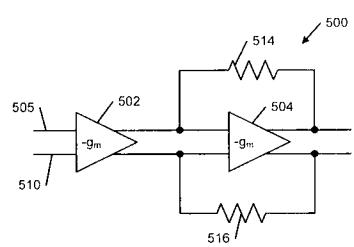

[0008]次に図5を参照する。TIA500は、オペアンプ502及び504の各々の二つの入力を用い、差動的に動作するよう構成されることがある。一方の入力505は、標準構成のTIAにおけるグランド又は仮想接地と同様に、基準として作用する。入力電圧 $v_i$ 及び出力電圧 $v_o$ は、基準入力505と第2の入力510の間の電圧差として計測される。フィードバック抵抗514及び516は、オペアンプ504の入力と出力との間に接続されている。

【0009】

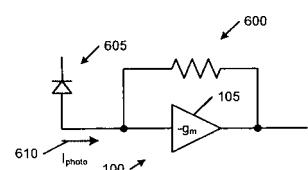

[0009]次に図6を参照する。比較的大きい帯域幅の要件を有するTIAの用途の一つは、光センサへの用途である。光センサ回路600は、オペアンプ105とTIA100の抵抗110とを備えており、これらはフォトダイオード605に接続されている。フォトダイオード605の出力は、TIA100への入力として作用する電流 $I_{phot}$ 610である。

【0010】

[0010]大きい帯域幅及び高利得の両者を要求する用途が増えてきている。例として、光ファイバ受信器のような光センサや、高速ハードディスクドライブ用のプリアンプライタ(preamplifier writer)がある。

【発明の概要】

【0011】

[0011]入れ子状の(ネステッド)トランスインピーダンス増幅器(TIA)回路が、入

10

20

30

40

50

力及び出力を有する0次のTIAと、第1の演算増幅器(オペアンプ)と、を備える。オペアンプは、0次のTIAの出力に接続する入力と、上記入力によって駆動される第1のトランジスタと、第1のバイアス電圧によって駆動されるものであって第1のトランジスタに接続する第2のトランジスタと、第2のトランジスタに接続する第1の電流源と、第1のトランジスタと第2のトランジスタの間のノードにある出力と、を有する。

【0012】

[0012]他の特徴においては、第2の電流源が、第1のトランジスタに接続する。オペアンプの利得は、0次のTIAの利得より大きい。オペアンプの帯域幅は、0次のTIAの帯域幅より小さい。

【0013】

[0013]他の特徴では、0次のTIAは、第1の入力及び第1の出力を有する第1のオペアンプと、第2の入力及び第2の出力を有する第2のオペアンプと、を備える。第2の入力は、第1の出力に接続する。抵抗が、第2の出力に接続する一の端部と、第2の入力に接続する第2の端部を有する。

【0014】

[0014]また、入れ子状の差動モードトランスインピーダンス増幅器(TIA)回路が、第1及び第2の入力、並びに第1の出力及び第2の出力を有する0次の差動モードTIAと、第1の差動モード演算増幅器(オペアンプ)と、を備える。オペアンプは、0次の差動モードTIAの出力のうち対応の出力にそれぞれ接続する複数の入力と、第1の入力によって駆動される第1のトランジスタと、第2の入力によって駆動される第2のトランジスタと、第1のバイアスによって駆動されるものであり第1のトランジスタに接続する第3のトランジスタと、第1のバイアス電圧によって駆動されるものであり第2のトランジスタに接続する第4のトランジスタと、第3のトランジスタに接続する第1の電流源と、第4のトランジスタに接続する第2の電流源と、第1のトランジスタと第3のトランジスタの間の接続部にある第1の出力及び第2のトランジスタと第4のトランジスタの間の接続部にある第2の出力と、を有する。

【0015】

[0015]他の特徴では、入れ子状の差動モードTIA回路は、第1のトランジスタと第2のトランジスタに接続する第3の電流源を備える。第1の差動モードオペアンプの利得は、0次の差動モードTIAの利得より大きい。第1の差動モードオペアンプの帯域幅は、0次の差動モードTIAの帯域幅より小さい。

【0016】

[0016]他の特徴では、0次の差動モードTIAは、入力及び出力を有する第2の差動モードオペアンプと、入力及び出力を有する第3の差動モードオペアンプを備える。第3の差動モードオペアンプの入力はそれぞれ、第2の差動モードオペアンプの出力のうち対応の出力に接続する。抵抗が第1の端部及び第2の端部を有している。第1及び第2の端部は、第3の差動モードオペアンプの入力及び出力にそれぞれ接続する。

【0017】

[0017]また、入れ子状の差動モードトランスインピーダンス増幅器(TIA)回路が、第1及び第2の入力、並びに第1及び第2の出力を有する0次の差動モードTIAと、第1及び第2の入力、並びに第1及び第2の出力を有する差動モードのプッシュプルオペアンプと、を備える。第1及び第2の入力はそれぞれ、0次の差動モードTIAの第1及び第2の出力のうち対応の出力に接続する。

【0018】

[0018]他の特徴では、差動モードのプッシュプルオペアンプの利得は、0次の差動モードTIAの利得より大きく、差動モードのプッシュプルオペアンプの帯域幅は、0次の差動モードTIAの帯域幅より小さい。

【0019】

[0019]他の特徴では、0次の差動モードTIAは、入力及び出力を有する第2の差動モードオペアンプと、入力及び出力を有する第3の差動モードオペアンプと、を備える。第

10

20

30

40

50

3の差動モードオペアンプの入力はそれぞれ、第2の差動モードオペアンプの出力のうち対応の出力に接続する。抵抗が第1の端部及び第2の端部を有する。第1の端部及び第2の端部は、第3の差動モードオペアンプの入力及び出力にそれぞれ接続する。

【0020】

[0020]また、入れ子状のトランスインピーダンス増幅器(TIA)回路が、入力及び出力を有する0次のTIAと、出力及び0次のTIAの出力に接続する入力を有する第1の演算増幅器(オペアンプ)と、0次のTIAに第1の電圧を印加するための第1の電源入力と、第2の電圧を受けるための第2の電源入力と、を備える。電荷ポンプモジュールが、第1の電圧及び第2の電圧に基づく第3の電圧を生成する。第3の電圧は、上記オペアンプに印加される。

10

【0021】

[0021]他の特徴では、0次のTIAは、第1の入力及び第1の出力を有する第1のオペアンプと、第2の入力及び第2の出力を有する第2のオペアンプと、を備える。第2の入力は、第1の出力に接続する。抵抗が、第2の出力に接続する一の端部と、第2の入力に接続する第2の端部とを有する。

【0022】

[0022]他の特徴では、電圧レギュレータ(調整器)が、第2の電圧を制御する。発光ダイオードが、オペアンプの出力に接続する。第1の電圧は、第2の電圧より大きい。第3の電圧は、第1の電圧と第2の電圧の和に略等しい。第1の電圧は、別の場合には、アナログ回路に印加され、第2の電圧は、別の場合には、デジタル回路に印加される。第1の電圧は、約2.5Vと3.3Vの間の電圧である。第2の電圧は、1.2Vである。

20

【0023】

[0023]また、差動トランスインピーダンス増幅器が、第1の反転入力、第1の非反転入力、第1の反転出力、及び第1の非反転出力を有する第1の演算増幅器と、第2の反転入力、第2の非反転入力、第2の反転出力、及び第2の非反転出力を有する第2の演算増幅器であって、第2の反転出力が第1の非反転入力に接続しており、第2の非反転出力が第1の反転入力に接続している当該第2の演算増幅器と、第1の非反転入力及び第1の反転出力に接続する第1のフィードバック素子と、第1の反転入力及び第1の非反転出力に接続する第2のフィードバック素子と、第2の反転入力及び第1の反転出力に接続する第3のフィードバック素子と、第1の非反転入力及び第1の非反転出力に接続する第4のフィードバック素子と、を備える。

30

【0024】

[0024]他の特徴では、第3及び第4のフィードバック素子はそれぞれ、第1及び第2の抵抗を備える。第3及び第4のフィードバック素子はそれぞれ、第1及び第2のキャパシタンスを備える。第1及び第2のフィードバック素子はそれぞれ、第1及び第2の抵抗を、備える。第1及び第2のフィードバック素子はそれぞれ、第1及び第2のキャパシタンスを備える。第1及び第2のフィードバック素子の各々は、第1の抵抗を、キャパシタンスと並列に設けられているインダクタンス及び第2の抵抗と直列に、備える。このキャパシタンスは、可変キャパシタンスを含む。第1及び第2のフィードバック素子の各々は、抵抗を、キャパシタンスと並列に備えている。このキャパシタンスは、可変キャパシタンスである。

40

【0025】

[0025]他の特徴では、第1及び第2のフィードバック素子の各々は、第1の抵抗を、インダクタンスと直列に備えており、第1の抵抗及びインダクタンスが、キャパシタンス及び第2の抵抗と並列に設けられている。このキャパシタンスは、可変キャパシタンスを含む。第1及び第2の演算増幅器は、相互コンダクタンス増幅器である。

【0026】

[0026]他の特徴では、積分器が、上記の差動トランスインピーダンス増幅器を備える。

【0027】

[0027]また、单一の入れ子状のトランスインピーダンス増幅器回路が、第3の反転入力

50

、第3の非反転入力、第3の反転出力、及び第3の非反転出力を有する第3の演算増幅器と、上記の差動トランスインピーダンス増幅器回路と、を備える。第2の反転入力は、第3の非反転出力に接続し、第2の非反転入力は、第3の反転出力に接続する。

【0028】

[0028]二重の入れ子状の差動トランスインピーダンス増幅器回路は、单一の入れ子状のトランスインピーダンス回路と、第4の反転入力、第4の非反転入力、第4の反転出力、及び第4の非反転出力を有する第4の演算増幅器と、を備える。第4の反転出力は、第3の非反転出力に接続し、第4の非反転出力は、第3の反転入力に接続する。

【0029】

[0029]他の特徴では、第5のフィードバック素子が、第4の反転出力及び第1の反転出力に接続する。第6のフィードバック素子が、第4の非反転出力及び第1の非反転出力に接続する。第5及び第6のフィードバック素子はそれぞれ、第1及び第2の抵抗を備える。第5及び第6のフィードバック素子は、第1及び第2のキャパシタンスを備える。

10

【0030】

[0030]また、シグマデルタ (Sigma-Delta) ・アナログ - デジタル変換器が、上記の差動トランスインピーダンス増幅器を備える。シグマデルタ・アナログ - デジタル変換器は、入力信号を受ける一方の入力を有する差動増幅器モジュールと、差動増幅器モジュールの出力に接続する積分器モジュールと、積分器モジュールの出力を受ける比較器モジュールと、比較器モジュールの出力及び差動増幅器モジュールの他方の入力に接続するデジタル - アナログ変換器と、を備える。

20

【0031】

[0031]他の特徴では、フィルタ及びデシメーション(間引き)モジュールが、比較器モジュールの出力を受ける。差動増幅器モジュール、積分器モジュール、及び比較器モジュールのうちの少なくとも一つは、上記の差動トランスインピーダンス増幅器を含む。

【0032】

[0032]また、差動トランスインピーダンス増幅器回路が、第1の反転入力、第1の非反転入力、第1の反転出力、及び第1の非反転出力を有する増幅用の第1の増幅手段と、第2の反転入力、第2の非反転入力、第2の反転出力、及び第2の非反転出力を有する増幅用の第2の増幅手段であって、第2の反転出力が第1の非反転入力に接続し、第2の非反転出力が第1の反転入力に接続する当該第2の増幅手段と、第1の非反転入力及び第1の反転出力に接続しフィードバックを提供する第1のフィードバック手段と、第1の反転入力及び第1の非反転出力に接続しフィードバックを提供する第2のフィードバック手段と、第2の反転入力及び第1の反転出力に接続しフィードバックを提供する第3のフィードバック手段と、第1の非反転入力及び第1の非反転出力に接続しフィードバックを提供する第4のフィードバック手段と、を備える。

30

【0033】

[0033]他の特徴では、第3及び第4のフィードバック手段は、抵抗を提供する第1及び第2の抵抗手段を、それぞれ備えている。第3及び第4のフィードバック手段は、キャパシタンスを提供する第1及び第2のキャパシタンスを、それぞれ備えている。第1及び第2のフィードバック手段は、抵抗を提供する第1及び第2の抵抗手段を、それぞれ備えている。第1及び第2のフィードバック手段は、キャパシタンスを提供する第1及び第2のキャパシタンスを、それぞれ備える。第1及び第2のフィードバック手段の各々は、抵抗を提供する第1の抵抗手段を、インダクタンスを提供するインダクタンス手段及び抵抗を提供する第2の抵抗手段と直列に備えており、当該インダクタンス手段及び第2の抵抗手段が、キャパシタンスを提供するキャパシタンス手段と並列に設けられている。キャパシタンス手段は、可変キャパシタンスを提供する。第1及び第2のフィードバック手段の各々は、抵抗を提供する抵抗手段を、キャパシタンスを提供するキャパシタンス手段と並列に備える。キャパシタンス手段は、可変キャパシタンスを提供する。第1及び第2のフィードバック手段の各々は、抵抗を提供する第1の抵抗手段を、インダクタンスを提供するインダクタンス手段と直列に備え、第1の抵抗手段及びインダクタンス手段が、キャパシ

40

50

タンスを提供するキャパシタンス手段及び抵抗を提供する第2の抵抗手段と並列に設けられている。キャパシタンス手段は、可変キャパシタンスを提供する。第1及び第2の増幅手段は、相互コンダクタンス増幅器を含む。

【0034】

[0034]また、単一の入れ子状のトランスインピーダンス増幅器回路が、第3の反転入力、第3の非反転入力、第3の反転出力、及び第3の非反転出力を有する増幅用の第3の増幅手段と、上記の差動トランスインピーダンス増幅器回路と、を備える。第2の反転入力は、第3の非反転出力に接続し、第2の非反転入力は、第3の反転出力に接続する。

【0035】

[0035]また、二重の入れ子状の差動トランスインピーダンス増幅器回路が、单一の入れ子状のトランスインピーダンス増幅器回路と、第4の反転入力、第4の非反転入力、第4の反転出力、及び第4の非反転出力を有する増幅用の第4の増幅手段と、を備える。第4の反転出力は、第3の非反転出力に接続し、第4の非反転出力は、第3の反転入力に接続する。

【0036】

[0036]他の特徴では、フィードバックを提供する第5のフィードバック手段が、第4の反転出力及び第1の反転出力と接続する。フィードバックを提供する第6のフィードバック手段が、第4の非反転出力及び第1の非反転出力と接続する。第5及び第6のフィードバック手段は、抵抗を提供する第1及び第2の抵抗手段を、それぞれ備える。

【0037】

[0037]また、シグマデルタ・アナログ - デジタル変換器が、上記の差動トランスインピーダンス増幅器を備える。シグマデルタ・アナログ - デジタル変換器は、入力信号を受信する一方の入力を有する増幅用の差動増幅器手段と、差動増幅器手段の出力に接続する積分用の積分器手段と、積分器手段の出力を受ける比較用の比較器手段と、比較器手段の出力及び差動増幅器手段の他方の入力に接続する変換用のデジタル - アナログ変換器手段と、を備える。

【0038】

[0038]他の特徴では、フィルタリング及び間引き用のフィルタ及び間引き手段が、比較器手段の出力を受ける。差動増幅器手段、積分器手段、及び比較器手段のうち少なくとも一つは、上記の差動トランスインピーダンス増幅器を含む。

【0039】

[0039]また、差動トランスインピーダンス増幅器回路が、第1の反転入力、第1の非反転入力、第1の反転出力、及び第1の非反転出力を有する第1の演算増幅器と、第2の反転入力、第2の非反転入力、第2の反転出力、及び第2の非反転出力を有する第2の演算増幅器であって、第2の反転出力が第1の非反転入力に接続し、第2の非反転出力が第1の反転入力に接続する当該第2の演算増幅器と、第3の反転入力、第3の非反転入力、第3の反転出力、及び第3の非反転出力を有する第3の演算増幅器であって、第2の反転入力が第3の非反転出力に接続し、第2の非反転入力が第3の反転出力に接続する当該第3の演算増幅器と、第4の反転入力、第4の非反転入力、第4の反転出力、及び第4の非反転出力を有する第4の演算増幅器であって、第4の反転出力が第3の非反転出力に接続し、第4の非反転出力が第3の反転入力に接続する当該第4の演算増幅器と、第2の非反転入力及び第2の反転出力に接続する第1のフィードバック素子と、第2の反転入力及び第2の非反転出力に接続する第2のフィードバック素子と、第3の非反転入力及び第1の反転出力に接続する第3のフィードバック素子と、第3の反転入力及び第1の非反転出力に接続する第4のフィードバック素子と、第4の反転入力及び第1の反転出力に接続する第5のフィードバック素子と、第4の非反転出力及び第1の非反転出力に接続する第6のフィードバック素子と、を備える。

【0040】

[0040]他の特徴では、第1及び第2のフィードバック素子は、第1及び第2の抵抗を、それぞれ備える。第3及び第4のフィードバック素子は、第1及び第2の抵抗を、それぞ

10

20

30

40

50

れ備える。第5及び第6のフィードバック素子は、第1及び第2の抵抗を、それぞれ備える。

【0041】

[0041]また、シグマデルタ・アナログ・デジタル変換器が、上記の差動トランスインピーダンス増幅器を備えている。シグマデルタ・アナログ・デジタル変換器は、入力信号を受ける一方の入力を有する差動増幅器モジュールと、差動増幅器モジュールの出力に接続する積分器モジュールと、積分器モジュールの出力を受ける比較器モジュールと、比較器モジュールの出力及び差動増幅器モジュールの他方の入力に接続するデジタル・アナログ変換器と、を備える。

【0042】

[0042]他の特徴では、フィルタ及び間引きモジュールが、比較器モジュールの出力を受ける。差動増幅器モジュール、積分器モジュール、及び比較器モジュールのうち少なくとも一つは、上記の差動トランスインピーダンス増幅器を含む。

【0043】

[0043]また、差動トランスインピーダンス増幅器回路は、第1の反転入力、第1の非反転入力、第1の反転出力、及び第1の非反転出力を有する増幅用の第1の増幅手段と、第2の反転入力、第2の非反転入力、第2の反転出力、及び第2の非反転出力を有する増幅用の第2の増幅手段であって、第2の反転出力が第1の非反転入力に接続し、第2の非反転出力が第1の反転入力に接続する当該第2の増幅手段と、第3の反転入力、第3の非反転入力、第3の反転出力、及び第3の非反転出力を有する増幅用の第3の増幅手段であって、第2の反転入力が第3の非反転出力に接続し、第2の非反転入力が第3の反転出力に接続する当該第3の増幅手段と、第4の反転入力、第4の非反転入力、第4の反転出力、及び第4の非反転出力を有する増幅用の第4の増幅手段であって、第4の反転出力が第3の非反転出力に接続し、第4の非反転出力が第3の反転入力に接続する当該第4の増幅手段と、フィードバックを提供する第1のフィードバック手段であって、第2の非反転入力及び第2の反転出力に接続する当該第1のフィードバック手段と、フィードバックを提供する第2のフィードバック手段であって、第2の反転入力及び第2の非反転出力に接続する当該第2のフィードバック手段と、フィードバックを提供する第3のフィードバック手段であって、第3の非反転入力及び第1の反転出力に接続する当該第3のフィードバック手段と、フィードバックを提供する第4のフィードバック手段であって、第3の反転入力及び第1の非反転出力に接続する当該第4のフィードバック手段と、フィードバックを提供する第5のフィードバック手段であって、第4の反転入力及び第1の反転出力に接続する当該第5のフィードバック手段と、フィードバックを提供する第6のフィードバック手段であって、第4の非反転出力及び第1の非反転出力に接続する当該第6のフィードバック手段と、を備える。

【0044】

[0044]他の特徴では、第1及び第2のフィードバック手段は、抵抗を提供する第1及び第2の抵抗手段を、それぞれ備えている。第3及び第4のフィードバック手段は、抵抗を提供する第1及び第2の抵抗手段を、それぞれ備えている。第5及び第6のフィードバック手段は、抵抗を提供する第1及び第2の抵抗手段を、それぞれ備える。

【0045】

[0045]また、シグマデルタ・アナログ・デジタル変換器が、上記の差動トランスインピーダンス増幅器を備えている。シグマデルタ・アナログ・デジタル変換器は、入力信号を受ける一方の入力を有する増幅用の差動増幅器手段と、差動増幅器手段の出力に接続する積分用の積分器手段と、積分器手段の出力を受ける比較用の比較器手段と、比較器手段の出力及び差動増幅器手段の他方の入力に接続する変換用のデジタル・アナログ変換器手段と、を備える。

【0046】

[0046]他の特徴では、フィルタリング及び間引き用のフィルタ及び間引き手段が、比較器手段の出力を受ける。差動増幅器手段、積分器手段、及び比較器手段のうち少なくとも

10

20

30

40

50

一つが、上記の差動トランスインピーダンス増幅器を含む。

【0047】

[0047]また、トランスインピーダンス増幅器が、入力及び出力を有する第1の演算増幅器を備える。第2の演算増幅器が、入力と、第1の演算増幅器の入力に接続する出力と、を備える。第1のフィードバック素子が、第1の演算増幅器の入力に接続する一端と、第1の演算増幅器の出力に接続する他端と、を有し、当該第1のフィードバック素子は、第1のキャパシタンスを備える。第2のフィードバック素子が、第1の演算増幅器の入力、及び第1の演算増幅器の出力に接続する他端に接続する。

【0048】

[0048]他の特徴では、第2のフィードバック素子が、第1の抵抗を備える。第1のキャパシタンスは、可変キャパシタンスを含む。第1のフィードバック素子は、第1の抵抗を第1のキャパシタンスと並列に備える。第2のフィードバック素子は、第1の抵抗を第1のインダクタンスと直列に備える。第1のキャパシタンスは、可変キャパシタンスを含む。第1の抵抗は、第1及び第2のフィードバック素子の他端に接続する一端と、第2の演算増幅器の出力に接続する他端と、を有する。第1のフィードバック素子は、更に、第1の抵抗を第1のキャパシタンスと直列に備えており、第2のフィードバック素子は、第1のインダクタンスを第2の抵抗と並列に第1のインダクタンスを備える。差動増幅器は、上記のトランスインピーダンス増幅器を備える。

【0049】

[0049]また、シグマデルタ・アナログ - デジタル変換器が、差動トランスインピーダンス増幅器を備えている。シグマデルタ・アナログ - デジタル変換器は、入力信号を受ける一方の入力を有する差動増幅器モジュールと、差動増幅器モジュールの出力に接続する積分器モジュールと、積分器モジュールの出力を受ける比較器モジュールと、比較器モジュールの出力及び差動増幅器モジュールの他方の入力に接続するデジタル - アナログ変換器と、を備えている。

【0050】

[0050]他の特徴では、フィルタ及び間引きモジュールが、比較器モジュールの出力を受ける。差動増幅器モジュール、積分器モジュール、及び比較器モジュールのうち少なくとも一つが、上記の差動トランスインピーダンス増幅器を含む。

【0051】

[0051]また、トランスインピーダンス増幅器が、入力及び出力を有する増幅用の第1の増幅手段を備えている。増幅用の第2の増幅手段は、入力、及び第1の増幅手段の入力に接続する出力を有する。フィードバックを提供する第1のフィードバック手段が、第1の増幅手段の入力に接続する一端と、第1の増幅手段の出力に接続する他端とを有する。第1のフィードバック手段は、キャパシタンスを提供する第1のキャパシタンス手段を備える。フィードバックを提供する第2のフィードバック手段が、第1の増幅手段の入力に接続する一端と、第1の増幅手段の出力に接続する他端と、を備える。

【0052】

[0052]他の特徴では、第2のフィードバック手段は、抵抗を提供する第1の抵抗手段を備える。第1のキャパシタンス手段は、可変キャパシタンスを提供する可変キャパシタンス手段を備える。第1のフィードバック手段は、抵抗を提供する第1の抵抗手段を、第1のキャパシタンス手段と並列に備える。第2のフィードバック手段は、抵抗を提供する第1の抵抗手段を、インダクタンスを提供する第1のインダクタンス手段と直列に備える。第1のキャパシタンス手段は、可変キャパシタンスを提供する可変キャパシタンス手段を備える。抵抗を提供する第1の抵抗手段は、第1及び第2のフィードバック手段の他端に接続する一端と、第2の増幅手段の出力に接続する他端と、を有する。第1のフィードバック手段は、更に、抵抗を提供する第1の抵抗手段を第1のキャパシタンス手段と直列に備えており、第2のフィードバック手段は、インダクタンスを提供する第1のインダクタンス手段を、抵抗を提供する第2の抵抗手段と並列に備える。差動トランスインピーダンス増幅器が、上記のトランスインピーダンス増幅器を備える。

10

20

30

40

50

## 【0053】

[0053]また、シグマデルタ・アナログ - デジタル変換器が、上記の差動トランスインピーダンス増幅器を備えている。シグマデルタ・アナログ - デジタル変換器は、入力信号を受ける一方の入力を有する増幅用の差動増幅器手段と、差動増幅器手段の出力に接続する積分用の積分器手段と、積分器手段の出力を受ける比較用の比較器手段と、比較器手段の出力及び差動増幅器手段の他方の入力に接続する変換用のデジタル - アナログ変換器手段と、を備えている。

## 【0054】

[0054]他の特徴では、フィルタリング及び間引き用のフィルタ及び間引き手段が、比較器手段の出力を受ける。差動増幅器手段、積分器手段、及び比較器手段のうち少なくとも一つは、上記の差動トランスインピーダンス増幅器を含む。

10

## 【0055】

[0055]本発明の応用の更なる範囲は、以下に提供する詳細な説明から明らかとなろう。詳細な説明及び個別の実施例は、本発明の好適な実施の形態を示すが、例示を目的とするものであり、本発明の範囲を制限することを意図するものではないことを理解すべきである。

## 【0056】

[0056]本発明は、詳細な説明及び添付の図面から、より完全に理解されよう。

## 【発明を実施するための最良の形態】

## 【0057】

20

[0103]以下の好適な実施の形態の説明は、本質的には単なる例示であり、本発明、その応用、又はその使用を制限することを意図するものではない。

## 【0058】

[0104]本発明は、TIAの利得帯域幅積を増加することに対する必要性に対処するものである。利得帯域幅積の向上は、TIAを他のTIA内において入れ子にすることによって達成可能である。即ち、フィードバック抵抗、キャパシタ、及び/又はオペアンプのような追加の回路素子を、TIAの入力側及び/又は出力側に追加する。図15～図17では、入力寄生キャパシタンスを容量的に打ち消す構成を提供する。図20～図24では、追加のフィードバック抵抗を提供する。図23及び図24では、入力及び/又はフィードバックキャパシタンスを提供する。

30

## 【0059】

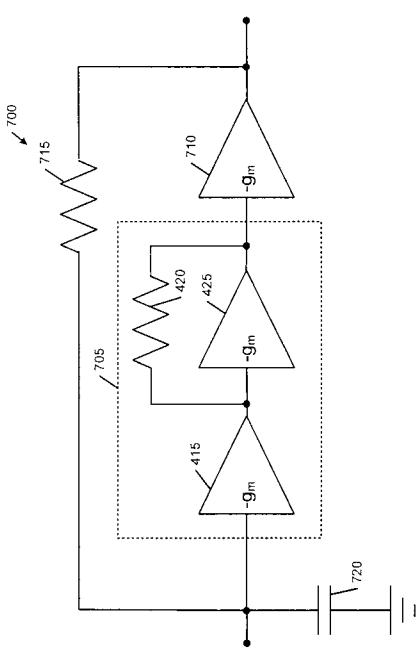

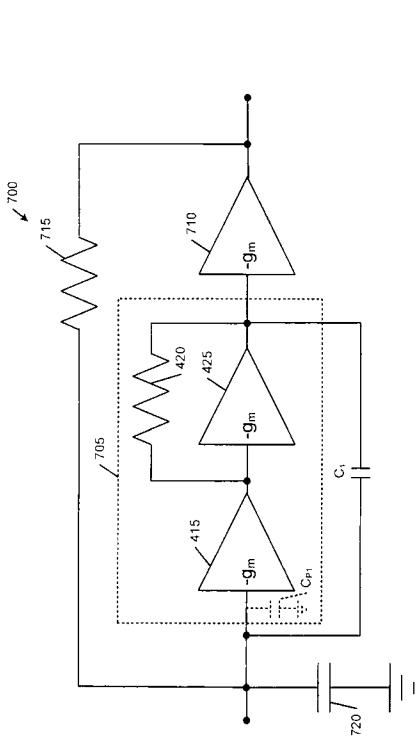

[0105]ここで、図7、図8、及び図9を参照する。「入れ子状の(nested)」TIAは、オペアンプ、フィードバック抵抗、及び/又はキャパシタを0次のTIAに追加することによって構成される。図10及び図11では、入れ子状のTIAはまた、差動モードで動作するように構成される。

## 【0060】

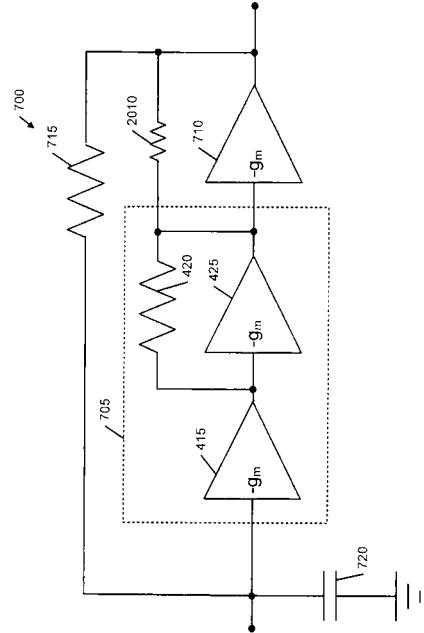

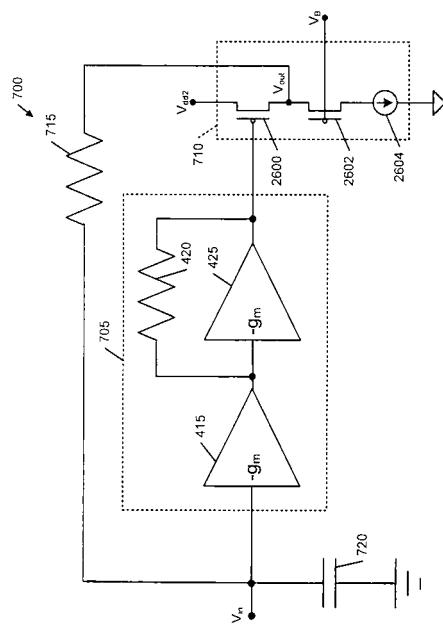

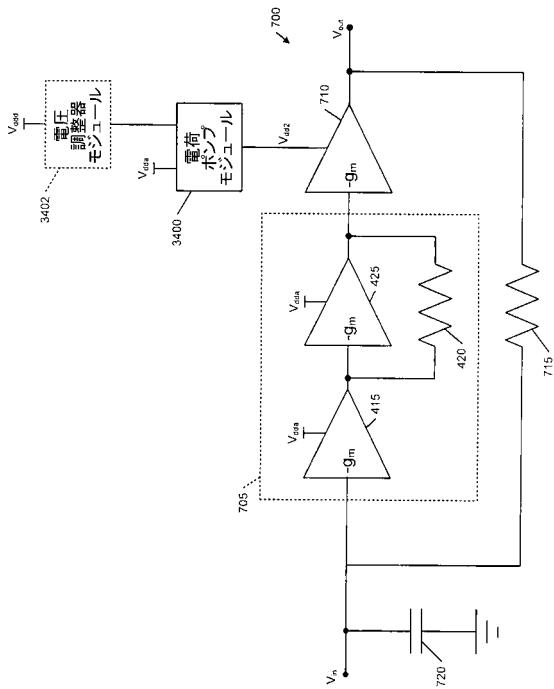

[0106]図7を再び参照する。この図は、1次の入れ子状のTIA700を示している。図4からの参照符号を図7においても使用して、同様の要素を特定する。TIA700は、従来のTIA705(本明細書では、「0次」のTIAとも呼ぶ)、オペアンプ710、及び、フィードバック抵抗715を備えている。フィードバック抵抗715は、標準の固定値の抵抗であってもよく、非線形の可変抵抗であってもよく、又は、MOS抵抗であってもよい。キャパシタ720は、TIA700の入力とグランド(又は仮想接地)の間に接続されている。

40

## 【0061】

[0107]TIAをこのように入れ子にすることによって、利得帯域幅積の向上を実現することができる。例えば、MOSトランジスタを使用する1次の入れ子状のTIA700は、閾値周波数 $f_T$ の10%～20%の帯域幅を実現し得る。この範囲は、対応の0次のTIAの帯域幅より約5～10倍大きいものである。

## 【0062】

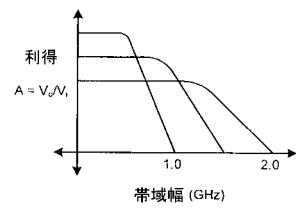

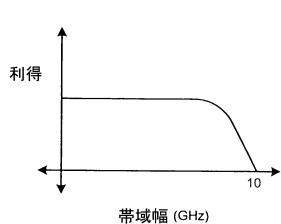

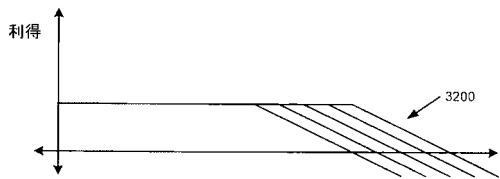

[0108]次に図12及び図13を参照する。これらの図におけるグラフは、0次のTIA

50

及び 1 次の入れ子状の TIA の特性利得帯域幅カーブを示している。通常、高い利得は小さい帯域幅に対応し、低い利得は大きい帯域幅に対応する。利得 A は、出力電圧  $v_o$  を入力電圧  $v_i$  で割った値として定義され、通常は、数百又は数千のオーダの値である（即ち、約  $10^2 \sim 10^3$ ）。 $0.13 \mu m$  の CMOS プロセスに対する閾値周波数 ( $f_T$ ) の値の通常の範囲は、 $30 \text{ GHz} \sim 40 \text{ GHz}$  である。

#### 【0063】

[0109] 図 12 に、三つの例示の特性カーブを示す。高い利得値は、約  $1 \text{ GHz}$  の帯域幅をもたらす。中程度の利得値は、帯域幅を  $2 \text{ GHz}$  に増加する。他の値の利得及び帯域幅もあり得る。例えば、TIA が、図 12 に示す最大値より高い特性利得値を有し、 $1 \text{ GHz}$  より小さい帯域幅を有することもある。また、TIA が、図 12 に示す最小の利得値より低い特性利得値を有し、 $2 \text{ GHz}$  より大きな帯域幅を有することがある。理解できるように、帯域幅は、利得の逆関数として変化する。この関数は、「拡散」と呼ばれることがある。この拡散は、MOS パークトランジスタを使用する TIA の場合に、バイポーラ接合トランジスタ (BJT) を使用する TIA の場合より大きい。したがって、TIA の帯域幅の性能を向上することに対する必要性は、BJT トランジスタより MOS トランジスタの場合に顕著である。

#### 【0064】

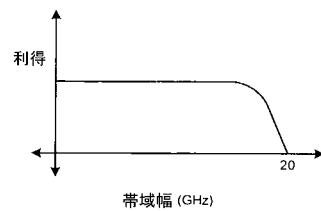

[0110] 図 12 に示す例示の帯域幅の値は、帯域幅の上限及び下限を定義するものではない。多くの実際の応用においては、 $1 \text{ GHz}$  又は  $2 \text{ GHz}$  のオーダの帯域幅は非常に小さいものである。OC192 光ファイバ受信器といった多くの応用は、 $10 \text{ GHz}$  のオーダの帯域幅を必要とする。高速ハードディスクドライブ用のプリアンプもまた、通常は、数  $\text{GHz}$  のオーダの帯域幅を必要とする。ここで、図 13 を参照する。1 次の入れ子状の TIA は、典型的な利得値で、約  $10 \text{ GHz}$  の帯域幅を有することがある。

#### 【0065】

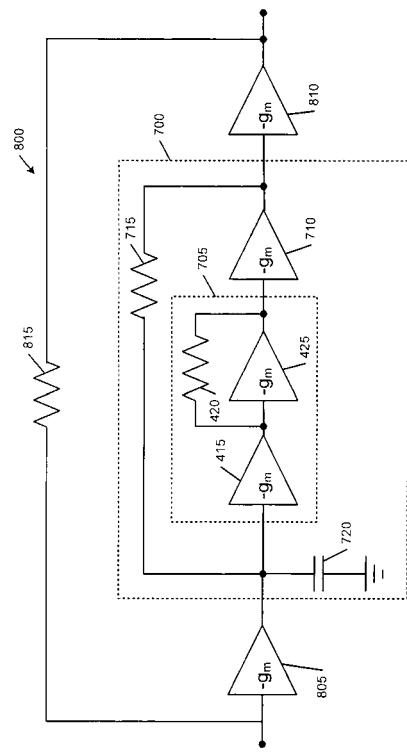

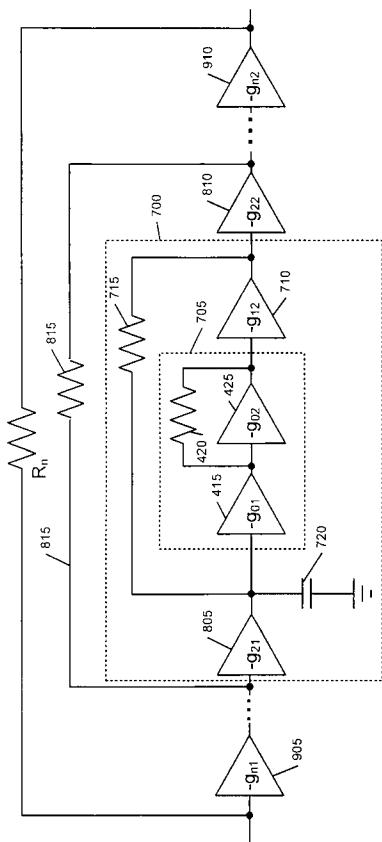

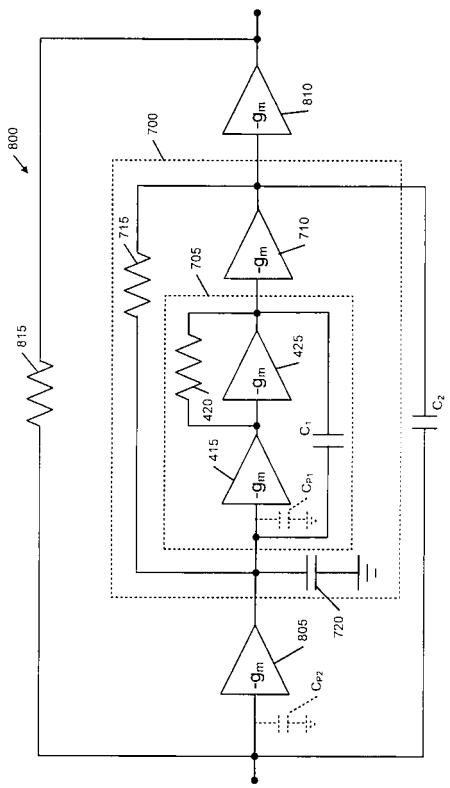

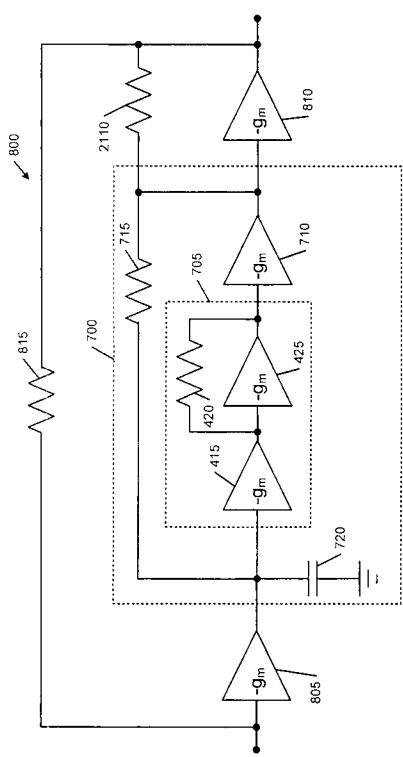

[0111] 次に図 8 を参照する。2 次の入れ子状の TIA 800 が、1 次の入れ子状の TIA 700 を基に構築されている。図 4 及び図 7 からの参照符号を図 8 においても使用し、同様の要素を特定する。2 次の入れ子状の TIA 800 は、オペアンプ 805 を、1 次の入れ子状の TIA 700 の入力に備えており、オペアンプ 810 を 1 次の入れ子状の TIA 700 の出力に備えている。追加のフィードバック抵抗 815 がまた、オペアンプ 805 の入力とオペアンプ 810 の出力の間に追加されている。2 次の入れ子状の TIA 800 を用いて生成される例示の利得帯域幅カーブを図 14 に示す。典型的な利得値の場合、約  $20 \text{ GHz}$  の帯域幅を達成し得る。

#### 【0066】

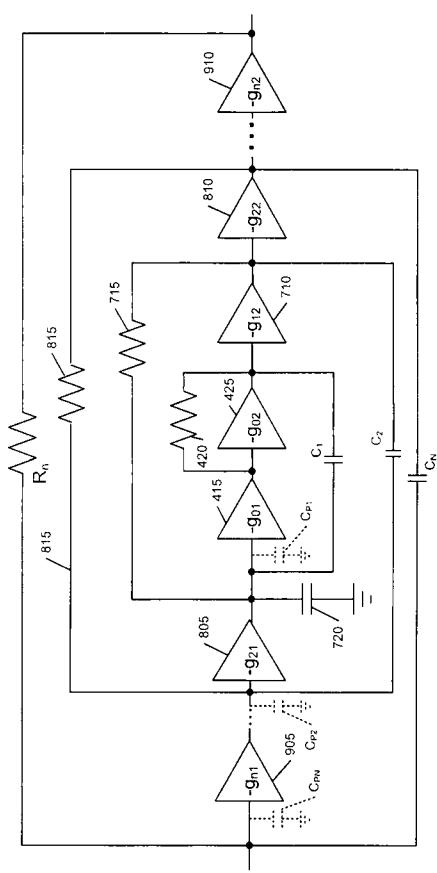

[0112] 次に図 9 を参照する。より高次の入れ子状の TIA は、追加のオペアンプ及びフィードバック抵抗を追加することによって構築し得る。図 4、図 7、及び図 8 からの参照符号を、図 9 においても使用して、同様の要素を特定する。例えば、3 次の入れ子状の TIA 900 は、オペアンプ 905 及び 910 と、フィードバック抵抗 915 を備えている。利得又は帯域幅の何れか、若しくはそれらの両者の値を、本発明の技術を繰り返すことによって、より高くすることが可能である。しかしながら、本回路の効率は、追加の入れ子の段が増すに連れて、寄生ノイズ及び増加する電力損失のために、低下する。一般的には、1 次の入れ子状の TIA、又は 2 次の入れ子状の TIA が、通常、十分な性能を提供するであろう。

#### 【0067】

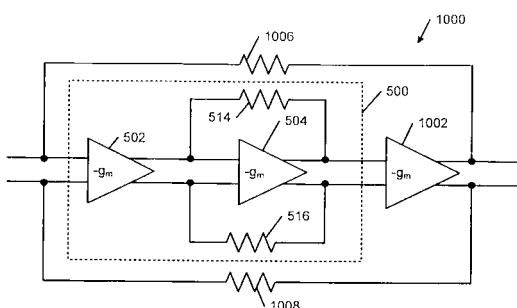

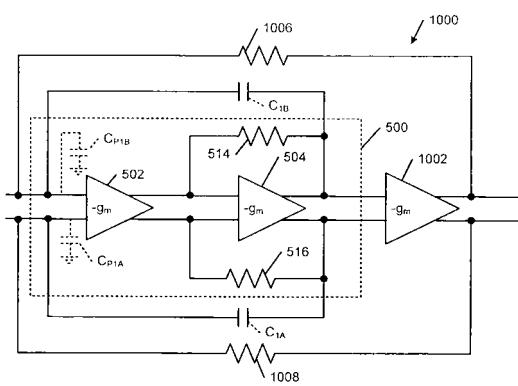

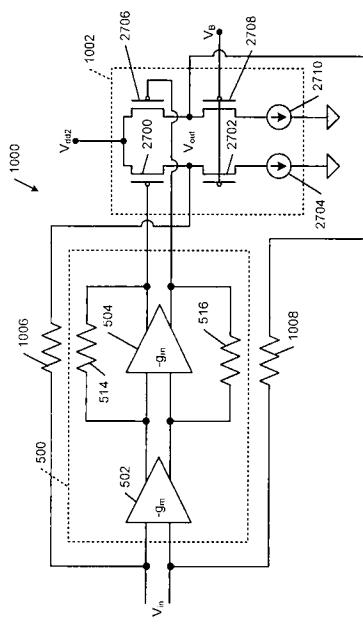

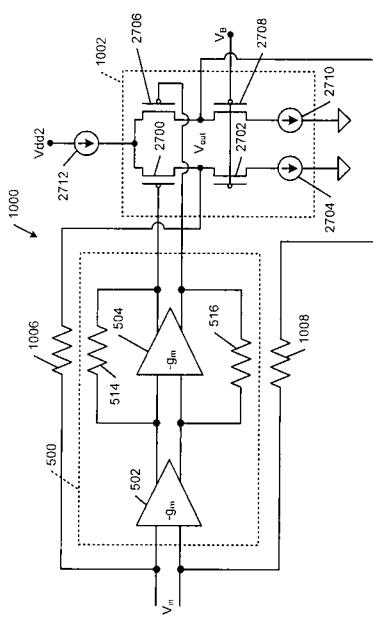

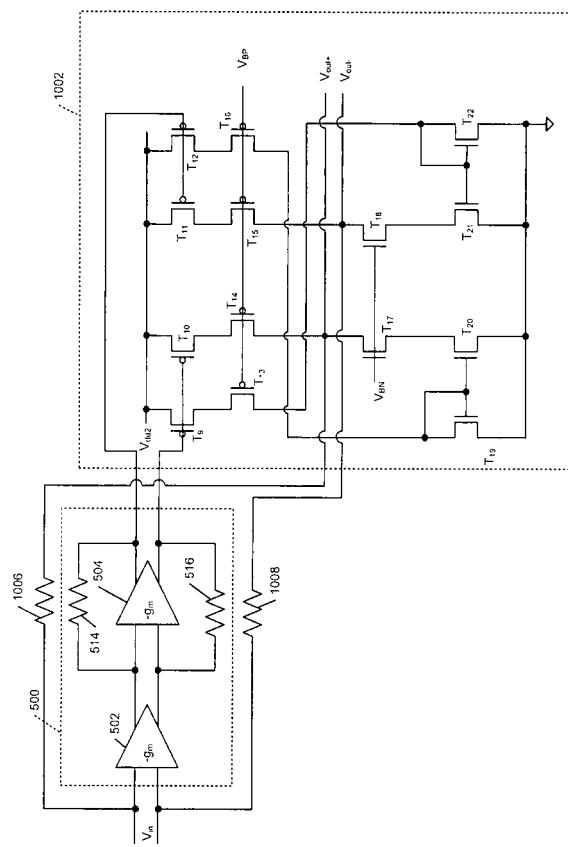

[0113] 次に図 10 を参照する。この図は、差動モードの 1 次の入れ子状の TIA 1000 を示している。図 5 からの参照符号を図 10 においても使用して同様の要素を特定している。オペアンプ 1002 が、オペアンプ 504 の出力に接続されている。フィードバック抵抗 1006 及び 1008 が、差動モードの TIA 500 の入力及びオペアンプ 1002 の出力に接続されている。この TIA の利得帯域幅積は向上されている。

#### 【0068】

[0114] 次に図 11 を参照する。差動モードの n 次の入れ子状の TIA 1100 が、図 9

10

20

30

40

50

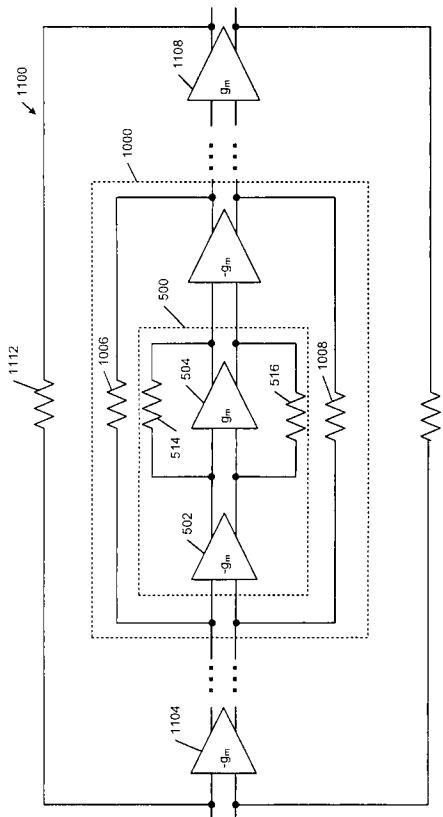

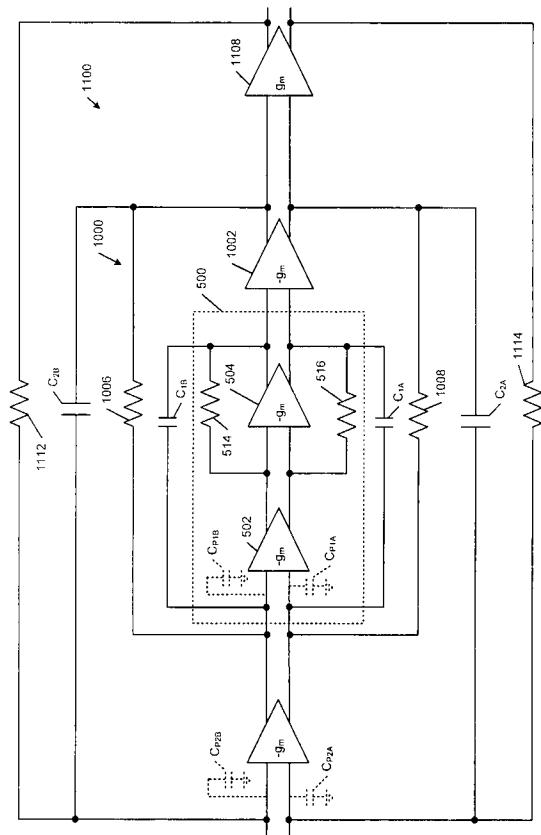

の  $n$  次の入れ子状の TIA と同様の態様で構築されている。図 5 及び図 10 からの参照符号を図 11 においても使用して同様の要素を特定している。追加のオペアンプ 1104 及び 1108 とフィードバック抵抗 1112 及び 1114 が、同様の態様で接続されている。差動モードの TIA の利得帯域幅特性は、図 12 ~ 図 14 に示す利得帯域幅特性と実質的に同様である。

#### 【0069】

[0115]入れ子状の TIA に使用されるオペアンプは、ガリウム砒素 (GaAs) トランジスタといったバイポーラ接合トランジスタ (BJT)、若しくは、CMOS 又は BIC MOS トランジスタといった金属酸化物半導体 (MOS) トランジスタの何れであってもよい。本発明の好適な実施の形態は、製造の容易さ、及び優れた電力消費特性のために、MOS トランジスタを使用する。

10

#### 【0070】

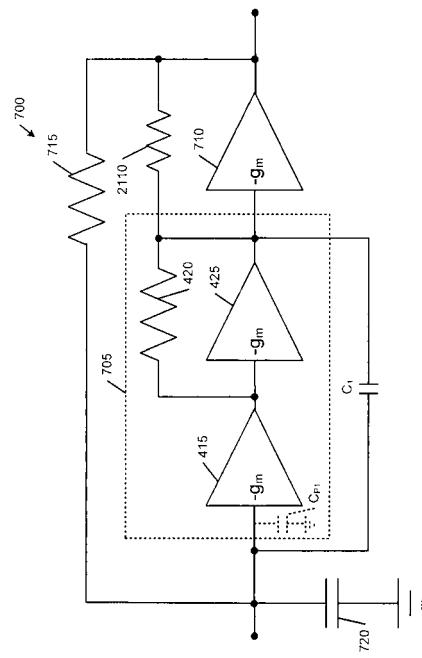

[0116]次に図 15 を参照する。この図は、1 次の入れ子状の TIA 700 を示すものであり、当該 TIA 700 は、追加のフィードバックキャパシタンス  $C_1$  を有しており、このキャパシタンス  $C_1$  は、オペアンプ 415 の入力における入力キャパシタンス  $C_{p1}$  の影響を実質的に打ち消す。フィードバックキャパシタンス  $C_1$  は、オペアンプ 415 の入力に接続する第 1 の端部と、オペアンプ 425 の出力に接続する第 2 の端部を有している。

#### 【0071】

[0117]次に図 16 を参照する。この図は、追加のフィードバックキャパシタンス  $C_1$  及び  $C_2$  を有する図 8 の 2 次の入れ子状の TIA 800 を示しており、これらキャパシタンスはそれぞれ、オペアンプ 415 及び 805 の入力における入力キャパシタンス  $C_{p1}$  及び  $C_{p2}$  の影響を、実質的に打ち消す。フィードバックキャパシタンス  $C_1$  は、オペアンプ 415 の入力に接続する第 1 の端部と、オペアンプ 425 の出力に接続する第 2 の端部を有している。フィードバックキャパシタンス  $C_2$  は、オペアンプ 805 の入力に接続する第 1 の端部と、オペアンプ 710 の出力に接続する第 2 の端部を有している。

20

#### 【0072】

[0118]次に図 17 を参照する。この図は、追加のフィードバックキャパシタンス  $C_1$ 、 $C_2$ 、 $\dots$ 、 $C_N$  を有する図 9 の  $n$  次の入れ子状の TIA を示しており、これらキャパシタンスはそれぞれ、オペアンプ 415、805 及び 905 の入力における入力キャパシタンス  $C_{p1}$ 、 $C_{p2}$ 、 $\dots$ 、 $C_{pN}$  の影響を実質的に打ち消す。フィードバックキャパシタンス  $C_1$  は、オペアンプ 415 の入力に接続する第 1 の端部と、オペアンプ 425 の出力に接続する第 2 の端部と、を有している。フィードバックキャパシタンス  $C_2$  は、オペアンプ 805 の入力に接続する第 1 の端部と、オペアンプ 710 の出力に接続する第 2 の端部と、を有している。フィードバックキャパシタンス  $C_N$  は、オペアンプ 905 の入力に接続する第 1 の端部と、オペアンプ 810 の出力に接続する第 2 の端部と、を有している。

30

#### 【0073】

[0119]次に図 18 を参照する。この図は、追加のフィードバックキャパシタ  $C_{1A}$  及び  $C_{1B}$  を有する 1 次の入れ子状の差動モード TIA 100 を示しており、これらキャパシタは、差動モードオペアンプ 502 の入力における入力寄生キャパシタンス  $C_{p1}$  及び  $C_{p2}$  の影響を実質的に打ち消す。フィードバックキャパシタンス  $C_{1A}$  は、差動モードオペアンプ 502 の入力に接続する第 1 の端部と、差動モードオペアンプ 504 の出力に接続する第 2 の端部と、を有している。図 19 では、追加のキャパシタンス  $C_{2A}$  及び  $C_{2B}$  が、2 次の差動モード TIA に、同様の態様で追加されており、寄生キャパシタンス  $C_{p2A}$  及び  $C_{p2B}$  を相殺している。より高次の回路は、同様の手法を使用する。

40

#### 【0074】

[0120]図 20 を再び参照する。この図は、図 7 の 1 次の入れ子状の TIA を追加のフィードバック抵抗 2010 付きで示している。フィードバック抵抗 2010 は、オペアンプ 710 の入力に接続する第 1 の端部を有している。抵抗 2010 の第 2 の端部は、オペア

50

ンプ 710 の出力に接続している。

【0075】

[0121] 次に図 21 を参照する。この図は、図 8 の 2 次の入れ子状の TIA を追加のフィードバック抵抗 2110 付きで示している。フィードバック抵抗 2110 は、オペアンプ 810 の入力に接続する第 1 の端部を有している。抵抗 2110 の第 2 の端部は、オペアンプ 810 の出力に接続している。

【0076】

[0122] 次に図 22 を参照する。この図は、図 15 の 1 次の入れ子状の TIA を、追加のフィードバック抵抗 2210 付きで示している。フィードバック抵抗 2210 は、オペアンプ 710 の入力に接続する第 1 の端部を有している。抵抗 2210 の第 2 の端部は、オペアンプ 710 の出力に接続している。

10

【0077】

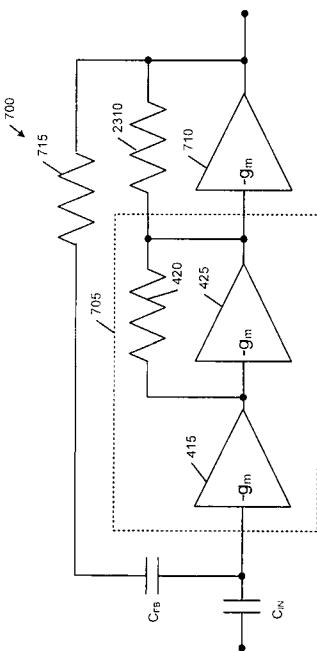

[0123] 次に図 23 を参照する。この図は、図 7 の 1 次の入れ子状の TIA を、入力キャパシタンス  $C_{IN}$ 、フィードバックキャパシタンス  $C_{FB}$ 、及びフィードバック抵抗 2310 付きで示している。入力キャパシタンス  $C_{IN}$  は、入れ子状の TIA 700 への入力信号を受ける第 1 の端部と、オペアンプ 415 の入力に接続する第 2 の端部と、を有している。フィードバックキャパシタンス  $C_{FB}$  は、オペアンプ 415 の入力に接続する第 1 の端部と、抵抗 715 の一端に接続する第 2 の端部と、を有している。

【0078】

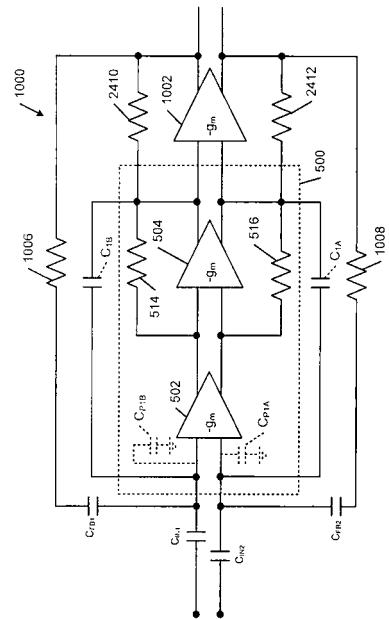

[0124] 追加のフィードバック抵抗、入力キャパシタンス、及び / 又はフィードバックキャパシタンスを、差動モードの入れ子状の TIA に追加することも可能である。ここで、図 24 を参照する。この図は、図 10 の 1 次の差動モードの入れ子状の TIA を、第 1 の入力キャパシタンス  $C_{IN1}$ 、第 2 の入力キャパシタンス  $C_{IN2}$ 、第 1 のフィードバックキャパシタンス  $C_{FB1}$ 、第 2 のフィードバックキャパシタンス  $C_{FB2}$ 、並びにフィードバック抵抗 2410 及び 2412 付きで示している。入力キャパシタンス  $C_{IN1}$  及び  $C_{IN2}$  は、入れ子状の差動モード TIA への入力信号を受ける第 1 の端部と、オペアンプ 502 の入力に接続する第 2 の端部と、を有している。フィードバックキャパシタンス  $C_{FB1}$  及び  $C_{FB2}$  はそれぞれ、オペアンプ 502 の入力に接続する第 1 の端部と、抵抗 1006 及び 1008 の第 1 の端部に接続する第 2 の端部と、を有している。第 1 のフィードバック抵抗 2410 及び第 2 のフィードバック抵抗 2412 は、入力に接続された第 1 の端部と、差動モードオペアンプ 1002 の出力に接続された第 2 の端部と、を有している。

20

【0079】

[0125] 理解可能なように、フィードバックキャパシタンス (図 15 ~ 図 19)、フィードバック抵抗 (図 20 ~ 図 24)、並びに、入力及びフィードバックキャパシタンス (図 23 及び図 24) を、任意の組合せで、第 1、第 2、. . . 、第  $n$  次の入れ子状の TIA 、及び / 又は差動モード TIA において、使用することが可能である。

30

【0080】

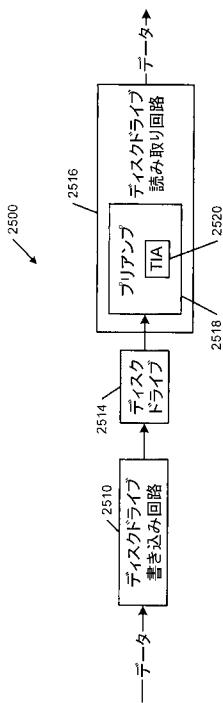

[0126] 次に図 25 を参照する。この図は、例示のディスクドライブシステム 2500 を示しており、当該システム 2500 は、ディスクドライブ 2514 に書き込むディスクドライブ書き込み回路 2510 を含んでいる。ディスクドライブ読み取り回路 2516 は、プリアンプ回路 2518 を含んでおり、当該回路 2518 は、2520 で特定されており上述したように実装される入れ子状の TIA 又は入れ子状の差動モード TIA を有している。

40

【0081】

[0127] 次に図 26 を参照する。この図は、図 7 の一次の入れ子状の TIA 700 を示しており、当該 TIA 700 は、オペアンプ 710 の第 1 の実装形態を含んでいる。オペアンプ 710 は、第 1 のトランジスタ 2600 を、第 2 のトランジスタ 2602 と直列に備えている。第 1 のトランジスタ 2600 のゲートは、0 次の TIA 705 の出力によって駆動される。第 2 のトランジスタ 2602 のゲートは、バイアス電圧  $V_B$  によって駆動さ

50

れる。TIA700の信号出力は、第1のトランジスタ2600のソースを第2のトランジスタ2602のドレインに接続するノードで取られている。第1の電流源2604は、第2のトランジスタ2602のソースから電流を引き込む。オペアンプ710は、ドレン電源電圧 $V_{dd2}$ によって電源供給される。電源供給の選択肢を、以下により詳細に説明する。

#### 【0082】

[0128]次に、図27を参照する。この図は、図10の差動モードの1次の入れ子状のTIA1000を示しており、当該TIA1000は、オペアンプ1002の第1の実装形態を含んでいる。オペアンプ1002は、第2のトランジスタ2702に接続する第1のトランジスタ2700を備えている。第1のトランジスタ2700のゲートは、差動の0次のTIA500の出力によって駆動される。第2のトランジスタ2702のゲートは、バイアス電圧 $V_B$ によって駆動される。TIA100の第1の信号出力は、第1のトランジスタ2600のソースを第2のトランジスタ2702のドレインに接続するノードで取られている。第1の電流源2704は、第2のトランジスタ2702のソースからの電流を引き込む。

#### 【0083】

[0129]第3のトランジスタ2706は、第4のトランジスタ2708に接続している。第3のトランジスタ2706のゲートは、差動の0次のTIA500の出力によって駆動される。第4のトランジスタ2708のゲートは、 $V_B$ によって駆動される。TIA1000の第2の信号出力は、第3のトランジスタ2706のソースを第4のトランジスタ2708のドレインに接続するノードで取られている。第2の電流源2710は、第2のトランジスタ2702のソースからの電流を引き込む。オペアンプ1002は、ドレン電源電圧 $V_{dd2}$ によって電源供給される。電源供給の選択肢を、以下により詳細に説明する。差動信号出力は、第1及び第2の信号出力にわたり、第1のトランジスタ2700及び第3のトランジスタ2706のそれぞれのソースで取られる。

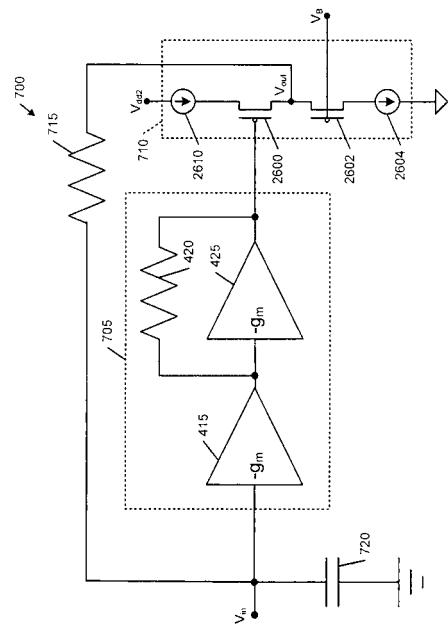

#### 【0084】

[0130]次に図28を参照する。この図は、図26の1次の入れ子状のTIA700を、示しており、当該TIA700は、オペアンプ710の第2の実装形態を含んでいる。第2の実装形態は、第2の電流源2610を有しており、当該第2の電流源2610は、第1のトランジスタ2600のドレインに電流を提供している。第2の電流源2610は、 $V_{dd2}$ から電流を引き込む。

#### 【0085】

[0131]次に図29を参照する。この図は、図27の差動モードの1次の入れ子状のTIA1000を示しており、当該TIA1000は、オペアンプ1002の第2の実装形態を含んでいる。第2の実装形態は、第3の電流源2712を含むものであり、当該第3の電流源2712は、第1のトランジスタ2700及び第3のトランジスタ2706のドレインに電流を提供するものである。第3の電流源2712は、 $V_{dd2}$ から電流を引き込む。

#### 【0086】

[0132]次に図30を参照する。この図は、図10の差動モードの1次の入れ子状のTIA1000を示しており、当該TIA1000はオペアンプ1002の第3の実装形態を含んでいる。オペアンプ1002は、プッシュプル構成を、図示のように含んでいる。オペアンプ1002は、正のバイアス電圧 $V_{Bp}$ 及び負のバイアス電圧 $V_{BN}$ を受ける。差動出力信号は、ノード $V_{out+}$ 及び $V_{out-}$ にわたって取られる。

#### 【0087】

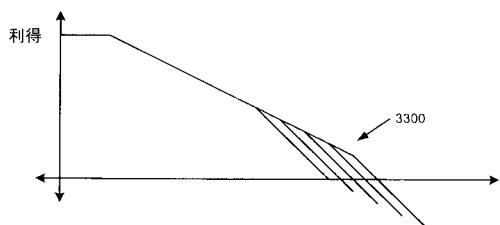

[0133]次に図31～図33を参照する。これらの図は、利得カーブの群を示している。これら利得カーブは、上述した種々の1次の入れ子状のTIAの典型的な利得パターンを示している。各グラフの対数縦軸は、利得 $A = V_{out} / V_{in}$ を示している。各グラフの対数横軸は、信号周波数を示している。図31のグラフは、種々のオペアンプの利得カーブ3100を示している。オペアンプは、0次のTIAより低い利得且つ大きい帯域幅

10

20

30

40

50

を提供する。このオペアンプの利得は、20 dB / decade の速度で低下する。

【0088】

[0134] 図32のグラフは、種々のTIAの利得カーブ3200の群を示している。最小の帯域幅をもつ利得カーブ3200は、0次のTIAに対応している。より大きな大域幅をもつ複数の利得カーブ3200は、入れ子の数が増加されたTIAに対応している。TIAは、一般に、オペアンプに比べて、高い利得と中程度の帯域幅を、提供する。0次のTIAの利得は、20 dB / decade の速度で低下する。

【0089】

[0135] 図33のグラフは、種々の1次の入れ子状のTIAの利得カーブ3300の群を示している。利得は、低い周波数で比較的に平坦である。周波数が増加するにつれて、利得が、図31に示すようにオペアンプの利得の影響により、20 dB / decade の速度で低下する。周波数が増加し続けるにつれて、利得は、オペアンプと選択された0次のTIAの組み合わせの影響により、40 dB / decade の速度で低下する。

10

【0090】

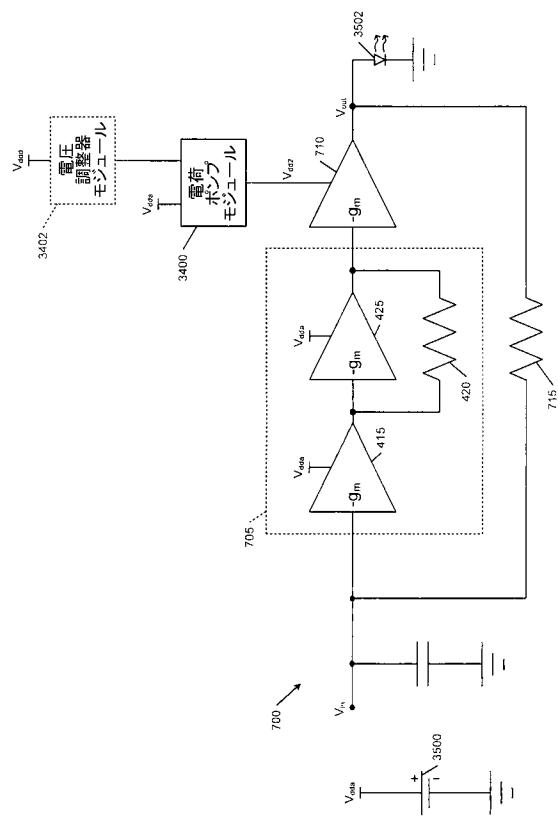

[0136] 次に、図34を参照する。この図は、1次の入れ子状のTIA用の電源構成の機能ブロック図を示している。この電源構成は、外部接続を二つの電圧及びグランドに提供するにもかかわらず、TIAチップに三つの固有の電圧レベルを提供する。図34は、図7の1次の入れ子状のTIA700に接続された電源を示しているが、当業者には、この電源が他のシングルエンドのTIA及び差動の1次の入れ子状のTIAに使用され得ることが理解される。アナログ電源 $V_{dd_a}$ は、外部接続の一方に結合されており、0次のTIAに電力を供給する。幾つかの実施形態では、 $V_{dd_a}$ は、約2.5 Vと3.3 Vの間の電圧である。

20

【0091】

[0137] アナログ電源 $V_{dd_a}$ はまた、電力を電荷ポンプモジュール3400に提供する。電荷ポンプモジュール3400はまた、電力をデジタル電源 $V_{dd_d}$ からも受ける。 $V_{dd_d}$ は、外部接続の他方に対応している。電荷ポンプモジュール3400は、1次の入れ子状のTIAと同じチップ上に形成することが可能である。幾つかの実施の形態では、 $V_{dd_d}$ は、約1.2 Vである。幾つかの実施の形態では、 $V_{dd_d}$ は、電圧調整器モジュール3402によって、電荷ポンプモジュール3400に印加する前に、調整することが可能である。電荷ポンプモジュール3400は、第2のデジタル電圧 $V_{dd_2}$ を生成するものであり、当該 $V_{dd_2}$ は、 $V_{dd_a} + V_{dd_d}$ に略等しい。従って、 $V_{dd_2} > V_{dd_a}$ である。当業者には、 $V_{dd_2}$ が、電荷ポンプモジュール3400に固有の損失及び/又は非効率性に起因して、 $V_{dd_a} + V_{dd_d}$ と正確には等しくないことが、理解されよう。

30

【0092】

[0138] 次に図35を参照する。この図は、図35の電源の応用を示している。 $V_{dd_a}$ は電池3500によって提供される。電池3500は、約2.7 Vと約4.2 Vの間の電圧を有するリチウムイオン電池であることができる。発光ダイオード(LED)が、オペアンプ710の出力に接続している。幾つかの実施の形態では、LEDは、約3.5 Vのターンオン電圧 $V_D$ を有する。電荷ポンプ回路3400は、電池3500からの $V_{dd_a}$ に $V_{dd_d}$ を加えて、LED3502を駆動するための十分な電圧を生成する。 $V_{dd_d}$ は、一般には、約1.2 Vの電圧を提供するだけであるので、LED3502への電力供給に単独で使用することはできない。電荷ポンプモジュール3400は、 $V_{dd_a}$ からの追加の電圧を提供して、3.5 Vの $V_D$ を超える約3.7 V ~ 4.2 Vの電圧をLEDに供給する。3.7 V ~ 4.2 Vの範囲は、電荷ポンプ回路における損失及び/又は非効率性を考慮したものであり、従って、正確には $V_{dd_a} + V_{dd_d}$ と等しくない。

40

【0093】

[0139] 本開示はまた、TIAの利得帯域幅積を向上する必要性に対処するものである。利得帯域幅積の向上は、他のTIAの内部にTIAを入れ子に設けることによって達成し得る。即ち、フィードバック抵抗、キャパシタンス、及び/又はオペアンプのような追加

50

の回路素子が、TIAの入力側及び/又はTIAの出力側に追加される。

【0094】

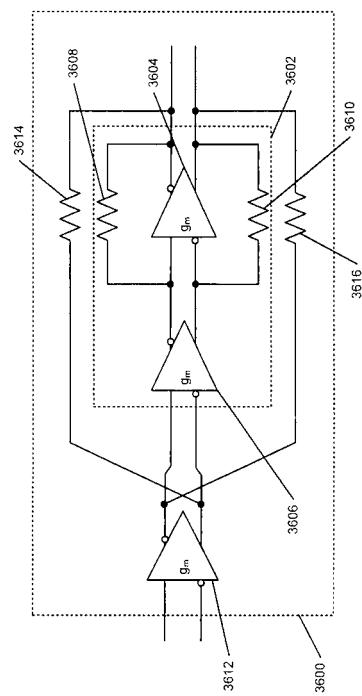

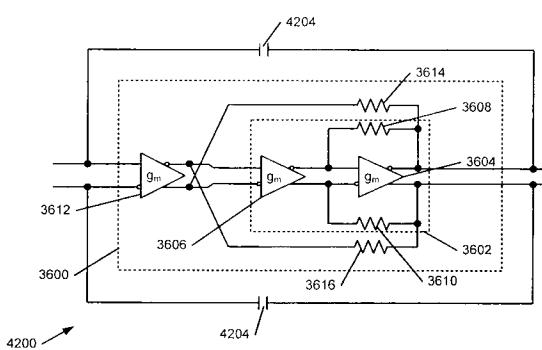

[0140]次に図36を参照する。この図は、内側のTIA3602を有する入れ子状のトランスインピーダンス増幅器(TIA)回路3600を示している。トランスインピーダンス増幅器3602は、第1の演算増幅器3604及び第2の演算増幅器3606を有している。この図及び後述の図に示す各演算増幅器は、「o」シンボルがないことによって特定される非反転入力及び非反転出力を有しており、「o」シンボルによって特定される反転入力及び反転出力を有している。トランスインピーダンス増幅器3602はまた、非反転入力及び反転出力に接続する第1のフィードバック抵抗3608と、反転入力及び非反転出力に接続する第2の抵抗3610を有している。

10

【0095】

[0141]入れ子状のトランスインピーダンス増幅器3600はまた、反転入力、反転出力、非反転入力、及び非反転出力を有する第3の演算増幅器3612を備えている。演算増幅器3612は、増幅器3606の非反転入力に接続する反転出力を有しており、増幅器3606の反転入力に接続する非反転出力を有している。

【0096】

[0142]フィードバック抵抗3614は、増幅器3612の非反転出力、及び増幅器3604の反転出力に接続している。増幅器3612の反転出力は、増幅器3604の非反転出力に接続している。即ち、抵抗3614は、増幅器3606の反転入力に接続し、一方、抵抗3616は、増幅器3606の非反転入力に接続している。

20

【0097】

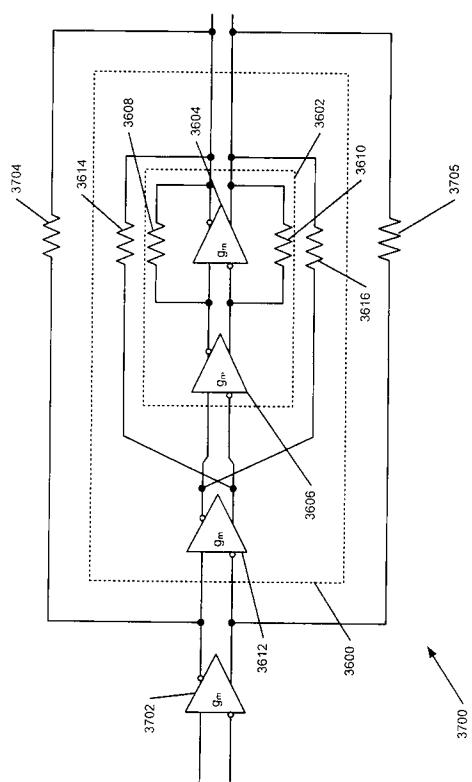

[0143]次に図37を参照する。この図は、二重の入れ子状のトランスインピーダンス増幅器3700を示している。二重の入れ子状のトランスインピーダンス増幅器は、トランスインピーダンス増幅器3602と、図36の入れ子状のトランスインピーダンス増幅器構造3600と、を備えている。したがって、これらの共通の回路部品を更には説明しない。この実施の形態では、反転及び非反転それぞれの入力及び出力を有する別の増幅器3702が、示されている。この実施の形態では、増幅器3702の反転出力は、増幅器3612の非反転入力に接続している。増幅器3702の非反転出力は、増幅器3612の反転入力に接続している。フィードバック抵抗3704は、増幅器3702の反転出力と増幅器3612の非反転入力の共通ノードに接続している。抵抗3704はまた、増幅器3604の反転出力に接続している。第2のフィードバック抵抗3705は、増幅器3702の非反転出力と増幅器3612の反転入力の間の共通ノード、及び増幅器3604の非反転出力に接続している。

30

【0098】

[0144]図36及び図37に示した差動の構造及びフィードバックの構造を提供することによって、より少ない反転(inversion)を所与のレベルの入れ子用に示した。これによって、潜在的に高い周波数での動作が、図7に示したようなデバイスから得られる。これらの例では、入れ子は、入れ子のレベルを増加するときに改善されるべき出力歪みを生じさせる出力ノードに発生している。

40

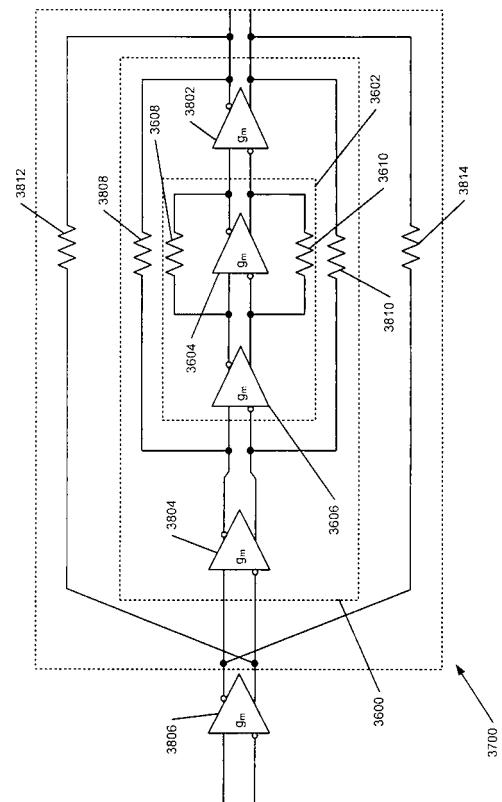

【0099】

[0145]次に図38を参照する。この図では、図36に示したトランスインピーダンス構造3602が、入れ子状のTIA3800において使用されている。この実施の形態では、演算増幅器3802が、増幅器3604の非反転出力に接続する反転入力を有している。増幅器3802の非反転入力は、増幅器3604の反転出力に接続している。

【0100】

[0146]別の増幅器3804は、増幅器3606の非反転入力に接続する反転出力を有している。増幅器3804の非反転出力は、増幅器3606の反転入力に接続している。別の演算増幅器3806は、増幅器3804の非反転入力に接続する反転出力、及び増幅器3804の反転入力に接続する非反転出力を有している。第1のフィードバック抵抗3808は、増幅器3804の反転出力と増幅器3606の非反転入力の間の共通ノード、及

50

び増幅器 3802 の反転出力に接続している。別のフィードバック抵抗 3810 は、増幅器 3804 の非反転出力と増幅器 3806 の反転入力の共通ノード、及び増幅器 3802 の非反転出力に接続している。

#### 【0101】

[0147] フィードバック抵抗 312 は、増幅器 3806 の非反転出力と反転の増幅器 3804 の間の共通ノード、及び増幅器 3802 の反転出力に接続している。別の抵抗 3814 は、増幅器 3806 の反転出力と増幅器 3804 の非反転入力の間のノード、及び増幅器 3802 の非反転出力に接続している。

#### 【0102】

[0148] 種々のタイプの入れ子を実施して、より高次の入れ子状のトランスインピーダンス増幅器を構築してもよい。増幅器 3802 は、入れ子に関する限りにおいては、重要ではない。回路の入力が、電圧ではなく電流である場合には、増幅器 3806 が不要なことがある。

10

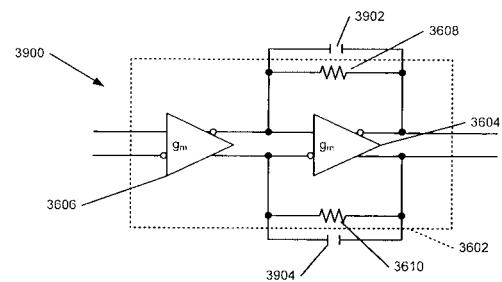

#### 【0103】

[0149] 次に、図 39A 及び 39B を参照する。これらの図はそれぞれ、容量性のフィードバックを有する差動のトランスインピーダンス増幅器、及びシングルエンドのトランスインピーダンス増幅器を示している。図 39A では、差動トライインピーダンス増幅器 3900 は、図 36 のトランスインピーダンス増幅器 3602 に類似するものであり、抵抗 3608 に並列の第 1 のキャパシタンス 3902 と、抵抗 3610 に並列の第 2 のキャパシタンス 3904 を有するように、示してある。この実施の形態では、トランスインピーダンスネットワークの周波数応答又は安定性を、キャパシタンス 3902 及び 3904 を備えることによって改善し得る。理解可能なように、キャパシタンスを、必要に応じてインダクタンスに置き換えることが可能である。

20

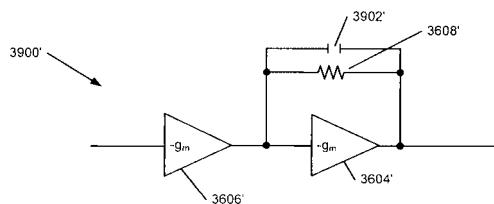

#### 【0104】

[0150] 図 39B は、シングルエンドのトランスインピーダンス増幅器 3900' を示しており、この増幅器 3900' は、図 39A に示す差動構成に類似するものである。図 39B では、同様の素子が、ダッシュ記号「」でラベル付けされている。増幅器 3604' 及び / 又は 3606' の相互コンダクタンス  $g_m$  は、負であってもよく、並びに / 若しくは、信号が、増幅器 3604' 及び / 又は 3606' の反転入力に結合されてもよい。

30

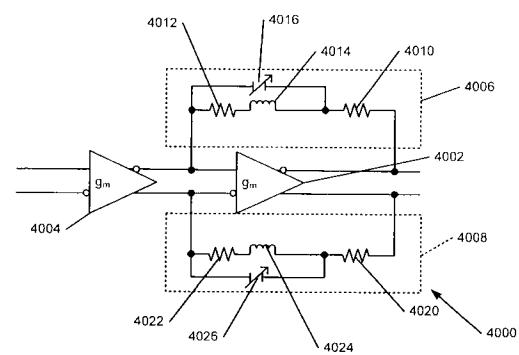

#### 【0105】

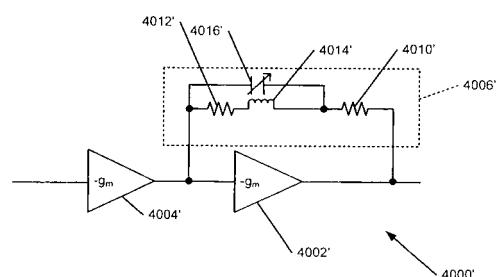

[0151] 次に図 40A 及び図 40B を参照する。これらの図では、それぞれ、差動トランスインピーダンス増幅器のフィードバック、及びシングルエンドのトランスインピーダンス増幅器のフィードバックに、LC タンク回路が設けられている。図 40A には、差動トランスインピーダンス増幅器 4000 を示してある。この実施の形態では、第 1 の演算増幅器 4002 が、増幅器 4004 の反転出力に接続する非反転入力を有している。増幅器 4002 の反転入力は、増幅器 4004 の非反転出力に接続している。フィードバック素子 4006 は、増幅器 4002 の非反転入力と増幅器 4004 の反転出力の共通ノード、及び増幅器 4002 の反転出力に接続している。同様に、第 2 のフィードバック素子 4008 は、増幅器 4002 の反転入力と増幅器 4004 の非反転出力の共通ノード、及び増幅器 4002 の非反転出力に接続している。

40

#### 【0106】

[0152] フィードバック素子 4006 は、抵抗 4010 と、直列結合の抵抗 4012 及びインダクタンス 4014 を有している。幾つかの実施の形態では、インダクタンス 4014 は、可変インダクタンスであることが可能である。可変キャパシタンス 4016 は、直列結合の抵抗 4012 及びインダクタンス 4014 と並列に結合されている。この並列結合体は、抵抗 4010 に直列に結合されている。同様に、フィードバック素子 4008 は、同様の方法で、抵抗 4020、インダクタンスに直列の第 2 の抵抗 4022、及び可変キャパシタンス 4026 を有して、構成されている。

#### 【0107】

[0153] 可変キャパシタンス 4016 及び 4026 は、当該キャパシタンスの値を変化さ

50

することによって、LCタンク回路における種々の共振周波数を調整し得ることを示すために、使用されている。実際の実施の形態においては、所望の共振周波数に設定する固定のキャパシタンスが使用されてもよい。回路4000は、超広帯域の動作（例えば、50MHz～1GHz）を有することが要請されるTVチューナにおけるRF増幅器としての使用に適している。この回路は、LCタンクの利点を広帯域で動作するトランスインピーダンス増幅器の特性と共に取り入れて、必要な信号を、不要な信号より、増幅する。並列のLCタンク回路は、フィードバックネットワークに、LCタンク回路の共振周波数で高インピーダンスをもたせる。

#### 【0108】

[0154]図40に示す構造を、上述した増幅器の構造において、入れ子にしてもよい。後続の入れ子の各々では、入れ子の性質が、LCタンク素子の共振周波数で有効になるよう10に、注目する信号周波数のみが増幅される。このために、入れ子状のLCタンク回路のトランスインピーダンス増幅器の選択性が顕著に改善され、一方、帯域外の信号は増幅されない。これは、増幅器の歪み性能を、不要な信号を増幅しないことによって向上する。同時に、帯域内の信号は、入れ子状のトランスインピーダンス増幅器の性質のために、極めて低い歪みで増幅される。

#### 【0109】

[0155]図40Bに、図40Aに示した差動構成に類似するシングルエンドのトランスインピーダンス増幅器4000'を示す。図40Bでは、同様の要素が、ダッシュ記号「-」を用いてラベル付けされている。増幅器4002'及び/又は4004'の相互コンダクタンス $g_m$ は負であってもよく、信号が増幅器4002'及び/又は4004'の反転20入力に結合されてもよい。

#### 【0110】

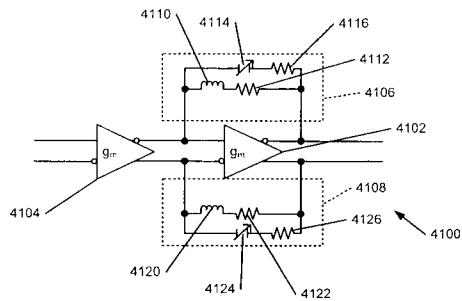

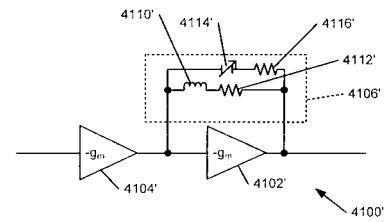

[0156]次に図41A及び図41Bを参照する。これらの図は、それぞれ、差動のトランジンピーダンス増幅器及びシングルエンドのトランジンピーダンス増幅器の別の実施の形態の概略図を示している。図41Aには、LC回路を用いた差動トランジンピーダンス増幅器4100を示している。この実施の形態では、第1の演算増幅器4102が、第2の増幅器4101に接続している。増幅器4104の反転出力は、増幅器4102の非反転入力に接続している。増幅器4104の非反転出力は、増幅器4102の反転入力に接続している。第1のLC回路4106は、増幅器4102の非反転入力及び増幅器4102の反転出力に接続している。第2のLC回路4108は、増幅器4102の反転入力及び非反転出力に接続している。30

#### 【0111】

[0157]LC回路4106は、インダクタンス4110を、抵抗4112と直列に有している。LC回路4106はまた、キャパシタンス4114を抵抗4116と直列に有している。キャパシタンス4114と抵抗4116の直列結合体は、インダクタンス4110と抵抗4112の直列結合体と並列になっている。

#### 【0112】

[0158]LC回路4108は、LC回路4106と同様に構成されている。LC回路4108は、インダクタンス4120を、抵抗4122と直列に有している。キャパシタンス4124は、抵抗4126と直列になっている。インダクタンス4120と抵抗4122の直列結合体は、キャパシタンス4124と抵抗4126の直列結合体と並列になっている。

#### 【0113】

[0159]図40に示したように、抵抗をLCタンク回路と並列に提供することによって、又は、インダクタンスとキャパシタンスの両者に抵抗を加えることによって、回路の発振が避けられる。図40と比べて、追加の抵抗は、増幅器の極性が高周波数で変化することを防止する。これを使用して、入れ子状のトランジンピーダンス増幅器内のフィードバック動作を防止している。

#### 【0114】

10

20

30

40

50

[0160]図41Bに、図41Aに示した差動構成と同様のシングルエンドの増幅器410'を示している。図41Bでは、同様の要素がダッシュ記号「」でラベル付けされている。増幅器4102'及び4104'の相互コンダクタンス $g_m$ は負であってもよく、及び/又は、信号が増幅器4102'及び/又は4104'の反転入力に結合されてもよい。

#### 【0115】

[0161]次に図42を参照する。この図は、入れ子状のトランスインピーダンス増幅器を使用して形成された積分器4200を示している。この実施の形態は、抵抗3704及び3705がキャパシタンス4202及び4204と置き換えられている以外、図37に示した二重の入れ子状のトランスインピーダンス増幅器と同一である。

10

#### 【0116】

[0162]積分器4200は、上記のトランスインピーダンス構成のために、高帯域幅を有する。出力インピーダンスは、高周波数であっても低い。低い出力インピーダンスのために、積分器4200は、大きな容量性の負荷を駆動するのに使用され得る。積分器4200の一つの応用は、ギガヘルツを超えるサンプリング周波数で動作するシグマデルタ・アナログ-デジタル変換機におけるものである。

#### 【0117】

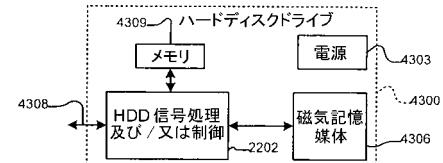

[0163]次に図43A～43Gを参照する。これらの図は、本開示に係る種々の例示の実装形態を示している。まず、図43Aを参照する。本開示は、ハードディスクドライブ4300の増幅器及び/又は積分器において実装することが可能である。本開示は、信号処理回路及び/又は制御回路の一方又は両者、並びに/若しくは電源4303において実装してもよく、及び/又は実装されてもよい。信号処理回路及び/又は制御回路は、図43Aにおいては参照符号4302で大まかに特定されている。幾つかの実装形態では、信号処理及び/又は制御回路4302、並びに/若しくはHDD4300内の他の回路(図示せず)は、データを処理し、符号化及び/又は暗号化を実行し、計算を実行し、並びに/若しくは、磁気記憶媒体4306に出力し及び/又は磁気記憶媒体4306から受け取るデータをフォーマット化し得る。

20

#### 【0118】

[0164]HDD4300は、コンピュータ、パーソナルデジタルアシスタント、携帯電話、メディア又はMP3プレーヤ等といった携帯計算デバイス、並びに/若しくは他のデバイスのようなホストデバイス(図示せず)と、一以上の有線又は無線の通信リンク4308を介して、通信してもよい。HDD4300は、ランダムアクセスメモリ(RAM)、フラッシュメモリといった低遅延不揮発性メモリ、リードオンリーメモリ(ROM)、及び/又は他の適切な電子データ記憶装置のようなメモリ4309に接続されてもよい。

30

#### 【0119】

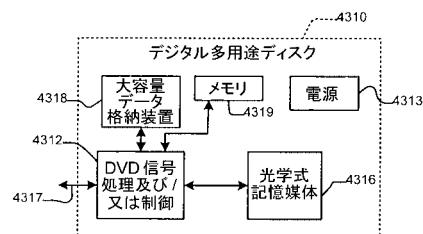

[0165]次に図43Bを参照する。本開示は、デジタル多用途ディスク(DVD)4310の増幅器及び/又は積分器において実装することが可能である。本開示は、図43Bにおいて参照符号4312で大まかに特定されている信号処理回路及び/又は制御回路の一方又は両者、DVDドライブ4310の大容量データ格納装置、並びに/若しくは、電源4313において、実装してもよく、及び/又は実装されてもよい。信号処理及び/又は制御回路4312、並びに/若しくは、DVD4310における他の回路(図示せず)は、データを処理し、符号化及び/又は暗号化を実行し、計算を実行し、並びに/若しくは、磁気記憶媒体4306から読み取られる及び/又は光学式記憶媒体4316に書き込まれるデータをフォーマット化し得る。幾つかの実施の形態では、信号処理及び/又は制御回路4312、並びに/若しくはDVD4310における他の回路(図示せず)はまた、符号化及び/又は復号、並びに/若しくはDVDドライブに関連する任意の他の信号処理のような別の機能を実行し得る。

40

#### 【0120】

[0166]DVDドライブ4310は、コンピュータ、テレビ装置、又は他のデバイスと、一以上の有線及び/又は無線の通信リンク4317を介して、通信してもよい。DVD4

50

310は、不揮発性の方式でデータを格納する大容量データ格納装置4318に接続してもよい。大容量データ格納装置4318は、ハードディスクドライブを含み得る。HDDは、図43Aに示す構成を有していてもよい。HDDは、約1.8インチより小さい直径を有する一以上のプラッタを有するミニHDDであってもよい。DVD4310は、RAM、ROM、フラッシュメモリといった低遅延の不揮発性メモリ、及び/又は他の適切な電子データ記憶装置のようなメモリ4319に接続されていてもよい。

#### 【0121】

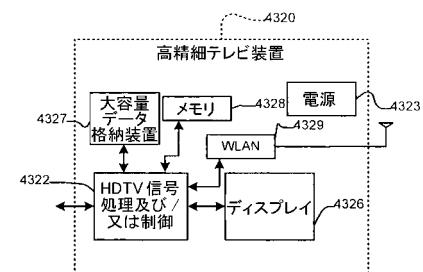

[0167]次に図43Cを参照する。本開示は、高精細テレビ装置(HDTV)4320の増幅器及び/又は積分器において実装することができる。本開示は、図43Eにおいて参考符号4322で大まかに特定されている信号処理回路及び/又は制御回路の一方又は両者、WLANインタフェイス、HDTV4320の大容量データ格納装置、並びに/若しくは電源4323において実装してもよく、及び/又は実装されてもよい。HDTV4320は、HDTV入力信号を、有線又は無線形式の何れかで受信し、HDTV出力信号をディスプレイ4326へ出力する。幾つかの実装形態では、信号処理及び/又は制御回路4322、並びに/若しくはHDTV4320の他の回路(図示せず)は、データを処理し、符号化及び/又は暗号化を実行し、計算を実行し、データをフォーマット化し、並びに/若しくは、必要とされ得る任意の他のタイプのHDTV処理を実行し得る。

10

#### 【0122】

[0168]HDTV4320は、光学式及び/又は磁気式の記憶デバイスのように不揮発性の方式でデータを格納する大容量データ格納装置4327に接続していてもよい。少なくとも一つのHDDが、図43Aに示した構成を有していてもよく、及び/又は少なくとも一つのDVDが、図43Bに示した構成を有していてもよい。HDDは、約1.8インチより小さい直径を有する一以上のプラッタを備えるミニHDDであってもよい。HDTV4320は、RAM、ROM、フラッシュメモリといった低遅延の不揮発性メモリ、及び/又は他の適切な電子データ記憶装置のようなメモリ4328に接続されてもよい。HDTV4320はまた、WLANとの接続を、WLANネットワークインタフェイス4329を介して、サポートしてもよい。

20

#### 【0123】

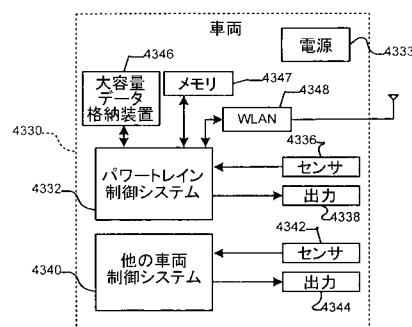

[0169]次に図43Dを参照する。本開示は、車両4330の制御システムに制御回路、WLANインタフェイス、車両制御システムの大容量データ格納装置、及び/又は電源4333の増幅器並びに/若しくは積分器において実装してもよく、及び/又は実装されてもよい。幾つかの実装形態では、本開示はパワートレイン制御システム4332を実施する。パワートレイン制御システム4332は、温度センサ、圧力センサ、回転センサ、エアーフローセンサ、及び/又は任意の他の適切なセンサから入力を受け取り、並びに/若しくは、エンジン動作パラメータ、トランスマッショントラクション動作パラメータ、及び/又は他の制御信号のような一以上の出力制御信号を生成する。

30

#### 【0124】

[0170]本開示は、車両4330の他の制御システム4340において実装してもよい。制御システム4340は、同様に、入力センサ4342から信号を受け取り、及び/又は、制御信号を一以上の出力デバイス4344に出力し得る。幾つかの実装形態では、制御システム4340は、アンチロックブレーキングシステム(ABS)、ナビゲーションシステム、テレマティックシステム、車両テレマティックシステム、車線逸脱システム、適応走行制御システム、並びに、ステレオ、DVD、及び、コンパクトディスク等の車両娛樂システムの一部となり得る。

40

#### 【0125】

[0171]車両制御システム4332は、不揮発性の方式でデータを格納する大容量データ格納装置4346に接続してもよい。大容量データ格納装置4346は、光学式及び/又は磁気式の格納装置、例えば、ハードディスクドライブHDD、及び/又はDVDを含むことができる。少なくとも一つのHDDが、図43Aに示す構成を有していてもよく、少なくとも一つのDVDが、図43Bに示す構成を有していてもよい。HDDは、約1.8

50

インチより小さい直径を有する一以上のプラッタを備えるミニHDDであってもよい。パワートレイン制御システム4332は、RAM、ROM、フラッシュメモリといった低遅延の不揮発性メモリ、及び／又は他の適切な電子データ記憶装置のようなメモリ4347に接続されていてもよい。パワートレイン制御システム4332はまた、WLANとの接続を、WLANネットワークインターフェイス4348を介して、サポートしてもよい。制御システム4340はまた、大容量データ格納装置、メモリ、及び／又はWLANインターフェイス（全て図示せず）を備えていてもよい。

【0126】

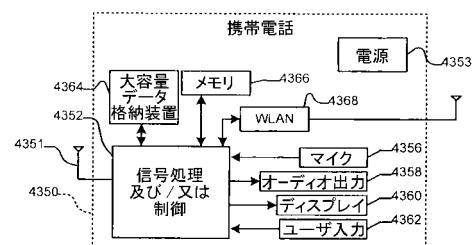

[0172]次に図43Eを参照する。本開示は、携帯アンテナ4351を有し得る携帯電話4350の増幅器、及び／又は積分器において実装することが可能である。本開示は、図43Eでは参照符号4352で大まかに特定されている信号処理回路及び／又は制御回路の一方又は両者、WLANインターフェイス、携帯電話4350の大容量データ格納装置、及び／又は電源4353において実装してもよく、及び／又は実装されてもよい。幾つかの実装形態では、携帯電話4350が、マイクロフォン4356、スピーカ及び／又はオーディオ出力ジャックのようなオーディオ出力4358、ディスプレイ4360、並びに／若しくは、キーパッド、ポインティングデバイス、音声駆動及び／又は他の入力デバイスのような入力デバイス4362を備える。信号処理及び／又は制御回路4352、並びに／若しくは、携帯電話4350における他の回路（図示せず）が、データを処理し、符号化及び／又は暗号化を実行し、計算を実行し、データをフォーマット化し、並びに／若しくは、他の携帯電話機能を実行してもよい。

10

20

【0127】

[0173]携帯電話4350は、大容量データ格納装置4346に接続してもよい。大容量データ格納装置4346は、光学式及び／又は磁気式の格納デバイス、例えば、ハードディスクドライブHDD、及び／又はDVDのように、不揮発性の方式でデータを格納する。少なくとも一つのHDDが、図43Aに示す構成を有してもよく、及び／又は少なくとも一つのDVDが図43Bに示す構成を有してもよい。HDDは、約1.8インチより小さい直径を有する一以上のプラッタを備えるミニHDDであってもよい。携帯電話4350は、RAM、ROM、フラッシュメモリといった低遅延の不揮発性メモリ、及び／又は他の適切な電子データ記憶装置のようなメモリ4366に接続されていてもよい。携帯電話4350はまた、WLANとの接続を、WLANネットワークインターフェイス4368を介して、サポートしてもよい。

30

【0128】

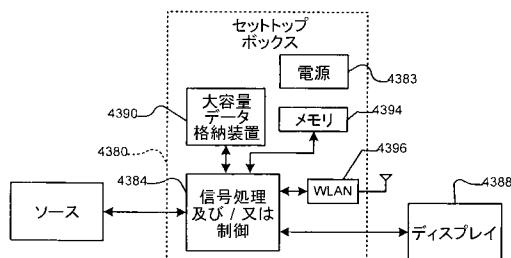

[0174]次に図43Fを参照する。本開示は、セットトップボックス4380の増幅器及び／又は積分器において実装することが可能である。本開示は、図43Fにおいて参照符号4384で大まかに特定されている信号処理回路及び／又は制御回路の一方又は両者、WLANインターフェイス、セットトップボックス4380の大容量データ格納装置、並びに／若しくは電源4383において実装してもよく、及び／又は実装されてもよい。セットトップボックス4380は、ブロードバンドソースのようなソースから信号を受信し、標準及び／又は高精細のオーディオ／ビデオ信号を、テレビ装置及び／又はモニタ、並びに／若しくは、他のビデオ及び／又はオーディオ出力デバイスのようなディスプレイ4388に、出力する。信号処理及び／又は制御回路4384、並びに／若しくはセットトップボックス4380の他の回路（図示せず）は、データを処理し、符号化及び／又は暗号化を実行し、計算を実行し、データをフォーマット化し、並びに／若しくは、任意の別のセットトップボックス機能を実行してもよい。

40

【0129】

[0175]セットトップボックス4380は、不揮発性の方式でデータを格納する大容量データ格納装置4390に接続してもよい。大容量データ格納装置4390は、光学式及び／又は磁気式の格納デバイス、例えば、ハードディスクドライブ、及び／又はDVDを含み得る。少なくとも一つのHDDが、図43Aに示す構成を有してもよく、及び／又は、少なくとも一つのDVDが、図43Bに示す構成を有してもよい。HDDは

50

、約1.8インチより小さい直径を有する一以上のプラッタを備えるミニHDDであってもよい。セットトップボックス4380は、RAM、ROM、フラッシュメモリのような低遅延の不揮発性メモリ、及び/又は他の適切な電子データ記憶装置に接続されていてもよい。セットトップボックス4380はまた、WLANへの接続を、WLANネットワークインターフェイス4396を介して、サポートしてもよい。

### 【0130】

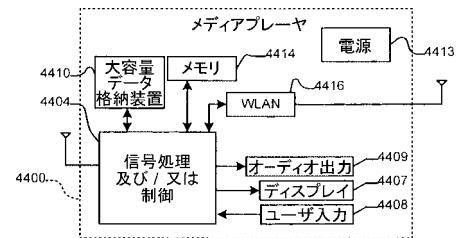

[0176]次に、図43Gを参照する。本開示は、メディアプレーヤ400の増幅器及び/又は積分器において実装することが可能である。本開示は、図43Gでは参照符号4404で大まかに特定されている信号処理回路及び/又は制御回路の一方又は両者、WLANインターフェイス、メディアプレーヤ4400の大容量データ格納装置、並びに/若しくは電源4403において、実装してもよく、及び/又は、実装されてもよい。幾つかの実装形態においては、メディアプレーヤ4400は、ディスプレイ4407、及び/又は、キーパッド、タッチパッド等のユーザ入力4408を有している。幾つかの実装形態では、メディアプレーヤ4400が、グラフィカルユーザインターフェイス(GUI)を採用してもよい。GUIは、通常、ディスプレイ4407及び/又はユーザ入力4408を介するメニュー、ドロップダウンメニュー、アイコン、並びに/若しくはポイント・クリックインターフェイスを採用する。メディアプレーヤ4400は、更に、スピーカ及び/又はオーディオジャックのようなオーディオ出力4409を備えている。信号処理及び/又は制御回路4404、並びに/若しくはメディアプレーヤ4400の他の回路(図示せず)は、データを処理し、符号化及び/又は暗号化を実行し、計算を実行し、データをフォーマット化し、並びに/若しくは、任意の他のメディアプレーヤ機能を実行し得る。

10

20

### 【0131】

[0177]メディアプレーヤ4400は、大容量データ格納装置4410に接続していてもよい。大容量データ格納装置4410は、圧縮されたオーディオ及び/又はビデオのコンテンツのようなデータを不揮発性の方式で格納する。幾つかの実装形態では、圧縮オーディオファイルが、MP3フォーマット、又は他の適切な圧縮オーディオ及び/又はビデオフォーマットに準拠するファイルを含む。大容量データ格納装置は、光学式及び/又は磁気式の格納装置、例えば、ハードディスクドライブHDD、及び/又はDVDを備えてもよい。少なくとも一つのHDDが、図43Aに示す構成を有していてもよく、及び/又は、少なくとも一つのDVDが、図43Bに示す構成を有していてもよい。HDDは、約1.8インチより小さい直径を有する一以上のプラッタを有するミニHDDであってもよい。メディアプレーヤ4400は、RAM、ROM、フラッシュメモリといった低遅延の不揮発性メモリ、及び/又は他の適切な電子データ記憶装置のようなメモリ4414に接続されていてもよい。メディアプレーヤ4400はまた、WLANとの接続を、WLANネットワークインターフェイス4416を介してサポートしてもよい。更に別の実装形態が、上述したものに加えて、想定される。

30

### 【0132】

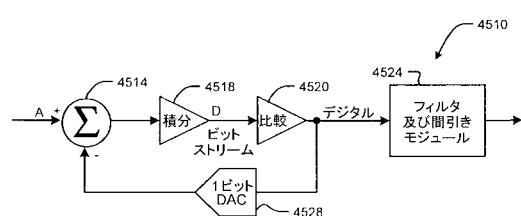

[0178]次に、図44を参照する。この図は、シグマデルタ・アナログ-デジタル変換器(ADC)モジュール4510を示している。シグマデルタADCモジュール2810は、アナログ入力信号を受ける差動増幅器モジュール4514を備える。差動増幅器モジュール4514の出力は、積分器モジュール4518への入力である。積分器モジュール4518の出力は、比較器モジュール4520の一方の入力である。比較器モジュール4520の他方の入力は、グランドのような基準電位に接続され得る。比較器モジュール4520の出力は、フィルタ及び間引きモジュール4524への入力であり、デジタル信号を出力する。比較器モジュール4520の出力は、デジタル-アナログ変換器(DAC)モジュール4528への入力である。DACモジュール4528は、1ビットのDACであってもよい。DACモジュール4528の出力は、差動増幅器モジュール4514の反転入力への入力である。

40

### 【0133】

[0179]使用の際には、DACモジュール4528の出力が、入力信号から差し引かれる

50

。得られる信号は、積分器モジュール4518によって積分される。積分器の出力電圧は、単一ビットのデジタル出力(1又は0)に、比較器モジュール4520によって変換される。得られるビットは、D A Cモジュール4528への入力になる。この閉ループ処理は、非常に高いサンプリングレートで、実行してもよい。比較器モジュールによるデジタルデータ出力は、1及び0からなるストリームであり、信号の値は、比較器モジュールによって出力される1の密度に比例する。値が増加する場合、1の密度も増加する。値が減少する場合、1の密度が減少する。エラー電圧を総計することによって、積分器は、入力信号へのローパスフィルタとして、また、量子化ノイズへのハイパスフィルタとして作用する。ビットストリームは、バイナリフォーマット出力を提供するために、フィルタ及び間引きモジュールによって、デジタル的にフィルタリングされる。

10

## 【0134】

[0180]理解可能なように、上に示した実施の形態において説明したT I A増幅器を使用して、シグマデルタD A Cモジュールにおける一以上の差動増幅器モジュール、積分器モジュール、比較器モジュールを実装してもよい。

## 【0135】

[0181]当業者は、上述の説明から、本発明の広い教示が種々の形態で実施され得ることを理解することが可能である。したがって、本発明をその特定の例示に関連して説明したが、他の変形態様が、当業者には、図面、明細書、及び特許請求の範囲を検討すれば、明らかになるので、本発明の範囲は、そのように限定されるべきではない。

## 【図面の簡単な説明】

20

## 【0136】

【図1】従来技術に係る電流-電圧T I A用の基本回路アーキテクチャである。

【図2】従来技術に係る電流-電圧T I A用の基本回路アーキテクチャである。

【図3】従来技術に係る電圧-電圧T I A用の基本回路アーキテクチャである。

【図4】従来技術に係る電圧-電圧T I A用の基本回路アーキテクチャである。

【図5】従来技術に係る差動構成のT I A用の基本回路アーキテクチャである。

【図6】従来技術に係り、T I Aに結合されたフォトダイオードを含む光センサを示す図である。

【図7】本発明に係る1次の入れ子状のT I Aである。

30

【図8】本発明に係る2次の入れ子状のT I Aである。

【図9】本発明に係るn次の入れ子状のT I Aである。

【図10】本発明に係る差動構成での1次の入れ子状のT I Aである。

【図11】本発明に係る差動構成でのn次の入れ子状のT I Aである。

【図12】T I Aの例示の利得帯域幅特性のグラフである。

【図13】1次の入れ子状のT I Aの例示の利得帯域幅特性のグラフである。

【図14】2次の入れ子状のT I Aの例示の利得帯域幅特性のグラフである。

【図15】本発明に係り、入力寄生キャパシタンスを容量的に打ち消す1次の入れ子状のT I Aである。

【図16】本発明に係り、入力寄生キャパシタンスを容量的に打ち消す2次の入れ子状のT I Aである。

40

【図17】本発明に係り、入力寄生キャパシタンスを容量的に打ち消すn次の入れ子状のT I Aである。

【図18】本発明に係り、入力寄生キャパシタンスを容量的に打ち消す差動構成での1次の入れ子状のT I Aである。

【図19】本発明に係り、入力寄生キャパシタンスを容量的に打ち消す差動構成での2次の入れ子状のT I Aである。

【図20】追加のフィードバック抵抗を有する図7の1次の入れ子状のT I Aを示す図である。

【図21】追加のフィードバック抵抗を有する図8の2次の入れ子状のT I Aを示す図である。

50

【図22】追加のフィードバック抵抗を有する図15の1次の入れ子状のTIAを示す図である。

【図23】追加の入力キャパシタンス、フィードバックキャパシタンス、及びフィードバック抵抗を有する図7の1次の入れ子状のTIAを示す図である。

【図24】追加の入力キャパシタンス、フィードバックキャパシタンス、及びフィードバック抵抗を有する図10の1次の差動モードのTIAを示す図である。

【図25】本発明に係る入れ子状のTIAを有するプリアンプを含む例示のディスクドライブシステムを示す図である。

【図26】第1の構成のオペアンプを含む図7の1次の入れ子状のTIAを示す図である。

【図27】第1の構成の差動オペアンプを含む図10の差動の1次の入れ子状のTIAを示す図である。

【図28】第2の構成のオペアンプを含む図26の1次の入れ子状のTIAを示す図である。

【図29】第2の構成の差動オペアンプを含む図27の差動の1次の入れ子状のTIAを示す図である。

【図30】ブッシュプル構成において差動オペアンプを含む図10の差動の1次の入れ子状のTIAを示す図である。

【図31】入れ子状のTIAの第1及び第2のステージの利得カーブの群を示す図である。

【図32】入れ子状のTIAの第1及び第2のステージの利得カーブの群を示す図である。

【図33】入れ子状のTIAの第1及び第2のステージの利得カーブの群を示す図である。

【図34】入れ子状のTIA用の電源の機能ブロック図である。

【図35】図34の電源を使用する例示のLEDドライブ回路を示す図である。

【図36】本開示の一側面に係る差動の単一の入れ子状のトランスインピーダンス増幅器を簡略図である。

【図37】本開示の第2の実施の形態に係る差動の二重の入れ子状のトランスインピーダンス増幅器の簡略図である。

【図38】本開示の第3の実施の形態に係る差動の入れ子状の増幅器の簡略図である。

【図39A】フィードバックループに補償キャパシタを有する差動且つシングルエンドのトランスインピーダンス増幅器の概略図である。

【図39B】フィードバックループに補償キャパシタを有する差動且つシングルエンドのトランスインピーダンス増幅器の概略図である。

【図40A】LCタンク回路を有する差動且つシングルエンドの入れ子状のトランスインピーダンス増幅器の概略図である。

【図40B】LCタンク回路を有する差動且つシングルエンドの入れ子状のトランスインピーダンス増幅器の概略図である。

【図41】本開示に係り、LCタンク回路及び抵抗をフィードバックループに有する差動且つシングルエンドのトランスインピーダンス増幅器の概略図である。

【図41B】本開示に係り、LCタンク回路及び抵抗をフィードバックループに有する差動且つシングルエンドのトランスインピーダンス増幅器の概略図である。

【図42】LCタンク回路を有するトランスインピーダンス増幅器の代替の実施の形態の概略図である。

【図43A】ハードディスクドライブの機能ブロック図である。

【図43B】デジタル多用途ディスク(DVD)の機能ブロック図である。

【図43C】高精細テレビの機能ブロック図である。

【図43D】車両制御システムの機能ブロック図である。

【図43E】携帯電話の機能ブロック図である。

【図43F】セットトップボックスの機能ブロック図である。

【図43G】メディアプレーヤの機能ブロック図である。

【図44】デルタシグマ・アナログ - デジタル変換器(ADC)の機能ブロック図である。

。

【符号の説明】

【0137】

3600...入れ子状のトランスインピーダンス増幅器(TIA)回路、3602...トランスインピーダンス増幅器、3604...第1の演算増幅器、3606...第2の演算増幅器、3608...第1のフィードバック抵抗、3610...第2の抵抗、3612...第3の演算増幅器、3614...フィードバック抵抗、3616...抵抗。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

### 【図17】

【図18】

【図19】

【 図 20 】

### 【図21】

## 【図22】

【図23】

## 【図24】

### 【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図 3 1】

【図 3 2】

【図 3 3】

【図 3 4】

【図35】

【図36】

【図37】

【図38】

【図 3 9 A】

【図 3 9 B】

【図 4 0 A】

【図 4 0 B】

【図4 1】

【図4 1 B】

【図4 2】

【図4 3 A】

【図43B】

【図43C】

【図43D】

【図43E】

【図4 3 F】

【図4 3 G】

【図4 4】

---

フロントページの続き

(31)優先権主張番号 60/817268

(32)優先日 平成18年6月29日(2006.6.29)

(33)優先権主張国 米国(US)

(31)優先権主張番号 11/495813

(32)優先日 平成18年7月28日(2006.7.28)

(33)優先権主張国 米国(US)

(31)優先権主張番号 11/643089

(32)優先日 平成18年12月21日(2006.12.21)

(33)優先権主張国 米国(US)

(31)優先権主張番号 11/643432

(32)優先日 平成18年12月21日(2006.12.21)

(33)優先権主張国 米国(US)

審査官 儀同 孝信

(56)参考文献 特開昭60-149210(JP, A)

特開昭61-274407(JP, A)

特公平06-011091(JP, B2)

特表2003-534679(JP, A)

特開平06-061752(JP, A)

特開平08-148944(JP, A)

特開昭58-047305(JP, A)

特表2003-514426(JP, A)

米国特許第06552605(US, B1)

米国特許第6762644(US, B1)

米国特許第6836182(US, B1)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00 - 3/45、 3/50 - 3/52、

3/62 - 3/64、 3/68 - 3/72