## (10) **DE 102 53 696 B4** 2012.08.02

(12)

## **Patentschrift**

(21) Aktenzeichen: 102 53 696.1(22) Anmeldetag: 18.11.2002(43) Offenlegungstag: 12.06.2003

(45) Veröffentlichungstag

der Patenterteilung: 02.08.2012

(51) Int Cl.: **G11C 7/00** (2006.01)

**G11C 7/22** (2012.01) **G11C 11/4076** (2012.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

| (30) Unionspriorität: 2001-72777 2002-63256                              | 01-72777 21.11.2001 KR |                      | (72) Erfinder:  Jeong, Yong Gwon, Sungnam, Kyoungki, KR; Kwon, Chang Ki, Seoul/Soul, KR |                     |  |

|--------------------------------------------------------------------------|------------------------|----------------------|-----------------------------------------------------------------------------------------|---------------------|--|

| (73) Patentinhaber: <b>Hynix Semiconductor Inc., Icheon, Kyonggi, KR</b> |                        |                      | (56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:       |                     |  |

| (74) Vertreter: isarpatent, 80801, München, DE                           |                        | US<br>US<br>US<br>US | 6 191 632<br>6 266 750<br>6 313 674<br>6 029 250                                        | B1<br>B1<br>B1<br>A |  |

(54) Bezeichnung: Speichersystem mit einer Vielzahl von getakteten Speichervorrichtungen

(57) Hauptanspruch: Speichersystem, welches eine Vielzahl von Speichervorrichtungen aufweist, welches beinhaltet: eine Steuerung zum Ausgeben eines ersten Taktsignals, eines zweiten Taktsignals und einer Vielzahl von Befehls-/Adress-Eingangssignalen, entsprechend der Vielzahl von jeweiligen Speichervorrichtungen, wobei das erste Taktsignal ein Schreibdaten-Takt und das zweite Taktsignal ein Befehls-/Adress-Takt ist; und

eine Register- und Verzögerungsschaltkreiseinheit zum Korrigieren einer Übertragungsverzögerung aufgrund von Übertragungsleitungen und zum Ausgeben von Befehls-/Adress-Ausgangssignalen in Abhängigkeit von den Befehls-/Adress-Eingangssignalen von der Steuerung unter Verwendung des zweiten Taktsignals;

wobei die Vielzahl der Speichervorrichtungen die Befehls-/ Adress-Ausgangssignale von der Register- und Verzögerungsschaltkreiseinheit über die jeweiligen Übertragungsleitungen empfängt und die Befehls-/Adress-Ausgangssignale unter Verwendung des ersten Taktsignals, welches direkt von der Steuerung eingegeben wird, abtastet.

#### **Beschreibung**

**[0001]** Die vorliegende Erfindung bezieht sich auf ein Speichersystem mit einer Vielzahl von getakteten Speichervorrichtungen, wobei eine Übertragungsverzögerung aufgrund von Übertragungsleitungen korrigierbar ist.

**[0002]** Die US 6,266,750 B1 offenbart ein Verfahren einer Vorrichtung zum Implementieren einer Pipeline mit variabler Länge in einem paketgesteuerten Speichersteuersystem.

**[0003]** Insbesondere offenbart diese Druckschrift eine Eingangsstufe, welche externe Befehls-/Adress-Signale zusammen mit Befehlstaktsignalen empfängt und in D-Typ-Flip-Flops zu den steigenden und fallenden Flanken des Befehltakts speichert. Die Flip-Flops legen die gespeicherten Befehls-/Adress-Signale an eine Befehlsverarbeitungspipeline.

Beschreibung des Standes der Technik

**[0004]** Eine Taktsteuervorrichtung herkömmlicher Speichervorrichtungen weist auf: einen Registerchip zum Puffern von Befehls-/Adress-Eingangssignalen und einen Phasenregelkreischip "PLL" zum Erzeugen von Zeitsignalen, im Falle eines Dual-in-Line Speichermoduls "DIMM". Wenn eine Vielzahl von DLL-Ausgangstakten erzeugt wird, wird ein Kompensationskondensator (nachfolgend als "C<sub>comp</sub>" bezeichnet) genutzt, um deren Flankenzeitverhalten zu steuern.

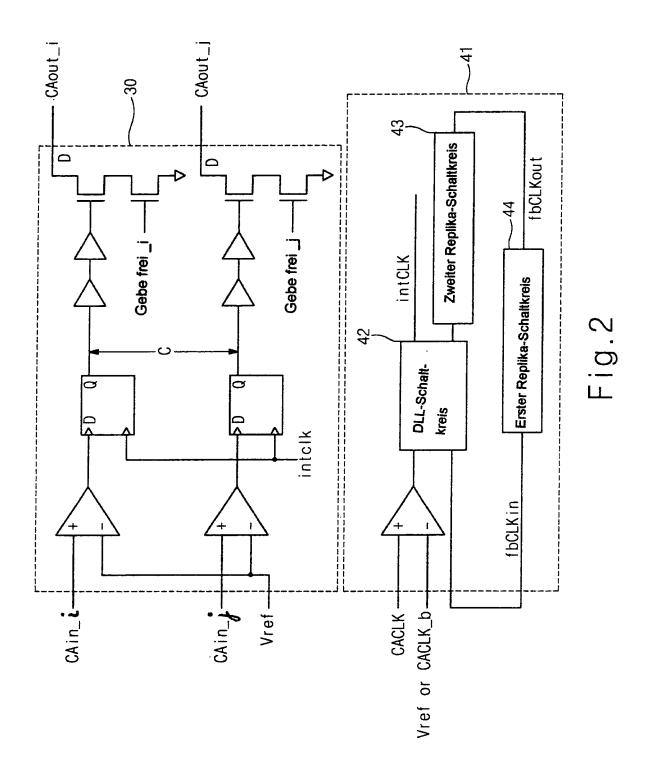

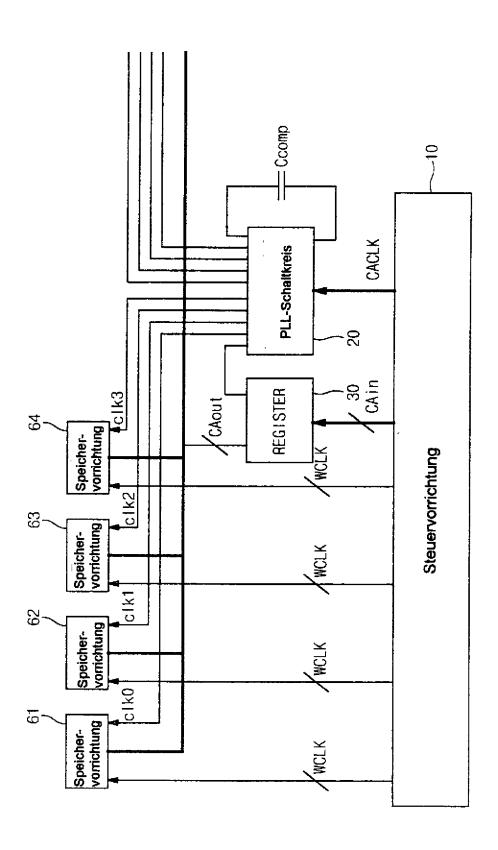

[0005] Fig. 3 zeigt ein Schaubild, welches ein Beispiel eines herkömmlichen Speichersystems darstellt, wobei verteilte Befehls-/Adress-Signale genutzt werden. Ein PLL-Schaltkreis 20 führt flankengesteuerte Befehls-/Adress-Takte "CACLK" aus, welche von einem Steuergerät 10 eingegeben werden, indem der C<sub>comp</sub> unter Berücksichtigung des Signalverzugs, welcher durch die Übertragungsleitung erzeugt wird, benutzt wird und stellt die flankengesteuerten CA-CLKs ein, so dass sie die gleiche Phase mit den CA-CLKs besitzen, welche in das Steuergerat 10 eingegeben werden und wendet dann die angepassten bzw. eingestellten CACLKs, CLK0, CLK1, CLK2 und CLK3 jeweils auf eine Vielzahl von Speichervorrichtungen 61, 62, 63 und 64 an. Hier wird eine Vielzahl von Befehls-/Adress-Eingangssignalen "CAin", welche von dem Steuergerät 10 ausgegeben werden, in eine Vielzahl von Speichervorrichtungen 61, 62, 63 und 64 jeweils ausgegeben, über Übertragungsleitungen zum Aufteilen von CACLKs und getrennten Übertragungsleitungen, nachdem sie in einem Register 30 gespeichert wurden.

**[0006]** Jedoch hat das herkömmliche Speichersystem die folgenden Probleme. Erstens, das Layout des Designs der Halbleitervorrichtung wird kompli-

ziert, da das herkömmliche Speichersystem CA-CLK-Übertragungsleitungen aufweisen sollte, welche der Anzahl einer Vielzahl von Speichervorrichtungen zum Übertragen von Befehls-/Adress-Signalen entsprechen und getrennten Befehls-/Adress-Takte in den jeweiligen Speichervorrichtungen. Zweitens kann Taktdomänenkollision zwischen den Befehls-/ Adress-Takten und den Schreibdatenempfangs-Takten erzeugt werden, da die Speichervorrichtungen Befehls-/Adress-Takte und getrennte Schreibdatenempfangs-Takte "WCLK" empfangen. Drittens sollte iede Speichervorrichtung einen individuellen PLLoder DLL-Schaltkreis aufweisen, wodurch der Jitter als auch die Kosten des Gesamtsystems ansteigen. Viertens, da ein Register und ein DLL-Schaltkreis beinhaltet sein sollten, wobei getrennte Chips benutzt werden, macht die Herstellung von zwei Chip-Anordnungen das Verfahren der Halbleitervorrichtungen kompliziert, wodurch die Kosten ansteigen. Schließlich werden aufgrund der Unterschiede einer Vielzahl von Kompensationskondensatoren die zeitlichen Eingrenzungen herabgesetzt.

#### Zusammenfassung der Erfindung

[0007] Um die oben beschriebenen Probleme zu überwinden ist es Aufgabe der vorliegenden Erfindung, ein Speichersystem zu liefern, welches das Layout für das Design einer Halbleitervorrichtung vereinfacht, durch Entfernen von Übertragungsleitungen zum Verteilen von Befehls-/Adress-Takten CACLK, es verhindert Takt-Domänenkollision durch Abtasten von Befehls-/Adress-Signalen entsprechend der Datenempfangs-Takte WCLKs oder Taktsignale, geteilt in ganzzahlige Vielfache, es reduziert die Kosten, ohne einen individuellen PLL- oder DLL-Schaltkreis zu erfordern, es verbessert die Jitter-Leistungsfähigkeit und verhindert ein Verschlechtern der Zeitgrenzwerte des Systems aufgrund von Unterschieden des Kompensationskondensators.

**[0008]** Eine bevorzugte Ausführungsform der vorliegenden Erfindung, welche in Anspruch 1 definiert ist, hat die Aufgabe ein Speichersystem zum Reduzieren der Kosten aufgrund von Vereinheitlichung des Registerchips, der PLL- oder DLL-Chips zu liefern.

**[0009]** Vorteilhafte Ausgestaltungen der Erfindung sind Gegenstand der Unteransprüche.

Kurze Beschreibung der Zeichnungen

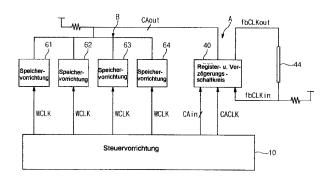

**[0010]** Fig. 1 ist ein Blockschaltbild eines Speichersystems in Übereinstimmung mit einer bevorzugten Ausführungsform der vorliegenden Erfindung.

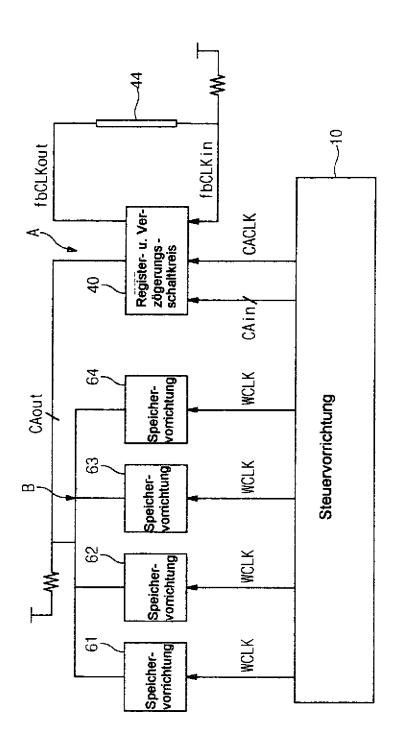

**[0011]** Fig. 2 ist ein detailliertes Schaubild, eines Register- und Verzögerungsschaltkreises in Übereinstimmung mit einer bevorzugten Ausführungsform der vorliegenden Erfindung.

**[0012]** Fig. 3 ist ein Blockschaltbild eines herkömmlichen Speichersystems, welches einen verteilten Befehls-/Adress-Takt nutzt.

Detaillierte Beschreibung der bevorzugten Ausführungsformen

[0013] Das beschriebene Speichersystem, welches eine Vielzahl von Speichervorrichtungen aufweist, beinhaltet: ein Steuergerät zum Ausgeben eines ersten Taktsignals, eines zweiten Taktsignals und einer Vielzahl von Befehls-/Adress-Eingangssignalen entsprechend der Vielzahl von jeweiligen Speichervorrichtungen; und eine Register- und Verzögerungsschaltkreiseinheit zum Ausgeben von Befehls-/ Adress-Ausgangssignalen nach dem Empfangen der Befehls-/Adress-Eingangssignale aus dem Steuergerät und dann Korrigieren der Übertragungsverzögerung aufgrund der Übertragungsleitungen; wobei die Vielzahl von Speichervorrichtungen das Befehls-/ Adress-Ausgangssignal von der Register- und Verzögerungsschaltkreiseinheit jeweils über die Übertragungsleitungen empfängt und wobei die Befehls-/ Adress-Ausgangssignale gesendet werden, indem das erste Taktsignal, welches direkt von dem Steuergerät eingegeben wird, genutzt wird.

**[0014]** Das beschriebene Speichersystem, welches eine Vielzahl von Speichervorrichtungen aufweist, wird detaillierter mit Bezug auf die nachfolgenden Beispiele beschrieben, welche nicht einschränkend wirken sollen.

[0015] Fig. 1 ist ein Blockschaltbild eines Speichersystems in Ubereinstimmung mit einer bevorzugten Ausfuhrungsform der vorliegenden Erfindung. Wie in Fig. 1 gezeigt wird, legt ein Steuergerät 10 zum Steuern der gesamten Operation des Speichersystems Befehls-/Adress-Eingangssginale CAin an eine Register- und Verzogerungsschaltkreiseinheit 40. Die Register- und Verzögerungsschaltkreiseinheit 40, welche die Befehls-/Adress-Eingangssignale CAin empfangt, gibt Befehls-/Adress-Ausgangsssignale CAout aus, nach dem Korrigieren der Übertragungsverzögerung aufgrund der Ubertragungsleitungen, welche mit den Speichervorrichtungen 61, 62, 63 und 64 verbunden sind und der Übertragungsverzögerung, welche von dem internen Ausgangspuffer erzeugt wird. Es ist vorzuziehen, dass die Ubertragungsverzogerung diejenige Übertragungsverzögerung bedeutet, welche von einem Punkt (A), welcher aus dem Register- und Verzögerungsschaltkreis **40** hervorgegangen ist zu einem vorher bestimmten Punkt (B) in jeder aus der Vielzahl der Übertragungsleitungen reicht. Die interne Übertragungsverzögerung kann auch eine Übertragungsverzögerung beinhalten, welche von der internen Register- und Verzögerungsschaltkreiseinheit der Befehls-/Adress-Signale CAin erzeugt wird. Die Vielzahl der Speichervorrichtungen 61, 62, 63 und 64 empfängt Befehls-/

Adress-Ausgangssignale CAout, welche von der Register- und Verzögerungsschaltkreiseinheit 40 über die Übertragungsleitungen ausgegeben wird und tastet dann die empfangenen CAouts ab, wobei der Schreibdaten-Takt (nachfolgend ein erstes Taktsignal: WCLK) genutzt wird, der direkt von dem Steuergerät 10 eingegeben wird. Da entsprechend keine getrennten Befehls-/Adress-Taktsignale genutzt werden, benötigt das Speichersystem der vorliegenden Erfindung keine separaten Übertragungsleitungen für Befehls-/Adress-Taktsignale wie das herkömmliche Speichersystem, Zusätzlich wird keine Kollision zwischen den Taktdomänen erzeugt, da nicht eine Anzahl von Takten in die Speichervorrichtungen eingegeben werden, sondern Befehls-/Adress-Signale CAout abgetastet werden, indem nur WCLK genutzt wird.

**[0016]** Fig. 2 ist ein Detail-Schaubild eines Registerund Verzogerungsschaltkreises entsprechend einer bevorzugten Ausführungsform der vorliegenden Erfindung.

[0017] Eine Registereinheit 30 gibt Befehls-/Adress-Ausgangssignale CAout\_i ~ CAout\_j durch Abtasten der Befehls-/Adress-Eingangssignale CAin\_i ~ CAin\_ j aus, wobei ein interner Takt (nachfolgend als ein drittes Taktsignal: intCLK bezeichnet) benutzt wird. Hier erzeugt ein Taktsteuerschaltkreis 41 ein drittes Taktsignal, nachdem die Übertragungsverzögerung aufgrund von Befehls-/Adress-Takt von Übertragungsleitungen (nachfolgend als zweites Taktsignal: CACLK bezeichnet), welches von dem Steuergerät 10 eingegeben wird und die Übertragungsverzögerung, welche von dem internen Ausgangspuffer erzeugt wird, korrigiert wird. Es ist vorzuziehen, dass die Übertragungsverzögerung diejenige Übertragungsverzögerung bedeutet, welche von einem Punkt (A), welcher seinen Ursprung im Register- und Verzögerungsschaltkreis 40 hat, bis zu einem vorher bestimmten Punkt (B) reicht. Die interne Ausgangspufferubertragungsverzögerung kann auch eine Übertragungsverzogerung beinhalten, welche von einem Ausgangspuffer im Punkt (C) in der Register- und Verzögerungsschaltkreiseinheit 40 des Befehls-/Adress-Signals bis zu einem Ausgangspunkt (D) reicht.

[0018] Wie vorzugsweise in Fig. 2 gezeigt wird, weist der Taktsteuerschaltkreis 41 einen DLL-Schaltkreis 42, einen ersten Replika-Schaltkreis 44 zum Modellieren der Übertragungsverzögerung aufgrund der Übertragungsleitungen und einen zweiten Replika-Schaltkreis 43 zum Modellieren der Übertragungsverzögerung des internen Ausgangspuffers auf. Der DLL-Schaltkreis 42 empfängt einen zweiten Takt CA-CLK von dem Steuergerät 10 und empfängt ein Ruckkopplungssignal (fbCLK\_in) über den ersten und den zweiten Replika-Schaltkreis 44 und 43 zurück, wodurch die Verzogerung korrigiert wird. Demzufolge

erzeugt der DLL-Schaltkreis 42 einen dritten Takt intCLK, um die gleiche Phase mit einem Rückkopplungsausgangs-Signal zu besitzen. Der erste Replika-Schaltkreis 44 zum Modellieren der Übertragungsverzogerung in der Register- und Verzögerungsschaltkreiseinheit 40 und den Speichervorrichtungen 61, 62, 63 und 64 kann durch Kombinationen von herkömmlichen passiven/aktiven Vorrichtungen gebildet werden, um die Übertragungsverzögerung einzustellen, welche im allgemeinen mit der Außenseite der Chips verbunden sind. Vorzugsweise kann der erste Replika-Schaltkreis 44 auch durch eine Befehls-/Adress-Übertragungsleitung gebildet werden und der Abschlussschaltkreis ist so aufgebaut, dass er die Unterschiede im Verfahren/ in der Spannungsversorgung/in der Temperatur des PCB-Boards kompensiert. Zusätzlich kann der zweite Replika-Schaltkreis zum Modellieren bzw. Aufbauen der Übertragung interner Ausgangspuffer vorzugsweise durch Ausgangspufferschaltkreis-Modelle in Chips gebildet werden, um die Unterschiede im Verfahren/in der Spannungsversorgung/in der Temperatur der Ausgangspuffer zu kompensieren.

[0019] Wie vorher diskutiert, kann das beschriebene Speichersystem entsprechend der vorliegenden Erfindung das Layout des Designs der Halbleitervorrichtung vereinfachen, da Befehls-/Adress-Taktsignale direkt an die Speichervorrichtungen geliefert werden und es keine Übertragungsleitungen zum Verteilen der Befehls-/Adress-Taktsignale gibt. Das Speichersystem kann auch die Kollision von Taktdomänen verhindern, indem Befehls-/Adress-Signale in Speichervorrichtungen abgetastet werden, wobei Schreibdatenempfangs-Takte genutzt werden. Außerdem kann das Speichersystem die Kosten reduzieren und das Jitterverhalten verbessern, da es nicht getrennte PLL- oder DLL-Schaltkreise benötigt und die Degradierung der Zeiteingrenzungen des Systems aufgrund von Unterschieden in einer Zahl von Kommunikationskondensatoren verhindern kann. Zusätzlich kann die vorliegende Erfindung eine bevorzugte Ausführungsform liefern, welche die Kosten aufgrund der Vereinheitlichung des Registerchips und des PLL-Chips reduziert.

### Patentansprüche

1. Speichersystem, welches eine Vielzahl von Speichervorrichtungen aufweist, welches beinhaltet: eine Steuerung zum Ausgeben eines ersten Taktsignals, eines zweiten Taktsignals und einer Vielzahl von Befehls-/Adress-Eingangssignalen, entsprechend der Vielzahl von jeweiligen Speichervorrichtungen, wobei das erste Taktsignal ein Schreibdaten-Takt und das zweite Taktsignal ein Befehls-/Adress-Takt ist; und

eine Register- und Verzögerungsschaltkreiseinheit zum Korrigieren einer Übertragungsverzögerung aufgrund von Übertragungsleitungen und zum Ausgeben von Befehls-/Adress-Ausgangssignalen in Abhängigkeit von den Befehls-/Adress-Eingangssignalen von der Steuerung unter Verwendung des zweiten Taktsignals;

wobei die Vielzahl der Speichervorrichtungen die Befehls-/Adress-Ausgangssignale von der Registerund Verzögerungsschaltkreiseinheit über die jeweiligen Übertragungsleitungen empfängt und die Befehls-/Adress-Ausgangssignale unter Verwendung des ersten Taktsignals, welches direkt von der Steuerung eingegeben wird, abtastet.

2. Speichersystem nach Anspruch 1, wobei die Register- und Verzögerungsschaltkreiseinheit beinhaltet:

einen Taktsteuerschaltkreis zum Ausgeben eines dritten Taktsignals, nach dem Empfangen des zweiten Taktsignals von der Steuerung und Korrigieren der Übertragungsverzögerung aufgrund der Übertragungsleitungen; und

eine Registereinheit zum Ausgeben des Befehls-/ Adress-Ausgangssignals nach dem Puffern der Befehls-/Adress-Eingangssignale der Steuerung und Abtasten der Befehls-/Adress-Eingangssignale, indem das dritte Taktsignal genutzt wird.

- 3. Speichersystem nach Anspruch 2, wobei der Taktsteuerschaltkreis und die Registereinheit in einem einzelnen Chip vereint sind.

- 4. Speichersystem nach Anspruch 2 oder 3, wobei der Taktsteuerschaltkreis aufweist:

einen DLL-Schaltkreis; und

einen ersten Replika-Schaltkreis zum Modellieren bzw. Aufbauen der Übertragungsverzögerung aufgrund der Übertragungsleitungen;

wobei der DLL-Schaltkreis das dritte Taktsignal einstellt, so dass es die gleiche Phase wie das zweite Taktsignal besitzt, und das dritte Taktsignal ausgibt, dessen Übertragungsverzögerung aufgrund der Übertragungsleitung korrigiert ist.

- 5. Speichersystem nach Anspruch 4, wobei der erste Replika-Schaltkreis aus der Gruppe gebildet wird, welche aus dem PCB-Leitungsmodell, einer aktiven Vorrichtung, einer passiven Vorrichtung und deren Kombinationen besteht.

- 6. Speichersystem nach Anspruch 2, wobei der Taktsteuerschaltkreis das dritte Taktsignal ausgibt, nach dem Empfangen des zweiten Taktsignals von der Steuerung und Korrigieren der Übertragungsverzögerung aufgrund der Übertragungsleitungen und der Übertragungsverzögerung von der Registereinheit.

- 7. Speichersystem nach Anspruch 6, wobei der Taktsteuerschaltkreis und die Registereinheit in einem einzelnen Chip vereint sind.

- 8. Speichersystem nach Ansprüchen 6 oder 7, wobei der Taktsteuerschaltkreis aufweist: einen DLL-Schaltkreis;

- einen ersten Replika-Schaltkreis zum Modellieren der Übertragungsverzögerung aufgrund der Übertra-

gungsleitungen; und einen zweiten Replika-Schaltkreis zum Modellieren der Übertragungsverzögerung der Registereinheit; wobei der DLL-Schaltkreis das dritte Taktsignal einstellt, so dass es die gleiche Phase wie das zweite Taktsignal besitzt und das dritte Taktsignal ausgibt, dessen Übertragungsverzögerung aufgrund der Übertragungsleitung korrigiert ist, wobei die Übertra-

9. Speichersystem nach Anspruch 8, wobei die ersten und zweiten Replika-Schaltkreise aus der Gruppe gebildet werden, welche aus einem PCB-Leitungsmodell, einer passiven Vorrichtung, einer aktiven Vorrichtung und deren Kombinationen besteht.

gungsverzögerung der Registereinheit beinhaltet ist.

- 10. Speichersystem nach Anspruch 1, wobei die Übertragungsleitungen von der Register- und Verzögerungsschaltkreiseinheit zu einem Verzweigungspunkt globale bzw. übergeordnete Leitungen aufweisen, welche sich vom Verzweigungspunkt verzweigen und mit einer Vielzahl von Speichervorrichtungen jeweils verbunden sind.

- 11. Speichersystem nach Anspruch 10, wobei ein Verfahren zum Verbinden der Übertragungsleitungen von der Register- und Verzögerungsschaltkreiseinheit mit der Vielzahl von Speichervorrichtungen aus der Gruppe gebildet wird, welche aus Prioritätsverkettung, Hybrid-T-Typ und Gabelung besteht.

- 12. Speichersystem nach Anspruch 10, wobei die Register- und Verzögerungsschaltkreiseinheit aufweist:

einen Taktsteuerschaltkreis zum Ausgeben eines dritten Taktsignals nach dem Empfangen eines zweiten Taktsignals aus der Steuerung und Korrigieren der Übertragungsverzögerung aufgrund der globalen Übertragungsleitungen; und

eine Registereinheit zum Ausgeben der Befehls-/ Adress-Ausgangssignale nach dem Puffern der Befehls-/Adress-Eingangssignale und Abtasten des dritten Taktsignals.

- 13. Speichersystem nach Anspruch 12, wobei der Taktsteuerschaltkreis und die Registereinheit in einem einzelnen Chip vereint sind.

- 14. Speichersystem nach Anspruch 12 oder 13, wobei der Taktsteuerschaltkreis aufweist: einen DLL-Schaltkreis; und einen ersten Replika-Schaltkreis zum Modellieren der Übertragungsverzögerung aufgrund der globalen Übertragungsleitungen;

wobei der DLL-Schaltkreis das dritte Taktsignal einstellt, so dass es die gleiche Phase wie das zweite Taktsignal hat, und das dritte Taktsignal ausgibt, dessen Übertragungsverzögerung aufgrund der globalen Übertragungsleitung korrigiert ist.

- 15. Speichersystem nach Anspruch 14, wobei der erste Replika-Schaltkreis aus der Gruppe gebildet wird, welche aus dem PCB-Leitungsmodell, einer aktiven Vorrichtung, einer passiven Vorrichtung und deren Kombinationen besteht.

- 16. Speichersystem nach Anspruch 12, wobei der Taktsteuerschaltkreis ein drittes Taktsignal ausgibt, nach dem Empfangen eines zweiten Taktsignals aus der Steuerung und Korrigieren der Übertragungsverzögerung aufgrund der globalen Übertragungsleitungen und der Übertragungsverzögerung in der Registereinheit.

- 17. Speichersystem nach Anspruch 16, wobei der Taktsteuerschaltkreis und die Registereinheit in einem einzelnen Chip vereint sind.

- 18. Speichersystem nach Anspruch 16 oder 17, wobei der Taktsteuerschaltkreis aufweist: einen DLL-Schaltkreis;

einen ersten Replika-Schaltkreis zum Modellieren der Übertragungsverzögerung aufgrund der globalen Übertragungsleitung; und

einen zweiten Replika-Schaltkreis zum Modellieren der Übertragungsverzögerung in der Registereinheit; wobei der DLL-Schaltkreis das dritte Taktsignal einstellt, so dass es die gleiche Phase wie das zweite Taktsignal besitzt, und das dritte Taktsignal ausgibt, dessen Übertragungsverzögerung aufgrund der globalen Übertragungsleitung korrigiert ist, wobei die Übertragungsverzögerung der Registereinheit beinhaltet ist.

19. Speichersystem nach Anspruch 18, wobei die ersten und zweiten Replika-Schaltkreise aus der Gruppe gebildet werden, welche aus dem PCB-Leitungsmodell, einer aktiven Vorrichtung, einer passiven Vorrichtung und deren Kombinationen besteht.

Es folgen 3 Blatt Zeichnungen

# Anhängende Zeichnungen

Fig.

Fig. 3 (Stand der Technik)