## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2003/0047765 A1 **Campbell**

Mar. 13, 2003 (43) Pub. Date:

#### (54) STOICHIOMETRY FOR CHALCOGENIDE GLASSES USEFUL FOR MEMORY DEVICES AND METHOD OF FORMATION

(76) Inventor: Kristy A. Campbell, Boise, ID (US)

Correspondence Address: DICKSTEIN SHAPIRO MORIN & OSHINSKY LLP 2101 L STREET NW **WASHINGTON, DC 20037-1526 (US)**

(21) Appl. No.: 09/941,544

(22) Filed: Aug. 30, 2001

#### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> | H01L | 29/76; | H01L   | 27/108; |

|------|-----------------------|------|--------|--------|---------|

|      |                       | H01L | 29/94  | ; H01L | 31/119  |

#### (57)**ABSTRACT**

A method of forming resistance changing elements with improved operational characteristics for use in memory devices and the resulting structures are disclosed. A chalcogenide glass having the formula  $(Ge_{x1}Se_{1-x1})_{1-y1}Ag_{y1}$ , wherein  $18 \le x_1 \le 28$ , or the formula  $(Ge_{x2}SE_{1-x2})_{1-y2}Ag_{y2}$ , wherein  $39 \le x_2 \le 42$ , and wherein in both the silver is in a concentration which maintains the germanium selenide glass in the glass forming region is used in a memory cell. The glass may also have a glass transition temperature (Tg) near or higher than typical temperatures used for fabricating and packaging memory devices containing the memory cell.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

### STOICHIOMETRY FOR CHALCOGENIDE GLASSES USEFUL FOR MEMORY DEVICES AND METHOD OF FORMATION

#### FIELD OF THE INVENTION

[0001] The present invention relates to the field of semiconductor devices formed using chalcogenide glasses.

#### BACKGROUND OF THE INVENTION

[0002] One type of integrated circuitry currently used in the semiconductor industry comprises memory circuitry where information is stored in the form of binary data. The circuitry can be either volatile or non-volatile. Volatile storing memory devices result in loss of data when power is interrupted. In contrast, non-volatile memory circuitry retains the stored data even when power is interrupted.

[0003] The operation of memory circuitry, and particularly that of programmable metallization cells, has been disclosed in the Kozicki et al. U.S. Pat. Nos. 5,761,115; 5,896,312; 5,914,893; and 6,084,796, the disclosures of which are incorporated by reference herein. Such a cell includes an insulating dielectric material disposed between opposing electrodes. A conductive material is doped into the dielectric material. The resistance of such material can be changed between highly insulative and highly conductive states. In its normal high resistive state and to perform a write operation, a voltage potential is applied across the opposing electrodes. The electrode having the positive voltage applied thereto functions as an anode, while the electrode held at a lower potential functions as a cathode. The conductivelydoped dielectric material has the capability of undergoing a structural change at a certain applied voltage. With such voltage applied, a conductive dendrite or filament extends between the electrodes, effectively interconnecting the top and bottom electrodes.

[0004] The dendrite remains when the voltage potentials are removed. This way, the resistance of the conductively-doped dielectric material between electrodes could drop by several orders of magnitude. Such material can be returned to its highly resistive state by reversing the voltage potential between the anode and cathode, effectively disrupting the dendrite connection between the top and bottom electrodes. Again, the highly resistive state is maintained once the voltage potential is removed. This way, such a device can function, for example, as a programmable memory cell.

[0005] The preferred resistance-variable material received between the electrodes typically comprises a chalcogenide material having metal ions diffused therein. A specific example is germanium selenide ( $Ge_xSe_{1-x}$ ) diffused with silver (Ag) ions. One method of diffusing the silver ions into the germanium selenide material is to initially evaporate the germanium selenide glass and then deposit a thin layer of silver upon the glass, for example by sputtering, physical vapor deposition, or other known technique in the art. The layer of silver is irradiated, preferably with electromagnetic energy at a wavelength less than 600 nanometers, so that the energy passes through the silver and to the silver/glass interface, to break a chalcogenide bond of the chalcogenide material. As a result, the glass is doped with silver. If, however, too much silver is doped into the chalcogenide material, the chalcogenide material changes from an amorphous state to a crystalline one and, consequently, the operation of the programmable memory cell is adversely affected.

[0006] When a chalcogenide glass is used in a memory device to insure that its properties do not change during various processing steps associated with fabrication of the memory device, the chalcogenide glass must have a glass transition temperature (Tg) which is about or higher than the fabrication and processing temperatures used in the subsequent steps of memory device fabrication. If the processing and/or packaging temperatures are higher than the glass transition temperature, the amorphous state of the chalcogenide material may change to a crystalline state or the glass stoichiometry may change or the mean coordination number of the glass may change and the operation of the memory cell affected. As such, the glass stoichiometry of the chalcogenide glass must be chosen so that the glass backbone (before and after metal doping) and/or metal-doped glass has a glass transition temperature which is about or higher than the processing temperatures subsequent to the glass deposition or subsequent to metal doping of the glass.

[0007] Accordingly, there is a need for a chalcogenide glass material that will remain in a glass forming region when doped with a metal such as silver and which allows maximization of subsequent possible processing temperatures, as well as a method of forming such a non-volatile memory element.

#### BRIEF SUMMARY OF THE INVENTION

[0008] The present invention provides a method of forming non-volatile or semi-volatile memory elements using a metal doped chalcogenide glass which has a stoichometry which keeps the glass in the glass forming region. The glass also has a glass transition temperature (Tg) which is about or higher than typical processing and/or packaging temperatures used for memory device formation.

[0009] According to an exemplary embodiment of the present invention, germanium selenide glasses for use as memory elements are selected from a range of germanium selenide glasses having stoichiometries that fall within a first stoichiometric range  $R_1$  including  $Ge_{18}Se_{82}$  (with a maximum atomic percentage of Ag when doped of about 30% or less) continuously to  $Ge_{28}Se_{72}$  (with a maximum atomic percentage of Ag when doped of about 20% or less) and which have the general formula  $(Ge_{x1}Se_{1-x1})_{1-y1}Ag_{y1}$ , wherein  $18 {\leq} x_1 {\leq} 28$  and wherein  $y_1$  represents the fit silver (Ag) atomic percentage which is the maximum amount which will keep the glass in the glass forming region. Typically,  $y_1$  is less than or equal to that which approximately satisfies equation (1):

$$y_1 = 19 + 15 \cdot \sin[0.217 \cdot x_1 + 3.23]$$

(1)

[0010] According to another embodiment of the present invention, germanium selenide glasses for memory elements are selected from a range of germanium-selenide glasses having stoichiometries that fall within a second stoichiometric range  $R_2$  of doped chalcogenide glasses including  $Ge_{39}Se_{61}$  (with a maximum atomic percentage of Ag when doped of about 20% or less) continuously to  $Ge_{42}Se_{58}$  (with a maximum atomic percentage of Ag when doped of about 15% or less) and which have the general formula  $(Ge_{x2}Se_{1-x2})_{1-y2}Ag_{y2}$ , wherein  $39 \le x_2 \le 42$  and wherein  $y_2$  represents the fit silver (Ag) atomic percentage which is the

maximum amount which will keep the glass in the glass forming region. Typically,  $y_1$  is less than or equal to that which approximately satisfies equation (2):

$y_2=21-11.5*exp[-(ln(x_2/44.4)/(0.84)^2)]tm (2)$

[0011] If the Ag-doped germanium selenide material has a stoichiometry that falls within the first or second stoichiometric range R1, R2, the doped germanium selenide glass will remain amorphous enabling its use in a memory device. If, however, the Ag-doped germanium selenide material has a stoichiometry that does not fall within the first or second stoichiometric range  $R_1$ ,  $R_2$ , the doped germanium selenide glass becomes crystalline precluding its use in a non-phase change-type memory device.

[0012] According to another embodiment of the present invention, and to produce an optimum non-volatile memory cell, the doped germanium selenide glass is selected to fall within the first or second stoichiometric range  $R_1$ ,  $R_2$  and to have a glass transition temperature (Tg) which is about or higher than the highest processing and/or packaging temperatures used for memory device formation.

#### BRIEF DESCRIPTION OF THE DRAWINGS

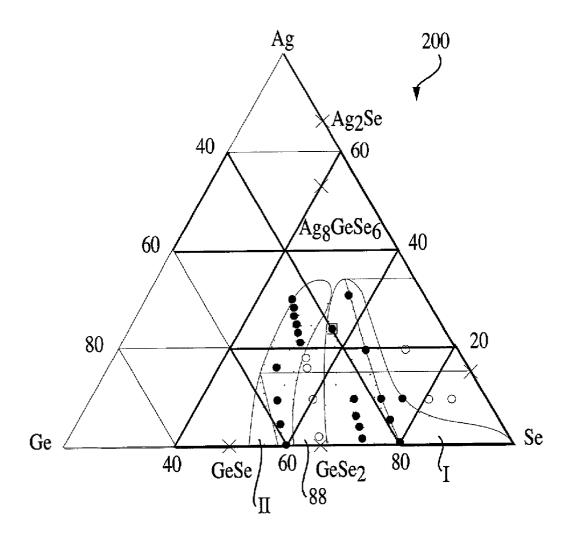

[0013] FIG. 1 illustrates a ternary phase diagram showing glass forming regions for  $(GE_xSe_{1-x})_{1-y}Ag_y$  compounds.

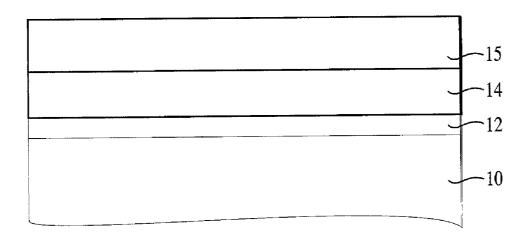

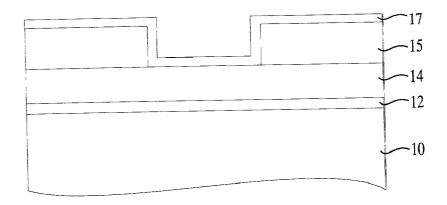

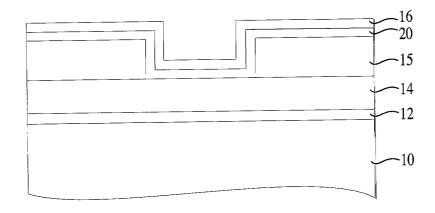

[0014] FIG. 2 illustrates a cross-sectional view of the early stages of fabrication of a a memory device in accordance with an embodiment of the present invention.

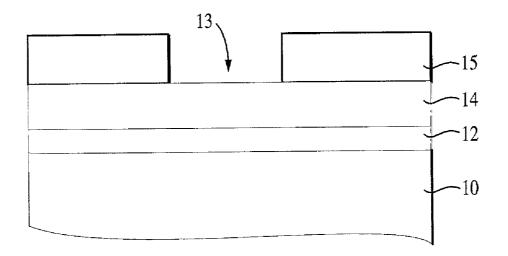

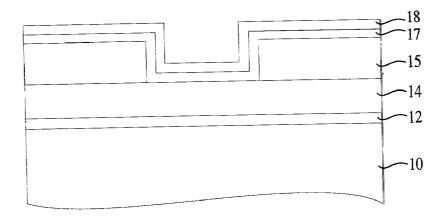

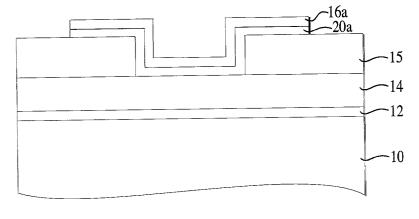

[0015] FIG. 3 illustrates a cross-sectional view of the memory device of FIG. 2 at a stage of processing subsequent to that shown in FIG. 2.

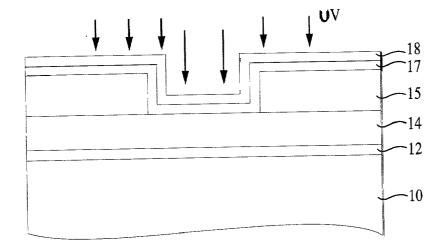

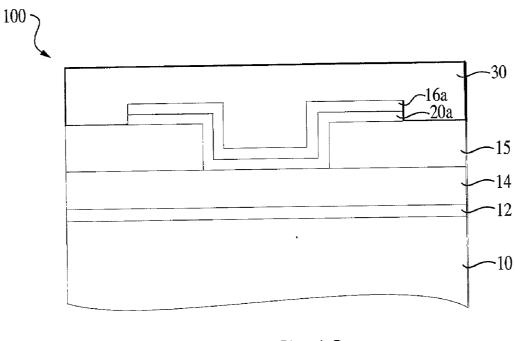

[0016] FIG. 4 illustrates a cross-sectional view of the memory device of FIG. 2 at a stage of processing subsequent to that shown in FIG. 3.

[0017] FIG. 5 illustrates a cross-sectional view of the memory device of FIG. 2 at a stage of processing subsequent to that shown in FIG. 4.

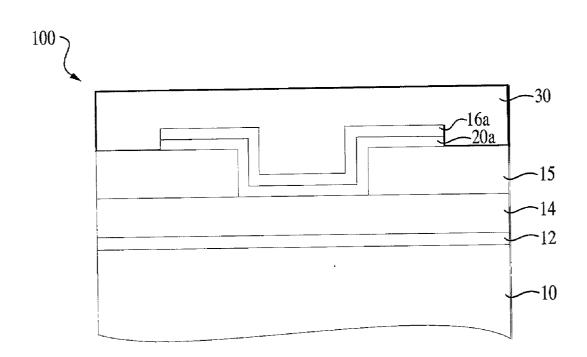

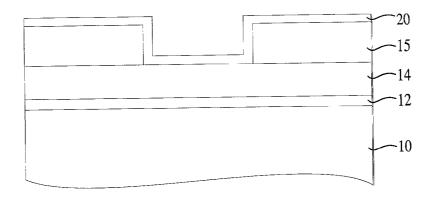

[0018] FIG. 6 illustrates a cross-sectional view of the memory device of FIG. 2 at a stage of processing subsequent to that shown in FIG. 5.

[0019] FIG. 7 illustrates a cross-sectional view of the memory device of FIG. 2 at a stage of processing subsequent to that shown in FIG. 6.

[0020] FIG. 8 illustrates a cross-sectional view of the memory device of FIG. 2 at a stage of processing subsequent to that shown in FIG. 7.

[0021] FIG. 9 illustrates a cross-sectional view of the memory device of FIG. 2 at a stage of processing subsequent to that shown in FIG. 8.

[0022] FIG. 10 illustrates a cross-sectional view of the memory device of FIG. 2 at a stage of processing subsequent to that shown in FIG. 9.

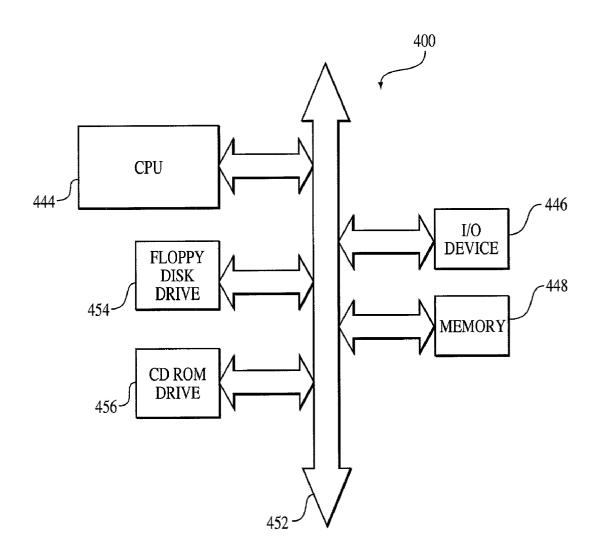

[0023] FIG. 11 illustrates a computer system having a memory cell formed according to the present invention.

# DETAILED DESCRIPTION OF THE INVENTION

[0024] In the following detailed description, reference is made to various specific embodiments in which the inven-

tion may be practiced. These embodiments are described with sufficient detail to enable those skilled in the art to practice the invention, and it is to be understood that other embodiments may be employed, and that various structural, logical and electrical changes may be made without departing from the spirit or scope of the invention.

[0025] The term "silver" is intended to include not only elemental silver, but silver with other trace metals or in various alloyed combinations with other metals as known in the semiconductor industry, as long as such silver alloy is conductive, and as long as the physical and electrical properties of the silver remain unchanged. Similarly, the terms "germanium" and "selenium" are intended to include not only elemental germanium and selenium, but germanium and selenium with other trace metals or in various alloyed combinations with other metals as known in the semiconductor industry, as long as the physical and electrical properties of the germanium or selenium remain unchanged.

[0026] The term "non-volatile memory device" is intended to include not only non-volatile memory device but also semi-volatile memory devices and any memory device which is capable of maintaining its memory state after power is removed from the device.

[0027] The present invention relates to a method of forming non-volatile memory elements under varying glass stoichiometries. The formation of a non-volatile memory device 100 (FIG. 10) including a memory element which comprises a doped chalcogenide glass having a selected stoichiometry will be explained below with reference to FIGS. 2-10. For a better understanding of the invention, however, the selection of a chalcogenide glass having a stoichiometry selected in accordance with the present invention and which is employed in the non-volatile memory device 100 (FIG. 10) is first explained below with reference to FIG. 1.

[0028] Referring to the drawings, where like elements are designated by like reference numerals, FIG. 1 illustrates a ternary phase diagram 200 showing glass forming regions for  $(Ge_xSe_{1-x})_{1-y}Ag_y$  compounds, as studied by Mitkova et al. in Dual Chemical Role of Ag as an Additive in Chalcogenide Glasses, Phys. Rev. Letters, Vol. 83, No 19 (Nov. 1999), the disclosure of which is incorporated by reference herein. According to Mitkova et al. and as shown in FIG. 1, ternary  $(Ge_xSe_{1-x})_{1-y}Ag_y$  glasses which comprise germanium selenide glasses with silver (Ag) as an additive form in two distinct compositional regions: a selenium-rich region labeled region I (FIG. 1) and a germanium-rich region labeled region II (FIG. 1). As also shown in FIG. 1, a corridor 88 separates the selenium-rich region I from the germanium-rich region II. Mitkova et al. mentions that no bulk glass formation occurs along the corridor 88 until the silver (Ag) concentration exceeds  $y \ge 0.2$  and the two selenium-rich and germanium-rich regions I and II coalesce.

[0029] The study conducted by Mitkova et al. concluded that silver (Ag) acts as a "network modifier" for the glass compositions of the selenium-rich region I (FIG. 1). In this region, silver (Ag) phase separates into an  $Ag_2Se_{-1}$ -rich phase and a  $Ge_tSe_{1-t}$  phase which has less Se than the starting  $Ge_{-1-x}$  material. In contrast, in the germanium-rich region II (FIG. 1), silver (Ag) acts as a "network former" for glass compositions, forms part of the backbone and reduces the connectivity of the glass.

[0030] Referring back to FIG. 1 and further analyzing the ternary phase diagram with glass forming regions for  $(Ge Se_{1-x})_{1-y}Ag_y$  compounds, Applicant has discovered that the careful selection of the stoichiometry of a chalcogenide glass is directly correlated to the ability of the doped chalcogenide glass to maintain an amorphous state over a wide and continuous range of dopant metal concentrations and, therefore, to successfully function as a programmable memory cell.

[0031] Accordingly, Applicant has discovered that, contrary to current belief in the semiconductor art, not all doped germanium selenide glass stoichiometries could be successfully used as non-volatile or semi-volatile memory devices. Applicant has discovered that optimization of a doped germanium selenide glass for switching operations in memory devices requires the doped germanium selenide glass all fully within a glass forming region, such as the glass forming regions I and II of FIG. 1 of Mitkova et al. In addition, for use in a memory device, the germanium selenide glass must have a glass transition temperature (Tg) high enough to allow the doped germanium selenide glass to withstand temperatures of subsequent wafer processing and/or chip packaging processes, for example wire bonding or encapsulation.

[0032] According to the present invention, germanium selenide glass compositions capable of creating functional non-volatile memory devices require glass stoichiometries to fall in one of the following two ranges:

[0033] a first stoichiometric range R₁ including Ge₁sSe₂2 (with a maximum atomic percentage of Ag when doped of about 30% or less) continuously to Ge₂sSe₁2 (with a maximum atomic percentage of Ag when doped of about 20% or less) and which have the general formula (Ge₂1Se₁-x1)₁-y1Agy₁, wherein 18≤x₁≤28 and wherein y₁ represents the fit silver (Ag) atomic percentage which is the maximum amount which will keep the glass in the glass forming region. Typically, y₁ is less than or equal to that which approximately satisfies equation (1):

$$y_1=19+15*\sin[0.217*x_1+3.23]$$

(2) [0034] or

[0035] a second stoichiometric range  $R_2$  of doped chalcogenide glasses including  $Ge_{39}Se_{61}$  (with a

maximum atomic percentage of Ag when doped of about 20% or less) continuously to  $Ge_{42}Se_{58}$  (with a maximum atomic percentage of Ag when doped of about 15% or less) and which have the general formula  $(Ge_{x2}Se_{1-x2})_{1-y2}Ag_{y2}$ , wherein  $39 \le x_2 \le 42$  and wherein  $y_2$  represents the fit silver (Ag) atomic percentage which is the maximum amount which will keep the glass in the glass forming region. Typically,  $y_1$  is less than or equal to that which approximately satisfies equation (2):

$$y_2 = 21 - 11.5 \exp[-(\ln(x_2/44.4)/(0.84)^2)]$$

(2)

[0036] For example, germanium selenide glasses having a selenium (Se) composition of about 62% to about 71% will not be able to form functional memory devices as the doped glass falls within the coridor 88 (FIG. 1) and out of the first and second stoichiometric ranges  $R_1$ ,  $R_2$ , described above. For example, a memory device using a doped germanium selenide glass having a selenium (Se) composition of about 63.5% and a silver (Ag) doping between about 7% to about 22% fails after one write/erase data retention cycle.

[0037] Similarly, germanium selenide glasses having a selenium (Se) composition greater than about 82% will also not be able to form functional memory devices, as they fall out of the first and second stoichiometric ranges  $R_1$ ,  $R_2$  described above, when the amount of silver (Ag) dopant is sufficient for the switching operation. Doped chalcogenide germanium selenide glasses having a selenium (Se) composition less than about 58% will also be incapable of forming functional memory devices since the maximum amount of silver (Ag) dopant allowable to remain in glass forming region  $R_2$  is insufficient for the switching operation (the maximum silver atomic percentage is lower than about 7%).

[0038] The following Table 1 is a compilation of data on silver-doped germanium selenide glasses used as non-volatile memory cells obtained by the Applicant. Carefully choosing the stoichiometry of the silver-doped germanium selenide glass to fall either within the first or second stoichiometric range  $R_{\rm 1},\,R_{\rm 2}$  described above allows the silver-doped germanium selenide glass to function as a non-volatile memory cell. This is because, above 82% Se, the maximum allowable Ag falls rapidly to less than 10% Ag allowed to remain in the glass forming region. This amount of Ag is insufficient to obtain good electrical switching.

TABLE 1

|                 | E        | dge      | _                                                                                                                       | Glass forming region Ag | Ag-doped glass in     |

|-----------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|

| Lot #, Wfr #    | at. % Se | at. % Ge | Functional?                                                                                                             | ternary phase diagram   | glass forming region? |

| 0641274, wfr 5  | 63.5     | 36.5     | Initially Yes; Fails<br>after a write/erase<br>data retention cycle.                                                    | >~7 and <~22 at. % Ag   | Only initially.       |

| 0440263, wfr 14 | 68.5     | 31.5     | No. Poor write erase characteristics and limited data retention.                                                        | >~18 and <~30 at. % Ag  | No.                   |

| 0540868, wfr 5  | 83.9     | 16.1     | No. Devices would<br>not switch, remaining<br>in low resistance state<br>characteristic of too<br>much Ag in the glass. | <-10 at. % Ag           | No.                   |

TABLE 1-continued

|                 | E        | dge      | _                                                                                    | Glass forming region Ag | Ag-doped glass in     |

|-----------------|----------|----------|--------------------------------------------------------------------------------------|-------------------------|-----------------------|

| Lot #, Wfr #    | at. % Se | at. % Ge | Functional?                                                                          | ternary phase diagram   | glass forming region? |

| 0440263, wfr 12 | 85.2     | 14.8     | No. Devices that would write were threshold switches.                                | <~7 at. % Ag            | No.                   |

| 0440263, wfr 8  | 80       | 20       | Yes. Good write<br>characteristics and<br>data retention. Good<br>subsequent erases. | up to 34 at. % Ag       | Yes.                  |

| 1344272, wfr 1  | 77       | 23       | Yes. Good write and erase characteristics.                                           | up to ~33 at. % Ag      | Yes.                  |

| 2349273, wfr 7  | 75       | 25       | Yes. Good write and erase characteristics                                            | up to ~33 at. % Ag      | Yes.                  |

[0039] The Ge<sub>20</sub>Se<sub>80</sub> glass doped with Ag up to 34% (Table 1) falls entirely within the first stoichiometric range R<sub>1</sub> of doped germanium selenide glasses and, therefore, falls within the glass forming regions of the present invention. Memory cells employing such Ge<sub>20</sub>Se<sub>80</sub> glass doped with Ag up to 34% exhibit good write/erase characteristics and are fully functional. Additionally, memory cells with Ge<sub>25</sub>Se<sub>77</sub> and Ge<sub>25</sub>Se<sub>75</sub> doped with up to 33% Ag exhibit good write/erase characteristics. In contrast, the first four silver-doped germanium selenide compositions of Table 1 fall out of the glass forming regions when doped with an adequate amount of Ag for good electrical switching. Accordingly, the memory cells which use such silver-doped germanium selenide compositions are all non-functional because the devices do not switch and/or have poor write/ erase characteristics. Out of the four non-functional silverdoped germanium selenide compositions of Table 1, only the Ge<sub>36.5</sub>Se<sub>63.5</sub> doped with silver (Ag) with an atomic percentage greater that about 7% but smaller than about 22% exhibits initially good write/erase characteristics, but fails after one cycle.

[0040] The data of Table 1 supports Applicant's observation that functional non-volatile memory devices based on a doped germanium selenide glass composition require such glass composition to have a particular stoichiometry that falls within one of the first or second stoichiometric range R<sub>1</sub>, R<sub>2</sub> described above. However, as noted above, optimization of functional memory devices based on doped germanium selenide glasses requires glass transition temperatures (Tg) that allow the doped germanium selenide glasses to withstand temperatures for conventional fabrication and/ or packaging processes, for example, wire bonding or encapsulation. Thus, in accordance with an embodiment of the present invention, germanium selenide glasses for nonvolatile or semi-volatile memory devices have stoichiometries that fall within the two stoichiometric ranges R<sub>1</sub>, R<sub>2</sub> described above, and have also a glass transition temperature (Tg) which is about or higher than the processing and/or packaging temperatures.

[0041] Table 2 lists glass transition temperatures (Tg) measured for nine germanium selenide chalcogenide glasses:

TABLE 2

| Tg     | at. % Ge | at. % Se |

|--------|----------|----------|

| 107.39 | 12       | 88       |

| 165.54 | 18       | 82       |

| 183.91 | 20       | 80       |

| 209.37 | 23       | 77       |

| 228.57 | 24       | 76       |

| 249.1  | 25       | 75       |

| 334.83 | 30       | 70       |

| 415.76 | 33       | 67       |

| 346.67 | 40       | 60       |

[0042] Typical temperatures for packaging of non-volatile memory devices are of about 170° C. to about 190° C. (e.g., for encapsulation) and can be as high as 230° C. (e.g., for wire bonding). Typical processing steps during the fabrication of such non-volatile memory devices, for example photoresist and/or nitride deposition processes, can also take place at temperatures of about 200° C. Accordingly, to obtain a viable chalcogenide glass composition for a memory cell of a memory device, the stoichiometry must fall within the first or second stoichiometric ranges R<sub>1</sub>, R<sub>2</sub> discussed above and must have a glass transition temperature (Tg) which is about or higher than the highest packaging and/or processing temperatures used during the formation of the memory device or of the packaging of the memory device itself. This way, the selection of a germanium selenide glass for a functional memory cell accounts for both a stoichiometry that falls within glass forming regions and an adequate glass transition temperature (Tg). For example, a Ge<sub>25</sub>Se<sub>75</sub> glass is a good candidate for a non-volatile memory device because the Ge<sub>25</sub>Se<sub>75</sub> glass falls within the first stoichiometric range R<sub>1</sub> described above and it also has a glass transition temperature (Tg) of about 250° C. Another good candidate is a Ge<sub>40</sub>Se<sub>60</sub> glass because it also falls within the second stoichiometric range R<sub>2</sub> described above and has a glass transition temperature (Tg) of about 347° C.

[0043] Reference is now made to FIGS. 2-10 which illustrate an exemplary embodiment of a non-volatile memory device 100 (FIG. 10) using a doped germanium selenide glass selected in accordance with the present invention. FIG. 2 depicts a portion of an insulating layer 12 formed over a semiconductor substrate 10. The insulating layer 12 may be formed by any known deposition methods, such as sputtering by chemical vapor deposition (CVD), plasma enhanced CVD (PECVD) or physical vapor deposition

(PVD), among others. The insulating layer 12 may be formed of a conventional insulating oxide, such as silicon oxide (SiO<sub>2</sub>), a silicon nitride (Si<sub>3</sub>N<sub>4</sub>), or a low dielectric constant material, among many others.

[0044] A first electrode 14 is next formed over the insulating layer 12, as also illustrated in FIG. 2. The first electrode 14 comprises any conductive material, for example, tungsten, tantalum, titanium, platinum, or silver, among many others. A dielectric layer 15 (FIG. 2) is next formed over the first electrode 14. The dielectric layer 15 may comprise similar materials to those described above with reference to the insulating layer 12.

[0045] Referring now to FIG. 3, an opening 13 is formed in the dielectric layer 15 and extending to the first electrode 14. The opening 13 may be formed by known methods of the art, for example, by a conventional patterning and etching process. A chalcogenide glass 17 is next formed over the dielectric layer 15, to fill in the opening 13, as shown in FIG. 4

[0046] According to an embodiment of the present invention, the chalcogenide glass 17 is a germanium selenide glass having a Ge<sub>23</sub>Se<sub>77</sub> stoichiometry that falls within the first stoichiometric range R<sub>1</sub> and within a glass forming region of the present invention. The formation of the germanium selenide glass 17 with Ge<sub>23</sub>Se<sub>77</sub> stoichiometry in accordance with one exemplary embodiment may be accomplished by evaporating a germanium selenide glass which has been synthesized with the exact stoichiometries, i.e. 23% germanium and 77% selenium. In accordance with another exemplary embodiment, the germanium selenide glass 17 with Ge<sub>23</sub>Se<sub>77</sub> stoichiometry is formed by cosputtering germanium and selenium in the appropriate ratios, or by sputtering using a Ge<sub>23</sub>Se<sub>77</sub> target. In yet another embodiment of the invention, the germanium selenide glass 17 with Ge<sub>23</sub>Se<sub>77</sub> stoichiometry is formed by chemical vapor deposition with stoichiometric amounts of GeH<sub>4</sub> and SeH<sub>2</sub> gases (or various compositions of these gases) which result in a Ge<sub>23</sub>Se<sub>77</sub> film.

[0047] Once the germanium selenide glass 17 with the desired stoichiometry has been formed, the doping concentration of the silver dopant is selected with a maximum concentration in accordance with the ternary phase diagram of FIG. 1 and the equations (1) and (2) outlined above. Accordingly, for the germanium selenide glass 17 with a Ge\_Se\_77 stoichiometry, the maximum silver doping is about 33%.

[0048] Referring now to FIG. 5, incorporation of silver into the  $Ge_{23}Se_{77}$  glass 17 may be accomplished by photodoping, that is depositing a thin layer 18 comprising silver, preferably predominantly elemental silver, over the  $Ge_{23}Se_{77}$  glass 17 and then "driving" the silver atoms within the  $Ge_{23}Se_{77}$  glass by using light (FIG. 6), or by cosputtering with Ag, Ge and Se, or Ag and a  $Ge_{23}Se_{77}$  target, or  $Ag_2Se$  and  $Ge_xSe_{1-x}$ . The thickness of the layer 18 comprising silver is selected so that, when the silver is subsequently diffused into the germanium selenide glass layer 17, the atomic percentage of Ag in resulting silver-doped chalcogenide glass 20 (FIG. 7) will allow such glass to fall within a glass forming region  $R_1$  or  $R_2$ .

[0049] Depending upon the glass stoichiometry, the silver atoms will either incorporate themselves into the glass

backbone (the Ge—Se structure) or react with Se to form  $Ag_2Se$ , leaving behind a silver-doped germanium selenide glass **20** (FIG. 7) with a new Ge—Se stoichiometry. Thus, when about 33% of silver is incorporated into the  $Ge_{23}Se_{77}$  glass, the system phase separates into an  $Ag_2Se$  phase and a  $Ge_{30}Se_{70}$  backbone glass.

[0050] As mentioned above, the proper selection of the germanium selenide glass for the memory element 100 (FIG. 10) requires the doped germanium selenide glass to fall within the glass forming region and to have a glass transition temperature (Tg) which is about or higher than the highest fabrication and/or packaging processing temperatures. Thus, for the exemplary embodiment described above, the silver-doped Ge<sub>23</sub>Se<sub>77</sub> glass 20 of the memory device 100 (FIG. 10) can withstand processing temperatures at least as high as about 210° C.

[0051] Referring now to FIG. 8, a second conductive electrode material 16 is formed over the doped germanium selenide glass 20. The second conductive electrode material 16 may comprise any electrical conductive material, for example, tungsten, tantalum, titanium, or silver, among many others, as long as it is a different material than the first electrode 14.

[0052] After the formation of the second conductive electrode material 16 (FIG. 8), further steps to create a functional memory cell may be carried out. Patterning by photolithography, for example, may be employed to produce memory element 20a and second electrode 16a, illustrated in FIG. 9. Referring now to FIG. 10, one or more dielectric layers 30 are formed over the second electrode 16a and the dielectric layer 15 to complete the formation of the nonvolatile memory device 100 (FIG. 10). Conventional processing steps can be further carried out to electrically couple the second electrode 16a to various circuits of memory arrays. Alternatively, additional multilevel interconnect layers and associated dielectric layers could be formed from the memory cell 100 to appropriate regions of the substrate 10, as desired.

[0053] Although only two electrodes 14, 16a are shown in FIGS. 2-10, it must be readily apparent to those skilled in the art that in fact any number of such electrodes may be formed. In addition, although the embodiments described above refer to the formation of only one non-volatile memory cell 100, it must be understood that the present invention contemplates the formation of any number of such non-volatile memory cells.

[0054] Although an exemplary memory cell fabrication has been described above using a  $Ge_{23}Se_{77}$  composition, other Ge/Se stoichiometries for the glass composition within the R1, R2 ranges described above, besides  $Ge_{23}Se_{77}$ , can be used. For example,  $Ge_{25}Se_{75}$  and  $Ge_{20}Se_{80}$  compositions have been found to be particularly good compositions for memory cell fabrication.

[0055] Although the present invention has been explained with reference to the formation of a doped germanium selenide glass with a stoichiometry selected according to the present invention, the invention is not limited to this embodiment and has applicability to other chalcogenide glasses. Accordingly, the stoichiometry of any chalcogenide glass comprising any one of oxygen (O), sulfur (S), selenium (Se) and tellurium (Te) and doped with a metal dopant

may be selected so that the doped chalcogenide glass maintains an amorphous state over a wide and continuous range of dopant metal concentrations. Thus, the present invention contemplates any doped chalcogenide glass that falls fully within a glass-forming region (corresponding to a respective ternary phase diagram for a particular chalcogenide glass) and has a glass transition temperature (Tg) which is about or higher than the highest processing temperature for memory device fabrication.

[0056] Further, although the invention has been explained with reference to the formation of a germanium selenide glass doped with silver, other dopants may be used also, depending on the device characteristics and as desired. Thus, the invention also contemplates chalcogenide glasses doped with copper, platinum, gold, silver, cadmium, iridium, ruthenium, cobalt, chromium, maganese or nickel, among many others

[0057] A typical processor-based system 400 which includes a memory circuit 448, for example a PCRAM, one or both of which contain non-volatile or semi-volatile memory cells, such as the non-volatile memory cell 100 according to the present invention is illustrated in FIG. 11. A processor system, such as a computer system, generally comprises a central processing unit (CPU) 444, such as a microprocessor, a digital signal processor, or other programmable digital logic devices, which communicates with an input/output (I/O) device 446 over a bus 452. The memory 448 communicates with the system over bus 452.

[0058] In the case of a computer system, the processor system may include peripheral devices such as a floppy disk drive 454 and a compact disk (CD) ROM drive 456 which also communicate with CPU 444 over the bus 452. Memory 448 is preferably constructed as an integrated circuit, which includes one or more non-volatile memory cells 100. If desired, the memory 448 may be combined with the processor, for example CPU 444, in a single integrated circuit.

[0059] The above description and drawings are only to be considered illustrative of exemplary embodiments which achieve the features and advantages of the present invention. Modification and substitutions to specific process conditions and structures can be made without departing from the spirit and scope of the present invention. Accordingly, the invention is not to be considered as being limited by the foregoing description and drawings, but is only limited by the scope of the appended claims.

What is claimed as new and desired to be protected by Letters Patent of the United States is:

- 1. A memory cell comprising:

- a chalcogenide glass doped with a metal, said chalcogenide glass having a stoichiometry and a maxium allowable amount of metal dopant which causes said chalcogenide glass to remain in a glass forming region;

- a first electrode and a second electrode in contact with said chalcogenide glass; and

- a dendrite formed between said first and second electrodes when voltage is applied to said first and second electrodes.

- 2. The memory cell of claim 1, wherein said chalcogenide glass has a glass transition temperature which is about or higher than the highest temperature used in the formation and packaging of a memory device containing said memory cell.

- 3. The memory cell of claim 1, wherein said chalcogenide glass comprises a material selected from the group consisting of oxygen, sulfur, tellurium and selenium.

- 4. The memory cell of claim 3, wherein said chalcogenide glass comprises oxygen.

- 5. The memory cell of claim 3, wherein said chalcogenide glass comprises sulfur.

- 6. The memory cell of claim 3, wherein said chalcogenide glass comprises tellurium.

- 7. The memory cell of claim 3, wherein said chalcogenide glass comprises selenium.

- 8. The memory cell of claim 1, wherein said metal is selected from the group consisting of silver, copper, platinum, gold, cadmium, ruthenium, cobalt, zinc, chromium, maganese and nickel.

- 9. The memory cell of claim 1, wherein said chalcogenide glass is a germanium selenide glass.

- 10. The memory cell of claim 9, wherein said chalcogenide glass is a germanium selenide glass doped with silver.

- 11. A non-volatile memory cell comprising:

- a germanium selenide glass doped with silver, said silver doping being in a concentration which maintains said germanium selenide glass in the glass forming region;

- a first electrode and a second electrode in contact with said doped germanium selenide glass; and

- a dendrite formed between said first and second electrodes when voltage is applied to said first and second electrodes.

- 12. The non-volatile memory cell of claim 11, wherein said germanium selenide glass has a glass transition temperature which is about or higher than the highest temperature used in the fabrication and packaging of a memory device containing said non-volatile memory cell.

- 13. The non-volatile memory cell of claim 11, wherein said germanium selenide glass comprises a material having the formula  $(Ge_{x_1}Se_{1-x_1})_{1-y_1}Ag_{y_1}$ , wherein  $18 \le x_1 \le 28$ .

- 14. The non-volatile memory cell of claim 13, wherein  $y_1$  represents a silver atomic percentage which is less than or equal to that which approximately satisfies equation  $y_1$ =19+15 \*  $\sin[0.217*x_1+3.23]$ .

- 15. The non-volatile memory cell of claim 11, wherein said germanium selenide glass comprises a material having the formula  $(Ge_{x2}Se_{1-x2})_{1-y2}Ag_{y2}$ , wherein  $39 \le x_2 \le 42$ .

- 16. The non-volatile memory cell of claim 15, wherein  $y_2$  represents a silver atomic percentage which is less than or equal to that which approximately satisfies equation  $y_2=21-11.5 \text{ *exp}[-(\ln(x_2/44.4)/(0.84)^2)].$

- 17. A chalcogenide glass material having the formula  $(Ge_{x1}Se_{1-x1})_{1-y1}Ag_{y1}$ , wherein  $18 \le x_1 \le 28$  and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region.

- 18. The chalcogenide glass material of claim 17, wherein  $x_1=23$ .

- 19. The chalcogenide glass material of claim 17, wherein  $x_1=25$ .

- **20**. The chalcogenide glass material of claim 17, wherein  $x_1$ =20.

- 21. The chalcogenide glass material of claim 17, wherein  $y_1$  represents a silver atomic percentage which is less than or equal to that which approximately satisfies equation  $y_1=19+15 * \sin[0.217*x_1+3.23]$ .

- 22. A chalcogenide glass material having the formula  $(Ge_{x2}Se_{1-x2})_{1-y2}Ag_{y2}$ , wherein  $39 \le x_2 \le 42$  and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region.

- 23. The chalcogenide glass material of claim 22, wherein  $y_2$  represents a silver atomic percentage which is less than or equal to that which approximately satisfies equation  $y_2=21-11.5 \exp[-(\ln(x_2/44.4)/(0.84)^2)]$ .

- 24. A memory cell comprising:

- a germanium selenide glass having the formula  $(Ge_{x_1}Se_{1-x_1})_{1-y_1}Ag_{y_1}$ , wherein  $18 \le x_1 \le 28$  and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region; and,

- at least two electrodes in contact with said germanium selenide glass, said germanium selenide glass forming a dendrite between at least two electrodes in response to a voltage applied across said at least two electrodes.

- 25. A memory cell comprising:

- a germanium selenide glass having the formula  $(Ge_{x2}Se_{1-x2})_{1-y2}Ag_{y2}$ , wherein  $39 \le x_2 \le 42$  and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region; and

- at least two electrodes in contact with said germanium selenide glass, said germanium selenide glass forming a dendrite between at least two electrodes in response to a voltage applied across said at least two electrodes.

- **26**. A method of forming a memory cell comprising the steps of:

providing a chalcogenide glass over a substrate;

doping said chalcogenide glass with a metal to form a doped chalcogenide glass, said doped chalcogenide glass having a stoichiometry which causes said doped chalcogenide glass to be in a glass forming region, said doped chalcogenide glass having a glass transition temperature which is about or higher than the highest temperature used in the formation and packaging of a memory device containing said memory cell; and,

forming a plurality of electrodes in contact with said doped chalcogenide glass.

27. A method of forming a memory cell comprising the steps of:

providing a germanium selenide glass having the formula  $(Ge_{x1}Se_{1-x1})_{1-y1}Ag_{y1}$ , wherein  $18 \le x_1 \le 28$  over a substrate, and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region; and,

forming at least two electrodes in contact with said germanium selenide glass at locations which permit said glass to transition between high and low resistance states in response to signals applied to said electrodes.

- **28**. The method of claim 27, wherein  $x_1=23$ .

- **29**. The method of claim 27, wherein  $x_1=25$ .

- **30**. The method of claim 27, wherein  $x_1=20$ .

- **31.** A method of forming a memory cell comprising the steps of:

- providing a germanium selenide glass having the formula  $(Ge_{x2}Se_{1-x2})_{1-y2}Ag_{y2}$ , wherein  $39 \le x_2 \le 42$  and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region; and,

- forming at least two electrodes in contact with said germanium selenide glass at locations which permit said glass to transition between high and low resistance states in response to signals applied to said electrodes.

- **32.** A method of operating a memory cell comprising the steps of:

- applying a voltage across a germanium selenide glass having the formula  $(Ge_{x1}Se_{1-x1})_{1-y1}Ag_{y1}$ , wherein  $18 \le x_1 \le 28$  and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region, to change the resistance state of said glass.

- 33. The method of claim 32, wherein  $x_1=23$ .

- **34**. The method of claim 32, wherein  $x_1=25$ .

- **35**. The method of claim 32, wherein  $x_1=20$ .

- **36**. A method of operating a memory cell comprising the steps of:

- applying a voltage across a germanium selenide glass having the formula  $(Ge_{x2}Se_{1-x2})_{1-y2}Ag_{y2}$ , wherein  $39 \le x_2 \le 42$  and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region, to change the resistance state of said glass.

- **37**. A processor system comprising:

- a processor; and

- an integrated circuit coupled to said processor, at least one of said processor and integrated circuit including a memory cell, said memory cell comprising:

- a germanium selenide glass having the formula( $Ge_{x1}Se_{1-x1}$ )<sub>1-y1</sub> $Ag_{y1}$ , wherein  $18 \le x_1 \le 28$  and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region; and

- at least two electrodes in contact with said doped germanium selenide glass, said germanium selenide glass changing a resistance state in response to application of a voltage across said at least two electrodes.

- **38**. The processor system of claim 37, wherein said processor and said integrated circuit are integrated on same chip.

- **39**. The processor system of claim 37, wherein  $x_1=23$ .

- **40**. The processor system of claim 37, wherein  $x_1=25$ .

- **41**. The processor system of claim 37, wherein  $x_1=20$ .

- 42. A processor system comprising:

- a processor; and

- an integrated circuit coupled to said processor, at least one of said processor and integrated circuit including a memory cell, said memory cell comprising:

- a germanium selenide glass having the formula  $(Ge_{x2}Se_{1-x2})_{1-y2}Ag_{y2}$ , wherein  $39 \le x_2 \le 42$  and wherein said silver is in a concentration which maintains said germanium selenide glass in the glass forming region; and

- at least two electrodes in contact with said doped germanium selenide glass, said germanium selenide glass changing a resistance state in response to application of a voltage across said at least two electrodes.

- **43**. The processor-based system of claim **42**, wherein said processor and said integrated circuit are integrated on same chip.

\* \* \* \* \*