(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6495251号

(P6495251)

(45) 発行日 平成31年4月3日(2019.4.3)

(24) 登録日 平成31年3月15日(2019.3.15)

(51) Int.Cl.

H02J 7/02 (2016.01)

H01M 10/44 (2006.01)

F 1

H02J 7/02

H01M 10/44F

Q

請求項の数 11 (全 20 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-515120 (P2016-515120)  |

| (86) (22) 出願日 | 平成26年5月23日 (2014.5.23)        |

| (65) 公表番号     | 特表2016-521953 (P2016-521953A) |

| (43) 公表日      | 平成28年7月25日 (2016.7.25)        |

| (86) 國際出願番号   | PCT/US2014/039380             |

| (87) 國際公開番号   | W02014/190283                 |

| (87) 國際公開日    | 平成26年11月27日 (2014.11.27)      |

| 審査請求日         | 平成29年4月26日 (2017.4.26)        |

| (31) 優先権主張番号  | 61/827,443                    |

| (32) 優先日      | 平成25年5月24日 (2013.5.24)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 14/065,752                    |

| (32) 優先日      | 平成25年10月29日 (2013.10.29)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                        |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                        |

| (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                        |

| (74) 代理人  | 100112807<br>弁理士 岡田 貴志                                                                                        |

前置審査

最終頁に続く

(54) 【発明の名称】マスタースレーブ多相充電

## (57) 【特許請求の範囲】

## 【請求項 1】

バッテリ充電器のための回路であって、

制御入力と、クロック入力と、誘導エレメントに接続するように構成されるスイッチング出力とを有するスイッチング回路と、

バッテリ端子に接続されたバッテリを充電するように電力を提供するために前記バッテリ端子に前記誘導エレメントを電気的に接続するように構成される充電端子と、

制御端子と、

クロック端子と、

前記スイッチング回路の前記制御入力および前記制御端子に内部で生成された制御信号を供給する第1の構成で動作することと、前記スイッチング回路の前記制御入力に前記制御端子上で受信された外部で生成された制御信号を供給する第2の構成で動作することとを行うように構成される制御セレクタと、

前記スイッチング回路の前記クロック入力および前記クロック端子に内部で生成されたクロック信号を供給する第1の構成で動作することと、前記スイッチング回路の前記クロック入力に前記クロック端子上で受信された外部で生成されたクロック信号を供給する第2の構成で動作することとを行うように構成されたクロックセレクタと、

前記内部で生成された制御信号のソースとしての役割を果たすフィードバック補償ネットワークと

を備え、前記第2の構成で動作するように構成される前記制御セレクタは、前記フィード

10

20

ドバック補償ネットワークを切斷するように構成される、回路。

**【請求項 2】**

前記スイッチング回路の前記スイッチング出力に接続された第1のFETと第2のFETとをさらに備え、前記第1のFETは、前記第2のFETに接続され、前記第1のFETと前記第2のFETとは、前記制御入力上で受信した制御信号と前記クロック入力上で受信したクロック信号とにしたがう前記スイッチング回路によってONとOFFが切り替えられる、

請求項1に記載の回路。

**【請求項 3】**

前記クロック入力に前記クロック端子上で受信した外部で生成されたクロック信号を供給するために、前記クロック入力と前記クロック端子との間の前記クロックセレクタによつて選択的に接続されることができる遅延エレメントをさらに備える、

請求項1に記載の回路。

**【請求項 4】**

前記遅延エレメントは、前記外部で生成されたクロック信号の選択可能な位相シフトを提供するように構成される、

請求項3に記載の回路。

**【請求項 5】**

前記内部で生成されたクロック信号を生成するクロック信号生成器と、遅延エレメントと

をさらに備え、

前記クロックセレクタは、前記第1の構成で動作するとき、前記スイッチング回路の前記クロック入力および前記クロック端子に前記クロック信号生成器を接続し、

前記クロックセレクタは、前記第2の構成で動作するとき、前記クロック入力に前記クロック端子上で受信した外部で生成されたクロック信号を供給するために、前記クロック端子と前記クロック入力との間に前記遅延エレメントを接続する、

請求項1に記載の回路。

**【請求項 6】**

前記遅延エレメントは、前記外部で生成されたクロック信号の位相シフトを生成するように構成される、

請求項5に記載の回路。

**【請求項 7】**

前記内部で生成された制御信号を生成する制御信号生成器をさらに備え、

前記制御セレクタは、前記第1の構成で動作するとき、前記スイッチング回路の前記制御入力および前記制御端子に、前記制御信号生成器を接続し、

前記制御セレクタは、前記第2の構成で動作するとき、前記制御入力に前記制御端子上で受信した外部で生成された制御信号を提供するために前記制御入力に前記制御端子を接続する、

請求項1に記載の回路。

**【請求項 8】**

外部の選択インジケータに接続するように構成されるセレクタ入力をさらに備え、前記制御セレクタと前記クロックセレクタは、前記選択インジケータに依存する前記第1の構成または前記第2の構成において動作する、

請求項1に記載の回路。

**【請求項 9】**

前記選択インジケータは、デジタル信号である、

請求項8に記載の回路。

**【請求項 10】**

前記選択インジケータは、アナログ信号である、

請求項8に記載の回路。

10

20

30

40

50

**【請求項 11】**

前記選択インジケータは、1つまたは複数の抵抗エレメントを備える、

請求項8に記載の回路。

**【発明の詳細な説明】****【関連出願の相互参照】****【0001】**

[0001]本願は、2013年10月29日に出願された米国特許出願第14/065,752号の優先権を主張し、それは同様に、2013年5月24日に出願された米国特許仮出願第61/827,443号の出願日の利益を受ける権限があり、かつ同利益を主張するものであり、それらの全ての内容は、全ての目的のためにその全体が参照により本明細書において組み込まれる。10

**【背景技術】****【0002】**

[0002]本明細書において別途示されない限り、このセクション内において説明されるアプローチは、本願内における特許請求の範囲に対する先行技術ではなく、このセクション内における包含によって先行技術であると認められるものではない。

**【0003】**

[0003]モバイル計算デバイス（例えば、スマートフォン、コンピュータタブレット、等）がより幅広く使用され続けるにつれて、バッテリの高速充電の必要性は、より有意となっている。高速バッテリ充電技法における進歩は、高速充電シーケンス中に生じる高温によって妨げられている。ほとんどのケースにおいて、高温は、高インダクタ温度によって引き起こされるが、それは、充電回路の温度を上回りかねない。20

**【発明の概要】****【0004】**

[0004]本開示は、バッテリ充電を実行するように構成された多段並列構成での動作ための多相充電回路について説明する。多相充電回路は、「マスター」動作のための、または「スレーブ」動作のための回路を構成する選択回路を含みうる。マスター構成では、多相充電回路は、マスターとして構成される回路自身中の充電回路の動作を制御することと、外部で生成された信号として、1つまたは複数のスレーブとして構成される回路に、それらの信号を供給することを行なうようにクロック信号および制御信号を生成しうる。スレーブ構成では、多相充電回路は、マスターとして構成される回路とその充電回路の動作を同期するように外部で生成されたクロック信号を使用しうる。いくつかの実施形態において、マスターとして構成されるデバイスは、スレーブとして構成される回路における制御動作に追加の制御信号を供給しうる。30

**【0005】**

[0005]以下の詳細な説明および添付の図面は、本開示の性質および利点のより良い理解を提供する。

**【図面の簡単な説明】****【0006】**

[0006]以下に続く論述および特に図面に関して、示される詳細は、例示的な論述の目的のために例を提示し、本開示の原理の説明および概念的な態様を提供するために提示されることが強調される。この点に関して、本開示の根本的な理解のために必要とされるものを超える実装の詳細を示すための試みは行われない。図面と連動した、以下に続く論述は、本開示にしたがった実施形態がどのように実施されうるかを当業者に明らかにする。添付の図面は以下の通りである。40

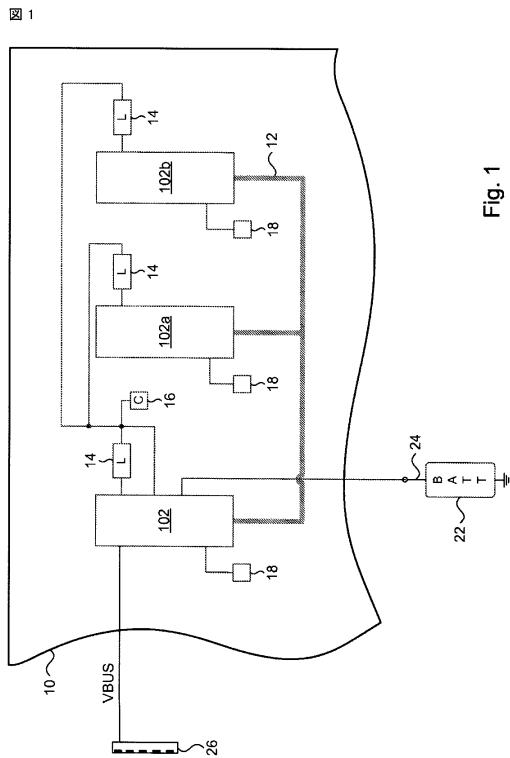

【図1】本開示のプリント回路基板（PCB）レベルの実施形態を示す。

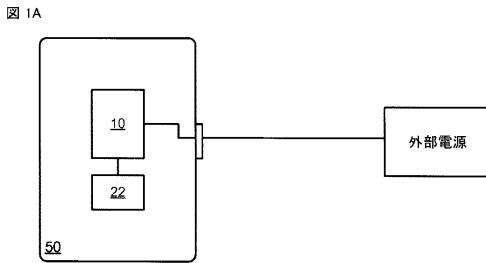

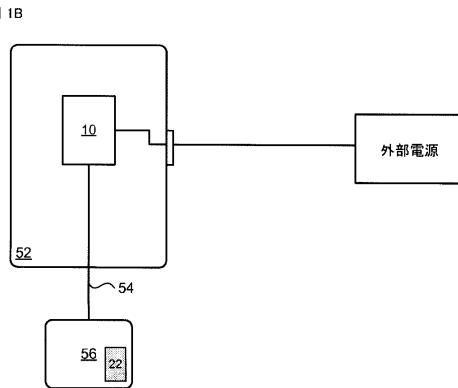

【図1A】本開示にしたがった追加の例示的な実施形態を示す。

【図1B】本開示にしたがった追加の例示的な実施形態を示す。

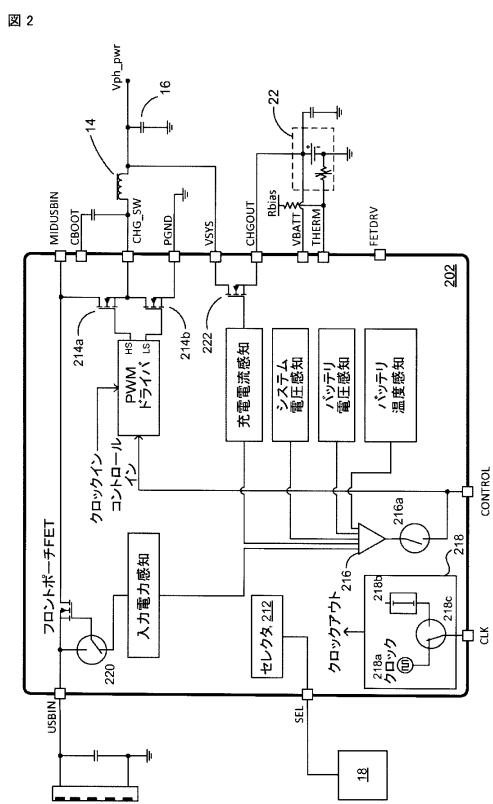

【図2】本開示にしたがった充電回路の概観を示す。

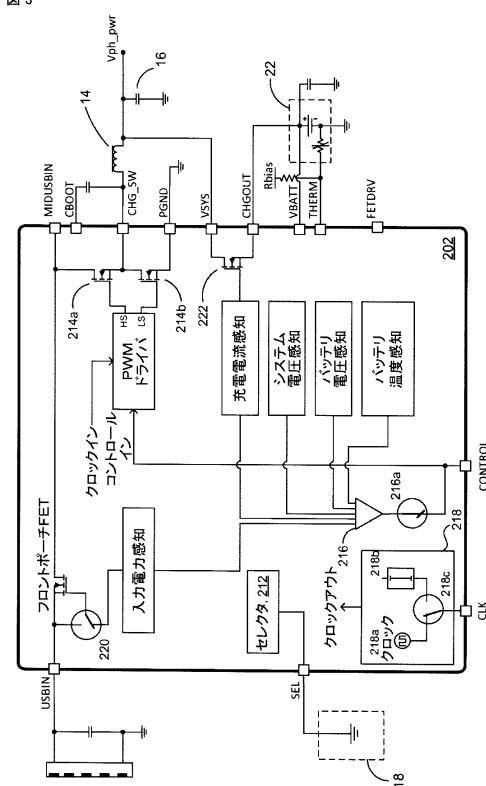

【図3】本開示にしたがった充電回路の単相構成を示す。50

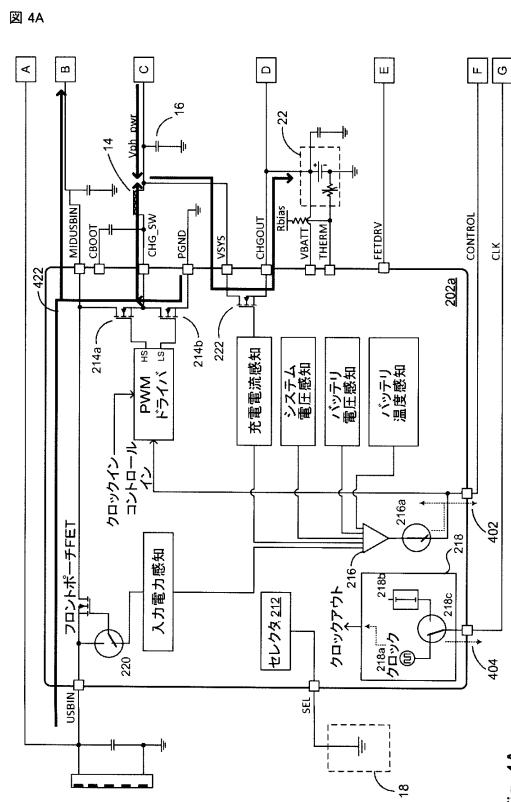

【図4A】本開示にしたがった充電回路の二相構成を示す。

【図4B】本開示にしたがった充電回路の二相構成を示す。

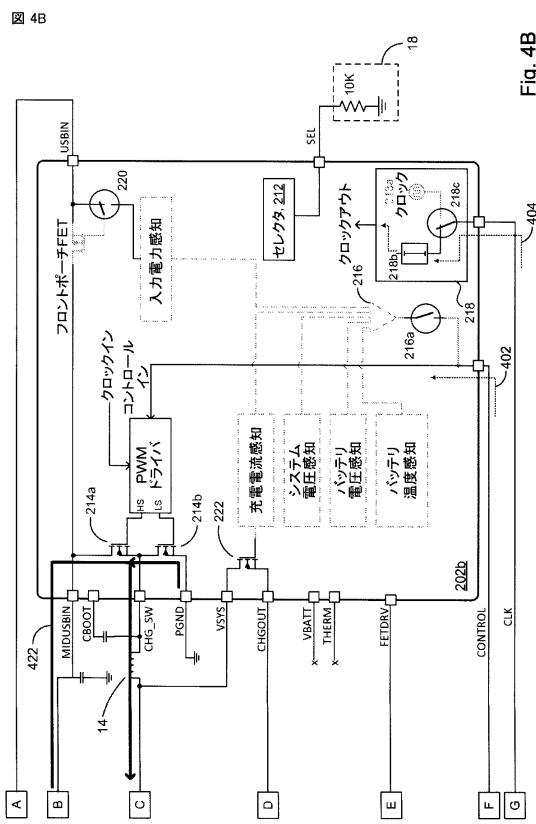

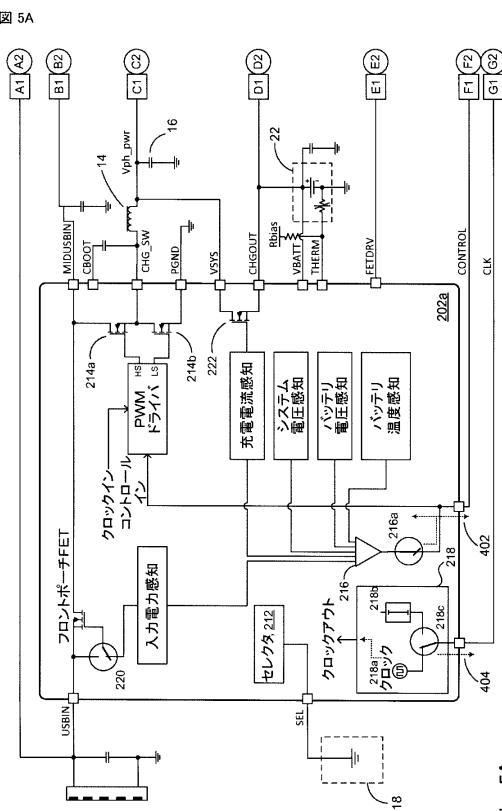

【図5A】本開示にしたがった充電回路の三相構成を示す。

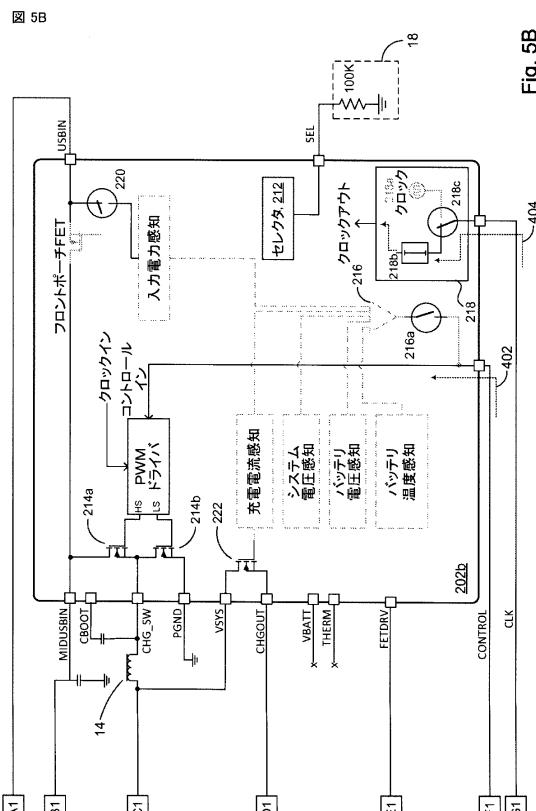

【図5B】本開示にしたがった充電回路の三相構成を示す。

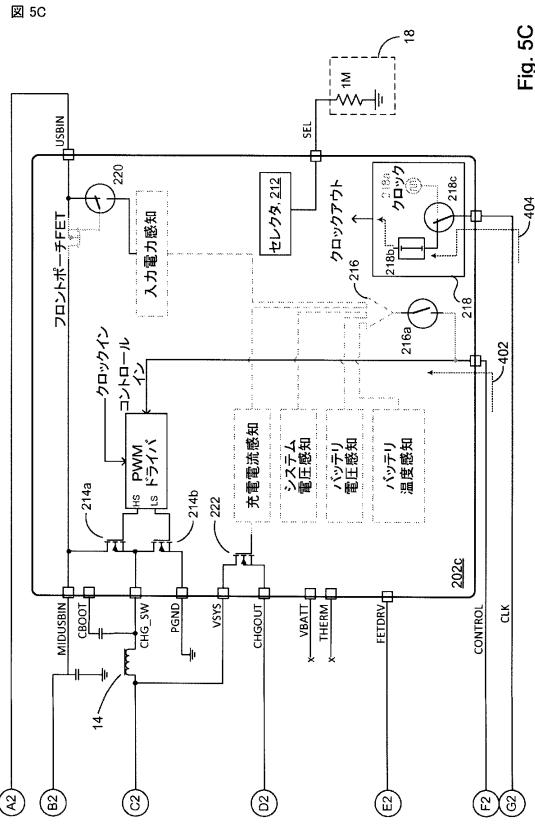

【図5C】本開示にしたがった充電回路の三相構成を示す。

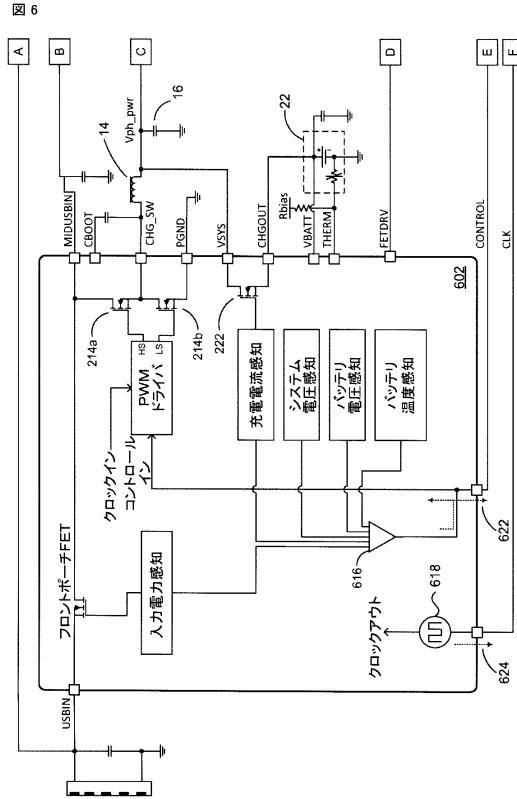

【図6】本開示にしたがったマスター・オンリー充電回路の実装の例を例示する。

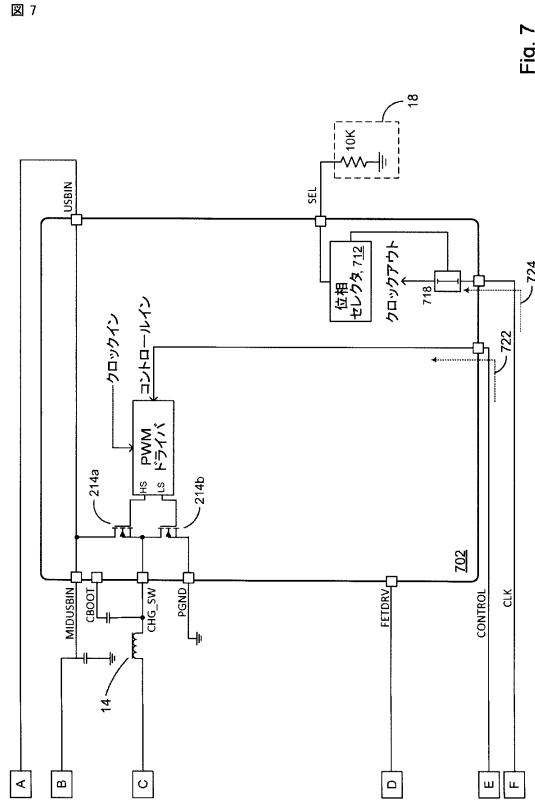

【図7】本開示にしたがったスレーブ・オンリー充電回路の実装の例を例示する。

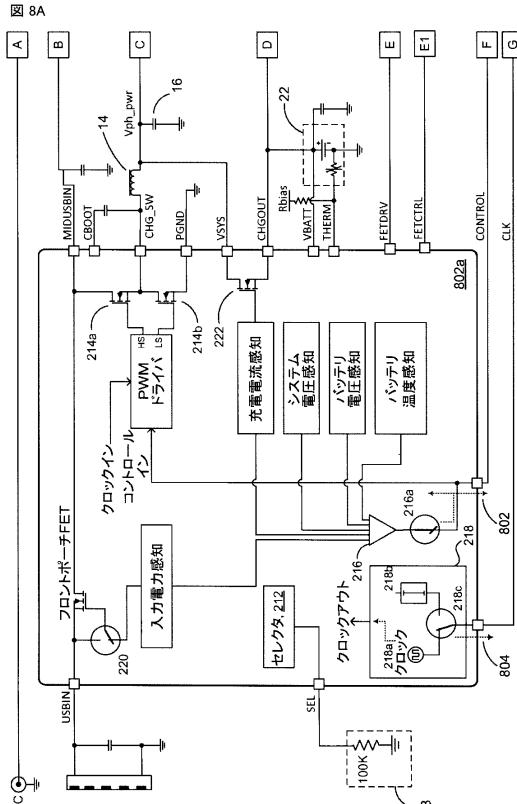

【図8A】デュアル入力マスター・スレーブ構成に関する実施形態を例示する。

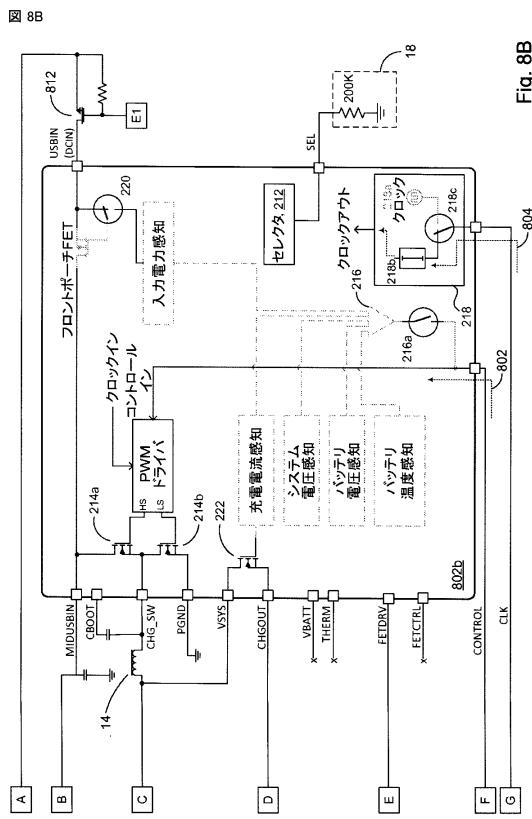

【図8B】デュアル入力マスター・スレーブ構成に関する実施形態を例示する。

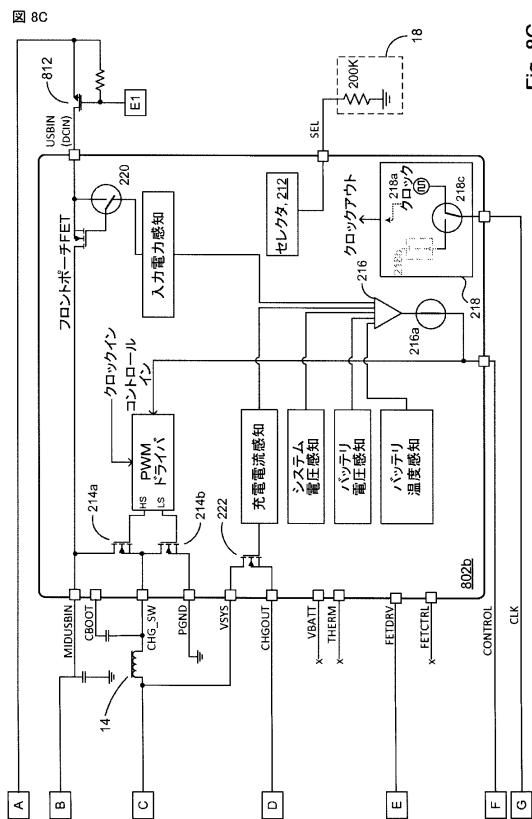

【図8C】デュアル入力マスター・スレーブ構成に関する実施形態を例示する。

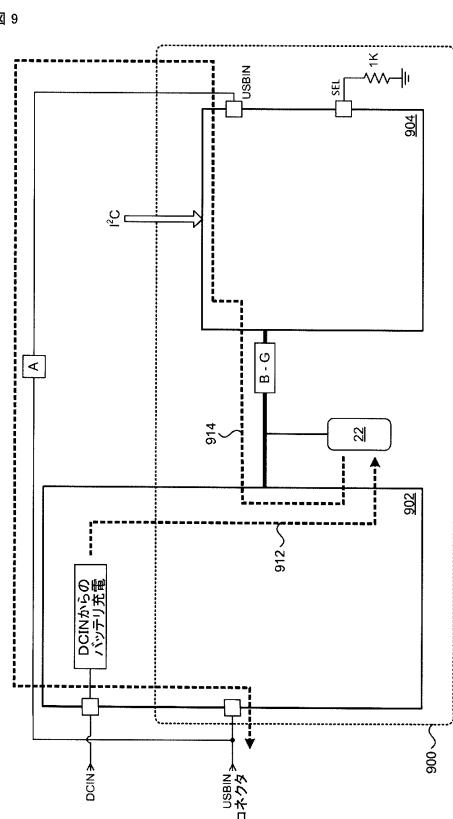

【図9】デュアル入力マスターに関する実施形態を例示する。

【詳細な説明】

【0007】

[0017]以下の説明において、説明の目的ために、本開示の完全な理解を提供するために数多くの例および特定の詳細が記載される。しかしながら、特許請求の範囲内において表される本開示が、これらの例における特徴のうちのいくつかまたは全てを、単独でまたは下記において説明される他の特徴と組み合わせて含み、本願明細書において説明される特徴および概念の修正および同等物をさらに含みうることは、当業者にとって明らかとなるであろう。

【0008】

[0018]図1は、本開示にしたがったバッテリ充電デバイスを配置したプリント回路基板(PCB)10の一部を示す。PCB10は、例えば、モバイル計算デバイス、スマートフォン、および一般に任意の電子デバイス内における回路基板であります。PCB10は、バッテリ充電デバイス102、102a、および102bを配置します。より少ないまたはより多いバッテリ充電デバイスが提供されうることが以下に続く論述内において認識されるであろう。バッテリ充電デバイス102、102a、102bの各々は、任意の適した集積回路(IGC)パッケージング形式(例えば、シングルインラインパッケージング、デュアルインラインパッケージング、表面実装デバイス、等)で具現化され、PCB10上において相互接続されうる。

【0009】

[0019]いくつかの実装形態において、バッテリ充電デバイス102、102a、102bは、動作の異なるモードのために構成されることができる同一デバイスである。例えば、デバイス102は、「マスター」モード動作のために構成されうるが、その一方でデバイス102a、102bは、「スレーブ」モード動作のために構成されうる。バッテリ充電デバイス102、102a、102bは、デバイスに、概して12で表された、PCB配線(trace)を使用してPCB10上において相互接続されることを可能にする(示されていない)ピンまたは端子を含みうることが理解されるであろう。

【0010】

[0020]本開示の原理にしたがって、バッテリ充電デバイス102、102a、102bは、バッテリ充電デバイスによるバッテリの協調充電(coordinated charging)のために接続部24(例えば、バッテリ端子)を介してバッテリ22に接続されうる。バッテリ22は、1つまたは複数のセルの任意の知られる構成(例えば、単一セル構成、マルチセル、マルチスタック構成、等)を備え、再充電を可能にする任意の適した化学的性質(chemistry)を使用しうる。

【0011】

[0021]いくつかの実施形態において、バッテリ充電デバイス102、102a、102bは、バックコンバータ(buck converter)として動作し、他の実施形態において、バッテリ充電デバイスは、バックブーストコンバータ(buck-boost converter)を備えうる。いくつかの実施形態において、バックコンバータの誘導コンポーネントは、PCB10上において提供された外部の誘導エレメント14として提供されうる。それ故に、各バッテ

10

20

30

40

50

リ充電デバイス 102、102a、102b は、インダクタのような、対応する外部の誘導エレメント 14 に接続されうる。誘導エレメント 14 は、バッテリ充電デバイス 102、102a、102b を備える充電 IC の一部ではないという点において「外部」である。本開示にしたがって、バックコンバータの容量コンポーネントは、各バッテリ充電デバイス 102、102a、102b によって共有されることができる PCB 10 上において外部の容量エレメント 16 として提供されうる。容量エレメント 16 は、バッテリ充電デバイス 102、102a、102b を備える充電 IC の一部ではないという点において「外部」である。

#### 【0012】

[0022]さらに本開示にしたがって、各バッテリ充電デバイス 102、102a、102b は、マスターまたはスレーブモード動作のためにデバイスを構成するよう対応する外部の選択インジケータ (selection indicator) 18 に接続されうる。各選択インジケータ 18 は、デバイスを備える充電 IC の一部ではないという点において「外部」である。いくつかの実施形態において、選択インジケータ 18 は、抵抗エレメントでありうる。例えば、接地電位（例えば、およそ 0 ）への接続は、デバイス（例えば、102）はマスター モードで動作すべきであると示す役割を果たしうる。非ゼロ抵抗値（例えば、10K、100K、等）は、デバイス（例えば、102a、102b）はスレーブモードで動作すべきであると示す役割を果たしうる。より一般的には、他の実施形態において、選択インジケータ 18 は、マスター モードまたはスレーブモードで動作するかどうかをデバイス 102、102a、102b に示す役目をすることができる、適したアナログ信号またはデジタル信号のソースでありうる。

#### 【0013】

[0023]バッテリ充電デバイス 102、102a、102b に対する電力は、任意の適したコネクタ 26 を介して外部から供給されうる。単に例として、コネクタ 26 は、USB コネクタでありうる。USB コネクタの VBUS 線からの電力は、（例えば、USB IN 端子において）デバイス 102 に接続されうるが、デバイス 102 は、その後、MIDUSB IN 端子を介して他のデバイス 102a、102b に電力を分配しうる。これらおよび他の端子は、下記においてより詳細に説明される。

#### 【0014】

[0024]当業者は、本開示にしたがった実施形態が任意の電子デバイスを含みうることを認識するであろう。例えば、図 1A は、PCB 10 がバッテリ 22 を充電するために任意の電子デバイス 50 内に組み込まれることを指摘する。図 1B は、第 2 の電子デバイス内においてバッテリ 22 を充電するために第 2 の電子デバイス 56 への接続 54 を有する第 1 の電子デバイス 52 内において PCB 10 が提供されうる別の構成を例示する。いくつかの実施形態において、接続 54 は、物理的でない可能性があり、例えば、デバイス 52 からのワイヤレスエネルギー転送は、（示されていない）磁気誘導回路を使用して供給されうる。

#### 【0015】

[0025]これから論述は、本開示のいくつかの実施形態にしたがったバッテリ充電デバイス 102 の詳細へと移る。図 2 は、バッテリ充電デバイス 102 の簡略化された概略図を示す。いくつかの実施形態において、バッテリ充電デバイス 102 は、充電 IC 202 を備えうる。いくつかの実装において、充電 IC の設計が 2 つ以上の IC 上において実装されうることが認識されるであろう。論述の目的のために、しかしながら、一般性を失うことなしに单一の充電 IC の実装を仮定することができる。

#### 【0016】

[0026]充電 IC 202 は、本開示の原理にしたがったバッテリ充電機能を提供するため回路を備える。いくつかの実施形態において、例えば、バッテリ充電機能は、バックコンバータ、またはバックブーストコンバータ、等を使用して提供されうる。それ故に、充電 IC 202 は、誘導エレメント 14 および容量エレメント 16 と連動したバックコンバータトポロジで構成ができるハイサイド FET 214a およびローサイド FET 214b である。

10

20

30

40

50

T 2 1 4 b を含みうる。

**【 0 0 1 7 】**

[0027] パルス幅変調された ( PWM ) ドライバ回路は、それぞれの F E T 2 1 4 a および 2 1 4 b のゲートを切り替えるためにその切り替え出力においてゲートドライブ信号 ( H S 、 L S ) を生成しうる。 PWM ドライバ回路は、 F E T 2 1 4 a および 2 1 4 b の切り替えを制御するためにその制御入力において電流モード制御信号を、およびそのクロック入力においてクロック信号を受信しうる。バックコンバータからの電力 ( V p h \_ p w r ) は、充電 I C 2 0 2 の V S Y S および C H G O U T 端子を介してバッテリ F E T 2 2 2 を通してバッテリ 2 2 を充電するよう接続されうる。バッテリ F E T 2 2 2 は、( 例えれば、充電電流感知回路を使用して ) 充電電流をモニタする役割を果たしうる。

10

**【 0 0 1 8 】**

[0028] 本開示に原理にしたがって、制御信号は、充電 I C 2 0 2 内において内部で生成されうるか、または充電 I C に外部から供給されうる。例えば、様々なフィードバック制御ループおよび比較器 2 1 6 を備えるフィードバック補償ネットワークは、内部で生成された制御信号のソースとしての役割を果たしうる。特定の実施形態において、フィードバック制御ループは、( 例えれば、 U S B I N において入力電力を感知する ) 入力電流感知回路、( 例えれば、バッテリ F E T 2 2 2 を使用する V S Y S および C H G O U T 端子において電流を感知する ) 充電電流感知回路、( 例えれば、 V S Y S 端子において電圧を感知する ) システム電圧感知回路、( 例えれば、 V B A T T 端子においてバッテリ電圧を感知する ) バッテリ電圧感知回路、および( 例えれば、 T H E R M 端子においてバッテリ温度を感知する ) バッテリ温度感知回路を含みうる。他の実施形態において、フィードバック制御ループは、より少ない、または追加の、感知回路を備えうる。比較器 2 1 6 は、内部で生成された制御信号としての役割を果たす基準を生成しうる。

20

**【 0 0 1 9 】**

[0029] 比較器 2 1 6 によって生成された制御信号は、制御信号が充電 I C 2 0 2 を備える回路によって生成されるという点において「内部」である。比較すると、制御信号は、例えば、充電 I C の C O N T R O L 端子を介して、信号が充電 I C 2 0 2 の外部に存在するソースから受信される場合に「外部から」供給されると考慮される。いくつかの実施形態において、制御セレクタ 2 1 6 a は、 PWM ドライバ回路に対する制御信号としての役割を果たすために、比較器 2 1 6 によって生成された内部の制御信号または C O N T R O L 端子上において受信される外部で生成された制御信号のいずれかを選択するよう提供されうる。

30

**【 0 0 2 0 】**

[0030] 本開示の原理にしたがって、クロック信号は、充電 I C 2 0 2 内において内部で生成されうるか、または充電 I C に外部から供給されうる。例えば、充電 I C 2 0 2 は、クロック信号 ( クロックアウト ) を生成するためのクロック生成器 2 1 8 を含みうる。クロック生成器 2 1 8 は、クロック生成回路 2 1 8 a および 遅延エレメント 2 1 8 b を含みうる。クロック生成回路 2 1 8 a は、内部で生成されたクロック信号としての役割を果たすクロック信号を生成しうる。遅延エレメント 2 1 8 b は、外部から供給されたクロック信号を受信しうる。

40

**【 0 0 2 1 】**

[0031] クロック生成回路 2 1 8 a によって生成されたクロック信号は、クロック信号が充電 I C 2 0 2 を備える回路、すなわちクロック生成回路によって生成されるという点において「内部」である。比較すると、クロック信号は、例えば、充電 I C の C L K 端子を介して、信号が充電 I C 2 0 2 の外部に存在するソースから受信される場合に「外部から」供給されると考慮される。いくつかの実施形態において、クロックセレクタ 2 1 8 c は、 PWM ドライバ回路に対するクロック信号としての役割を果たすために、クロック生成回路 2 1 8 a によって生成された内部のクロック信号または C L K 端子上において供給される外部のクロック信号のいずれかを選択するよう提供され、遅延エレメント 2 1 8 b によって遅延 ( 位相シフト ) されうる。

50

## 【0022】

[0032]充電 I C 2 0 2 は、充電 I C の S E L 入力上において提供された外部選択インジケータ 1 8 にしたがって「マスター」モードまたは「スレーブ」モードで動作するよう充電 I C を構成するためにセレクタ回路 2 1 2 を含みうる。選択インジケータ 1 8 は、回路、またはアナログ信号のソース（例えば、アナログ信号生成器）あるいはデジタル信号のソース（例えば、デジタル論理）でありうる。いくつかの実施形態において、例えば、選択インジケータ 1 8 は、直接または抵抗エレメントを通してのいずれかの、接地電位への電子接続でありうる。セレクタ回路 2 1 2 は、選択インジケータ 1 8 にしたがって制御セレクタ 2 1 6 a およびクロックセレクタ 2 1 8 c を動作させうる。セレクタ回路 2 1 2 はまた、選択インジケータ 1 8 にしたがって電流入力の感知を有効または無効にするためにスイッチ 2 2 0 を動作させうる。

## 【0023】

[0033]本開示にしたがって、充電 I C 2 0 2 は、単相スタンドアローンデバイスとして構成されうるか、または多相構成内において使用されうる。本論述はまず、単相構成について説明する。図 3 は、スタンドアローンバッテリ充電器として動作するよう構成された充電 I C 2 0 2 の例を例示する。充電 I C 2 0 2 は、マスターモードで動作するよう S E L 入力を使用して構成されうる。いくつかの実施形態において、充電 I C 2 0 2 内におけるマスターモード動作は、接地電位への S E L 入力の接続を備える選択インジケータ 1 8 によって指定されうる。マスターモード動作を指定するためのこの慣例（convention）は、他の実施形態において、他の慣例がマスターモード動作を示すために採用されうるという理解のもと、本開示の残りの箇所に対して使用される。

## 【0024】

[0034]実施形態において、セレクタ 2 1 2 は、マスターモード動作のために充電 I C 2 0 2 を構成することによって S E L 入力における接地接続の存在に応答するよう構成されうる。例えば、セレクタ 2 1 2 は、P W M ドライバ回路の制御入力に内部で生成された制御信号を供給するために第 1 の構成内において制御セレクタ 2 1 6 a を動作させうる。内部で生成された制御信号はまた、充電 I C 2 0 2 の C O N T R O L 端子に供給されるが、それは、図 3 内において示される単相構成とは関係ない。

## 【0025】

[0035]同様に、セレクタ 2 1 2 は、P W M ドライバ回路のクロック入力に（例えば、クロック生成回路 2 1 8 a を介して）内部で生成されたクロック信号を供給するために第 1 の構成内においてクロックセレクタ 2 1 8 c を動作させうる。内部で生成されたクロック信号はまた、充電 I C 2 0 2 の C L K 端子に供給されるが、それは、図 3 内において示される単相構成とは関係ない。セレクタ 2 1 2 はまた、電力入力 U S B I N 上において入力電流感知を可能にする構成に対するスイッチ 2 2 0 を動作させうる。

## 【0026】

[0036]動作において、図 3 内において示されるマスターモード構成の充電 I C 2 0 2 は、バッテリ 2 2 を充電するためにバックコンバータとして動作する。P W M ドライバ回路に対するフィードバック制御は、充電 I C 2 0 2 を備える回路によって提供され、同様に、回路に対するクロック信号は、充電 I C 内から供給される。構成は、1 つの充電 I C しか存在しないという点において「スタンドアローン」構成である。

## 【0027】

[0037]これから論述は、本開示にしたがった充電 I C 2 0 2 の多相構成、特に二相構成の例の説明へと移る。二相構成において、2 つの充電 I C 2 0 2 は、バッテリ 2 2 を充電するためにともに接続され、動作する。充電 I C 2 0 2 のうちの 1 つは、マスターデバイスとして、もう一方はスレーブデバイスとして構成されうる。図 4 A および 4 B は、それぞれマスターデバイスとしておよびスレーブデバイスとして動作するよう構成された充電 I C 2 0 2 a および 2 0 2 b の例を示す。充電 I C 2 0 2 a、2 0 2 b は、接続部 A、B、C、D、E、F、および G においてともに接続される。結果として生じる電流フローは、フロー 4 2 2 として図 4 A および 4 B 内において例示される。

10

20

30

40

50

**【0028】**

[0038]図4A内において示される充電IC202aは、図3内において説明されるようにマスター モード動作のために構成される。本開示にしたがって、充電IC202a内における比較器216によって生成された制御信号は、充電IC内におけるPWMドライバ回路のために、内部で生成された制御信号としての役割を果たすことに加えて、(例えば、CONTROL端子を介して)外部で生成された制御信号402として供給される。同様に、クロック生成器218によって生成されたクロック信号は、充電IC202a内におけるPWMドライバ回路のために、内部で生成されたクロック信号としての役割を果たすことに加えて、(例えば、CLK端子を介して)外部で生成されたクロック信号404として供給される。

10

**【0029】**

[0039]図4Bを参照すると、充電IC202bは、スレーブモード動作のために構成される。充電IC202bは、スレーブモードで動作するようSEL入力を使用して構成されうる。いくつかの実施形態において、スレーブモード動作は、抵抗エレメントを備える選択インダクタ18によって指定されうる。スレーブモード動作を指定するためのこの慣例は、他の実施形態において、他の慣例がスレーブモード動作を示すために採用されうるという理解のもと、本開示の残りの箇所に対して使用される。特定の実施形態において、例えば、10K抵抗器は、スレーブモード動作を示すために使用されうる。別の抵抗値が使用されることは、もちろん認識されるであろう。セレクタ212は、スレーブモード動作のために充電IC202bを構成することによってSEL入力における10K抵抗の検出に応答するよう構成されうる。

20

**【0030】**

[0040]スレーブモード動作において、セレクタ212は、充電IC202bのCONTROL端子上において受信される外部で生成された制御信号402を受信するために第2の構成内において制御セレクタ216aを動作させうる。制御セレクタ216aは、PWMドライバ回路の制御入力に外部で生成された制御信号402を供給する。第2の構成内における制御セレクタ216aの動作は、PWMドライバ回路から充電IC202b内におけるフィードバックネットワークの接続を切断するか、またはそうでなければ効果的に無効にする。この「切断された接続」は、グレーに塗りつぶされた破線を使用して充電IC202b内におけるフィードバックネットワークのエレメントを例示することによって本図面内において強調される。

30

**【0031】**

[0041]充電202b内におけるセレクタ212はまた、CLK端子上において外部で生成されたクロック信号404を受信するために第2の構成内においてクロックセレクタ218cを動作させうる。クロックセレクタ218cは、遅延エレメント218bに外部で生成されたクロック信号404を供給する。PWMドライバ回路に供給されたクロック信号は、遅延エレメント218bからのものであり、したがって、充電IC202b内におけるクロック生成回路218aの接続を切断するか、またはそうでなければ効果的に無効にする。

**【0032】**

40

[0042]スイッチ220は、充電IC202bのUSBIN端子における電流感知を無効にすること(例えば、セレクタ212によって)構成されうる。ハイおよびローサイドFET214a、214bへの電力は、接続部Bを介してMIDUSBIN端子によって供給されうる。同様に、スレーブ構成の充電IC202b内における充電電流感知は、そのバッテリFET222を無効にすることによって無効にされうる。

**【0033】**

[0043]前述の説明から認識ができるように、スレーブモード充電IC202b内におけるPWMドライバ回路の動作は、マスター モード充電IC202a内において生成され、それぞれ外部で生成された制御およびクロック信号402、404としてスレーブモード充電IC202bに供給される制御信号およびクロック信号によって制御され

50

る。スレーブモード充電 I C 2 0 2 b の観点からすれば、マスター モード充電 I C 2 0 2 a 内において生成された制御およびクロック信号は、「外部で生成された」と見なされる。

#### 【 0 0 3 4 】

[0044]マスター モード充電 I C 2 0 2 a は、F E T D R V 端子上において信号をアサートすることによってスレーブモード充電 I C 2 0 2 b と同期しうる。例えば、マスター モード充電 I C 2 0 2 a が F E T D R V 端子 L O をプル (pull) する場合、スレーブモード充電 I C 2 0 2 b 内における P W M ドライバ回路は、無効にされる。マスター モード充電 I C 2 0 2 a が F E T D R V 端子 H I をプルする場合、スレーブモード充電 I C 2 0 2 b 内における P W M ドライバ回路は、切り替えを開始する。いくつかの実施形態において、F E T D R V 端子は、軽負荷および重負荷効率のバランスを取るために、入力電流がしきい値を超えた後にスレーブモード充電 I C 2 0 2 b 内において切り替えを開始するようマスター モード充電 I C 2 0 2 a によって使用されうる。例えば、軽負荷における切り替え損失は、低下した伝導損失を上回りかねないが、それは、すぐにスレーブモード充電 I C 2 0 2 b を有効にしないことによって避けることができる。有効後、スレーブモード充電 I C 2 0 2 b は、マスター モード充電 I C 2 0 2 a からのクロック信号と同期して動作するであろう。スレーブモード充電 I C 2 0 2 b 内における P W M ドライバ回路の制御は、マスター モード充電 I C 2 0 2 a からの制御信号によって提供され、したがって、マスターに、充電電流限界値、入力電流限界値、等を設定することを可能にするであろう。

#### 【 0 0 3 5 】

[0045]本開示にしたがって、遅延エレメント 2 1 8 b は、二相動作に適した選択可能である位相シフトを提供するよう（例えば、セレクタ 2 1 2 によって）構成されうる。例えば、遅延エレメント 2 1 8 b は、外部で生成されたクロック信号 4 0 4 の 1 8 0 度の位相シフトを提供しうる。それ故に、スレーブモード充電 I C 2 0 2 b 内における P W M ドライバ回路のクロック入力に供給されるクロック信号は、マスター モード充電 I C 2 0 2 a 内におけるクロック信号と比較して位相が 1 8 0 度ずれている。その結果として、マスター モード充電 I C 2 0 2 a の充電サイクルは、スレーブモード充電 I C 2 0 2 b の充電サイクルと比較して位相が 1 8 0 度ずれているであろう。例えば、ハイサイド F E T 2 1 4 a がマスター デバイス内において O N である場合、スレーブ デバイス内におけるハイサイド F E T は、O F F であり、その逆もまた然りである。

#### 【 0 0 3 6 】

[0046]これから論述は、本開示にしたがった充電 I C 2 0 2 の三相構成の説明へと移る。三相構成において、3つの充電 I C 2 0 2 は、バッテリ 2 2 を充電するためにともに接続され、動作する。充電 I C 2 0 2 のうちの1つは、マスター デバイスとして、他方の2つは、スレーブ デバイスとして構成されうる。図 5 A ~ 5 C は、それぞれ、マスター デバイス、第1のスレーブ デバイス、および第2のスレーブ デバイスとして動作するよう構成された実例的な充電 I C 2 0 2 a 、 2 0 2 b 、 および 2 0 2 c を示す。充電 I C 2 0 2 a 、 2 0 2 b 、 2 0 2 c は、接続部 A 1 、 B 1 、 C 1 、 D 1 、 E 1 、 F 1 、 および G 1 と、接続部 A 2 、 B 2 、 C 2 、 D 2 、 E 2 、 F 2 、 および G 2 とにおいて接続される。

#### 【 0 0 3 7 】

[0047]図 5 A 内におけるマスター デバイスは、図 4 A に関連して説明されたように構成される。（図 5 B および 5 C の）第1および第2のスレーブ デバイスは、図 4 B に関連して説明されたように構成される。三相動作において、第1および第2のスレーブ デバイス内における遅延エレメント 2 1 8 b は、それぞれの P W M ドライバ回路に対するクロック入力として外部で生成されたクロック信号 4 0 4 の、それぞれ、1 2 0 度および 2 4 0 度の位相シフトを提供するよう構成されうる。例えば、図 5 B の第1のスレーブ デバイス内における選択インジケータ 1 8 は、1 2 0 度の位相シフトを示す 1 0 0 K 抵抗器であり、同様に、図 5 C の第2のスレーブ デバイス内における選択インジケータ 1 8 は、2 4 0 度の位相シフトを示す 1 M 抵抗器でありうる。他の抵抗値が使用されうることは、もちろん認識されるであろう。動作において、（図 5 A の）マスター デバイスの充電サイクルは、

10

20

30

40

50

(図5Bの)第1のスレーブデバイスの充電サイクルと比較して位相が120度ずれ、(図5Cの)第2のスレーブデバイスの充電サイクルと比較して位相が240度ずれるであろう。

### 【0038】

[0048]より一般的には、N相動作が図面内において示される例にしたがってN個の充電IC(1つのマスターDEバイスおよび(N-1)のスレーブDEバイス)を使用し、それらを接続して提供されることは認識されるであろう。(N-1)のスレーブDEバイスの各々は、外部で生成された制御信号402および外部で生成されたクロック信号404をマスターDEバイスから受信する。いくつかの実施形態において、m番目のスレーブDEバイスは、そのPWMドライバ回路に対するクロック入力として外部で生成されたクロック信号404の $m \times (360 \div N)$ 度の位相シフトを(例えば、遅延エレメント218bを使用して)提供するように(例えば、適した選択インジケータ18を使用して)構成されうる。いくつかの実施形態において、量( $m \div N$ )は、360の整数倍である。10

### 【0039】

[0049]これから論述は、本開示にしたがった充電ICの別の実施形態へと移る。いくつかの実施形態において、充電ICは、マスターONリーデバイスとして実装されうる。言い換れば、充電ICは常に、マスターモードで動作し、スレーブモードとして動作するよう構成可能ではない。図6は、例えば、他のコンポーネントの中でもとりわけ、比較器616にフィードするいくつかのセンサコンポーネント(例えば、入力電流感知、充電電流感知、等)をそなえるフィードバックネットワークを備える充電IC602を示す。比較器出力は、PWMドライバ回路の制御入力にフィードする内部で生成された制御信号を生成し、それは、CONTROL端子において出力される外部で生成された制御信号622としての役割を果たす。充電IC602はさらに、内部で生成されたクロック信号を生成するクロック信号を生成するクロック618を備え、それは、PWMドライバ回路のクロックインにフィードし、それは、CLK端子において出力される外部で生成されたクロック信号624としての役割を果たす。充電ICのこの特定の実施形態は常に、その内部で生成された制御およびクロック信号を使用し、常にそれぞれ外部で生成された制御およびクロック信号としてそれらの信号を出力する。そのため、充電IC602は、より小さく、より低成本なデバイスを実現するために、セレクタ212と、セレクタ216a、218b、および220と、遅延エレメント218bとを省略することができる。20

### 【0040】

[0050]いくつかの実施形態において、充電ICは、スレーブONリーデバイスとして実装されうる。図7は、例えば、(例えば、CONTROL端子から)外部で生成された制御信号722のみを受信する制御入力を有するPWMドライバ回路を備える充電IC702を示す。PWMドライバ回路はさらに、(例えば、CLK端子から)外部で生成されたクロック信号724のみを受信するクロック入力を有する。セレクタ712は、選択インジケータ18にしたがって外部で生成されたクロック信号724の位相シフティングを提供するために遅延エレメント718を構成する役割を果たす。例えば、遅延エレメント718は、セレクタ712に何が接続されているかに依存して外部で生成されたクロック信号の $m \times (360 \div (M + 1))$ 度の位相シフトを提供するよう構成され、ここにおいて、mは、充電IC702が合計M個のスレーブDEバイスの中でm番目のスレーブDEバイスであると識別する。30

### 【0041】

[0051]充電IC702は、その制御およびクロック信号を内部で生成せず、むしろ充電ICの外部に存在するソースからそれらを取得するという点において「スレーブONリーダー」である。制御信号およびクロック信号が常に外部で生成されることから、スレーブONリーダー充電IC702は、フィードバックネットワークおよびクロックを備える回路を省略することができる。同様に、スレーブONリーダー充電IC702は、デバイスが入力電流を感じ取る必要がないことから、入力FETおよびバッテリFETを省略することができる。これは、特に入力およびバッテリFETがダイ上においてかなりのエリアを占有するこ4050

とができる電力FETであることから、より小さいデバイスおよび／またはより低コストなデバイスに関して有利であることができる。

#### 【0042】

[0052]いくつかの実施形態において、スレーブオンリー充電IC702は、性能を向上させるために追加の回路を含みうる。例示されていないが、例えば、スレーブオンリー充電ICは、ピーク電流制限のためにインダクタ電流感知回路を含みうる。別の例として、スレーブオンリー充電ICは加えて、接合部温度が最大動作限界値を上回らないことを確実にするために熱ループを含みうる。

#### 【0043】

[0053]これから論述は、デュアル入力二相マスタースレーブ構成の説明へと移る。図8A、8B、および8Cを参照すると、本開示にしたがった充電ICはさらに、FETCTR端子を含みうる。図8Aは、デュアル入力マスターとして構成された充電IC802aを示す。特定の実施形態において、例えば、デュアル入力マスター構成は、100K抵抗器を備える選択インジケータ18で示されうる。図8Bは、スレーブモードで動作する、デュアル入力スレーブとして構成された充電IC802bを示す。図8Cは、マスター モードで動作する充電IC802bを示す。特定の実施形態において、デュアル入力スレーブ構成は、200K抵抗器を備える選択インジケータ18を使用して示されうる。本構成は、2つの電圧入力が存在するという点において「デュアル入力」である。例えば図8A～8C内において例示されるように、第1の電圧入力（例えば、USBIN）は、デュアル入力マスター802aに接続され、第2の電圧入力（例えば、DCIN）は、DCINFET812を介してデュアル入力スレーブ802bに接続されうる。10

#### 【0044】

[0054]動作において、デュアル入力マスター802aのUSBIN端子上において電圧が存在する場合、デュアル入力構成の充電IC802aおよび802bは、上記で説明されたようにマスター／スレーブモードで動作する。例えば、デュアル入力マスター802aは、マスターによって使用され、CONTROL端子を介して（図8Bの）スレーブに供給されるフィードバック制御信号802を生成する。同様に、デュアル入力マスター802aは、マスターによって使用され、CLK端子を介してスレーブに供給されるクロック信号804を生成する。図8B内において示されるデュアル入力スレーブ802bは、そのPWMドライバ回路を制御するために外部から供給された制御信号802およびクロック信号804を使用する。加えて、デュアル入力マスター802aは、デュアル入力スレーブ802bに接続されたDCINFET812をOFFにするためにFETCTRをアサートする（例えば、HIGHになる）。これは、デュアル入力スレーブ802bのUSBIN（DCIN）端子から（存在する場合に）DCIN電圧ソースを電気的に隔離する役割を果たす。デュアル入力マスター820aは、スレーブモードで動作するためにデュアル入力スレーブ802bにシグナリングするようFETDRVをアサートする（例えば、HIGHをプルする）。

#### 【0045】

[0055]デュアル入力マスター802aのUSBIN端子上において電圧が存在しない場合、マスターは、バッテリ充電を遂行しない。デュアル入力マスター802aは、DCIN電圧ソースからの電流フローを可能するためにDCINFET812をONにするようFETCTRをアサートする（例えば、LOWになる）であろう。デュアル入力スレーブ802bは、そのUSBIN端子上において提供されたDCIN入力を使用してバッテリ充電を遂行するためにマスター モードで動作する。デュアル入力スレーブ802bのこのマスター動作モードは、図8C内において例示される。とりわけ、デュアル入力スレーブ802bは、デュアル入力マスター802aがバッテリ充電を遂行していないことから、そのCONTROLおよびCLK端子上において外部の制御信号またはクロック信号を受信しない。代わりに、デュアル入力スレーブ802bは、それ自体の制御およびクロック信号を生成し、マスター モードでDCINからのバッテリ充電を遂行する。40

#### 【0046】

50

20

30

50

[0056] これから論述は、2つの電圧ソース入力のために構成された本開示の充電ICを、マスター・デバイスとして、使用する多相マスタースレーブ構成の説明へと移る。図9は、スレーブモード動作のために構成された充電IC904で構成されたデュアル入力充電IC902を例示する。境界ボックス(bounding box)900は、デバイス904およびデバイス902の一部が図4Aおよび4B内において例示されるように構成されることを示すために使用される。いくつかの実施形態において、デバイス902は、常にマスター・モードで動作するよう構成されうる。デバイス904は、スレーブがオン・ザ・ゴー(OTG: on-the-go)モードで動作しうることを示すために1kΩ抵抗器を備える選択インジケータで構成されうる。

## 【0047】

10

[0057] 動作において、USBINから充電する場合、デバイス902、904は、前述の実施形態において説明されたようにバッテリ22の多相充電を提供するためにマスター/スレーブモードで動作しうる。しかしながら、デバイス902がDCINから充電している場合、デバイス904は、OTGモードで動作するようシグナリングされうる。例えば、デバイス904は、集積回路間(I<sup>2</sup>C: Inter-Integrated Circuit)通信プロトコルを介してコマンドを受信するために(示されていない)インターフェース回路を含みうる。任意の他の適したシグナリングが使用されうることは、もちろん認識されるであろう。

## 【0048】

20

[0059] OTGモードにおいて、デバイス904は、直接USBIN端子にバッテリ22から電力を供給する。図9は、動作のこの「OTG」モードの2つの異なる電流フロー912、914を例示する。フロー912は、バッテリ22を充電するためのデュアル入力充電IC902からの充電電流を表す。フロー914は、バッテリ22からデバイス902のUSBIN端子への電流を表す。デバイス902からの制御およびクロック信号は、そのそれぞれのCONTROLおよびCLK端子上において供給されうるが、信号は、OTGモードのデバイス904によって使用されないことに留意されたい。

利点および技術的効果

## 【0049】

30

[0059] 本開示にしたがう充電回路は、多数のバッテリ充電の並列化を考慮する。各バッテリ充電器は、自身の誘導エレメントに接続され、従って、より小さいインダクタの使用を考慮することによって改善された温度性能のための機会(opportunity)を生成する。加えて、より小さいインダクタは、より小さいパッケージングフットプリント(packaging footprints)を考慮する。多数のバッテリ充電器は、電流共有を考慮するので、バッテリ充電の間の電力負荷を分配する。各バッテリ充電器が他のバッテリ充電器に対して異相で動作するので、バッテリは、リップルを低減した充電電流を「見る」。

## 【0050】

[0060] 本開示にしたがう実施形態の別の利点は、システム設計における柔軟性である。各バッテリ充電器は、単層スタンドアローン構成中でまたは2つまたは2つより多くのデバイスの多相構成中で使用されうる。

## 【0051】

40

[0061] 追加の柔軟性は、より大きい電力管理IC中にマスター・デバイスを組み込むことによって実現されることができる。特定のユーザは、その際、それらのシステムに、1つまたは複数のスレーブとして構成されるデバイスを単に追加することによって多相構成を設計しうる。

## 【0052】

[0062] 上記の説明は、どのように特定の実施形態の態様が実装されうるかの例とともに、本開示の様々な実施形態を例示する。上記の例は、唯一の実施形態であると見なされるべきではなく、以下の特許請求の範囲によって定義される特定の実施形態の柔軟性および利点を例示するために提示された。上記の開示および以下の特許請求の範囲に基づいて、他の配置、実施形態、実装および同等物が、特許請求の範囲によって定義される本開示の

50

範囲から逸脱することなしに用いられる。

**[0053]**

[0063]特許請求の範囲は以下の通りである。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

**[C 1]**

バッテリ充電器のための回路であって、

制御入力と、クロック入力と、誘導エレメントに接続するように構成されるスイッチング出力とを有するスイッチング回路と、

バッテリ端子に接続されたバッテリを充電するように電力を提供するために前記バッテリ端子に前記誘導エレメントを電気的に接続するように構成される充電端子と、

制御端子と、

クロック端子と、

前記スイッチング回路の前記制御入力および前記制御端子に内部で生成された制御信号を供給する第1の構成で動作することと、前記スイッチング回路の前記制御入力に前記制御端子上で受信された外部で生成された制御信号を供給する第2の構成で動作することとを行うように構成される制御セレクタと、

前記スイッチング回路の前記クロック入力および前記クロック端子に内部で生成されたクロック信号を供給する第1の構成で動作することと、前記スイッチング回路の前記クロック入力に前記クロック端子上で受信された外部で生成されたクロック信号を供給する第2の構成で動作することとを行うように構成されたクロックセレクタと

を備える、回路。

**[C 2]**

前記スイッチング回路の前記スイッチング出力に接続された第1のFETと第2のFETとをさらに備え、前記第1のFETは、前記第2のFETに接続され、前記第1のFETと前記第2のFETとは、前記制御入力上で受信した制御信号と前記クロック入力上で受信したクロック信号とにしたがう前記スイッチング回路によってONとOFFが切り替えられる、

[C 1]に記載の回路。

**[C 3]**

前記クロック入力に前記クロック端子上で受信された外部で生成されたクロック信号を供給するために、前記クロック入力と前記クロック端子との間に前記クロックセレクタによって選択的に接続されることができる遅延エレメントをさらに備える、

[C 1]に記載の回路。

**[C 4]**

前記遅延エレメントは、前記外部で生成されたクロック信号の選択可能な位相シフトを提供するように構成される、

[C 3]に記載の回路。

**[C 5]**

前記内部で生成されたクロック信号を生成するクロック信号生成器と、遅延エレメントとをさらに備え、

前記クロックセレクタは、前記第1の構成で動作するとき、前記スイッチング回路の前記クロック入力および前記クロック端子に前記クロック信号生成器を接続し、

前記クロックセレクタは、前記第2の構成で動作するとき、前記クロック入力に前記クロック端子上で受信された外部で生成されたクロック信号を供給するために、前記クロック端子と前記クロック入力との間に前記遅延エレメントを接続する、

[C 1]に記載の回路。

**[C 6]**

前記遅延エレメントは、前記外部で生成されたクロック信号の位相シフトを生成するように構成される、

10

20

30

40

50

[ C 5 ] に記載の回路。

[ C 7 ]

前記内部で生成された制御信号を生成する制御信号生成器をさらに備え、

前記制御セレクタは、前記第1の構成で動作するとき、前記スイッチング回路の前記制御入力および前記制御端子に、前記制御信号生成器を接続し、

前記制御セレクタは、前記第2の構成で動作するとき、前記制御入力に前記制御端子上で受信した外部で生成された制御信号を提供するために前記制御入力に前記制御端子を接続する、

[ C 1 ] に記載の回路。

[ C 8 ]

10

外部選択インジケータに接続するように構成されるセレクタ入力をさらに備え、前記制御セレクタと前記クロックセレクタは、前記選択インジケータに依存する前記第1または第2の構成において動作する、

[ C 1 ] に記載の回路。

[ C 9 ]

前記遅延エレメントは、前記選択インジケータに依存する前記外部で生成されたクロック信号の位相シフトを生成するように構成される、

[ C 8 ] に記載の回路。

[ C 10 ]

20

前記外部選択インジケータは、デジタル信号である、

[ C 8 ] に記載の回路。

[ C 11 ]

前記外部選択インジケータは、アナログ信号である、

[ C 8 ] に記載の回路。

[ C 12 ]

前記外部選択インジケータは、1つまたは複数の抵抗エレメントを備える、

[ C 8 ] に記載の回路。

[ C 13 ]

制御端子と、

クロック端子と、

30

ハイサイドFETおよびローサイドFETと、

前記ハイサイドFETおよび前記ローサイドFETを駆動するためのPWMドライバと、

複数の制御ループを備えるフィードバック回路、前記フィードバック回路は、制御信号を生成する、と、

クロック生成器と遅延エレメントとを備えるクロックモジュール、前記クロックモジュールは、前記PWMドライバに提供されるクロック信号を生成する、と、

第1の構成または第2の構成における前記充電回路を構成する選択モジュールとを備え、前記第1の構成において、前記制御信号は、前記PWMドライバに、そして前記制御端子に供給され、前記クロック信号は、前記クロック生成器から生成され、

前記第2の構成において、前記制御端子上で受信した外部で生成された制御信号は、前記PWMドライバに供給され、前記クロック端子上で受信した外部で生成されたクロック信号は、前記遅延エレメントに供給され、前記クロック信号は、前記遅延エレメントの出力である、

充電回路。

[ C 14 ]

前記遅延エレメントは、選択可能な位相シフトを提供する、

[ C 13 ] に記載の充電回路。

[ C 15 ]

40

前記第1の構成において、前記クロック信号は、前記遅延エレメントから生成されず、

50

前記第2の構成において、前記クロック信号は、前記クロック生成器から生成されない、

[C13]に記載の充電回路。

[C16]

前記第1の構成において、前記フィードバック回路によって生成され、前記制御端子上で供給される前記制御信号は、外部で生成された制御信号としての役割を果たす、

[C13]に記載の充電回路。

[C17]

前記第1の構成において、前記クロックモジュールによって生成され、前記クロック端子上で供給される前記クロック信号は、外部で生成されたクロック信号としての役割を果たす、

[C13]に記載の充電回路。

10

[C18]

ハイサイドFETとローサイドFETとを駆動するためのPWMドライバと、

遅延エレメントと、

第1の入力ピン上で受信した外部で供給される制御信号を前記PWMドライバに提供する、前記PWMドライバに接続された前記第1の入力ピンと、

第2の入力ピン上で受信した外部で供給されるクロック信号を前記遅延エレメントに提供するために、前記遅延エレメントに接続された前記第2の入力ピンと

を備え、前記遅延エレメントは、前記PWMドライバに提供される遅延クロック信号を供給するために前記クロック信号を遅延する、

20

充電回路。

[C19]

前記PWMドライバへの前記制御信号は、前記外部で供給された制御信号によってのみ供給される、

[C18]に記載の充電回路。

[C20]

前記PEMドライバへの前記クロック信号は、前記外部で供給されたクロック信号からのみ生じる、

[C18]に記載の充電回路。

【図1】

Fig. 1

【図1A】

Fig. 1A

【図1B】

Fig. 1B

【図2】

Fig. 2

【図3】

Fig. 3

【図 4 A】

Fig. 4A

【図 4 B】

Fig. 4B

【図 5 A】

Fig. 5A

【図 5 B】

Fig. 5B

【図 5 C】

Fig. 5C

【図 6】

Fig. 6

【図 7】

Fig. 7

【図 8 A】

Fig. 8A

【図 8 B】

**Fig. 8B**

【図 8 C】

Fig. 8C

【図9】

Fig. 9

---

フロントページの続き

(74)代理人 100184332

弁理士 中丸 慶洋

(72)発明者 スポルック、クリスチャン・ジー.

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 ガーシア、ジオバンニ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 ハワウニ、シャディ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 猪瀬 隆広

(56)参考文献 特開2011-147269(JP,A)

特開2007-116853(JP,A)

特開平08-065911(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02J 7/00 - 7/12

H02J 7/34 - 7/36

H02M 3/00 - 3/44

H01M 10/42 - 10/48