(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5877246号

(P5877246)

(45) 発行日 平成28年3月2日(2016.3.2)

(24) 登録日 平成28年1月29日(2016.1.29)

|                |           |

|----------------|-----------|

| (51) Int.Cl.   | F 1       |

| HO 1 L 21/8247 | (2006.01) |

| HO 1 L 27/115  | (2006.01) |

| HO 1 L 21/336  | (2006.01) |

| HO 1 L 29/788  | (2006.01) |

| HO 1 L 29/792  | (2006.01) |

請求項の数 19 (全 13 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-526134 (P2014-526134)  |

| (86) (22) 出願日 | 平成24年8月14日 (2012.8.14)        |

| (65) 公表番号     | 特表2014-522131 (P2014-522131A) |

| (43) 公表日      | 平成26年8月28日 (2014.8.28)        |

| (86) 國際出願番号   | PCT/US2012/050796             |

| (87) 國際公開番号   | W02013/025719                 |

| (87) 國際公開日    | 平成25年2月21日 (2013.2.21)        |

| 審査請求日         | 平成27年8月3日 (2015.8.3)          |

| (31) 優先権主張番号  | 13/211,033                    |

| (32) 優先日      | 平成23年8月16日 (2011.8.16)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595168543<br>マイクロン テクノロジー, インク.<br>アメリカ合衆国, アイダホ州 83716<br>-9632, ボイズ, サウス フェデ<br>ラル ウエイ 8000 |

| (74) 代理人  | 100106851<br>弁理士 野村 泰久                                                                        |

| (74) 代理人  | 100074099<br>弁理士 大菅 義之                                                                        |

| (72) 発明者  | テッサリオル, パオロ<br>イタリア共和国, ヴェネト州 31044<br>, モンテベッルーナ, ヴィア ガツィエ<br>56                             |

最終頁に続く

(54) 【発明の名称】異なる少数キャリア寿命を有するチャネル領域を含む装置および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の終端と第2の終端とを有する、細長いチャネル領域があつて、

前記細長いチャネル領域は、前記第1の終端に位置する第1の再結合領域と、前記第2の終端に位置する第2の再結合領域と、前記第1の再結合領域と前記第2の再結合領域との間に挟まれた本体領域と、を含み、

前記細長いチャネル領域を覆う電荷蓄積構造と、

前記電荷蓄積構造を介して前記本体領域と相対する複数のメモリセルゲートと、

前記電荷蓄積構造を介して前記第1の再結合領域と相対する第1の選択ゲートと、

前記電荷蓄積構造を介して前記第2の再結合領域と相対する第2の選択ゲートと、

前記第1の終端で、前記第1の再結合領域に隣接して連結されるソース領域と、

前記第2の終端で、前記第2の再結合領域に隣接して連結されるドレイン領域と、をさらに備え、

前記第1の再結合領域および前記第2の再結合領域の少なくとも1つは、前記本体領域とは異なる格子歪み状態を有する、

ことを特徴とする装置。

## 【請求項 2】

前記第1の再結合領域および前記第2の再結合領域の少なくとも1つは、前記本体領域とは異なる格子歪み状態を有すると共に、前記本体領域とは異なるドーピング濃度を有する、請求項1に記載の装置。

## 【請求項 3】

前記第 1 の再結合領域および前記第 2 の再結合領域の少なくとも 1 つを、前記本体領域とは異なる半導体材料で構成することにより、前記本体領域と異なる格子歪み状態とする、請求項 1 に記載の装置。

## 【請求項 4】

前記第 1 の再結合領域および前記第 2 の再結合領域の少なくとも 1 つの格子内に不純物元素を導入することにより、前記本体領域とは異なる格子歪み状態とする、請求項 1 に記載の装置。

## 【請求項 5】

前記細長いチャネル領域は p 型にドープされ、前記ソース領域および前記ドレイン領域は n 型にドープされ、前記第 1 の再結合領域および前記第 2 の再結合領域の前記少なくとも 1 つは、前記本体領域よりも高濃度にドープされる、請求項 1 に記載の装置。 10

## 【請求項 6】

前記電荷蓄積構造は、誘電体層を含む、請求項 1 に記載の装置。

## 【請求項 7】

前記装置は、NAND メモリストリングのアレイを備える、請求項 1 に記載の装置。

## 【請求項 8】

前記装置は、前記 NAND メモリストリングのアレイを備えるメモリデバイスに連結されたプロセッサをさらに備える、請求項 7 に記載の装置。 20

## 【請求項 9】

前記プロセッサに連結された表示デバイスをさらに備える、請求項 8 に記載の装置。

## 【請求項 10】

互いに連結された再結合領域および本体領域と、

前記再結合領域に連結され、前記本体領域と反対方向に延在する 1 つのソースドレイン領域と、

前記再結合領域および前記本体領域を覆う電荷蓄積構造と、

前記電荷蓄積構造を介して前記再結合領域と相対する選択ゲートと、

前記電荷蓄積構造を介して前記本体領域と相対する複数のメモルセルゲートと、を含み、

前記再結合領域は、前記本体領域とは異なる格子歪み状態を有する、ことを特徴とする装置。 30

## 【請求項 11】

前記再結合領域は、前記本体領域とは異なる格子歪み状態を有すると共に、前記本体領域とは異なるドーピング濃度を有する、請求項 10 に記載の装置。

## 【請求項 12】

前記再結合領域を、前記本体領域とは異なる半導体材料で構成することにより、前記本体領域と異なる格子歪み状態とする、請求項 10 に記載の装置。

## 【請求項 13】

前記本体領域は、「U」形を形成する、請求項 10 に記載の装置。

## 【請求項 14】

前記再結合領域の格子内に不純物元素を導入することにより、前記本体領域とは異なる格子歪み状態とする、請求項 10 に記載の装置。 40

## 【請求項 15】

メモリストリングを形成する方法であって、

ソース領域およびドレイン領域を形成することと、

前記ソース領域および前記ドレイン領域の間に連結される細長いチャネル領域を形成することと、

前記細長いチャネル領域を覆う電荷蓄積構造を形成することと、

前記細長いチャネル領域の少なくとも 1 つの終端を含み、前記ソース領域および前記ドレイン領域のいずれか一方と隣接する終端部分を形成することと、 50

前記終端部分と相対する選択ゲートを形成することと、を含み、

前記細長いチャネル領域の前記終端部分は、前記細長いチャネル領域の他の部分とは異なる格子歪みを有する、方法。

**【請求項 16】**

ソース領域およびドレイン領域を形成することは、n型にドープされたソース領域およびドレイン領域を形成することを含み、細長いチャネル領域を形成することは、p型にドープされた細長いチャネル領域を形成することを含む、請求項15に記載の方法。

**【請求項 17】**

終端部分を形成することは、ドープされたポリシリコンを、前記細長いチャネル領域の前記他の部分を形成するために用いられるよりも高いドーパント濃度で蒸着して前記終端部分を形成することを含む、請求項15に記載の方法。

10

**【請求項 18】**

終端部分を形成することは、前記細長いチャネル領域の前記他の部分を形成するために用いられるよりも高いドーパント濃度でドーパントを注入して前記終端部分を形成することを含む、請求項15に記載の方法。

**【請求項 19】**

終端部分を形成することは、前記終端部分の格子内にドーパント元素とは異なる不純物元素を導入することを含む、請求項15に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

20

**【0001】**

<優先権出願>

本願は、2011年8月16日に出願された米国出願番号13/211,033に対する優先権を主張し、これは参考により全体として本願に組み込まれる。

**【背景技術】**

**【0002】**

より高密度なメモリデバイスは、常に需要がある。メモリデバイスを半導体チップの表面上に横方向に形成すると、多大なチップ面積を使用する。旧来のメモリデバイスを超える、メモリ密度をさらに高めるための、新しい構成による改良されたメモリデバイスが必要とされる。

30

**【図面の簡単な説明】**

**【0003】**

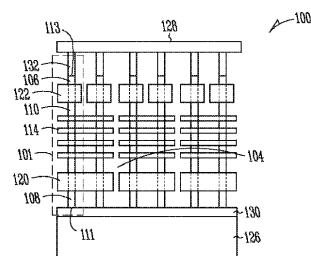

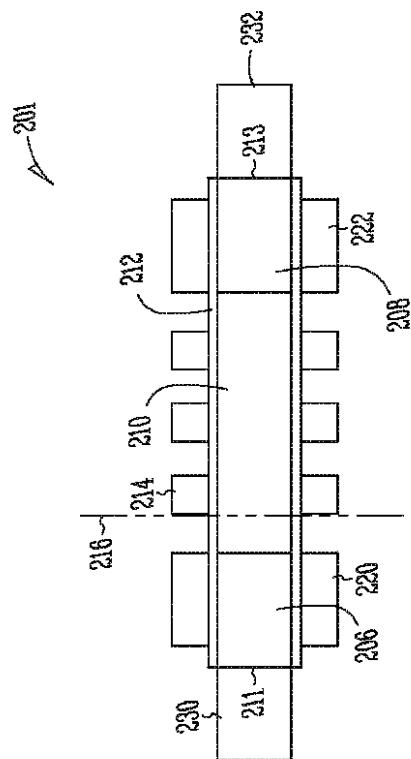

【図1A】本発明の実施形態による、メモリデバイスを示す。

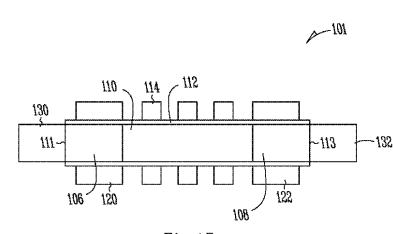

【図1B】本発明の実施形態による、図1Aからのメモリストリングのブロック図を示す。

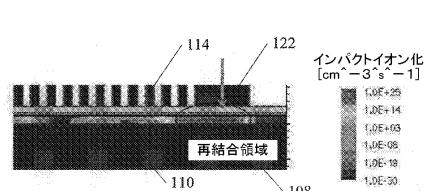

【図1C】本発明の実施形態による、メモリストリングの動作におけるキャリア発生のモデルを示す。

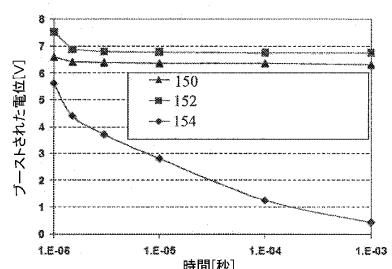

【図1D】本発明の実施形態による、メモリストリングの動作におけるキャリア発生のモデルを示す。

【図2】本発明の実施形態による、メモリストリングのチャネル領域についての電位時間グラフを示す。

40

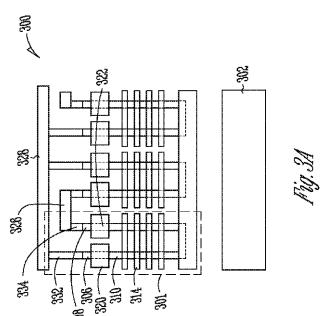

【図3A】本発明の実施形態による、別のメモリデバイスを示す。

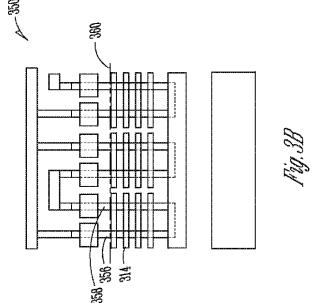

【図3B】本発明の実施形態による、別のメモリデバイスを示す。

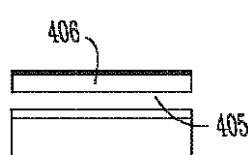

【図4A】本発明の実施形態による、メモリデバイスのための処理オペレーションを示す。

【図4B】本発明の実施形態による、メモリデバイスのための処理オペレーションを示す。

【図4C】本発明の実施形態による、メモリデバイスのための処理オペレーションを示す。

【図4D】本発明の実施形態による、メモリデバイスのための処理オペレーションを示す。

50

- 。【図4E】本発明の実施形態による、メモリデバイスのための処理オペレーションを示す

- 。【図4F】本発明の実施形態による、メモリデバイスのための処理オペレーションを示す

- 。【図4G】本発明の実施形態による、メモリデバイスのための処理オペレーションを示す

- 。【図4H】本発明の実施形態による、メモリデバイスのための処理オペレーションを示す

- 。【図4I】本発明の実施形態による、メモリデバイスのための処理オペレーションを示す

10

- 。【図5】本発明の実施形態による、メモリデバイスを用いた情報取扱いシステムを示す。

#### 【発明を実施するための形態】

##### 【0004】

以下の本発明の詳細な説明において、本願の一部を形成する添付の図面に対する参照がなされ、そこで説明のために、本発明が実施され得る具体的な実施形態が示される。これらの実施形態は、当業者が本発明を実施することができるよう、十分に詳細に説明される。他の実施形態が利用されてもよく、および、論理的、電気的変更等がなされ得る。

##### 【0005】

図1Aは、基板102上に形成された、メモリデバイス100の形の装置を示す。図1Bは、図1Aからのメモリストリング101を示す。電荷蓄積構造112（例えば、トンネル誘電体、ポリシリコン、および電荷ブロッキング材料の組み合わせ、窒化物、酸化物、および窒化物の組み合わせ、または現在知られているか、もしくは将来開発される、電荷蓄積機能を提供することができるあらゆる他の材料の組み合わせ）は、図1Bに示すように、細長いチャネル領域110を実質的に取り囲み、複数のメモリセルゲート114（これはまた細長いチャネル領域110および電荷蓄積構造（複数可）112の各々の横断面を実質的に取り囲み得る）のそれぞれに対応する各々の電荷蓄積構造を形成する。電荷蓄積構造は、単一の構造の各々の複数の部分であってもよく、または複数の分離した別々の構造から成ってもよい。

20

##### 【0006】

第1の選択ゲート120および第2の選択ゲート122は、細長いチャネル領域110をソース領域130およびドレイン領域132に各々選択的に連結するように示される。誘電体104は、上述のもの等のコンポーネントの間の空間を埋めることができる。

30

##### 【0007】

一例では、細長いチャネル領域110は、p型および/または非ドープポリシリコン等の半導体材料から形成される。細長いチャネル領域110は、第1の終端111が第2の終端113および/または中間部分等の細長いチャネル領域110の他の部分を形成するために用いられるものとは異なるポリシリコン蒸着活動で形成されるように、複数のプロセス活動において形成されることができる。ソース領域130およびドレイン領域132は、細長いチャネル領域110の第1の終端111および第2の終端113に各々連結されて示される。一例では、ソース領域130およびドレイン領域は、n+ポリシリコン等のn型半導体材料を含む。

40

##### 【0008】

動作中、ソース領域130、細長いチャネル領域110、およびドレイン領域132を備えるバスは、途中の信号伝送を可能にする（または阻害する）ように動作する選択ゲート120、122、メモリセルゲート114を持つn-p-nトランジスタとして働く。コンポーネントは、まとまってメモリストリング101を形成する、ソース領域130、細長いチャネル領域110、ドレイン領域132、選択ゲート120、122、電荷蓄積構造112、およびメモリセルゲート114を備える。一例では、メモリストリングは、回路の中に構成され、NANDメモリストリングとして動作する。

50

## 【0009】

ビット線 128 等のソース線 126 およびデータ線は、ソース領域 130 およびドレン領域 132 に各々連結されて示される。ソース線 126 およびビット線 128 は、アルミニウム、銅、もしくはタンゲステン等の金属、またはこれらもしくは他の導体金属の合金を含むか、それらから成るか、または基本的にそれらから成ることができる。本開示において、「金属」という用語は、金属窒化物、または主に導体として動作する他の金属をさらに含む。

## 【0010】

図 1B は、図 1A からのメモリストリング 101 のブロック図を示す。図に示されるいくつかのメモリセルゲート 114 は、説明のみを目的とする。一例では、メモリストリング 101 は、選択ゲート 120、122 の間に 8 個のメモリセルゲート 114 を備える。

10

## 【0011】

チャネル領域 110 は、図 1A および図 1B に示すように、第 1 の再結合領域 106、および第 2 の再結合領域 108（および第 1 の再結合領域と第 2 の再結合領域との間の本体領域）を含むことができる。第 1 の再結合領域 106 および第 2 の再結合領域 108 は、細長いチャネル領域 110 の一部として形成され、かつ同一の導電型のものであることができる。一例では、第 1 の再結合領域 106 および第 2 の再結合領域 108 は、細長いチャネル領域 110 の本体領域の少数キャリア寿命よりも低い少数キャリア寿命を有するように構成される。一例では、第 1 の再結合領域 106 および第 2 の再結合領域 108 は、実質的に類似の構成に形成され、実質的に同一の少数キャリア寿命を有する。一例では、第 1 の再結合領域 106 および第 2 の再結合領域 108 は、異なる少数キャリア寿命を有し、両方の少数キャリア寿命は、細長いチャネル領域 110 の本体領域の少数キャリア寿命よりも低い。

20

## 【0012】

いくつかの構成および関連付けられる形成のプロセスが、第 1 の再結合領域 106 および第 2 の再結合領域 108 について可能である。一例では、第 1 の再結合領域 106 および第 2 の再結合領域 108 は、本体領域 110 よりも高濃度にドープされ、より低い少数キャリア寿命を提供する。一例では、細長いチャネル領域（第 1 の再結合領域 106 および第 2 の再結合領域 108 を備える）は、p 型ドーパントでドープされる。p 型ドーパントの例は、ホウ素、アルミニウム、ガリウム、およびインジウムを含むがこれらに限定されない。

30

## 【0013】

ドーピング濃度の一例は、約  $5 \times 10^{18}$  原子 /  $\text{cm}^3$  またはそれ以上の濃度にドープされる第 1 の再結合領域 106 および第 2 の再結合領域 108 を持つ、約  $1 \times 10^{18}$  原子 /  $\text{cm}^3$  の濃度にドープされる細長いチャネル領域 110 の本体領域を含む。第 1 の再結合領域 106 および第 2 の再結合領域 108 におけるより高いドーピング濃度は、細長いチャネル領域 110 の本体領域におけるものよりも低い少数キャリア寿命をもたらす。別の例は、非ドープの本体領域 110 よりも高い実効濃度にドープされる第 1 の再結合領域 106 および第 2 の再結合領域 108 を持つ、非ドープである細長いチャネル領域 110 を含む。

40

## 【0014】

複数のメモリセルゲート 114 の外側の領域におけるより低い少数キャリア寿命は、メモリ動作の間に細長いチャネル領域 110 のより良い選択的隔離を提供するはずである。例えば、消去動作の間、消去のためにストリング 101 が選択され得る。この場合、他のストリング 101 が隔離されることが望ましい。第 1 の再結合領域 106 および第 2 の再結合領域 108 において少数キャリア寿命を低くすることにより、電荷が選択されていないストリングを貫流しづらくなり、そしてより高いパフォーマンスとともに、メモリ動作がより信頼性の高いものとなる。

## 【0015】

図 1C は、細長いチャネル領域 110、再結合領域 108、およびメモリセルゲート 1

50

14のモデル例を示す。図は、衝突イオン化領域において、抑止条件の間、消去動作等の動作において、選択されていないストリングについて、キャリア発生が電位降下によって維持されていることを示す。本発明の実施形態の適用なしでは、ブーストされたチャネルが短時間でその電位を失い得る。例えば、図1Dは、再結合領域を持たないデバイスのためのチャネル領域電位154を示す。図からわかるように、チャネル領域電位154は時間とともに低下する。本発明の実施形態によるドーパント加工例を用いると、チャネル領域電位152が同一の期間で維持されることがわかっている。

【0016】

第1の再結合領域106および第2の再結合領域108についての他の構成および関連付けられる形成のプロセスは、歪みエンジニアリングおよび代替的な材料の選択を含む。歪みエンジニアリングの例では、ドーパント元素を含む可能性があるか、または含まない可能性がある不純物元素が、第1の再結合領域106および第2の再結合領域108内の格子の内部へと注入されるか、または別様に導入される。不純物元素（複数可）の追加によって格子に提供された歪みは、領域を修正し（すなわち、本体領域とは異なる格子歪み状態を有する領域をもたらす）、これは細長いチャネル領域110の本体領域よりも低い少数キャリア寿命を有する領域をもたらす。

【0017】

代替的な材料の例では、第1の再結合領域106および第2の再結合領域108は、細長いチャネル領域110の本体領域を形成するために用いられるものとは異なる半導体材料から形成される。材質の選択の異なる特性は、再結合領域106、108において、細長いチャネル領域110の本体領域におけるよりも低い少数キャリア寿命をもたらす。図1Dは、材料を工夫した例のモデル例を示す。図からわかるように、材料を工夫した例についてのチャネル領域電位150は、経時的に維持されるように示される。

【0018】

一例では、第1の再結合領域106および第2の再結合領域108は、それぞれ少なくとも選択ゲート122、120内部の各々の位置から（領域106の場合）および/または個々の位置へ（領域108の場合）伸張する。図1Bは、第1の再結合領域106および第2の再結合領域108がそれぞれ、選択ゲート122、120の各々の縁部から、および/または縁部まで伸張する例を示す。

【0019】

図2は、メモリストリング201を示す。メモリストリング201は、その間に細長いチャネル領域210が連結されたソース領域230およびドレイン領域232を備える。細長いチャネル領域210に隣接し、いくつかの電荷蓄積構造212によって細長いチャネル領域210から分離されたいくつかのメモリセルゲート214が示される。第1の選択ゲート220は、細長いチャネル領域210の第1の終端211に配置され、および第2の選択ゲート222は、細長いチャネル領域210の第2の終端213に配置される。

【0020】

細長いチャネル領域210は、第1の再結合領域206および第2の再結合領域208（ならびに第1のおよび第2の再結合領域206、208の間の細長い本体領域）を備える。一例では、第1の再結合領域206および第2の再結合領域208は、選択ゲート220、222の縁部の前および/または越えたそれぞれの位置からおよび/または位置へと各々伸張する。図2に示される例では、第1の再結合領域206は、選択ゲート220の縁部の前の位置から伸張し（例えば、これはメモリセルゲート214の縁部216から伸張する）、第2の再結合領域208は、選択ゲート222の縁部を越えた位置まで伸張する（例えば、これはメモリセルゲート214の別の縁部217まで伸張する）。

【0021】

図1A、図1B、および図2は、垂直配向のメモリストリングを図示する。水平および「U」形を含む他の構成もまた可能である。図3Aおよび図3Bは、「U」形メモリストリングの例を図示する。図3Aは、その間に連結された細長いチャネル領域310および細長いチャネル領域310の長さに沿って位置するいくつかのメモリセルゲート314を

10

20

30

40

50

持つ、ソース領域 332 およびドレイン領域 334 を備えるメモリストリング 300 を示す。示される構成において、ソース領域 332 およびドレイン領域 334 は、上向きであり、細長いチャネル領域 310 が「U」形を形成している。

【0022】

図 3 A で、細長いチャネル領域 310 は、第 1 の再結合領域 306 および第 2 の再結合領域 308 ( およびその間の本体領域 ) を備える。一例では、第 1 の再結合領域 306 および第 2 の再結合領域 308 は、より高濃度のドーピング、歪みエンジニアリング、または細長いチャネル領域 310 の本体領域を形成するために用いられるものとは異なる材料選択を用いて上述のとおりに形成される。

【0023】

図 3 A は、第 1 の選択ゲート 320 および第 2 の選択ゲート 322 の各々の縁部から各々伸張する、第 1 の再結合領域 306 および第 2 の再結合領域 308 を示す。図 3 B は、第 1 の選択ゲート 320 および第 2 の選択ゲート 322 の各々の縁部の前の位置から伸張する ( 例えば、いくらかのゲート 314 の縁部 360 からそれぞれ伸張する ) 第 1 の再結合領域 356 および第 2 の再結合領域 358 を持つ、類似のメモリストリング 350 を示す。

【0024】

上述の図に関連して記載されたように、垂直、水平、および「U」形等のメモリストリングの数個の異なる構成が可能である。以下の図 4 A ~ 図 4 I は、垂直メモリストリングを形成するために用いられることのできるプロセスの例を説明する。本プロセスは、他の構成と合わせて、前述の構成を形成するための一般的指針として用いられることができる。

【0025】

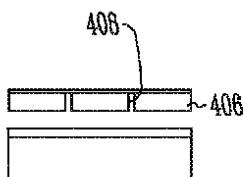

図 4 A は、基板 402 の一部上の n 型にドープされた領域 404 の形成を示す。一例では、基板 402 の一部分がソース線を形成する。一例では、 n 型にドープされた領域 404 は、 n + になるように、高濃度にドープされる。図 4 B で、誘電体層 405 が形成され、ポリシリコン 406 の層が形成される。

【0026】

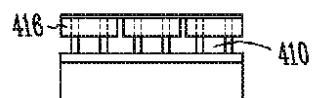

図 4 C で、ポリシリコン 406 には、パターニングおよびエッチングをし、ポリシリコン 406 を部分的に隔離する開口 408 を形成する。図 4 D で、第 1 の選択ゲート 416 を形成するポリシリコン 406 の一部を通じて第 1 の再結合領域 410 が形成される。一例では、第 1 の再結合領域 410 は、ドープしたポリシリコンとして蒸着される。他の例では、第 1 の再結合領域 410 のための材料が蒸着され、続いて拡散、イオン注入、または他のドーピング方法等によってドープされる。一例では、第 1 の再結合領域 410 は、 p + になるように、高濃度にドープされる。一例では、第 1 の再結合領域 410 は、約  $5 \times 10^{18}$  原子 / cm<sup>3</sup> のドーパント濃度を含む。

【0027】

一例では、第 1 の再結合領域 410 は、歪みエンジニアリングによって形成される。歪みエンジニアリングの一例は、ポリシリコン構造を形成することと、第 1 の再結合領域 410 の格子を歪ませて第 1 の再結合領域 410 内の少数キャリア寿命を修正する不純物元素を注入するか、または別様にともに形成することとを含む。

【0028】

一例では、第 1 の再結合領域 410 は、続いて形成される細長いチャネル領域の本体領域 412 よりも低い少数キャリア寿命を有する材料から形成される。一例では、第 1 の再結合領域 410 のための材料選択は、ガリウムヒ素、ゲルマニウム等の非シリコン半導体を含む。

【0029】

図 4 D に示される例では、第 1 の再結合領域 410 は、ドープされた領域 404 からポリシリコン 406 を通り、第 1 の選択ゲート 416 の縁部まで伸張する。他の例では、図 2 に示されるように、第 1 の再結合領域 410 は、第 1 の選択ゲート 416 の縁部を越え

10

20

30

40

50

いくつかのメモリセルゲートの縁部まで伸張する。多くの実施形態では、第1の再結合領域410は、複数の処理オペレーションにおいて形成される細長いチャネル領域の一部である。

【0030】

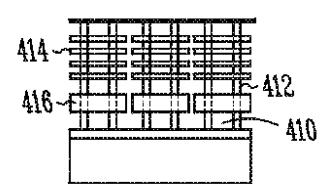

図4Eは、細長いチャネル領域の本体領域412の形成、および細長いチャネル領域の本体領域412の長さに沿ったいくつかのメモリセルゲート414の形成を示す。一例では、本体領域412はp型にドープされているが、他の例では異なるようにドープされるか、または非ドープであってもよい。一例では、領域412は、約 $1 \times 10^{-8}$ 原子/cm<sup>3</sup>のp型ドーパント濃度を含む。前述のとおり、本体領域412は、複数の処理オペレーションにおいて形成される細長いチャネル領域の一部である。

10

【0031】

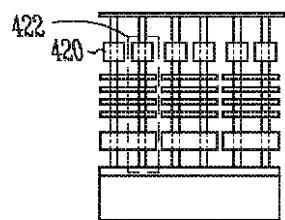

図4Fは、別のポリシリコン層418の形成を示す。図4Gで、ポリシリコン層418は、パターニングおよびエッチングされて第2の選択ゲート420を形成する。示される例では、それぞれの第2の選択ゲート420が個別のメモリストリング422の専用である一方で、第1の選択ゲート416は、2つの隣接するストリング422によって共有される。他の例は、メモリデバイス構成の要件に応じ、共有される第2の選択ゲート420および個別の第1の選択ゲート420の組み合わせを含む。

【0032】

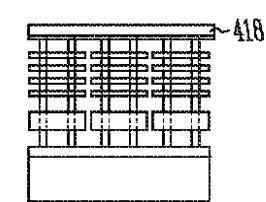

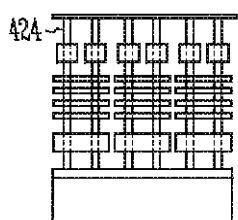

図4Hで、第2の再結合領域424は、第2の選択ゲート420を通って形成される。第1の再結合領域410と同じく、一例では、第2の再結合領域424は、ドープされたポリシリコンとして蒸着される。他の例では、第2の再結合領域424のための材料が蒸着され、続いて拡散、イオン注入、または他のドーピング方法等によってドープされる。一例では、第2の再結合領域424は、p+になるように、高濃度にドープされる。一例では、第2の再結合領域424は、約 $5 \times 10^{-8}$ 原子/cm<sup>3</sup>のドーパント濃度を含む。歪みエンジニアリング、または第1の再結合領域410の場合と同じく材料選択等の他の例が第2の再結合領域424内で用いられることができ、細長いチャネル領域の本体領域412よりも低い少数キャリア寿命を提供する。

20

【0033】

図4Hに示される例では、第2の再結合領域424は、第2の選択ゲート420の縁部から伸張する。他の例では、図2に示すように、第2の再結合領域424は、いくつかのメモリセルゲート414の縁部から伸張する。前述のとおり、第2の再結合領域424は、複数の処理オペレーションにおいて形成される細長いチャネル領域の一部分である。

30

【0034】

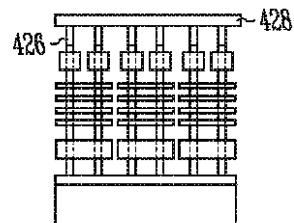

図4Iで、第2の再結合領域424に接続されるように、n型にドープされた領域426が形成される。細長いチャネル領域がp型にドープされた領域である実施形態では、n型にドープされた領域426、細長いチャネル領域（第2の再結合領域424、本体領域412、および第1の再結合領域410を含む）、およびn型にドープされた領域404は、メモリストリングとして機能するn-p-n接合を形成する。最後に、図4Iで、データ線428（例えばビット線）が形成され、メモリストリングと接続し、メモリデバイスを形成する。

40

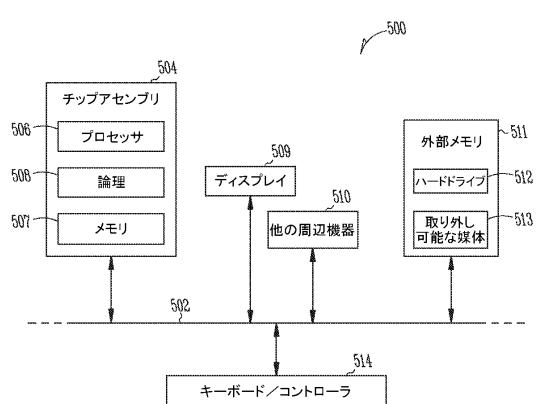

【0035】

コンピュータ等の情報取扱いシステムの形をとる装置の実施形態は図5に含まれ、高レベルなデバイス応用の本発明のための実施形態を示す。図5は、上記に記載の本発明の実施形態による1つ以上のメモリデバイス507を組み込んだ、情報取扱いシステム500のブロック図である。情報取扱いシステム500は、そこで本発明のメモリデバイスが用いられることができる、電子システムの単なる一実施形態である。他の例は、タブレットコンピュータ、カメラ、携帯情報端末（PDA）、携帯電話、MP3プレーヤ、航空機、衛星、軍用車両等を含むがこれらに限定されない。

【0036】

本例では、情報取扱いシステム500は、システムの種々のコンポーネントを連結する

50

システムバス 502 を備えるデータ処理システムを備える。システムバス 502 は、情報取扱いシステム 500 の種々のコンポーネント間に通信リンクを提供し、単一のバス、バスの組み合わせ、またはあらゆる他の適切な手法において実装され得る。

【0037】

チップアセンブリ 504 は、システムバス 502 に連結される。チップアセンブリ 504 は、あらゆる回路または動作可能に互換性のある組み合わせの回路を含み得る。一実施形態では、チップアセンブリ 504 は、あらゆる種類であることができるプロセッサ 506 を備える。本願において用いられる「プロセッサ」とは、マイクロプロセッサ、マイクロコントローラ、グラフィックプロセッサ、デジタル信号プロセッサ (DSP)、またはあらゆる他の種類のプロセッサまたはプロセッサ回路等を含むがこれらに限定されない、あらゆる種類の計算回路を意味する。

10

【0038】

一実施形態では、メモリデバイス 507 は、チップアセンブリ 504 内に含まれる。一実施形態では、メモリデバイス 507 は、上記に記載の実施形態による NAND メモリデバイス等のメモリデバイスを備える。本願に記載のプロセスによって形成されたメモリデバイス 507 は、別個のデバイスまたはチップとして一体化され (プロセッサ 506 および / または論理 508 と組み合わされてチップアセンブリ 504 の一部を形成しない)、バス 502 に連結されてもよい。

【0039】

一実施形態では、チップアセンブリ 504 内にプロセッサチップの他に追加的な論理チップ 508 が含まれる。プロセッサの他の論理チップ 508 の例は、アナログ・デジタル変換器を備える。本発明の一実施形態では、カスタム回路、特定用途向け集積回路 (ASIC) 等の論理チップ 508 上の他の回路もまた含まれる。

20

【0040】

情報取扱いシステム 500 はまた、外部メモリ 511 を含んでもよく、外部メモリ 511 は、1 つ以上のハードドライブ 512 等の、特定の用途に適した 1 つ以上のメモリ要素および / またはコンパクトディスク (CD)、フラッシュドライブ、デジタルビデオディスク (DVD)、および同等のもの等の取り外し可能な媒体 513 を取扱う 1 つ以上のドライブを含むことができる。上記の例において説明されるように、構成される半導体メモリダイは、おそらくメモリ 511 の一部として情報取扱いシステム 500 内に含まれる。

30

【0041】

情報取扱いシステム 500 はまた、モニタまたはタッチスクリーン等の表示デバイス 509、スピーカ等の追加の周辺コンポーネント 510、およびキーボードおよび / またはコントローラ 514 を含んでもよく、これらはマウス、タッチスクリーン、トラックボール、ゲームコントローラ、声認識デバイス、またはシステムユーザが情報取扱いシステム 500 に情報を入力し、およびこのシステムから情報を受信することを許可する、あらゆる他のデバイスを含み得る。

【0042】

本願において使用される「水平な」という用語は、ウエハまたはダイ等の従来型の平面または基板の表面に、基板の配向に関わらず、平行な平面として定義される。「垂直な」という用語は、上記で定義された水平に対して直角の向きを指す。「~上の」、「側」(「側壁」に見られる)、「より高い」、「より低い」、「上方の」、「下方の」等の前置詞は、基板の配向に関わらず、基板の表面の頂面にある従来型の平面または表面に関して定義される。以下の詳細な説明は、したがって、制限的な意味に捉えられず、かつ本発明の範囲は、添付の請求項によってのみ、かかる請求項が権利を有する均等物の全体の範囲とあわせて画定される。

40

【0043】

本発明のいくつかの実施形態が記載されたが、上記の列挙は網羅的であることを意図するものではない。本願において具体的な実施形態が説明され記載されているが、同一の目的を達成するために計画されたあらゆる配置が、示された具体的な実施形態の代わりとな

50

り得るということは、当業者には認識されるであろう。本願は、本発明のあらゆる適合または変形を含めることを意図する。上記の記述は説明的であることを意図し、制限的であることを意図しないことが理解されるものとする。上記の実施形態および他の実施形態の組み合わせは、上記の説明を閲読すれば当業者には明白となるであろう。

【図 1 A】

Fig. 1A

【 1 B 】

Fig. 1B

【図1C】

【図 1 D】

【図2】

Fig. 2

【図3 A】

Fig. 3A

【図3 B】

Fig. 3B

【図4 A】

Fig. 4A

【図4 B】

Fig. 4B

【図4 C】

Fig. 4C

【図4 D】

Fig. 4D

【図4 E】

Fig. 4E

【図4 F】

Fig. 4F

【図4G】

Fig. 4G

【図4I】

Fig. 4I

【図4H】

Fig. 4H

【図5】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/10 (2006.01)

(72)発明者 マウリ, オウレリオ, ジャンカルロ

イタリア共和国, ロンバルディア州 20036, メーダ, ヴィア アルノ 20

(72)発明者 合田 晃

アメリカ合衆国, アイダホ州 83706, ボイズ, イースト モントレー ドライブ 1818

(72)発明者 チャオ, イージェ

アメリカ合衆国, アイダホ州 83709, ボイズ, ウエスト K-バー-T ドライブ 108

74

審査官 小山 満

(56)参考文献 特開2008-147664 (JP, A)

特開2011-070730 (JP, A)

特開2007-180389 (JP, A)

特開2010-199312 (JP, A)

米国特許出願公開第2008/0135912 (US, A1)

米国特許出願公開第2011/0075481 (US, A1)

米国特許出願公開第2007/0158736 (US, A1)

米国特許出願公開第2010/0213538 (US, A1)

特開2010-199235 (JP, A)

特開2010-114370 (JP, A)

特開2010-114369 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/8247

H 01 L 21/336

H 01 L 27/10

H 01 L 27/115

H 01 L 29/788

H 01 L 29/792