(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5779213号

(P5779213)

(45) 発行日 平成27年9月16日(2015.9.16)

(24) 登録日 平成27年7月17日(2015.7.17)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

H02M 3/155E

Y

請求項の数 27 (全 17 頁)

(21) 出願番号 特願2013-204019 (P2013-204019)

(22) 出願日 平成25年9月30日 (2013.9.30)

(65) 公開番号 特開2014-87252 (P2014-87252A)

(43) 公開日 平成26年5月12日 (2014.5.12)

審査請求日 平成25年10月1日 (2013.10.1)

(31) 優先権主張番号 61/715,947

(32) 優先日 平成24年10月19日 (2012.10.19)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 13/710,127

(32) 優先日 平成24年12月10日 (2012.12.10)

(33) 優先権主張国 米国(US)

(73) 特許権者 593219551

リニア テクノロジー コーポレイション

Linear Technology Corporation

アメリカ合衆国 カリフォルニア 950

35, ミルピタス, マッカーシー ブール

バード 1630

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】スイッチングレギュレータにおける磁場キャンセル

## (57) 【特許請求の範囲】

## 【請求項 1】

入力電圧を受け取り、かつ調整出力を生成するスイッチングレギュレータ回路であって、前記回路は、

トランジスタスイッチ制御信号を生成するコントローラ(19)と、

前記コントローラによって制御される第1のスイッチ(14A)であって、前記コントローラは、調節可能なデューティサイクルにおける単一のスイッチングサイクルの間、前記第1のスイッチが導電状態と非導電状態との間でスイッチされるように制御して、前記スイッチングレギュレータ回路の前記調整出力を制御し、前記デューティサイクルは、前記第1のスイッチが前記単一のスイッチングサイクルの間に導電状態にある時間のパーセンテージである、第1のスイッチ(14A)と、

前記第1のスイッチを有するカレントループの一部として、前記第1のスイッチへ連結された第1のバイパスコンデンサ(20A)と、

前記第1のスイッチ(14A)と並列に接続された第2のスイッチ(14B)であって、前記第2のスイッチは、前記第1のスイッチと同じデューティサイクルを有するように前記第1のスイッチと同じ状態にあるように前記コントローラによって制御されて、前記スイッチングレギュレータ回路の前記調整出力を制御する、第2のスイッチ(14B)とを含み、

前記第1のスイッチは、導電状態へとスイッチされると、第1のカレントループ(25)を発生させるように位置付けられ、第1の電流は、前記第1のカレントループにおいて

10

20

第1の方向に流れて第1の磁場を生成し、前記第1の磁場は、第1の大きさを第1の方向に有し、

前記第2のスイッチは、導電状態へとスイッチされると、第2のカレントループ(24)を発生させるように位置付けられ、第2の電流は、前記第2のカレントループにおいて第2の方向に流れて第2の磁場を生成し、前記第2の方向は前記第1の方向と反対方向であり、前記第2の磁場は、第2の大きさを第2の方向に有し、これにより、前記第1の磁場および前記第2の磁場が協働して、前記スイッチングレギュレータ回路によって発生した電磁干渉(EMI)を低減する、回路。

【請求項2】

前記第1の大きさは、前記第2の大きさとほぼ同じである、請求項1に記載の回路。 10

【請求項3】

スイッチングレギュレータ回路であって、前記回路は、

トランジスタスイッチ制御信号を生成するコントローラ(19)と、

前記コントローラによって制御される少なくとも第1のスイッチ(12)であって、前記第1のスイッチのデューティサイクルは、前記スイッチングレギュレータ回路の調整出力を制御し、前記コントローラは、調節可能なデューティサイクルにおける単一のスイッチングサイクルの間、前記第1のスイッチが導電状態と非導電状態との間でスイッチされるように制御して、前記スイッチングレギュレータ回路の前記調整出力を制御し、前記デューティサイクルは、前記第1のスイッチが前記単一のスイッチングサイクルの間に導電状態にある時間のパーセンテージである、少なくとも第1のスイッチ(12)と、 20

前記第1のスイッチを有するカレントループの一部として、前記第1のスイッチへ連結された第1のバイパスコンデンサ(20)と、

前記第1のスイッチのスイッチングによって同時に発生させられる少なくとも第1のカレントループ(52)および第2のカレントループ(54)であって、第1の電流は、前記第1のカレントループにおいて第1の方向に流れて第1の磁場を生成し、前記第1の磁場は、第1の大きさを第1の方向に有し、第2の電流は、前記第2のカレントループにおいて第2の方向に流れて第2の磁場を生成し、前記第2の方向は前記第1の方向と反対方向であり、前記第2の磁場は、第2の大きさを第2の方向に有し、これにより、前記第1の磁場および前記第2の磁場が協働して、前記スイッチングレギュレータ回路によって発生した電磁干渉(EMI)を低減する、少なくとも第1のカレントループ(52)および第2のカレントループ(54)と、 30

前記第1のスイッチの第1の端子と前記第1のバイパスコンデンサの第1の端子との間に接続された第1の導体(55)と、

前記第1のバイパスコンデンサの第2の端子と基準電圧との間に接続された第2の導体と

を含み、

前記第1の導体および前記第2の導体は相互に交差して、電流を互いに反対方向に伝導する前記第1のカレントループおよび前記第2のカレントループを形成するように8字型形状を形成し、

前記第1のカレントループおよび前記第2のカレントループは、同一平面上にあり、かつ、相互に横方向にずらされている、回路。 40

【請求項4】

前記8字型形状は、前記第1のバイパスコンデンサ(20)の下側に交差点を形成することによって構築される、請求項3に記載の回路。

【請求項5】

前記回路は、第3のスイッチ(12)をさらに含み、

前記第1のスイッチ(14A)および前記第2のスイッチ(14B)は、前記第3のスイッチの対向する側に置かれ、これにより、前記第1のスイッチおよび前記第3のスイッチ内へ流れる前記第1の電流によって前記第1のカレントループ(25)を発生させ、前記第2のスイッチおよび前記第3のスイッチ内に流れる前記第2の電流によって前記第2

のカレントループ (24) を発生させる、請求項 1 に記載の回路。

【請求項 6】

前記第 1 のスイッチ (14A) および第 2 のスイッチ (14B) がオンであり、かつ前記第 3 のスイッチ (12) がオフになると、前記第 1 の電流が前記第 1 のスイッチを通じて前記第 3 のスイッチの寄生コンデンサ内へと流れ、前記第 2 の電流が前記第 2 のスイッチを通じて前記第 3 のスイッチの前記寄生コンデンサ内へと流れ、請求項 5 に記載の回路。

【請求項 7】

前記第 1 のバイパスコンデンサ (20A) は、前記第 3 のスイッチ (12) と前記第 1 のスイッチ (14A) との間に連結され、前記第 1 のバイパスコンデンサは前記第 1 のカレントループ (25) の一部である、請求項 5 に記載の回路。

10

【請求項 8】

前記第 3 のスイッチ (12) と前記第 2 のスイッチ (14B) との間に連結された第 2 のバイパスコンデンサ (20B) をさらに含み、前記第 2 のバイパスコンデンサは、前記第 2 のカレントループ (24) の一部である、請求項 7 に記載の回路。

【請求項 9】

前記第 1 のバイパスコンデンサ (50) も前記第 3 のスイッチと前記第 2 のスイッチとの間に連結され、前記第 1 のバイパスコンデンサも前記第 2 のカレントループ (24) の一部である、請求項 7 に記載の回路。

【請求項 10】

20

前記第 1 のバイパスコンデンサ (50) は、前記第 1 のスイッチおよび前記第 2 のスイッチから実質的に等距離となるように、前記第 1 のスイッチ (14A) と前記第 2 のスイッチ (14B) との間に対称に設置される、請求項 9 に記載の回路。

【請求項 11】

前記回路は、同時に伝導するように並列接続された第 3 のスイッチ (12A) および第 4 のスイッチ (12B) をさらに含み、前記第 3 のスイッチは前記第 1 のスイッチ (14A) に対向して位置付けられ、前記第 4 のスイッチ (12B) は前記第 2 のスイッチ (14B) に対向して位置付けられ、前記第 4 のスイッチは前記第 3 のスイッチに隣接し、前記第 1 のスイッチは前記第 2 のスイッチに隣接し、前記第 1 のカレントループ (30) を、前記第 1 のスイッチおよび前記第 3 のスイッチ内へと流れる前記第 1 の電流によって発生させ、前記第 2 のカレントループ (32) を、前記第 2 のスイッチおよび前記第 4 のスイッチ内へと流れる前記第 2 の電流によって発生させる、請求項 1 に記載の回路。

30

【請求項 12】

前記第 1 のスイッチ (14A) および第 2 のスイッチ (14B) がオンになり、かつ前記第 3 のスイッチ (12A) および第 4 のスイッチ (12B) がオフになると、前記第 1 の電流は、前記第 1 のスイッチを通じて前記第 3 のスイッチの寄生コンデンサ内へと流れ、前記第 2 の電流は、前記第 2 のスイッチを通じて前記第 4 のスイッチの前記寄生コンデンサ内へと流れ、請求項 11 に記載の回路。

【請求項 13】

40

前記第 1 のバイパスコンデンサ (34) は、前記第 3 のスイッチ (12A) と前記第 1 のスイッチ (14A) との間に連結され、前記第 1 のバイパスコンデンサは前記第 1 のカレントループ (30) の一部である、請求項 11 に記載の回路。

【請求項 14】

前記第 4 のスイッチ (12B) と前記第 2 のスイッチ (14B) との間に連結された第 2 のバイパスコンデンサ (36) をさらに含み、前記第 2 のバイパスコンデンサは、前記第 2 のカレントループ (32) の一部である、請求項 13 に記載の回路。

【請求項 15】

前記回路は、同時にスイッチされ、かつ前記第 1 のスイッチ (14A) と前記第 2 のスイッチ (14B) のスイッチングに対向してスイッチされるように並列接続された第 3 のスイッチ (12A) および第 4 のスイッチ (12B) をさらに含み、

50

前記第1のスイッチおよび前記第2のスイッチは、スイッチからなる対向する対を発生させるために、前記第3のスイッチおよび前記第4のスイッチに対向して位置付けられ、

前記対向する対は、複数のカレントループを発生させ、前記複数のカレントループは、前記第1のカレントループ(30)および前記第2のカレントループ(32)を含み、いくつかのカレントループは、前記カレントループのうち他のカレントループと反対方向に流れて、反対方向の複数の磁場を発生させ、これにより、前記スイッチングレギュレタ回路によって生成されたEMIを低減させる、請求項1に記載の回路。

【請求項16】

前記第1のバイパスコンデンサ(34)を含む複数のバイパスコンデンサ(34, 36)をさらに含み、前記バイパスコンデンサのうち関連付けられたバイパスコンデンサは、前記第1のスイッチ、前記第2のスイッチ、前記第3のスイッチ、および前記第4のスイッチの間に連結されて、前記カレントループを形成する、請求項15に記載の回路。 10

【請求項17】

少なくとも4つのカレントループ(24A, 24B, 25A, 25B)を、前記第1のカレントループ(24A)および前記第2のカレントループ(24B)と、第3のカレントループ(25A)および第4のカレントループ(25B)とを含んで発生させ、前記第3のカレントループ中の電流の方向は、前記第4のカレントループ中の電流の方向と反対方向である、請求項16に記載の回路。

【請求項18】

前記第1のカレントループ(25)および前記第2のカレントループ(24)は平面状であり、前記第1のスイッチ(14A)および前記第2のスイッチ(14B)が形成された基板表面に対して実質的に平行である、請求項1に記載の回路。 20

【請求項19】

前記第1のカレントループ(60)および前記第2のカレントループ(62)は垂直コンポーネントを有し、前記垂直コンポーネントは、前記第1のスイッチ(14A)および前記第2のスイッチ(14B)が形成された基板表面に対して非平面状である、請求項1に記載の回路。

【請求項20】

前記第1のバイパスコンデンサ(70)は、前記第1のスイッチ(14A)および前記第2のスイッチ(14B)と非平面状である、請求項19に記載の回路。 30

【請求項21】

前記第1のスイッチ(14A)および前記第2のスイッチ(14B)はMOSFETである、請求項1に記載の回路。

【請求項22】

前記第1のスイッチ(14A)および前記第2のスイッチ(14B)は、集積回路チップ(46, 58)上に形成される、請求項1に記載の回路。

【請求項23】

前記集積回路チップ(46)は、交互またはインターリープ配置された外部端子を前記第1のスイッチ(14A)および前記第2のスイッチ(14B)に対して有する、請求項22に記載の回路。 40

【請求項24】

前記集積回路チップ(46)は、前記第1のスイッチ(14A)および前記第2のスイッチ(14B)に対して2組の外部端子を有し、1組が前記集積回路パッケージの各側部にある、請求項22に記載の回路。

【請求項25】

前記集積回路チップ(46)は、前記チップを収容する集積回路パッケージの外部にある複数のコンデンサ(20, 48, 50)を利用して、前記第1のスイッチ(14A)および前記第2のスイッチ(14B)の前記端子全てまたはその一部へと接続する、請求項22に記載の回路。

【請求項26】

50

前記集積回路チップ(46)は、前記チップを収容する集積回路パッケージの内部にある複数のコンデンサを利用して、いくつかの位置において前記第1のスイッチ(14A)および前記第2のスイッチ(14B)へと接続する、請求項22に記載の回路。

【請求項27】

前記第1のスイッチ(14A)および前記第2のスイッチ(14B)は、端子を有する同一パッケージ中に収容され、前記第1のバイパスコンデンサ(48)が前記パッケージの外部にある前記端子へ接続されたときに前記第1のカレントループおよび前記第2のカレントループが形成されるように、前記端子が前記パッケージ上に配置される、請求項1に記載の回路。

【発明の詳細な説明】

10

【技術分野】

【0001】

本出願は、仮出願シリアル番号第61/715,947号(出願日:2012年10月19日、名称:「Magnetic Field Cancellation In Switching Regulators」、Leonard Shtargotら)からの優先権を主張する。本明細書中、同文献を参考のため援用する。

【0002】

本発明は、スイッチングレギュレータに関し、詳細には、高周波スイッチングにより発生する磁場に起因する電磁干渉(EMI)を低減するための技術に関する。

【背景技術】

20

【0003】

スイッチングレギュレータは典型的には、100KHz ~ 5MHzの周波数において切り替わる。小型カレントループがこのような高速で発生した場合、大磁場の発生の原因となり得る。集積回路(IC)内に形成されたスイッチの場合、カレントループがIC全体内において発生するか、ICの内部において部分的にまたは外部において部分的に発生し得る。電源スイッチ閉鎖または同期整流器スイッチ閉鎖に起因してループが初期過渡電流を伝導した場合、比較的高いd i / d tに起因して高磁場が発生し、その結果電磁干渉(EMI)が発生し得る。

【0004】

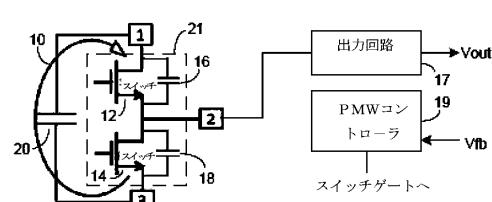

図1Aは、スイッチング電源内の従来技術のカレントループ10を示す。このカレントループ10の場合、ループ(例えば、トランジスタ、ワイヤ/トレース、コンデンサ、寄生など)を形成している回路全体は磁場を増加させて、その結果EMIが発生する。スイッチ12および14をMOSFETとして図示しているが、スイッチ12および14は他の任意の種類のスイッチ(例えば、バイポーラトランジスタ)であってもよい。スイッチ12および14はnチャネルMOSFETとして図示しているが、用途に応じてCMOSトランジスタを用いてもよい。スイッチの寄生容量16および18を図示している。

30

【0005】

本例において、スイッチ12および14を同期的に切り換えて、端子1での電源電圧(Vcc)を出力端子2へ接続した後、端子3での対地電圧を出力端子2へと接続する交互接続を行うと仮定する。バックレギュレータ内の出力回路17の一部として、インダクタ(図示せず)を端子2へ接続することができる。レギュレータの一例において、PWMコントローラIC19を2つのスイッチ12および14のゲートに接続して、調整電圧Voutまたは調整電流を出力するスイッチデューティサイクルを制御する。デューティサイクルを制御することで、レギュレータの出力電圧に比例するフィードバック電圧Vfbを発生させて、基準電圧に整合させる。これらのスイッチのうちの1つを電源スイッチと呼び、他方は同期整流器である。同期整流器は、本質的に低電圧降下ダイオードとして機能する。短絡を回避するため、スイッチ12および14は同時にオンにされない。

40

【0006】

レギュレータは、任意の種類(例えば、バック、ブースト、フライバックなど)でよく、スイッチ12および14のインダクタへの特定の接続は、レギュレータの種類によって

50

決定される。本発明は、任意の種類のスイッチングレギュレータにおいて用いることが可能であり、本発明を標準的なバックレギュレータスイッチング構成に適用した場合のコンセプトを例示するために、特定の例を示す。

【0007】

図1A中、従来のバイパスコンデンサ20が端子1と端子3との間に接続された様子が図示される。バイパスコンデンサは典型的には、従来技術のスイッチング回路において使用される。端子1がVccへ接続されかつ端子3が接地されていると仮定した場合、スイッチ12および14が開閉する際、バイパスコンデンサ20は過渡電流を平滑化する。例えば、レギュレータコントローラがスイッチ12を閉鎖してインダクタを充電した場合、端子2を介してインダクタへ接続されている充電されたコンデンサ20により、サージ電流が発生する。これにより、サージ電流に起因するVccの降下全てのオフセットが支援され、スイッチング過渡電流が平滑化される。コンデンサ20は、端子2、3および1の周囲のカレントループの一部を形成する。スイッチ12および14の寄生容量16および18もカレントループの一部であり、スイッチ14がオフにされスイッチ12がオンにされると、寄生コンデンサ18が充電する。

【0008】

理解されるように、スイッチング周波数において、超高速かつ高電流パルス(高di/dt)がループ10を通じて発生する。このパルスによってEMIが発生し、近隣電気回路と干渉し得るか近隣電気回路中の歪みの原因となり得る。

【0009】

スイッチ12および14は、IC21内にあり得、PWMコントローラIC19の一部となり得る。

【0010】

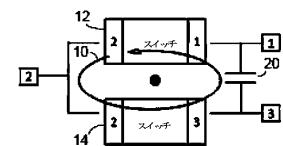

図1Bは、図1Aの回路の別の図であり、プリント基板(PCB)上またはICパッケージ内のトランジスタスイッチ位置を示す。端子1、2および3は、ICパッケージから伸びたピンの接続ノードであり得る。カレントループ10は、反時計回り方向に流れる過渡電流を示し、この過渡電流に起因して、磁場方向が上方向となる(黒丸で図示)。磁場は、全ての方向において放射状に広がって、特定のパターンを形成する。

【0011】

必要とされているのは、EMI低減のために、スイッチングレギュレータによって生成される磁場全体を低減するための技術である。

【発明の概要】

【発明が解決しようとする課題】

【0012】

本発明は、大幅に低減した磁場全体を生成するスイッチングレギュレータである。磁場は、スイッチ電流を迅速に変化させることと関連付けられる。

【課題を解決するための手段】

【0013】

本発明の技術は、従来技術の単一の磁気ループを分割して、(それぞれが高周波数スイッチを組み入れる)複数の磁気ループとする。これら複数のループは、連結された対向する磁場を有する。これらの連結された対向する磁場は相互にキャンセルし合うため、従来技術の設計と比較して、磁場全体およびEMIが大幅に低減することになる。

【0014】

本発明の磁場キャンセル技術は、スイッチモード電源内の平面スイッチング回路および三次元(3D)スイッチング回路双方に適用することが可能である。平面構造は、集積回路およびプリント基板を含む。3D構造は、積層(垂直配向)ループコンポーネントと、積層集積回路要素と、積層プリント基板とを含む。

【0015】

一実施形態において、上側電源スイッチおよび同期整流器スイッチ(下側スイッチ)を以下のように分割および配置する。平面の実施形態において、下側スイッチを分割して、

10

20

30

40

50

並列動作する 2 つの同一の下側スイッチとし、下側スイッチを上側スイッチの他方側上に配置する。第 1 のバイパスコンデンサを第 1 の下側スイッチと上側スイッチとの間に接続し、第 2 のバイパスコンデンサを第 2 の下側スイッチと上側スイッチとの間に接続する。この構成は本質的に鏡像であり、上側スイッチが中間にある。上側スイッチがオンされた直後を想定した場合、カレントループは上側スイッチおよび第 1 の下側スイッチを通じて反時計回りとなり、カレントループは上側スイッチおよび第 2 の下側スイッチを通じて時計回りとなる。発生するこれら 2 つの磁場の方向は、反対方向である。これらのループは極めて密接しているため、これらの発生した磁場は実質的にキャンセルされるため、レギュレータから放射状に広がる磁場全体が大幅に低減し、その結果 E M I が低減する。

## 【0016】

10

本技術は、上側スイッチを分割することにも適用することができる。第 1 の一対の上側スイッチおよび下側スイッチにより、第 1 のカレントループが 1 方向に発生し、第 2 の一対の上側スイッチおよび下側スイッチにより、第 2 のカレントループが反対方向に発生して、キャンセル磁場が発生する。

## 【0017】

別の実施形態において、上側スイッチおよび下側スイッチを分割して、4 つの下側スイッチおよび 2 つの上側スイッチとする。これらの 4 つの下側スイッチおよび 2 つの上側スイッチは、4 つのカレントループを形成する。これらの 4 つのカレントループは、x 方向および y 方向において相互に対向して、磁場全体をさらに低減させる。

## 【0018】

20

対向するカレントループが垂直に配向される 3 D 構成において、類似の技術を用いることができる。例えば、スイッチ上に重ねてバイパスコンデンサを置くことができる。

## 【0019】

さらに、スイッチを積層してもよいし、あるいは、各レベルごとに発生する磁場をキャンセルするように P C B を積層してもよい。

## 【0020】

別の実施形態において、単一の電流路を 8 の字形状で形成して、2 つの対向するカレントループを生成することで、磁場のキャンセルが生じる。

## 【0021】

他の実施形態が想定される。

30

例えば、本願発明は、以下の項目を提供する。

## (項目 1)

スイッチングレギュレータ回路であって、

トランジスタスイッチ制御信号を生成するコントローラと、

少なくとも上記コントローラによって制御される第 1 のスイッチであって、上記第 1 のスイッチのデューティサイクルは、上記スイッチングレギュレータ回路の調整出力を制御する、第 1 のスイッチと、

上記第 1 のスイッチへ連結された第 1 のバイパスコンデンサと、

上記第 1 のスイッチのスイッチングにより同時に発生させる少なくとも第 1 のカレントループおよび第 2 のカレントループであって、第 1 の電流は、上記第 1 のカレントループにおいて第 1 の方向に流れて第 1 の磁場を生成し、上記第 1 の磁場は、第 1 の大きさを第 1 の方向に有し、第 2 の電流は、上記第 2 のカレントループにおいて第 2 の方向に流れて第 2 の磁場を生成し、上記第 2 の方向は上記第 1 の方向と反対方向であり、上記第 2 の磁場は、第 2 の大きさを第 2 の方向に有し、これにより、上記第 1 の磁場および上記第 2 の磁場が協働して、上記スイッチングレギュレータ回路によって発生した電磁干渉 ( E M I ) を低減する、第 1 のカレントループおよび第 2 のカレントループと、

を含む、回路。

## (項目 2)

40

上記第 1 の大きさは、上記第 2 の大きさとほぼ同じである、上記項目に記載の回路。

## (項目 3)

50

上記第1のスイッチの第1の端子と上記第1のバイパスコンデンサの第1の端子との間に接続された第1の導体と、

上記第1のバイパスコンデンサの第2の端子と基準電圧との間に接続された第2の導体と、

をさらに含み、

上記第1の導体および上記第2の導体は相互に交差して、電流を互いに反対方向に伝導する上記第1のカレントループおよび上記第2のカレントループを形成するように8字型形状を形成する、上記項目のいずれか一項に記載の回路。

(項目4)

上記8字型形状は、上記第1のバイパスコンデンサの下側に交差点を形成することによって構築される、上記項目のいずれか一項に記載の回路。 10

(項目5)

上記第1のスイッチは第3のスイッチおよび第4のスイッチを含み、上記第3のスイッチおよび第4のスイッチは、同時に伝導するように並列接続され、上記回路は、

第2のスイッチをさらに含み、

上記第3のスイッチおよび上記第4のスイッチは、上記第2のスイッチの対向する側に置かれ、これにより、上記第3のスイッチおよび上記第2のスイッチ内へ流れる上記第1の電流によって上記第1のカレントループを発生させ、上記第4のスイッチおよび上記第2のスイッチ内に流れる上記第2の電流によって上記第2のカレントループを発生させる、

上記項目のいずれか一項に記載の回路。 20

(項目6)

上記第3のスイッチおよび第4のスイッチがオンであり、かつ上記第2のスイッチがオフになると、上記第1の電流が上記第3のスイッチを通じて上記第2のスイッチの寄生コンデンサ内へと流れ、上記第2の電流が上記第4のスイッチを通じて上記第2のスイッチの上記寄生コンデンサ内へと流れる、上記項目のいずれか一項に記載の回路。

(項目7)

上記第1のバイパスコンデンサは、上記第2のスイッチと上記第3のスイッチとの間に連結され、上記第1のバイパスコンデンサは上記第1のカレントループの一部である、上記項目のいずれか一項に記載の回路。 30

(項目8)

上記第2のスイッチと上記第4のスイッチとの間に連結された第2のバイパスコンデンサをさらに含み、上記第2のバイパスコンデンサは、上記第2のカレントループの一部である、上記項目のいずれか一項に記載の回路。

(項目9)

上記第1のバイパスコンデンサも上記第2のスイッチと上記第4のスイッチとの間に連結され、上記第1のバイパスコンデンサも上記第2のカレントループの一部である、上記項目のいずれか一項に記載の回路。

(項目10)

上記第1のバイパスコンデンサは、上記第3のスイッチおよび上記第4のスイッチから実質的に等距離となるように、上記第3のスイッチと上記第4のスイッチとの間に対称に設置される、上記項目のいずれか一項に記載の回路。 40

(項目11)

上記第1のスイッチは、同時に伝導するように並列接続された第3のスイッチおよび第4のスイッチを含み、上記回路は、

第2のスイッチをさらに含み、

上記第2のスイッチは、同時に伝導するように並列接続された第5のスイッチおよび第6のスイッチを含み、上記第5のスイッチは上記第3のスイッチに対向して位置付けられ、上記第6のスイッチは上記第4のスイッチに対向して位置付けられ、上記第6のスイッチは上記第5のスイッチに隣接し、上記第3のスイッチは上記第4のスイッチに隣接し、

上記第1のカレントループを、上記第3のスイッチおよび上記第5のスイッチ内へと流れる上記第1の電流によって発生させ、上記第2のカレントループを、上記第4のスイッチおよび上記第6のスイッチ内へと流れる上記第2の電流によって発生させる、上記項目のいずれか一項に記載の回路。

(項目12)

上記第3のスイッチおよび第4のスイッチがオンになり、かつ上記第5のスイッチおよび第6のスイッチがオフになると、上記第1の電流は、上記第3のスイッチを通じて上記第5のスイッチの寄生コンデンサ内へと流れ、上記第2の電流は、上記第4のスイッチを通じて上記第6のスイッチの上記寄生コンデンサ内へと流れ、上記項目のいずれか一項に記載の回路。

10

(項目13)

上記第1のバイパスコンデンサは、上記第5のスイッチと上記第3のスイッチとの間に連結され、上記第1のバイパスコンデンサは上記第1のカレントループの一部である、上記項目のいずれか一項に記載の回路。

(項目14)

上記第6のスイッチと上記第4のスイッチとの間に連結された第2のバイパスコンデンサをさらに含み、上記第2のバイパスコンデンサは、上記第2のカレントループの一部である、上記項目のいずれか一項に記載の回路。

(項目15)

上記第1のスイッチは、同時に切り替えられるように並列接続された複数の第1のスイッチ部を含み、上記回路は、

20

第2のスイッチであって、上記第2のスイッチは、同時にスイッチされるように並列接続された複数の第2のスイッチ部を含む第2のスイッチ、をさらに含み、

上記第1のスイッチ部は、第1のスイッチ部および第2のスイッチ部からなる対向する対を発生させるために、上記第2のスイッチ部に対向して位置付けられ、

上記対向する対は、複数のカレントループを発生させ、上記複数のカレントループは、上記第1のカレントループおよび上記第2のカレントループを含み、いくつかのカレントループは、上記カレントループのうち他のカレントループと反対方向に流れて、反対方向の複数の磁場を発生させ、これにより、上記スイッチングレギュレータ回路によって生成されたEMIを低減させる、上記項目のいずれか一項に記載の回路。

30

(項目16)

上記第1のバイパスコンデンサを含む複数のバイパスコンデンサをさらに含み、上記バイパスコンデンサのうち関連付けられたバイパスコンデンサは、上記第1のスイッチ部と上記第2のスイッチ部との間に連結されて、上記カレントループを形成する、上記項目のいずれか一項に記載の回路。

(項目17)

少なくとも4つのカレントループを、上記第1のカレントループおよび上記第2のカレントループと、第3のカレントループおよび第4のカレントループとを含んで発生させ、上記第3のカレントループ中の電流の方向は、上記第4のカレントループ中の電流の方向と反対方向である、上記項目のいずれか一項に記載の回路。

40

(項目18)

上記第1のカレントループおよび上記第2のカレントループは平面であり、上記第1のスイッチおよび上記第2のスイッチが形成された基板表面に対して実質的に平行である、上記項目のいずれか一項に記載の回路。

(項目19)

上記第1のカレントループおよび上記第2のカレントループは垂直コンポーネントを有し、上記垂直コンポーネントは、上記第1のスイッチおよび上記第2のスイッチが形成された基板表面に対して非平面である、上記項目のいずれか一項に記載の回路。

(項目20)

上記第1のバイパスコンデンサは、上記第1のスイッチおよび上記第2のスイッチと共に

50

に非平面である、上記項目のいずれか一項に記載の回路。

(項目21)

上記第1のスイッチおよび上記第2のスイッチはMOSFETである、上記項目のいずれか一項に記載の回路。

(項目22)

上記第1のスイッチおよび上記第2のスイッチは、集積回路チップ上に形成される、上記項目のいずれか一項に記載の回路。

(項目23)

上記集積回路チップは、交互またはインターリーブ配置された外部端子を上記第1のスイッチおよび上記第2のスイッチに対して有する、上記項目のいずれか一項に記載の回路。

(項目24)

上記集積回路チップは、上記第1のスイッチおよび上記第2のスイッチに対して2組の外部端子を有し、1組が上記集積回路パッケージの各側部にある、上記項目のいずれか一項に記載の回路。

(項目25)

上記集積回路チップは、上記チップを収容する集積回路パッケージの外部にある複数のコンデンサを利用して、上記第1のスイッチおよび上記第2のスイッチの上記端子全てまたはその一部へと接続する、上記項目のいずれか一項に記載の回路。

(項目26)

上記集積回路チップは、上記チップを収容する集積回路パッケージの内部にある複数のコンデンサを利用して、いくつかの位置において上記第1のスイッチおよび上記第2のスイッチへと接続する、上記項目のいずれか一項に記載の回路。

(項目27)

上記第1のスイッチおよび上記第2のスイッチは、端子を有する同一パッケージ中に収容され、上記第1のバイパスコンデンサが上記パッケージの外部にある上記端子へ接続されたときに上記第1のカレントループおよび上記第2のカレントループが形成されるように、上記端子が上記パッケージ上に配置される、上記項目のいずれか一項に記載の回路。

(摘要)

本発明は、新規なスイッチングレギュレータ構造を使用する。このスイッチングレギュレータ構造は、連結された対向する磁場を用いて单一の磁気ループを分割して複数の磁気ループとしてキャンセル効果を発生させ、これにより、磁場全体を大幅に低減する。その結果、EMIが低減する。一実施形態において、同期的に切り替えられたトランジスタを並列上側トランジスタと並列下側トランジスタとに分割する。上側トランジスタは、下側トランジスタに対向するように位置付けられバイパスコンデンサをこれらの対間に接続することで、複数のカレントループを発生させる。これらのコンポーネントを多様なカレントループの鏡像を形成するように配置することで、その結果発生する磁場が反対方向となり相互に実質的にキャンセルし合う。導体およびコンポーネントを8の字型パターンで交差点と共に形成することにより対向するカレントループの発生を達成することもできる。

【図面の簡単な説明】

【0022】

【図1A】従来のスイッチングレギュレータにおいて使用される従来技術スイッチング回路を示す図である。

【図1B】図1Aの異なる図であり、ICまたはPCB上のトランジスタスイッチの位置を示す図である。

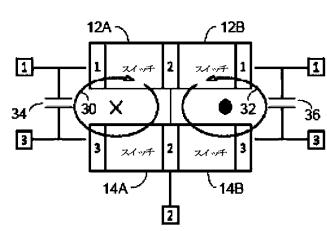

【図2A】大幅に低減したEMIと共に、図1Aの回路のスイッチング機能を達成するスイッチング構成を示す図である。

【図2B】図2Aの別の図を示し、ICまたはPCB上のトランジスタスイッチの位置を示す、ICまたはPCBの一部の斜視図である。

【図3A】図1Aの回路のスイッチング機能を達成しつつ、EMIをさらに低減するスイ

10

20

30

40

50

ツチの別の構成を示す図である。

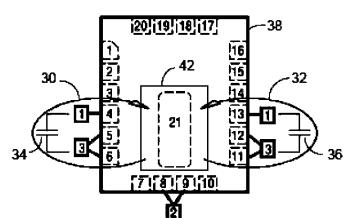

【図3B】パッケージピンレイアウトと、図3A中の端子に対応するピンとを示す、1つまたは複数のIC用のパッケージの半透明の上から見下ろした図である。

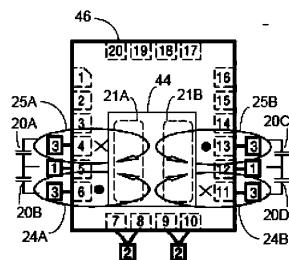

【図4】パッケージピンレイアウトと、スイッチ構成中の端子に対応するピンとを示し、図2Bの3つのスイッチを分割して合計6つのスイッチとし、パッケージ内において鏡像として位置付けることで、EMIをさらに低減する、IC用パッケージの半透明の上から見下ろした図である。

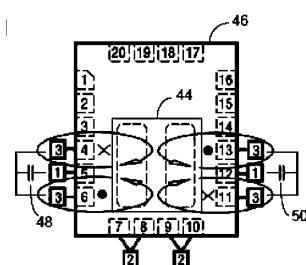

【図5】EMIを低減しつつ、コンデンサを2つだけ節約する、図4と同じであるがバイパスコンデンサ接続が異なるスイッチ配置構成を示す図である。

【図6】8の字形状の交差配線により、対向するカレントループが作成され得る様子を示す図である。 10

【図7A】6個のスイッチ、例えば、図4のスイッチを含むICを示し、バイパスコンデンサをトランジスタの上方に積層することで、対向する垂直カレントループを形成して、EMIを低減することを示す側面図である。

【図7B】図7Bの上側からの側面図である図7AのICの上から見下ろした図である。

【図8A】4つのスイッチを含むICを示し、バイパスコンデンサをトランジスタの上方に積層して、対向する垂直カレントループを形成してEMIを低減することを示す、側面図である。 20

【図8B】図8Bの上側からの側面図である図8AのICの上から見下ろした図である。

【発明を実施するための形態】

【0023】

図面中、同一または同等の要素は、同一の参照符号によって示す。

【0024】

全ての実施形態において、MOSFETスイッチのゲートがDC/DC変換器用の従来の同期PWMコントローラに接続されていると仮定し、従来の出力回路を特定の種類の変換器による必要性に応じて端子1、2および3へと接続する。出力回路は典型的には、1つまたは複数のインダクタと、1つまたは複数の大型平滑コンデンサとを含む。LT8611同期ステップダウンレギュレータについてのデータシートは、Linear Technology Corporationのウェブサイトから入手可能であり、当該データシートにおいて、本明細書中に記載のスイッチのための適切なPWMコントローラと、出力回路とが例示されている。本明細書中、同期スイッチのためのPWMコントローラおよび出力回路の典型例として同データシートを参考のため援用する。他の適切なPWMコントローラおよび出力回路について、本譲受人へ譲渡された米国特許第5,731,731号および第5,847,554号中に記載がある。本明細書中、これらの特許を参考のため援用する。コントローラは、固定周波数または可変周波数において切り替え可能である。 30

【0025】

本発明によれば、スイッチを複数のスイッチ部に分割し、これら複数のスイッチ部を電気的に相互接続して、複数の類似の反対方向のカレントループを発生させることにより、平面構造における磁気ループキャンセルが達成される。この構成により、対向する磁場が近接して設置され、これにより、磁場放射全体が低減される。垂直構造において、カレントループ中の1つまたは複数のコンポーネント（例えば、ワイヤ/トレースまたはバイパスコンデンサ）はICまたはPCB表面の上方にあり、対向する垂直カレントループを作成し、これにより磁場全体を低減する。 40

【0026】

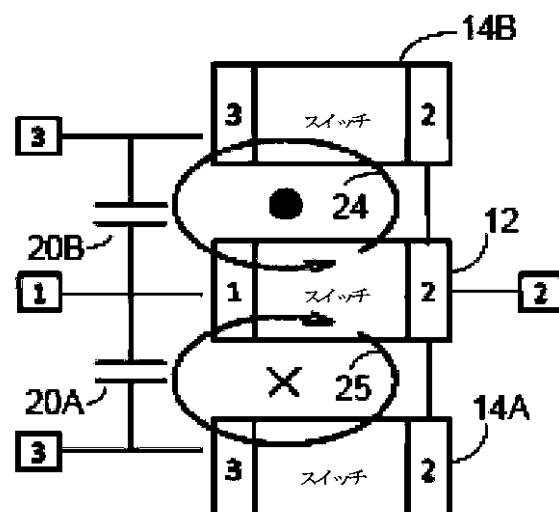

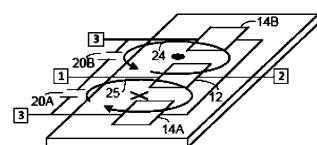

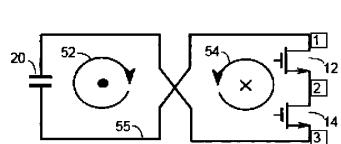

図2Aは、図1Aのスイッチング回路を分割して複数のループとし、これらの複数のループにおいて反対方向の電流を伝導して、反対方向の磁場（黒丸および×により図示）を発生させて、各ループによって発生する磁場を部分的にキャンセルする様子を示す。よって、回路から放出される磁場全体が低減する。平面構造の場合、50%以上の磁場キャンセルが可能となる。 50

## 【0027】

図2Aにおいて、図1A中の下スイッチ14の代わりに2つのスイッチ14Aおよび14Bを並列に用い、これら2つのスイッチは、面内の他方のスイッチ12（高側スイッチ）を挟む。対向するカレントループ24および25をチップまたはPCB上においてできるだけ密接して設置することで、キャンセルを向上させる。図1A中のバイパスコンデンサ20の代わりにバイパスコンデンサ20Aおよび20Bを用いて、バイパスコンデンサ20と同じ機能を行う。スイッチ14Aおよび14Bのサイズはそれぞれスイッチ14のサイズの半分にすることができるため、サイズの大幅な増加は無い。スイッチ14Aおよび14Bは、MOSFET、バイポーラトランジスタ、またはスイッチングレギュレータコントローラIC19によって制御される他の任意のスイッチング要素であり得、これらのスイッチは、PWMコントローラIC19上にあってよい。端子2は、図1Aの出力回路17へと接続され得る。10

## 【0028】

図2Aは、平面回路構造を示す。後述する3D構造を発生させることによっても、磁場キャンセルを達成することができる。

## 【0029】

図2Bは、IC28上の図2Aのスイッチのレイアウトを示す。このスイッチは、制御回路も含み得る。

## 【0030】

全実施形態中の全バイパスコンデンサは、パッケージの内部に置いてもよいし、パッケージの外部に置いてもよい。コンデンサをパッケージの内部に設けた方が、最適なキャンセルのための対向する磁場の対称関係をより良く確保することができる。20

## 【0031】

本例において同期スイッチ型トランジスタを用いているが、他の種類のスイッチングレギュレータによって、例えば、スリープ動作モードまたは不連続モードにおいて、双方のスイッチを同時にオフにしてもよい。同期整流器スイッチを他のスイッチによって同期的に切り替えるのではなく、同期整流器スイッチを逆電圧検出回路によって制御してもよい。

## 【0032】

図3Aに示す別の例は、図1Aのスイッチング回路を分割することで複数のカレントループ30/32を発生させて、これらのカレントループ30/32が反対方向の電流を伝導することで、反対方向または極性（黒丸および×によって図示）の磁場を発生させて、各ループごとに磁場を部分的にキャンセルする様子を示す。バイパスコンデンサ34および36はまた、各ループの一部として図示される。図3Aにおいて、図1A中の下スイッチ14の代わりに、並列接続された2つのスイッチ14Aおよび14Bを用い、図1A中の上スイッチ12の代わりに、並列接続された2つのスイッチ12Aおよび12Bを用いる。回路をPCB上またはシリコン内にレイアウトして、対向する方向のループをできるだけ近接して設置して、キャンセルを向上させる。各スイッチ（例えば、MOSFET）のサイズを従来技術スイッチのサイズの半分にすることができるため、同じパワー処理仕様を達成することができる。なぜならば、これら2つのMOSFETは並列接続されているからである。そのため、最終的サイズも大幅に増加しない。30

## 【0033】

図3Bは、1つまたは複数のICのためのパッケージ38の半透明の上から見下ろした図であり、パッケージピンレイアウトと、図3A中の端子1、2および3に対応するピンとを示す。端子1、2および3は、PCB上の接続ノードであり得る。パッケージは、20個の周辺ピンと、PCB上の接地ピンまたはパッドへの接続のための中央接地パッド21とを有する。図3A中の2組のスイッチを含むIC42の外形が図示される。ボンドワイヤ、リードフレーム、PCBまたは他のコネクタにより、IC42上の端子をパッケージ38のピンへと接続することができる。複数の端子およびピンを相互に接続することで、より高い電流の取り扱いおよび/または所望のカレントループパターンを発生させるが4050

可能になる。

【0034】

図2Bおよび3B中の磁場キャンセルは、構造が非対称であるため、x方向およびy方向が異なる。より対称なキャンセル構造を得るために、図4の構成を使用することができる。

【0035】

図4において、IC44の外形を露出パッド21Aおよび21Bとともに示す。IC44は6個のスイッチを含み、ここで、スイッチ14A、14Bおよび12を分割して均等かつ対向するカレントループ24Aおよび25Bならびに24Bおよび25Bを発生させることにより、図2B中のスイッチ構成の鏡像が作成される。さらなるバイパスコンデンサ24Bおよび25Bが、端子1および3へ接続される。その結果得られた磁場が相互に対称にキャンセルすることにより、EMIが全方向において低減する。4つの類似のカレントループ構造を発生させるために、端子1、2および3（例えば、電源およびバイパスコンデンサへの接続のためのPCB上のノード）は、関連付けられたパッケージピン（ピン4～13）に近接させる必要がある。よって、（カレントループの一部を形成する）パッケージピンの選択は、極めて近接した類似形状のカレントループを発生させるために重要である。

【0036】

ピンを相互に結合させることにより、抵抗の低減と、磁場キャンセルの支援とを行うことができる。

【0037】

図5は、図4中の同一のパッケージ46およびIC44を用いた別の回路配置構成を示す。この構成において、2つのバイパスコンデンサ48および50のみを使用する。対向するカレントループ24Aおよび25Bならびに24Bおよび25Bはそれぞれ、バイパスコンデンサ48または50を共有することができる。

【0038】

図5中の各バイパスコンデンサ（48または50）は、各関連付けられた外側スイッチ（例えば、図2B中のスイッチ14Aおよび14B）から実質的に等距離となるように、関連付けられた外側スイッチ間において最適に対称的に設置され、これにより、反対方向の磁場が均等化される。

【0039】

スイッチ構成と、バイパスコンデンサ構成と、パッケージからICリードへの配線と、パッケージ中の任意の内部トレースと、IC中の金属導体構成と、IC/パッケージ端子/ピン配置構成と、PCBトレースとの組み合わせは全て、最大量の磁場キャンセルを達成できるように考慮する必要がある。

【0040】

全ての実施形態において、スイッチを同一シリコンチップ上に形成する必要は無く、複数のシリコンチップを単一のパッケージ内において相互接続することができ、ここで、相互接続（例えば、ワイヤまたはトレース）はカレントループの一部である。

【0041】

多様なスイッチ/コンデンサ配置構成の目的は、類似しかつ反対の磁場特性を生成する電流路を最少で2つ提供することである。これは、図2A～図5について記載した方法以外の方法によっても達成可能である。図6～図8Bは、これらの他の方法のうちいくつかを示す。

【0042】

図6は、バイパスコンデンサ20へ接続されたスイッチ12および14の交差配線構成を示す。バイパスコンデンサ20は、発生磁場全体を低減するための対向するカレントループ52および54をICまたはPCB中ににおいて発生させる。キャンセルカレントループは、8字型形状を形成する。8字型形状を挙げると、丸みを帯びた8字型形状および直線状の8字型形状がある。2つ以上の対向するカレントループは、ワイヤ55またはト

10

20

30

40

50

レースを絶縁層を挟んで交差させることにより、得られる。ワイヤ／トレース 55 は、IC の内部または外部に設けてもよいし、部分的に内部および外部に設けてもよい。

【0043】

バイパスコンデンサ 20 は、交差点などの、カレントループ内の任意の位置に設けることができる。その後、交差点をコンデンサの下側に設置することができる。

【0044】

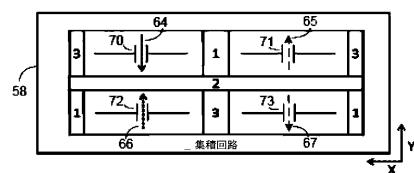

図 7A および図 7B は、IC 58 中の回路構成の側面図および上から見下ろした図をそれぞれ示す。この構成において、対向するカレントループ 60 および 62 は、図 7B 中の磁場 64、65、66 および 67 をキャンセルするための垂直コンポーネントを有する。磁場の方向を矢印によって示す。平面ループではなく垂直カレントループを発生させるためにバイパスコンデンサ 70、71、72 および 73 を IC 58 の上方に取り付けることにより、磁場キャンセルを形成する。全方向の磁場をキャンセルする 6 個のスイッチを使用して、4 つの垂直カレントループを発生させる。これら 6 個のスイッチは、3 つの並列スイッチに分割された上側スイッチと、3 つの並列スイッチに分割された下側スイッチとを図 7B 中に示す配置構成において含む。図 7B の上半分は、（端子 1 および 2 に接続された）中央上側スイッチを挟んで（端子 3 および 2 に接続された）2 つの下側スイッチを有し、図 7B の下半分は、非対称配置構成を形成するために（端子 3 および 2 に接続された）中央下側スイッチを挟んで（端子 1 および 2 に接続された）2 つの上側スイッチを有する態様に留意されたい。

【0045】

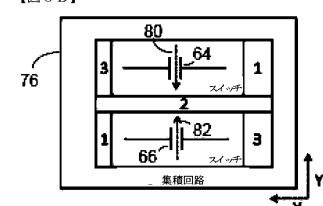

図 8A および図 8B は、IC 76 中の垂直回路の別の実施形態の側面図および上から見下ろした図を示す。この回路において、図 8B 中の磁場 80 および 82 をキャンセルする反対方向のカレントループ 78（そのうち 1 つのカレントループのみを図 8A 中に示す）がある。図 8B において、4 つのスイッチがある。ここで、図 8B に示される配置構成において、上側スイッチを分割して 2 つの並列スイッチとし、下側スイッチを分割して 2 つの並列スイッチとする。図 8B は、図 7B の回路の左半分において不可欠であり、図 8B において、各スイッチは、電流のうち半分を搬送するためにより大型になっている。

【0046】

一般的に、3D 構造中の磁気ループキャンセルは、垂直配向鏡像構成において電流を循環させるための経路を備えた複数の電源スイッチデバイスを形成することにより、形成される。この構造は、対向する電流ループを発生させることでキャンセル効果のための逆並列磁場を生成するように、設計される。

【0047】

例えば、同一 IC パッケージ中の、ループの近隣においては、より良好なキャンセルが得られるが、より長距離にすることにより、従来技術の単一のループ設計と比較して、キャンセルをさらに向上させる。

【0048】

記載された多様な実施形態において、2 つ以上のキャンセルカレントループを通じて流れる正味電流に起因して発生する磁場全体は、二次元または三次元キャンセル設計を切断する任意の面における従来技術の単一のループ設計の個々のループまたは比較可能なループの絶対磁場の合計よりも小さい。よって、本発明の技術を使用することにより、EMI が低減する。

【0049】

多様な実施形態において、対向する磁場の大きさは同じとしたが、本発明は、対向する磁場の大きさが異なる場合（例えば、カレントループのループ半径または形状が異なる場合）においても、EMI をより低い程度まで低減するように機能する。

【0050】

EMI を低減させる同一キャンセルにより、寄生インダクタンスも低減することができる。寄生インダクタンスは、高スイッチング周波数における損失機構である。よって、本キャンセル技術を用いた場合、従来技術と比較して、高スイッチング周波数においてより

10

20

30

40

50

高効率の電源が得られる。これは、磁場キャンセル技術において予期しない驚くべき結果である。

【0051】

本発明の特定の実施形態について図示および記載してきたが、本発明のより広範な態様から逸脱することなく変更および改変が可能であり、よって、添付の特許請求の範囲は、本発明の要旨および範囲内のこのような変更および改変全てをその範囲内に包含することが、当業者にとって明らかとなろう。

【図1A】

【図1A (従来技術)】

【図1B】

【図1B (従来技術)】

【図2A】

【図2A】

【図2B】

【図2B】

【図3A】

【図3A】

### 【図3B】

【図3B】

【図4】

【図4】

【圖 5】

[図5]

【 四 6 】

[図6]

### 【図 7 A】

[図7.A]

【図7B】

【図7B】

【図 8 A】

【図8A】

【 図 8 B 】

図 9 B W

---

フロントページの続き

(72)発明者 レオナルド シュタルゴット

アメリカ合衆国 カリフォルニア 95008, キャンベル, ウエストモント アベニュー

1305

(72)発明者 ダニエル チェン

アメリカ合衆国 カリフォルニア 94043, マウンテン ビュー, ドーチェスター ドラ

イブ 34

(72)発明者 ジョン ガードナー

アメリカ合衆国 カリフォルニア 94705, バークレー, ラッセル ストリート 243

8, アパートメント ビー

(72)発明者 ジェフリー ウィット

アメリカ合衆国 カリフォルニア 94618, オークランド, カレス アベニュー 554

0

(72)発明者 ク里斯チャン クエック

ドイツ国 デー-59348 リューディングハウゼン, ベッカーシュトラーセ 20

審査官 今井 貞雄

(56)参考文献 特開2012-059896(JP, A)

特開2010-268536(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155