(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4606520号

(P4606520)

(45) 発行日 平成23年1月5日(2011.1.5)

(24) 登録日 平成22年10月15日(2010.10.15)

|              |                              |

|--------------|------------------------------|

| (51) Int.Cl. | F 1                          |

| G 11 C 13/00 | (2006.01) G 11 C 13/00 A     |

| H 01 L 27/10 | (2006.01) H 01 L 27/10 4 5 1 |

| H 01 L 45/00 | (2006.01) H 01 L 45/00 Z     |

| H 01 L 49/00 | (2006.01) H 01 L 49/00 Z     |

請求項の数 6 (全 39 頁)

(21) 出願番号 特願2010-529176 (P2010-529176)

(86) (22) 出願日 平成22年3月15日 (2010.3.15)

(86) 国際出願番号 PCT/JP2010/001833

(87) 国際公開番号 WO2010/109803

(87) 国際公開日 平成22年9月30日 (2010.9.30)

審査請求日 平成22年7月26日 (2010.7.26)

(31) 優先権主張番号 特願2009-74572 (P2009-74572)

(32) 優先日 平成21年3月25日 (2009.3.25)

(33) 優先権主張国 日本国 (JP)

早期審査対象出願

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 110000556

特許業務法人 有古特許事務所

(72) 発明者 魏 志強

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

(72) 発明者 東 亮太郎

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

(72) 発明者 高木 剛

大阪府門真市大字門真1006番地 パナ

ソニック株式会社内

最終頁に続く

(54) 【発明の名称】抵抗変化型不揮発性記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1平面内において第1方向に亘り平行に伸びる複数の第1配線と、

前記第1平面と平行な第2平面内において第2方向に亘り平行にかつ前記第1配線と

立体交差するように伸びる複数の第2配線と、

前記第1配線と前記第2配線との立体交差点のそれぞれに対応して設けられたメモリセルとを備え、

前記メモリセルのそれぞれは1個のトランジスタと1個の抵抗変化型素子とを備え、

前記トランジスタのそれぞれは第1主端子と第2主端子と制御端子とを備え、

前記抵抗変化型素子のそれぞれは第1電極と第2電極と前記第1電極および前記第2電

極の間に設けられた抵抗変化層とを備え、 10

前記第1方向に沿って並ぶ複数の前記メモリセルについて、隣接する2個のメモリセルに含まれる一方のメモリセルの第1主端子と他方のメモリセルの第2主端子とが接続されることで、複数のメモリセルの主端子を順次に直列に接続して前記第1方向に伸びる直列経路が形成され、

前記メモリセルのそれについて、

前記制御端子が当該メモリセルに対応する前記第1配線に接続され、

前記第2電極が前記メモリセルに対応する前記第2配線の一部であるか前記第2配線に接続され、

前記第1電極が前記メモリセルに対応する前記直列経路の一部であるか直列経路に接 20

続されている、

不揮発性記憶装置。

**【請求項 2】**

前記第1方向に互いに平行に伸びる複数の第3配線を備え、

前記第1方向に沿って並ぶ複数のメモリセルは、連続して並んだ所定個数のメモリセルにより複数のメモリブロックを構成し、

それぞれの前記メモリブロック毎に前記直列経路が前記第3配線と接続されている、請求項1に記載の不揮発性記憶装置。

**【請求項 3】**

それぞれの前記メモリブロック毎に前記直列経路の両端が前記第3配線と接続されている、請求項2に記載の不揮発性記憶装置。 10

**【請求項 4】**

それぞれの前記メモリセルに含まれる抵抗変化型素子に電圧を印加するための電源回路を備え、

前記電源回路は、選択されたメモリセルについて、対応する前記直列経路と対応する前記第3配線との接続部から前記メモリセルの第1電極までの前記直列経路に含まれるトランジスタの数に応じて出力する電圧を変化させるように構成されている、請求項2に記載の不揮発性記憶装置。

**【請求項 5】**

前記第1主端子および前記第2主端子はそれぞれシリサイド層を有し、

20

前記シリサイド層が前記第1電極を構成する、請求項1に記載の不揮発性記憶装置。

**【請求項 6】**

前記シリサイド層は白金シリサイドからなる、請求項5に記載の不揮発性記憶装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化素子とトランジスタとで構成されたメモリセルを有する抵抗変化型不揮発性記憶装置に関する。

**【背景技術】**

**【0002】**

30

近年、抵抗変化素子を用いて構成されたメモリセルを有する不揮発性記憶装置の研究開発が進んでいる。抵抗変化素子とは、電気的信号によって抵抗値が可逆的に変化する性質を有し、さらにはこの抵抗値に対応したデータを、不揮発的に記憶することが可能な素子をいう。

**【0003】**

抵抗変化型素子を用いたメモリセルについて、その1つにいわゆるクロスポイント構造が用いられる。クロスポイント構造では、直交するように配置されたビット線とワード線との交点の位置に、ビット線とワード線とに挟まれて、各メモリセルが構成される。メモリセル面積は $4F^2$ を実現可能である。特許文献1には、バイポーラタイプの抵抗変化型素子を用いたクロスポイント型の抵抗変化型記憶装置が示されている。この抵抗変化型記憶装置では、データ書き込み時において、選択ビット線にVpp、選択ワード線にVss(0V)、非選択ワード線および非選択ビット線に1/2Vppが印加される。また、データ消去時において、選択ワード線にVpp、選択ビット線にVss(0V)、非選択ワード線および非選択ビット線にVpp/2が印加される。 40

**【0004】**

また、抵抗変化素子を用いた不揮発性記憶装置として、直交するように配置されたビット線とワード線、ソース線との交点の位置に、MOSトランジスタと抵抗変化素子を直列に接続した、いわゆる1T1R型と呼ばれるメモリセルをマトリックス状にアレイ配置した不揮発性記憶装置が一般的に知られている。このメモリセルの面積は、最小でも $6F^2$ を必要である。 50

**【0005】**

特許文献2では、ペロブスカイト型結晶構造の酸化物を抵抗変化素子として用いた1T1R型メモリセルで構成された不揮発性記憶装置が示されている。

**【0006】**

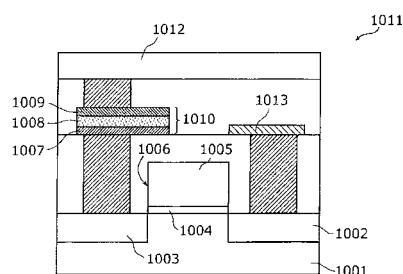

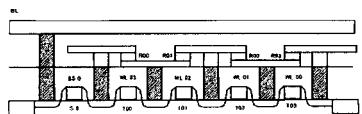

図47は、特許文献2に図2として開示されているメモリセルの断面の模式図である。

**【0007】**

メモリセル1011は、トランジスタ1006と抵抗変化素子1010とを電気的に直列に接続して形成されている。

**【0008】**

トランジスタ1006は、半導体基板1001上に作製した第1の拡散層領域であるソース領域1002、第2の拡散層領域であるドレイン領域1003、およびゲート酸化膜1004上に形成されたゲート電極1005からなる。

10

**【0009】**

抵抗変化素子1010は、電圧印加によって抵抗値が変化する可変抵抗層1008を、下部電極1007と上部電極1009との間に挟持してなる。

**【0010】**

ドレイン領域1003と下部電極1007とは電気的に接続されている。

**【0011】**

上部電極1009は、ビット線1012となる金属配線に接続され、ゲート電極1005はワード線に接続され、ソース領域1002はソース線1013となる金属配線に接続される。

20

**【0012】**

ここでは、可変抵抗層1008に用いる材料としては、 $\text{Pr}_{1-x}\text{Ca}_x\text{MnO}_3$ 、 $\text{La}_{1-x}\text{Ca}_x\text{MnO}_3$ (PCM0)などが開示されているが、電極材料に関しては特に言及されていない。

**【0013】**

また、メモリセル1011への書き込み方法については、上部電極1009にVpp、ソース領域1002にVss、ゲート電極に所定の電圧振幅Vwpのパルス電圧を印加すると、低抵抗状態から高抵抗状態に変化し、逆に、上部電極1009にVss、ソース領域1002にVpp、ゲート電極に所定のVweのパルス電圧を印加すると、高抵抗状態から低抵抗状態に変化できることが開示されている。

30

**【0014】**

また、1T1Rメモリ構造を用いて、メモリセル面積を4F<sup>2</sup>に実現できる構造は特許文献3と特許文献4で開示されている。

**【0015】**

図48は、特許文献3に図5として開示されている回路図である。ここでは、抵抗変化素子とトランジスタは並列で配置され、メモリセルを構成する。メモリセルを直列接続し、メモリアレイを構成する。この配置により、メモリセルの面積はトランジスタの面積で決め、4F<sup>2</sup>まで実現できる。

**【先行技術文献】**

40

**【特許文献】****【0016】**

**【特許文献1】**特開2006-203098号公報

**【特許文献2】**特開2005-25914号公報

**【特許文献3】**特開2004-272975号公報

**【特許文献4】**米国特許第7298640号明細書

**【発明の概要】****【発明が解決しようとする課題】****【0017】**

しかしながら、1T1Rの6F<sup>2</sup>のメモリセル面積より縮小した前記の特許文献2では

50

、整流素子としてバリスタを適用したクロスポイント型の抵抗変化型記憶装置が開示されている。一般に、クロスポイント型の抵抗変化型記憶装置では、整流素子としてダイオードが用いられる。ダイオードは、電圧に対し指数関数的に電流が増加するという特性を有している。ダイオードを流れる電流値は、印加される電圧が閾値電圧  $V_{th}$  より低くても完全にゼロになるわけではない。特許文献 2 のように非選択のメモリセルに  $V_{pp}/2$  の電位差が印加された場合、Schottky MIM 型ダイオードモデルを採用すると、非選択セルを流れる電流は選択セルを流れる電流の百分の 1 から千分の 1 程度となる。大規模なメモリアレイでは、1 行または 1 列に数百から数千のメモリセルが配設されるため、選択ビット線または選択ワード線に接続された非選択セルを流れる電流（漏れ電流）が、選択セルを流れる電流値と比較して必ずしも無視できなくなる。

10

#### 【0018】

また、特許文献 3 と特許文献 4 は、抵抗変化素子とトランジスタとを並列配置するため、直列配置のメモリセル中の一つのセルを選択するとき、同一列に配置したトランジスタはすべて ON の状態となり、選択しない抵抗変化素子にもソース・ドレイン間の電圧が印加される。また、抵抗変化素子の低抵抗は数百オームであり、トランジスタの ON 抵抗は  $1\text{ k}\Omega$  程度であるため、トランジスタに流れる電流より多くの電流が低抵抗の抵抗変化素子に流れ、メモリ特性は劣化する。

#### 【0019】

本発明は上記課題を解決するものであり、抵抗変化素子を配置する構造を工夫することで、非選択メモリセルに流れる電流を効果的に抑制しつつ、 $4\text{ F}^2$  のメモリセルを実現する不揮発性記憶装置を提供することを主たる目的とする。

20

#### 【課題を解決するための手段】

#### 【0020】

上記課題を解決すべく、本発明の不揮発性記憶装置は、第 1 平面内において第 1 方向に互いに平行に伸びる複数の第 1 配線と、前記第 1 平面と平行な第 2 平面内において第 2 方向に互いに平行にかつ前記第 1 配線と立体交差するように伸びる複数の第 2 配線と、前記第 1 配線と前記第 2 配線との立体交差点のそれぞれに対応して設けられたメモリセルとを備え、前記メモリセルのそれぞれは 1 個のトランジスタと 1 個の抵抗変化型素子とを備え、前記トランジスタのそれぞれは第 1 主端子と第 2 主端子と制御端子とを備え、前記抵抗変化型素子のそれぞれは第 1 電極と第 2 電極と前記第 1 電極および前記第 2 電極の間に設けられた抵抗変化層とを備え、前記第 1 方向に沿って並ぶ複数の前記メモリセルについて、隣接する 2 個のメモリセルに含まれる一方のメモリセルの第 1 主端子と他方のメモリセルの第 2 主端子とが接続されることで、複数のメモリセルの主端子を順次に直列に接続して前記第 1 方向に伸びる直列経路が形成され、前記メモリセルのそれぞれについて、制御端子がそのメモリセルに対応する第 1 配線に接続され、第 2 電極がそのメモリセルに対応する第 2 配線に接続され、第 1 電極がそのメモリセルに対応する直列経路に接続されている。

30

#### 【0021】

かかる構成では、非選択メモリセルに流れる電流を効果的に抑制しつつ、 $4\text{ F}^2$  のメモリセルを実現する不揮発性記憶装置が提供される。

40

#### 【0022】

上記不揮発性記憶装置は、前記第 1 方向に互いに平行に伸びる複数の第 3 配線を備え、前記第 1 方向に沿って並ぶ複数のメモリセルは、連続して並んだ所定個数のメモリセルにより複数のメモリブロックを構成し、それぞれのメモリブロック毎に前記直列経路が前記第 3 配線と接続されていてよい。

#### 【0023】

かかる構成では、ビット線 BL に抵抗率の低い導体を用いることで、直列経路における配線遅延を抑制することができる。

#### 【0024】

上記不揮発性記憶装置において、それぞれのメモリブロック毎に前記直列経路のそれぞ

50

れの両端が前記第3配線と接続されていてもよい。

**【0025】**

かかる構成では、直列経路の両側から電位が伝播するため、配線遅延がより効果的に抑制される。

**【0026】**

上記不揮発性記憶装置は、それぞれのメモリセルに含まれる抵抗変化型素子に電圧を印加するための電源回路を備え、前記電源回路は、選択されたメモリセルについて、対応する前記直列経路と対応する前記第3配線との接続部からそのメモリセルの第1電極までの前記直列経路に含まれるトランジスタの数に応じて出力する電圧を変化させるように構成されていてもよい。

10

**【0027】**

かかる構成では、メモリセルの位置によらず抵抗変化型素子の両電極間に印加される電圧が一定となり、従前の構成に比べ、書き込み後の抵抗値をより一定に保ち、かつ抵抗変化型素子にかかる不必要的電圧ストレスをより抑制できる。

**【0028】**

上記不揮発性記憶装置において、前記第1主端子および前記第2主端子はそれぞれシリサイド層を有し、前記シリサイド層が前記第1電極を構成してもよい。

**【0029】**

上記不揮発性記憶装置において、前記シリサイド層は白金シリサイドからなっていてもよい。

20

**【0030】**

本発明の上記目的、他の目的、特徴、及び利点は、添付図面参照の下、以下の好適な実施態様の詳細な説明から明らかにされる。

**【発明の効果】**

**【0031】**

本発明は、上記のような構成を有し、非選択メモリセルに流れる電流を効果的に抑制しつつ、 $4 F^2$  のメモリセルを実現する不揮発性記憶装置を提供することが可能となる。

**【図面の簡単な説明】**

**【0032】**

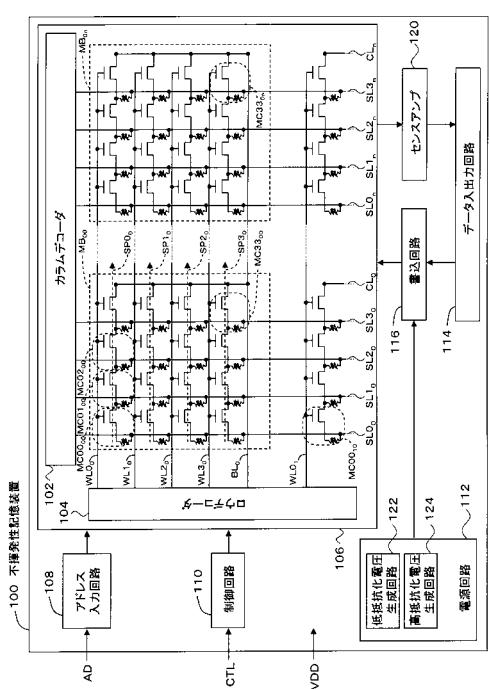

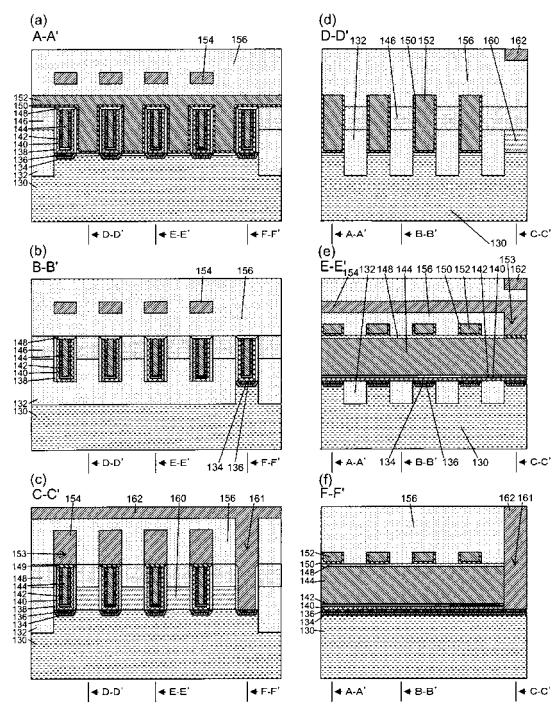

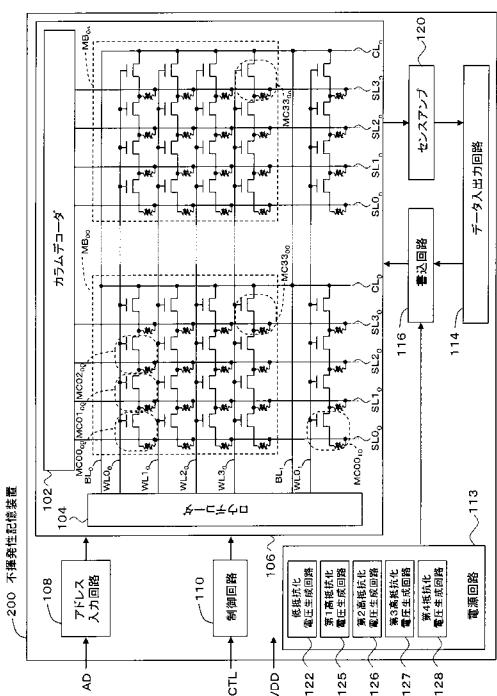

**【図1】**図1は、本発明の第1実施形態に係る不揮発性記憶装置100の回路構成の一例を示すブロック図である。

30

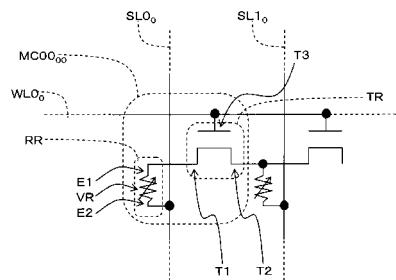

**【図2】**図2は、図1におけるメモリセルMCの部分を拡大した図である。なお、添え字は対応するメモリブロックの行または列の番号を示す。

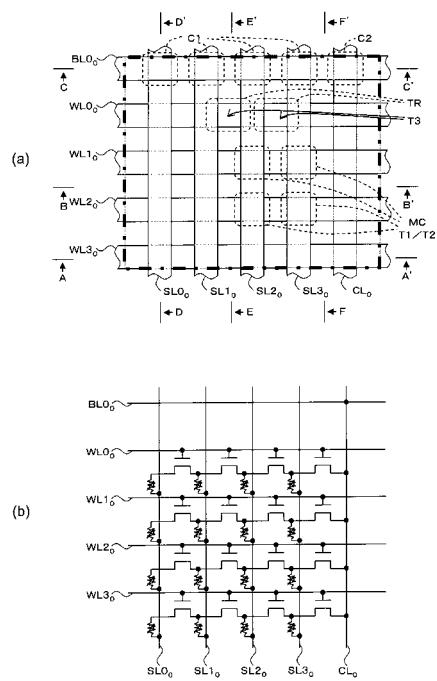

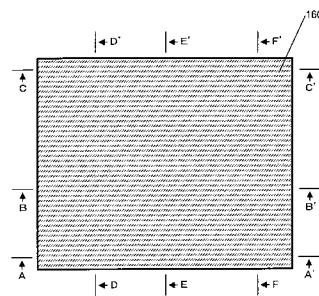

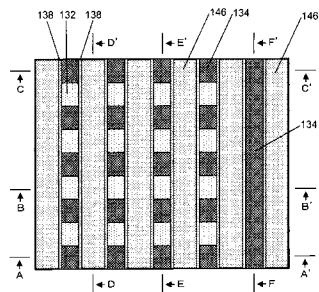

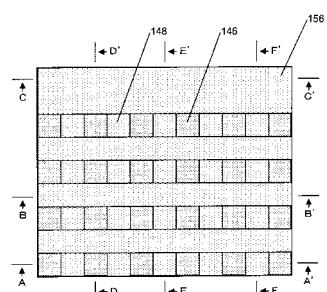

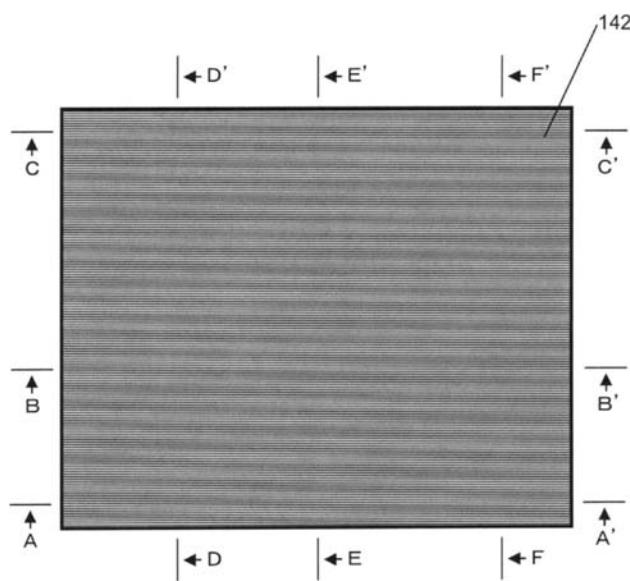

**【図3】**図3は、1個のメモリブロックを示す図であり、図3(a)はメモリブロックの上面図、図3(b)は図3(a)の等価回路図である。

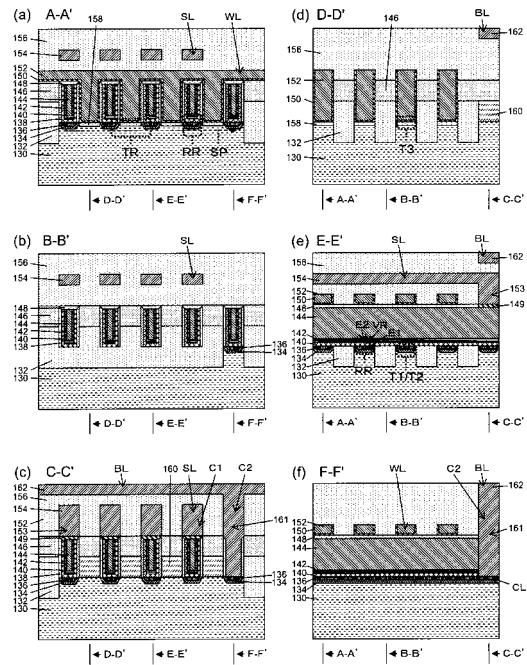

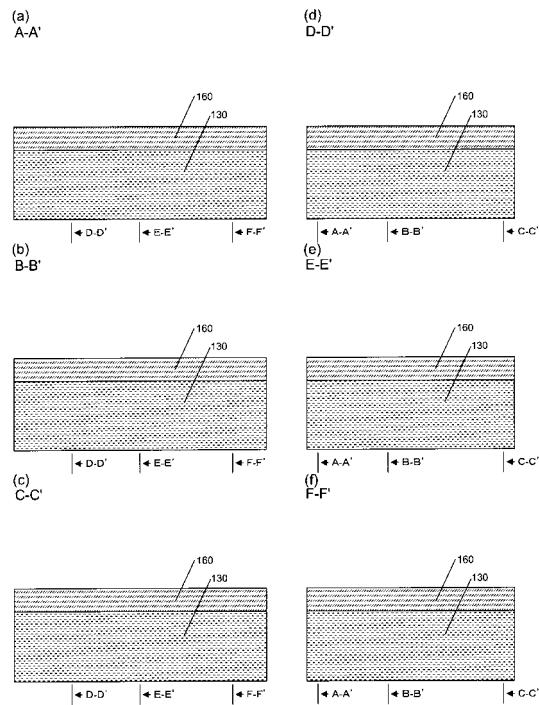

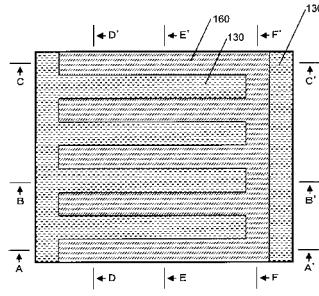

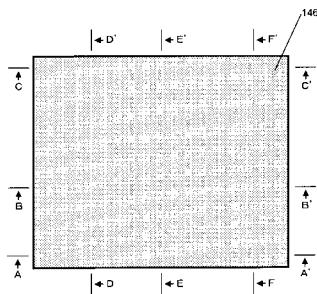

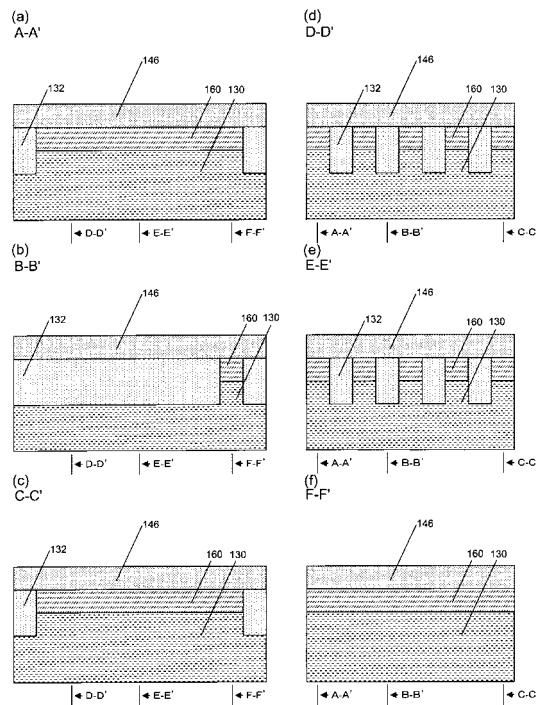

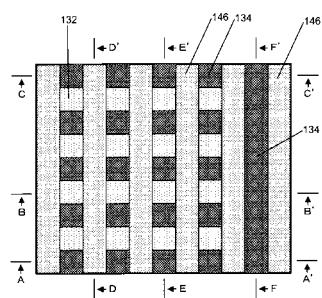

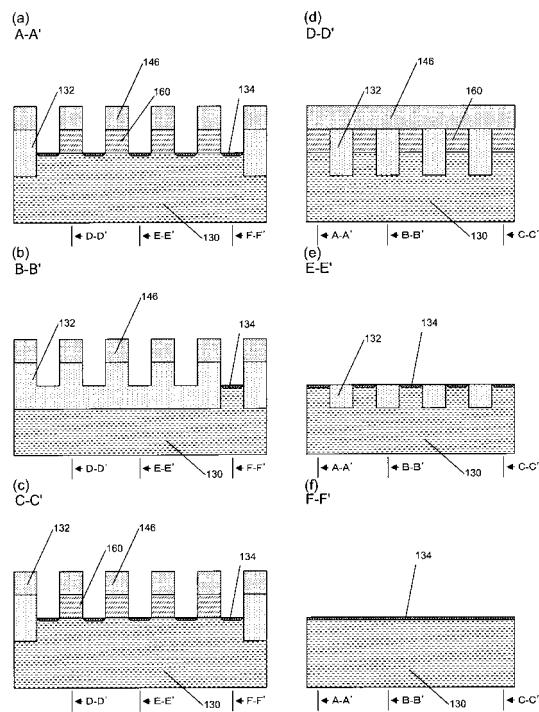

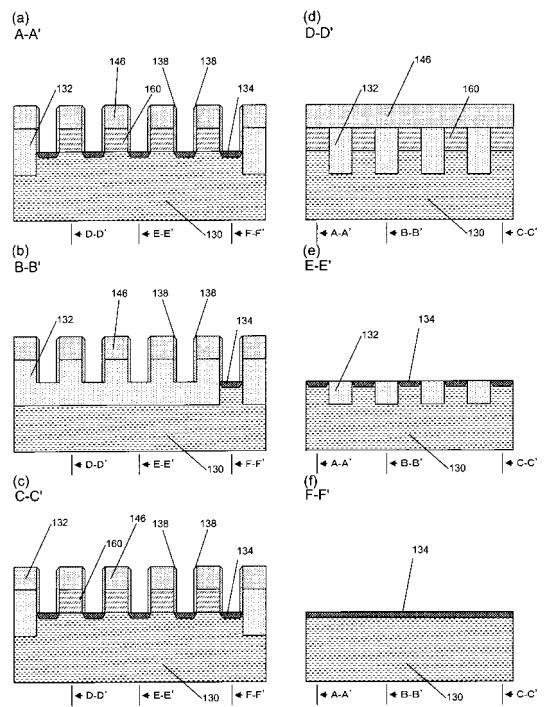

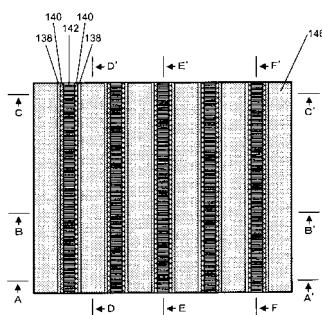

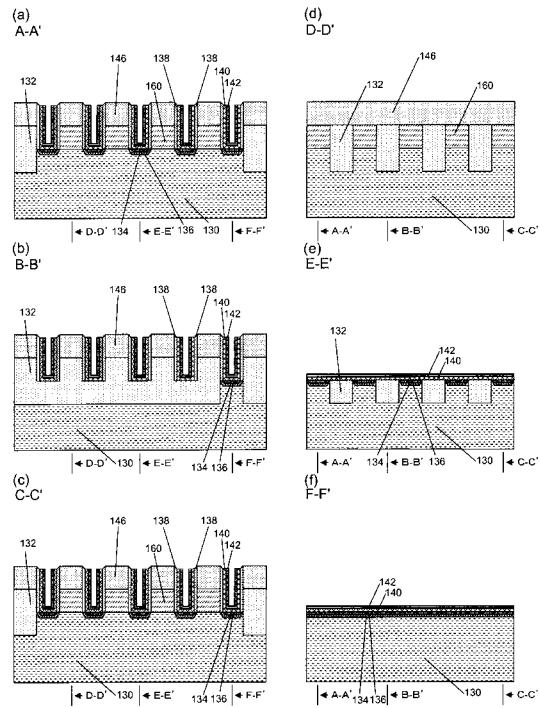

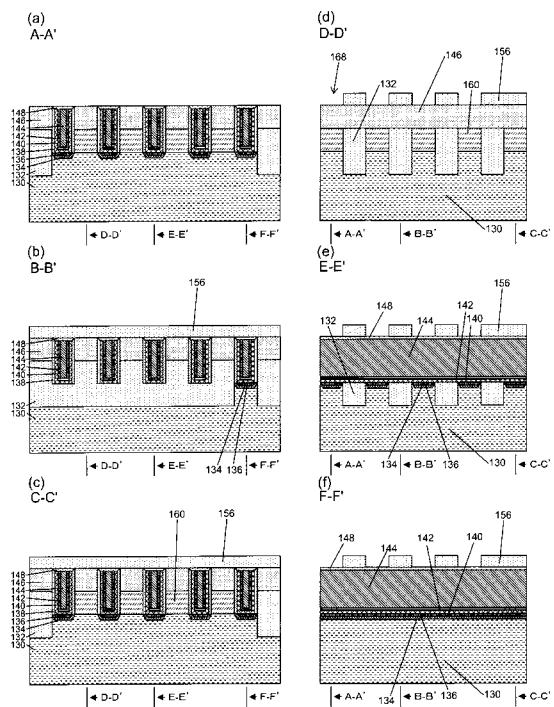

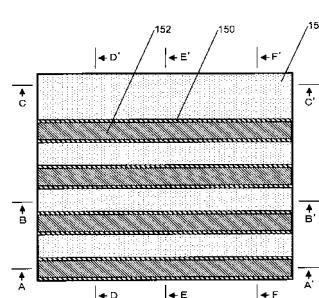

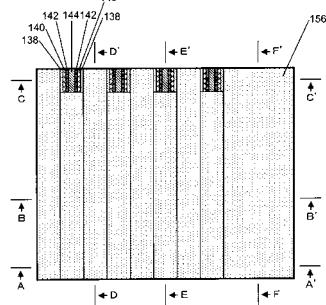

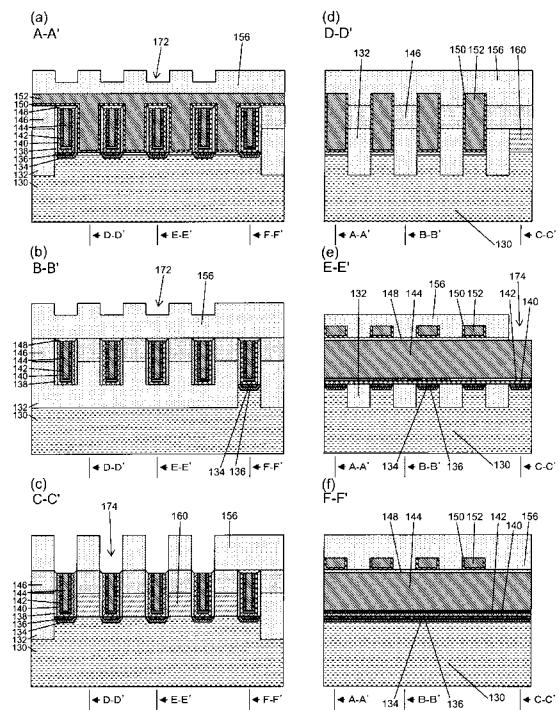

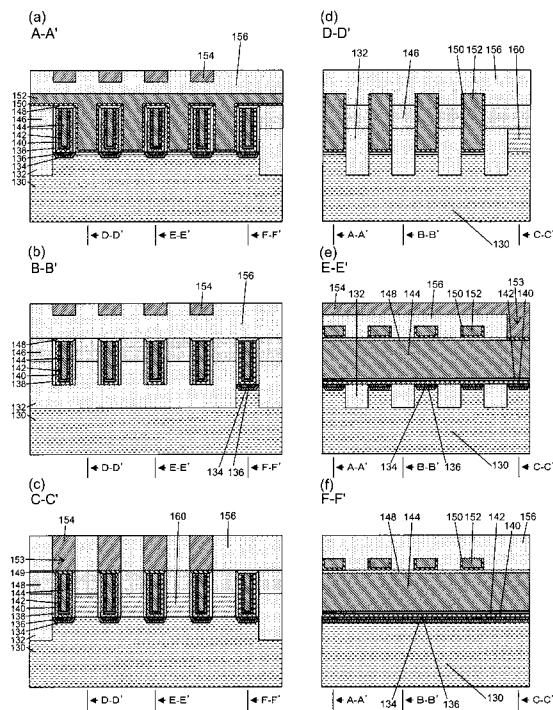

**【図4】**図4は、図3の一点鎖線で示したメモリブロックの断面を示す図であり、図4(a)は図3の線A-A'に沿って切った断面図、図4(b)は図3の線B-B'に沿って切った断面図、図4(c)は図3の線C-C'に沿って切った断面図、図4(d)は図3の線D-D'に沿って切った断面図、図4(e)は図3の線E-E'に沿って切った断面図、図4(f)は図3の線F-F'に沿って切った断面図である。

40

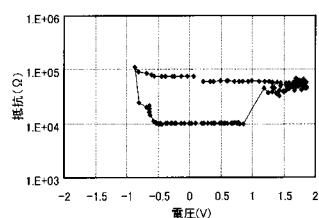

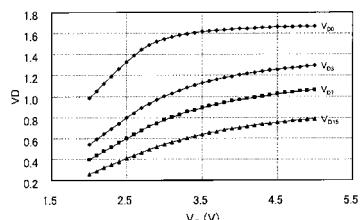

**【図5】**図5は、本発明の第1実施形態にかかる不揮発性記憶装置に含まれる抵抗変化型素子の特性(電圧と抵抗値との関係)の一例を示す図である。

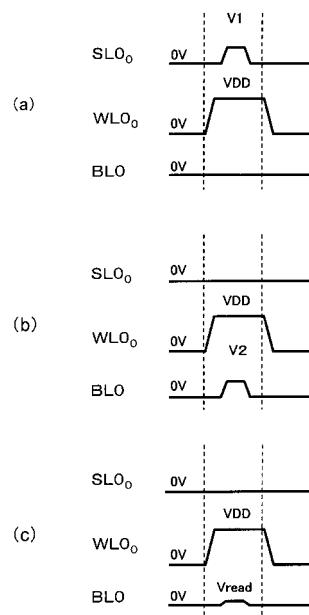

**【図6】**図6は、本発明の第1実施形態にかかる不揮発性記憶装置の動作例を示すタイミングチャートであり、図6(a)はメモリセルMC000に“0”を書き込む場合(抵抗変化型素子RRを低抵抗化させる場合)、図6(b)はメモリセルMC000に“1”を書き込む場合(抵抗変化型素子RRを高抵抗化させる場合)、図6(c)はメモリセルMC000に書き込まれているデータを読み出す場合を示す。

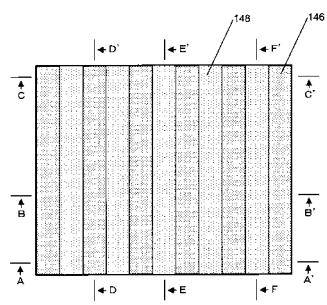

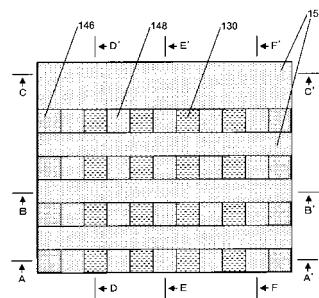

**【図7】**図7は、P型シリコン基板上にポリシリコン層を形成する工程を示す上面図である。

**【図8】**図8は、P型シリコン基板上にポリシリコン層を形成する工程を示す断面図であ

50

り、図 8 ( a ) は図 7 において A - A' に沿って切った断面を矢印方向に見た断面図、図 8 ( b ) は図 7 において B - B' に沿って切った断面を矢印方向に見た断面図、図 8 ( c ) は図 7 において C - C' に沿って切った断面を矢印方向に見た断面図、図 8 ( d ) は図 7 において D - D' に沿って切った断面を矢印方向に見た断面図、図 8 ( e ) は図 7 において E - E' に沿って切った断面を矢印方向に見た断面図、図 8 ( f ) は図 7 において F - F' に沿って切った断面を矢印方向に見た断面図である。

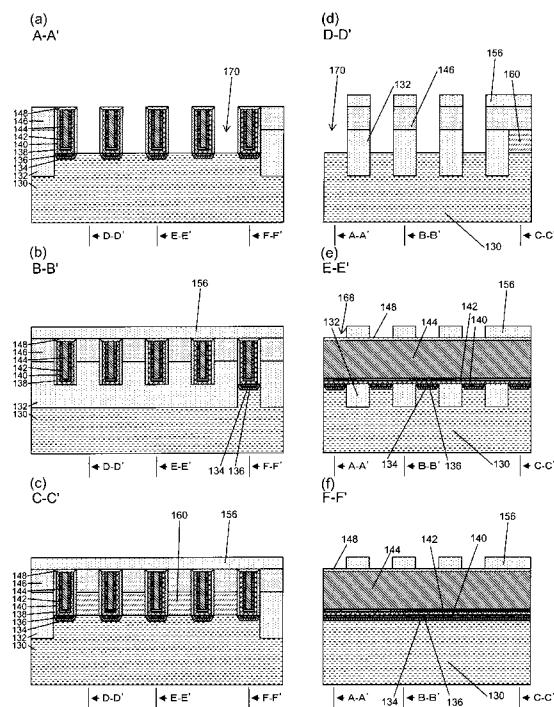

【図 9】図 9 は、P 型シリコン基板とポリシリコン層とをエッチングして STI を形成するための溝を形成する工程を示す上面図である。

【図 10】図 10 は、P 型シリコン基板とポリシリコン層とをエッチングして STI を形成するための溝を形成する工程を示す断面図であり、図 10 ( a ) は図 9 において A - A' に沿って切った断面を矢印方向に見た断面図、図 10 ( b ) は図 9 において B - B' に沿って切った断面を矢印方向に見た断面図、図 10 ( c ) は図 9 において C - C' に沿って切った断面を矢印方向に見た断面図、図 10 ( d ) は図 9 において D - D' に沿って切った断面を矢印方向に見た断面図、図 10 ( e ) は図 9 において E - E' に沿って切った断面を矢印方向に見た断面図、図 10 ( f ) は図 9 において F - F' に沿って切った断面を矢印方向に見た断面図である。

【図 11】図 11 は、溝に二酸化珪素を埋め込むことで STI を形成する工程を示す上面図である。

【図 12】図 12 は、溝に二酸化珪素を埋め込むことで STI を形成する工程を示す断面図であり、図 12 ( a ) は図 11 において A - A' に沿って切った断面を矢印方向に見た断面図、図 12 ( b ) は図 11 において B - B' に沿って切った断面を矢印方向に見た断面図、図 12 ( c ) は図 11 において C - C' に沿って切った断面を矢印方向に見た断面図、図 12 ( d ) は図 11 において D - D' に沿って切った断面を矢印方向に見た断面図、図 12 ( e ) は図 11 において E - E' に沿って切った断面を矢印方向に見た断面図、図 12 ( f ) は図 11 において F - F' に沿って切った断面を矢印方向に見た断面図である。

【図 13】図 13 は、二酸化珪素層とポリシリコン層とを覆うように Si<sub>3</sub>N<sub>4</sub> 層を形成する工程を示す上面図である。

【図 14】図 14 は、二酸化珪素層とポリシリコン層とを覆うように Si<sub>3</sub>N<sub>4</sub> 層を形成する工程を示す断面図であり、図 14 ( a ) は図 13 において A - A' に沿って切った断面を矢印方向に見た断面図、図 14 ( b ) は図 13 において B - B' に沿って切った断面を矢印方向に見た断面図、図 14 ( c ) は図 13 において C - C' に沿って切った断面を矢印方向に見た断面図、図 14 ( d ) は図 13 において D - D' に沿って切った断面を矢印方向に見た断面図、図 14 ( e ) は図 13 において E - E' に沿って切った断面を矢印方向に見た断面図、図 14 ( f ) は図 13 において F - F' に沿って切った断面を矢印方向に見た断面図である。

【図 15】図 15 は、メモリ溝を形成する工程を示す上面図である。

【図 16】図 16 は、メモリ溝を形成する工程を示す断面図であり、図 16 ( a ) は図 15 において A - A' に沿って切った断面を矢印方向に見た断面図、図 16 ( b ) は図 15 において B - B' に沿って切った断面を矢印方向に見た断面図、図 16 ( c ) は図 15 において C - C' に沿って切った断面を矢印方向に見た断面図、図 16 ( d ) は図 15 において D - D' に沿って切った断面を矢印方向に見た断面図、図 16 ( e ) は図 15 において E - E' に沿って切った断面を矢印方向に見た断面図、図 16 ( f ) は図 15 において F - F' に沿って切った断面を矢印方向に見た断面図である。

【図 17】図 17 は、各メモリ溝の底面において P 型シリコン基板が露出した部分にリン原子 ( P ) を注入する工程を示す上面図である。

【図 18】図 18 は、各メモリ溝の底面において P 型シリコン基板が露出した部分にリン原子 ( P ) を注入する工程を示す断面図であり、図 18 ( a ) は図 17 において A - A' に沿って切った断面を矢印方向に見た断面図、図 18 ( b ) は図 17 において B - B' に沿って切った断面を矢印方向に見た断面図、図 18 ( c ) は図 17 において C - C' に沿

10

20

30

40

50

つて切った断面を矢印方向に見た断面図、図18(d)は図17においてD-D'に沿って切った断面を矢印方向に見た断面図、図18(e)は図17においてE-E'に沿って切った断面を矢印方向に見た断面図、図18(f)は図17においてF-F'に沿って切った断面を矢印方向に見た断面図である。

【図19】図19は、各メモリ溝の左右の側壁にSi<sub>3</sub>N<sub>4</sub>部(サイドウォール)を形成する工程を示す上面図である。

【図20】図20は、各メモリ溝の左右の側壁にSi<sub>3</sub>N<sub>4</sub>部(サイドウォール)を形成する工程を示す断面図であり、図20(a)は図19においてA-A'に沿って切った断面を矢印方向に見た断面図、図20(b)は図19においてB-B'に沿って切った断面を矢印方向に見た断面図、図20(c)は図19においてC-C'に沿って切った断面を矢印方向に見た断面図、図20(d)は図19においてD-D'に沿って切った断面を矢印方向に見た断面図、図20(e)は図19においてE-E'に沿って切った断面を矢印方向に見た断面図、図20(f)は図19においてF-F'に沿って切った断面を矢印方向に見た断面図である。

【図21】図21、各メモリ溝に形成された一対のSi<sub>3</sub>N<sub>4</sub>部の間ににおいてP型シリコン基板が露出した部分にリン原子(P)を注入する工程を示す上面図である。

【図22】図22は、各メモリ溝に形成された一対のSi<sub>3</sub>N<sub>4</sub>部の間ににおいてP型シリコン基板が露出した部分にリン原子(P)を注入する工程を示す断面図であり、図22(a)は図21においてA-A'に沿って切った断面を矢印方向に見た断面図、図22(b)は図21においてB-B'に沿って切った断面を矢印方向に見た断面図、図22(c)は図21においてC-C'に沿って切った断面を矢印方向に見た断面図、図22(d)は図21においてD-D'に沿って切った断面を矢印方向に見た断面図、図22(e)は図21においてE-E'に沿って切った断面を矢印方向に見た断面図、図22(f)は図21においてF-F'に沿って切った断面を矢印方向に見た断面図である。

【図23】図23は、各メモリ溝に形成された一対のSi<sub>3</sub>N<sub>4</sub>部の間ににおいてP注入領域が露出した部分に白金シリサイド層を形成する工程を示す上面図である。

【図24】図24は、各メモリ溝に形成された一対のSi<sub>3</sub>N<sub>4</sub>部の間ににおいてP注入領域が露出した部分に白金シリサイド層を形成する工程を示す断面図であり、図24(a)は図23においてA-A'に沿って切った断面を矢印方向に見た断面図、図24(b)は図23においてB-B'に沿って切った断面を矢印方向に見た断面図、図24(c)は図23においてC-C'に沿って切った断面を矢印方向に見た断面図、図24(d)は図23においてD-D'に沿って切った断面を矢印方向に見た断面図、図24(e)は図23においてE-E'に沿って切った断面を矢印方向に見た断面図、図24(f)は図23においてF-F'に沿って切った断面を矢印方向に見た断面図である。

【図25】図25は、各メモリ溝の側面および底面を含む全面にタンタル酸化物層と窒化タンタル層とを形成する工程を示す上面図である。

【図26】図26は、各メモリ溝の側面および底面を含む全面にタンタル酸化物層と窒化タンタル層とを形成する工程を示す断面図であり、図26(a)は図25においてA-A'に沿って切った断面を矢印方向に見た断面図、図26(b)は図25においてB-B'に沿って切った断面を矢印方向に見た断面図、図26(c)は図25においてC-C'に沿って切った断面を矢印方向に見た断面図、図26(d)は図25においてD-D'に沿って切った断面を矢印方向に見た断面図、図26(e)は図25においてE-E'に沿って切った断面を矢印方向に見た断面図、図26(f)は図25においてF-F'に沿って切った断面を矢印方向に見た断面図である。

【図27】図27は、メモリ溝の内部に存在する部分を除いてタンタル酸化物層と窒化タンタル層とを除去する工程を示す上面図である。

【図28】図28は、メモリ溝の内部に存在する部分を除いてタンタル酸化物層と窒化タンタル層とを除去する工程を示す断面図であり、図28(a)は図27においてA-A'に沿って切った断面を矢印方向に見た断面図、図28(b)は図27においてB-B'に沿って切った断面を矢印方向に見た断面図、図28(c)は図27においてC-C'に沿

10

20

30

40

50

って切った断面を矢印方向に見た断面図、図28(d)は図27においてD-D'に沿って切った断面を矢印方向に見た断面図、図28(e)は図27においてE-E'に沿って切った断面を矢印方向に見た断面図、図28(f)は図27においてF-F'に沿って切った断面を矢印方向に見た断面図である。

【図29】図29は、窒化タンタル層の内側に形成された溝にタングステン層を形成すると共に凹部に二酸化珪素層を形成する工程を示す上面図である。

【図30】図30は、窒化タンタル層の内側に形成された溝にタングステン層を形成すると共に凹部に二酸化珪素層を形成する工程を示す断面図であり、図30(a)は図29においてA-A'に沿って切った断面を矢印方向に見た断面図、図30(b)は図29においてB-B'に沿って切った断面を矢印方向に見た断面図、図30(c)は図29においてC-C'に沿って切った断面を矢印方向に見た断面図、図30(d)は図29においてD-D'に沿って切った断面を矢印方向に見た断面図、図30(e)は図29においてE-E'に沿って切った断面を矢印方向に見た断面図、図30(f)は図29においてF-F'に沿って切った断面を矢印方向に見た断面図である。

10

【図31】図31は、全面に二酸化珪素層を形成し、さらにワード線を埋め込むための溝を形成する工程を示す上面図である。

【図32】図32は、全面に二酸化珪素層を形成し、さらにワード線を埋め込むための溝を形成する工程を示す断面図であり、図32(a)は図31においてA-A'に沿って切った断面を矢印方向に見た断面図、図32(b)は図31においてB-B'に沿って切った断面を矢印方向に見た断面図、図32(c)は図31においてC-C'に沿って切った断面を矢印方向に見た断面図、図32(d)は図31においてD-D'に沿って切った断面を矢印方向に見た断面図、図32(e)は図31においてE-E'に沿って切った断面を矢印方向に見た断面図、図32(f)は図31においてF-F'に沿って切った断面を矢印方向に見た断面図である。

20

【図33】図33は、トランジスタの制御電極(ゲート)を埋め込むためのホールを形成する工程を示す上面図である。

【図34】図34は、トランジスタの制御電極(ゲート)を埋め込むためのホールを形成する工程を示す断面図であり、図34(a)は図33においてA-A'に沿って切った断面を矢印方向に見た断面図、図34(b)は図33においてB-B'に沿って切った断面を矢印方向に見た断面図、図34(c)は図33においてC-C'に沿って切った断面を矢印方向に見た断面図、図34(d)は図33においてD-D'に沿って切った断面を矢印方向に見た断面図、図34(e)は図33においてE-E'に沿って切った断面を矢印方向に見た断面図、図34(f)は図33においてF-F'に沿って切った断面を矢印方向に見た断面図である。

30

【図35】図35は、ワード線とトランジスタの制御電極(ゲート)とを形成する工程を示す上面図である。

【図36】図36は、ワード線とトランジスタの制御電極(ゲート)とを形成する工程を示す断面図であり、図36(a)は図35においてA-A'に沿って切った断面を矢印方向に見た断面図、図36(b)は図35においてB-B'に沿って切った断面を矢印方向に見た断面図、図36(c)は図35においてC-C'に沿って切った断面を矢印方向に見た断面図、図36(d)は図35においてD-D'に沿って切った断面を矢印方向に見た断面図、図36(e)は図35においてE-E'に沿って切った断面を矢印方向に見た断面図、図36(f)は図35においてF-F'に沿って切った断面を矢印方向に見た断面図である。

40

【図37】図37は、ソース線を埋め込むための溝とコンタクトを埋め込むためのホールとを形成する工程を示す上面図である。

【図38】図38は、ソース線を埋め込むための溝とコンタクトを埋め込むためのホールとを形成する工程を示す断面図であり、図38(a)は図37においてA-A'に沿って切った断面を矢印方向に見た断面図、図38(b)は図37においてB-B'に沿って切った断面を矢印方向に見た断面図、図38(c)は図37においてC-C'に沿って切っ

50

た断面を矢印方向に見た断面図、図38(d)は図37においてD-D'に沿って切った断面を矢印方向に見た断面図、図38(e)は図37においてE-E'に沿って切った断面を矢印方向に見た断面図、図38(f)は図37においてF-F'に沿って切った断面を矢印方向に見た断面図である。

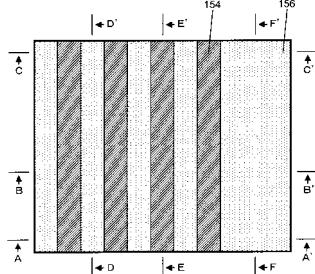

【図39】図39は、ソース線とコンタクトとを形成する工程を示す上面図である。

【図40】図40は、ソース線とコンタクトとを形成する工程を示す断面図であり、図40(a)は図39においてA-A'に沿って切った断面を矢印方向に見た断面図、図40(b)は図39においてB-B'に沿って切った断面を矢印方向に見た断面図、図40(c)は図39においてC-C'に沿って切った断面を矢印方向に見た断面図、図40(d)は図39においてD-D'に沿って切った断面を矢印方向に見た断面図、図40(e)は図39においてE-E'に沿って切った断面を矢印方向に見た断面図、図40(f)は図39においてF-F'に沿って切った断面を矢印方向に見た断面図である。 10

【図41】図41は、ビット線とコンタクトとを形成する工程を示す上面図である。

【図42】図42は、ビット線とコンタクトとを形成する工程を示す断面図であり、図42(a)は図41においてA-A'に沿って切った断面を矢印方向に見た断面図、図42(b)は図41においてB-B'に沿って切った断面を矢印方向に見た断面図、図42(c)は図41においてC-C'に沿って切った断面を矢印方向に見た断面図、図42(d)は図41においてD-D'に沿って切った断面を矢印方向に見た断面図、図42(e)は図41においてE-E'に沿って切った断面を矢印方向に見た断面図、図42(f)は図41においてF-F'に沿って切った断面を矢印方向に見た断面図である。 20

【図43】図43は、本発明の第1実施形態の変形例にかかる不揮発性記憶装置100の回路構成の一例を示すブロック図である。

【図44】図44は、本発明の第2実施形態にかかる不揮発性記憶装置200の回路構成の一例を示すブロック図である。

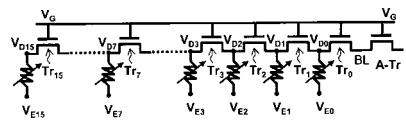

【図45】図45は、基板バイアス効果による電位降下をシミュレーションするための概念図である。

【図46】図46は、図45の概念図に基づいて基板バイアス効果による電位降下をシミュレーションにより求めた結果を示す図である。

【図47】図47は、特許文献2で示されているメモリセルの断面の模式図である。

【図48】図48は、特許文献3で開示されている回路図である。 30

#### 【発明を実施するための形態】

##### 【0033】

以下、本発明の好ましい実施の形態を、図面を参照しながら説明する。

##### 【0034】

(第1実施形態)

[装置構成]

図1は、本発明の第1実施形態に係る不揮発性記憶装置100の回路構成の一例を示すブロック図である。図2は、図1におけるメモリセルMCの部分を拡大した図である。なお、添え字は対応するメモリブロックの行または列の番号を示す。

##### 【0035】

図1および図2に示すように、不揮発性記憶装置100は、第1平面内において第1方向に互いに平行に伸びる複数のワード線WL<sub>0\_0</sub>、WL<sub>1\_0</sub>、WL<sub>2\_0</sub>、WL<sub>3\_0</sub>、WL<sub>1\_1</sub>、WL<sub>1\_1</sub>、…(第1配線、例えばタンゲステンからなる:以下単に「WL」とする)と、第1平面と平行な第2平面内において第2方向に互いに平行にかつ第1配線と立体交差するように伸びる複数のソース線SL<sub>0\_0</sub>、SL<sub>1\_0</sub>、SL<sub>2\_0</sub>、SL<sub>3\_0</sub>、SL<sub>0\_1</sub>、SL<sub>1\_1</sub>、…(第2配線、例えば銅からなる:以下単に「SL」とする)と、ワード線WLとソース線SLとの立体交差点のそれぞれに対応して設けられたメモリセルMC<sub>00\_0\_0</sub>、MC<sub>01\_0\_0</sub>、MC<sub>02\_0\_0</sub>、MC<sub>03\_0\_0</sub>、MC<sub>10\_0\_0</sub>、…MC<sub>33\_0\_0</sub>、…MC<sub>32\_m\_n</sub>、MC<sub>33\_m\_n</sub>(以下単に「MC」とする)とを備えている。 40

## 【0036】

メモリセルMCのそれぞれは1個のトランジスタTR（例えば、FETトランジスタ）と1個の抵抗変化型素子RR（例えば、ReRAM素子）とを備えている。トランジスタTRのそれぞれは第1主端子T1（ソース／ドレイン）と第2主端子T2（ソース／ドレイン）と制御端子T3（ゲート）とを備えている。抵抗変化型素子RRのそれぞれは第1電極E1（例えば、白金あるいは白金シリサイドからなる下部電極）と第2電極E2（例えば、窒化タンタルからなる上部電極）と第1電極E1および第2電極E2の間に設けられた抵抗変化層VR（例えば、TaやNi、Ti、Hf、Zrなどの遷移金属の酸化物を含む。タンタル酸化物を含むのが好ましく、タンタル酸化物からなるのがさらに好ましい。）とを備えている。

10

## 【0037】

第1方向に沿って並ぶ複数のメモリセルMCについて、隣接する2個のメモリセルMCに含まれる一方のメモリセルMCの第1主端子T1と他方のメモリセルMCの第2主端子T2とが接続されることで、複数のメモリセルの主端子を順次に直列に接続して第1方向に伸びる直列経路SP<sub>000</sub>、SP<sub>100</sub>、SP<sub>200</sub>、SP<sub>300</sub>、SP<sub>001</sub>、…（以下、単に「SP」とする）が形成されている。

## 【0038】

メモリセルMCのそれぞれについて、制御端子T3がそのメモリセルMCに対応するワード線WLに接続されている。

メモリセルMCのそれぞれについて、第2電極E2がそのメモリセルMCに対応するソース線SLに接続されている。第2電極E2はそのメモリセルMCに対応するソース線SLの一部であってもよい。

20

## 【0039】

メモリセルMCのそれぞれについて、第1電極E1がそのメモリセルMCに対応する直列経路SPに接続されている。第1電極E1はそのメモリセルMCに対応する直列経路SPの一部であってもよい。

## 【0040】

以上のような構成では、トランジスタ1個につき抵抗変化型素子が1個形成されることになる。すなわち、隣接する2個の抵抗変化型素子が、第1電極E1において1個のトランジスタを共有すると共に、第2電極E2がトランジスタに接続されずに配線に接続される。選択メモリセルに通流される電流は直列経路SPを流れ、非選択メモリセルの両電極間には流れない。かかる構成により、非選択メモリセルに流れる電流を効果的に抑制しつつ、4F<sup>2</sup>のメモリセルからなる1T1R型メモリセルアレイを備えた不揮発性記憶装置が実現される。

30

## 【0041】

不揮発性記憶装置100はさらに、第1方向に互いに平行に伸びる複数のビット線BL0、BL1、…（第3配線、例えば銅からなる：以下単に「BL」とする）を備え、第1方向に沿って並ぶ複数のメモリセルMCは、連続して並んだ所定個数のメモリセルMCにより複数のメモリブロックMBを構成し、それぞれのメモリブロックMB毎に直列経路SPが第2方向に伸びるコンタクト配線CL（例えば、白金シリサイドからなる：以下単に「CL」とする）を介してビット線BLと接続されている。

40

## 【0042】

かかる構成では、ビット線BLに抵抗率の低い導体を用いることで、直列経路における配線遅延を抑制することができる。

## 【0043】

本実施形態では、第1主端子T1および第2主端子T2はそれぞれシリサイド層を有し、このシリサイド層が第1電極E1を構成する。このシリサイド層は白金シリサイドからなるのが好ましい。

## 【0044】

かかる構成では、シリコン基板に形成されたシリサイドが抵抗変化型素子の電極に用い

50

られるため、素子サイズをさらに小形化できる。特に、白金は抵抗変化型素子の電極材料として好適であることから、シリサイド層は白金シリサイドからなることが望ましい。

#### 【 0 0 4 5 】

ソース線 S L は、それぞれカラムデコーダ 102 に接続されている。ワード線 W L およびビット線 B L は、それぞれロウデコーダ 104 に接続されている。メモリセル M C 、ワード線 W L 、ソース線 S L 、ビット線 B L 、コンタクト配線 C L 、カラムデコーダ 102 、ロウデコーダ 104 は、全体として 1 個のメモリセルアレイ 106 を構成する。

#### 【 0 0 4 6 】

メモリセルアレイ 106 には、m 行 n 列のメモリブロック M B が含まれる。それぞれのメモリブロック M B には、 $4 \times 4 = 16$  個のメモリセル M C が含まれる。メモリセルアレイ 106 全体では、 $16 m n$  個のメモリセル M C が含まれる。ワード線 W L の数は 4 m 、ソース線の数は 4 n 、ビット線の数は m 、コンタクト配線 C L の数は n である。

#### 【 0 0 4 7 】

同じ列 ( y 列 ) のメモリセルブロック  $M B_{x,y}$  に属するメモリセル M C は、メモリセルブロック  $M B_{x,y}$  内における列の番号 (  $4 \times 4$  のマトリクスにおける列番号 ) が同じものが、同一のソース線 S L で互いに接続されている。具体的には、例えば、1 列目のメモリセルブロック  $M B_{x,0}$  に属する左側から 1 番目 ( 1 列目 ) のメモリセル同士 (  $M C_{0,0,0}, M C_{1,0,0}, M C_{2,0,0}, M C_{3,0,0}, M C_{0,0,1,0}, \dots$  ) は同一のソース線 S L 0 で互いに接続され、左側から 2 番目 ( 2 列目 ) のメモリセル同士 (  $M C_{0,1,0,0}, M C_{1,1,0,0}, M C_{2,1,0,0}, M C_{3,1,0,0}, M C_{0,1,1,0}, \dots$  ) は同一のソース線 S L 1 で互いに接続される。

#### 【 0 0 4 8 】

不揮発性記憶装置 100 はさらに、外部からアドレス信号 A D を受け取ってメモリセルアレイ 106 へと送るアドレス入力回路 108 と、外部から制御信号 C T L を受け取ってメモリセルアレイ 106 へと送る制御回路 110 と、所定の電圧 ( 低抵抗化電圧、高抵抗化電圧などの書き込み電圧や、読み出し電圧など ) を出力する電源回路 112 と、外部とのデータの受け渡しを行うデータ入出力回路 114 と、データ入出力回路から出力される書き込みデータに基づいて電源回路 112 から出力される電圧をメモリセルアレイへと入力する書き込み回路 116 と、センスアンプ 120 とを備えている。センスアンプ 120 は、選択したビット線に流れる電流量を検出し、この電流量が、メモリセルが高抵抗状態である場合に対応する電流量のときをデータ「 1 」に、メモリセルが低抵抗状態である場合に対応する電流量のときをデータ「 0 」と判定する。

#### 【 0 0 4 9 】

電源回路 112 は、メモリセル M C を低抵抗化する ( メモリセル M C に含まれる抵抗変化型素子 R R を低抵抗状態とする ) 場合に印加される電圧を生成するための低抵抗化電圧生成回路 122 と、メモリセル M C を高抵抗化する ( メモリセル M C に含まれる抵抗変化型素子 R R を高抵抗状態とする ) 場合に印加される電圧を生成するための高抵抗化電圧生成回路 124 とを備えている。

#### 【 0 0 5 0 】

[ メモリブロックの概略構成 ]

図 3 は、1 個のメモリブロックを示す図であり、図 3 ( a ) はメモリブロックの上面図、図 3 ( b ) は図 3 ( a ) の等価回路図である。図 3 ( b ) は、図 1 におけるメモリブロック M B を抜き出して拡大したものになっている。

#### 【 0 0 5 1 】

図 3 ( a ) に示すように、ワード線 W L ( 第 1 配線 ) は第 1 平面内において第 1 方向 ( 図中の左右方向 ) に互いに平行に伸びており、ソース線 S L ( 第 2 配線 ) は第 1 平面と平行な第 2 平面内において第 2 方向 ( 図中の上下方向 ) に互いに平行にかつワード線 W L と立体交差するように伸びており、ビット線 B L ( 第 3 配線 ) は第 2 平面と平行な第 3 平面内において第 1 方向 ( 図中の左右方向 ) に互いに平行に伸びており、コンタクト配線 C L ( 第 4 配線 ) は第 3 平面と平行な第 4 平面内において第 2 方向 ( 図中の上下方向 ) に互いに平行に伸びてお

10

20

30

40

50

に平行に伸びている。

**【0052】**

ワード線WLとソース線SLとの立体交差点のそれぞれにはメモリセルMCと、トランジスタTRの第1主端子T1および第2主端子T2が設けられている。ワード線WLにおいて、ソース線SLと重ならない部分には、トランジスタTRの制御端子T3が設けられている。

**【0053】**

ビット線BLとソース線SLとの立体交差点の下方にはコンタクトC1（ソース線SLと第2電極E2との接続部）が設けられている。なお後述するように、本実施形態において第2電極E2は第2方向に伸びるように形成され、複数の抵抗変化型素子RRの上部電極として機能する。したがって、等価回路図（図3（b））ではメモリセル毎に第2電極E2がソース線SLと接続されているように見えるが、実際には第2電極E2はメモリセルブロック毎にソース線SLと接続される。ただし、回路としては図3（b）と等価である。

**【0054】**

ビット線BLとコンタクト配線CLとの立体交差点にはコンタクトC2（ビット線BLとコンタクト配線CLとの接続部）が設けられている。

**【0055】**

[メモリブロックの断面構成]

図4は、図3の一点鎖線で示したメモリブロックの断面を示す図であり、図4（a）は図3の線A-A'に沿って切った断面図、図4（b）は図3の線B-B'に沿って切った断面図、図4（c）は図3の線C-C'に沿って切った断面図、図4（d）は図3の線D-D'に沿って切った断面図、図4（e）は図3の線E-E'に沿って切った断面図、図4（f）は図3の線F-F'に沿って切った断面図である。以下、図4においてソース線SLが伸びる方向を前後方向、基板の厚み方向を上下方向、ワード線WLの伸びる方向を左右方向とする。図4において、同じメッシュ模様は原則的にほぼ同じ材料からなることを示す。ただし、同じメッシュ模様で示された部分であっても、詳細な組成や成分は異なる場合がある。

**【0056】**

図4に示すように、メモリブロックMBにおいては、P型シリコン基板層130の上に所定の間隔を置いて左右方向に伸びるように複数の二酸化珪素層132が形成されている。ただし、二酸化珪素層132の左端は前後方向に連続している。二酸化珪素層132のうち左右に伸びる部分は、STI [Shallow Trench Insulator] 領域を構成する。STI領域の大きさは、例えば幅0.18μm、深さ300nmである。

**【0057】**

二酸化珪素層132の上半分を前後方向に貫いて伸びるように複数の溝（以下、「メモリ溝」と呼ぶ。図4におけるメモリ溝の数は5）が形成されている。メモリ溝の大きさは、例えば幅0.18μm、深さ550nm（STI+ダミーゲート高さ）である。メモリ溝の左右の側壁部にSi<sub>3</sub>N<sub>4</sub>部138（サイドウォール）が形成されている。Si<sub>3</sub>N<sub>4</sub>部138の表面とメモリ溝の底面とを覆うようにタンタル酸化物層140（抵抗変化層）と、窒化タンタル層142（上部電極層）とがこの順に形成されている。タンタル酸化物層140の底部の厚みは例えば30nmである。窒化タンタル層142の内側に形成された溝を埋めるようにタンゲステン層144（埋込導体層）が形成されている。Si<sub>3</sub>N<sub>4</sub>部138とタンタル酸化物層140と窒化タンタル層142とタンゲステン層144とは、全体としてメモリ溝を埋めており、上端面は凹部を形成し、該凹部を二酸化珪素層148が埋めている。ただし、銅層154（ソース線SL）と窒化タンタル層142とが接続される部分（C-C'断面）においては、該凹部をチタン/窒化チタン層149（密着層）が埋めている。埋込導体層は銅やアルミニウムなどで形成してもよい。

**【0058】**

STI領域の形成されていない部分の上方には、ワード線WLを構成するタンゲステン

10

20

30

40

50

層 152 と、チタン / 窒化チタン層 150（密着層）とが、左右方向に伸びるように形成されている。タンゲステン層 152 の大きさは、例えば幅 0.18 μm、深さ 300 nm である。メモリ溝のない部分では、タンゲステン層 152 とチタン / 窒化チタン層 150 とは下方に伸び、二酸化珪素層 158 を介して P 型シリコン基板層 130 に接している。二酸化珪素層 158 の厚みは、例えば 10 nm である。タンゲステン層 152 が二酸化珪素層 158 を挟んで P 型シリコン基板層 130 と接続されている部分が、トランジスタ TR の制御端子 T3（ゲート）として機能する。制御端子 T3 の大きさは、例えば 0.18 μm × 0.18 μm である。

#### 【0059】

P 型シリコン基板層 130 とメモリ溝との接続部分には、P 注入領域 134（ソース / ドレイン領域）が形成されている。P 注入領域 134 の上には白金シリサイド層 136 が形成されている。P 注入領域 134 と白金シリサイド層 136 とは、P 型シリコン基板層 130 の内部に形成されている。P 注入領域 134 は、As 注入領域（リン原子 [P] の代わりに砒素原子 [As] を用いる）であってもよい。

#### 【0060】

5 本のメモリ溝のうち、最も右側のもの（以下、コントラクト配線溝）は STI 領域においても二酸化珪素層 132 が形成されておらず、メモリ溝と P 型シリコン基板層 130 とが接続されている。コントラクト配線溝の底面には、P 注入領域 134 と、白金シリサイド層 136 とが連続するように（前後方向に伸びるように）形成されている。コントラクト配線溝と接続する白金シリサイド層 136 は、コントラクト配線 CL を構成する。

#### 【0061】

コントラクト配線溝以外のメモリ溝と接続する白金シリサイド層 136 は、下部電極層（第 1 電極 E1）を構成する。窒化タンタル層 142 のうち下部電極層と対応する部分が、第 2 電極 E2 として機能する。タンタル酸化物層 140 のうち下部電極層と上部電極層とではさまれた部分が抵抗変化層 VR として機能する。A-A' 断面において、P 注入領域 134 と白金シリサイド層 136 とは、トランジスタ TR の第 1 主端子 T1（ソース / ドレイン）および第 2 主端子 T2（ソース / ドレイン）として機能する。

#### 【0062】

A-A' 断面において、タンゲステン層 152 が二酸化珪素層 158 を挟んで P 型シリコン基板層 130 と接続されている部分（ゲート）と、P 注入領域 134 と白金シリサイド層 136 とからなる部分（ソース / ドレイン）とが、左右方向に交互に連続的に並ぶことで、1 本の直列経路 SP が形成される。抵抗変化型素子 RR の下部電極を構成する白金シリサイド層 136 は、同時に、直列経路 SP の一部を構成する。トランジスタ TR の第 1 主端子 T1 および第 2 主端子 T2 の構成要素である P 注入領域 134 も、直列経路 SP の一部を構成する。

#### 【0063】

二酸化珪素層 156（層間絶縁層）を挟んでタンゲステン層 152 の上方に、前後方向に伸びるように、ソース線 SL を構成する銅層 154 が複数形成されている。C-C' 断面において、銅層 154 はチタン / 窒化チタン層 149（密着層）と接続されており、該接続部の銅層 154 はコントラクト 153（図 3 におけるコントラクト C1）を構成する。なお、図では示していないが、銅層 154 と二酸化珪素層 156 との境界部分にも密着層としてチタン / 窒化チタン層が形成されてもよい。

#### 【0064】

C-C' 断面において、二酸化珪素層 156（層間絶縁層）を挟んで銅層 154 の上方には左右方向に伸びるように、ビット線 BL を構成する銅層 162 が形成されている。F-F' 断面において銅層 162 は、白金シリサイド層 136 と接続されており、該接続部の銅層 162 はコントラクト 161（図 3 におけるコントラクト C2）を構成する。すなわち、この部分ではタンタル酸化物層 140 や窒化タンタル層 142 やタンゲステン層 144 は除去され、ビット線 BL と白金シリサイド層 136（コントラクト配線 CL）とはコントラクト 161 を介して短絡されている。なお、図では示していないが、銅層 162 と二酸化

10

20

30

40

50

珪素層 156 との境界部分にも密着層としてチタン / 窒化チタン層が形成されてもよい。

#### 【0065】

C - C' 断面においてメモリ溝同士の間には、下半分に製造過程に由来するポリシリコン層 160 が形成されている。ポリシリコン層 160 の厚みは、例えば 250 nm である。また、ポリシリコン層 160 の上および二酸化珪素層 132 の上には、製造過程に由来する Si<sub>3</sub>N<sub>4</sub> 層 146 が形成されている。Si<sub>3</sub>N<sub>4</sub> 層 146 の厚みは、例えば 50 nm である。

#### 【0066】

##### [ 抵抗変化型素子の特性 ]

図 5 は、本発明の第 1 実施形態にかかる不揮発性記憶装置に含まれる抵抗変化型素子の特性（電圧と抵抗値との関係）の一例を示す図である。

10

#### 【0067】

図 5 の例では、下部電極が白金（厚み 50 nm）、抵抗変化層がタンタル酸化物（TaO<sub>x</sub> と表記したとき、0 < x < 2.5）、上部電極が窒化タンタル（厚み 100 nm）であり、電極面積が 0.5 μm × 0.5 μm である抵抗変化型素子を作成した。タンタル酸化物はスパッタリング（300 °C）により形成した。

#### 【0068】

得られた抵抗変化型素子に対し、パルス幅 100 ns で、電圧を徐々に変えながら電気的パルスを印加した。毎回の印加の度に、50 mV の電圧を印加して電流を測定することで、抵抗変化型素子の抵抗値を得た。図のプロットでは、素子に実際に抵抗変化型素子に印加された電圧（上部電極と下部電極との間に発生した電圧）を示している。なお、電圧の極性は、上部電極を基準とした下部電極の電位で示す。すなわち、下部電極が上部電極よりも電位が高い場合をプラスとした。

20

#### 【0069】

図 5 に示すように、印加電圧が -0.8 V を下回ると抵抗変化型素子は高抵抗状態（約 10<sup>5</sup> Ω）から低抵抗状態（約 10<sup>4</sup> Ω）へと変化した。一方、印加電圧が +0.8 V を上回ると抵抗変化型素子は低抵抗状態から高抵抗状態へと変化した。

#### 【0070】

##### [ 動作 ]

以上のように構成された不揮発性記憶装置 100 について、その動作の概略を以下説明する。

30

#### 【0071】

図 6 は、本発明の第 1 実施形態にかかる不揮発性記憶装置の動作例を示すタイミングチャートであり、図 6 (a) はメモリセル MC0000 に “0” を書き込む場合（抵抗変化型素子 RR を低抵抗化させる場合）、図 6 (b) はメモリセル MC0000 に “1” を書き込む場合（抵抗変化型素子 RR を高抵抗化させる場合）、図 6 (c) はメモリセル MC0000 に書き込まれているデータを読み出す場合を示す。本実施形態においては、抵抗変化型素子 RR が低抵抗状態（LR）にある場合をデータ “0” に対応させ、抵抗変化型素子 RR が高抵抗状態（HR）にある場合をデータ “1” に対応させる。

#### 【0072】

40

図 6 (a) における V<sub>1</sub> は低抵抗化電圧生成回路 122 が出力する電圧である。図 5 に示した素子では、例えば V<sub>1</sub> = +1.5 V（図 5 における低抵抗化の閾値である -0.8 V より絶対値の大きな正の電圧）とすることができます。

#### 【0073】

図 6 (b) における V<sub>2</sub> は高抵抗化電圧生成回路 124 が出力する電圧である。図 5 に示した素子では、例えば V<sub>2</sub> = +1.5 V（図 5 における高抵抗化の閾値である +1.2 V より絶対値の大きな正の電圧）とすることができます。

#### 【0074】

図 6 (c) における V<sub>read</sub> は、センスアンプ 120 で発生された読出用電圧である。図 5 に示した素子では、例えば V<sub>read</sub> = +0.5 V（図 5 における低抵抗状態ディ

50

スタート境界電圧 [ 低抵抗状態にある抵抗変化型素子の抵抗値が変化しない上限の電圧 ] である + 0 . 8 V よりも絶対値の大きな正の電圧 ) とすることができます。

#### 【 0 0 7 5 】

図 6 における V D D は、不揮発性記憶素子 1 0 0 に外部から供給される電源電圧に対応しており、例えば + 4 . 5 V である。

#### 【 0 0 7 6 】

抵抗変化型素子 R R にデータ “ 0 ” を書き込む場合 ( 抵抗変化型素子 R R を低抵抗化する場合 ) 、図 6 ( a ) に示すように、まず選択ビット線 B L 0 および選択ソース線 S L 0 。の電圧を 0 V ( G N D ) に設定する。他のビット線 B L およびソース線 S L はハイインピーダンス状態に設定される。次に、選択ワード線 W L 0 。の電圧を V D D に設定する。

10 次に、選択ソース線 S L 0 。の電圧を所定時間だけ V 1 に設定した後で 0 V に戻す。すなわち、選択ソース線 S L 0 。に矩形の電圧パルス ( 電気的パルス ) を印加する。これにより、メモリセル M C 0 0 。に含まれる抵抗変化型素子 R R の電極間には、第 2 電極 E 2 ( 上部電極 ) を基準として第 1 電極 E 1 ( 下部電極 ) に - V 1 ( - 1 . 5 V ) の電圧が印加される。その結果、抵抗変化型素子 R R は高抵抗状態から低抵抗状態へと変化する。その後、選択ワード線 W L 0 0 の電圧が 0 V に設定され、データ “ 0 ” の書き込み動作が完了する。

#### 【 0 0 7 7 】

抵抗変化型素子 R R にデータ “ 1 ” を書き込む場合 ( 抵抗変化型素子 R R を高抵抗化する場合 ) 、図 6 ( b ) に示すように、まず選択ビット線 B L 0 および選択ソース線 S L 0 。の電圧を 0 V ( G N D ) に設定する。他のビット線 B L およびソース線 S L はハイインピーダンス状態に設定される。次に、選択ワード線 W L 0 。の電圧を V D D に設定する。

20 次に、選択ビット線 B L 0 の電圧を所定時間だけ V 2 に設定した後で 0 V に戻す。すなわち、選択ビット線 B L 0 に矩形の電圧パルス ( 電気的パルス ) を印加する。これにより、メモリセル M C 0 0 。に含まれる抵抗変化型素子 R R の電極間には、第 2 電極 E 2 ( 上部電極 ) を基準として第 1 電極 E 1 ( 下部電極 ) に + V 2 ( + 1 . 5 V ) の電圧が印加される。その結果、抵抗変化型素子 R R は低抵抗状態から高抵抗状態へと変化する。その後、選択ワード線 W L 0 0 の電圧が 0 V に設定され、データ “ 1 ” の書き込み動作が完了する。

#### 【 0 0 7 8 】

アドレス入力回路 1 0 8 は、外部回路 ( 図示せず ) からアドレス信号を受け取り、このアドレス信号に基づいて行アドレス信号をカラムデコーダ 1 0 2 へ出力するとともに、列アドレス信号をロウデコーダ 1 0 4 へ出力する。ここで、アドレス信号は、複数のメモリセルのうちの選択される特定のメモリセルのアドレスを示す信号である。

30

#### 【 0 0 7 9 】

制御回路 1 1 0 は、データの書き込みサイクルにおいては、データ入出力回路 1 1 4 に入力された入力データ D i n に応じて、書き込み用電圧の印加を指示する書き込み信号を書き込み回路 1 1 6 へ出力する。

#### 【 0 0 8 0 】

カラムデコーダ 1 0 2 は、アドレス入力回路 1 0 8 から出力された行アドレス信号を受け取り、この行アドレス信号に応じて、ロウデコーダ 1 0 4 より、複数のワード線のうちの選択されたワード線に対して、所定の電圧を印加する。また同様に、カラムデコーダ 1 0 2 は、アドレス入力回路 1 0 8 から出力された行アドレス信号を受け取り、この行アドレス信号に応じて、カラムデコーダ 1 0 2 より、複数のソース線のうちの選択されたソース線に対して、所定の電圧を印加する。

40

#### 【 0 0 8 1 】

また、ロウデコーダ 1 0 4 は、アドレス入力回路 1 0 8 から出力された列アドレス信号を受け取り、この列アドレス信号に応じて、複数のビット線のうちの何れかを選択し、その選択されたビット線に対して、書き込み用電圧または読み出し用電圧を印加する。

#### 【 0 0 8 2 】

書き込み回路 116 は、制御回路 110 から出力された書き込み信号を受け取った場合、ロウデコーダ 104 に対して選択されたビット線に対して書き込み用電圧の印加を指示する信号を出力する。書き込み用電源 112 は、低抵抗化用の L R 化用電源 122 と高抵抗化用の H R 化用電源 124 より構成され、その出力は各々、ロウデコーダ 104 および書き込み回路 116 に入力されている。

#### 【0083】

抵抗変化型素子 R R に書き込まれているデータを読み出す場合、図 6 (c) に示すように、まず選択ビット線 B L 0 および選択ソース線 S L 0 の電圧を 0 V (GND) に設定する。他のビット線 B L およびソース線 S L はハイインピーダンス状態に設定される。次に、選択ワード線 W L 0 の電圧を V D D に設定する。次に、選択ビット線 B L 0 の電圧を所定時間だけ V r e a d に設定した後で 0 V に戻す。これは、クランプ回路 118 により供給される電圧を選択ビット線 B L 0 に供給することで行われる。センスアンプ 120 により、選択されたメモリセル M C 0 0 に流れる電流値を検出することで、抵抗変化型素子 R R が低抵抗状態にあるか(データが“0”であるか)、高抵抗状態にあるか(データが“1”であるか)が判定される。その後、選択ワード線 W L 0 0 の電圧が 0 V に設定され、データの読み出し動作が完了する。

#### 【0084】

##### [製造方法]

図 7 ~ 図 42 は、本発明の第 1 実施形態の不揮発性記憶装置を製造する工程を示す図である。なお、不揮発性記憶装置 100 を製造するためには、図 7 ~ 42 以外の工程も必要であるが、それらの工程については周知の方法を用いることができるため記載を省略する。

#### 【0085】

図 7 および図 8 は、それぞれ、P 型シリコン基板上にポリシリコン層を形成する工程を示す上面図および断面図である。図 8 (a) は図 7 において A - A' に沿って切った断面を矢印方向に見た断面図、図 8 (b) は図 7 において B - B' に沿って切った断面を矢印方向に見た断面図、図 8 (c) は図 7 において C - C' に沿って切った断面を矢印方向に見た断面図、図 8 (d) は図 7 において D - D' に沿って切った断面を矢印方向に見た断面図、図 8 (e) は図 7 において E - E' に沿って切った断面を矢印方向に見た断面図、図 8 (f) は図 7 において F - F' に沿って切った断面を矢印方向に見た断面図である。

#### 【0086】

P 型シリコン基板上にポリシリコン層を形成する工程(ステップ S 1)では、P 型シリコン層 130 からなる P 型シリコン基板の上に、ポリシリコンが C V D 法(条件は、例えにより堆積されることにより、ポリシリコン層 160 が形成される。なお、ダミーゲートの高さは、ドライエッチング特性等のプロセスに最適化された膜厚にて行うことが望ましい。

#### 【0087】

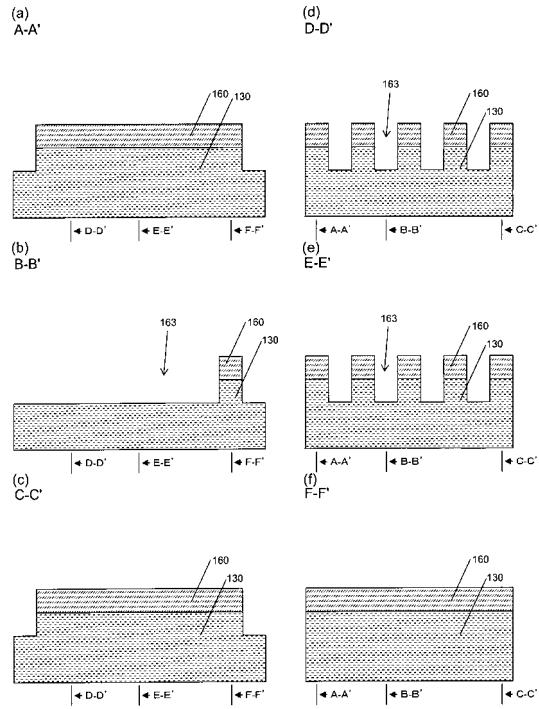

図 9 および図 10 は、それぞれ、P 型シリコン基板とポリシリコン層とをエッチングして S T I を形成するための溝を形成する工程を示す上面図および断面図である。図 10 (a) は図 9 において A - A' に沿って切った断面を矢印方向に見た断面図、図 10 (b) は図 9 において B - B' に沿って切った断面を矢印方向に見た断面図、図 10 (c) は図 9 において C - C' に沿って切った断面を矢印方向に見た断面図、図 10 (d) は図 9 において D - D' に沿って切った断面を矢印方向に見た断面図、図 10 (e) は図 9 において E - E' に沿って切った断面を矢印方向に見た断面図、図 10 (f) は図 9 において F - F' に沿って切った断面を矢印方向に見た断面図である。

#### 【0088】

P 型シリコン基板とポリシリコン層とをエッチングして S T I を形成するための溝 163 を形成する工程(ステップ S 2)では、マスクを用いたパターニング工程により、所望の溝が形成される。

#### 【0089】

10

20

30

40

50

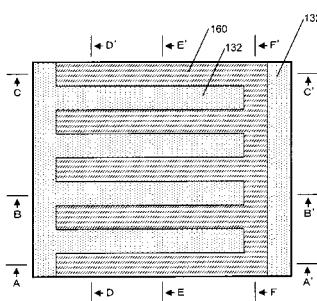

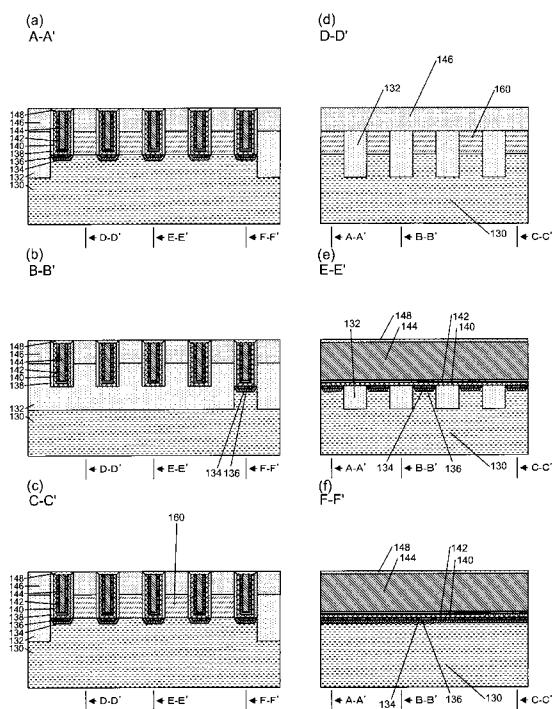

図11および図12は、それぞれ、溝に二酸化珪素を埋め込むことでSTIを形成する工程を示す上面図および断面図である。図12(a)は図11においてA-A'に沿って切った断面を矢印方向に見た断面図、図12(b)は図11においてB-B'に沿って切った断面を矢印方向に見た断面図、図12(c)は図11においてC-C'に沿って切った断面を矢印方向に見た断面図、図12(d)は図11においてD-D'に沿って切った断面を矢印方向に見た断面図、図12(e)は図11においてE-E'に沿って切った断面を矢印方向に見た断面図、図12(f)は図11においてF-F'に沿って切った断面を矢印方向に見た断面図である。

#### 【0090】

溝に二酸化珪素を埋め込むことでSTIを形成する工程(ステップS3)では、ステップS2で形成された溝163を埋めるように二酸化珪素(SiO<sub>2</sub>)(HDP-NSG膜)をHDP-CVD法(600nm)により堆積させ、CMPによりポリシリコン層160の上端面に達するまで二酸化珪素を除去することで、二酸化珪素層130が形成される。

#### 【0091】

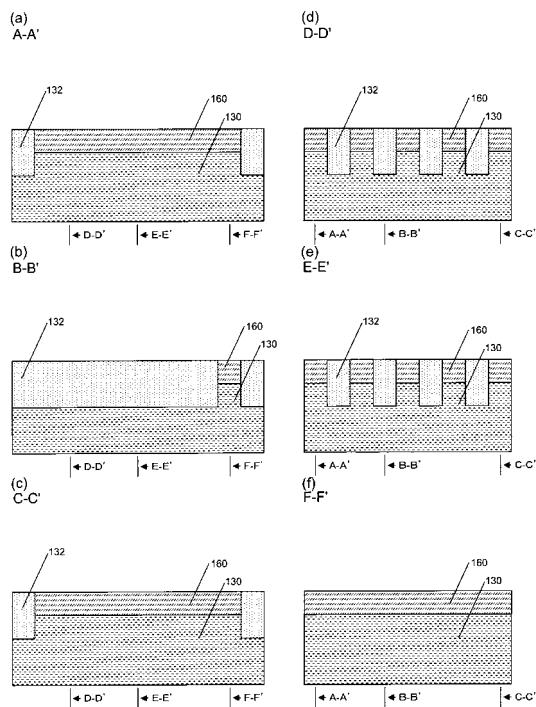

図13および図14は、それぞれ、二酸化珪素層とポリシリコン層とを覆うようにSi<sub>3</sub>N<sub>4</sub>層を形成する工程を示す上面図および断面図である。図14(a)は図13においてA-A'に沿って切った断面を矢印方向に見た断面図、図14(b)は図13においてB-B'に沿って切った断面を矢印方向に見た断面図、図14(c)は図13においてC-C'に沿って切った断面を矢印方向に見た断面図、図14(d)は図13においてD-D'に沿って切った断面を矢印方向に見た断面図、図14(e)は図13においてE-E'に沿って切った断面を矢印方向に見た断面図、図14(f)は図13においてF-F'に沿って切った断面を矢印方向に見た断面図である。

#### 【0092】

二酸化珪素層とポリシリコン層とを覆うようにSi<sub>3</sub>N<sub>4</sub>層を形成する工程(ステップS4)では、全面にCVD法によりSi<sub>3</sub>N<sub>4</sub>が堆積されることにより、Si<sub>3</sub>N<sub>4</sub>層146が形成される。

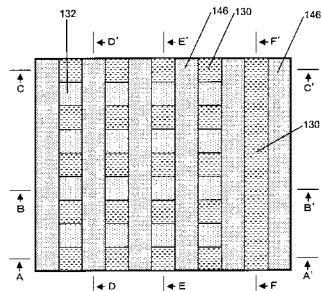

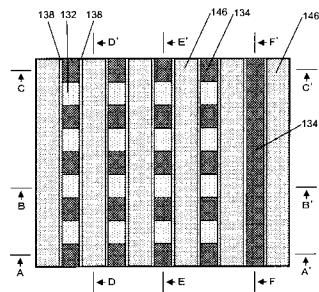

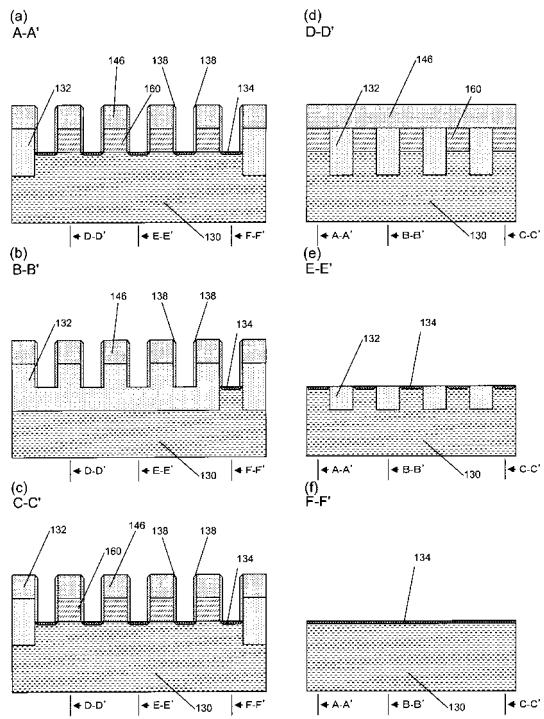

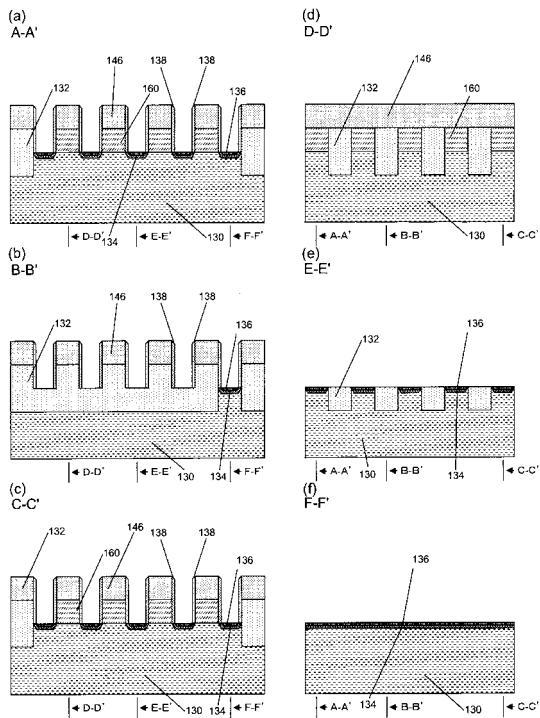

#### 【0093】

図15および図16は、それぞれ、メモリ溝を形成する工程を示す上面図および断面図である。図16(a)は図15においてA-A'に沿って切った断面を矢印方向に見た断面図、図16(b)は図15においてB-B'に沿って切った断面を矢印方向に見た断面図、図16(c)は図15においてC-C'に沿って切った断面を矢印方向に見た断面図、図16(d)は図15においてD-D'に沿って切った断面を矢印方向に見た断面図、図16(e)は図15においてE-E'に沿って切った断面を矢印方向に見た断面図、図16(f)は図15においてF-F'に沿って切った断面を矢印方向に見た断面図である。

#### 【0094】

メモリ溝を形成する工程(ステップS5)では、図15の上下方向(第2方向)に伸びるように、所定の幅と間隔で、Si<sub>3</sub>N<sub>4</sub>層146とポリシリコン層160と二酸化珪素層132とが除去されて、メモリ溝164が形成される。メモリ溝の底面は平坦であり、その位置は、ポリシリコン層160の底面と一致するように調整される。図16(a)において、5本形成されるメモリ溝164のうち、最も右側がコンタクト配線溝166となる。

#### 【0095】

図17および図18は、それぞれ、各メモリ溝の底面においてP型シリコン基板が露出した部分にリン原子(P)を注入する工程を示す上面図および断面図である。図18(a)は図17においてA-A'に沿って切った断面を矢印方向に見た断面図、図18(b)は図17においてB-B'に沿って切った断面を矢印方向に見た断面図、図18(c)は図17においてC-C'に沿って切った断面を矢印方向に見た断面図、図18(d)は図17においてD-D'に沿って切った断面を矢印方向に見た断面図、図18(e)は図17においてE-E'に沿って切った断面を矢印方向に見た断面図である。

10

20

30

40

50

7においてE-E'に沿って切った断面を矢印方向に見た断面図、図18(f)は図17においてF-F'に沿って切った断面を矢印方向に見た断面図である。

#### 【0096】

各メモリ溝の底面においてP型シリコン基板が露出した部分にリン原子(P)を注入する工程(ステップS6)では、イオン注入法により、ステップS5で形成されたメモリ溝164の底面に低エネルギーでリン原子(P)を注入し、さらに高速アニールによりP注入領域134が形成される。メモリ溝164の底面において、P型シリコン基板層130が露出している部分にのみリン原子が注入され、P注入領域134が形成される。メモリ溝164の底面において、二酸化珪素層132が露出している部分にはリン原子は注入されず、P注入領域134も形成されない。したがって、コンタクト配線溝166の底面には、全面に渡ってP注入領域134が形成される。一方、その他のメモリ溝164の底面には、所定の間隔で島状に、P注入領域134が形成される(図17参照)。なお、リン原子の代わりに砒素(As)原子を注入してもよい。10

#### 【0097】

図19および図20は、それぞれ、各メモリ溝の左右の側壁にSi<sub>3</sub>N<sub>4</sub>部(サイドウォール)を形成する工程を示す上面図および断面図である。図20(a)は図19においてA-A'に沿って切った断面を矢印方向に見た断面図、図20(b)は図19においてB-B'に沿って切った断面を矢印方向に見た断面図、図20(c)は図19においてC-C'に沿って切った断面を矢印方向に見た断面図、図20(d)は図19においてD-D'に沿って切った断面を矢印方向に見た断面図、図20(e)は図19においてE-E'に沿って切った断面を矢印方向に見た断面図、図20(f)は図19においてF-F'に沿って切った断面を矢印方向に見た断面図である。20

#### 【0098】

各メモリ溝の左右の側壁にSi<sub>3</sub>N<sub>4</sub>部(サイドウォール)を形成する工程(ステップS7)では、Si<sub>3</sub>N<sub>4</sub>がCVD法により全面に70nm堆積され、さらにドライエッティングによりメモリ溝の側面以外に付着したSi<sub>3</sub>N<sub>4</sub>が除去されることで、Si<sub>3</sub>N<sub>4</sub>部138が形成される。

#### 【0099】

図21および図22は、それぞれ、各メモリ溝に形成された一対のSi<sub>3</sub>N<sub>4</sub>部の間ににおいてP型シリコン基板が露出した部分にリン原子(P)を注入する工程を示す上面図および断面図である。図22(a)は図21においてA-A'に沿って切った断面を矢印方向に見た断面図、図22(b)は図21においてB-B'に沿って切った断面を矢印方向に見た断面図、図22(c)は図21においてC-C'に沿って切った断面を矢印方向に見た断面図、図22(d)は図21においてD-D'に沿って切った断面を矢印方向に見た断面図、図22(e)は図21においてE-E'に沿って切った断面を矢印方向に見た断面図、図22(f)は図21においてF-F'に沿って切った断面を矢印方向に見た断面図である。30

#### 【0100】

各メモリ溝に形成された一対のSi<sub>3</sub>N<sub>4</sub>部の間ににおいてP型シリコン基板が露出した部分にリン原子(P)を注入する工程(ステップS8)では、イオン注入法により、ステップS7で形成されたSi<sub>3</sub>N<sub>4</sub>部(サイドウォール)の間に、低エネルギーでリン原子(P)を注入し、さらに高速アニールによりP注入領域134がさらに深く形成される。ステップS6と同様、二酸化珪素層132が露出している部分にはリン原子は注入されず、P注入領域134も形成されない。40

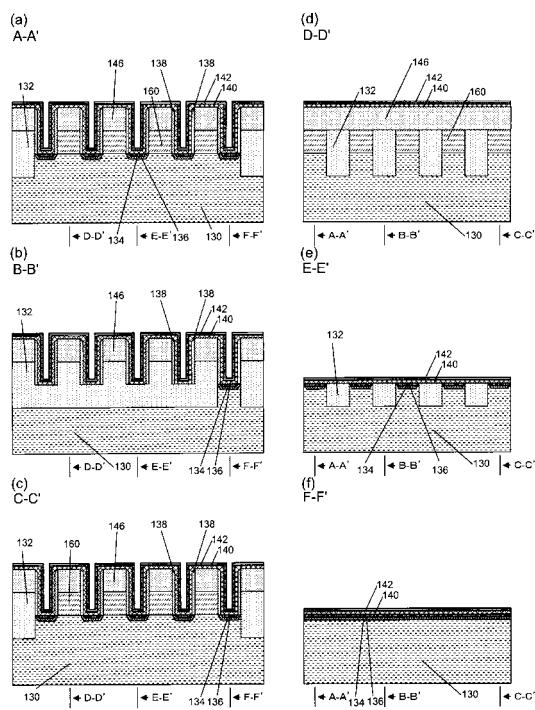

#### 【0101】

図23および図24は、それぞれ、各メモリ溝に形成された一対のSi<sub>3</sub>N<sub>4</sub>部の間ににおいてP注入領域が露出した部分に白金シリサイド層を形成する工程を示す上面図および断面図である。図24(a)は図23においてA-A'に沿って切った断面を矢印方向に見た断面図、図24(b)は図23においてB-B'に沿って切った断面を矢印方向に見た断面図、図24(c)は図23においてC-C'に沿って切った断面を矢印方向に見た50

断面図、図24(d)は図23においてD-D'に沿って切った断面を矢印方向に見た断面図、図24(e)は図23においてE-E'に沿って切った断面を矢印方向に見た断面図、図24(f)は図23においてF-F'に沿って切った断面を矢印方向に見た断面図である。

#### 【0102】

各メモリ溝に形成された一対のSi<sub>3</sub>N<sub>4</sub>部の間においてP注入領域が露出した部分に白金シリサイド層を形成する工程(ステップS9)では、まずスパッタリング(条件は、例えば5nm)により白金がメモリ溝の底面に堆積される。次に、アニーリング(条件は、例えば500、10分)によりP注入領域134と堆積された白金層との境界部分において白金シリサイドが生成する。これにより、白金シリサイド層136が形成される。余分な白金層は、標準プロセスにより除去される。

10

#### 【0103】

図25および図26は、それぞれ、各メモリ溝の側面および底面を含む全面にタンタル酸化物層と窒化タンタル層とを形成する工程を示す上面図および断面図である。図26(a)は図25においてA-A'に沿って切った断面を矢印方向に見た断面図、図26(b)は図25においてB-B'に沿って切った断面を矢印方向に見た断面図、図26(c)は図25においてC-C'に沿って切った断面を矢印方向に見た断面図、図26(d)は図25においてD-D'に沿って切った断面を矢印方向に見た断面図、図26(e)は図25においてE-E'に沿って切った断面を矢印方向に見た断面図、図26(f)は図25においてF-F'に沿って切った断面を矢印方向に見た断面図である。

20

#### 【0104】

各メモリ溝の側面および底面を含む全面にタンタル酸化物層と窒化タンタル層とを形成する工程(ステップS10)では、スパッタリング(例えば、反応性スパッタリング法では成膜時の酸素流量を高くすれば酸素含有率が高くすることができ、ここではアルゴン34sccm、酸素24sccm、パワー1.6kWの条件で、酸素含有率72atm%程度)によりタンタル酸化物が堆積されてタンタル酸化物層140が形成される。次に、タンタルターゲットをアルゴンと窒素ガス雰囲気中でスパッタリングする、いわゆる、反応性スパッタリングにより窒化タンタルが堆積されて窒化タンタル層142が形成される。このとき、タンタル酸化物層の厚みは、段差被覆性(側壁部と平面部との大きさの比)を考慮して、側壁部の厚みが適切に(例えば3nm)確保されるように決定される。すなわち、段差被覆性が10%の場合、平面部(メモリ溝の底面を含む)の厚みが30nmとなるようにタンタル酸化物が堆積される。このとき、側壁部のタンタル酸化物層140の厚みは約3nmとなる。

30

#### 【0105】

図27および図28は、それぞれ、メモリ溝の内部に存在する部分を除いてタンタル酸化物層と窒化タンタル層とを除去する工程を示す上面図および断面図である。図28(a)は図27においてA-A'に沿って切った断面を矢印方向に見た断面図、図28(b)は図27においてB-B'に沿って切った断面を矢印方向に見た断面図、図28(c)は図27においてC-C'に沿って切った断面を矢印方向に見た断面図、図28(d)は図27においてD-D'に沿って切った断面を矢印方向に見た断面図、図28(e)は図27においてE-E'に沿って切った断面を矢印方向に見た断面図、図28(f)は図27においてF-F'に沿って切った断面を矢印方向に見た断面図である。

40

#### 【0106】

メモリ溝の内部に存在する部分を除いてタンタル酸化物層と窒化タンタル層とを除去する工程(ステップS11)では、CMPにより、メモリ溝の内部に存在する部分を除いてタンタル酸化物層140と窒化タンタル層142とが除去される。このとき、CMPの研磨圧力を大きくしたり、研磨時間を長くすることで、タンタル酸化物層140と窒化タンタル層142の上端面がSi<sub>3</sub>N<sub>4</sub>層146の上端面より低くなるよう調整される。なお、これはCMPの条件を調整することの他、エッチバックによっても行うことができる。

#### 【0107】

50

図29および図30は、それぞれ、窒化タンタル層の内側に形成された溝にタングステン層を形成すると共に凹部に二酸化珪素層を形成する工程を示す上面図および断面図である。図30(a)は図29においてA-A'に沿って切った断面を矢印方向に見た断面図、図30(b)は図29においてB-B'に沿って切った断面を矢印方向に見た断面図、図30(c)は図29においてC-C'に沿って切った断面を矢印方向に見た断面図、図30(d)は図29においてD-D'に沿って切った断面を矢印方向に見た断面図、図30(e)は図29においてE-E'に沿って切った断面を矢印方向に見た断面図、図30(f)は図29においてF-F'に沿って切った断面を矢印方向に見た断面図である。

#### 【0108】

窒化タンタル層の内側に形成された溝にタングステン層を形成すると共に凹部に二酸化珪素層を形成する工程(ステップS12)では、窒化タンタル層142の内側に形成された、前後方向に伸びる溝を埋めるようにタングステン層144が形成される。これは、CVDとCMPにより行われる。次に、Si<sub>3</sub>N<sub>4</sub>層138(サイドウォール)と、タンタル酸化物層140と、窒化タンタル層142と、タングステン層144とがなす凹部に二酸化珪素が充填されて、二酸化珪素層148が形成される。これは、CVDによるTEOSを形成(例えば50nm)とCMPにより行われる。

10

#### 【0109】

図31および図32は、それぞれ、全面に二酸化珪素層を形成し、さらにワード線を埋め込むための溝を形成する工程を示す上面図および断面図である。図32(a)は図31においてA-A'に沿って切った断面を矢印方向に見た断面図、図32(b)は図31においてB-B'に沿って切った断面を矢印方向に見た断面図、図32(c)は図31においてC-C'に沿って切った断面を矢印方向に見た断面図、図32(d)は図31においてD-D'に沿って切った断面を矢印方向に見た断面図、図32(e)は図31においてE-E'に沿って切った断面を矢印方向に見た断面図、図32(f)は図31においてF-F'に沿って切った断面を矢印方向に見た断面図である。

20

#### 【0110】

全面に二酸化珪素層を形成し、さらにワード線WLを埋め込むための溝を形成する工程(ステップS13)では、二酸化珪素をCVDによるTEOSを堆積した上で、マスクを用いたエッチングでその一部を除去することで、ワード線WLを埋め込むための溝168が形成され、トランジスタの制御電極T3(ゲート)が形成される部分のSi<sub>3</sub>N<sub>4</sub>層146が露出される(図31参照)。

30

#### 【0111】

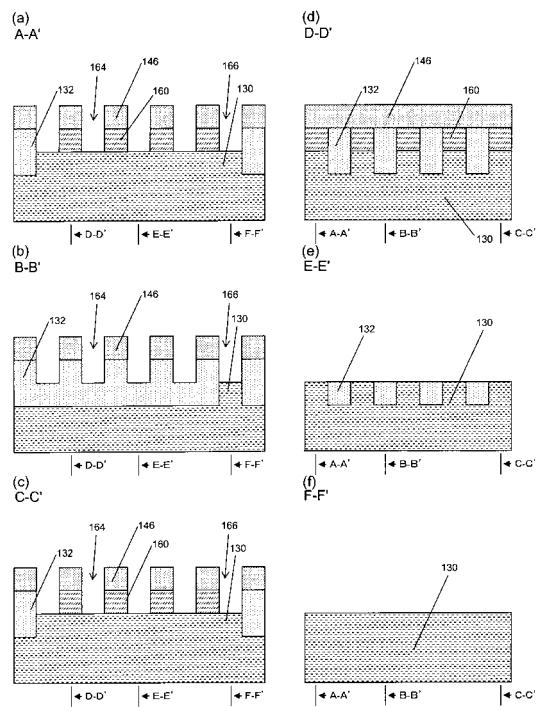

図33および図34は、それぞれ、トランジスタの制御電極(ゲート)を埋め込むためのホールを形成する工程を示す上面図および断面図である。図34(a)は図33においてA-A'に沿って切った断面を矢印方向に見た断面図、図34(b)は図33においてB-B'に沿って切った断面を矢印方向に見た断面図、図34(c)は図33においてC-C'に沿って切った断面を矢印方向に見た断面図、図34(d)は図33においてD-D'に沿って切った断面を矢印方向に見た断面図、図34(e)は図33においてE-E'に沿って切った断面を矢印方向に見た断面図、図34(f)は図33においてF-F'に沿って切った断面を矢印方向に見た断面図である。

40

#### 【0112】

トランジスタの制御電極(ゲート)を埋め込むためのホールを形成する工程(ステップS14)では、マスクを用いたドライエッチングでトランジスタの制御電極T3(ゲート)が形成される部分のSi<sub>3</sub>N<sub>4</sub>層146を除去する。ポリシリコン層160は、TMAHなどのアルカリ溶液に溶けるが、CF<sub>4</sub>+O<sub>2</sub>のケミカルドライエッチングを用いても良い。これにより、トランジスタの制御電極(ゲート)を埋め込むためのホール170が形成される。

#### 【0113】

図35および図36は、それぞれ、ワード線とトランジスタの制御電極(ゲート)とを形成する工程を示す上面図および断面図である。図36(a)は図35においてA-A'

50

に沿って切った断面を矢印方向に見た断面図、図36(b)は図35においてB-B'に沿って切った断面を矢印方向に見た断面図、図36(c)は図35においてC-C'に沿って切った断面を矢印方向に見た断面図、図36(d)は図35においてD-D'に沿って切った断面を矢印方向に見た断面図、図36(e)は図35においてE-E'に沿って切った断面を矢印方向に見た断面図、図36(f)は図35においてF-F'に沿って切った断面を矢印方向に見た断面図である。

#### 【0114】

ワード線とトランジスタの制御電極T3(ゲート)とを形成する工程(ステップS15)では、まずスパッタ法によりチタン/窒化チタン層150(密着層)が形成され、さらにメッキ法によりタンクステン層152(ワード線WLおよび制御電極T3)が形成される。

10

#### 【0115】

図37および図38は、それぞれ、ソース線を埋め込むための溝とコンタクトを埋め込むためのホールとを形成する工程を示す上面図および断面図である。図38(a)は図37においてA-A'に沿って切った断面を矢印方向に見た断面図、図38(b)は図37においてB-B'に沿って切った断面を矢印方向に見た断面図、図38(c)は図37においてC-C'に沿って切った断面を矢印方向に見た断面図、図38(d)は図37においてD-D'に沿って切った断面を矢印方向に見た断面図、図38(e)は図37においてE-E'に沿って切った断面を矢印方向に見た断面図、図38(f)は図37においてF-F'に沿って切った断面を矢印方向に見た断面図である。

20

#### 【0116】

ソース線SLを埋め込むための溝とコンタクトC1を埋め込むためのホールとを形成する工程(ステップS16)では、二酸化珪素を熱酸化法(条件は、例えば10nm)により堆積した上で、マスクを用いたエッチングでその一部を除去することで、ソース線SLを埋め込むための溝172とコンタクトC1を埋め込むためのホール174とが形成される。

#### 【0117】

図39および図40は、それぞれ、ソース線とコンタクトとを形成する工程を示す上面図および断面図である。図40(a)は図39においてA-A'に沿って切った断面を矢印方向に見た断面図、図40(b)は図39においてB-B'に沿って切った断面を矢印方向に見た断面図、図40(c)は図39においてC-C'に沿って切った断面を矢印方向に見た断面図、図40(d)は図39においてD-D'に沿って切った断面を矢印方向に見た断面図、図40(e)は図39においてE-E'に沿って切った断面を矢印方向に見た断面図、図40(f)は図39においてF-F'に沿って切った断面を矢印方向に見た断面図である。

30

#### 【0118】

ソース線とコンタクトとを形成する工程(ステップS17)では、ステップS16で形成された溝172とホール174とに、ダマシンプロセスにより銅が埋め込まれ、CMPにより余分な銅が除去される。これにより、銅層154とコンタクト153(図3におけるコンタクトC1)とが形成される。

40

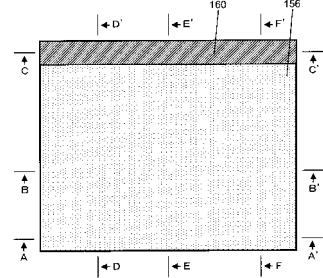

#### 【0119】

図41および図42は、それぞれ、ビット線とコンタクトとを形成する工程を示す上面図および断面図である。図42(a)は図41においてA-A'に沿って切った断面を矢印方向に見た断面図、図42(b)は図41においてB-B'に沿って切った断面を矢印方向に見た断面図、図42(c)は図41においてC-C'に沿って切った断面を矢印方向に見た断面図、図42(d)は図41においてD-D'に沿って切った断面を矢印方向に見た断面図、図42(e)は図41においてE-E'に沿って切った断面を矢印方向に見た断面図、図42(f)は図41においてF-F'に沿って切った断面を矢印方向に見た断面図である。

#### 【0120】

10

20

30

40

50

ビット線とコンタクトとを形成する工程（ステップS18）では、銅層154とコンタクト153とを覆うように、前面に二酸化珪素をCVDによるTEOSを堆積した上で、マスクを用いたエッティングでその一部を除去することで、ビット線BLを埋め込むための溝とコンタクトC2を埋め込むためのホールとが形成される。この溝とホールとに、ダマシンプロセスにより銅が埋め込まれ、CMPにより余分な銅が除去される。これにより、銅層162とコンタクト161（図3におけるコンタクトC2）とが形成される。

#### 【0121】

以上の工程により、図3および図4に示すメモリブロックが製造される（図42は図4と同一である）。

#### 【0122】

10

##### [変形例]

図43は、本発明の第1実施形態の変形例にかかる不揮発性記憶装置100'の回路構成の一例を示すブロック図である。図43に示すように、それぞれのメモリブロック毎に直列経路のそれぞれの両端がビット線（第3配線）と接続されていてもよい。

#### 【0123】

かかる構成は、図3および図4において、SL0の左側にコンタクト配線CLを一本追加し、これをコンタクトC2を介してビット線BL0と接続することにより得られる。追加されるコンタクト配線の構成は、第1実施形態のコンタクト配線と同様とすることができる。具体的な構成および製造方法の詳細は、上述の説明から当業者にとって明らかであるため、省略する。

20

#### 【0124】

かかる構成では、直列経路の両側から電位が伝播するため、配線遅延がより効果的に抑制される。

#### 【0125】

なお、本変形例において、直列経路SPとビット線BLとの接続関係以外は、図1に示した実施形態と同様である。よって、図1と図43とで共通する要素には同一の符号および名称を付して説明を省略する。

#### 【0126】

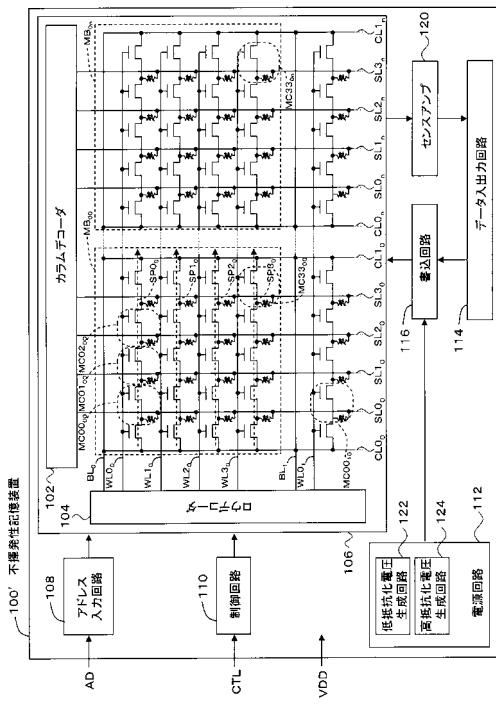

##### (第2実施形態)

図44は、本発明の第2実施形態にかかる不揮発性記憶装置の回路構成の一例を示すブロック図である。

30

#### 【0127】

第2実施形態の不揮発性記憶装置200は、それぞれのメモリセルに含まれる抵抗変化型素子に電圧を印加するための電源回路113を備え、電源回路113は、選択されたメモリセルについて、対応する直列経路SPと対応するビット線（第3配線）との接続部からそのメモリセルMCの第1電極E1までの直列経路SPに含まれるトランジスタTRの数に応じて出力する電圧を変化させるように構成されている。

#### 【0128】

より具体的には、不揮発性記憶装置200は、図1の不揮発性記憶装置100において、電源回路112を電源回路113とし、高抵抗化電圧生成回路124を、第1高抵抗化電圧生成回路125と第2高抵抗化電圧生成回路126と第3高抵抗化電圧生成回路127と第4高抵抗化電圧生成回路128とに置き換えたものであり、その他の構成は不揮発性記憶装置100と同一である。よって、図1と図44とで共通する要素には同一の符号および名称を付して説明を省略する。

40

#### 【0129】

第1高抵抗化電圧生成回路125は、メモリブロックの左から一列目に位置するメモリセルMCを高抵抗化する場合に、選択ビット線BLに印加する電圧V2。（第1高抵抗化電圧）を出力する。直列経路SPのうち、該メモリセルに含まれる抵抗変化型素子RRの第1電極E1とビット線BLとを結ぶ部分にh組まれるトランジスタの数は4個である。

#### 【0130】

50

第2高抵抗化電圧生成回路126は、メモリブロックの左から二列目に位置するメモリセルMCを高抵抗化する場合に、選択ビット線BLに印加する電圧V2<sub>1</sub>（第2高抵抗化電圧）を出力する。直列経路SPのうち、該メモリセルに含まれる抵抗変化型素子RRの第1電極E1とビット線BLとを結ぶ部分にh組まれるトランジスタの数は3個である。

## 【0131】

第3高抵抗化電圧生成回路127は、メモリブロックの左から三列目に位置するメモリセルMCを高抵抗化する場合に、選択ビット線BLに印加する電圧V2<sub>2</sub>（第3高抵抗化電圧）を出力する。直列経路SPのうち、該メモリセルに含まれる抵抗変化型素子RRの第1電極E1とビット線BLとを結ぶ部分にh組まれるトランジスタの数は2個である。

## 【0132】

第4高抵抗化電圧生成回路128は、メモリブロックの左から四列目に位置するメモリセルMCを高抵抗化する場合に、選択ビット線BLに印加する電圧V2<sub>3</sub>（第4高抵抗化電圧）を出力する。直列経路SPのうち、該メモリセルに含まれる抵抗変化型素子RRの第1電極E1とビット線BLとを結ぶ部分にh組まれるトランジスタの数は1個である。

## 【0133】

電圧V2<sub>0</sub>と電圧V2<sub>1</sub>と電圧V2<sub>2</sub>と電圧V2<sub>3</sub>とは、それぞれ、各列に配設されたメモリセルの第1電極E1とビット線BLとを結ぶ最短の直列経路の経路長（抵抗変化型素子とビット線とをつなぐ最短の直列経路に含まれるトランジスタの数）に応じて、基板バイアス効果を考慮して、抵抗変化型素子RRの両電極間に印加される電圧がメモリブロック中の位置によらずに等しくなるように設定されている。

## 【0134】

すなわち、それぞれのメモリセルは、選択ソース線SLを高電位、選択ビット線BLを低電位（例えば接地電位）とする場合（第1実施形態の例では、図6(a)のように低抵抗化する場合）には選択したトランジスタにほとんど基板バイアス効果が発生しないため、印加した電圧がほぼそのまま抵抗変化型素子RRの両電極間に印加される。一方、選択ソース線SLを低電位、選択ビット線BLを高電位とする場合（第1実施形態の例では、図6(b)のように高抵抗化する場合）には、選択トランジスタに逆バイアスの基板バイアス効果が発生するため、現実に抵抗変化型素子RRの両電極間に印加される電圧は、選択ソース線SLと選択ビット線BLとの間に印加される電圧よりも小さくなる。

## 【0135】

図45は、基板バイアス効果による電位降下をシミュレーションするために用いた回路を示す図である。図45において、A-Trは、電源回路とメモリセルの間に存在する制御用トランジスタ、Tr<sub>0</sub>~Tr<sub>15</sub>は各々のメモリセルに接続されているトランジスタである。V<sub>E0</sub>~V<sub>E15</sub>は、メモリセルを構成する各トランジスタのV<sub>D</sub>（V<sub>D0</sub>~V<sub>D15</sub>）を0Vとして計算したときのソース線上の電圧である。図46は、図45の回路図に基づいて各トランジスタのV<sub>D</sub>（V<sub>D0</sub>~V<sub>D15</sub>）の、基板バイアス効果による電位降下をシミュレーションにより求めた結果を示す図である。なお、シミュレーションに用いたトランジスタの構成は、Tr<sub>0</sub>~Tr<sub>15</sub>およびA-Trのいずれについても共通であって、3.3V系NMOSトランジスタ（ゲート幅W=440nm、ゲート長L=380nm、ゲート酸化膜厚=9.7nm）である。

## 【0136】

図45に示すように、隣接する一方のトランジスタの第1主端子（ソース／ドレイン）と他方のトランジスタの第2主端子（ソース／ドレイン）とが接続されるように連続して設けられたトランジスタ列を考える。それぞれのトランジスタの制御端子（ゲート）は接続され、同一の電位（V<sub>G</sub>）が印加される。また、隣接する2個のトランジスタの接続部（主端子）のそれには、抵抗変化型素子の下部電極が接続されている。各々のメモリセルに接続されているトランジスタのうち、一番右側のトランジスタTr<sub>0</sub>の右側の主端子には抵抗変化型素子は接続されておらず、右側の主端子がビット線BLに接続されていると考える。抵抗変化型素子の上部電極はいずれも接地されていると考える。

## 【0137】

10

20

30

40

50

このとき、A-Trの主端子に接続されたビット線に印加する電圧をV<sub>BL</sub>とし、右から1番目～15番目の抵抗変化型素子に実際に印加される電圧をそれぞれV<sub>D0</sub>～V<sub>D15</sub>とする。V<sub>BL</sub>=+1.8Vのとき、V<sub>D0</sub>～V<sub>D15</sub>は、A-Trからの遠い位置のノードの電位ほど小さくなる。また、V<sub>D0</sub>～V<sub>D15</sub>は、V<sub>G</sub>の大きさによっても変化する。図46は、V<sub>D0</sub>、V<sub>D3</sub>、V<sub>D7</sub>、V<sub>D15</sub>とV<sub>G</sub>との関係を示す図である。V<sub>G</sub>=VDD=+4.5Vとすれば、V<sub>D3</sub>までは+1.2V以上となる。高抵抗化のためには、図5における高抵抗化の閾値である+1.2Vより絶対値の大きな正の電圧が印加される必要がある。したがって、図5の素子特性および上記電圧関係の下では、4個のメモリセルまで1本の直列経路に接続できることになる。各トランジスタのオン抵抗を下げたり、基板バイアス効果を低減することにより、より多くのメモリセルを接続可能とすることができる。以上の理由から第1実施形態では4個のメモリセルを1本の直列経路に接続する構成（メモリブロック内の1行に4個のメモリセルが含まれる構成）とした。なお、V<sub>G</sub>やV<sub>BL</sub>を調整することで、より多くのメモリセルを1本の直列経路に接続することもできる。10

#### 【0138】

ここで、V<sub>BL</sub>が一定である限り、直列経路上の位置（抵抗変化型素子とビット線とをつなぐ経路に含まれるトランジスタの数）に応じて、基板バイアス効果による電位降下の程度は異なるから、抵抗変化型素子に実際に印加される電圧も変化する。書き込み後の抵抗値を一定にし、かつ抵抗変化型素子に不必要的電圧ストレスをかけないためには、直列経路上の位置によらず印加電圧が一定であることが望ましい。そこで、メモリセルの第1電極E1とビット線BLとを結ぶ最短の直列経路の経路長（抵抗変化型素子とビット線とをつなぐ最短の直列経路に含まれるトランジスタの数）に応じて、抵抗変化型素子RRの両電極間に印加される電圧がメモリブロック中の位置によらずに等しくなるように、予めV<sub>BL</sub>を調整しておくことが望ましい。本実施形態では、第1高抵抗化電圧生成回路125と第2高抵抗化電圧生成回路126と第3高抵抗化電圧生成回路127と第4高抵抗化電圧生成回路128とを用い、メモリセルの位置に応じてV<sub>BL</sub>を上記のようにV<sub>20</sub>～V<sub>23</sub>と変化させることで、かかる制御を実現する。20

#### 【0139】

以上のような構成によれば、メモリセルMCの位置によらず抵抗変化型素子RRの両電極間に印加される電圧が一定となり、従前の構成に比べ、書き込み後の抵抗値をより一定に保ち、かつ抵抗変化型素子にかかる不必要的電圧ストレスをより抑制できる。30

#### 【0140】

##### 〔変形例〕

本実施形態においても、第1実施形態と同様の変形例が可能である。

#### 【0141】

上記説明から、当業者にとって本発明の多くの改良や他の実施形態が明らかである。従って、上記説明は、例示としてのみ解釈されるべきであり、本発明を実行する最良の態様を当業者に教示する目的で提供されたものである。本発明の精神を逸脱することなく、その構造及び／又は機能の詳細を実質的に変更できる。

#### 【産業上の利用可能性】

#### 【0142】

本発明に係る不揮発性記憶装置は、非選択メモリセルに流れる電流を効果的に抑制しつつ、4F<sup>2</sup>のメモリセルを実現する不揮発性記憶装置として有用である。

#### 【符号の説明】

#### 【0143】

100、100' 不揮発性記憶装置

102 カラムデコーダ

104 ロウデコーダ

106 メモリセルアレイ

108 アドレス入力回路

|         |                                  |    |

|---------|----------------------------------|----|

| 1 1 0   | 制御回路                             |    |

| 1 1 2   | 電源回路                             |    |

| 1 1 4   | データ入出力回路                         |    |

| 1 1 6   | 書込回路                             |    |

| 1 1 8   | クランプ回路                           |    |

| 1 2 0   | センスアンプ                           |    |

| 1 2 2   | 低抵抗化電圧生成回路                       | 10 |

| 1 2 4   | 高抵抗化電圧生成回路                       |    |

| 1 2 5   | 第1高抵抗化電圧生成回路                     |    |

| 1 2 6   | 第2高抵抗化電圧生成回路                     |    |

| 1 2 7   | 第3高抵抗化電圧生成回路                     |    |

| 1 2 8   | 第4高抵抗化電圧生成回路                     |    |

| 1 3 0   | P型シリコン基板層                        |    |

| 1 3 2   | 二酸化珪素層                           |    |

| 1 3 4   | P注入領域                            |    |

| 1 3 6   | 白金シリサイド層                         |    |

| 1 3 8   | Si <sub>3</sub> N <sub>4</sub> 部 |    |

| 1 4 0   | タンタル酸化物層                         |    |

| 1 4 2   | 窒化タンタル層                          |    |

| 1 4 4   | タングステン層                          | 20 |

| 1 4 6   | Si <sub>3</sub> N <sub>4</sub> 層 |    |

| 1 4 8   | 二酸化珪素層                           |    |

| 1 4 9   | チタン/窒化チタン層                       |    |

| 1 5 0   | チタン/窒化チタン層                       |    |

| 1 5 2   | タングステン層                          |    |

| 1 5 3   | コンタクト                            |    |

| 1 5 4   | 銅層                               |    |

| 1 5 6   | 二酸化珪素層                           |    |

| 1 5 8   | 二酸化珪素層                           |    |

| 1 6 0   | ポリシリコン層                          | 30 |

| 1 6 1   | コンタクト                            |    |

| 1 6 2   | 銅層                               |    |

| 1 6 3   | 溝                                |    |

| 1 6 4   | メモリ溝                             |    |

| 1 6 6   | コンタクト配線溝                         |    |

| 1 6 8   | 溝                                |    |

| 1 7 0   | ホール                              |    |

| 1 7 2   | 溝                                |    |

| 1 7 4   | ホール                              |    |

| 2 0 0   | 不揮発性記憶装置                         | 40 |

| B L     | ビット線                             |    |

| C L     | コンタクト配線                          |    |

| C 1、C 2 | コンタクト                            |    |

| D / S   | ドレイン/ソース                         |    |

| E 1     | 第1電極                             |    |

| E 2     | 第2電極                             |    |

| G       | ゲート                              |    |

| M C     | メモリセル                            |    |

| R R     | 抵抗変化型素子                          |    |

| S L     | ソース線                             | 50 |

- T 1 第1主端子(ドレン／ソース)

T 2 第2主端子(ドレン／ソース)

T 3 制御端子(ゲート)

T R トランジスタ

V R 抵抗変化層

W L ワード線

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図26】

【 図 27 】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図4-2】

【 図 4 3 】

【図44】

【図45】

【図46】

【図47】

【図48】

【図25】

---

フロントページの続き

(72)発明者 飯島 光輝

大阪府門真市大字門真1006番地 パナソニック株式会社内

(72)発明者 神澤 好彦

大阪府門真市大字門真1006番地 パナソニック株式会社内

審査官 園田 康弘

(56)参考文献 特開2008-146740(JP,A)

特開2004-200641(JP,A)

特開2008-269741(JP,A)

特開2007-026627(JP,A)

特開昭61-030063(JP,A)

特開2006-303150(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 13/00

H01L 27/10

H01L 45/00

H01L 49/00