#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization International Bureau

(43) International Publication Date 23 November 2006 (23.11.2006)

$\Gamma$  (10) International Publication Number WO~2006/124966~A2

(51) International Patent Classification: C23F 1/00 (2006.01) C23C 16/00 (2006.01) H01L 21/306 (2006.01)

(21) International Application Number:

PCT/US2006/019028

(22) International Filing Date: 16 May 2006 (16.05.2006)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

11/131,900 17 May 2005 (17.05.2005) US

(71) Applicant: APPLIED MATERIALS, INC. [US/US]; 3050 Bowers Avenue, Santa Clara, CA 95054 (US).

(72) Inventors: RAMASWAMY, Kartik; 1646 Tawnygate Way, San Jose, CA 95124 (US). HANAWA, Hiroji; 696

Spruce Drive, Sunnyvale, CA 94086 (US). GALLO,

Biagio; 160 College Avenue, Los Gatos, CA 95030 (US). COLLINS, Kenneth, S.; 7214 Glenview Drive, San Jose, CA 95120 (US). MA, Kai; 750 N.Shoreline Blvd.141, Mountain View, CA 94043 (US). PARIHAR, Vijay; 41521 Joyce Avenue, Fremont, CA 94539 (US). JENNINGS, Dean; 6 Thoreau Circle, Beverly, MA 01915 (US). MAYUR, Abhilash; 17651 Olson Place, Salinas, CA 93907 (US). AL-BAYATI, Amir; 3302 Chemin De Riviere, San Jose, CA 95148 (US). NGUYEN, Andrew; 3148 Hostetter Road, San Jose, CA 95132 (US).

(74) Agent: WALLACE, Robert, M.; LAW OFFICE OF ROBERT M. WALLACE, 2112 Eastman Avenue, Suite 102, Ventura, CA 93003 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI,

[Continued on next page]

**(54) Title:** LOW TEMPERATURE ABSORPTION LAYER DEPOSITION AND HIGH SPEED OPTICAL ANNEALING SYSTEM

(57) Abstract: An integrated system for processing a semiconductor wafer includes a toroidal source plasma reactor for depositing a heat absorbing layer, the reactor including a wafer support, a reactor chamber, an external reentrant toroidal conduit coupled to said chamber on generally opposing sides thereof, an RF source power applicator for coupling power to a section of said external reentrant conduit and a process gas source containing a heat absorbing material precursor gas. The integrated system further includes an optical annealing chamber.

- NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Declaration under Rule 4.17:**

as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

#### **Published:**

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

# LOW TEMPERATURE ABSORPTION LAYER DEPOSITION AND HIGH SPEED OPTICAL ANNEALING SYSTEM

Inventors: Kartik Ramaswamy, Hiroji Hanawa, Biagio Gallo, Kenneth S. Collins, Kai Ma, Vijay Parihar, Dean Jennings, Abhilash Mayur, Amir Al-Bayati, Andrew Nguyen

# **BACKGROUND OF THE INVENTION**

- High speed integrated circuits formed on a crystalline semiconductor [01]wafer have ultra shallow semiconductor junctions formed by ion implanting dopant impurities into source and drain regions. The implanted dopant impurities are activated by a high temperature anneal step which causes a large proportion of the implanted atoms to become substitutional in the crystalline semiconductor lattice. Such a post-ion implantation anneal step are done by a rapid thermal process (RTP)-employing powerful lamps that heat the entire wafer volume to a very high temperature for a short time (e.g., a rate-of-rise of about 100-200 degrees C per second and an intial rate-of-fall of 50-100 degrees C per second). The heating duration must be short to avoid degrading the implanted junction definition by thermally induced diffusion of the dopant impurities from their implanted locations in the semiconductor wafer. This RTP approach is a great improvement over the older post-ion implant anneal technique of heating the wafer in a furnace for a long period of time. RTP using lamps is effective because the time response of the heat source (the lamp filament) is short in contrast to the furnace annealing step in which the heater response time is very slow. The high temperature, short duration heating of the RTP method favors the activation of implanted impurities while minimizing thermally induced diffusion.

- [02] An improved anneal is done by a flash lamp anneal process employing powerful flash lamps that heat the surface (only) of the entire wafer to a very high

temperature for a very short time (e.g., a few milliseconds). The heating duration must be short to avoid degrading the implanted junction definition by thermally induced diffusion of the dopant impurities from their implanted locations in the semiconductor wafer. This flash approach is an improvement over the RTP approach, because the bulk of the wafer acts as a heat sink and permits rapid cooling of the hot wafer surface. High speed anneal using flashlamps is more effective because the heating is confined to the surface of the wafer, in contrast to the RTP annealing step in which the entire volume of the wafer is heated to approximately the same anneal temperature. The short duration at high temperature of the flash method minimizes thermally induced diffusion. However, it is difficult to achieve thermal uniformity over the entire wafer. Greater thermal non-uniformity within wafer creates significant amount of mechanical stress, resulting in wafer breakage and limits the highest operating temperature to approximately 1150°C for anneal using flash lamps. The surface temperature during flashlamp annealing is determined by the intensity and pulse duration of flashlamps, which are difficult to control in a repeatable manner from one wafer to the next.

[03] One problem with RTP is that as device size decreases to 65 nanometers (nm) and below, the minimal thermal diffusion caused by RTP or flash heating becomes significant relative to the device size, despite the short duration of the RTP or flash heating. Another problem is that the degree of activation of the implanted dopant impurities is limited by the maximum temperature of the RTP or flash process. Heating the entire wafer volume in the RTP process above the maximum temperature (e.g., 1100 degrees C) can create mechanical stresses in the wafer that cause lattice defects and wafer breakage in extreme cases. Limiting the wafer temperature to a maximum level (e.g., 1100 degrees C) prevents such breakage, but unfortunately limits the proportion of implanted (dopant) atoms that are activated (i.e., that become substitutional in the semiconductor crystalline lattice). Limiting the dopant activation limits sheet conductivity and limits device speed. This problem becomes more significant as device size is reduced below 65 nm (e.g., down to 45 nm).

In order to raise the level of dopant activation beyond that achieved by [04] RTP or flash annealing, laser annealing has been introduced as a replacement for RTP. One type of laser that has been used is a CO2 laser having an emission wavelength of 10.6 microns. This laser produces a narrow cylindrical beam, which must be raster-scanned across the entire wafer surface. In order to decrease the surface reflectivity at 10.6 microns, the beam is held at an acute angle relative to the wafer surface. Since the CO2 laser wavelength corresponds to a photon energy less than the bandgap of silicon, the silicon must be pre-heated to populate the conduction band with free carriers in order to facilitate the absorption of 10.6 micron photons through free carrier absorption. A fundamental problem is that the absorption at 10.6 microns is pattern-dependent because it is affected by the dopant impurities (which among other factors, determines the local free carrier concentration), so that the wafer surface is not heated uniformly. Also, conductive or metallic features on the wafer are highly reflective at the 10.6 micron laser wavelength, so that this process may not be useful in the presence of conductive thin film features.

- [05] The post-implant anneal step has been performed with short wavelength pulsed lasers (the short wavelength corresponding to a photon energy greater than the bandgap of silicon). While the surface heating is extremely rapid and shallow, such pulsed lasers bring the semiconductor crystal to its melting point, and therefore the heating must be restricted to an extremely shallow depth, which reduces the usefulness of this approach. Typically, the depth of the heated region does not extend below the depth of the ultra-shallow junctions (about 200 Angstroms).

- [06] The foregoing problems have been overcome by employing an array of diode lasers whose multiple parallel beams are focused along a narrow line (e.g., about 300 microns wide) having a length on the order of the wafer diameter or radius. The diode lasers have a wavelength of about 810 nm. This wavelength corresponds to a photon energy in excess of the bandgap energy of the semiconductor crystal (silicon), so that the laser energy excites electron transitions between the valence and conduction bands, which subsequently release the absorbed energy to the lattice and raises the lattice temperature. The narrow laser

beam line is scanned transversely across the entire wafer surface (e.g., at a rate of about 300 mm/sec), so that each point on the wafer surface is exposed for a very short time (e.g., about 1 millisec). This type of annealing is disclosed in U.S. Patent Publication No. US 2003/0196996A1 (October 23, 2003) by Dean C. Jennings et al. The wafer is scanned much more quickly by the wide thin beam line than by the pencil-like beam of a single laser spot, so that productivity is much greater, approaching that of RTP. But, unlike RTP, only a small portion of the wafer surface is heated, so that the stress is relieved in the remaining (bulk) portion of the wafer, allowing the peak temperature to be increased above the maximum RTP temperature (e.g., to about 1250-1300 degrees C). The entire wafer volume may also be preheated during the laser scanning anneal in order to improve the annealing characteristics. The maximum preheated temperature is dictated by the technology nodes, process requirements, compatibility with semiconductor materials, etc. As a result, dopant activation is much higher, so that sheet resistivity is lower and device speed is higher. Each region of the wafer surface reaches a temperature range of about 1250-1300 degrees C for about 50 microsec. The depth of this region is about 10-20 microns. This extends wellbelow the ultra-shallow semiconductor junction depth of about 200 Angstroms. [07]The wafer surface must be heated above a minimum temperature (e.g., 1250 degrees C) in order to achieve the desired degree of activation of the implanted (dopant) atoms. The elevated temperature is also required to anneal other lattice damage and defects caused by any preceeding implant or thermal steps, in order to improve the electrical characteristics of the junctions such as their electrical conductivity and leakage. The wafer surface must be kept below a maximum temperature (e.g., 1350 degrees C) in order to avoid the melting temperature of the semiconductor crystal (e.g., crystalline or polycrystalline silicon). In order to uniformly heat the entire wafer surface within this desired temperature range, the optical absorption of the wafer surface must be uniform across the wafer, and the surface temperature in the illuminated portion of the wafer surface must be accurately monitored while the laser beam line is scanned across the wafer (to enable precise temperature control). This is accomplished by measuring the emission of light by the heated portion of the wafer surface (usually

of a wavelength different from that of the laser light source), and the measurement must be uniformly accurate. As employed in this specification, the term "optical" is meant to refer to any wavelength of a light or electromagnetic radiation emitted from a light source (such as a laser) that is infrared or visible or ultraviolet or emitted from the heated wafer surface.

The problem is that the underlying thin film structures formed on the wafer surface present different optical absorption characteristics and different optical emissivities in different locations on the wafer surface. This makes it difficult if not impossible to attain uniform anneal temperatures across the wafer surface and uniformly accurate temperature measurements across the wafer surface. This problem can be solved by depositing a uniform optical absorption layer over the entire wafer surface that uniformly absorbs the laser radiation and then conducts the heat to the underlying semiconductor wafer. Such a film must withstand the stress of heating during the laser anneal step without damage or separation, and must be selectively removable after the laser anneal step with respect to underlayers and must not contaminate or damage the underlying semiconductor wafer or thin film features. Further, the absorber film must attain excellent step coverage (high degree of conformality) over the underlying thin film features. One advantage of such a film is that lateral heat conduction in the film can mask non-uniformities in the light beam. This approach has been attempted but has been plagued by problems. One type of absorber layer consists of alternating metal and dielectric layers that form an anti-reflective coating. The different layers in this type of absorber material tend to fuse together under the intense heat of the laser beam, and become difficult to remove following the laser anneal step or contaminate underlying layers with metal.

[09] A better approach used in the present invention is to employ an absorber layer that can be deposited by plasma enhanced chemical vapor deposition (PECVD). As disclosed in U.S. Patent Application Serial No. 10/679,189 filed October 3, 2003 entitled "Absorber Layer for DSA Processing" by Luc Van Autryve et al. and assigned to the present assignee, the PECVD-deposited absorber layer may be amorphous carbon. One advantage of amorphous carbon is that it is readily and selectively (with respect to underlayers of other materials)

removed by oxidation in a plasma process or a downstream oxidation process employing radicals, at a wafer temperature less than 400C. Another advantage is that carbon is generally compatible with semiconductor plasma processes and therefore does not involve contamination, so long as excessive implantation does not occur. One problem is that the deposited layer is vulnerable to cracking or peeling under the high temperatures of the laser anneal step, unless the layer is deposited at a very high temperature (e.g., 550 degrees C). (The tendency or resistance to such cracking, peeling or separation of the deposited layer from the underlying layer in response to high temperature or high temperature gradients is generally referred to in this specification as the thermal or thermal-mechanical properties of the deposited layer.) Also the thermal budget (time and temperature) associated with this PECVD deposition process caused dopants to form clusters which are difficult to dissolve with the subsequent laser anneal step, particularly for feature sizes below 65 nm (such as feature sizes of about 45 nm). Attempting to solve this problem by reducing the wafer temperature (e.g., to 400 degrees C) during PECVD deposition of the absorber layer material creates two problems. First, the thermal properties of the deposited layer are such that it will fail (by cracking, peeling or separation from the wafer) during the laser annealing step. Secondly, the deposited layer that is produced is transparent or has insufficient optical absorption. Another problem encountered with this absorber layer is that it has poor step coverage. We have observed that the PECVD 550 degree absorber layer can have very large voids in the vicinity of pronounced steps in the underlying layer or thin film structures sizes below 65 nm. We feel that failure of the absorber layer (e.g., by peeling or cracking) [10] arises from a lack of high quality chemical bonds (between the underlying layer

[10] We feel that failure of the absorber layer (e.g., by peeling or cracking) arises from a lack of high quality chemical bonds (between the underlying layer and the deposited material) capable of withstanding the stress of being rapidly heated to 1300 degrees C during the laser anneal step. We feel that, in order to improve the thermal properties of the deposited layer, achieving such high quality bonds at low wafer temperature requires high ion energies during the PECVD process. Such high ion energies are not readily attainable in conventional PECVD reactors. We feel that poor step coverage by the absorber layer or amorphous carbon layer is the result of the inability of a conventional PECVD or HDPCVD

reactor to provide an intermediate range of ionization (ion-to-radical ratio) with an adequate level of energetic ion bombardment. These inadequacies arise, in part, because such conventional PECVD and HDPCVD reactors cannot operate within a wide intermediate range of source power coupling (to generate plasma electrons), chamber pressure and wafer voltage. Indeed, the different types of conventional PECVD and HDPCVD reactors tend to operate at either very high or very low ranges of source power coupling (to generate plasma electrons), chamber pressure and wafer voltage. Conventional PECVD reactors employ capacitivelycoupled RF source power at relatively high-pressure, resulting in a very low range of ionization (ion-to-radical ratio) with an inadequate level of energetic ion bombardment (and no separate control of voltage or energy). This is due to the inefficient source power coupling (to generate plasma electrons) and the damping of ion energies by collisions with neutrals at high pressure. Even if separate RF biasing of the wafer is added, the damping of ion energies by collisions with neutrals at high pressure limits the voltage and energy range to a low range. Conversely, conventional HDPCVD reactors typically employ inductivelycoupled RF source power at very low pressure. This type of plasma source typically initiates the plasma capacitively, and then has a high power threshold to transition to inductively coupled power mode. Once the power coupled is above this threshold and the source is operating in an inductive mode, the source power coupling is highly efficient and the minimum possible plasma density and range of ionization (ion-to-radical ratio) is very high. The separate RF wafer bias is coupled to the relatively dense plasma, which presents a very low electrical impedance load. The resultant RF bias power required to produce energetic ion bombardment is very high (>>10kW for >2kV). High energies are not generally attainable due to practical RF delivery system limitations (RF generators, matching networks, and feed structures). Most of the bias power (e.g., ~80%) is dissipated as heat on the wafer. It is very difficult to remove the heat at low pressure at an adequate rate to maintain low wafer temperature (<400 deg. C or lower). Finally, both capacitively-coupled PECVD and inductively-coupled HDPCVD reactors may have power coupling drift (with on-time) issues when used with carbon chemistry when depositing absorbing or semiconducting films

(on RF windows or insulators). The need (fulfilled by the toroidal plasma CVD reactor and process described in detail below) is for a reactor capable of providing ionization ratios in a wide intermediate range together with an adequate level of energetic ion bombardment in all cases, through an ability to operate in a wide intermediate range of source power coupling and level, wafer voltage and chamber pressure. The toroidal plasma CVD reactor does not exhibit power coupling drift when used with carbon chemistry when depositing absorbing or semiconducting films. This is because the toroidal plasma CVD reactor is already conducting (metal), having only very thin, isolated DC breaks, which do not accumulate much deposition and are easily in-situ plasma cleaned.

- [11]One type of conventional PECVD reactor is a capacitively coupled plasma reactor having a pair of closely-spaced parallel plate electrodes across which RF plasma source power is applied. Such a capacitively coupled reactor typically is operated at high chamber pressure (2-10 Torr). High pressure and close-spacing (relative to electrode radius) are employed to maximize deposition rate on the wafer, and to minimize deposition outside the process region. The plasma source power couples to both electrons in the bulk plasma and to ions in the plasma sheaths. The voltage across the electrodes is typically relatively low (less than 1KVpp at source power of several kW for 300 mm wafer) and the plasma sheath is very collisional, so that the ion energy is typically low. This type of reactor produces a very low ion-to-neutral population ratio and ion-to-radical ratio, so that the ion flux is low, which probably increases the ion energy level or wafer temperature required to obtain the requisite high quality bonds between the deposited and underlying materials. However, because of the low inter-electrode voltage and the high loss of ion energy in the collisional sheath, it is very difficult to generate the ion energy distribution required for high quality bonds.

- [12] Another type of conventional PECVD reactor is an inductively coupled high plasma density CVD (HPDCVD) reactor in which RF source power is applied to an inductive antenna. The reactor must be operated at a low chamber pressure (e.g., 5-10 milliTorr) and high plasma source power level, because of the high minimum induced electric field required to maintain the inductively coupled plasma mode, which in turn produces a high plasma density. The degree of

ionization (ratio of ion-to-neutral density) produced in this reactor is confined to a range of very high values (four or five orders of magnitude greater than that of the capacitive reactor discussed above), because a large amount of RF source power is required to sustain the inductively coupled mode and because the RF induced electric field couples directly to electrons in the bulk plasma. This contrasts with a capacitively coupled plasma in which the RF electric field less efficiently couples to electrons indirectly by displacement across the plasma sheath or through plasma sheath oscillations. As a result, plasma density and conductivity is very high, making it difficult to generate a high wafer voltage at practical bias power levels (since the wafer voltage is loaded down through the highly conductive plasma). As a result, high ion energies cannot be attained without applying excessive amounts of RF bias power to the wafer. This could overheat the wafer and perhaps destroy the ultra shallow junction definition in the underlying semiconductor crystal lattice (by thermal diffusion). Typically, for a 300 mm wafer, a wafer voltage of 1-2 kV peak-to-peak would require RF bias power of about 10 kWatts. Cooling the wafer to maintain ultra-shallow junction definition is difficult at high bias power, and even higher bias voltage (than 1-2 kV) and thus higher power is desired for best film properties. RF power delivery systems > 10kW are very expensive and have limited availability.

[13] Another problem with the HDPCVD reactor is that a large non-conductive window must be provided in the chamber ceiling through which the plasma source power may be inductively coupled from the coil antenna. This prevents the use of a conductive showerhead directly overlying the wafer, which limits gas distribution uniformity at the wafer and RF bias ground reference uniformity over the wafer. Moreover, coupling of source power into the chamber may be effectively reduced or even blocked if the reactor is employed to deposit a non-insulating material on the wafer, since that same material will also accumulate on the dielectric window during processing, creating a conductive shield or semi-conductive attenuator to the RF power. The temperature of a non-conductive surface, such as the dielectric window of the HDPCVD reactor, cannot be effectively controlled, so that deposition during processing and post-process cleaning of the reactor interior is more difficult. A related problem in both types

of reactors is that plasma source power seeks a ground return from any available conductive surface in the chamber, so that process control is hampered by electrical changes due to deposition of by-products on the chamber surfaces. With both dielectric and metallic materials constituting the chamber surfaces, removal of deposited plasma by-products after processing may be difficult or may involve undue wear of chamber parts. This may be circumvented by employing disposable shields or process kits to prevent deposition on chamber surfaces. However, such disposable shields cannot provide good RF ground reference nor be thermally controlled with any precision.

In summary, the conventional reactors are either confined to a narrow low [14]chamber pressure window (in the case of the HDPCVD reactor) or a narrow high chamber pressure window (in the case of the capacitively coupled reactor). Neither chamber can achieve a high ion energy, either because the sheath is highly collisional (in the capacitively coupled reactor) or because the plasma is highly conductive (in the HDPCVD reactor). Also, they are confined to either a narrow high degree-of-ionization regime (the HDPCVD reactor) or a narrow low degreeof-ionization regime (the capacitively coupled reactor). Moreover, both types of reactors are susceptible to wide deviations in performance whenever they are used for deposition of non-insulating materials, since the accumulation of noninsulating materials across electrode boundaries in a capacitively coupled reactor or on the dielectric window of an inductively coupled reactor will distort or inhibit the coupling of RF source power into the chamber. What is needed is a deposition process carried out at a very low temperature (e.g., room temperature up to several hundred degrees C) for forming an optical absorber layer having such high quality bonds with the underlying layers (including the semiconductor lattice) that it is impervious to mechanical failure or separation during the laser annealing step. The process should have a wide source power window, a wide degree-ofionization window in an intermediate range, a wide wafer voltage (bias power) window with wide ion energy window, and a wide wafer temperature window.

#### SUMMARY OF THE INVENTION

[15] An integrated system for processing a semiconductor wafer includes a toroidal source plasma reactor for depositing a heat absorbing layer, the reactor including a wafer support, a reactor chamber, an external reentrant toroidal conduit coupled to said chamber on generally opposing sides thereof, an RF source power applicator for coupling power to a section of said external reentrant conduit and a process gas source containing a heat absorbing material precursor gas. The integrated system further includes an optical annealing chamber.

# BRIEF DESCRIPTION OF THE DRAWINGS

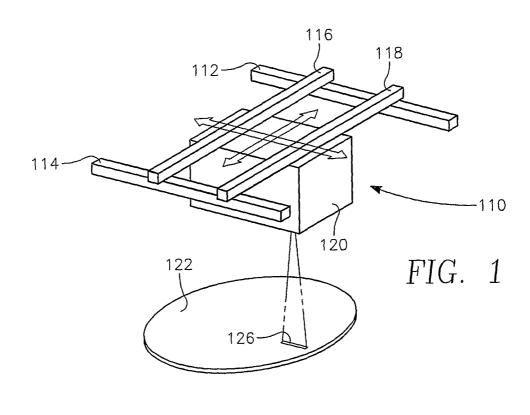

- [16] FIG. 1 illustrates a dynamic surface annealing apparatus.

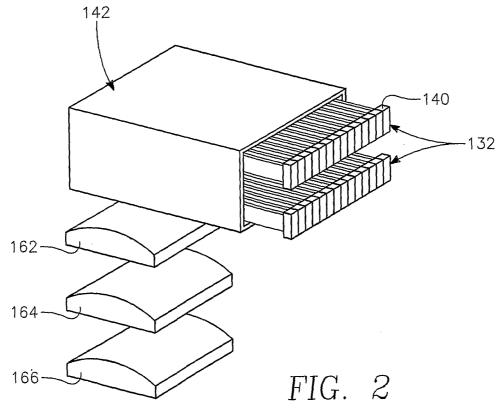

- [17] FIG. 2 is a top view of the optics of the apparatus of FIG. 1.

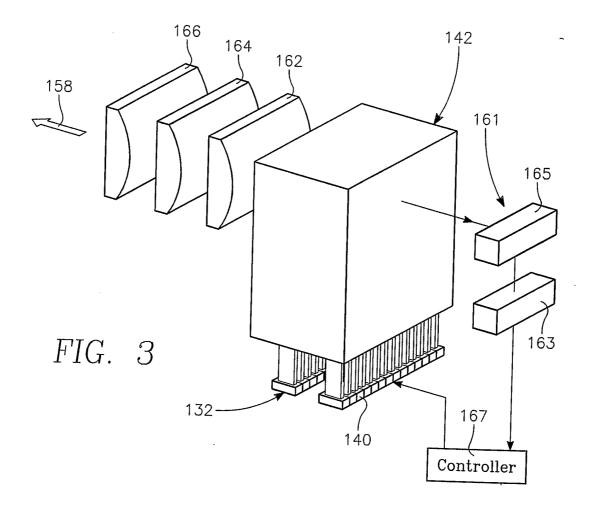

- [18] FIG. 3 is an elevational view corresponding to FIG. 2.

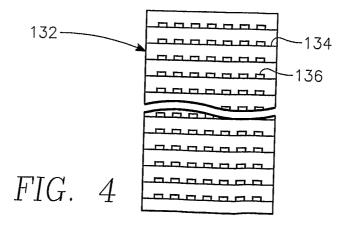

- [19] FIG. 4 is a broken sectional view of the laser array employed in the apparatus of FIG. 1.

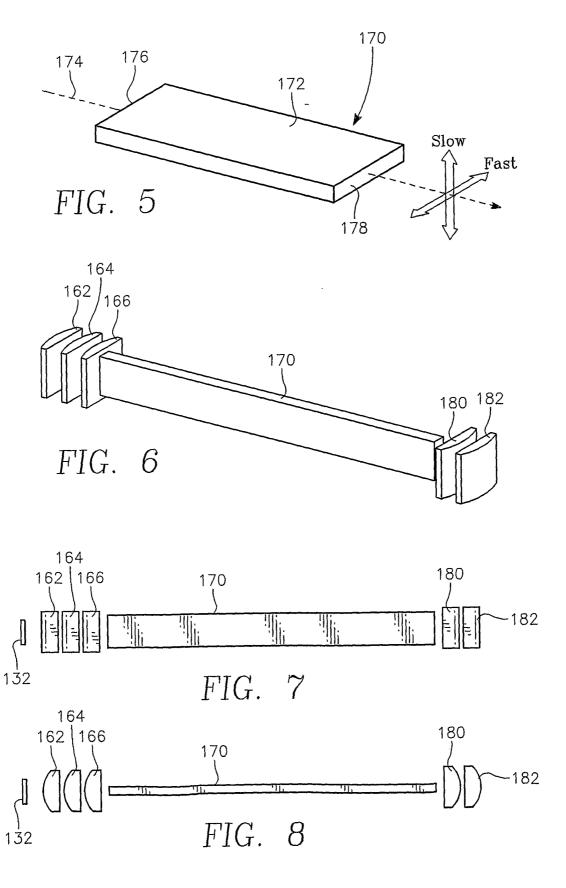

- [20] FIG. 5 is a perspective view of a homogenizing light pipe of the apparatus of FIG. 1.

- [21] FIG. 6 is a perspective side view of the light pipe of FIG. 5 with collimating and focusing lenses.

- [22] FIG. 7 is a side view corresponding to FIG. 6.

- [23] FIG. 8 is a top view corresponding to FIG. 6.

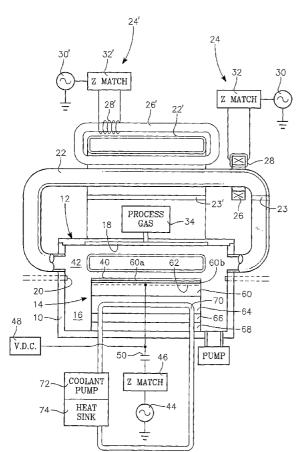

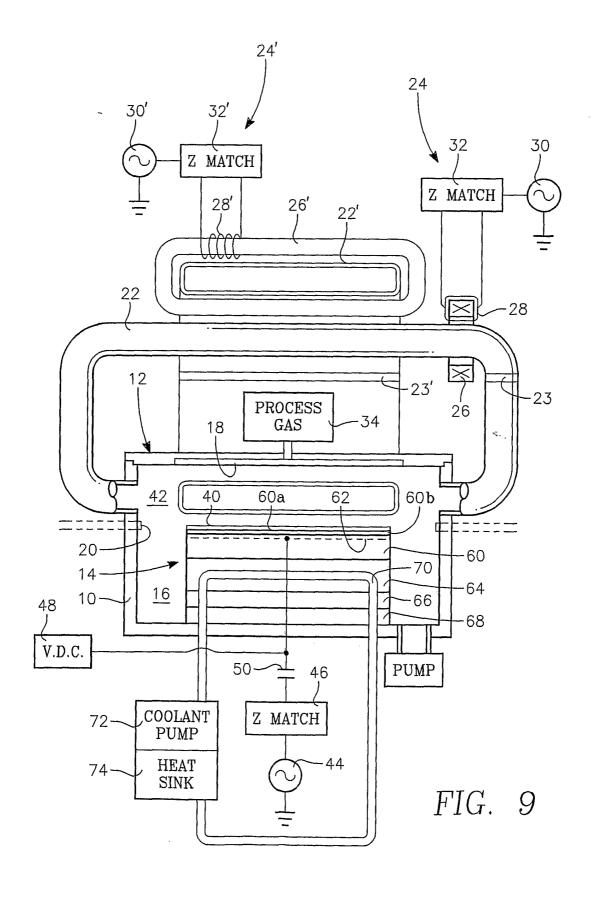

- [24] FIG. 9 depicts a toroidal source plasma reactor employed in carrying out a low temperature CVD process.

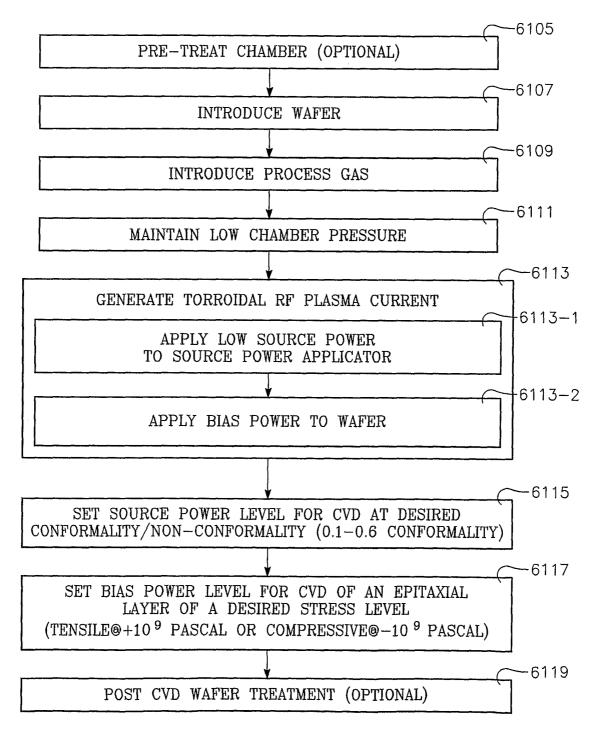

- [25] FIG. 10 is a block diagram depicting a general low temperature CVD process performed in the reactor of FIG. 9.

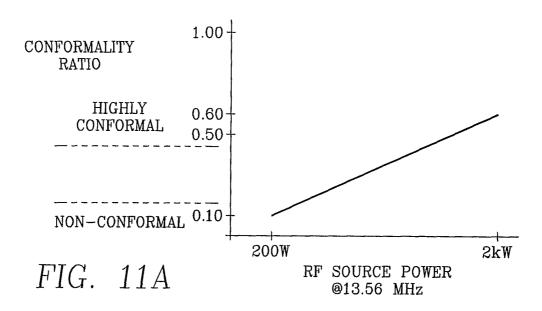

- [26] FIG. 11A is a graph illustrating conformality of the layer deposited in the low temperature process of FIG. 10 as a function of source power.

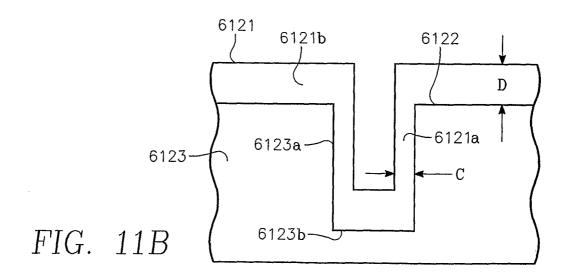

- [27] FIG. 11B is a cross-sectional view of a high aspect ratio opening and deposited layer that illustrates the definition of conformality.

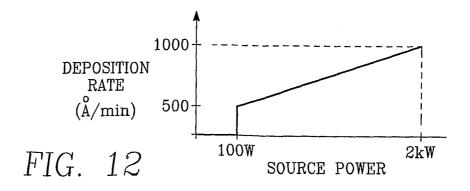

- [28] FIG .12 is a graph depicting CVD deposition rate as a function of plasam source power.

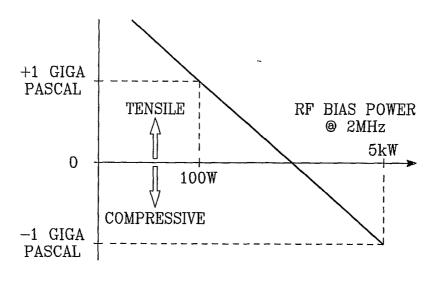

- [29] FIG. 13 is a graph illustrating the stress of the deposited layer as a function of bisa power level.

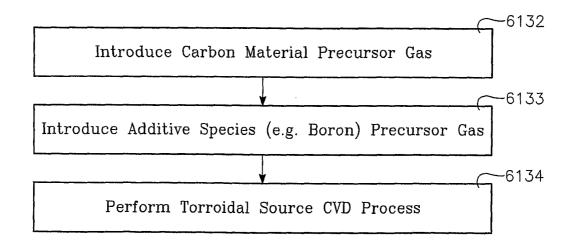

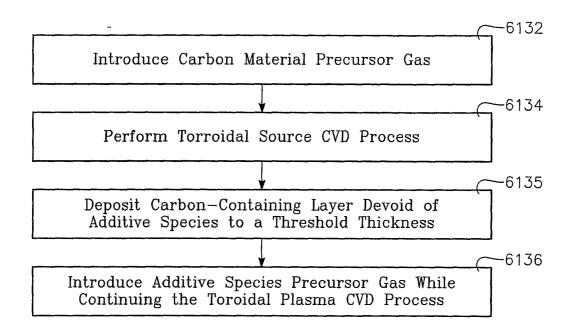

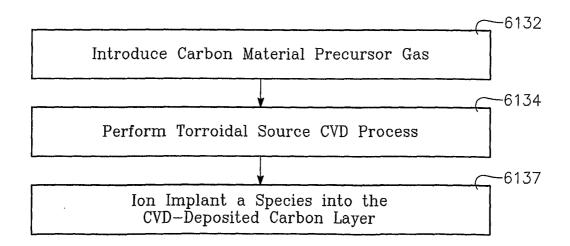

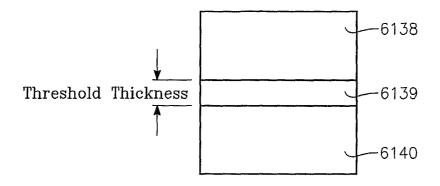

[30] FIG. 14 is a block diagram illustrating an embodiment of the process of FIG .10.

- [31] FIG. 15 is a block diagram illustrating another embodiment of the process of FIG .10.

- [32] FIG. 16 is a block diagram of yet another embodiment of the process of FIG. 10.

- [33] FIG. 17 is a cross-sectional view of a thin film structure formed by the process of either FIG. 15 or FIG .16.

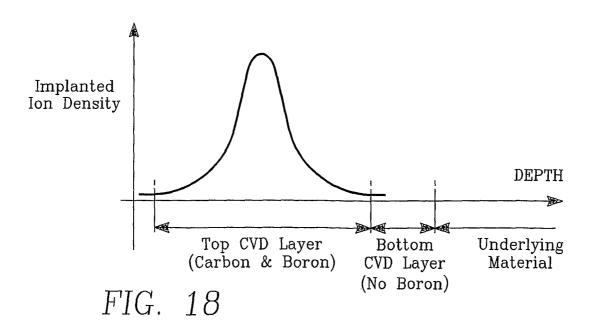

- [34] FIG .18 is a graph depicting the implanted ion density as a function of depth below the wafer surface in the process of either FIG .15 or FIG. 16.

- [35] FIG. 19 is a block diagram illustrating a yet further embodiment of the process of FIG. 10.

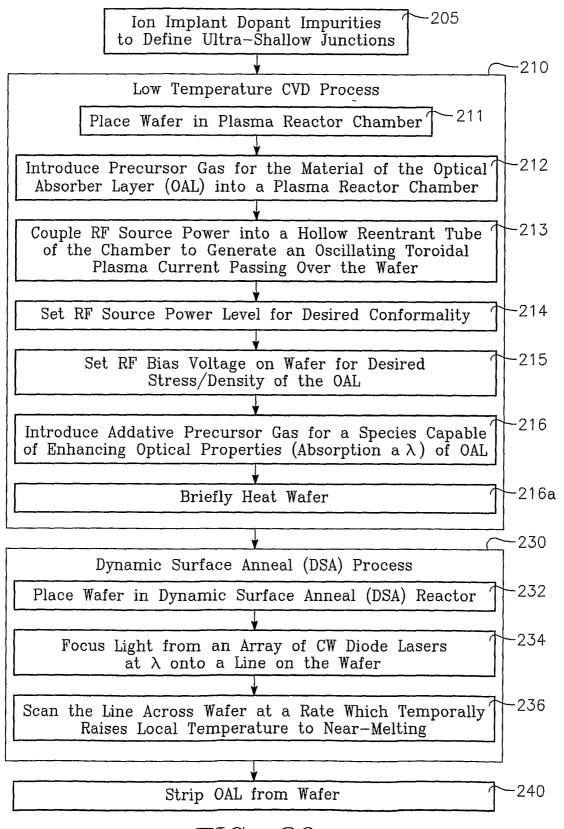

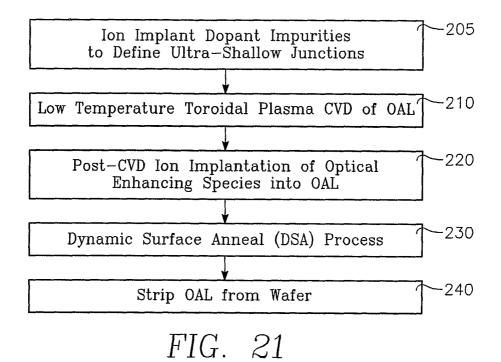

- [36] FIG. 20 is a block diagram of a process for forming ultra-shallow junctions.

- [37] FIG. 21 is block diagram of an alternative embodiment of the process of FIG. 20.

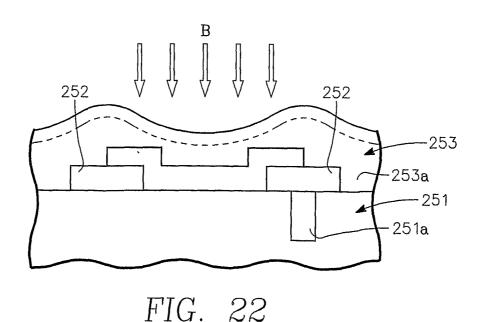

- [38] FIG. 22 is a cross-sectional view of a thin film structure formed in the process of FIG. 21.

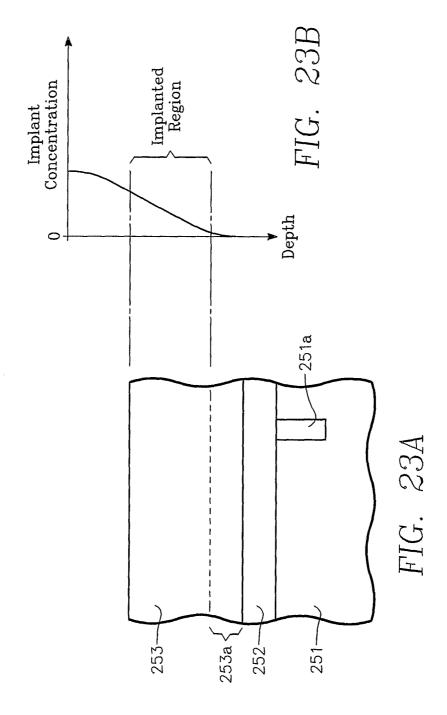

- [39] FIG. 23A is a cross-sectional view of a thin film structure formed in the process of FIG. 21.

- [40] FIG. 23B is a graph of ion implanted species concentration as a function of depth in the thin film structure of FIG. 23A.

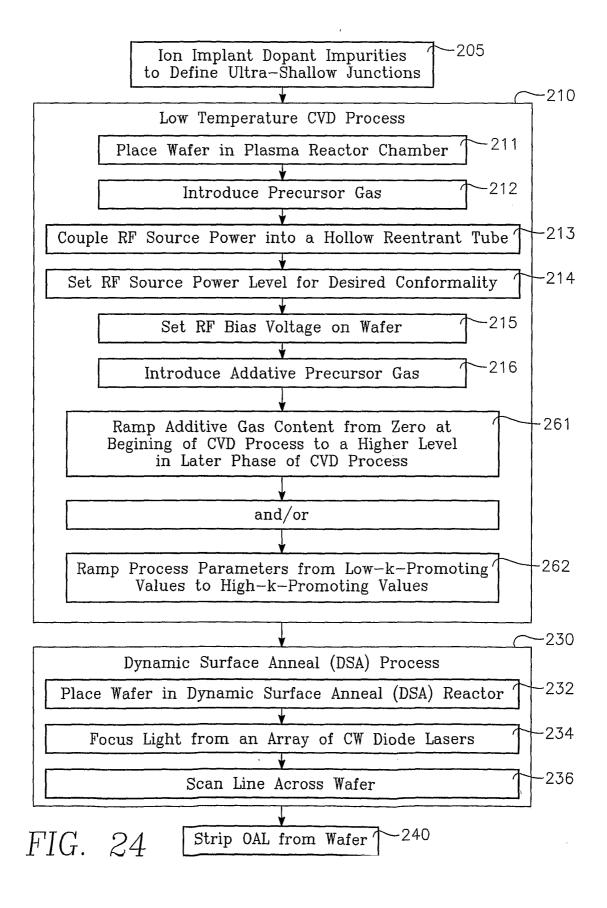

- [41] FIG. 24 is a block diagram of an alternative embodiment of the process of FIG. 20.

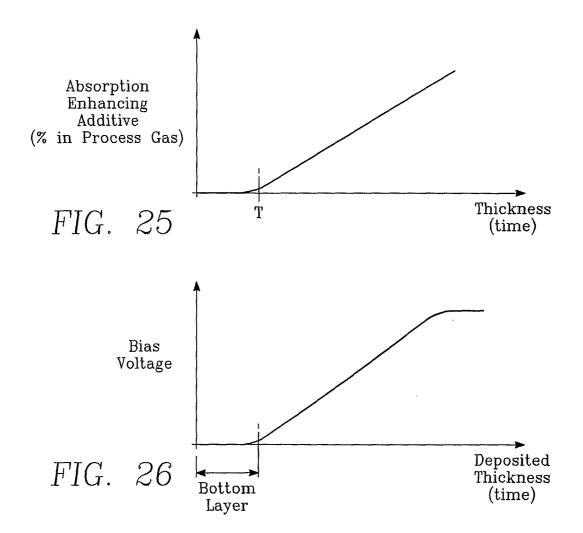

- [42] FIG. 25 is a graph of the additive gas flow rate as a function of time in the process of FIG. 24.

- [43] FIG .26 is a graph of the RF wafer bias voltage as a function of time in the process of FIG. 24.

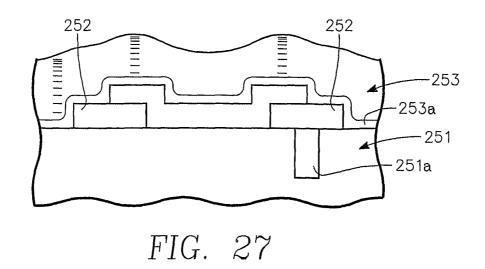

- [44] FIG. 27 is a cross-sectional view of a thin film structure formed by the process of FIG. 24.

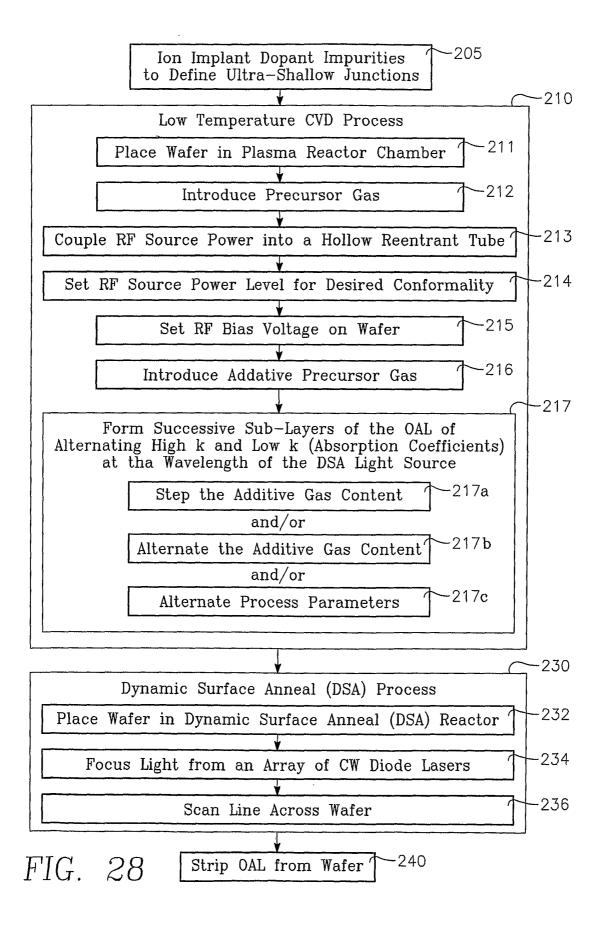

- [45] FIG. 28 is a block diagram of another alternative embodiment of the process of FIG. 20.

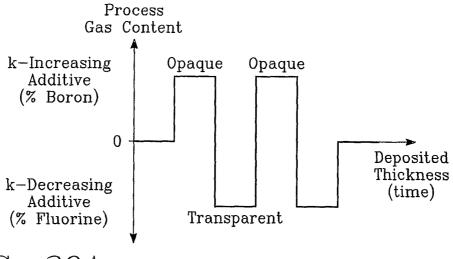

[46] FIG. 29A is graph illustrating the proportion of two different additive gases as a function of time in the process of FIG. 24.

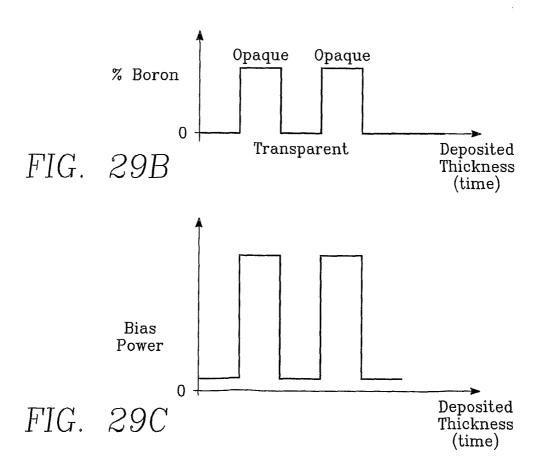

- [47] FIG. 29B is a graph illustrating the proportion of a single additive gas in another version of the process of FIG. 24.

- [48] FIG. 29C illustrates the wafer RF bias power as a function of time in yet another version of the process of FIG. 24.

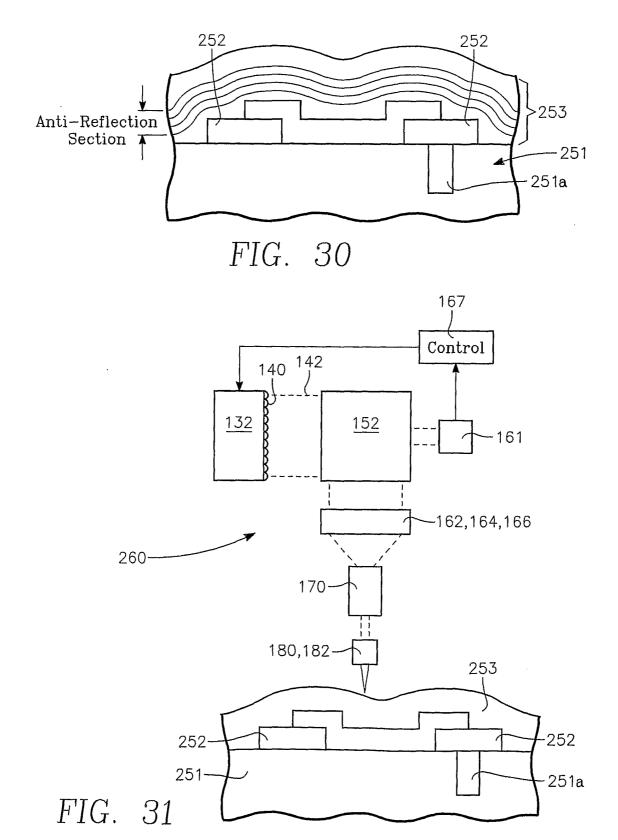

- [49] FIG. 30 depicts a thin film structure having a mult-layered deposited coating formed by the process of FIG. 24.

- [50] FIG. 31 illustrates an operation for annealing ultra-shallow junctions in the semiconductor wafer.

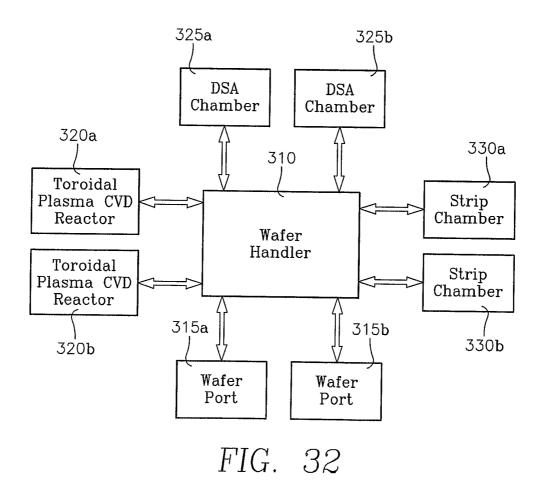

- [51] FIG. 32 illustrates an integrated system for treating a wafer in accordance with the invention.

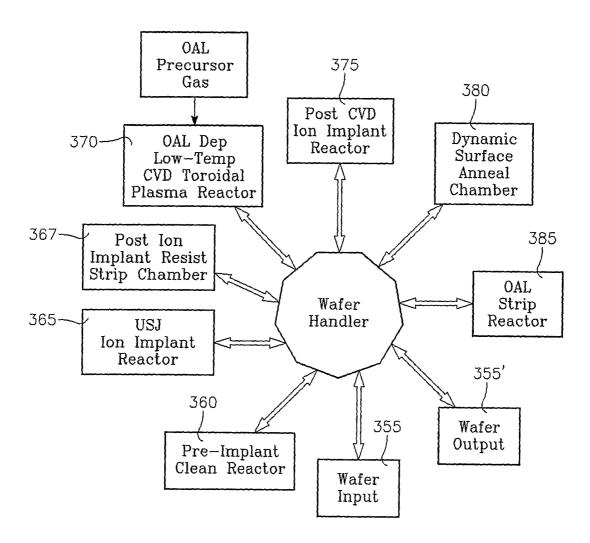

- [52] FIG. 33 illustrates an integrated system for performing all the steps entailed in forming ultra-shallow junctions in the surface of a wafer.

# DETAILED DESCRIPTION OF THE INVENTION

#### Introduction:

All the problems mentioned above in the background discussion are solved [53] by depositing the amorphous carbon optical absorber layer in a low temperature PECVD process employing a toroidal source plasma reactor. The toroidal source can be operated with a wide range of ion energy, unlike either the HDPCVD reactor or the capacitively coupled PECVD reactor. Thus, a moderate ion flux can be maintained along with a moderate (or high) ion energy, so that a high quality bond between the deposited layer and the underlying substrate or thin films is established without requiring elevated wafer temperatures. In fact, the wafer temperature may be as cool as room temperature (which minimizes any impact on the implanted ultra-shallow junctions such as recrystallization of an amorphous layer formed during the implant process, dopant cluster formation or thermal diffusion). As a result, the absorber layer formed by this process can withstand the laser beam exposure and extreme heating without separating from the wafer and without cracking. The wide bias power or bias voltage range over which the toroidal plasma source reactor may be operated enables the stress of the deposited

layer to be selected within a very wide range, i.e., from tensile to compressive stress levels. The wide source power range over which toroidal plasma source reactor may be operated enables the conformality of the deposited layer to be precisely controlled, for example, to guarantee a high degree of conformality for excellent step coverage. The toroidal source plasma reactor may be operated over a much wider range of chamber pressure (e.g., 10-80 mT), so that ion density and plasma sheath collisionality may be controlled over a much wider range. Since a high ion density is not required, a high wafer voltage and high ion energy may be maintained with a relatively small amount of bias power (e.g., 7 kV wafer voltage with only 7kW of bias power for a 300 mm wafer). The toroidal plasma source reactor does not require a dielectric window for coupling RF power from an inductive antenna into the chamber (and requires only a very thin dielectric "DCbreak"), and therefore a conductive shower head may be placed at the ceiling. This feature provides the best uniformity of process gas distribution and a highly uniform low-impedance RF ground reference over the wafer. Because there is no requirement for a dielectric window for inductive coupling, virtually the entire chamber can be metal and therefore be thermally controlled to regulate deposition during processing and to expedite post-processing high temperature cleaning of the chamber surfaces. The toroidal plasma source generates a plasma with low potential and the toroidal plasma current requires no ground return through chamber surfaces, so the potential to cause a drift-current out of the process region is low and therefore there is little or no deposition on chamber surfaces outside of the processing zone. Another advantage of the lack of any need for a dielectric window in the toroidal plasma reactor is that the reactor may be employed to deposit non-insulating materials on the wafer without bad effects from accumulation of the non-insulating material on chamber interior surfaces.

[54] The present invention concerns dynamic surface annealing of ultra-shallow junctions in a semiconductor wafer using an array of continuous wave (CW) diode lasers collimated and focused to a single knife-edge light beam. The knife-edge light beam is highly intense and is scanned across the wafer in a direction transverse to its length. The temperature is raised briefly (to nearly the melting point of silicon) in such a highly localized area about the beam, that its cooling is

extremely rapid because of the small volume that is thus heated at any particular instant. This technology is described in U. S. Patent Application Publication No. US 2003/0196996 A1 by Dean C. Jennings et al., published Oct. 23, 2003 (hereinafter referred to as Publication A). At extremely small feature sizes (e.g., 45 nm), it is difficult to heat the wafer uniformly due to the presence of 3-dimensional topological features. These features may be comprised of different materials or have different optical properties. Such features render heat absorption non-uniform. They also render the surface emissivity non-uniform, so that it is impossible to monitor the surface temperature accurately.

These problems have been addressed in the past by depositing an optical [55] absorber layer over the entire wafer (which is later removed). This absorber layer has a high imaginary component of the complex refractive index (the "k" value of the n + ik, where 'n' is the refractive index and 'k' is the extinction coefficient). A sufficiently thick absorber layer masks emissivity variations due to the underlying films on the wafer, as well as their dimensional topological features, promoting improved laser absorption and uniformity of the heat absorption across the wafer (as well as magnitude and uniformity of surface emissivity). The problem is that the optical absorber layer must withstand the near-melting point temperatures sustained during dynamic surface (laser) annealing, without peeling or separating from the underlying layers. In order to avoid such peeling or separation, a high quality bond between the absorber layer and the underlying wafer features is achieved by depositing the absorber layer at a high temperature. The high temperature also serves to provide good film structural, optical and electrical properties. The problem is that if the wafer temperature is sufficiently high to achieve a high quality absorber layer that is immune to cracking, peeling or separation, then the wafer temperature causes the undesirable effects of either recrystallizing a pre-existing amorphous silicon layer or causes the ultra-shallow junctions to diffuse and thereby become poorly defined, thereby degrading circuit features on the wafer. Lower temperature conventional CVD absorber layers also have significantly reduced "k" values, requiring much thicker films to achieve the same net absorption and immunity to underlayer absorption characteristics.

[56] These problems are overcome in accordance with the invention by depositing the absorber layer in a low temperature chemical vapor deposition process using the toroidal plasma source low temperature CVD process of U.S. Patent Application Publication No. 2004/0200417 by Hiroji Hanawa et al., published Oct. 14, 2004 (hereinafter referred to as Publication B). This process employs a unique toroidal source plasma reactor that is described in detail in Publication B. The process is carried out at very low temperatures, such as under 300 degrees C or even as low as room temperature. Thus, it has little or no bad effects (e.g., thermal diffusion or dopant migration, or re-crystallization) upon the ultra-shallow junction features already formed on the wafer. If the absorber layer is to be amorphous carbon, then a carbon-containing process gas is employed. In order to enhance absorption of heat from the laser beam in the absorber layer, the deposited amorphous carbon layer is rendered more opaque by doping it with an impurity such as boron, phosphorous, arsenic, silicon or germanium. This may be done by an ion implantation step using the toroidal source plasma immersion ion implantation (P3i) process also described in Publication B, or (alternatively) by incorporating boron into the process gas mixture during the CVD low temperature deposition process. Ion implantation of other impurities (such as nitrogen) into the deposited amorphous carbon absorber layer may be employed in order to adjust or control the dielectric constant or refractive index of the absorber layer, in order to obtain a high dielectric constant, for example. Alternatively, other impurities (such as nitrogen, hydrogen, oxygen, fluorine) may be incorporated by including them in the process gas mixture during the CVD low temperature deposition process.

[57] The thermal properties, i.e., the immunity of the low temperature deposited absorber layer from peeling, cracking or separation during the dynamic surface laser annealing step, are enhanced by making the deposited layer a compressively stressed layer. This is accomplished by raising the RF plasma bias power or bias voltage to a relatively high level in the low temperature plasma CVD process, as described in Publication B. Excellent step coverage over all the 3-dimensional micro-circuit features previously formed on the wafer is obtained by depositing the absorber layer with relatively high conformality. This is accomplished by

setting the plasma RF source power in the low temperature plasma CVD process to a relatively high level, as described in Publication B. The adhesion of the deposited film may be enhanced by pre-treating the wafer in a cleaning process to remove surface oxidation or other contamination. One pre-treatment process uses a hydrogen plasma generated by plasma source power or bias power. A bias voltage may be added to enhance the cleaning rate. It is believed that the hydrogen ions and/or radicals etch the thin oxide or contaminant film. Another pre-treatment process uses a nitrogen and/or oxygen plasma generated by plasma source power or bias power. A bias voltage may be added to enhance the cleaning rate. It is believed that the nitrogen and/or oxygen ions and/or radicals etch the thin organic contaminant film. This pre-treatment process may be followed by the hydrogen plasma pre-treatment process to remove oxidation. Another pretreatment process uses an inert gas plasma such as helium, neon, argon or xenon to sputter clean the surface oxidation or contamination. Alternatively, a wet pretreatment process may be used to clean the wafer surface (to enhance bonding) prior to depositing the film.

[58] The absorber layer film optical properties may be tuned with process variables in order to have a high absorption or extinction coefficient or imaginary part of the complex refractive index at the wavelength of radiation of the laser light beam and the wavelength of the temperature measurement pyrometer. Such process variables may include impurity (e.g., nitrogen) concentration in the absorber layer, dopant (e.g., boron) concentration in the absorber layer, wafer temperature, process gas pressure, gas flow rates (of C-containing gas, impuritycontaining-gas, dilution gas such as helium, hydrogen or argon), RF bias voltage or power, RF plasma source power, process time and layer thickness. Additional enhancement of the properties of the absorber layer may be obtained by grading the concentration of such impurities with depth in the layer. This may be accomplished by adjusting the implantation depth profile of impurities that are ion implanted by the P3i process referred to above, or by ramping the concentration of such impurities in the process gas or changing RF bias voltage or power or RF plasma source power or pressure during the low temperature CVD process described in Publication B. Additional enhancement of the properties of the

absorber layer may be obtained by curing the wafer with deposited absorber layer. Curing may include thermal (time at temperature) or UV exposure or a combination. This may further increase or stabilize the absorption or extinction coefficient or imaginary part of the complex refractive index.

The same toroidal source plasma chamber of Publication B may be [59] employed to perform both the absorber layer deposition using low temperature CVD process of Publication B as well as any P3i ion implantation processes (as described in Publication B) of impurities into the absorber layer, so that the wafer need not be transported between different chambers. Moreover, the process chamber of Publication A (that performs the laser beam dynamic surface anneal (DSA) process) is preferably integrated into the same tool or platform with the toroidal source plasma reactor of Publication B, so that the wafer can be coated with the absorber layer (e.g., of amorphous carbon), the absorber layer may be enhanced by P3i ion implantation of selected impurities and/or dopants, and the wafer then laser annealed using the DSA laser light source of Publication A, all in the same tool. This reduces risk of contamination of the wafer. Moreover the same toroidal plasma source chamber or a second (dedicated) toroidal source plasma chamber (of the same type described in Publication B) or a different type of plasma chamber may be integrated onto the same tool or platform for removing the absorber layer upon completion of the laser anneal DSA process.

[60] A fully integrated process requires the following chambers which are used on a given wafer in the following order: a plasma immersion ion implantation (P3i) chamber for implanting dopants to form ultra-shallow junction (USJ) source/drain structures; a resist strip chamber for removing the USJ structure-defining or patterned photoresist; a wet clean chamber for post resist-strip cleaning; a toroidal source or P3i plasma reactor for performing the low temperature CVD process by which the amorphous carbon absorber layer is formed; a chamber containing the DSA multiple laser light source and scanning apparatus; a carbon-strip chamber for removing the absorber layer; and a wet clean chamber for post-strip cleaning of the wafer. At least two or more of the foregoing chambers may be integrated onto a common platform to reduce wafer handling, reduce contamination and increase productivity.

[61] The absorber layer is preferably amorphous carbon, although other suitable materials may be chosen instead. The product of the film thickness and the absorption or extinction coefficient or imaginary part of the complex refractive index at the wavelength of radiation of the laser light beam of the absorber layer must be sufficient to deposit over all the 3-dimensional topological features or micro-circuit structures on the wafer such that the optical properties of the underlying materials are masked to the degree required by the absorber layer. The absorber layer optical properties are selected to maximize heat absorption from the laser beam. The absorber layer thermal or thermal-mechanical properties are selected to render the absorber layer immune from peeling, cracking or separation from the underlying wafer during DSA laser annealing despite the near-melting point temperatures of the process.

- [62] The absorber layer maximizes uniform absorption from the laser beam even in the presence of pronounced 3-dimensional surface topological features on the wafer. The absorber layer is a good heat conductor and therefore provides uniform heat distribution across the locally radiated area of the wafer. The uniform surface of the absorber layer renders the surface emissivity of the wafer uniform, so that accurate measurements of wafer temperature may be continuously made, for good process control.

- [63] The absorber layer as described above may also be advantageously used for more conventional annealing techniques, such as RTA (rapid thermal anneal) or "spike" anneal or flashlamp anneal, to improve the magnitude or uniformity of light absorption, and to reduce across wafer and wafer-to-wafer temperature variation. Such a layer may be used to mask the variation in the optical properties, including 3-D geometric effects, of underlayers. In this case, the absorber layer deposition / implantation is tuned for the desirable optical properties across the spectrum of wavelengths that the filament or arc/gas discharge light source produces. The heat absorber layer of the present invention may also be used in RTA annealing of semiconductor wafers having 3-dimensional micro-circuit topological features. In such a case, the absorber layer optical properties are adapted to the RTA light source. Such devices may include

such highly reflective structures as silicon-on-insulator or polysilicon on dielectric structures.

# Laser Thermal Flux Annealing Light Source:

The dynamic surface anneal light source referred to above uses CW diode lasers to produce very intense beams of light that strikes the wafer as a thin long line of radiation. The line is then scanned over the surface of the wafer in a direction perpendicular to the long dimension of the line beam. One embodiment of the light source is illustrated in the schematic orthographic representation of FIG. 1. A gantry structure 110 for two-dimensional scanning includes a pair of fixed parallel rails 112, 114. Two parallel gantry beams 116, 118 are fixed together a set distance apart and supported on the fixed rails 112, 114 and are controlled by an unillustrated motor and drive mechanism to slide on rollers, source, or ball bearings together along the fixed rails 112, 114. A beam source 120 is slidably supported on the gantry beams 116, 118, e.g. suspended below the beams 116, 118 and is controlled by unillustrated motors and drive mechanisms to slide along them. A silicon wafer 40 or other substrate is stationarily supported below the gantry structure 110. The beam source 120 includes laser light source and optics to produce a downwardly directed fan-shaped beam 124 that strikes the wafer 40 as a line beam 126 extending generally parallel to the fixed rails 112, 114, in what is conveniently called the slow direction. Although not illustrated here, the gantry structure further includes a Z-axis stage for moving the laser light source and optics in a direction generally parallel to the fan-shaped beam 124 to thereby controllably vary the distance between the beam source 120 and the wafer 40 and thus control the focusing of the line beam 126 on the wafer 40. Exemplary dimensions of the line beam 126 include a length of 1 cm and a width of 100 microns with an exemplary power density of 400kW/cm<sup>2</sup>. Alternatively, the beam source and associated optics may be stationary while the wafer is supported on a stage which scans it in two dimensions.

[65] In typical operation, the gantry beams 116, 118 are set at a particular position along the fixed rails 112, 114 and the beam source 120 is moved at a uniform speed along the gantry beams 116, 118 to scan the line beam 126

perpendicularly to its long dimension in a direction conveniently called the fast direction. The line beam 126 is thereby scanned from one side of the wafer 40 to the other to irradiate a 1cm swath of the wafer 40. The line beam 126 is narrow enough and the scanning speed in the fast direction fast enough that a particular area of the wafer is only momentarily exposed to the optical radiation of the line beam 126 but the intensity at the peak of the line beam is enough to heat the surface region to very high temperatures. However, the deeper portions of the wafer 40 are not significantly heated and further act as a heat sink to quickly cool the surface region. Once the fast scan has been completed, the gantry beams 116, 118 are moved along the fixed rails 112, 114 to a new position such that the line beam 126 is moved along its long dimension extending along the slow axis. The fast scanning is then performed to irradiate a neighboring swath of the wafer 40. The alternating fast and slow scanning are repeated, perhaps in a serpentine path of the beam source 120, until the entire wafer 40 has been thermally processed. One example of optics beam source 120, orthographically illustrated in FIGS. 2 and 3, receives laser radiation at about 810 nm from two laser bar stacks 132, one of which is illustrated in end plan view in FIG. 4. Each laser bar stack 132 includes 14 parallel bars 134, generally corresponding to a vertical p-n junction in a GaAs semiconductor structure, extending laterally about 1 cm and separated by about 0.9 mm. Typically, water cooling layers are disposed between the bars 134. In each bar 134 are formed 49 emitters 136, each constituting a separate GaAs laser emitting respective beams having different divergence angles in orthogonal directions. The illustrated bars 134 are positioned with their long dimension extending over multiple emitters 136 and aligned along the slow axis and their short dimension corresponding to the less than 1-micron p-n depletion layer aligned along the fast axis. The small source size along the fast axis allows effective collimation along the fast axis. The divergence angle is large along the fast axis and relatively small along the slow axis.

[66] Returning to FIGS. 2 and 3 two arrays of cylindrical lenslets 140 are positioned along the laser bars 134 to collimate the laser light in a narrow beam along the fast axis. They may be bonded with adhesive on the laser stacks 132 and aligned with the bars 134 to extend over the emitting areas 136. The two sets

of beams from the two bar stacks 132 are input to conventional optics 142. The source beam 158 is then passed through a set of cylindrical lenses 162, 164, 166 to focus the source beam 158 along the slow axis before it enters a one-dimensional light pipe 170 with a finite convergence angle along the slow axis but being substantially collimated along the fast axis. The light pipe 170, more clearly illustrated in the orthographic view of FIG. 5 acts as a beam homogenizer to reduce the beam structure along the slow axis introduced by the multiple emitters 136 in the bar stack 132 spaced apart on the slow axis. The light pipe 170 may be implemented as a rectangular slab 172 of optical glass having a sufficiently high index of refraction to produce total internal reflection. It has a short dimension along the slow axis and a longer dimension along the fast axis. The slab 172 extends a substantial distance along an axis 174 of the source beam 158 converging along the slow axis on an input face 176 is internally reflected several times from the top and bottom surfaces of the slab 172, thereby removing much of the texturing along the slow axis and homogenizing the beam along the slow axis when it exits on an output face 178. The source beam 158, however, is well collimated along the fast axis and the slab is wide enough that the source beam 158 is not internally reflected on the side surfaces of the slab 172 but maintains its collimation along the fast axis. The light pipe 170 may be tapered along its axial direction to control the entrance and exit apertures and beam convergence and divergence. The one-dimensional light pipe can alternatively be implemented as two parallel reflective surfaces corresponding generally to the upper and lower faces of the slab 172 with the source beam passing between them.

[67] The source beam output by the light pipe 170 is generally uniform. As further illustrated in the schematic view of FIG. 6, a further anamorphic lens set 180, 182 expands the output beam in the slow axis and includes a generally spherical lens to project the desired line beam 126 on the wafer 40. The anamorphic optics 180 shape the source beam in two dimensions to produce a narrow line beam of limited length. In the direction of the fast axis, the output optics have an infinite conjugate for the source at the output of the light pipe 170 (although systems may be designed with a finite source conjugate) and a finite conjugate at the image plane of the wafer 40 while, in the direction of the slow

axis, the output optics has a finite conjugate at the source at the output of the light pipe 170 and a finite conjugate at the image plane. Further, in the direction of the slow axis, the radiation from the multiple laser diodes of the laser bars is homogenized, which is otherwise non-uniform. The ability of the light pipe 170 to homogenize strongly depends on the number of times the light is reflected traversing the light pipe 170. This number is determined by the length of the light pipe 170, the direction of the taper if any, the size of the entrance aperture 176 and the exit aperture 178 as well as the launch angle into the light pipe 170. Further anamorphic optics focus the source beam into the line beam of desired dimensions on the surface of the wafer 40.

[68] Figures 7 and 8 are perpendicularly arranged side views along the fast and slow axes respectively showing the light pipe 170 and some associated optics. In the direction of the fast axis, the beam from the lasers bars 132 is well collimated and not affected by the light pipe 170 or anamorphic optics. On the other hand, in the direction of the slow axis, the input anamorphic optics 162, 164, 166 condense and converge the beam into the input end of the light pipe 170. The beam exits the light pipe 170 with substantially uniform intensity along the slow axis but with a substantial divergence. The output anamorphic optics 180, 182 expand and collimate the output beam along the slow axis.

[69] In order to regulate or control the peak wafer temperature, the temperature of the illuminated portion of the wafer 40 is constantly monitored by a pyrometry system. The pyrometry system uses the same optics used to focus the laser source light on the wafer to direct thermal radiation emitted from the illuminated area of the wafer 40 in the neighborhood of the line beam 126 in the reverse direction to a pyrometer 161 schematically shown in FIG. 3. The pyrometer 161 includes an optical detector 163, such as a photodiode, and an optical filter 165 blocking the wavelength of the laser light source (e.g., 810 nm). The pyrometer filter 165 preferably is a narrow passband filter centered at a region of the Plankian blackbody radiation curve which is quickly changing at the temperature of interest. For example, the pyrometer passband may be centered at 950 nm, in which case the detector 163 is a silicon photodiode. The optics are generally reciprocal and thus in the reverse direction detect only a small area of the wafer 40

on or very near to the line beam 126, and optically expands that image to a much larger area. The output of the detector 163 is used by a controller 167 to control the power to the laser array 132. A filter (not shown) may be placed in front of the laser array 132 to block any emission it may have at the pyrometer wavelength (e.g., 950 nm).

[70] The features of the present invention described below may be employed with other laser types: CO2 gas-lasers; Neodymium YAG lasers (neodymium:yttrium-aluminum-garnet) which may optionally be frequency-doubled; Excimer lasers (a rare-gas halide or rare-gas metal vapor laser emitting in the ultraviolet (126 to 558 nm) that operates on electronic transitions of molecules, up to that point diatomic, whose ground state is essentially repulsive) with excitation by E-beam or electric discharge; diode lasers (light-emitting diode designed to use stimulated emission to form a coherent light output).

# Low Temperature CVD Process of the Toroidal Source Plasma Reactor:

FIG. 9 depicts a toroidal source plasma reactor with which a low [71] temperature CVD process is carried out. The plasma reactor has a cylindrical side wall 10, a ceiling 12 and a wafer contact-cooling electrostatic chuck 14. A pumping annulus 16 is defined between the chuck 14 and the sidewall 10. Process gases are introduced through a gas distribution plate 18 (or "showerhead") forming a large portion of the ceiling 12. Optionally, process gases may also be introduced through side injection nozzles 20 or by other means. The reactor of FIG. 9 has a reentrant RF toroidal plasma source consisting of an external reentrant tube 22 coupled to the interior of the reactor through opposite sides of the sidewall 10 (or, through openings in the ceiling 12 not shown in FIG. 1). An insulating ring 23 provides a D.C. break along the reentrant tube 22. The toroidal plasma source further includes an RF power applicator 24 that may include a magnetically permeable toroidal core 26 surrounding an annular portion of the reentrant tube 22, a conductive coil 28 wound around a portion of the core 26 and an RF plasma source power generator 30 coupled to the conductive coil through an optional impedance match circuit 32. A second external reentrant tube 22' transverse to the first tube 22 is coupled to the interior of the reactor through

opposite sides of the sidewall 10 (or, through openings in the ceiling 12 not shown in FIG. 1). An insulating ring 23' provides a D.C. break along the second reentrant tube 22'. A second RF power applicator 24' includes a magnetically permeable toroidal core 26' surrounding an annular portion of the reentrant tube 22', a conductive coil 28' wound around a portion of the core 26' and an RF plasma source power generator 30' coupled to the conductive coil through an optional impedance match circuit 32'. A process gas supply 34 is coupled to the gas distribution plate 18 (or to the gas injectors 20). A semiconductor wafer or workpiece 40 is placed on top of the chuck 14. A processing region 42 is defined between the wafer 40 and the ceiling 12 (including the gas distribution plate 18). A toroidal plasma current oscillates at the frequency of the RF plasma source power generator 30 along a closed toroidal path extending through the reentrant tube 22 and the processing region 42.

RF bias power or voltage is applied to the chuck 14 by an RF bias power generator 44 through an impedance match circuit 46. A D.C. chucking voltage is applied to the chuck 14 from a chucking voltage source 48 isolated from the RF bias power generator 44 by an isolation capacitor 50. The RF power delivered to the wafer 40 from the RF bias power generator 44 can heat the wafer 40 to temperatures beyond 400 degrees C, depending upon the level and duration of the applied RF plasma bias power from the generator 44 if no wafer cooling is employed. It is believed that about 80% or more of the RF power from the bias power generator 44 is dissipated as heat in the wafer 40. The wafer support pedestal 14 is an electrostatic chuck having an insulative or semi-insulative top layer or puck 60. A metal (molybdenum, for example) wire mesh or metal layer 62 inside of the puck 60 forms a cathode (or electrode) to which the D.C. chucking voltage and RF bias voltage is applied. The puck 60 is supported on a metal layer 64 that rests on a highly insulative layer 66. A metal base layer 68 may be connected to ground. The wafer 40 is electrostatically held on the chuck 14 by applying a D.C. voltage from the chucking voltage source 48 to the electrode 62. This induces an opposite (attractive) image charge in the bottom surface of the wafer 40. The effective gap between the two opposing charge layers is so minimal as a result of the upward charge migration in the semi-

insulator layer 60 that the attractive force between the chuck and the wafer 40 is very large for a relatively small applied chucking voltage. The puck semi-insulator layer 60 therefore is formed of a material having a desired charge mobility, so that the material is not a perfect insulator. RF bias power or voltage from the RF bias power generator 44 may be applied to the electrode 62 or, alternatively, to the metal layer 64 for RF coupling through the semi-insulative puck layer 60. Heat is removed from the puck 60 by cooling the metal layer 64. For this reason, internal coolant passages 70 are provided within the metal layer 64 coupled to a coolant pump 72 and heat sink or cooling source 74. Heat sink 74 may optionally be a heat exchanger which can also furnish heat, if desired, to metal layer 64. A very high heat transfer coefficient between the wafer 40 and the puck 60 is realized by maintaining a very high chucking force. The force can be enhanced by providing a polished surface 60a.

A low-temperature chemical vapor deposition process preferably employs [73] an electrostatic wafer chuck that both serves to couple RF bias power or voltage to the wafer and removes (or provides) heat to maintain the wafer temperature at the desired level or below a threshold. More preferably, the electrostatic chuck is the type described immediately above with reference to FIG. 9 and in greater detail in U.S. Patent Application Serial No. 10/929,104 filed August 26, 2004 by Douglas A. Buchberger, Jr., et al. and entitled GASLESS HIGH VOLTAGE HIGH CONTACT FORCE WAFER CONTACT-COOLING ELECTROSTATIC The use of the aforementioned electrostatic chuck (with its high heat CHUCK. transfer coefficient) permits operating of the source power at a higher level (i.e., 5kW per toroidal source) and bias power at a higher level (i.e., 10kW) while maintaining wafer temperature under 200 degrees C, or even under 100 degrees C, if desired. In addition, the chamber pressure is maintained in a range between about 5 and 200 mtorr that is sufficiently low to avoid a defective (e.g., flaky) CVD layer without requiring high wafer temperature. The low chamber pressure avoids excessive ion recombination that would otherwise depress plasma ion density and/or ion energy below that required to deposit a high quality film without heating the workpiece. The maintenance of a moderate plasma ion density in the process region obviates the need for any heating of the wafer, so

that a high quality CVD film can be deposited at very low temperature (less than 100 degrees C), unlike the PECVD reactor. The fact that the plasma density is not very high and the plasma source power level need not be high permits a wide operating range of bias voltage, without requiring excessive bias power levels, unlike the HDPCVD reactor.

The fact that the CVD reaction can be carried out in the toroidal source [74] reactor at a low source power level, if desired, implies a large window in which source power can be varied, from the minimum level up to a maximum level (e.g., about 5kW per toroidal source). This window is sufficiently large to vary the conformality of the CVD deposited layer between non-conformal (0.1 conformality ratio) and conformal (>0.5 conformality ratio). At the same time, the stress level of the CVD deposited layer may be varied by varying the plasma bias power or voltage applied to the wafer between a low level for tensile stress in the deposited layer (e.g., 500 Watts) and a high level for compressive stress in the deposited layer (e.g., 3 kWatts or higher). As a result, the conformality and stress of each plasma CVD deposited layer are independently adjusted by adjusting the source and bias power levels, respectively, to different layers which are either conformal or non-conformal and having either tensile or compressive stress. Nonconformal films are useful for deep trench filling and for creating removable layers over photoresist. Conformal layers are useful for etch stop layers and passivation layers. Layers with compressive stress enhance carrier mobility in underlying or adjacent P-channel MOSFETs, while layers with tensile stress enhance carrier mobility in underlying or adjacent N-channel MOSFETs. The low minimum plasma source power of the toroidal source plasma reactor of FIG. 9 and the highly controllable plasma ion density that the reactor provides as source power is increased follows from the unique reactor structure of the toroidal source plasma reactor. Plasma source power is applied via a power applicator to a reentrant external conduit through which the toroidal RF plasma current circulates (oscillates), so that the source power density is very low. This feature makes plasma ion density at the wafer surface highly controllable and not subject to excessive increases with plasma source power, in contrast to the HDPCVD plasma reactor (when the transition to inductive coupling occurs). Moreover, the highly

efficient coupling of the RF source power applicator to the process gases within the external reentrant conduit makes the minimum plasma source power for plasma ignition much smaller than a conventional reactor (such as the HDPCVD reactor). The low temperature CVD process solves the problem of providing a plasma CVD process for 65 nm or 45 nm or smaller devices (for example) where the device temperature cannot exceed 400 degrees C for any significant amount of time without destroying the device structure. It also permits plasma CVD deposition over photoresist layers without disrupting or destroying the underlying photoresist. This possibility opens up an entirely new class of processes described below that are particularly suited for nm-sized design rules and can be carried out without disturbing photoresist masking on the device.

- [75] Post-CVD ion implantation processes can be carried out in the same toroidal source reactor that was used to perform the low temperature CVD process. The post CVD ion implantation processes include processes for enhancing adhesion between an amorphous or polycrystalline CVD deposited layer and its base layer, for raising the proportion of a species in the CVD layer beyond a stochiometric proportion, for implanting into the CVD layer a species not compatible with plasma CVD processes, or for implanting into the CVD layer a species that alters a particular material quality of the layer, such as dielectric constant or stress.

- [76] The low temperature plasma CVD process is useful for CVD formation of silicon films, silicon nitride films, silicon-hydrogen films, silicon-nitrogen-hydrogen films, and versions of the foregoing films further containing oxygen or fluorine. The films exhibit excellent quality and excellent thermal properties, being free of cracking, peeling, flaking, etc., despite the very low temperature at which the CVD process is carried out. For application to CMOS devices, passivation layers are deposited over P- and N-channel devices with compressive and tensile stresses, respectively, using high non-conformality to enable selective etching and photoresist masking and removal, and etch stop layers with zero (neutral) stress can be deposited over all devices with high conformality. Low temperature plasma CVD process is also useful for CVD formation of carbon films.

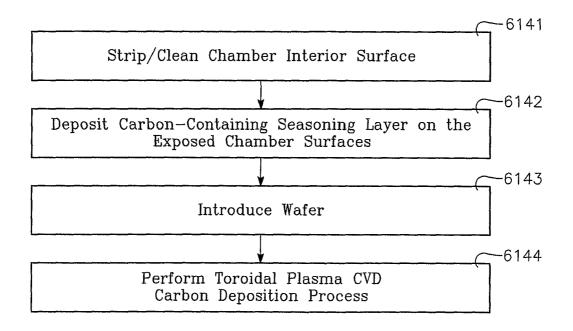

A low temperature plasma CVD process employing the toroidal reactor of FIG. 9 is illustrated in FIG. 10. In this process a carbon or carbon-containing layer is deposited in a toroidal plasma chemical vapor deposition process. The deposited layer may have some of the attributes of an amorphous carbon material, a polymer carbon material, or a graphitic carbon material, for example, and a wide range of electrical and optical properties, depending upon how the process is carried out. In a later portion of this specification, process control of the properties of the deposited material will be described. A first step (block 6105 of FIG. 10), which is optional, is to coat the interior surfaces of the chamber with a passivation layer to prevent or minimize metal contamination on the wafer. The passivation layer may, for example, be of the same material as the CVD film that is to be deposited (e.g., a material containing carbon). The passivation coating on the chamber interior surfaces is carried out by introducing a suitable process gas mixture (e.g., a carbon-containing gas such as propylene), and applying plasma source power to generate a toroidal RF plasma current, as in the above-described embodiments. This step is carried out until a suitable thickness of the passivation material has been deposited on interior chamber surfaces. Then, a production workpiece or semiconductor wafer is placed on the wafer support pedestal (block 6107 of FIG. 10). Process gases are introduced (block 6109) containing carbon and (optionally) other species such as hydrogen, or nitrogen, for example. The chamber pressure is maintained at a low or modest level, e.g., from about 5 to about 200 mTorr (block 6111 of FIG. 10). A reentrant toroidal plasma current is generated in the toroidal source reactor (block 6113). The toroidal plasma current is produced by coupling RF plasma source power (e.g., 100 Watts to 5 kW) (block 6113-1 of FIG. 10) into each re-entrant external conduit 22, 22', and applying RF plasma bias power between 0 and 10 kWatts (block 6113-2 of FIG. 10). The source power is preferably at an HF frequency on the order of 10 MHz (e.g., such as 13.56 MHz), which is very efficient for producing plasma ions. The bias power is preferably at an LF frequency on the order of a MHz (e.g., such as 2 MHz), which is very effective for producing a relatively large plasma sheath voltage for a given amount of bias power. The magnitude of the source power delivered by the RF generators 180 is adjusted to deposit by chemical vapor deposition a film on

the wafer with the desired conformality (block 6115). The magnitude of the bias power or voltage delivered by the RF generator 162 is adjusted so that the deposited film has the desired stress, compressive or tensile (block 6117 of FIG. 10). The foregoing process is carried out until the desired deposited film thickness is reached. Thereafter, certain optional post-CVD ion implant processes

may be performed (block 6119 of FIG. 10).

FIG. 11A is a graph of conformality ratio of the deposited layer (vertical axis) as a function of the applied RF source power (horizontal axis). As shown in FIG. 11B, the conformality ratio of a layer 6121 deposited by a CVD process on a base layer or substrate 6123 is the ratio C/D of the thickness C of a vertical section 6121a of the layer 6121 (deposited on a vertical face 6123a of the base layer 6123) to the thickness D of a horizontal section 6121b of the layer 6121 (deposited on a horizontal section 6123b of the base layer 6123). A conformality ratio exceeding 0.5 indicates a highly conformal CVD-deposited film. A conformality ratio of about 0.1 indicates a non-conformal CVD-deposited film. FIG. 11A illustrates how the wide source power window of the toroidal source reactor of FIG. 9 spans the conformality ratio range from non-conformal (at about 100 Watts source power) to highly conformal (at about 1 kW source power). FIG. 11A shows that the same toroidal source reactor can be used for plasma CVD deposition of both conformal and non-conformal films. FIG. 12 is a graph illustrating the CVD deposition rate (vertical axis) as a function of applied source power (horizontal axis). From zero up to 100 Watts of RF source power, no plasma is ignited in the toroidal source reactor of FIG. 9, and the deposition rate is zero. Starting at about 100 Watts of source power at about 13,56 MHz with a constant bias voltage of about 5 kV at about 2 MHz, the deposition rate starts at about 500 Angstroms per minute (at 100 Watts source power) and reaches about 1000 Angstroms per minute (at about 2 kW of source power). The advantage is that the deposition rate is sufficiently low so that a high quality defect-free CVD film is formed without requiring any heating or annealing to cure defects that would otherwise form at high deposition rates (e.g., 5,000 Angstroms per minute). Therefore, the source power of the toroidal plasma reactor (FIG. 9) can be varied anywhere within the range required to switch the conformality ratio between non-

conformal and conformal (i.e., from 200 Watts to 2 kW) without requiring heating of the wafer, so that the wafer can remain at a low processing temperature, i.e., below 200 or even 100 degrees C. The fact that the toroidal plasma reactor source power may be so increased (to attain a high degree of conformality) without causing excessive CVD deposition rates follows from the structure of the toroidal source reactor which avoids excessive increases in ion density in the process region overlying the wafer 120. Such excessive ion density is avoided in part because each plasma source power applicator (i.e., each core 26, 26' surrounding a respective reentrant conduit 22, 22' and the corresponding primary winding 28, 28') applies plasma source power to a section of the reentrant conduit 22, 22' that is external of the reactor chamber defined by the side wall 10 and ceiling 12, and is remote from the process region 42 overlying the wafer 40. Fortunately, the low and therefore highly controllable increase in plasma ion density with source power of the toroidal plasma reactor of FIG. 9 is accompanied by a very low minimal source power for plasma ignition (e.g., only 100 Watts), which results in the wide source power window spanning the entire conformality range. This minimal source power level for plasma ignition is a result of the efficient manner in which the toroidal source reactor of FIG. 9 generates the toroidal RF plasma current at HF frequencies such as 13.65 MHz. Another feature of the toroidal plasma reactor of FIG. 9 is the wide range of RF plasma bias (sheath) voltage with which the reactor may be operated (e.g., from zero to 10 kV). One aspect of this feature is illustrated in the graph of FIG. 13: the bias voltage operating range (horizontal axis of FIG. 13) spans the range of stress in the CVD deposited film (vertical axis in the graph of FIG. 13), from tensile stress (+ 1 gigaPascal) to compressive stress (-1 gigaPascal). Such post-CVD ion implantation treatments will be described later in this specification. The large range in RF plasma bias (sheath) voltage is attained by using a low frequency (LF) plasma bias source, such as a 2 MHz RF source. Such a low frequency translates to a high impedance across the plasma sheath over the surface

of the wafer, with a proportionately higher sheath voltage. Thus, a relatively small amount of plasma bias power (5 kW) can produce a very large sheath voltage (10 kV) at the wafer surface. Such a relatively low bias power level

reduces the heating load on the wafer and reduces the heat and electric field load on the wafer support pedestal. Of course, the toroidal source reactor of FIG. 9 does not require such a large sheath voltage in order to ignite or sustain a plasma, and the bias power can be reduced well below 5 kW, to zero, if desired, without extinguishing the plasma. The conformality selection (between non-conformal and highly conformal) illustrated in FIG. 11A and the stress selection (between tensile and compressive) illustrated in FIG. 13 are performed independently using the very wide source power and bias power operating windows of the toroidal source reactor of FIG. 9. As a result, the toroidal source reactor of FIG. 9 performs a low temperature CVD process of FIG. 10 in which different layers may be deposited with different selections of stress (tensile, zero, or compressive) and different selections of conformality ratio (non-conformal or highly conformal).