US 20010002056A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2001/0002056 A1 Manning

#### (54) PROCESS FOR MANUFACTURING INTEGRATED CIRCUIT SRAM

(75) Inventor: H. Montgomery Manning, Kuna, ID (US)

> Correspondence Address: SCHWEGMAN, LUNDBERG, WOESSNER & KLUTH, P.A. P.O. Box 2938 Minneapolis, MN 55402 (US)

- (73) Assignce: Micron Technology, Inc.

- (21) Appl. No.: 09/757,844

- (22) Filed: Jan. 10, 2001

### **Related U.S. Application Data**

(62) Division of application No. 08/854,867, filed on May 12, 1997.

## May 31, 2001 (43) **Pub. Date:**

#### **Publication Classification**

(51) Int. Cl.<sup>7</sup> ..... H01L 21/3205; H01L 21/4763; H01L 31/119; H01L 29/94; H01L 29/76; H01L 31/062; H01L 31/113 (52) U.S. Cl. ..... 257/368; 438/238; 438/587; 257/903; 257/904

#### (57) ABSTRACT

An SRAM cell is described which has a reduced cell area, and a reduced processing cost from conventional SRAM's. A fabrication process is described where self-aligned contacts to substrate active area and contact to a first layer of polysilicon are formed in one etch step. Electrical connection between the substrate and polysilicon is provided through a conductive layer coupled to the contacts. Self aligned contacts are fabricated to contact the active area.

FIG. 1

ഗ

#### PROCESS FOR MANUFACTURING INTEGRATED CIRCUIT SRAM

#### FIELD OF THE INVENTION

**[0001]** The present invention relates generally to a lowcost method for fabricating devices and integrated circuits with reduced cross-sectional area, and more specifically to a low-cost method for fabricating a static random access memory (SRAM) having reduced cross-sectional area.

#### BACKGROUND OF THE INVENTION

**[0002]** Electronics technology has proliferated with the advent of inexpensive and high performance integrated circuits, including communication transceivers, microprocessors, and memory. As a result, complex electronic systems, such as personal computers and cellular telephones have become widely held consumer goods.

**[0003]** Integrated circuits are fabricated with multiple processing steps. Integrated circuits are often fabricated with one or more device types including diodes, capacitors, and different varieties of transistors. These devices often have microscopic features that can only be manufactured with critical processing steps that require careful alignment of equipment used to build the devices. The critical processing steps are expensive because they must be accomplished with costly and sophisticated equipment, and experienced operators. When a processing step, particularly a critical processing step, is unsuccessful, the device and integrated circuit may fail. As a result, fabrication yields decrease. Therefore, a process with a diminished number of critical processing steps to reduce production costs is desirable.

**[0004]** Further, prior art typically uses Buried Contacts (BC) that connect a first conductor to substrate active area. The BC process however is a lower yielding process than the self aligned contacts described herein. In addition, BC's require full enclosure by the first conductor which requires additional area, thereby increasing the cell size.

**[0005]** Additionally, it is preferable to reduce the crosssectional area of devices and integrated circuits. When device and integrated circuit cross-sectional area is reduced, more devices and integrated circuits can be produced on a single substrate. As a result, device and integrated circuit fabrication costs decrease. Therefore, a low cost process with fewer critical processing steps for fabricating devices and integrated circuit with reduced cross-sectional areas is desirable. An integrated circuit is also needed which electrically couples substrate active area with a conductor without the need for a buried contact.

#### SUMMARY OF THE INVENTION

**[0006]** In accordance with the present invention, there is provided a method of fabricating devices having smaller cross-sectional areas with fewer critical processing steps. One embodiment of the present invention permits fabrication of an SRAM with fewer processing steps. Further features and advantages of the present invention, as well as the structure and operation of various embodiments of the present invention are described in detail below with reference to the accompanying drawings.

**[0007]** A static random access memory (SRAM) device is described which comprises a self-aligned electrical contact

to semiconductor active area and a second electrical contact to a non-active area electrically conductive structure. The self-aligned electrical contact and the second electrical contact are defined by a process comprising a single dielectric etch step.

[0008] In another embodiment, a method of fabricating electrical interconnects in a static random access memory (SRAM) cell is described. The method comprises the steps of forming first and second dielectric-conductor-dielectric layered structures, and a dielectric-conductor layered structure on a semiconductive base. Vertical dielectric structures are formed and attach to exposed vertical surfaces of the first and second dielectric-conductor-dielectric structures and the dielectric-conductor structure. A dielectric layer is formed over the first and second dielectric-conductor-dielectric structures, the dielectric-conductor structure, and exposed semiconductive base between the first and second structures. A single etch step is performed on the dielectric layer to define a self aligned contact to the semiconductive base located between the first and second dielectric-conductordielectric structures, and a contact to the conductor of the dielectric-conductor structure.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0009]** The present invention is described with reference to the accompanying drawings. In the drawings, like reference numbers indicate identical or functionally similar elements.

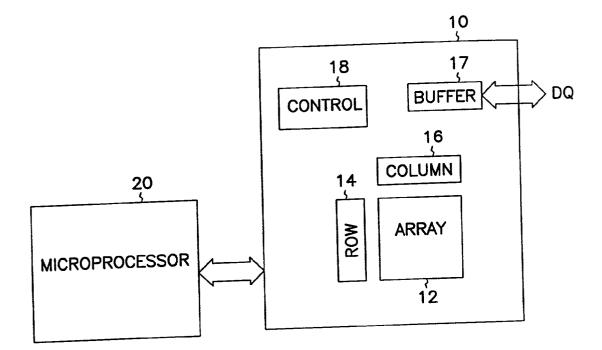

**[0010]** FIG. 1 is a block diagram of a memory device of the present invention;

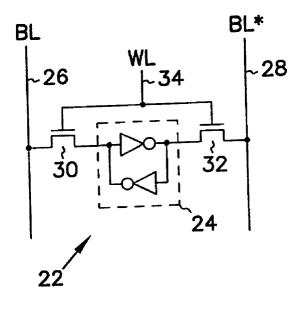

[0011] FIG. 2 is a schematic diagram of a basic static memory cell;

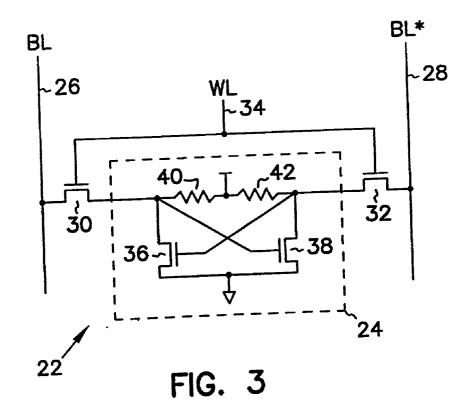

[0012] FIG. 3 is a more detailed schematic diagram of the static memory cell of FIG. 2;

**[0013]** FIG. 4 is a plan view of a static memory cell of the present invention;

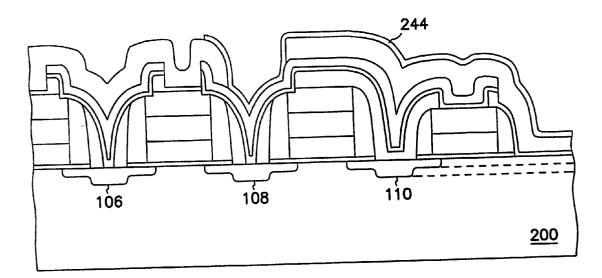

[0014] FIG. 5 is a cross-section of the static memory cell of FIG. 4;

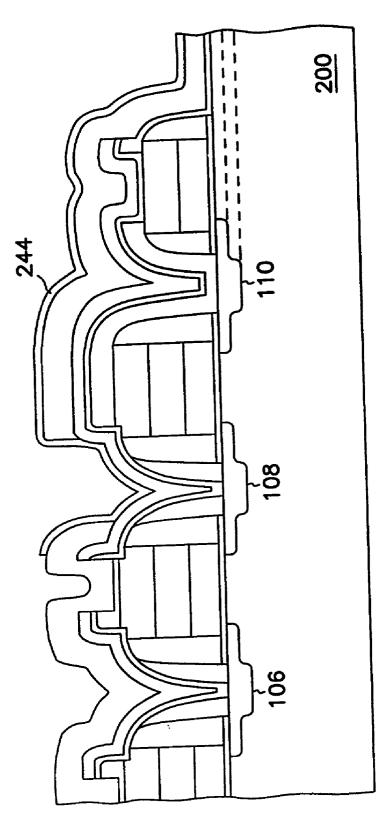

**[0015]** FIGS. **6-10** are a cross-section views of the static memory cell of **FIG. 4** during fabrication;

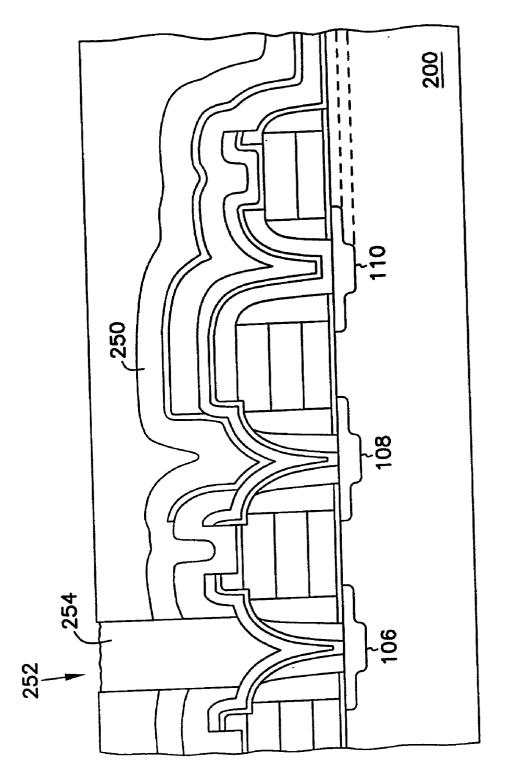

**[0016]** FIGS. 11 and 12 are cross-sections of the static memory cell of FIG. 4 illustrating the fabrication of a third layer of polysilicon; and

[0017] FIG. 13 illustrates the fabrication of a final dielectric layer and contact to FIG. 12.

#### DETAILED DESCRIPTION OF THE EMBODIMENTS

**[0018]** In the following detailed description of the preferred embodiments, reference is made to the accompanying drawings which form a part hereof, and in which is shown by way of illustration specific preferred embodiments in which the invention may be practiced. These embodiments are described in sufficient detail to enable those skilled in the art to practice the invention, and it is to be understood that other embodiments may be utilized and that logical, mechanical and electrical changes may be made without departing from the spirit and scope of the present invention. The following detailed description is, therefore, not to be taken in a limiting sense, and the scope of the present invention is defined only by the appended claims.

**[0019]** The present invention is directed towards facilitating low-cost fabrication of devices and integrated circuits. This goal is achieved by reducing the cross-sectional area of devices and integrated circuits, and fabricating the devices and integrated circuits with fewer critical processing steps.

[0020] Referring to FIG. 1, the basic static memory 10 is well known in the art to include a memory array 12 constructed of rows and columns of static memory cells having inputs and outputs corresponding to rows and columns. Row decode circuit 14 and column 16 decode circuitry is provided to access the memory array in response to an address provided by an external controller 20, such as a standard microprocessor. Control circuitry 18 is provided to control either synchronous or asynchronous data communication between the memory 10 and external devices. Buffers are coupled to the data communication lines (DQ's) for bi-directional data communication with the memory array 12. It will be appreciated that the description of SRAM 10 has been simplified to focus on specific features of the present invention and is not intended to be a detailed description of all the circuitry of a basic SRAM.

#### Basic SRAM Cell

[0021] FIG. 2 illustrates a functional diagram of a static memory cell 22. The memory cells operate as a data latch 24 which can be connected to complementary bit lines 26 and 28 by activating access transistors 30 and 32 using a common word line 34. The static memory cell can be fabricated as shown in FIG. 3 having two cross coupled pulldown transistors 36 and 38. To write data to the memory cell, the access transistors 30 and 32 are activated by providing a signal on the word line 34. Voltages provided on the complimentary bit lines 26 and 28 are sufficient to place the latch in a state corresponding to the bit lines. If the memory cell was storing data of an opposite logic state, the bit line voltages toggle the latch 24 by overpowering bias currents through pull-up resistors 40 and 42. That is, if bit line 26 is at a high potential and bit line 28 is at a low potential when the word line transitions to a high potential, transistor 38 is activated and transistor 36 is turned off. To read a memory cell, the access transistors are activated to couple the pulldown transistors 36 and 38 to bit lines 26 and 28. Sense amplifier circuitry (not shown) is provided to detect and amplify a differential voltage provided on the bit lines. It will be understood that the SRAM 10 is fabricated as an integrated circuit and that a minimum memory cell layout is desired to maximize memory density.

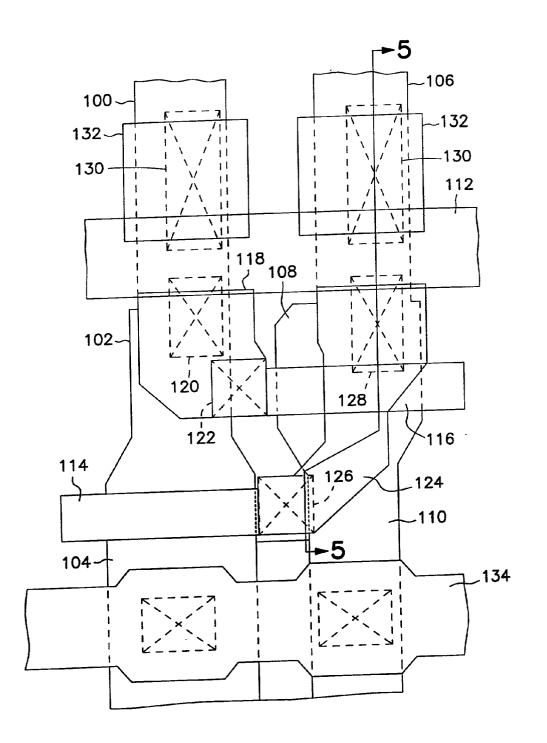

**[0022] FIG. 4** is a plan view of a single word line SRAM memory cell of the present invention fabricated such that current flows from Vss to bit line contacts entirely in active area. The gates of both pulldown transistors are fabricated essentially parallel to the common word line.

[0023] Referring to FIG. 4, a static memory cell is shown which has a first access transistor fabricated using active area regions 100 and 102 as drain and source regions, respectively. A polysilicon gate is fabricated as a common word line 112 which also forms a gate for a second access transistor. The second access transistor is defined by drain and source regions 106 and 108, respectively, formed using continuous active area. The source of each access transistor is integrally connected to a pulldown transistor. The source of the first access transistor is connected to the drain of a first pulldown transistor defined by active area **102** which acts as a drain region, active area **104** which operates as a source region, and a polysilicon gate **114**. Likewise, the source of the second access transistor is connected to the drain of a second pulldown transistor defined by active area **108** which acts as a drain region, active area **110** which operates as a source region, and a polysilicon gate **116**. The source region of each pulldown transistor is connected to a supply voltage, preferably VSS. It will be appreciated that in these described embodiments, an SRAM cell using such devices for pulldown and access devices may just as easily be constructed using p-channel devices where Vcc is substituted for Vss and the polarities of signals are reversed.

[0024] The pulldown transistor drain 102 is connected to the gate poly 116 of the second pulldown transistor through a second polysilicon layer 118 and two contacts. The second layer of polysilicon 118 is connected to the active area region 102 through a self-aligned contact 120, as known to those skilled in the art. The gate 116 is connected to second polysilicon layer 118 through a cell contact 122. The second pulldown transistor drain 108 is connected to the gate 114 of the first pulldown transistor through a second polysilicon layer 124 and a cell contact 126. Likewise, second polysilicon layer 124 is connected to active area 108 through a self-aligned contact 128. Self-aligned contacts 130 are preferably used to connect active areas 100 and 106 to second layers of polysilicon 132 which can be connected to complementary bit lines (not shown) through their use as landing pads for subsequently formed bit line contacts.

[0025] An polysilicon second layer 134 is provided to strap the VSS active area connected to the source regions of the pulldown transistors. Active areas 100, 102 and 104 are a continuous strip. Likewise, active areas 106, 108 and 110 are a continuous strip. These strips are coupled through polysilicon second layer 134. It will be appreciated by those skilled in the art that polysilicon second layer 134 can be eliminated and active area regions 100, 102, 104, 106, 108 and 110 can be formed from a single uninterrupted active area, where the continuous strips are connected at the source of the pulldowns (Vss). It is also possible to form the active area pattern in a continuous pattern as described above and still use polysilicon second layer 134 to strap the Vss active are to reduce it's resistance.

**[0026]** In this arrangement, the active area is aligned in strips to reduce two-dimensional encroachment corners which exist in the prior single word line memory cell. Cross coupling of the pulldown transistor gates to the other pulldown transistor's drain is done using cell contacts and a second level of interconnect poly. This interconnect poly does not carry any appreciable current since it is only used to charge up the pulldown gates. Therefore, variability in the internal contact's resistance does not cause cell stability failure. The use of a single word line greatly reduces the area required for the cell while still enabling a very symmetrical cell (in terms of device characteristics versus misalignment). This is due to the elimination of the internal cell contacts that carry current from VSS to the bit lines.

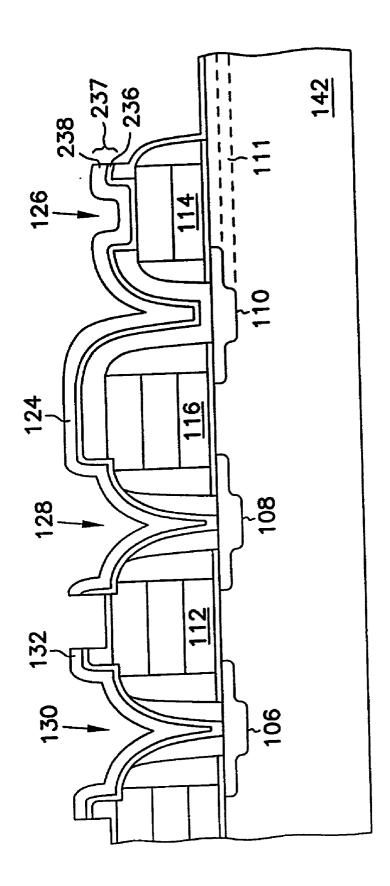

[0027] FIG. 5 is a cross section of the memory cell of FIG. 4 along line 5-5. The single active area of substrate 142 connects the source region 110/111 of the second pulldown

transistor to the self-aligned contact **130** which is coupled to the bit line poly **2** contact area **132**. Region **108** is connected to the first pulldown transistor gate **114** through contact **128**, poly layer **124** and cell contact **126**.

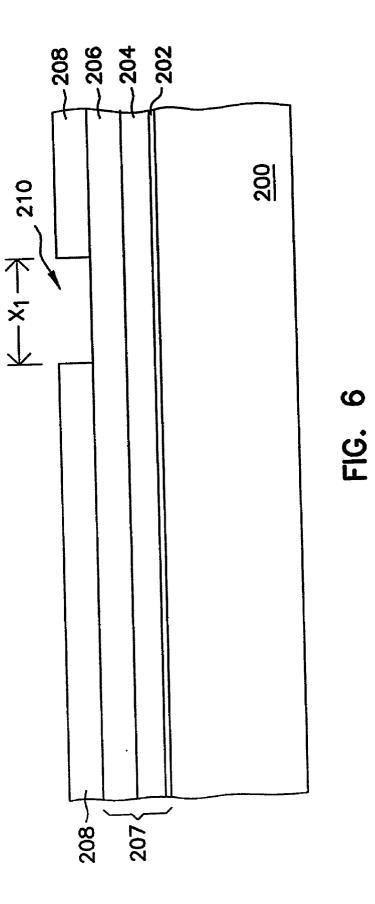

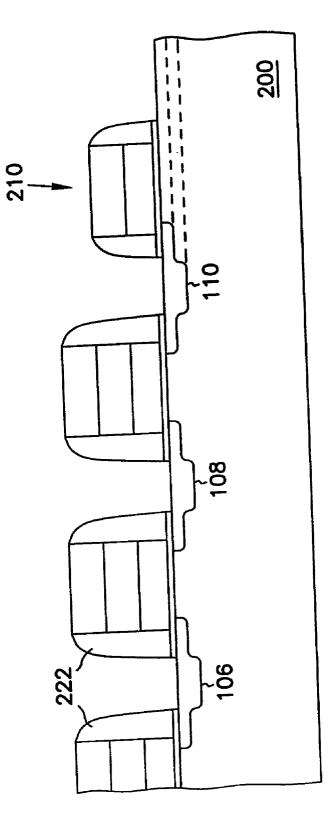

[0028] A detailed description of a preferred method of fabricating the above described SRAM cell is provided as follows with reference to FIGS. 6-10. Referring to FIG. 6, a base layer 200, or substrate, is first processed to form n-wells, p-wells, and device isolation regions by known processing means. For example, LOCOS, poly buffered LOCOS (PBL) and shallow trench isolation (STI) processes can be employed. Next, threshold adjust implants and field isolation implants are performed into desired locations. A gate oxide layer 202 is formed on the base layer 200. A first conductive layer **204** is fabricated on the layer of gate oxide. The first conductor material is preferably deposited polysilicon, referred to as the poly one layer. The polysilicon is doped, either during the deposition, or at some point after deposition. A layer of silicide 206, such as tungsten silicide, is fabricated on top of the poly one layer 204. A conductive stack layer, therefore, is formed by the poly one layer and the layer of silicide. This stacked conductor is referred to herein as the first conductor 207. It will be appreciated by those skilled in the art that the first conductor can be a single layer instead of a conductive stack.

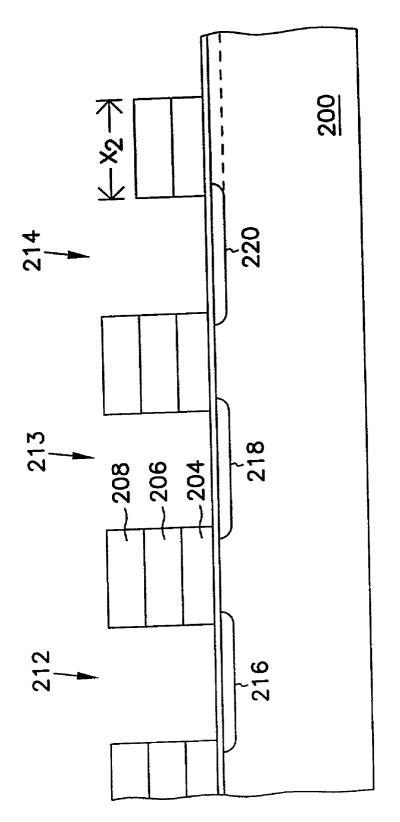

[0029] A capping layer of oxide 208 is fabricated over the first conductor. Areas of the capping layer are selectively removed using known techniques, such as a resist mask combined with a subsequent etch process, to expose portions of the first conductor in opening 210. This opening will allow later contact between the first conductor and the self aligned contact 126. After the capping layer has been selectively removed, the capping layer 208 and first conductor layer of silicide 206 and poly one 204 are removed to expose areas of oxide 202 at regions 212, 213 and 214, see FIG. 7. Again, known techniques for removing these layers can be used. In the preferred embodiment, the opening 210 in the capping layer 208 (shown as  $X_1$ ) is wider than the resultant first conductor width X<sub>2</sub>. That is, the capping oxide is patterned so that no oxide remains on the top of selected portions the first conductor after the first conductor is patterned to expose the substrate. By making the opening wide, some misalignments can be tolerated when removing the first conductor 207. It will be appreciated that in alternate embodiments  $X_1$  may be fabricated to be smaller than the resultant first conductor width X2. Thus oxide can remain on the top of selected portions the first conductor.

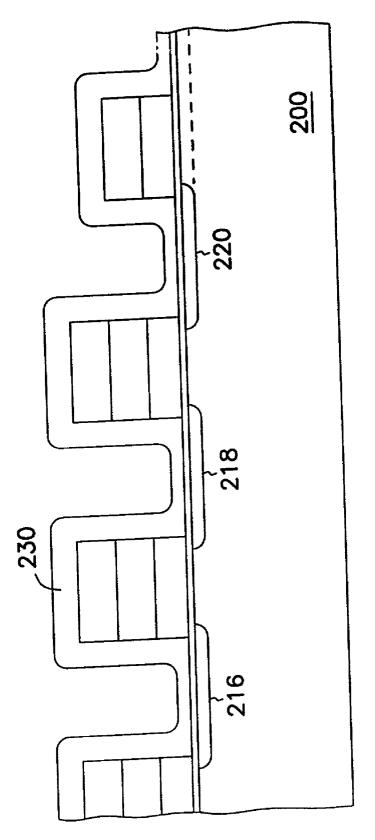

[0030] An ion implant step may be performed to form optional LDD active regions in the exposed areas of the substrate 216, 218 and 220. This implant step can be performed through the thin oxide layer 202.

[0031] A layer of oxide 230 is then deposited over the substrate 200, first conductor 207, and capping layer 208, see FIG. 8. An anisotropic step is then performed to remove the deposited oxide from the horizontal surfaces. After the etch is complete, oxide areas 222 (see FIG. 9) remain in the vertical direction on the side walls of the capping layer and first conductor. At this point in the fabrication process, the first conductor is completely enclosed by dielectrics except for the region 210 where the capping layer was removed prior to patterning the first conductor. Oxide layer 202 is also etched to expose areas of the substrate.

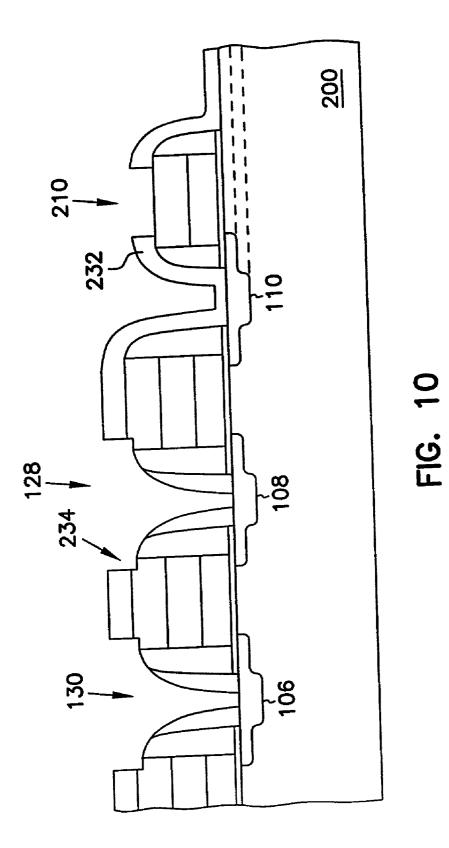

**[0032]** A second ion implant is then performed to complete transistor source and drain regions **106**, **108** and **110**. This implant is a higher concentration than the earlier implant used to form the LDD regions. It will be appreciated that either, or both, the first or second implant step can be eliminated without departing from the present invention. If both implants are eliminated, then source and drain doping in selected regions may be provided through out-diffusion of dopants from the second poly layer.

[0033] Referring to FIG. 10, a dielectric layer 232 is deposited over the circuit as an isolation barrier for a later fabricated second conductor. The dielectric is preferably TEOS, but can be any dielectric material such as nitride, or oxide. The dielectric layer is patterned and etched to expose substrate regions 106 and 108 for the formation of exhumed contacts 128 and 130. The pattern for the etch extends over the first conductor features to insure that the small regions between the first conductor are uncovered, even upon misalignment of the pattern. Because the capping oxide layer is fabricated to be thicker than the amount of over etch required to clear the oxide from the active area in regions 106 and 108, the first conductor is not exposed during this etch step, see area 234. The dielectric is also removed above the first conductor where the capping layer was removed (region 210) to expose the first conductor layer for the formation of another exhumed contact 126. The contacts to both active area and the poly one layer are therefore formed in one etch step.

[0034] The above described oxide etch step is used to create contact regions to transistor drain area 106, source area 108 and first conductor 114. The exhumed contacts to areas 106 and 108 are referred to herein as self aligned. The exhumed contact to first conductor 114 is referred to herein as a poly contact.

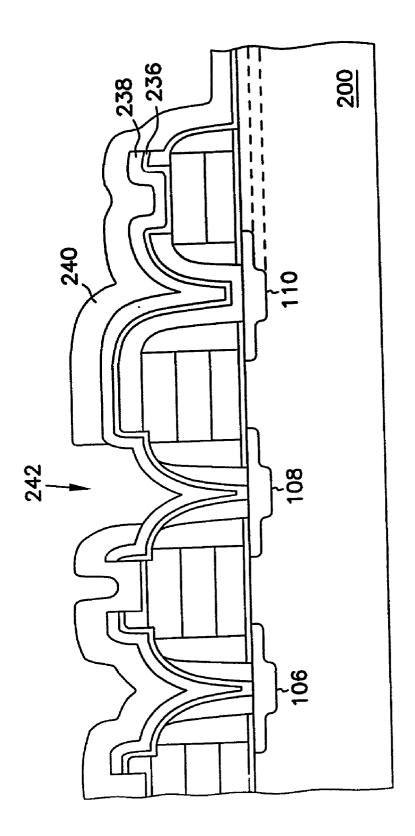

[0035] A second conductor 237 is formed such that it overlays the dielectric and makes contact to exposed active areas and the first exposed conductor 114, see

[0036] When used to form an SRAM cell, this process allows the second conductor 237 to cross couple the inputs and outputs of the SRAM cell's internal invertors since it makes contact to both the first conductor 207 and active area. As stated above, prior art typically uses Buried Contacts (BC) that connected the first conductor to active area. The BC process however is a lower yielding process than the self aligned contacts described herein. Further, BC's require full enclosure by the first conductor which requires additional area, thereby increasing the cell size.

**[0037]** The second conductor **237** may also be used to carry VSS into the cell, as well as being used as landing pads for final contacts into the cell. When used in this way, a three-poly cell is possible. Current art typically uses four levels of poly. If a BC is used, five layers of polysilicon and two poly depositions for poly one layer are required. This process then, in addition to reducing cell area, also reduces process costs.

#### Conclusion

**[0038]** An SRAM cell is described which has a reduced cell area, and a reduced processing cost from conventional SRAM's. A fabrication process is described where self-aligned contacts to substrate active area and contact to a first

conductor are formed in one etch step. Electrical connection between the substrate and polysilicon is provided through a conductive layer coupled to the contacts.

**[0039]** Although specific embodiments have been illustrated and described herein, it will be appreciated by those of ordinary skill in the art that any arrangement which is calculated to achieve the same purpose may be substituted for the specific embodiment shown. This application is intended to cover any adaptations or variations of the present invention. Therefore, it is manifestly intended that this invention be limited only by the claims and the equivalents thereof.

What is claimed is:

**1**. A static random access memory (SRAM) device comprising a self-aligned electrical contact to semiconductor active area and a second electrical contact to a non-active area electrically conductive structure defined by a process comprising a single dielectric etch step.

**2**. The SRAM of claim 1 wherein the process further comprises the steps of:

- forming a layer of dielectric material over the semiconductor active area and the non-active area electrically conductive structure prior to the single dielectric etch step; and

- forming a conductive material over the semiconductor active area and the non-active area electrically conductive structure after the single dielectric etch step to make electrical contact between the semiconductor active area and the non-active area electrically conductive structure.

- 3. The SRAM of claim 2 further comprising:

- a memory cell having first and second cross coupled pulldown transistors, a gate of the first pulldown transistor is coupled to a drain of the second pulldown transistor through the conductive material via the selfaligned electrical contact, the conductive material is coupled to the gate of the first pulldown transistor via the second electrical contact to the non-active area structure.

**4**. The SPAM of claim 1 wherein the non-active area electrically conductive structure comprises a layer of polysilicon separated from the semiconductor active area by dielectric.

5. The SRAM of claim 1 wherein the non-active area electrically conductive structure comprises a layer of polysilicon separated from the semiconductor active area by dielectric, and a layer of silicide on top of the layer of polysilicon

6. The SRAM of claim 1 wherein the semiconductor active area and the non-active area electrically conductive structure are electrically coupled through a conductor, the self aligned contact and the contact.

7. A method of fabricating electrical interconnects in a memory cell, the method comprising the steps of:

- forming first and second dielectric-conductor-dielectric layered structures, and a dielectric-conductor layered structure on a semiconductive base;

- forming vertical dielectric structures attached to exposed vertical surfaces of the first and second dielectricconductor-dielectric structures and the dielectric-conductor structure;

- forming a dielectric layer over the first and second dielectric-conductor-dielectric structures, the dielectric-conductor structure, and exposed semiconductive base between the first and second structures; and

- performing a single etch step of the dielectric layer to define a self aligned contact to the semiconductive base located between the first and second dielectric-conductor-dielectric structures, and a contact to the conductor of the dielectric-conductor structure.

**8**. The method of claim 7 wherein the step of forming the first and second dielectric-conductor-dielectric structures, and the dielectric-conductor structure comprises the steps of:

- forming a first dielectric layer over a semiconductive base;

- forming a first conductive layer over the first dielectric layer;

- forming a second dielectric layer over the first conductive layer;

- selectively removing the second dielectric layer to expose a portion of the first conductive layer; and

- patterning and removing portions of the second dielectric layer and the first conductive layer, thereby defining the first and second dielectric-conductor-dielectric structures and the dielectric-conductor structure.

9. The method of claim 8 wherein the exposed portion of the first conductive layer has a greater horizontal opening than a horizontal width of the dielectric-conductor structure.10. The method of claim 7 further comprising the step of:

forming a conductive material over the first and second dielectric-conductor-dielectric layered structures and the dielectric-conductor layered structure after the single dielectric etch step to make electrical contact with the conductor of the dielectric-conductor structure.

**11**. The method of claim 10 wherein the conductive material comprises a layer of polysilicon.

**12**. The method of claim 10 wherein the conductive material comprises a layer of silicide on top of a layer of polysilicon.

**13**. The method of claim 10 wherein the conductive material comprises a layer of metal.

**14**. A method of fabricating an interconnect in a memory cell, the method comprising the steps in the order of:

providing a semiconductive substrate;

- forming a layer of gate oxide on a top surface of the semiconductive substrate;

- forming a first polysilicon layer on top of the gate oxide layer;

- forming a layer of silicide on top of the first polysilicon layer;

- forming a capping layer of oxide on top of the layer of silicide;

- selectively etching the capping layer to expose a portion of the layer of silicide;

- performing an etch process to selectively remove vertically aligned portions of the capping layer, the layer of

silicide, and the first polysilicon layer to define first, second and third structures;

- the first and second structures comprising vertically stacked layers of gate oxide, first polysilicon, silicide, and capping oxide;

- the third structure located substantially vertically under the exposed portion of the layer of silicide, and comprising vertically stacked layers of gate oxide, first polysilicon, and silicide;

- exposing first and second areas of the semiconductive substrate, the first exposed area of the semiconductive substrate is located between the first and second structure, and the second exposed area of the semiconductive substrate is located between the second and third structure;

- forming a third layer of oxide over the first, second and third structures, and the first and second areas of the semiconductive substrate;

- etching the third layer of oxide to form vertical oxide structures attached to vertical side walls of the first, second and third structures;

etching the layer of gate oxide to expose the substrate;

- forming a fourth layer of oxide over the first, second and third structures, the exposed first and second areas of the semiconductive substrate, and the vertical oxide structures;

- etching portions of the fourth layer of oxide to form a self aligned contact region located in the first exposed area of the semiconductive substrate, and to form an exhumed contact to the silicide layer of the third structure; and

- forming a first conductive layer which makes electrical contact to the semiconductive substrate via the self aligned contact and makes electrical contact with the third structure via the exhumed contact.

- 15. The method of claim 14 further comprising the step of:

- forming doped regions in a first area of the semiconductive substrate located between the first and second structure, and a second area of the semiconductive substrate is located between the second and third structure.

**16**. The method of claim 14 wherein the first conductive layer is in-situ doped polysilicon.

**17**. The method of claim 14 further comprising the step of:

performing a second ion implant after the step of etching the layer of oxide to form vertical oxide structures.

**18**. The method of claim 14 further comprising the step of:

- forming a first dielectric layer over the first conductive layer;

- forming a third contact through the dielectric layer to expose the first conductive layer; and

- forming a second conductive layer over the first dielectric layer and the third contact to electrically couple to the first conductor.

**19**. A method of fabricating an interconnect in a static random access memory (SRAM) cell, the method comprising the steps of:

forming a first oxide layer over a semiconductive base;

forming a first conductive layer over the first oxide layer;

- forming a second oxide layer over the first conductive layer;

- selectively removing the second oxide layer to create an opening in the second oxide and expose a portion of the first conductive layer;

- patterning and removing portions of the first and second oxide layers and the first conductive layer, thereby defining first and second oxide-conductor-oxide structures, and an oxide-conductor structure, the oxideconductor structure being substantially vertically aligned with the opening in the second oxide;

- forming a third oxide layer over the first and second oxide-conductor-oxide structures, the oxide-conductor structure, and semiconductive base; and

- etching portions of the third oxide layer to define a self aligned contact to the semiconductive base located between the first and second oxide-conductor-oxide structures, and a contact to the conductor of the oxideconductor structure.

**20**. The method of claim 19 wherein the first conductive layer comprises polysilicon.

**21**. The method of claim 19 wherein the first conductive layer comprises a layer of silicide over a layer of polysilicon.

**22.** The method of claim 19 wherein the oxide-conductor structure having a horizontal cross-sectional area less than a horizontal cross-sectional area of the opening

**23**. The method of claim 19 further comprising the step of:

forming vertical oxide structures attached to exposed vertical surfaces of the first and second oxide-conductor-oxide structures and the oxide-conductor structure.

**24.** The method of claim 19 wherein the step of etching the third oxide layer is performed in a single etch step.

**25**. A method of fabricating an interconnect in a static random access memory (SRAM) cell, the method comprising the steps of:

- forming first and second structures on a substrate, the first and second structures being laterally spaced apart to define a first area of the substrate located laterally between the first and second structures;

- forming a third structure on the substrate comprising a conductor electrically insulated from the substrate, the conductor having an exposed top surface;

- forming an oxide layer over the first and second structures, the third structure, and the first area of the substrate; and

- performing a single etch step of the oxide layer to define a self aligned contact to the substrate located at first area of the substrate between the first and second structures, and a contact to the conductor of the third structure.

\* \* \* \* \*