(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3613799号 (P3613799)

(45) 発行日 平成17年1月26日(2005.1.26)

(24) 登録日 平成16年11月12日 (2004.11.12)

(51) Int.C1.7

FI

GO2F 1/133

GO2F 1/133 520

請求項の数 11 (全 20 頁)

(21) 出願番号 特願平8-503789

(86) (22) 出願日 平成7年7月12日 (1995.7.12)

(86) 国際出願番号 PCT/JP1995/001387 (87) 国際公開番号 W01996/002865

(87) 国際公開日 平成8年2月1日 (1996.2.1)

審査請求日 平成14年7月2日 (2002.7.2)

(31) 優先権主張番号 特願平6-162378

(32) 優先日 平成6年7月14日 (1994.7.14)

(33) 優先権主張国 日本国 (JP) (31) 優先権主張番号 特願平6-320906

(32) 優先日 平成6年12月22日 (1994.12.22)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人

弁理士 大渕 美千栄

(74) 代理人

弁理士 井上 一

|(74) 代理人

弁理士 布施 行夫

|(72) 発明者 伊藤 克典

長野県諏訪市大和3丁目3番5号 セイコ

ーエプソン株式会社内

審査官 柏崎 康司

最終頁に続く

#### (54) 【発明の名称】電源回路、液晶表示装置及び電子機器

# (57)【特許請求の範囲】

#### 【請求項1】

第1電圧レベルと該第1電圧レベルより低い第2電圧レベルとを含む電圧レベルを供給する第1電源と、前記第2電圧レベルより低い第3電圧レベルを含む電圧レベルを供給する第2電源とに基づき、第1駆動電圧群と第2駆動電圧群とを表示素子に対して供給する電源回路であって、

前記第1電源により動作し、前記第1駆動電圧群を供給する供給回路と、

該供給回路から供給される前記第1駆動電圧群の電圧レベルを変換して、前記第3電圧レベルを基準に設定される前記第2駆動電圧群を出力する電圧変換回路とを含み、

前記電圧変換回路が、

電圧変換用コンデンサと、

該電圧変換用コンデンサに接続され、該電圧変換用コンデンサを前記第 1 駆動電圧群により充電するためのオン・オフ動作を行う第 1 スイッチ群と、

前記電圧変換用コンデンサに接続され、該電圧変換用コンデンサを放電し前記第2駆動電圧群を出力するためのオン・オフ動作を行う第2スイッチ群とを含むことを特徴とする電源回路。

# 【請求項2】

第1電圧レベルと該第1電圧レベルより低い第2電圧レベルとを含む電圧レベルを供給する第1電源と、前記第2電圧レベルより低い第3電圧レベルを含む電圧レベルを供給する第2電源とに基づき、第1駆動電圧群と第2駆動電圧群とを表示素子に対して供給する電

源回路であって、

前記第1電源により動作し、前記第1駆動電圧群を供給する第1供給回路と、

前記第1電源の電圧レベルを変換して、前記第3電圧レベルを基準に設定される第3電源 の電圧レベルを出力する電圧変換回路と、

前記第3電源により動作し、前記第2駆動電圧群を供給する第2供給回路とを含み、

前記電圧変換回路が、

電圧変換用コンデンサと、

該電圧変換用コンデンサに接続され、該電圧変換用コンデンサを前記第1電源により充電 するためのオン・オフ動作を行う第1スイッチ群と、

前記電圧変換用コンデンサに接続され、該電圧変換用コンデンサを放電し前記第3電源の 電圧レベルを出力するためのオン・オフ動作を行う第2スイッチ群とを含むことを特徴と する電源回路。

# 【請求項3】

請求項2において、

前記第1電源の前記第1、第2電圧レベルを用いて、前記第1駆動電圧群を供給するため の1又は複数の第1分割電圧レベルを出力する回路と、

前記第2電源の電圧レベルと前記第2電源の前記第3電圧レベルとを用いて、前記第2駆 動電圧群を供給するための1又は複数の第2分割電圧レベルを出力する回路とを含むこと を特徴とする電源回路。

# 【請求項4】

請求項2又は3において、

前記第3電源を監視し、前記第1、第2スイッチ群の少なくとも一方の動作を停止する回 路を含むことを特徴とする電源回路。

#### 【請求項5】

請求項2乃至4のいずれかにおいて、

前記第3電源を監視し、前記第1、第2電源の少なくとも一方から前記第3電源に電流を 供給する回路を含むことを特徴とする電源回路。

# 【請求項6】

請求項1乃至3のいずれかにおいて、

前記電圧変換用コンデンサ、前記第1、第2スイッチ群を複数組設け、複数組の第1スイ 30 ッチ群を交互にオン・オフすると共に、複数組の第2スイッチ群を交互にオン・オフし、 複数組の電圧変換用コンデンサを交互に充放電することを特徴とする電源回路。

#### 【請求項7】

請求項1乃至3のいずれかにおいて、

前記第1電源に含まれる電圧レベル間の電圧が低下した場合に、該第1電源に含まれる電 圧レベルと前記第3電圧レベルとの間のインピーダンスを低下させる回路を含むことを特 徴とする電源回路。

## 【請求項8】

請求項1乃至7のいずれかの電源回路と、液晶素子がマトリクス状に配置される液晶パネ ルと、該液晶パネルを駆動するための駆動回路とを含む液晶表示装置であって、

前記駆動回路が、前記電源回路から供給される前記第1、第2駆動電圧群に基づき前記液 晶パネルの駆動を行うことを特徴とする液晶表示装置。

# 【請求項9】

請求項8において、

前記第1電源が、前記駆動回路の電源となるロジック駆動用電源であることを特徴とする 液晶表示装置。

#### 【請求項10】

請求項1乃至7のいずれかの電源回路を含むことを特徴とする電子機器。

#### 【請求項11】

請求項8乃至9のいずれかの液晶表示装置を含むことを特徴とする電子機器。

20

40

#### 【発明の詳細な説明】

# 「技術分野 ]

本発明は電源回路、該電源回路を含む液晶表示装置、該電源回路又は該液晶表示装置を含む電子機器に関する。

# 「背景技術 ]

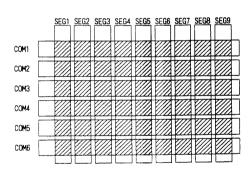

図18は時分割駆動される液晶パネルの電極の模式図である。簡単化のためセグメント電極が9本、コモン電極が6本からなる液晶パネルを示す。各長方形が液晶パネル内に形成された電極を表しており、これらの電極は、加えられる信号によってセグメント電極(SEG1~SEG9)とコモン電極(COM1~COM6)とに分けられる。各電極が交差する正方形の部分は表示ドットを表す。各表示ドットはコンデンサとして働くため、セグメント電極とコモン電極は対応する表示ドットにおいてコンデンサで結合している。

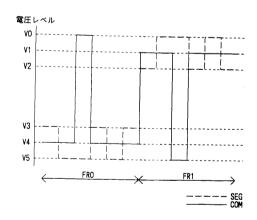

液晶の高デューティ時分割駆動(6 レベル駆動法)に必要な電圧レベルV0~V5は、一般に図19に示す通り、V0・V1 = V1・V2 = V3・V4 = V4・V5並びにV0 > V1 > V2 > V3 > V4 > V5の関係を持つ。ここでV0~V2を第1駆動電圧群、V3~V5を第2駆動電圧群と呼ぶことにする。第1駆動電圧群V0~V2の電圧範囲は、第2駆動電圧群V3~V5の電圧範囲とノンオーバラップであり且つ離れたものとなる。

図19は、セグメント電極、コモン電極に加えられる信号波形の例である。セグメント電極に加えられる信号は一般に、フレーム 0 (以下FR0と呼ぶ)の期間では電圧レベルV3とV5との間で切り替わる。またフレーム 1 (以下FR1と呼ぶ)の期間では電圧レベルV0とV2との間で切り替わる。このセグメント電極における電圧レベルの切り替えは、表示するパターンに依存する。一方、コモン電極に加えられる信号は、FR0期間では、非選択状態の時に電圧レベルV4となり、選択状態の時に電圧レベルV0となる。またFR1期間では、非選択状態の時に電圧レベルV1となり、選択状態の時に電圧レベルV5となる。コモン電極が選択状態になる期間は全てのコモン電極で異なっており、複数のコモン電極が同時に選択状態になる事はない。FR0期間とFR1期間では、液晶を交流駆動するために電圧レベルが反転する。

セグメント、コモン電極での電圧レベルの切り替わりは、液晶パネルに存在する容量の充放電を伴う。この結果、液晶パネルを通してV0~V5の各電圧レベル間に電流が流れる。以下、このような電流をパネル電流と呼ぶ。セグメント電極の電圧レベルは、V0とV2の間(FR1期間)あるいはV3とV5の間(FR0期間)で切り替わる。またコモン電極は、大部分の期間で非選択状態となっており、その電圧レベルは大部分の期間でV1(FR1期間)あるいはV4(FR0期間)となっている。したがって、セグメント電極の電圧レベルの切り替わりに伴うパネル電流(以下、セグメント・パネル電流と呼ぶ)は、主に、第1駆動電圧群V0、V1、V2の相互間、あるいは第2駆動電圧群V3、V4、V5の相互間で流れる。一方、コモン電極の電圧レベルの切り替わりに伴うパネル電流(コモン・パネル電流と表す)は、主にV5と第1駆動電圧群V0、V1、V2との間、あるいはV0と第2駆動電圧群V3、V4、V5との間で流れる。

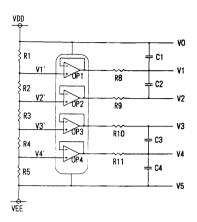

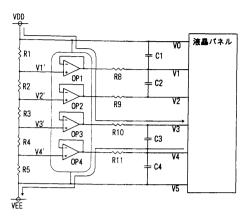

このようなパネル電流を供給する電源回路として、特開平 2 - 150819号に開示された従来技術がある。図20にその構成を示す。図20において、VDD > VEEの関係を有する外部電源VDD、VEEは、電源回路を動作させる電源である。VDD、VEE間に抵抗R1~R5を直列に接続することで、分割電圧レベルV1′~V4′が生成される。これらの分割電圧レベルは、ボルテージ・フォロア接続された演算増幅器OP1~OP4に入力される。OP1~OP4は、VDD、VEEを電源としており、V1′~V4′の出力インピーダンスを低くする変換を行う。コンデンサC1~C4は、OP1~OP4の出力電圧レベルV1~V4の変動をおさえる平滑コンデンサである。抵抗R8~R11は演算増幅器OP1~OP4の出力電流を制限し、演算増幅器OP1~OP4の消費電力を減らす働きをする。

しかしながら、この従来技術には以下のような問題点があった。

第1に、この従来技術には、パネル電流供給の際に無駄に消費している電力が大きいという問題がある。その理由は以下の通りである。この電源回路を用いて液晶パネルを駆動したときに、パネル電流は、VDDからVEEへ流れる電流の一部分として供給される。例えば電

10

20

30

40

30

40

50

圧レベルV3からV4へ流れるセグメント・パネル電流を考えると、このセグメント・パネル 電流は図21に示す様に、最初に電源VDDから流れ出し、演算増幅器OP3を通して液晶パネル に流れ込む。そして液晶パネルから演算増幅器0P4を通り、最終的に電源VEEに流れ込む。 このように電圧レベルV3からV4へとセグメント・パネル電流を供給した場合、VDDからV3 まで流れる電流は演算増幅器OP3の発熱を引き起こす。またV4からVEEまで流れる電流は演 算増幅器0P4の発熱を引き起こす。即ち、これらの電流は、液晶パネルの駆動に対して有 効な働きをしていない。同様の事は他のすべてのパネル電流に対してあてはまる。つまり 図20の電源回路を用いてセグメント・パネル電流、コモン・パネル電流を供給する場合、 演算増幅器を発熱させる無駄な電力を消費している。ここでコモン・パネル電流は主に、 V5と第1駆動電圧群V0、V1、V2との間、あるいはV0と第2駆動電圧群V3、V4、V5の間で流 れる。従って電流の流れる電圧レベル間の電圧は大きく、この電圧と、電源VDD、VEE間の 電圧との差は小さい。これに対して、セグメント・パネル電流は主に第 1 駆動電圧群V0、 V1、V2の相互間、あるいは第2駆動電圧群V3、V4、V5の相互間で流れる。従って電流の流 れる電圧レベル間の電圧は小さく、この電圧と、VDD、VEE間の電圧との差は大きい。この ためセグメント・パネル電流を供給する場合の方が、コモン・パネル電流の場合よりも、 演算増幅器等で消費される無駄な電力の割合が大きいことがわかる。即ち、このような消 費電力の無駄を防止するためには、セグメント・パネル電流の供給手法に対策を施す必要 がある。

第2に、この従来技術には、演算増幅器のアイドリング電流に起因する消費電力が大きいという問題がある。即ち、図20に示すように、この従来技術では、演算増幅器OP1~OP4は電源VDD、VEEにより動作する。しかしながらこの電源VDD、VEEは、液晶パネルの駆動電圧を生成するための電源でもあるため、VDD、VEE間の電圧は非常に大きい。消費電力は、電流を一定とした場合には電圧に比例する。従って、VDD、VEE間の電圧は大きくなれば、演算増幅器OP1~OP4のアイドリング電流に起因して無駄に消費される電力も大きくなる。第3に、この従来技術では、上記のように電圧差の大きいVDD、VEEを電源としているため、価格が高い高耐圧の演算増幅器を用いなければならないという問題もある。

一般に、液晶表示装置の高デューティ化を図る場合、電源VDD、VEE間の電圧を更に大きくする必要がある。従って、この場合には、上記第1~第3の問題は、更に深刻なものとなる。

なお特開平3-200214号公報には、スイッチドキャパシタ回路を用いて電圧レベルV1からV5、V2からV4を生成し、これらを液晶パネルに供給する電源回路の従来技術が開示されている。しかしながら、この従来技術は、演算増幅器の個数あるいは電源回路と液晶パネルとの間の結線を減らし、装置の小型化を図ることをその目的としており、本発明のように低消費電力化を目的とするものではない。

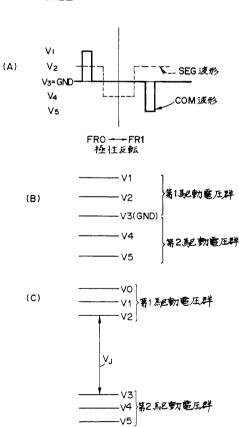

またこの従来技術では5レベル出力となっており、極性反転の前後で、即ち図22(A)に示すFRO期間とFR1期間で、コモン電極の非選択時の電圧が同一(V3 = GND)となっている。この電源構成で液晶駆動の高デューティ化を図るためには、図22(B)のV1、V3間の電圧及びV3、V5間の電圧を大きくする必要がある。このため高耐圧の液晶駆動用ドライバICが必要になるという問題が生じる。従って図22(B)の電源構成は、低デューティで液晶を駆動する場合に用いられるのが一般的である。一方、図22(C)に示す電源構成の手法は、高デューティで液晶を駆動する場合に図22(B)の電源構成で生じる問題を解決するために考案されたものであり、現在、高デューティの液晶駆動に一般的に用いられている手法である。本発明は、この図22(C)に示す電源構成を対象とするものであり、図22(B)の電源構成を対象とする上記従来技術とはその目的、構成が全く異なる。

本発明は以上述べた技術的課題を解決するためになされたものであり、その目的とするところは、消費電力が小さく安価な電源回路、液晶表示装置及び電子機器を提供することにある。

# 「発明の開示]

上記目的を達成するために、本発明は、第1、第2電圧レベルを含む電圧レベルを供給する第1電源と、前記第1、第2電圧レベルとは異なる第3電圧レベルを含む電圧レベルを

供給する第2電源とに基づき、第1駆動電圧群と、該第1駆動電圧群の電圧範囲とノンオーバラップであり且つ離れた電圧範囲を有する第2駆動電圧群とを表示素子に対して供給する電源回路であって、

前記第1電源により動作し、前記第1駆動電圧群を供給する供給回路と、

該供給回路から供給される前記第1駆動電圧群の電圧レベルを変換して、前記第3電圧レベルを基準に設定される前記第2駆動電圧群を出力する電圧変換回路とを含み、

前記電圧変換回路が、

電圧変換用コンデンサと、

該電圧変換用コンデンサに接続され、該電圧変換用コンデンサを前記第 1 駆動電圧群により充電するためのオン・オフ動作を行う第 1 スイッチ群と、

前記電圧変換用コンデンサに接続され、該電圧変換用コンデンサを放電し前記第2駆動電圧群を出力するためのオン・オフ動作を行う第2スイッチ群とを含むことを特徴とする。本発明によれば、第2駆動電圧群は、第1駆動電圧群の電圧レベルを変換することで得られる。そしてこの第1駆動電圧群は、第1電源で動作するインピーダンス変換回路等の供給回路により供給される。従って、ノンオーバラップで離れた電圧範囲を有する第1、第2駆動電圧群を、共に第1電源から電源供給できることになる。この結果、例えば第1、第2駆動電圧群の電圧範囲が更に離れた場合においても、第1電源から供給される必要最低限の電力で表示素子を駆動できることになる。更に供給回路は第1電源により動作するため、供給回路での無駄な電力の消費を抑えることができる。また供給回路を高耐圧化する必要が無くなるため、低耐圧の製造プロセスを採用することも可能となる。

さて本発明では、第1スイッチ群をオンすると共に第2スイッチ群をオフすることで、供給回路を介して第1電源により電圧変換用コンデンサを充電する。また第1スイッチ群をオフすると共に第2スイッチ群をオンすることで、この電圧変換用コンデンサを放電する。そして電圧変換回路からは、第3電圧レベルと電圧変換用コンデンサの充電電圧により電圧レベルが決められる第2駆動電圧群が出力される。これにより、第2駆動電圧群で消費される電力を第1電源により供給できることになる。

なお第1駆動電圧群の全てを供給回路により供給する必要はなく、第1電源の電圧レベルを直接に第1駆動電圧群として用いてもよい。また供給回路は、抵抗等の素子を介して第1駆動電圧群を供給してもよい。更に電圧変換回路で変換される第1駆動電圧群の電圧レベルは複数であってもよい。

また本発明は、第1、第2電圧レベルを含む電圧レベルを供給する第1電源と、前記第1、第2電圧レベルとは異なる第3電圧レベルを含む電圧レベルを供給する第2電源とに基づき、第1駆動電圧群と、該第1駆動電圧群の電圧範囲とノンオーバラップであり且つ離れた電圧範囲を有する第2駆動電圧群とを表示素子に対して供給する電源回路であって、前記第1電源により動作し、前記第1駆動電圧群を供給する第1供給回路と、

前記第1電源の電圧レベルを変換して、前記第3電圧レベルを基準に設定される第3電源の電圧レベルを出力する電圧変換回路と、

前記第3電源により動作し、前記第2駆動電圧群を供給する第2供給回路とを含み、前記電圧変換回路が、

電圧変換用コンデンサと、

該電圧変換用コンデンサに接続され、該電圧変換用コンデンサを前記第1電源により充電 するためのオン・オフ動作を行う第1スイッチ群と、

前記電圧変換用コンデンサに接続され、該電圧変換用コンデンサを放電し前記第3電源の電圧レベルを出力するためのオン・オフ動作を行う第2スイッチ群とを含むことを特徴と する

本発明によれば、第3電源の電圧レベルは、電圧変換回路を介して第1電源により供給される。そして、インピーダンス変換回路等の第2供給回路は、この第3電源により動作し、第2駆動電圧群を供給する。従って、結局、第1、第2駆動電圧群を共に第1電源により供給できることになる。しかも、第1、第2供給回路は第1電源により動作するため、第1、第2供給回路の消費電力を低減できると共に、第1、第2供給回路として低耐圧の

10

20

30

ものを用いることが可能となる。

また本発明は、前記第1電源の前記第1、第2電圧レベルを用いて、前記第1駆動電圧群を供給するための1又は複数の第1分割電圧レベルを出力する回路と、

前記第3電源の電圧レベルと前記第2電源の前記第3電圧レベルとを用いて、前記第2駆動電圧群を供給するための1又は複数の第2分割電圧レベルを出力する回路とを含むことを特徴とする。

本発明によれば、第1分割電圧レベルは、第1電源の第1、第2電圧レベルにより、第2分割電圧レベルは、第3電源の電圧レベルと第2電源の第3電圧レベルとから生成される。これにより、第1電源の電圧レベルと第2電源の電圧レベルとの間を分割して電圧を生成する必要が無くなる。この結果、第1電源と第2電源との間で流れる電流を低減でき、更なる低消費電力化を図れる。

また本発明は、前記第3電源を監視し、前記第1、第2スイッチ群の少なくとも一方の動作を停止する回路を含むことを特徴とする。

本発明によれば、電圧変換用コンデンサに充放電され電流が小さい時に第1、第2スイッチ群の動作を停止させることで、第1、第2スイッチ群の動作によって消費される電力等を低減できる。

また本発明は、前記第3電源を監視し、前記第1、第2電源の少なくとも一方から前記第3電源に電流を供給する回路を含むことを特徴とする。

本発明によれば、供給回路で消費する電力が増大し、電圧変換用コンデンサによる電力供給が追いつかなくなった時に、電力の一部を第1、第2電源から供給できる。これにより供給回路の電力供給能力を向上させることができる。

また本発明は、前記電圧変換用コンデンサ、前記第1、第2スイッチ群を複数組設け、複数組の第1スイッチ群を交互にオン・オフすると共に、複数組の第2スイッチ群を交互にオン・オフし、複数組の電圧変換用コンデンサを交互に充放電することを特徴とする。

本発明によれば、複数組の第2スイッチ群の中の1の第2スイッチ群がオフしている場合にも、この時にオンしている他の第2スイッチ群を介して電流を供給できる。これにより電圧変換回路から取り出し得る電流を増加させることが可能となる。

また本発明は、前記第1電源に含まれる電圧レベル間の電圧が低下した場合に、該第1電源に含まれる電圧レベルと前記第3電源に含まれる電圧レベルとの間のインピーダンスを低下させる回路を含むことを特徴とする。

本発明によれば、電源回路を動作させる電源が遮断された場合等に、第 1 、第 3 電源間のインピーダンスを低下でき、電源回路の出力を速やかに落とすことが可能となる。これにより表示素子の保護等が可能となる。

また本発明は、上記電源回路と、液晶素子がマトリクス状に配置される液晶パネルと、該液晶パネルを駆動するための駆動回路とを含む液晶表示装置であって、

前記駆動回路が、前記電源回路から供給される前記第1、第2駆動電圧群に基づき前記液晶パネルの駆動を行うことを特徴とする。

本発明によれば、液晶パネルの駆動により、第1駆動電圧群の相互間又は第2駆動電圧群の相互間で電流が流れる場合等において、これらの電流を、少ない電圧差の電圧レベルを出力する第1電源により供給できる。これにより液晶表示装置の高デューティ化等に伴い第1駆動電圧群と第2駆動電圧群との間が離れた場合において、無駄な電力の消費を最低限に抑えることができ、低消費電力の液晶表示装置を実現できる。

また本発明は、前記第1電源が、前記駆動回路の電源となるロジック駆動用電源であることを特徴とする。

本発明によれば、ロジック駆動用電源を用いて液晶駆動用の電圧群を生成できる。これにより液晶表示装置に外部から供給する電源の種類を少なくでき、液晶表示装置の利便性を高めることができる。

また本発明の電子機器は、上記電源回路又は上記液晶表示装置を含むことを特徴とする。 本発明によれば電子機器全体の低消費電力化を図れる。また第1電源として、電子機器の 動作に使用する電源を用いれば、電子機器の電源回路構成の簡易化を図れる。 10

20

30

40

#### 【図面の簡単な説明】

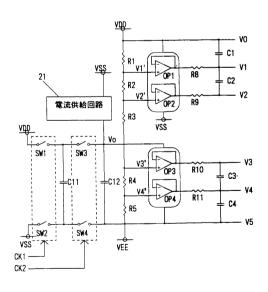

- 図1は、実施例1の電源回路の構成例を示す図である。

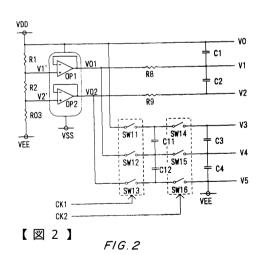

- 図2は、CK1、CK2の信号波形図である。

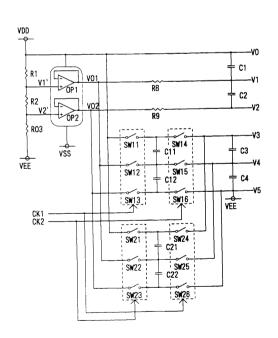

- 図3は、実施例2の電源回路の構成例を示す図である。

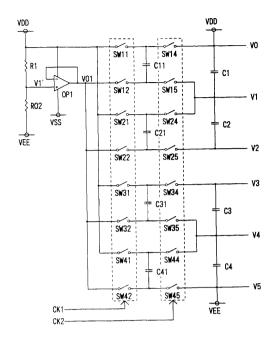

- 図4は、実施例3の電源回路の構成例を示す図である。

- 図5は、実施例4の電源回路の構成例を示す図である。

- 図6は、インピーダンス低下回路の構成例を示す図である。

- 図7は、実施例5の電源回路の構成例を示す図である。

- 図8は、実施例6の電源回路の構成例を示す図である。

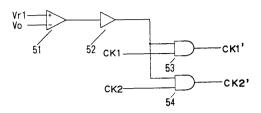

- 図9は、スイッチ信号発生回路の構成例を示す図である。

- 図10は、実施例7の電源回路の構成例を示す図である。

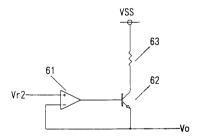

- 図11は、電源供給回路の構成例を示す図である。

- 図12は、実施例8の電源回路の構成例を示す図である。

- 図13は、電圧変換回路の他の例を示す図である。

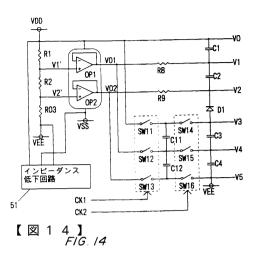

- 図14は、パルス制御回路の構成例を示す図である。

- 図15は、パルス制御回路の他の例を示す図である。

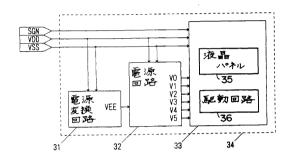

- 図16は、実施例9の液晶表示装置の構成例を示す図である。

- 図17は、実施例10のパーソナル・コンピュータの構成例を示す図である。

- 図18は、時分割駆動する液晶パネルの電極の模式図である。

- 図19は、セグメント、コモン電極に加える信号を説明するための図である。

- 図20は、従来の電源回路を示す図である。

- 図21は、従来の電源回路における電流の流れを説明するための図である。

- 図22(A)、(B)、(C)は、本発明と従来技術との相違を説明するための図である。 [発明を実施するための最良の形態]

- 以下、本発明の好適な実施例について図面を用いて説明する。

# 〔実施例1〕

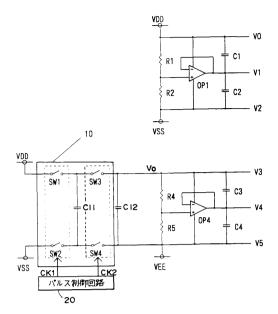

図 1 に、時分割駆動の液晶表示装置に対して本発明を適用した実施例 1 の電源回路の構成例を示す。図 1 において VDD、 VSS、 VEEは VDD > VSS > VEEなる関係を持つ外部電源である。 VDD、 VSS は第 1 電源の電圧レベルに、 VEEは第 2 電源の電圧レベルに相当する。もちろん第 1、第 2 電源にこれ以外の電圧レベルを含ませても構わない。図 1 に示すように、 VDD 及び VEEの間には抵抗 R1、 R2、 R03が直列に接続され、分割電圧レベル V1'、 V2'が発生する。 なお図 1 では、 VDD及び VEEの間を抵抗分割したが、 VDD及び VSS の間を抵抗分割してもよい。

これらの各分割電圧レベルは、VDD及びVSSを電源とする演算増幅器(インピーダンス変換回路)0P1、0P2に入力される。そして低インピーダンス化されたV01、V02が0P1、0P2から出力される。V01、V02は、演算増幅器の出力電流を制限する抵抗R8、R9を介して第 1 駆動電圧群V1、V2となる。また第 1 電源であるVDDが、第 1 駆動電圧群の 1 つであるV0となる。但し必ずしも第 1 電源の電圧レベルをそのまま第 1 駆動電圧群V0 ~ V2の 1 つとして使用する必要はない。同様に第 2 電源の電圧レベル、例えばVEEを、そのまま第 2 駆動電圧群V3 ~ V5 の 1 つとして使用する必要もない。

本実施例では、演算増幅器 OP1、OP2等が供給回路に相当する。そして演算増幅器 OP1、OP2 は第 1 電源 VDD、VSSにより動作するため、第 1 駆動電圧群 VO ~ V2は、第 1 電源から電源供 給されることになる。

C11、C12は電圧変換用コンデンサに相当する。このように本発明の電圧変換用コンデンサは複数であってもよい。SW11~SW13は第1スイッチ群に相当し、SW14~SW16は第2スイッチ群に相当する。そして電圧変換回路はC11、C12及びSW11~SW13、SW14~SW16を含むものである。SW11~SW13は信号CK1によって制御され、SW14~SW16は信号CK2によって制御される。ここでSW11~SW16は信号がハイレベル(以下Hと表す)でオンし、ローレベル(以下Lで表す)でオフする。

なお実施例1では第1、第2のスイッチ群のオン・オフは電気的に制御されているが、必

10

20

30

40

30

40

50

要であればリレー等の機械機構を用いるなど他の方法で制御してもよい。また図 1 のC1 ~ C4はV1 ~ V4の電圧変動を抑える平滑コンデンサである。

図 2 にCK1、CK2の信号波形の例を示す。CK1、CK2は、SW11~SW13とSW14~SW16とが同時にオンしないように、ノンオーバラップ信号となっている。即ち、CK1がLであるときCK2はHであり、CK2がLであるときCK1がHとなる。またCK1が立ち下がってから一定時間経過した後にCK2が立ち上がり、CK2が立ち下がってから一定時間経過した後にCK1が立ち上がる。

CK1が日でありCK2がLである期間ではSW11~SW13がオンし、SW14~SW16がオフする。これによりコンデンサC11、C12はVDD、V01、V02により充電され、それぞれのコンデンサの端子間にVDD、V01間、V01、V02間の電圧が保持される。CK1がLでありCK2が日である期間ではSW11~SW13がオフし、SW14~SW16がオンする。これによりコンデンサC12の下側の端子がVEEに接続され、コンデンサC11、C12の上側の端子が、各々、V3、V4を出力する。CK1が日でありCK2がLである期間は、SW14~SW16がオフし、C11、C12によってはV3、V4は出力されない。しかしながらC3、C4によりV3、V4は電圧が保持されている。図2においてCK1、CK2の立ち上り及び立ち下がり部分では、図1における異なる電圧レベル間の短絡を防ぐため、CK1、CK2が同時に日にならないようになっている。以上の動作が継続的に繰り返されることにより、V3、V4から流れる電流を継続的にVDD、V01、V02から供給できる。これによりV3、V4を液晶を駆動する電源として用いることが可能となる。

SW11~SW13、C11、C12及びSW14~SW16等から成る回路が、本発明の電圧変換回路に相当する。この電圧変換回路は、OP1、OP2等から供給される第1駆動電圧群V0、V01(V1と同等)、V02(V2と同等)の電圧レベルを変換して、VEE(第3電圧レベル)を基準に設定される第2駆動電圧群V3、V4、V5を出力する。

なお図1では、OP1の出力端子をSW12に、OP2の出力端子をSW13に接続しているが、これに代えて、R8の出力端子をSW12に、R9の出力端子をSW13に接続してもよい。

演算増幅器のアイドリング電流及びセグメント電極の電圧レベルの切り替わりに起因する電流は、図20の従来の電源回路ではVDD、VEEで供給されていた。一方、図1の電源回路ではてれるの電流はすべてVDD、VSSで供給される。従って図1の回路を用いた場合、これらの電流に起因する消費電力は従来の(VDD - VSS)/(VDD - VEE)倍となる。また、図1の演算増幅器の耐圧はVDD - VSS以上であれば良い。これは図20の演算増幅器の耐圧として必要なVDD - VEEと比較して小さな値である。つまり図1の回路では演算増幅器に高価な高耐圧のものを用いる必要はない。さらに演算増幅器の数も、図20の回路では4個使用しているのに対し、図1の回路では2個ですむという利点がある。

具体的には、 $320 \times 480$ ドット表示(1/320デューティ)の液晶表示装置では、VDD - VEEは25V程度であり、V0 - V2 = V3 - V5は3.5V程度である。図 1 の電源回路を用い、VDD、VSSとして液晶表示装置のロジック駆動用電源(5V)を用いる。すると演算増幅器のアイドリング電流及びセグメント電極の電圧レベルの切り替わりに起因する電流によって消費される電力を、従来の1/5程度に減少させることができる。また演算増幅器の耐圧も従来の1/5程度ですむ。従って図 1 の電源回路によれば、前述の従来技術の問題点を大幅に改善できる。〔実施例 2 〕

図3に、実施例2の電源回路の構成例を示す。実施例1との相違は、電圧変換用コンデンサ、第1、第2スイッチ群を複数組、例えば2組設けている点である。実施例1と同様に、VDD、VSSは第1電源の電圧レベルに、VEEは第2電源の電圧レベルに相当する。またV0~V2は第1駆動電圧群に相当し、V3~V5は第2駆動電圧群に相当する。実施例1と同様に第1電源VDDがV0としても用いられ、第2電源VEEがV5としても用いられている。

実施例 1 で 1 組であった電圧変換用コンデンサC11は、実施例 2 ではC11、C21の 2 組となる。同様に、実施例 1 で 1 組であったC12は、実施例 2 ではC12、C22の 2 組となる。同様に実施例 2 では、第 1 スイッチ群としてSW11~SW13及びSW21~SW23が設けられ、電圧変換用コンデンサに対応して第 1 スイッチ群が 2 組設けられている。また第 2 スイッチ群としてSW14~SW16及びSW24~SW26が設けられ、第 2 スイッチ群も 2 組設けられている。このように本発明の電圧変換用コンデンサ及び第 1、第 2 スイッチ群は複数組であってもよい。

30

40

50

SW11~SW13とSW24~SW26は信号CK1によって制御され、SW14~SW16とSW21~SW23は信号CK2によって制御される。SW11~SW16、SW21~SW26は制御する信号(CK1又はCK2)がHでオフし、Lでオンする。C1~C4はV1~V4の変動を抑える平滑コンデンサである。

実施例 2 においても、信号CK1、CK2として、図 2 に示す波形の信号が印加される。信号CK 1が H でありCK2が L である期間では、コンデンサC11、C12がVDD、V01、V02により充電される。そしてコンデンサC21、C22の上側の端子(VEEに接続されていない端子)からV3、V 4が出力される。CK1が L でありCK2が H である期間では、コンデンサC21、C22がVDD、V01、V02により充電される。そしてコンデンサC11、C12の上側の端子からV3、V4が出力される。

実施例 1 では、CK1が H でありCK2が L である期間ではSW14 ~ SW16がオフしているため、C1 1、C12からはV3、V4の電圧レベルは出力されなかった。即ち上記期間では、C3、C4に保持された電圧が出力される。これに対し実施例 2 では、CK1が H でありCK2が L である期間ではSW24 ~ SW26がオンしているため、C21、C22からV3、V4が出力される。このように実施例 2 では、V3、V4から流れる電流をVDD、V01、V02から供給する回数が、実施例 1 の 2 倍になっている。このため、実施例 1 と比較してV3、V4からより多くの電流を取り出すことができる。このように実施例 2 は、実施例 1 の利点に加え、取り出し得る電流が大きいという利点を持つ。

# 〔実施例3〕

図4に、実施例3の電源回路の構成例を示す。図4においてVDD、VSS、VEEは実施例1、 2 と同様に外部電源から供給される。実施例 3 では、VDD、VEE間に抵抗R01、R02を直列に 接続し、分割電圧レベルV1'を発生させる。そしてこのV1'を、電源VDD、VSSで動作する演 算増幅器OP1で低インピーダンス化することで、V01が生成される。実施例3では、SW11、 SW12、SW21、SW22、C11、C12、SW14、SW15、SW24、SW25から成る電圧変換回路が設けられ 、この電圧変換回路がVDD、V01の電圧レベルを変換し、第1駆動電圧群V0~V2を出力する 。この時、演算増幅器OP1は第1電源VDD、VSSにより動作するため、第1駆動電圧群V0~V 2は第1電源 VDD、 VSSから供給されることになる。また実施例3では、SW31、SW32、SW41 、SW42、C31、C41、SW34、SW35、SW44、SW45から成る電圧変換回路が設けられ、この電圧 変換回路がVDD、V01の電圧レベルを変換し、VEEを基準に設定された第2駆動電圧群V3∼V 5を出力する。この時、演算増幅器OP1は第1電源VDD、VSSにより動作するため、第2駆動 電圧群V3~V5も第1電源VDD、VSSから供給されることになる。図4に示すように、SW11、 SW12、SW21、SW22、SW31、SW32、SW41、SW42は信号CK1によって制御され、SW14、SW15、S W24、SW25、SW34、SW35、SW44、SW45は信号CK2によって制御される。これらのスイッチ制 御の方法は実施例1、2と同様である。またC1~C4はV1~V4の変動を抑える平滑コンデン サである。

実施例3においても、信号CK1、CK2として、図2に示す波形の信号が印加される。信号CK 1が H であり CK2が L である期間では、コンデンサC11、C21、C31、C41はVDD、V01より充電 される。CK1が L でありCK2が H である期間では、コンデンサC11の一方の端子が電源VDDに 接続され他方の端子がV1を出力し、コンデンサC21の一方の端子がV1に接続され他方の端 子がV2を出力する。またコンデンサC41の一方の端子が電源VEEに接続され他方の端子がV4 を出力し、コンデンサC31の一方の端子が電源V4に接続され他方の端子がV3を出力する。 実施例1、2では、図1、図3の演算増幅器0P1、0P2はV01、V02の電圧レベルを出力する 必要がある。このため、演算増幅器の電源として用いられているVSSを、V02より高い電圧 レベルにすることはできなかった。これに対して実施例 3 では、図 4 の演算増幅器 0P1は 、V01の電圧レベルを出力すればよい。このため、演算増幅器の電源として用いられてい るVSSは、V01より低い電圧レベルであれば良い。即ち実施例3では、VDD、VSS間の電圧を 、実施例1、2のVDD、VSS間の電圧よりも小さくすることが可能となる。従って、演算増 幅器のアイドリング電流及びセグメント電極の電圧レベルの切り替わりに起因する電流に よる消費電力を、実施例1、2よりも小さくすることができる。また実施例1、2では、 分割電圧発生用抵抗がVDD、VEE間に接続される。これに対して実施例3では、この分割電 圧発生用抵抗をVDD、VSS間に接続することも可能である。従って、この抵抗部分で消費す る電力も実施例1、2と比較して小さくすることが可能となる。

実施例3では、電圧レベルVDDに基づいてチャージポンプ回路と同様の構成、動作によってV1、V2を得ていると考えることができる。また電圧レベルV01に基づいて、スイッチト・キャパシタ回路として知られる一般的な昇圧回路と同様の構成、動作によって、V1、V2を得ていると考えることもできる。しかしながらV2、V3間の電圧は、一般に、V0、V1間の電圧の10倍以上あり、チャージ・ポンプ回路でV3、V4、V5を得るためには多くのコンデンサと多くのスイッチが必要となり、実際的ではない。これに対して本実施例では、第2駆動電圧群V3~V5がVEEを基準にして設定されているため、多くのコンデンサ等を用いてチャージ・ポンプ動作等を行う必要がない。そして第2駆動電圧群は、VEEを基準に設定されながらも、第1電源VDD、VSSから電源供給されるため、無駄な電力が消費されない等の利点がある。

#### 〔実施例4〕

図 5 に、実施例 4 の電源回路の構成例を示す。実施例 1 との相違は、VDD、VSS間の電圧が下がった場合にVDD、VEE間のインピーダンスを低下させるインピーダンス低下回路51を新たに付加した点である。図 5 のダイオードD1は、VDD、VEE間が低インピーダンスになった場合に、V2、V3の電圧レベルが逆転するのを防止するためのものである。

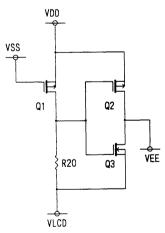

図 6 にインピーダンス低下回路51の一例を示す。図 6 においてVLCDは、インピーダンス低下回路51を動作させるための外部電源である。VDD、VSS間の電圧がMOS型電界効果トランジスタQ1のしきい値電圧よりも大きな場合は、MOS型電界効果トランジスタQ1及びQ3がオンし、Q2がオフする。これによりVEEの電圧レベルはVLCDとなる。一方、VDD、VSS間の電圧がQ1のしきい値電圧よりも小さくなった場合は、Q2がオンし、Q1及びQ3がオフする。これによりVEE、VDD間のインピーダンスが低下し、VEEの電圧レベルはVDDとなる。なお図 6のR20は、Q1を流れる電流を制限するための抵抗である。Q2、Q3は常にいずれか一方がオフしているので、図 6 の回路の消費電力は、抵抗R20を大きくすることで低く抑えることができる。

本発明の電源回路では、図20の従来例と異なり、VDD、VEE間に演算増幅器が接続されていない。従ってVDD、VEE間及びVO、V5間が非常に高インピーダンスになる。また電圧レベルを安定させるため、例えば外部電源VSS、VEE間、VDD、VSS間には大きな容量を持つコンデンサが挿入されていることが一般的である。このような外部電源を用いて動作している電源回路により液晶を駆動した場合、外部電源を切った時に、電源VEEが浮いた状態になる。これにより、VEEの電圧レベルがVDD又はVSSの電圧レベル近くまで落ちるまでに必要な時間が長くなる。またこれに伴い、V3、V4の電圧レベルが落ちるまでの時間も長くなる。そのため外部電源を切った時、長時間、液晶に直流電圧が印加される恐れがある。従ってこれを防ぐために、VEE(V5)及びV3、V4の電圧レベルを速やかにV0近くまで落としてやる必要があり、そのためには例えば外部電源が切られたらすぐにVDDとVEEの間及びV3、V4とVDDの間のインピーダンスを低下させる必要がある。

図5の回路では、VDD、V01、V02相互間の電圧の低下は演算増幅器のOP1、OP2の電源電圧の低下により引き起こされる。そこでインピーダンス低下回路51がVDD、VSS間の電圧を調べる。そして、その電圧がQ1のしきい値電圧よりも小さくなったときに、第1電源の電圧レベルであるVDDと、第2電源の電圧レベルであるVEE間のインピーダンスを低くするようにしている。図5の回路では、VEEの電圧レベルがVDD近くになれば、V3、V4も自動的にVDD近くの電圧レベルになる。従って、V3、V4に対しては特別な回路を付加する必要がない

図 6 に示すインピーダンス低下回路51では、第 1 電源の電圧レベルの低下を、MOS型電界効果トランジスタを用いて調べている。しかしながらインピーダンス低下回路51は必ずしもこのような構成とする必要はなく、例えば装置の外部よりインピーダンス低下回路51に対して制御信号を送ることで、VSS、VEE間のインピーダンスを調整してもよい。

以上のように実施例 4 によれば、外部電源遮断時に第 2 電源の電圧レベルが落ちるのに時間がかかるという問題は解決され、液晶をより安全に駆動することができる。

〔実施例5〕

50

40

10

20

20

30

40

50

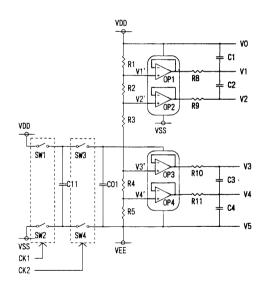

図7に、実施例5の電源回路の構成例を示す。図20に示す従来例との主な相違は、演算増幅器0P1~0P4の電源部である。図7においてVDD、VSSは第1電源の電圧レベルに、VEEは第2電源の電圧レベルに、Voは第3電源の電圧レベルに相当する。またC11は電圧変換用コンデンサに、SW1、SW2は第1スイッチ群に、SW3、SW4は第2スイッチ群に相当する。SW1、SW2は信号CK1によって制御され、SW3、SW4は信号CK2によって制御される。

ボルテージ・フォロア接続された演算増幅器OP1、OP2等は第1供給回路に相当する。そして演算増幅器OP1、OP2は第1電源VDD、VSSにより動作するため、第1駆動電圧群VO~V2は、第1電源から電源供給されることになる。

SW1、SW2、C11、SW3、SW4等から成る回路は電圧変換回路に相当する。この電圧変換回路は、第1電源の電圧レベルVDD、VSSを変換して、VEE(第3電圧レベル)を基準に設定される第3電源の電圧レベルVoを出力する。

ボルテージ・フォロア接続された演算増幅器OP3、OP4等は第2供給回路に相当する。これらのOP3、OP4は、Vo、VEEにより動作し、電圧を1対1に変換すると共に、第2駆動電圧群V3~V5を供給するためのインピーダンス変換を行う。

但し第1、第2供給回路は、ボルテージ・フォロア接続された演算増幅器に限らず、演算増幅器を用いた他の回路であってもよいし、バイポーラ・トランジスタ、電界効果トランジスタ等を用いた回路であってもよい。C01は、演算増幅器OP3、OP4に供給される電源電圧を保持するためのコンデンサである。

実施例 5 においても、信号CK1、CK2として、図 2 に示す波形の信号が印加される。そして信号CK1がHであり、信号CK2がLである期間ではSW1、SW2がオンし、コンデンサC11は電源VDD、VSSにより充電される。一方、信号CK1がLでありCK2がHである期間ではSW3、SW4がオンし、C11の一方の端子がVEEに接続され、他方の端子がVo = VEE + VDD - VSSの電圧レベルを出力する。このVoの電圧レベルはC01によって保持される。即ち、次に信号CK1がH、CK2がLとなった場合にも、コンデンサC01によりVoの電圧レベルがほぼ一定に保持される。以上により演算増幅器OP3、OP4は、VDD - VSSの電圧で動作することになる。即ち実施例 1 等と同様に、OP3、OP4で消費する電力は第 1 電源VDD、VSSから供給される。

演算増幅器のアイドリング電流及びセグメント電極の電圧の切り替わりに起因する電流は、図20の従来例ではVDDとVEEから供給されていた。これに対し本実施例では、これらの電流はすべてVDD、VSSから供給される。従って、これらの電流に起因する消費電力は大幅に減少する。また本実施例では、演算増幅器の耐圧はVDD - VSS以上であればよいので、図20の従来例で使用される演算増幅器の耐圧として必要なVDD - VEEと比較して、小さな値ですむ。つまり本実施例では演算増幅器に高価な高耐圧のものを用いる必要がない。また第1駆動電圧群V0~V2、第2駆動電圧群V3~V5は、従来例と同様に演算増幅器により安定化されているため、V0~V5の安定性は従来例と同等となる。

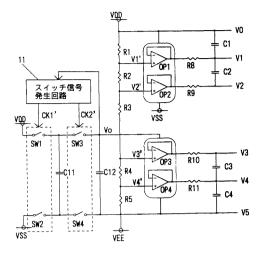

# 〔実施例6〕

図 8 に、実施例 6 の電源回路の構成例を示す。上記実施例 5 との相違は、スイッチ信号発生回路11を新たに付加した点である。スイッチ信号発生回路11は、第 3 電源 Voの電圧レベルを監視し、この Voの電圧レベルに応じて第 1 スイッチ群 SW1、SW2、第 2 スイッチ群 SW3、SW4の少なくとも一方の動作を停止させるものである。

以下、スイッチ信号発生回路11の動作の詳細について説明する。

スイッチ信号発生回路11は、Voの電圧レベルを監視する。そしてVoの電圧レベルが所与の基準電圧レベル(以下Vr1と表す)まで低下したら、図 2 に示す波形の信号CK1、CK2を信号CK1'、CK2'として出力し、Voの電圧レベルを上昇させる。一方、Voの電圧レベルが基準電圧レベルVr1以上であれば、信号CK1'、CK2'を共にLにし、スイッチSW1~SW4の動作を停止する。ここでVoの電圧レベルは、演算増幅器OP3、OP4が動作可能となる電圧レベル以上に設定される。またこのVoの電圧レベルは、スイッチSW3、SW4等がオフしている時にもコンデンサC12に保持される。演算増幅器OP3、OP4が電流をほとんど必要としないときには、Voの電圧レベルは長時間Vo > Vr1の状態にあるため、スイッチSW1~SW4はほとんど動作しない。一方、演算増幅器OP3、OP4が多くの電流を必要とするときには、Vo > Vr1である時間が短くなり、単位時間あたりのSW1~SW4の動作回数が増大する。基準電圧レベルVr

20

30

40

50

1を、演算増幅器OP3、OP4が動作可能となる電圧レベル以上に設定しておけば、スイッチSW1~SW4は、電源VDD、VSSから演算増幅器OP3、OP4に電流を供給するのに必要な最低限のスイッチ回数で動作するようになる。これによりスイッチSW1~SW4を動作させるのに必要な電力を低減できる。

このようなスイッチ信号発生回路11は例えば図9の回路で実現できる。図9において、コンパレータ51は、Voの電圧レベルと基準電圧レベルVr1とを比較するものである。基準電圧レベルVr1を得るには例えば電源VDD、VEEを抵抗分割しても良いし、ツェナー・ダイオード等を用いても良いし、図8の中にある適当な電圧レベルを用いても良い。レベルシフタ52は、コンパレータ51の出力をロジック用電圧に変換するものでである。信号ライン501、502には、図2示す波形の信号が入力される。レベル・シフタ52の出力は、Vo < Vr1のとき H となり、Vo > Vr1のとき L となる。従ってVo < Vr1の時には、AND53、54の出力信号CK1、CK2'として、図2に示す波形の信号CK1、CK2が出力される。一方、Vo > Vr1のときは、CK1'、CK2'はともに L となる。

実施例6では、SW1~SW4が停止している場合等に、Voの電圧レベルが変動する。しかしながら演算増幅器0P3、0P4が動作可能となる電圧レベル以下にならないように、Voが制御されているため、演算増幅器0P3、0P4の働きによって電圧レベルV3、V4はほとんど変動しない。従って、従来の電源回路と比較して表示品位が低下する事はない。

# 〔実施例7〕

図10に、実施例7の電源回路の構成例を示す。上記実施例5との相違は、電源供給回路21を新たに付加した点である。スイッチSW1~SW4は実施例1と同様の動作をする。但し信号CK1、CK2としては、図2に示す波形の信号を用いても良いし、図8のスイッチ信号発生回路11が出力する信号CK1'、CK2'を用いても良い。なおC12は、Vo、VEE間の電圧を保持するためのコンデンサである。

電源供給回路21は、第3電源のVoの電圧レベルを監視し、第1、第2電源の少なくとも一方(図10ではVSS)から第3電源Voに電流を供給するものである。

以下、電源供給回路21の動作の詳細について説明する。

電源供給回路21はVoの電圧レベルを監視する。そしてVoの電圧レベルが所与の基準電圧レベル(以下Vr2と表す)まで低下したら、電源VSSからVoへ電流を流し、Voを上昇させる。一方、Voの電圧レベルが基準電圧レベルVr2以上であれば、電源VSSとVoとの間を遮断する。基準電圧レベルVr2は、演算増幅器OP3、OP4が動作可能となる電圧レベル以上に設定される。演算増幅器OP3、OP4がそれほど多くの電流を必要としないときには、スイッチSW1~SW4及びコンデンサC11の働きによって、演算増幅器OP3、OP4で消費する電流は電源VDD、VSSから供給される。この時、電源供給回路21は特に何の働きもしない。演算増幅器OP3、OP4が多くの電流を必要とし、その電流を、スイッチSW1~SW4及びコンデンサC11の働きによって電源VDD、VSSから供給しきれなくなった場合に、Voの電圧レベルは低下し、VoくVr2となる。このとき電源供給回路21は、電源VSSからVoへ電流を供給し、演算増幅器OP3、OP4の動作可能電圧を確保する。但し電源供給回路21が働いている場合でも、演算増幅器OP3、OP4の動作可能電圧を確保する。但し電源供給回路21が働いている場合でも、演算増幅器OP3、OP4の電流の一部は電源VDD、VSSから供給されている。

このような電源供給回路21は、例えば図11の回路で実現できる。図11において、コンパレータ61は、Voの電圧レベルと、適当な方法で得られた基準電圧レベルVr2とを比較する。抵抗63は、トランジスタ62を保護するための抵抗である。トランジスタ62は、Vo < Vr2のときオンとなり、電源VSSからVoへ電流を流し、Vo > Vr2のときオフとなり、電源VSSとVoとの間を遮断する。

実施例 7 によれば、Voの電圧レベルは変動するが、演算増幅器0P3、0P4の働きによって、電圧レベルV3、V4についてはほとんど変動しない。従って、従来の電源回路と比較して表示品位が低下するような事はない。

実施例 7 の電源回路を用いて、パネル・サイズの大きな液晶表示装置を駆動した場合を考える。パネル電流は、パネル・サイズの大きな液晶パネルほど大きい。しかし文字パターンのような典型的な表示をしている場合は、セグメント・パネル電流はそれほど大きくならない。このため他の実施例と同様に電源VDD、VSSから演算増幅器OP3、OP4へ電流が供給

30

40

50

され、他の実施例と同様に低消費電力化が図れる。また非常に大きなセグメント・パネル電流が必要な特殊パターンを表示し、演算増幅器OP3、OP4に必要な電流を、スイッチSW1~SW4及びコンデンサC11の働きによって電源VDD、VSSから供給しきれなくなった場合を考える。この場合においても、電流の不足分を電源VSS、VEEから供給することで、演算増幅器OP3、OP4は正常に動作し、適正な電圧レベルV3、V4を出力できる。つまり実施例7によれば、スイッチSW1~SW4、コンデンサC11等の能力を低く押さえたまま、液晶表示装置が使用され得る全ての条件にわたって電圧レベルV1~V4を安定に出力できるとともに、液晶表示装置が普通に使用される条件での消費電力を低減できる。

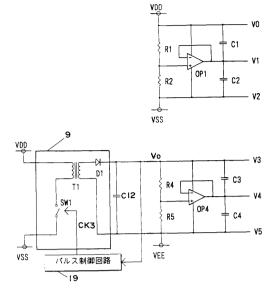

図12に、実施例 8 の電源回路の構成例を示す。図12において、VDD、VSSは第 1 電源の電圧レベルに、VEEは第 2 電源の電圧レベルに、Voは第 3 電源の電圧レベルに相当する。またC 11は電圧変換用コンデンサに、SW1、SW2は第 1 スイッチ群に、SW3、SW4は第 2 スイッチ群に相当する。SW1~SW4は、パルス制御回路20から出力される信号CK1、CK2によって制御される。

実施例 8 では、演算増幅器 OP1等が第 1 供給回路に相当する。演算増幅器 OP1は第 1 電源 VD D、VSSにより動作するため、第 1 駆動電圧群 VO ~ V2は、第 1 電源から電源供給されることになる。また実施例 1 等と異なり、第 1 電源 VDD、VSS間を抵抗 R1、R2で分割した電圧が演算増幅器 OP1に入力される。そして、この分割電圧レベルを演算増幅器 OP1によりインピーダンス変換したものが、V1として出力される。但し OP1を設けずに、この分割電圧レベルをそのまま V1として出力することも可能である。また図 12では、第 1 電源 VDD、VSSをそのまま V0、V2として用いているが、必ずしもそのようにする必要はない。なお C1、C2は電圧平滑用のコンデンサである。

電圧変換回路10は、SW1、SW2、C11、SW3、SW4等を含み、第1電源の電圧レベルVDD、VSSを変換して、VEE(第3電圧レベル)を基準に設定される第3電源の電圧レベルVoを出力する。

実施例 8 では、演算増幅器 OP4等が第 2 供給回路に相当する。演算増幅器 OP4には、Vo、VE E間を抵抗 R4、R5で分割した電圧が入力される。そして、この分割電圧レベルを演算増幅器 OP4によりインピーダンス変換したものが、V4として出力される。但し OP4を設けずに、この分割電圧レベルをそのまま V4として出力することも可能である。また図 12では、Vo、VEEをそのまま V3、V5として用いているが、必ずしもそのようにする必要はない。

なおC3、C4は電圧平滑用のコンデンサである。また図12においてC12は必ずしも設ける必要はなく、Voの電圧保持はC3、C4等で代用できる。

実施例 8 では、演算増幅器 OP1は第 1 電源 VDD、VSSから電源供給され、VDD - VSSの電圧で動作する。またパルス制御回路 20からは、図 2 に示す波形の信号が入力されるため、実施例 5 等と同様の動作により、Voの電圧レベルは VEE + VDD - VSSとなる。これにより、演算増幅器 OP2も第 1 電源 VDD、VSSから電源供給され、VDD - VSSの電圧で動作することになる。以上により演算増幅器のアイドリング電流及びセグメント電極の電圧の切り替わりに起因する電流を大幅に低減でき、低消費電力化を図れる。

また実施例 1 等あるいは従来例では、分割電圧レベルを得るための抵抗はVDD、VEE間に接続されていた。従って、液晶表示装置の高デューティ化等に伴い、VDD、VEE間の電圧が大きくなると、これらの抵抗を流れる電流も増加し、低消費電力化が妨げられる。これに対して実施例 8 では、抵抗 R1、R2 は VDD、VSS間に接続され、抵抗 R4、R5 は Vo、VEE間に接続される。そして液晶表示装置が高デューティ化しても、VDD、VEE間の電圧は大きくなるが、VDD、VSS間及び Vo、VEE間の電圧はそれほど変化しない。従って、これらの抵抗を流れる電流も大きくならず、実施例 1 等よりも更に低消費電力化を図れる。

さて図12では、電圧変換回路をSW1~SW4、C11等で構成したが、電圧変換回路はこのような構成に限られるものではない。例えば図13の電圧変換回路9は、トランスT1、ダイオードD1、スイッチSW1を含む。スイッチSW1は、パルス制御回路19からの信号CK3によってオン・オフするものである、SW1としては、バイポーラ・トランジスタ、MOSFET、リレー等のスイッチ素子を用いることができる。電圧変換回路9は、入力・出力間が絶縁されたス

イッチング・レギュレータ回路に相当する。信号CK3によりSW1をオン・オフし、トランスT1の一次コイルに交流電流を流すことで、トランスT1の二次コイルに交流電流を発生させる。そして発生した交流電流をダイオードD1により整流すると共に、ダイオードD1の一方の端子に発生する電圧をコンデンサC12により平滑化する。これによりVDD、VSSと絶縁された直流電圧レベルVoが発生される。パルス制御回路19は、Vo(V3)、VEE(V5)間の電圧をフィードバックし、Vo、VEE間の電圧が一定に保たれるように、信号CK3を制御する。以上のように電圧変換回路の構成としてはあらゆる構成のものを採用できる。

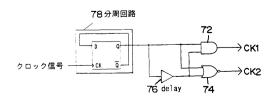

なお図14、図15に、パルス制御回路の構成の一例を示す。SW1、SW2とSW4、SW4とが同時にオンすると、Voの電圧レベルが低下する等の不具合が生じる。このため信号CK1とCK2とは、図2に示すようなノンオーバラップの信号である必要がある。そこで図14では、発振回路70から出力される発振信号を、AND72、NOR74、DELAY76から成る回路に入力して、信号CK1、CK2を得ている。一方、図15では、外部から供給されるクロック信号を分周回路78により分周し、これをAND72、NOR74、DELAY76から成る回路に入力している。図15の回路では発振回路が必要ないため、図15の回路には、回路規模及び消費電力を小さくでき集積回路化しやすいという利点がある。

#### 〔実施例9〕

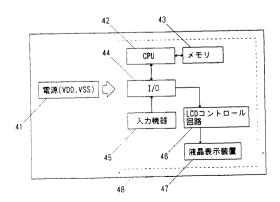

図16の実施例9は、本発明の電源回路を含む時分割駆動の液晶表示装置の構成例を示すものである。この液晶表示装置34は、電源変換回路31、電源回路32、表示ユニット33を含み、表示ユニット33は、液晶素子がマトリクス状に配置される液晶パネル35と、この液晶パネル35を駆動するための駆動回路36を含む。電源回路32は、実施例1~8で説明した電源回路を用いる。電源回路32で生成された電圧レベルV0~V5は表示ユニット33に供給される。電源VDD、VSSはロジック駆動用の電源(デジタル電源)であり、駆動回路36を制御する信号SGNとともに液晶表示装置34の外部から供給される。電源変換回路31は、電源VDD、VSSから電源VEEをつくる回路であり、電源VEEを電源回路32に供給する。図16では、電源変換回路31を用いて液晶表示装置の内部で電源VEEを生成しているが、液晶表示装置34の外部から電源回路32に電源VEEを供給する構成としてもよい。

電源回路32に図20の従来例を用いた場合、電源VDDからVEEに大きな電流が流れ、この電流を供給する電源変換回路31は大規模にならざるを得なかった。そのため液晶表示装置34に電源変換回路31を内蔵させることは実装スペース的に困難であった。しかしながら電源回路32として、実施例1~8に示す構成のものを用いれば、電源VDDからVEEに流れる電流を大幅に低減でき、電源変換回路31を小規模化できる。これにより液晶表示装置34への電源変換回路31の内蔵及び液晶表示装置の小規模化等を図れる。

また本実施例によれば、外部から電源VDD、VSSを供給するだけで良く、液晶表示装置に必要な電源の種類を少なくでき、その利便性を上げることができる。また本実施例では、駆動回路36等の電源となるロジック電源VDD、VSSを用いて、液晶駆動電圧群VO~V5を生成している。従って液晶表示装置に必要な電源の種類を更に少なくでき、利便性を更に向上できる。

# 〔実施例10〕

実施例10は、本発明の電源回路を具備した液晶表示装置を、電子機器の1つであるパーソナル・コンピュータに搭載した例を示すものであり、図17にその構成例を示す。このパーソナル・コンピュータ48は、電源41、CPU42、メモリ43、I/0(入出力ポート)44、キーボード、マウス等の入力機器45、LCDコントロール回路46、液晶表示装置47を含む。LCDコントロール回路46は、I/044から出力された信号を液晶表示装置の制御信号に変換する回路である。液晶表示装置47としては例えば実施例9で示した構成のものを用いる。電源41は、例えばロジック電源VDD、VSSを供給する。

このように実施例9の液晶表示装置47を用いることによって、パーソナル・コンピュータ48全体での消費電力を低減できる。また必要とされる電源はVDD、VSSのみであるため、パーソナル・コンピュータ48の電源回路構成が簡単になる。以上の改善は、パーソナル・コンピュータに限らず、本発明の電源回路を具備した液晶表示装置を用いた全ての電子機器に対して適用できる。

10

20

30

なお、本発明は上記実施例 1~10に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能である。

例えば上記実施例では、6レベル法で時分割駆動する液晶表示装置に本発明を適用した場合について説明した。しかしながら本発明はこれに限らず、6レベル法以外の駆動方法で駆動する液晶表示装置、あるいは液晶素子以外の表示素子を駆動する表示装置等、種々のものに適用できる。

また上記実施例では、第 1 駆動電圧群を $V0 \sim V2$ とし、第 2 駆動電圧群を $V3 \sim V5$ としたが、この逆でも構わない。

また電源回路の構成としては、実施例 1 ~ 8 を組み合わせた種々の構成のものを採用できる。例えば実施例 2 (図 3 )、実施例 3 (図 4 )、実施例 4 (図 5 )の手法は実施例 1 の改良として説明したが、実施例 5 (図 7 )、実施例 6 (図 8 )、実施例 7 (図 10)、実施例 8 (図 12、13)等の改良としても採用できる。同様に実施例 6 、実施例 7 の手法も、実施例 5 のみならず他の実施例の改良としても採用できる。

【図1】 F/G./

【図3】 FIG.3

【図4】 F/G.4

【図5】 F/G.5

【図6】 *F/G.6*

【図15】 *FIG.15*

【図7】 F/G.7

【図8】 F/G.8

【図9】 FIG.9

【図16】 FIG.16

【図10】 FIG.10

【図11】 F/G.//

【図17】 FIG.17

【図 1 2 】 F/G. 12

【図13】 *F/G./3*

【図18】 FIG.18

【図19】 FIG.19

【図20】 F/G.20

【図21】 FIG.21

【図22】 *FIG.22*

# フロントページの続き

(56)参考文献 特開平03-063998(JP,A)

特開平03-200214(JP,A)

特開平04-136981(JP,A)

特開昭54-005399(JP,A)

(58)調査した分野(Int.CI.<sup>7</sup>, DB名)

G02F 1/133 520