(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6069586号

(P6069586)

(45) 発行日 平成29年2月1日(2017.2.1)

(24) 登録日 平成29年1月6日(2017.1.6)

(51) Int.Cl.

F 1

|            |           |      |       |      |

|------------|-----------|------|-------|------|

| GO6K 7/00  | (2006.01) | GO6K | 7/00  | 052  |

| GO6F 13/38 | (2006.01) | GO6K | 7/00  | 069  |

| GO6F 13/42 | (2006.01) | GO6K | 7/00  | 086  |

|            |           | GO6F | 13/38 | 320A |

|            |           | GO6F | 13/42 | 320A |

請求項の数 20 (全 22 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-515956 (P2016-515956)  |

| (86) (22) 出願日 | 平成26年8月18日 (2014.8.18)        |

| (65) 公表番号     | 特表2016-534420 (P2016-534420A) |

| (43) 公表日      | 平成28年11月4日 (2016.11.4)        |

| (86) 國際出願番号   | PCT/US2014/051482             |

| (87) 國際公開番号   | W02015/026717                 |

| (87) 國際公開日    | 平成27年2月26日 (2015.2.26)        |

| 審査請求日         | 平成28年2月16日 (2016.2.16)        |

| (31) 優先権主張番号  | 61/867,343                    |

| (32) 優先日      | 平成25年8月19日 (2013.8.19)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 61/867,353                    |

| (32) 優先日      | 平成25年8月19日 (2013.8.19)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                       |

|-----------|---------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サンディエゴ モアハウス ドラ<br>イブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                |

| (72) 発明者  | ユヴァル・コーリー・ハーシュ<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ドラ<br>イブ・5775               |

最終頁に続く

(54) 【発明の名称】大容量記憶装置ベースのインターフェースを通じてM-PHYベースの通信を運用すること、ならびに関連するコネクタ、システム、および方法

## (57) 【特許請求の範囲】

## 【請求項1】

どの種類のカードがホストデバイス差し込み口に入れられたかを確認する方法であって、

メモリカードフォームファクタ差し込み口へのメモリカードコネクタの挿入を検出するステップと、

前記メモリカードコネクタがメモリカードと関連付けられているかどうか、または前記メモリカードコネクタがM-PHYプロトコルに従って動作するよう構成された回路と関連付けられているかどうかを判断するステップと、

前記判断するステップが、前記メモリカードコネクタが前記メモリカードと関連付けられていると判断する場合、第1のモードで動作するステップと、

前記判断するステップが、前記メモリカードコネクタが前記M-PHYプロトコルに従って動作するよう構成された前記回路と関連付けられていると判断する場合、第2のモードで動作するステップと

を含む、方法。

## 【請求項2】

前記メモリカードコネクタが前記メモリカードと関連付けられているかどうかを判断するステップが、メモリカード規格と関連付けられるコマンドを送信し、応答を検出するステップを含む、請求項1に記載の方法。

## 【請求項3】

10

20

前記メモリカードコネクタが前記メモリカードと関連付けられているかどうかを判断するステップが、各コマンドが異なるメモリカード規格と一意に関連付けられる複数のコマンドを送信し、前記複数のコマンドの各々によって応答が生成されるかどうかを評価するステップを含む、請求項1に記載の方法。

**【請求項4】**

前記メモリカードコネクタが、コンパクトフラッシュ(登録商標)(ⅠおよびⅡ)、セキュアデジタル(SD)(SD、miniSD、microSD、SDHC、miniSDHC、microSDHC、SDXC)、メモリスティック(スタンダード、Pro、Pro Duo、Pro-HG Duo、Micro(M2)、xC)、MultiMediaCard(MMC)(MMC、RS-MMC、MMCmobile、MMCplus、MMCmicro、eMMC)、シリアル周辺機器インターフェース(SPI)、xD(スタンダード、Type M、Type H、Type M+)、XQD、およびウルトラハイスピード(UHS:Ultra High Speed)(ⅠおよびⅡ)から成る群から選択されるメモリカード規格に従って動作するように構成された前記回路に関連付けられているかどうかを判断するステップをさらに含む、請求項1に記載の方法。

10

**【請求項5】**

前記メモリカードコネクタが、ユニバーサルフラッシュストレージ(UFS)システムと結合されたM-PHY規格に従って動作するように構成された前記回路と関連付けられているかどうかを判断するステップをさらに含む、請求項1に記載の方法。

**【請求項6】**

前記メモリカードコネクタと関連付けられた電源ピンが、前記メモリカードフォームファクタ差し込み口に含まれる電源ピンに導電結合されることに応答して、前記メモリカードコネクタと関連付けられた前記電源ピンを検出するステップをさらに含む、請求項1に記載の方法。

20

**【請求項7】**

前記電源ピンを通じて電力を提供するステップをさらに含む、請求項6に記載の方法。

**【請求項8】**

どの種類のカードがホストデバイス差し込み口に入れられたかを確認する方法であって、

メモリカードフォームファクタ差し込み口へのメモリカードコネクタの挿入を検出する

ステップと、

前記メモリカードコネクタ内の論理手段に、第1のメモリカード通信プロトコルと一意に関連付けられる第1のコマンドを提供するステップと、

30

前記第1のコマンドへの第1の応答が、前記メモリカードコネクタ内の前記論理手段からホストデバイスに提供されるかどうかを判断するステップと、

第1の応答が提供されない場合、前記メモリカードコネクタ内の前記論理手段に、第2のメモリカード通信プロトコルと関連付けられる第2のコマンドを提供するステップと、

前記第2のコマンドへの第2の応答が、前記メモリカードコネクタ内の前記論理手段から前記ホストデバイスに提供されるかどうかを判断するステップと、

第2の応答が提供されない場合、M-PHYプロトコルに従って前記メモリカードコネクタを通じて前記メモリカードコネクタと関連付けられた回路と対話するステップとを含む、方法。

40

**【請求項9】**

前記第1のメモリカード通信プロトコルが、セキュアデジタル(SD)プロトコルを含む、請求項8に記載の方法。

**【請求項10】**

前記第2のメモリカード通信プロトコルが、MMCプロトコルを含む、請求項8に記載の方法。

**【請求項11】**

前記メモリカードコネクタが、コンパクトフラッシュ(登録商標)(ⅠおよびⅡ)、セキュアデジタル(SD)(SD、miniSD、microSD、SDHC、miniSDHC、microSDHC、SDXC)、メモリスティック(スタンダード、Pro、Pro Duo、Pro-HG Duo、Micro(M2)、xC)、MultiMediaCard(MMC)

50

C)(MMC、RS-MMC、MMCmobile、MMCplus、MMCMicro、eMMC)、シリアル周辺機器インターフェース(SPI)、xD(スタンダード、Type M、Type H、Type M+)、XQD、およびウルトラハイスピード(UHS:Ultra High Speed)(IおよびII)から成る群から選択されるメモリカード規格に従って動作するように構成された前記回路と関連付けられているかどうかを判断するステップをさらに含む、請求項8に記載の方法。

**【請求項12】**

前記メモリカードコネクタが、ユニバーサルフラッシュストレージ(UFS)システムと結合されたM-PHY規格に従って動作するように構成された前記回路と関連付けられているかどうかを判断するステップをさらに含む、請求項8に記載の方法。

**【請求項13】**

前記メモリカードコネクタと関連付けられた電源ピンが、前記メモリカードフォームファクタ差し込み口に含まれる電源ピンに導電結合されることに応答して、前記メモリカードコネクタと関連付けられた前記電源ピンを検出するステップをさらに含む、請求項8に記載の方法。

**【請求項14】**

前記電源ピンを通じて電力を提供するステップをさらに含む、請求項13に記載の方法。

**【請求項15】**

メモリカードフォームファクタ差し込み口へのメモリカードコネクタの挿入を検出し、前記メモリカードコネクタがメモリカードと関連付けられているかどうか、または前記メモリカードコネクタがM-PHYプロトコルに従って動作するように構成された回路と関連付けられているかどうかを判断し、

前記判断が、前記メモリカードコネクタが前記メモリカードと関連付けられていると判断する場合、第1のモードで動作し、

前記判断が、前記メモリカードコネクタが前記M-PHYプロトコルに従って動作するよう構成された前記回路と関連付けられていると判断する場合、第2のモードで動作するための命令を有するソフトウェアを含む非一時的コンピュータ可読記録媒体。

**【請求項16】**

前記メモリカードコネクタが前記メモリカードと関連付けられているかどうかを判断するための前記命令が、メモリカード規格と関連付けられるコマンドを送信し、応答を検出するための命令を含む、請求項15に記載のコンピュータ可読記録媒体。

**【請求項17】**

前記メモリカードコネクタが前記メモリカードと関連付けられているかどうかを判断するための前記命令が、各コマンドが異なるメモリカード規格と一意に関連付けられる複数のコマンドを送信し、前記複数のコマンドの各々によって応答が生成されるかどうかを評価するための命令を含む、請求項15に記載のコンピュータ可読記録媒体。

**【請求項18】**

前記命令が、前記メモリカードコネクタが、ユニバーサルフラッシュストレージ(UFS)システムと結合されたM-PHY規格に従って動作するように構成された前記回路と関連付けられているかどうかを判断するための命令をさらに含む、請求項15に記載のコンピュータ可読記録媒体。

**【請求項19】**

メモリカードコネクタを収納するように構成され、メモリカードフォームファクタ内の接点と嵌合するように構成された電気接点を有する差し込み口と、

前記電気接点に動作可能に結合され、

前記差し込み口への前記メモリカードコネクタの挿入を検出し、

前記メモリカードコネクタがメモリカードと関連付けられているかどうか、または前記メモリカードコネクタがM-PHYプロトコルに従って動作するように構成された回路と関連付けられているかどうかを判断し、

前記判断が、前記メモリカードコネクタが前記メモリカードと関連付けられていると判断する場合、第1のモードで動作し、

10

20

30

40

50

前記判断が、前記メモリカードコネクタが前記M-PHYプロトコルに従って動作するよう構成された前記回路と関連付けられると判断する場合、第2のモードで動作するよう構成された制御システムとを含む、コンピューティングデバイス。

【請求項 20】

前記差し込み口が、電源ピンを含み、前記制御システムが、前記電源ピンを通じて前記メモリカードコネクタに電力を提供するように構成された、請求項19に記載のコンピューティングデバイス。

【発明の詳細な説明】

【技術分野】

10

【0001】

優先権出願

本出願は、参照によりその全体を本明細書に組み込まれている、2013年8月19日に出願した、「OPERATING M-PHY BASED COMMUNICATIONS OVER MASS STORAGE-BASED INTERFACES, AND RELATED CONNECTORS, SYSTEMS AND METHODS」という名称の米国仮特許出願第61/867353号の優先権およびその利益を主張するものである。

【0002】

本出願は、参照によりその全体を本明細書に組み込まれている、2013年8月19日に出願した、「OPERATING M-PHY BASED COMMUNICATIONS OVER MASS STORAGE-BASED INTERFACES, AND RELATED CONNECTORS, SYSTEMS AND METHODS」という名称の米国仮特許出願第61/867343号の優先権およびその利益もまた主張するものである。

20

【0003】

本出願は、参照によりその全体を本明細書に組み込まれている、2014年5月2日に出願した、「OPERATING M-PHY BASED COMMUNICATIONS OVER MASS STORAGE-BASED INTERFACES, A ND RELATED CONNECTORS, SYSTEMS AND METHODS」という名称の米国特許出願第14/267983号の優先権およびその利益もまた主張するものである。

【0004】

本開示の技術は、概して、電子デバイス間の通信に使用される通信インターフェースに関する。

【背景技術】

30

【0005】

社会全体にわたって、広範なアプリケーションおよび用途をサポートする電子デバイスが急増している。デバイスの数および種類が拡大するにつれて、電子デバイスが互いに通信する必要性が増している。この必要性に応じて、様々なプロトコルが提案され、採用されてきた。多くの場合、プロトコルは、電子デバイス間で通信される信号レベル、関連するデータ表現、およびタイミングを定義する。これらのプロトコルの例は、電気電子技術者協会(IEEE: Institute of Electrical and Electronics Engineers)によって示される802.11規格およびBLUETOOTH(登録商標)などのワイヤレス通信を含む。ワイヤレス信号プロトコルは、周波数および電力レベルを指定することもできる。これらのプロトコルの他のものは、有線ベースである。プロトコルが有線ベースである場合、デバイス間の通信を行うには、標準化された物理コネクタが必要とされることがある。様々な物理コネクタ、たとえば登録ジャック-11(RJ-11:Registered Jack-11)、RJ-14、RJ-21、RJ-45、およびRJ-49が、様々な目的およびプロトコルにうまく使用してきた。

40

【0006】

モバイルプラットフォームデバイスの増加、およびこれらのデバイスの各々において機能が増加したことに伴い、周辺機器間のデータレートが指数関数的に増加した。これに関連して、モバイル業界プロセッサインターフェース(Mobile Industry Processor Interface:MIPI(登録商標))アライアンスは、最近、レーンあたり10Kbpsから5.8Gbpsのデータレートを定義するM-PHY(登録商標)物理層規格を提案した。M-PHY規格は、モバイル端末、スマートフォンなどのためのカメラ、ディスプレイなど、モバイル用途に最適化されている

50

。しかしながら、M-PHY規格は高帯域能力を有するシリアルインターフェース技術を提供するが、M-PHY仕様は、コネクタ定義を意図的に避け、デバイス間の永続的トレースに基づく接続(permanent trace based connection)を支持する。永続的トレースに基づく接続は、ユーザが求める接続の柔軟性をなくす。

【発明の概要】

【課題を解決するための手段】

【0007】

詳細な説明において開示される実施形態は、大容量記憶装置ベースのインターフェースを通じてM-PHY通信を運用することを含む。関連するコネクタ、システム、および方法もまた開示される。詳細には、本開示の実施形態は、M-PHY規格対応の信号を採用し、メモリカードベースのコネクタを有する2つのM-PHY規格対応のデバイスが通信できるように、メモリカード対応のコネクタをそれらに通過させる。これらのコネクタに対する確かな製造基盤およびその物理的限界の理解があるので、メモリカードのフォームファクタを再利用することにより、製造および業界内の受入れの効率化を考慮し、これは、そのようなコネクタをその製品に組み入れる際に設計者の助けとなる。

10

【0008】

別の実施形態では、どの種類のカードがホストデバイス差し込み口に入れられたかを確認する方法が開示される。この方法は、メモリカードフォームファクタ差し込み口へのメモリカードコネクタの挿入を検出するステップを含む。この方法はまた、メモリカードコネクタが、メモリカードと関連付けられているか、またはM-PHYプロトコルに従って動作しているかを判断するステップを含む。この方法はまた、この判断するステップに基づいて動作するステップを含む。

20

【0009】

別の実施形態では、どの種類のカードがホストデバイス差し込み口に入れられたかを確認する方法が開示される。この方法は、メモリカードフォームファクタ差し込み口へのメモリカードコネクタの挿入を検出するステップを含む。この方法はまた、第1のメモリカード通信プロトコルと一緒に関連付けられる第1のコマンドを、メモリカードコネクタ内のロジックに第1のコマンドを提供するステップを含む。この方法はまた、第1のコマンドへの第1の応答が、メモリカードコネクタ内のロジックからホストデバイスに提供されるかどうかを判断するステップを含む。この方法はまた、第1の応答が提供されない場合、第2のメモリカード通信プロトコルと一緒に関連付けられる第2のコマンドを、メモリカードコネクタ内のロジックに提供するステップを含む。この方法はまた、第2のコマンドへの第2の応答が、メモリカードコネクタ内のロジックからホストデバイスに提供されるかどうかを判断するステップを含む。この方法はまた、第2の応答が提供されない場合、M-PHYプロトコルに従って動作するステップを含む。

30

【0010】

別の実施形態では、非一時的コンピュータ可読媒体が開示される。この媒体は、メモリカードフォームファクタ差し込み口へのメモリカードコネクタの挿入を検出するための命令を有するソフトウェアを含む。この媒体はまた、メモリカードコネクタが、メモリカードと関連付けられているか、またはM-PHYプロトコルに従って動作しているかを判断するための命令を有するソフトウェアを含む。この媒体はまた、この判断に基づいて動作するための命令を有するソフトウェアを含む。

40

【0011】

別の実施形態では、コンピューティングデバイスが開示される。このデバイスは、メモリカードコネクタを収納するように構成され、メモリカードフォームファクタ内の接点と嵌合するように構成された電気接点を有する差し込み口を含む。このデバイスはまた、電気接点に動作可能に結合され、差し込み口へのメモリカードコネクタの挿入を検出するよう構成された制御システムを含む。制御システムはまた、メモリカードコネクタが、メモリカードと関連付けられているか、またはM-PHYプロトコルに従って動作しているかを判断するように構成される。制御システムはまた、この判断に基づいて動作するように構

50

成される。

**【図面の簡単な説明】**

**【0012】**

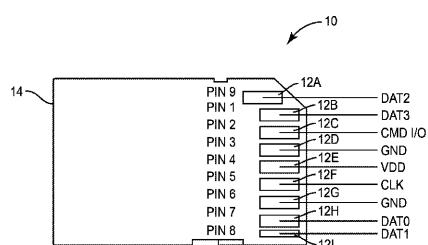

【図1A】ピン配置を有する例示的な従来のSecure Digital(商標)(SD)型メモリカードの上面図である。

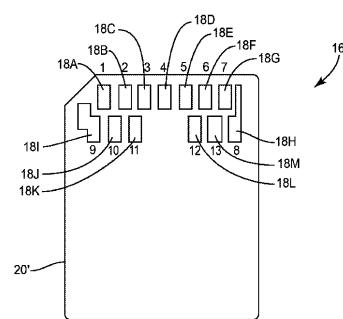

【図1B】ピン配置を有する例示的な従来のMultiMediaCard(MMC)型メモリカードの上面図である。

【図1C】ピン配置を有する例示的な従来のMMCplus型メモリカードの上面図である。

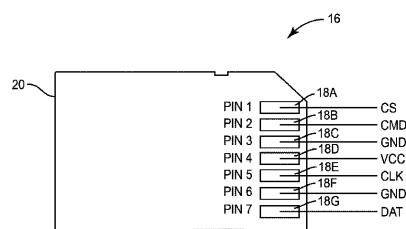

【図1D】ホストデバイスに挿入された従来のメモリカードの簡略図である。

【図2A】M-PHY規格用のM-PHYデータバスへのシリアル周辺機器インターフェース(SPI: Serial Peripheral Interface)型メモリカードピンの例示的なマッピングを示す表である。

10

【図2B】M-PHY規格用のM-PHYデータバスへのSD型メモリカードピンの例示的なマッピングを示す表である。

【図2C】M-PHY規格用のM-PHYデータバスへのUHS-II型メモリカードピンの例示的なマッピングを示す表である。

【図2D】M-PHY規格用のM-PHYデータバスへのMMC型メモリカードピンの例示的なマッピングを示す表である。

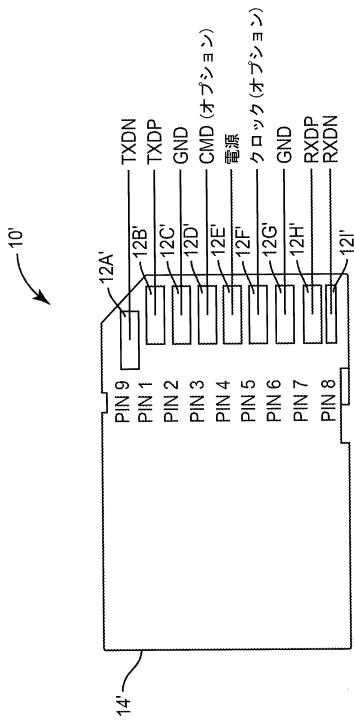

【図2E】M-PHY規格のために再目的化された(repurposed)例示的な実施形態SD型メモリカードフォームファクタの上面図である。

20

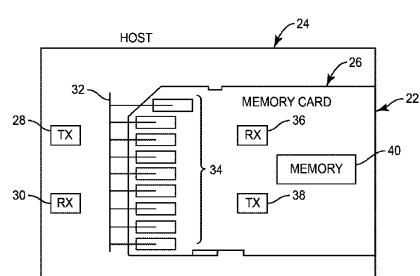

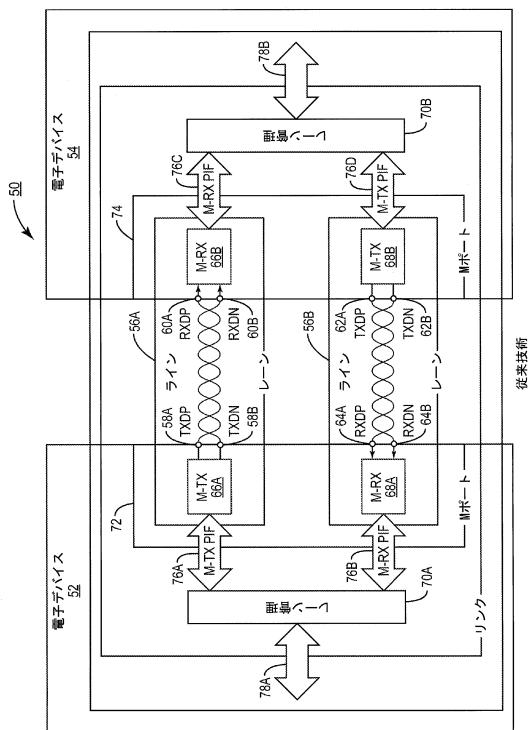

【図3A】M-PHY規格対応の電子デバイスの接続のための従来のM-PHY単一レーン信号バスの例示的な実施形態のブロック図である。

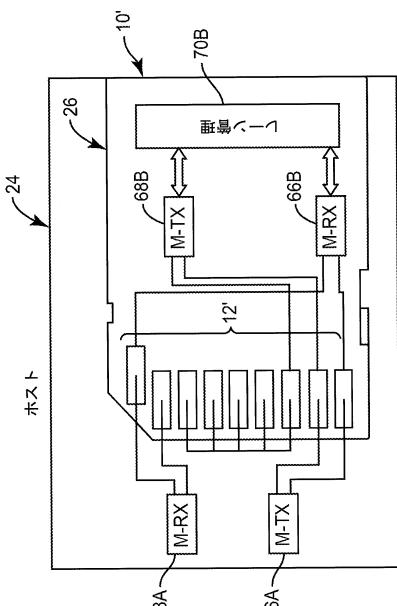

【図3B】ホストデバイスに挿入された再目的化されたメモリカードフォームファクタの簡略図の例示的な実施形態である。

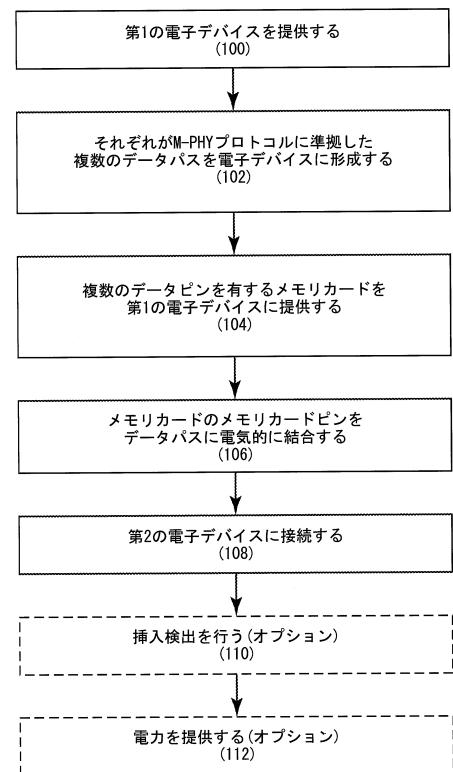

【図4】M-PHY規格データバスにメモリカードフォームファクタのメモリカードピンをマッピングするための例示的なプロセスを示すフローチャートである。

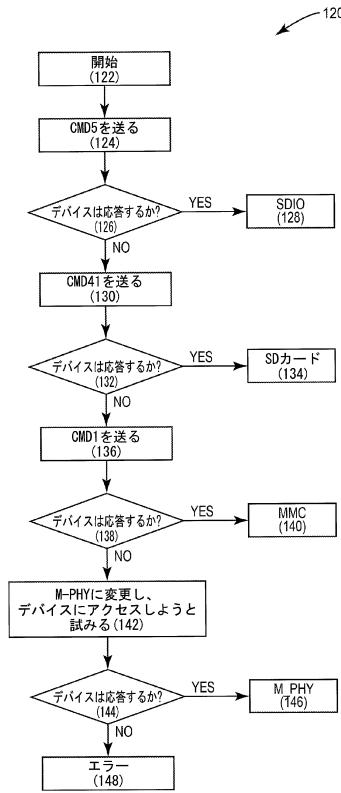

【図5】様々なタイプのメモリカードピンレイアウトを適応させる例示的なデバイス検出プロセスを示すフローチャートである。

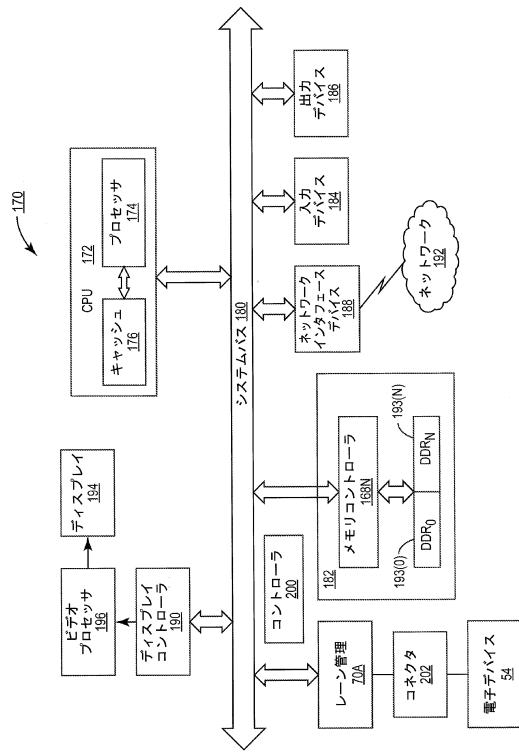

【図6】本明細書に開示する実施形態によるM-PHY規格データバスにマップされたピンを有するメモリカード型コネクタを含むことができる、例示的なプロセッサベースの電子デバイスおよびシステムのブロック図である。

30

**【発明を実施するための形態】**

**【0013】**

次に図面に関して、本開示のいくつかの例示的な実施形態について説明する。「例示的な」という用語は、本明細書では「例、事例、または実例として役に立つこと」を意味するように使用される。「例示的」として本明細書で説明するいかなる実施形態も、他の実施形態よりも好ましいまたは有利であると必ずしも解釈されるべきではない。

**【0014】**

詳細な説明において開示される実施形態は、大容量記憶装置ベースのインターフェースを通じてM-PHY通信を運用することを含む。関連するコネクタ、システム、および方法もまた開示される。詳細には、本開示の実施形態は、M-PHY規格対応の信号を採用し、メモリカードベースのコネクタを有する2つのM-PHY規格対応のデバイスが通信できるように、メモリカード対応のコネクタをそれらに通過させる。これらのコネクタに対する確かな製造基盤およびその物理的限界の理解があるので、メモリカードのフォームファクタを再利用することにより、製造および業界内の受入れの効率化を考慮し、これは、そのようなコネクタをその製品に組み入れる際に設計者の助けとなる。

40

**【0015】**

モバイル業界プロセッサインターフェース(MIPI(登録商標))アライアンスは、デバイスが互いに通信する方法を詳述する物理層プロトコルであるM-PHY規格を提案している。しかしながら、MIPI(登録商標)アライアンスは、M-PHY規格を定義または強制されず、規格

50

に適合する特定のコネクタタイプから始めなければならず、物理コネクタの設計を、このスペースに製品を配置する実体に委ねる。既存のコネクタタイプに関係なくそのような物理コネクタを設計することは可能であるが、ここでは既存のコネクタが、シグナルインテグリティおよびMIPI(登録商標)アライアンスM-PHY規格の他の要件を満たすように適合される。詳細には、メモリカード業界は、いくつかのあらかじめ定義されたフォームファクタを有し、その各々が複数の電気的接続(ピン)を有する。既存のメモリカード規格内にも、サブフォームファクタがあることがある(たとえば、セキュアデジタル(SD)は、SD、miniSD、microSD、SDHC、miniSDHC、microSDHCなどのフォーマットを有する)。記載するよう 10 に、これらのフォームファクタの各々が、メモリカード内の論理セルおよび/またはメモリセルとの通信を可能にする複数の電気的接続(ピン)を有する。これらのピンの存在は、フォームファクタがM-PHY対応のデバイスで使用するために再目的化され得る機会を考慮し、フォームファクタ上のピンはM-PHY対応の信号を運ぶために使用される。メモリカード業界内にはいくつかの専用のピンレイアウトがあるが、各メモリカードと関連するフォームファクタは、十分に文書化され、理解されており、したがって本明細書でさらに開示するように再目的化され得る。非限定的な例として、MIPI(登録商標)アライアンスM-PHY規格に使用されるように適合されるメモリカードフォームファクタは、コンパクトフラッシュ(登録商標)(IおよびII)、セキュアデジタル(SD)(SD、miniSD、microSD、SDHC、miniSDHC、microSDHC、SDXC)、メモリスティック(スタンダード、Pro、Pro Duo、Pro-HG Duo、Micro(M2)、xC)、MultiMediaCard(MMC)(MMC、RS-MMC、MMCmobile、MMCplus、MMCmicro、eMMC)、カードフォーマット内の動作のシリアル周辺機器インターフェース(SPI)モード、xD(スタンダード、Type M、Type H、Type M+)、XQD、またはウルトラハイスピード(UHS:Ultra High Speed)(IおよびII)ピンレイアウトのいずれかであり得る。メモリカードコネクタをM-PHY規格に適合させる実施形態を説明する前に、まずメモリカードコネクタについて、図1A～図1Dに関して説明する。本開示の例示的な実施形態の説明は、図2Aに関して以下に始める。

#### 【0016】

これに関連して、図1A～図1Dは、単独の、およびホストデバイスで使用中の、例示的な従来のメモリカードを示す(ホストデバイスは、メモリカードコントローラまたはカードコントローラと呼ばれることもあることに注意する)。そのようなメモリカードの一般的な使用は、デジタルカメラ、スマートフォン、および他の小型携帯デバイスにおけるものである。データは、一般的に小型携帯デバイスを介して取得され、メモリカードに記憶される。その後、カードは取り外され、デスクトップコンピュータなどのコンピューティングデバイス上の差し込み口に挿入され、ファイルは、コンピューティングデバイスに転送される。そのような使用は、業界ではよく理解されている。しかしながら、完全を期すために、物理的属性および機能の概要を提供する。

#### 【0017】

これに関連して、図1Aは、ピン12A～12I(まとめてピン12)を有するSDカード10を示す。SDカード10は、通常プラスティックまたは他のポリマー材料で作られたおおむね五角形のハウジング14を有する。ピン12は通常、同一平面上にあり、またはハウジング14内にわずかに埋め込まれており、導電性の接点領域を形成し、それを通して電気的接続が行われ得る。以下のTABLE 1(表1)は、各ピン12に対する本開示の参照番号と共に従来のピン割当てを列挙している。

#### 【0018】

【表1】

TABLE 1:従来の SD ピン割当て

| <u>SD ピン#</u> | <u>開示#</u> | <u>SD 信号名</u> | <u>SD 説明</u> |

|---------------|------------|---------------|--------------|

| 1             | 12B        | CD/DAT3       | カード検出/データ#3  |

| 2             | 12C        | CMD           | コマンド/応答      |

| 3             | 12D        | VSS1          | グラウンド        |

| 4             | 12E        | VDD           | 電源電圧         |

| 5             | 12F        | CLK           | クロック         |

| 6             | 12G        | VSS2          | グラウンド        |

| 7             | 12H        | DAT0          | データ#0        |

| 8             | 12I        | DAT1          | データ#1        |

| 9             | 12A        | DAT2          | データ#2        |

10

【0019】

SD仕様に関するさらなる情報については、興味のある読者は、mac6.ma.psu.edu/においてSDグループから入手可能である、SD仕様書、パート1、Physical Layer Simplified Specification、バージョン2.00、2006年9月25日を参照されたい。これによりその全体を参考により組み込まれる。さらに、興味のある読者は、SDグループによって公開されているバージョン3.00または4.00にアクセスすることができる可能性がある。

20

【0020】

SDメモリカード10は、初期のカード、すなわちMMCの発展である。例示的な従来のMMC16が、図1Bに示されている。MMC16は、ピン18A～18G(まとめてピン18)を有する。MMC16は、SDカード10のハウジング14と実質的に同一であるおおむね五角形のハウジング20を有する。主な違いは、SDカード10が、MMC16の7つのピンを超えて2つのさらなるピン(すなわち、ピン12Aおよび12I)を有することである。以下のTABLE 2(表2)は、各ピン18に対する本開示の参照番号と共に従来のピン割当てを列挙している。

【0021】

【表2】

30

TABLE 2:従来の MMC ピン割当て

| <u>MMC ピン#</u> | <u>開示#</u> | <u>MMC 信号名</u> | <u>MMC 説明</u> |

|----------------|------------|----------------|---------------|

| 1              | 18A        | CS             | チップ選択         |

| 2              | 18B        | CMD            | コマンド/応答       |

| 3              | 18C        | GND            | グラウンド         |

| 4              | 18D        | VCC            | 電源電圧          |

| 5              | 18E        | CLK            | クロック          |

| 6              | 18F        | GND            | グラウンド         |

| 7              | 18G        | DAT            | データ           |

40

【0022】

上記のように、MMCはSD規格よりもさらに古い規格であり、業界は、規格に対応したカードを製造することおよびその操作をよく知っている。また標準的なMMCは、7つのピンを有し、MMCの変形(permutation)は、より多くのピンを備えて存在する(たとえばMMCplus、MMCmicro、eMMC)ことに注意する。7つのピンしかないより古い基本的なMMC(ならびにRS-MMCおよびSecureMMC)は、本明細書に記載するように再目的化にあまり適していない。しかしながら、13のピンを有するMMCplusから始まるMMC規格の後続製品(たとえば、MMCplus、MMCmobile)は、本明細書に記載する再目的化に適している。したがって、図1Cは、ハウジング20と実質的に似ているハウジング20'を有する従来のMMCplusカード16'を示している

50

。MMCplusカード16'は、MMCカード16(図1B)のピン18A～18Gと同一のピン18A～18Gを有するが、さらなるピン18H～18Lも追加し、さらなるデータチャネルを可能にする。以下のTABLE 3(表3)は、各ピン18に対する本開示の参照番号と共に従来のピン割当てを列挙している。

#### 【0023】

##### 【表3】

TABLE 3:従来の MMCPLUS ピン割当て

| <u>MMC ピン#</u> | <u>開示#</u> | <u>MMC 信号名</u> | <u>MMC 説明</u> |

|----------------|------------|----------------|---------------|

| 1              | 18A        | DAT3           | データ           |

| 2              | 18B        | CMD            | コマンド/応答       |

| 3              | 18C        | VSS            | グラウンド         |

| 4              | 18D        | VDD            | 電源電圧          |

| 5              | 18E        | CLK            | クロック          |

| 6              | 18F        | VSS            | グラウンド         |

| 7              | 18G        | DAT0           | データ           |

| 8              | 18H        | DAT1           | データ           |

| 9              | 18I        | DAT2           | データ           |

| 10             | 18J        | DAT4           | データ           |

| 11             | 18K        | DAT5           | データ           |

| 12             | 18L        | DAT6           | データ           |

| 13             | 18M        | DAT7           | データ           |

10

20

30

#### 【0024】

図1A～図1Cには3つの従来のカードピンレイアウトしか示されていないが、当然のことながら他の従来のメモリカードが同様によく理解されている。したがって、MMCMicro、コンパクトフラッシュ(登録商標)、メモリスティック、SPI、xD、XQD、またはUHSのためのピンレイアウトは提供されていないが、これらのフォーマットを使用するカードは定着しており、各フォーマットに対する公表された規格が存在し、興味のある読者は、関連する規格設定機関(たとえば、JEDEC)の公表文献を通じて、より知ることができる。

30

#### 【0025】

各メモリカードは、ホストデバイスまたはメモリカードコントローラと呼ばれることがある、ある種のデバイスで使用されるように構成され、そのデバイスは、デジタルカメラなどの携帯電子デバイスであるか、デスクトップコンピュータなどのより固定されたデバイスである。図1Dは、従来のホスト24に差し込まれた従来のカード22の簡略図を示す。詳細には、ホスト24は、標準的なサイズのカード22に適合するようなサイズの差し込み口26を含む。さらにホスト24は、カード22に信号を提供し、カード22から信号を受信するために電気接点32と相互運用するように構成された送信(TX)要素28と受信(RX)要素30とを含む。詳細には、カード22は、よく理解されるように、通信バスを生じさせるためにホスト24の電気接点32に電気的に結合する接点またはピン34を含む。カード22は、RX要素36およびTX要素38ならびにコンピュータ可読メモリ40をさらに含む。RX要素36およびTX要素38は、よく理解されるように、ホスト24から信号を受信し、ホスト24に信号を送るために、ピン34と相互運用する。

40

#### 【0026】

メモリカードの他のフォーマットに対して、同様の表が、容易に作成され得る。メモリカード規格は定着しているので、業界は規格化されたフォームファクタを開発する時間があった。定着したフォームファクタに従ってコネクタを製造することができる数多くの製造業者がある。同様に、ストレス耐性および屈曲耐性、ならびに他の疲労に関連する耐性などは、そのようなコネクタを使用する人々によってよく理解されている。メモリカード

50

仕様書には多くの特定の定義および要件が示され、業界は、これらの定義および要件を満たすことに慣れている。

#### 【0027】

本開示は、どの業界がメモリカード型コネクタを扱うかを、および詳細にはカード10、16、16'、22のハウジング(および対応する差し込み口26)を熟知していることを活用し、M-PHY規格対応のデバイスで使用するためにそのようなコネクタを再目的化することを提案する。詳細には、M-PHY規格対応のデバイスに既存のメモリカード型コネクタを使用することにより、業界がメモリカード型コネクタで有する専門知識および熟知していることのすべてが活用されて、M-PHY規格対応のデバイスでそれを使用することをすぐに受け入れられるようになる。定着した製造基盤により、M-PHY規格対応のデバイスに組み込むためのコネクタを容易に確保すること(securing)ができる。すなわち、M-PHY規格対応のデバイスへの参入準備のためにコネクタの許容できる製造業者を確保する際のラグタイムがほとんどまたは全くなくなることになり、既存の製造業者間の競争は、個々のコネクタのコストが妥当なものとなりそうであることを意味する。同様に、コネクタは現在、大量に作られているので、適切な量産効果(economies of scale)によりコストの削減となり得る。10

#### 【0028】

本開示の例示的な実施形態により、様々なカードフォーマットの多くが再目的化され得るが、本明細書に示されるのはほんの一部にすぎない。一般に、再目的化(repurposing)は、データ専用のピン、または予約されたピンを採用し、そのようなピンを使用して、差動M-PHYデータ信号を運ぶ差動データピンペアを形成する。クロック信号、電力信号、および挿入検出ピンが残され得る。この一般的な再目的化は、特に検討されているが、既存のフォームファクタのピンの目的を完全に入れ替える他の再目的化が考えられる。これに関連して、図2Aに関して、チャート42が提供されて、シリアル周辺機器インターフェース(SPI)モードの対応するSDカードコネクタへのM-PHY規格対応のピン名のマッピングを示す。詳細には、図2Aは、データ入力(DI)ライン、予備(RSV)ライン、データ出力(DO)ライン、および第2のRSVライン用のピンが、そのそれぞれのSPI信号使用から、対応するM-PHY信号使用に再目的化されている。したがって、本開示の例示的な実施形態では、データ入力に使用されていたDIピンは、TXDP信号に使用され、将来の規格開発に備えて予約されていた第1のRSVピンは、TXDN信号に使用され、データ出力信号に使用されていたDOピンは、RXDN信号に使用され、将来の規格開発に備えて予約されていた第2のRSVピンは、RXDP信号に使用される。20

#### 【0029】

図2Bに関して、チャート44が、対応するSDカードコネクタ信号(SPI動作なし)へのM-PHY規格対応のピン名のマッピングを示す。詳細には、図2Bは、DAT0ライン、DAT1ライン、DAT2ライン、およびDAT3ライン用のピンが、そのそれぞれのSD信号使用から、対応するM-PHY信号使用に再目的化されている。したがって、本開示の例示的な実施形態では、データ入力に使用されていたDAT0ピンは、TXDP信号に使用され、データ入力に使用されていたDAT1ピンは、TXDN信号に使用され、データ出力信号に使用されていたDAT2ピンは、RXDN信号に使用され、データ出力信号に使用されていたDAT3ピンは、RXDP信号に使用される。30

#### 【0030】

図2Cに関して、チャート46が、対応するUHS-IIカードコネクタ信号へのM-PHY規格対応のピン名のマッピングを示す。詳細には、図2Cは、D0+ライン、D0-ライン、D1+ライン、およびD1-ライン用のピンが、そのそれぞれのUHS-II信号使用から、対応するM-PHY信号使用に再目的化されている。したがって、本開示の例示的な実施形態では、データ入力に使用されていたD0+ピンは、TXDP信号に使用され、データ入力に使用されていたD0-ピンは、TXDN信号に使用され、データ出力信号に使用されていたD1+ピンは、RXDN信号に使用され、データ出力信号に使用されていたD0-ピンは、RXDP信号に使用される。ピン1、2、3、および5によって形成される第2のレーンはオプションであり、第2の差動レーンには4つの予約されたピンを使用することに注意されたい。40

#### 【0031】

10

20

30

40

50

図2Dに関して、チャート48は、M-PHY規格対応のピン名の、対応するMMCplusコネクタ信号へのマッピングを示す。詳細には、図2Dは、DAT0ラインからDAT7ライン用のピンが、そのそれぞれのMMC信号使用から、対応するM-PHY信号使用に再目的化されている。したがって、本開示の例示的な実施形態では、データ入力に使用されていたDAT0ピンおよびDAT1ピンは、TXDP0信号およびTXDN0信号に使用され、データ出力に使用されていたDAT2ピンおよびDAT3ピンは、RXDN0信号およびRXDP0信号に使用され、データ入力信号に使用されていたDAT4ピンおよびDAT5ピンは、TXDP1信号およびTXDN1信号に使用され、データ出力信号に使用されていたDAT6ピンおよびDAT7ピンは、RXDN1信号およびRXDP1信号に使用される。ピン10、11、12、および13によって形成される第2のレーンはオプションであり、実装はピン1、7、8、および9によって形成される1つの差動レーンだけを使用し得ることに注意されたい。10

### 【0032】

図2A～図2Dのチャートは、特定のメモリカードフォームファクタのための再割当てを知る際に役立つが、再目的化されたメモリカードフォームファクタを見ることもまた役立つ可能性がある。これに関連して、図2Eは、ピン12A'～ピン12I'(まとめてピン12')を有する、再目的化されたSD型メモリカードフォームファクタコネクタ10'の上面図を示す。ピン12'は、ハウジング14'内に配置されている。ハウジング14'は、図1Aのハウジング14と同一のサイズにされ、ピン12'は、図1Aのピン12と同じ場所に配置されている。しかしながら、上記の説明のように、ピン12の再目的化は、メモリカードフォームファクタコネクタ10'がM-PHYプロトコルにより動作できるようにする。さらに、実際のペアは、互いから離れている(たとえば、送信はメモリカードコネクタの一方の端部にあり、受信は反対の端部にある)が、ピンレイアウトおよび再目的化は、各差動ペアの2つのピンを互いに隣接して配置するように設計される(たとえば、ピン1およびピン9がTXDNおよびTXDP差動ペアを運び、ピン7およびピン8がRXDPおよびRXDN差動ペアを運ぶ)。ピン12'の再目的化は、以下のTABLE 4(表4)にまとめられている。20

### 【0033】

#### 【表4】

TABLE 4: M-PHY SD ピン割当て

| <u>SD ピン#</u> | <u>開示#</u> | <u>M-PHY 信号名</u> | <u>SD 説明</u> |

|---------------|------------|------------------|--------------|

| 1             | 12B'       | TXDP             | データ#3        |

| 2             | 12C'       | CMD(オプション)       | コマンド/応答      |

| 3             | 12D'       | グラウンド            | グラウンド        |

| 4             | 12E'       | 電源               | 電源電圧         |

| 5             | 12F'       | クロック(オプション)      | クロック         |

| 6             | 12G'       | グラウンド            | GND          |

| 7             | 12H'       | RXDP             | データ#0        |

| 8             | 12I'       | RXDN             | データ#1        |

| 9             | 12A'       | TXDN             | データ#2        |

30

40

### 【0034】

メモリカード規格およびプロトコルからのデータチャネルのこの再マッピングは、従来のメモリカード用の同じフォームファクタが、M-PHY対応のデバイスで使用されることを可能にする。さらに、業界の認知度および規格化されたメモリカードフォームファクタでメモリカードを作るための定着した製造プロセスを考えると、そのような規格化されたコネクタを実装するM-PHYデバイスのための容易に利用可能な製造チェーンがあるはずである。

### 【0035】

50

図3Aに関して、ピン要件を有する例示的な従来のM-PHY信号バスレイアウト50が提供される。すなわち、第1の電子デバイス52が、第2の電子デバイス54に接続される。第1の電子デバイス52は、(図6に関して以下に説明する)制御システムまたはプロセッサを含むことができ、これが適切なデバイスドライバを通じて、(本明細書ではインターフェースのための手段と呼ばれることもある)通信インターフェースの信号レーン56A、56Bを制御することができる。信号レーン56Aは、第1の電子デバイス52が、RXDPピン60AおよびRXDNピン60BへのTXDPピン58AおよびTXDNピン58Bを通じて第2の電子デバイス54にデータを送信するレーンである。同様に、第2の電子デバイス54は、RXDPピン64AおよびRXDNピン64BへのTXDPピン62AおよびTXDNピン62Bを通じて第1の電子デバイス52にデータを送信する。各電子デバイス52、54は、それぞれのレーン管理モジュール70A、70Bによって制御される、その独自のそれぞれの送信機M-TX66A、68Bと、受信機M-RX68A、66Bとを有する。レーン管理モジュール70A、70Bは、要求に応じてハードウェア、またはソフトウェア、またはこの2つの混合であってもよく、リンク78A、78Bを介して制御システムと通信することができる。ピン58A、58B、64A、64Bは、単一のMポート72にあってもよく、ピン60A、60B、62A、62Bは、それらが第2の異なるデバイス上にあることから、第2のMポート74にあると定義される。10

### 【0036】

引き続き図3Aに関して、レーン管理モジュール70Aは、周辺機器交換フォーマット(PIF: peripheral interchange format)リンク76Aを介して送信機66Aと、およびPIFリンク76Bを介して受信機68Aと、通信することができる。同様に、レーン管理モジュール70Bは、PIFリンク76Cを介して受信機66B、およびPIFリンク76Dを介して送信機68Bと通信することができる。レーン管理モジュール70A、70B、リンク78A、78B、送信機66A、68B、受信機66B、68A、およびPIFリンク76A～76Dは、M-PHY規格に示されており、興味のある読者は、そこでこれらの要素に関するより多くの情報を得られる。図のように、第1の電子デバイス52は、第2の電子デバイス54に直接接続されている。明示的に示していないが、当然のことながら、直接接続は、コネクタ、ケーブル、または組合せによって代替され得る。やはり、信号およびレーン管理要素は、M-PHY規格によって定義されるが、ピンおよび任意のコネクタの配置は、未定義のままである。しかしながら、図2A～図2Eに関して記載したように、メモリカード型コネクタは、メモリカードフォームファクタに物理的変更を求めるこなく、データピンをTXDP、TXDN、RXDN、RXDP信号バスにマップすることによって、再目的化され得る。これに関連して、メモリカードフォームファクタは、本明細書では接続する手段と呼ばれることがあってもよい。20

### 【0037】

ホストデバイス24に挿入された再目的化されたメモリカードフォームファクタコネクタ10'の例示的な簡略図が、図3Bに提供されている。詳細には、メモリカードフォームファクタコネクタ10'は、適切なピン58A、58B、64A、64B(図3A)を介してホストデバイス24の送信機M-TX66Aおよび受信機M-RX68Aからの出力に結合するピン12'を有する。メモリカードフォームファクタコネクタ10'のハウジング14'の内部には、受信機66Bおよび送信機68Bならびに従来のレーン管理70Bがある。30

### 【0038】

図4を見ると、フローチャートが提供され、M-PHY規格を使用して動作するように構成された、電子デバイス52などの第1の電子デバイスを、嵌合接続部(mated connection)、嵌合接続部を有するケーブルなどを介して電子デバイス54などの第2の電子デバイスに接続する方法を示している。最初に方法は、電子デバイスを提供し(ブロック100)、電子デバイスに複数のデータバスを形成する。各バスは、M-PHY規格に準拠している(ブロック102)。方法は、第1の電子デバイスに複数のピンを有するメモリカード型コネクタを提供する(ブロック104)。例示的な実施形態では、メモリカード型コネクタは、次の標準フォームファクタの1つに準拠する:SD、MMC、コンパクトフラッシュ(登録商標)、メモリスティック、SPI、xD、XQD、またはUHS。40

### 【0039】

50

引き続き図4に関して、方法は、メモリカード型フォームファクタ内のピンを、データバスに電気的に結合する(ブロック106)。例示的な実施形態では、ピンは、第1の送信ピンをM-PHY TXDPデータバスに電気的に結合し、第2の送信ピンをM-PHY TXDNデータバスに電気的に結合し、第1の受信ピンをM-PHY RXDNデータバスに電気的に結合し、第2の受信ピンをM-PHY RXDPデータバスに電気的に結合することによってマップされる。メモリカードコネクタフォームファクタが正常に4つのデータバスを持っていない場合、予約された接点が、その代わりに使用され得る。同様に、データバスが送信または受信データバスとして特に指定されていない場合、そのような指定が選択され得る。

#### 【0040】

引き続き図4に関して、およびデータバスがメモリカード型フォームファクタ内のそれぞれのピンに接続されて、第1の電子デバイスは、第2の電子デバイス(たとえば、第2のデバイス54)に接続され得る(ブロック108)。接続中またはその後すぐに、コネクタに関連する制御システムは、挿入検出を行う(ブロック110)および/または第2の電子デバイス54に電力を供給する(ブロック112)ことができる。

10

#### 【0041】

上記の説明は、メモリカード型フォームファクタ内のデータバスを再目的化することに焦点を当てたが、メモリカード型フォームファクタ内には、挿入検出および/または電力供給などの他の目的に使用され得る他のピンがある。たとえば、ほとんどのメモリカードは、電源ピンを含む。電源ピンの存在は、挿入検出を可能にし、第2の電子デバイス54に電力を供給する能力を与える。挿入検出により、第1の電子デバイス52は、データを送るまたは第2の電子デバイス54からのデータをリッスンすることができます許容できるかを知ることができる。同様に、第2の電子デバイス54は、第1の電子デバイス52が接続されたことを検出するはずである。挿入検出を通して他の利点も実現される可能性があり、本開示はこれに限るものではない。同様に、第2の電子デバイス54に電力を提供することにより、設計者は第2の電子デバイス54に電源コードまたは代替電源を提供する必要を回避することができる。

20

#### 【0042】

同じ一般的なフォームファクタを有するが、潜在的に異なるピン構成および使用を有する非常に多くのメモリカードが存在することから、ホストデバイスが、どのタイプのカードが挿入されたかを確かめるための何らかの方法が必要である。どのタイプのカードが挿入されたかを判断するための例示的なプロセス120が、図5に示されている。プロセス120は、ブロック122から始まり、第1の電子デバイス52は、差し込み口26内のカードにCMD5メッセージを送る(ブロック124)。ブロック126においてカードが応答する場合、第1の電子デバイス52は、差し込み口26内のカードが、セキュアデジタル入力出力(SDIO:secure digital input output)カードであると判断する(ブロック128)。しかしながら、ブロック126において応答が得られない場合、第1の電子デバイス52は、差し込み口26内のカードにCMD41メッセージを送る(ブロック130)。ブロック132においてカードが応答する場合、第1の電子デバイス52は、差し込み口26内のカードが、SDカードであると判断する(ブロック134)。しかしながら、ブロック132において応答が得られない場合、第1の電子デバイス52は、差し込み口26内のカードにCMD1メッセージを送る(ブロック136)。

30

#### 【0043】

引き続き図5に関して、ブロック138においてカードが応答する場合、第1の電子デバイス52は、差し込み口26内のカードが、MMCであると判断する(ブロック140)。しかしながら、ブロック138において応答が得られない場合、第1の電子デバイス52は、差し込み口26内のカードは、M-PHYプロトコルに従って動作していると推論し、M-PHYインターフェースに変え、カードにアクセスしようと試みる(ブロック142)。ブロック144において差し込み口26内のカードが応答する場合、ホストデバイス52は、差し込み口26内のカードが、M-PHY対応のデバイスであると判断する(ブロック146)。差し込み口26内のカードが依然として応答しない場合、プロセスはエラーを生成する(ブロック148)。

40

#### 【0044】

50

プロセス120は、差し込み口26に挿入されたカードが特定のタイプのカードであったかどうかを判断するための特定のコマンドについて検討し、説明しているが、当然のことながら、これらのカードタイプの各々に対する規格は、複数の一意のコマンド(すなわち、その規格に対してのみ存在し、他の規格には対応するコマンドがないコマンド(たとえば、SDに対してのみ存在するが、MMC、UHSなどに対しては存在しないコマンド))を有する。したがって、本開示の範囲を逸脱することなくどのカードタイプが挿入されているかについて判断する助けとなるように他のコマンドが使用され得る。

#### 【0045】

上記の説明は、メモリカードフォームファクタ内のピンを再目的化することに焦点を当てたが、本開示はこれに限らない。さらに、本開示は、メモリカードフォームファクタと併せてユニバーサルフラッシュストレージ(UFS:Universal Flash Storage)ストレージシステムを使用することを考える。UFSは従来、コンピューティングデバイスのボードにはんだ付けされたフラッシュメモリなどの固定メモリユニットに対してのみ提案されていることに注意されたい。参照によってその全体をこれにより組み込まれている、2011年10月12日公表のYuping ChungによるJEDEC公表UFS PHY and UNIPRO(登録商標)から明らかであるように、UFSは、M-PHYプロトコルと強く結びついている。ChungはM-PHY物理層を通して実装されるUFSを検討するが、Chungは、取り外し可能なメモリカードでUFSを使用すること、または上述のように標準化されたコネクタを介してM-PHYを使用して、メモリカードと通信することを検討しない。本開示は、既存のUFS機能を、取り外し可能なメモリカードコネクタに使用可能にすること、容易に利用可能なカードフォームファクタを使用すること、および本明細書に開示する再目的化技法によって、これを拡張することを考える。

#### 【0046】

本開示は、様々なメモリカード規格からM-PHY使用へ特定のピンを再目的化することに焦点を当てているが、メモリカードフォームファクタ上のいかなるピンも、送信機および受信機差動ペアを保持するように再目的化され得ることに注意されたい。設計の選択の問題として、M-PHY使用下で送信機および受信機差動ペアとして働くようにメモリカードフォームファクタからのデータピンを再目的化することの方がより理にかなっている。同様に、多くの場合、M-PHY使用において他のメモリカードフォームファクタピンの目的を保つことは理にかなっている。たとえば、グラウンド接続をグラウンド接続として保つことは理にかなっている。同様に、電源ピンとして指定されているピンは、M-PHYシステムにおいて電源ピンとして保たれ得る。ピン機能のそのような保存は、相互運用性を促進し、1つのシステムに詳しい設計者が再目的化されたシステムにおけるピンレイアウトに容易に適応することを可能にする。SDおよびMMCplusのみが明確に示されているが、それによって示される再目的化の概念は、コンパクトフラッシュ(登録商標)(IおよびII)、セキュアデジタル(SD)(SD、miniSD、microSD、SDHC、miniSDHC、microSDHC、SDXC)、メモリスティック(スタンダード、Pro、Pro Duo、Pro-HG Duo、Micro(M2)、xC)、MultiMediaCard(MMC)(MMC、RS-MMC、MMCmobile、MMCplus、MMCmicro、eMMC)、シリアル周辺機器インターフェース(SPI)、xD(スタンダード、Type M、Type H、Type M+)、XQD、およびウルトラハイスピード(UHS:Ultra High Speed)(IおよびII)などの、様々な他のメモリカードコネクタに適用可能であることは、繰り返して述べる価値がある。

#### 【0047】

補足説明として、共有クロックの使用は、(既存のクロックピンを使用して、またはクロック信号を運ぶように再目的化された異なるピンを使用して)行われ得る。共有クロックの使用は、M-PHYタイプIIの利用を可能にし、UFSがクロック信号を必要とするので、(M-PHYタイプIはクロックを必要としないが)M-PHYタイプIを使用するUFSにも合致する。

#### 【0048】

図示していないが代替的実施形態では、メモリは、TXDP/TXDNペアのみを必要とする書き込み専用メモリであってもよく、したがってデータ伝送に2つのピンしか必要とされないことになる。そのような利用の例示的な状況は、監視局、センサアレイ(sensory array)、または遠隔測定システムが、データをメモリに書き込むが、これを決して読み返さない。

10

20

30

40

50

い(たとえば、監視者、ロケット、気象観測気球、航空機ブラックボックスなどに書き込まれる)ことであろう。

#### 【0049】

本明細書に開示される実施形態により、メモリカードフォームファクタインターフェースを使用するM-PHY通信プロトコルの運用、ならびに関連するデバイス、システム、および方法は、任意のプロセッサベースのデバイスにおいて提供され得る、またはこれに統合され得る。例は、セットトップボックス、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、固定位置データユニット、モバイル位置データユニット、携帯電話、セルラ電話またはスマートフォン、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、およびポータブルデジタルビデオプレーヤを含むが、これらに限らない。10

#### 【0050】

これに関連して、図6は、図2A～図2Dのマッピング(または、本明細書に開示する他の概念に合致する他のマッピング)を適用してメモリカード型コネクタを使用することができるプロセッサベースのシステム170の例を示す。コントローラ200が、図のようにレーン管理モジュール70Aと相互運用する。図6のために、メモリカード型コネクタは、コネクタ202と呼ぶ。この例では、プロセッサベースのシステム170は、1つまたは複数の中央処理装置(CPU)172を含み、各CPUが1つまたは複数のプロセッサ174を含んでいる。CPU172は、マスターデバイスであってもよい。CPU172は、一時的に記憶されたデータへの高速アクセスのためにプロセッサ174に結合されたキャッシュメモリ176を有することができる。CPU172は、システムバス180に結合され、プロセッサベースのシステム170に含まれるマスターデバイスおよびスレーブデバイスを相互結合することができる。システムバス180は、バス相互接続であってよい。よく知られているように、CPU172は、システムバス180を通じてアドレス、制御、およびデータ情報を交換することによって、これらの他のデバイスと通信する。たとえば、CPU172は、スレーブデバイスの一例として、メモリコントローラ168(N)にバストランザクション要求を通信することができる。図6には示していないが、複数のシステムバス180が設けられることができ、各システムバス180が異なる構造(fabric)を構成する。2030

#### 【0051】

他のマスターデバイスおよびスレーブデバイスが、システムバス180に接続され得る。図6に示すように、これらのデバイスは、例として、メモリシステム182、1つまたは複数の入力デバイス184、1つまたは複数の出力デバイス186、1つまたは複数のネットワークインターフェースデバイス188、および1つまたは複数のディスプレイコントローラ190を含むことができる。入力デバイス184は、入力キー、スイッチ、音声プロセッサなどを含む、ただしこれらに限らない、いかなるタイプの入力デバイスも含むことができる。出力デバイス186は、オーディオ、ビデオ、他の視覚的表示器などを含む、ただしこれらに限らない、いかなるタイプの出力デバイスも含むことができる。ネットワークインターフェースデバイス188は、ネットワーク192へのおよびネットワーク192からのデータの交換を可能にするように構成されたいかなるデバイスでもあり得る。ネットワーク192は、有線またはワイヤレスネットワーク、プライベートまたはパブリックネットワーク、ローカルエリアネットワーク(LAN)、ワイドローカルエリアネットワーク(WLAN)、およびインターネットを含む、ただしこれらに限らない、いかなるタイプのネットワークでもあり得る。ネットワークインターフェースデバイス188は、所望のいかなるタイプの通信プロトコルもサポートするように構成され得る。メモリシステム182は、1つまたは複数のメモリユニット193(0～N)を含むことができる。アービタは、システムバス180と、たとえばメモリシステム182に設けられたメモリユニット193(0～N)など、システムバス180に結合されたマスターデバイスおよびスレーブデバイスとの間に設けられ得る。40

#### 【0052】

CPU172はまた、システムバス180を介してディスプレイコントローラ190にアクセスして、1つまたは複数のディスプレイ194に送られる情報を制御するように構成することもできる。ディスプレイコントローラ190は、1つまたは複数のビデオプロセッサ196を介して表示されるようにディスプレイ194に情報を送り、1つまたは複数のビデオプロセッサ196は、表示される情報を処理して、ディスプレイ194に適したフォーマットにする。ディスプレイ194は、陰極線管(CRT)、液晶ディスプレイ(LCD)、プラズマディスプレイなどを含む、ただしこれに限らない、いかなるタイプのディスプレイも含むことができる。

#### 【 0 0 5 3 】

CPU172およびディスプレイコントローラ190は、システムバス180を通じてアービタへのメモリアクセス要求を行うためのマスターデバイスとして働くことができる。CPU172およびディスプレイコントローラ190内の様々なスレッドが、アービタへの要求を行うことができる。10

#### 【 0 0 5 4 】

本明細書に開示する実施形態に関連して説明する様々な例示的論理ブロック、モジュール、回路、およびアルゴリズムは、電子ハードウェア、メモリにもしくは別のコンピュータ可読媒体に記憶され、プロセッサもしくは他の処理デバイスによって実行される命令、または両方の組合せとして実装され得ることは、当業者にはさらに理解されよう。本明細書に記載するアービタ、マスターデバイス、およびスレーブデバイスは、例として、いかなる回路、ハードウェアコンポーネント、集積回路(IC)、またはICチップにおいても、使用され得る。本明細書に開示するメモリは、いかなるタイプおよびサイズのメモリであってもよく、所望のいかなるタイプの情報も記憶するように構成され得る。このような互換性をわかりやすく説明するために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップを、概してその機能に関して上述した。そのような機能がいかにして実装されるかは、システム全体に課される特定の用途、設計選択、および/または設計制約によって決まる。当業者は、特定の用途ごとに様々な方法で、記載した機能を実装することができるが、そのような実装の決定は、本開示の範囲からの逸脱を生じさせると解釈されるべきではない。20

#### 【 0 0 5 5 】

本明細書に開示する実施形態と関連して説明する様々な例示的論理ブロック、モジュール、および回路は、プロセッサ、デジタル信号プロセッサ(DSP)、特定用途用集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブルロジックデバイス、個別のゲートもしくはトランジスタロジック、個別のハードウェアコンポーネント、または本明細書に記載した機能を行うように設計されたこれらの任意の組合せを用いて、実装または実行され得る。プロセッサは、マイクロプロセッサとすることができるが、代替的にプロセッサは、いかなる従来のプロセッサ、コントローラ、マイクロコントローラ、または状態機械とすることもできる。プロセッサは、たとえばDSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと連結した1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成など、コンピューティングデバイスの組合せとしても実装され得る。30

#### 【 0 0 5 6 】

本明細書に開示する実施形態は、ハードウェアにおいて、およびハードウェアに記憶されている命令において具体化されることが可能であり、たとえば、ランダムアクセスメモリ(RAM)、フラッシュメモリ、リードオンリメモリ(ROM)、電気的プログラム可能ROM(EPRO:Electrically Programmable ROM)、電気的消去可能プログラム可能ROM(EEPROM:Electrically Erasable Programmable ROM)、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られているその他の形式のコンピュータ可読媒体に、常駐することが可能である。プロセッサが記憶媒体から情報を読み取ること、および記憶媒体に情報を書き込むことができるように、例示的記憶媒体がプロセッサに結合される。代替的に記憶媒体は、プロセッサと一体化され得る。プロセッサおよび記憶媒体は、ASIC内に存在し得る。ASICは、遠隔局に存在し得る。代替的にプロセッサおよび記憶媒体は、遠4050

隔局、基地局、またはサーバに個別構成要素として存在し得る。

**【0057】**

本明細書の例示的な実施形態のいずれかに記載する動作ステップは、例および説明を提供するために記載されていることにも注意されたい。記載する動作は、例示の順序以外の数多くの異なる順序で行われ得る。さらに、単一の動作ステップに記載する動作が、実際にはいくつかの異なるステップで行われ得る。その上、例示的な実施形態に記載される1つまたは複数の動作ステップは、結合され得る。フローチャート図に示す動作ステップは、当業者には容易にわかるように、数多くの異なる変更の影響を受ける可能性がある。情報および信号は、多種多様な技術および技法のいずれかを使用して表され得ることもまた、当業者には理解されよう。たとえば、上記の説明全体を通して参照され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁性粒子、光場もしくは光粒子、またはその任意の組合せによって表され得る。

**【0058】**

本開示についての前述の説明は、当業者が本開示を作成または利用することができるよう<sup>10</sup>に提供する。本開示への様々な変更形態が当業者には容易に理解されることになり、本明細書で規定する包括的な原理は、本開示の趣旨または範囲から逸脱することなく他の変形形態に適用され得る。したがって、本開示は、本明細書に記載する例および設計に限定されるものではなく、本明細書で開示する原理および新規の特徴に合致する最も広い範囲を与えられるべきである。

**【符号の説明】**

**【0059】**

|    |                |    |

|----|----------------|----|

| 10 | SDカード          | 30 |

| 12 | ピン             |    |

| 14 | ハウジング          |    |

| 16 | マルチメディアカード     |    |

| 18 | ピン             |    |

| 20 | ハウジング          |    |

| 22 | 従来のカード         |    |

| 24 | ホスト            |    |

| 26 | 差し込み口          |    |

| 28 | 送信要素           |    |

| 30 | 受信要素           |    |

| 32 | 電気接点           |    |

| 34 | ピン             |    |

| 36 | 受信要素           |    |

| 38 | 送信要素           |    |

| 40 | コンピュータ可読メモリ    |    |

| 50 | M-PHY信号バスレイアウト | 40 |

| 52 | 電子デバイス         |    |

| 54 | 電子デバイス         |    |

| 56 | 信号レーン          |    |

| 58 | ピン             |    |

| 60 | ピン             |    |

| 62 | ピン             |    |

| 64 | ピン             |    |

| 66 | 送信機、受信機        |    |

| 68 | 送信機、受信機        |    |

| 70 | レーン管理モジュール     |    |

| 72 | Mポート           | 50 |

- 74 Mポート

76 周辺機器交換フォーマット(PIF)リンク

78 リンク

172 中央処理装置(CPU)

174 プロセッサ

176 キャッシュメモリ

180 システムバス

182 メモリシステム

184 入力デバイス

186 出力デバイス

188 ネットワークインターフェースデバイス

190 ディスプレイコントローラ

192 ネットワーク

193 メモリユニット

194 ディスプレイ

196 ビデオプロセッサ

200 コントローラ

202 コネクタ 10

【図 1 A】

FIG. 1A

PRIOR ART

【図 1 C】

FIG. 1C

PRIOR ART

【図 1 B】

FIG. 1B

PRIOR ART

【図 1 D】

FIG. 1D

PRIOR ART

【図 2 A】

42

| UHS-II |       | M-PHY                |                           |

|--------|-------|----------------------|---------------------------|

| ピン番号   | ピン名   | マスター/ホスト側<br>レガシーモード | スレーブ/<br>デバイス側<br>レガシーモード |

| 1      | RSV   | TXDP1                | RXDP1                     |

| 2      | RSV   | TXDN1                | RXDN1                     |

| 3      | RSV   | RXDN1                | TXDN1                     |

| 4      | VDD1  | 電源(オフショット)           | 電源(オフショット)                |

| 5      | RSV   | TXDP1                | RXDP1                     |

| 6      | RSV   | クロック入力               | クロック(オフショット)              |

| 7      | RCLK< | クロック入力               | クロック(オフショット)              |

| 8      | RCLK> | クロック入力               | クロック(オフショット)              |

| 9      | RSV   | レガシーモード              | レガシーモード                   |

| 10     | VSS3  | グランド                 | グランド(オフショット)              |

| 11     | D0+   | 出力データ                | 入力データ                     |

| 12     | D0-   | 出力データ                | 入力データ                     |

| 13     | VSS4  | グランド                 | グランド(オフショット)              |

| 14     | VDD4  | 電源                   | 電源(オフショット)                |

| 15     | D1-   | 入力データ                | 出力データ                     |

| 16     | D1+   | 入力データ                | 出力データ                     |

| 17     | VSS5  | グランド                 | グランド(オフショット)              |

【図 2 B】

44

| SD SPI |      | M-PHY           |                        |

|--------|------|-----------------|------------------------|

| ピン番号   | ピン名  | マスター/ホスト側<br>役割 | スレーブ/<br>デバイス側<br>役割   |

| 1      | CS   | チップ選択           | ホットプラグ存在検出             |

| 2      | DI   | データ出力           | TXDP                   |

| 3      | VSS  | グランド            | グランド(オプション)グランド(オプション) |

| 4      | VDD  | 電源              | 電源(オプション)              |

| 5      | SCLK | クロック            | クロック(オプション)            |

| 6      | VSS2 | グランド            | グランド(オプション)グランド(オプション) |

| 7      | DO   | データ入力           | TXDP                   |

| 8      | RSV  | 予備              | RXDN                   |

| 9      | RSV  | 予備              | RXDN                   |

【図 2 C】

46

| MMC Plus |      | M-PHY                |                      |

|----------|------|----------------------|----------------------|

| ピン番号     | ピン名  | マスター/ホスト側<br>データビット3 | マスター/ホスト側<br>データビット3 |

| 1        | DAT3 | 電源/デバイス側<br>役割       | RXDP0                |

| 2        | CMD  | コマンド応答               | コマンド(オプション)          |

| 3        | VSS  | グランド                 | グランド(オプション)          |

| 4        | VDD  | 電源電圧                 | 電源(オプション)            |

| 5        | CLK  | クロック                 | クロック(オプション)          |

| 6        | VSS  | グランド                 | グランド(オプション)          |

| 7        | DAT0 | データビット0              | TXDP0                |

| 8        | DAT1 | データビット1              | TXDN0                |

| 9        | DAT2 | データビット2              | RXDN0                |

| 10       | DAT4 | データビット4              | TXDP1                |

| 11       | DAT5 | データビット5              | TXDN1                |

| 12       | DAT6 | データビット6              | RXDN1                |

| 13       | DAT7 | データビット7              | TXDP1                |

【図 2 D】

48

| SD   |         | M-PHY           |                        |

|------|---------|-----------------|------------------------|

| ピン番号 | ピン名     | マスター/ホスト側<br>役割 | スレーブ/<br>デバイス側<br>役割   |

| 1    | CD/DAT3 | カード検出           | データ#3                  |

| 2    | CMD     | コマンド            | 応答                     |

| 3    | VSS1    | グランド            | グランド(オプション)グランド(オプション) |

| 4    | VDD     | 電源              | 電源(オプション)              |

| 5    | CLK     | クロック            | クロック(オプション)            |

| 6    | VSS2    | グランド            | グランド(オプション)グランド(オプション) |

| 7    | DAT0    | データ#0           | TXDP                   |

| 8    | DAT1    | データ#1           | RXDN                   |

| 9    | DAT2    | データ#2           | RXDN                   |

【図2E】

【図3A】

【図3B】

【図4】

【図5】

【図6】

---

フロントページの続き

(31)優先権主張番号 14/267,983

(32)優先日 平成26年5月2日(2014.5.2)

(33)優先権主張国 米国(US)

早期審査対象出願

(72)発明者 ヨーラム・リモニ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 甲斐 哲雄

(56)参考文献 特開2003-281477(JP,A)

特表2013-505507(JP,A)

米国特許第7664902(US,B1)

(58)調査した分野(Int.Cl., DB名)

G 06 K 7 / 00 - 7 / 14

G 06 F 13 / 20 - 13 / 42