(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 602 06 232 T2 2006.06.22**

(12)

## Übersetzung der europäischen Patentschrift

(97) **EP 1 298 443 B1**

(51) Int Cl.<sup>8</sup>: **G01R 31/319 (2006.01)**

(21) Deutsches Aktenzeichen: **602 06 232.2**

(96) Europäisches Aktenzeichen: **02 016 652.6**

(96) Europäischer Anmeldetag: **25.07.2002**

(97) Erstveröffentlichung durch das EPA: **02.04.2003**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **21.09.2005**

(47) Veröffentlichungstag im Patentblatt: **22.06.2006**

(30) Unionspriorität:

**967443** 28.09.2001 US

(84) Benannte Vertragsstaaten:

**DE, GB**

(73) Patentinhaber:

**Agilent Technologies, Inc., Palo Alto, Calif., US**

(72) Erfinder:

**Karlquist, Richard K., Cupertino, California 95014, US**

(74) Vertreter:

**BOEHMERT & BOEHMERT, 80336 München**

(54) Bezeichnung: **Schaltung und Methode zum Regeln einer Taktverschiebung in einem Kommunikationssystem**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****HINTERGRUND DER ERFINDUNG****Technisches Gebiet der Erfindung**

**[0001]** Die vorliegende Erfindung betrifft das Einstellen des Timings innerhalb eines Kommunikationssystems, insbesondere das Einstellen des Taktzeitintervalls zwischen Vorrichtungen innerhalb des Kommunikationssystems.

**Beschreibung verwandten Stands der Technik**

**[0002]** Die Druckschrift US 6,239,629 betrifft ein System zum Signalvergleich, welches ermittelt, ob ein Datensignal nahe bei den Übergängen seines Taktsignals Übergänge aufweist, wodurch mögliche Fehler beim Abtasten des Datensignals auftreten können. Das System zum Signalvergleich umfaßt eine Vielzahl von Latches, die ein erstes Signal und ein zweites Signal empfangen und die einen jeweiligen Wert des ersten Signals abhängig von einem Übergang des zweiten Signals übertragen. Ein Verzögerungsmechanismus verzögert den Übergang des zweiten Signals bevor der Übergang von den Latches empfangen wird, so daß der Übergang um verschiedene Beiträge relativ zu jedem Latch verzögert ist. Ein Rückkopplungsmechanismus empfängt die von den Latches übermittelten Werte und ermittelt, ob diese Werte in logischer Hinsicht äquivalent sind. Daraufhin überträgt der Rückkopplungsmechanismus ein Rückkopplungssignal in Reaktion auf die Ermittlung, daß sich einer der Werte logisch von einem anderen der Werte unterscheidet.

**[0003]** Die Druckschrift US 4,550,405 betrifft einen Schaltkreis zum Einstellen des Timings einer elektrischen Impulsflanke, wobei der Schaltkreis ein oder mehrere Elemente zum Entfernen des Taktversatzes (deskew element) umfaßt. In jedem Element zum Entfernen des Taktversatzes wird ein Impulszug durch einen Invertierer geleitet. Die Abfallgeschwindigkeit der Impulsflanken an der Ausgangsleitung des Invertierers wird von einer Kapazität und einer einstellbaren Stromsenke gesteuert, die die Entladungsgeschwindigkeit der Ausgangskapazität bestimmen. Ausgehend von der Ausgangsleitung werden die Impulse zu einem weiteren Element zum Entfernen des Taktversatzes geleitet, welches die Impulse erneut invertiert und die vormals steigenden Impulsflanken verzögert. Jede Stromsenke kann unabhängig eingestellt werden, um bei steigenden und fallenden Flanken verschiedene Verzögerungen vorzusehen zu können.

**[0004]** Die Druckschrift US 5,856,753 betrifft eine analoge Vor-Ansteuereinheit und ein Anschlußfeld, sowie eine Zelle zum Einstellen des Tastverhältnisses, die vor der Vor-Ansteuereinheit und dem An-

schlußfeld vorgesehen ist. Die Vor-Ansteuereinheit und das Anschlußfeld können entweder in einem 3 Volt-Modus, einem 5 Volt-Modus oder einer dazwischenliegenden Spannung betrieben werden, wobei diese lediglich von der vorliegenden Stromversorgungsspannung abhängig ist. Es sind weder Konfigurationen während der Herstellung noch nach der Herstellung notwendig. Das Patent offenbart einen speziellen Vorspannungsschaltkreis, und die Herstellungsabweichungen abhängig von Vcc, der Temperatur und anderer Größen zu reduzieren. Eine Tastverhältniszelle erzeugt einen Intervall an Taktverhältnissen, wenn der Schaltkreis in einem Intervall zwischen 3 und 5 Volt betrieben wird.

**[0005]** Üblicherweise verwenden synchron getaktete Logiksysteme eine Timingmethodik, die erfordert, daß alle Logikelemente simultan oder zumindest mit einem zulässigen Taktversatz (clock skew) getaktet werden. Diese Methodik ist für Computer geeignet, in denen die gesamte Zentralverarbeitungseinheit in einem einzelnen integrierten Schaltkreis vorgesehen ist, so daß die Verzögerungen gut gesteuert werden können. Jedoch ist diese Methodik bei digitalen Kommunikationssystemen, die mit höheren Geschwindigkeiten betrieben werden, ineffektiv, beispielsweise bei Ethernet und faseroptischen Datenverbindungen. In diesen Systemen durchlaufen die Daten zahlreiche Datenverarbeitungskomponenten in einer zum Teil asynchronen Weise. Typischerweise umfassen Datenkommunikationskomponenten in diesen Systemen Multiplexer/Demultiplexer (die auch als Parallel/Seriellumsetzer bzw. Seriell-Parallelumsetzer bekannt sind), Fehlerkorrekturprozessoren und Protokoll- bzw. Format-Umwandler. In einigen digitalen Kommunikationssystemen können viele Takte zahlreiche Phasen zueinander aufweisen, und in vielen Fällen arbeiten die Takte mit verschiedenen ganzzähligen Vielfachen einer Taktfrequenz.

**[0006]** Ferner sind Verzögerungen in digitalen Kommunikationssystemen oft länger als Verzögerungen in traditionellen Systemen. Beispielsweise sind Verzögerungen in einigen digitalen Kommunikationssystemen hinsichtlich ihrer Länge ein Vielfaches von Taktperioden. Die Verzögerungen in digitalen Kommunikationssystemen sind oft länger als die Verzögerungen in traditionellen Systemen, da einige Datenverarbeitungsaufgaben bzw. -tasks zur Verarbeitung mehr als eine Taktperiode benötigen. Ferner sind diese Verzögerungen oft länger als die Verzögerungen in traditionellen Systemen, da die physikalische Länge der Übertragungsleitungen, welche die Komponenten zusammen verbinden, länger als die Übertragungsleitungen sind, die bei traditionellen Systemen verwendet werden. Es ist ersichtlich, daß längere Verzögerungen zu Schwierigkeiten bei der Datenübertragung zwischen den Komponenten in einem System führen können.

**[0007]** Ferner ergeben sich Schwierigkeiten beim Datentransfer zwischen Systemkomponenten in digitalen Kommunikationssystemen dadurch, daß viele Systemkomponenten interne Takte erzeugen, die mit einem extern zur Verfügung stehenden Takt hinsichtlich ihrer Phase verriegelt sind und nicht vorherbestimmbare Phasenverschiebungen zu dem extern zur Verfügung stehenden Takt aufweisen können. Oftmals gibt es keine bestimmte Beziehung hinsichtlich des Timings zwischen dem Zeitpunkt, zu dem die Eingangsdaten abgetastet werden, dem Zeitpunkt, zu dem die Ausgangsdaten der Komponente einen Übergang aufweisen, und dem Auftreten der Auslöseflanke des(der) internen Taks(e). Daher sollte das Timing innerhalb von Systemen, beispielsweise digitale Kommunikationssysteme, so eingestellt werden, daß die Systemkomponenten die Daten zu dem geeigneten Zeitpunkt abtasten.

**[0008]** Ansätze zur besseren Steuerung des Timings zwischen Komponenten in einem System waren nur beschränkt erfolgreich. Einige Systeme und Testausrüstungen legen ein sich wiederholendes Testmuster an eine Systemkomponente an, während die Ausgabe der Systemkomponente mit einem Hochgeschwindigkeits-Abtastungsozilloskop beobachtet wird. Während dieser Zeit kann die Phase des Takteingangs der Systemkomponente manuell eingestellt werden, bis die zu untersuchende Systemkomponente die korrekten Ausgangsdaten erzeugt, basierend auf den Daten, die in die Komponente hineingeführt werden. Das Oszilloskop kann viele verschiedene Taktphasen effektiv abtasten, so daß üblicherweise keine Probleme bei der Synchronisierung des Oszilloskops mit den Ausgangsdaten bestehen. Jedoch gibt es zwei wichtige Beschränkungen einer derartigen Anwendung eines Oszilloskops. Zunächst beschränkt das Oszilloskop die maximale Datenrate des Systems auf die maximale Datenrate, die mit dem schnellsten zur Verfügung stehenden Oszilloskop beobachtbar ist. Als zweites ist es bei Systemen, die außerhalb von Labors verwendet werden, ökonomisch nicht sinnvoll, ein kostenaufwendiges Oszilloskop in das System zum Zwecke des Einstellens des Taktversatzes am jeweiligen Einsatzort einzubauen.

**[0009]** Ein früherer Ansatz, die Nachteile des oben beschriebenen Oszilloskop-basierten Systems zu umgehen, umfaßt das Messen der Bitfehlerrate der Datenausgabe, die von der zu überprüfenden Systemkomponente erzeugt wird, während der Taktversatz variiert wird, um den Taktversatz mit der geringsten Bitfehlerrate zu wählen. Jedoch ist dieser Ansatz problematisch, da üblicherweise in einem Bitfehlertest eine Anzahl hintereinander geschalteter Systemkomponenten verwendet werden, die alle den richtigen Taktversatz haben müssen, um an dem Ausgang der Kette hintereinandergeschalteter Komponenten die richtigen Daten zu erhalten. Dieser Ansatz, die Bitfehlerrate eines Systems zu messen, er-

fordert daher eine multidimensionale Suche, um zu einem verwertbaren Satz Taktversätze zu kommen. Ferner ist die Beziehung zwischen der Bitfehlerrate und dem Taktversatz derart, daß die Identifizierung einer minimalen Bitfehlerrate oft schwierig ist.

**[0010]** Ausgehend von dem obenstehenden besteht ein Bedarf an einem einfachen und akkuraten Verfahren zum Einstellen des Taktversatzes oder eines anderen Timings innerhalb eines Kommunikationssystems.

#### ABRISS DER ERFINDUNG

**[0011]** Die vorliegende Erfindung sieht ein Verfahren zum Einstellen von Taktsignalen nach Anspruch 1 und einen Schaltkreis zum Einstellen von Taktsignalen nach Anspruch 5 vor.

**[0012]** Die Ausführungen der vorliegenden Erfindung überwinden die Nachteile bekannter Techniken zum Einstellen des Timings und befriedigen einen bedeutenden Bedarf an einem Verfahren und einer Vorrichtung zum relativ schnellen und akkurate Einstellen von Taktignalen für Vorrichtungen in einem System. Zunächst wird ein Taktversatz (clock skew) und/oder die Phase zwischen dem Takteingang einer zu überprüfenden Vorrichtung und einem Takteingang einer Datenquelle auf 180 Grad eingestellt. Danach wird der 180 Grad-Taktversatz um ungefähr 180 Grad verschoben, um einen Taktversatz (clock skew) von ungefähr 0 Grad zu erreichen. Insbesondere wird der Taktversatz auf ungefähr 180 Grad eingestellt, indem an die zu überprüfende Vorrichtung ein Eingangsdatenmuster mit einer vorbestimmten Gleichanteil-Offsetspannung angelegt wird und eine Gleichanteil-Offsetspannung des Ausgangs der zu überprüfenden Vorrichtung bei einer Vielzahl verschiedener Taktversatz-Beträge gemessen wird. Der Taktversatz, der den größten Betrag des Gleichanteil-Offsets am Datenausgang der zu überprüfenden Vorrichtung erzeugt, ist der Taktversatz mit 180 Grad.

**[0013]** Beispielhafte Schaltungen zur Umsetzung des Einstellens und Verschiebens des Taktversatzes umfassen eine Phasenschieberschaltung, die mit einem Takteingang einer der zu überprüfenden Vorrichtungen und mit der Datenquelle verbunden ist, sowie einen Spannungsmeßschaltkreis, der mit dem Ausgang der zu überprüfenden Vorrichtung verbunden ist.

**[0014]** Ferner sieht die Erfindung Ausführungen mit anderen Merkmalen und Vorteilen vor, die zu den oben genannten hinzutreten oder statt deren vorgesehen werden. Viele dieser Merkmale und Vorteile ergeben sich aus der folgenden Beschreibung unter Bezugnahme auf die folgenden Zeichnungen.

## KURZBESCHREIBUNG DER ZEICHNUNGEN

[0015] Unter Bezugnahme auf die folgende detaillierte Beschreibung in Kombination mit den beigefügten Zeichnungen erlaubt sich ein weitergehendes vollständigeres Verständnis des Verfahrens und der Vorrichtung der vorliegenden Erfindung. In den Zeichnungen zeigen:

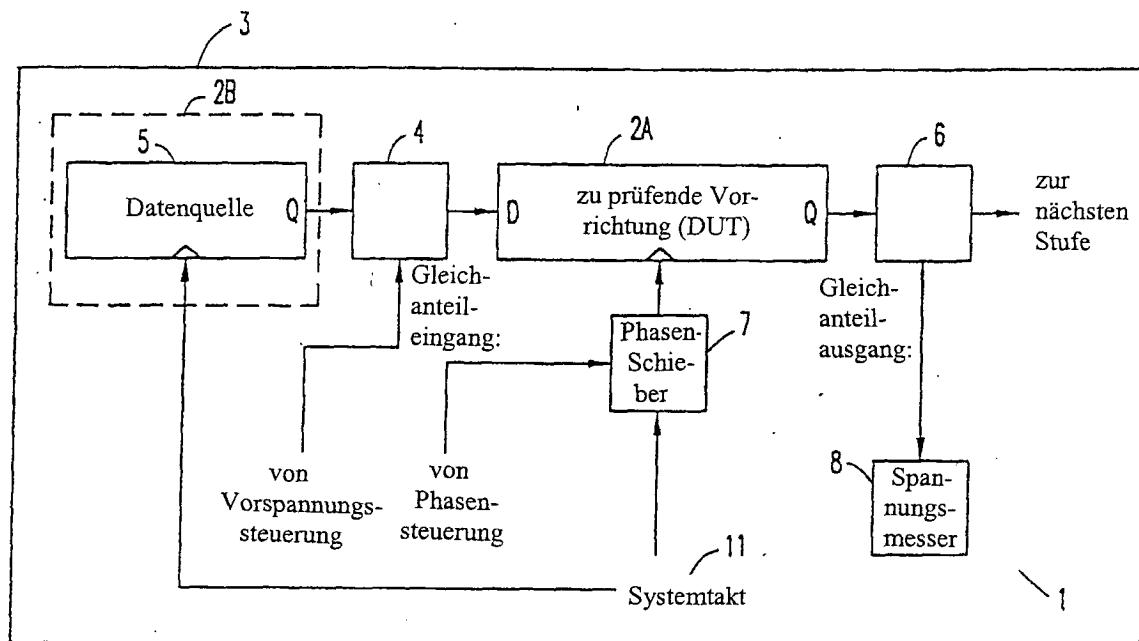

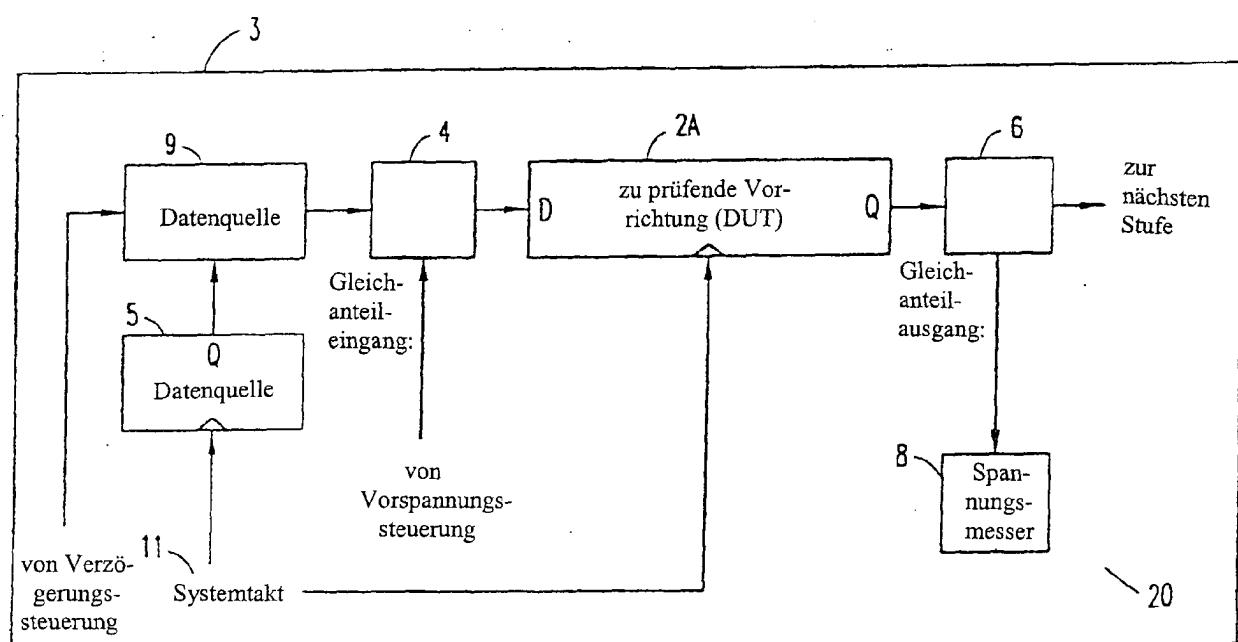

[0016] [Fig. 1](#) ein Blockdiagramm eines Abschnitts eines Kommunikationssystems gemäß einer beispielhaften Ausführung der vorliegenden Erfindung;

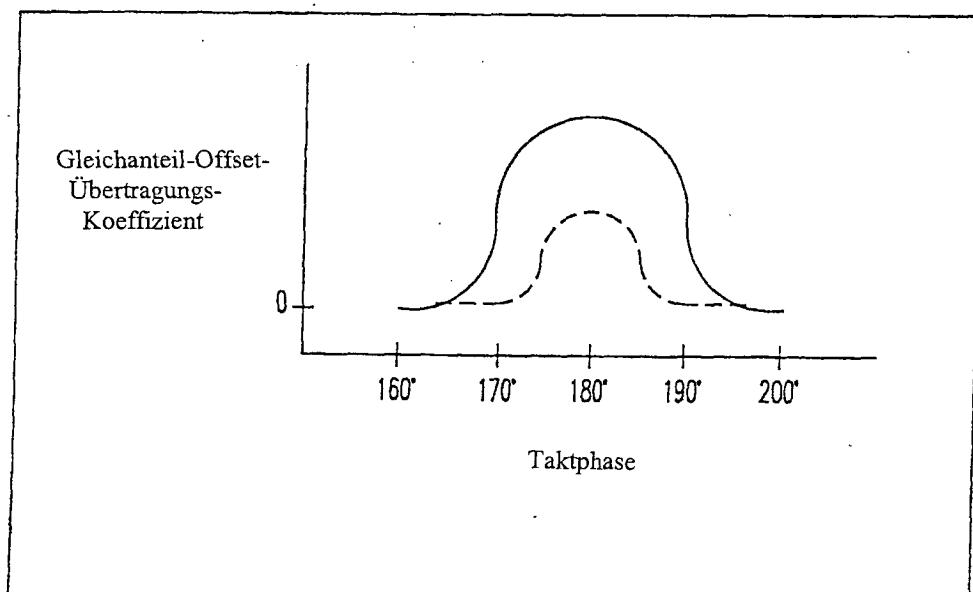

[0017] [Fig. 2](#) eine Darstellung einer Gleichanteil-Offset-Übergangskurve, die dem Abschnitt des Kommunikationssystems von [Fig. 1](#) entspricht;

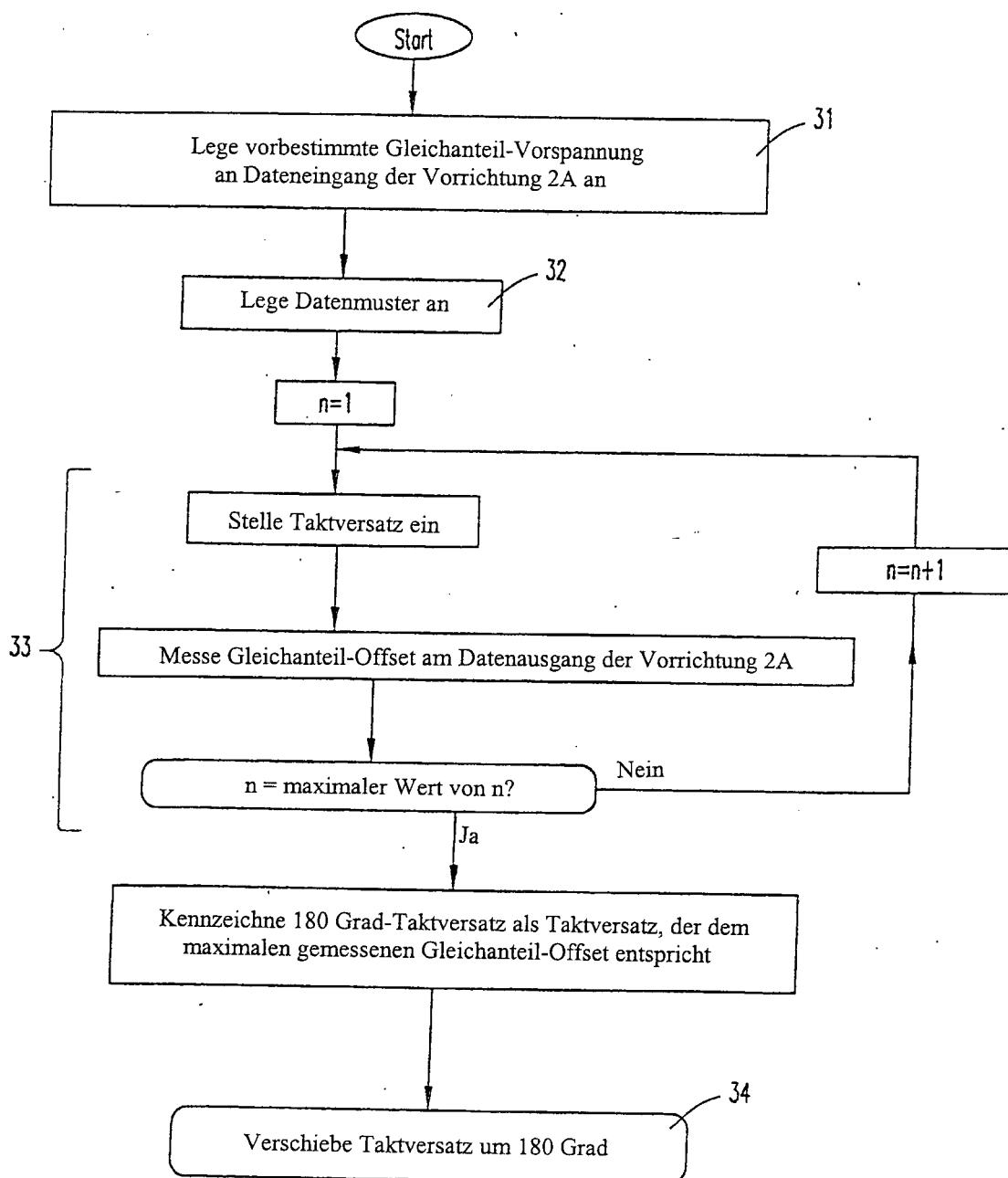

[0018] [Fig. 3](#) ein Flußdiagramm, das den Betrieb des Abschnitts des Kommunikationssystems von [Fig. 1](#) darstellt;

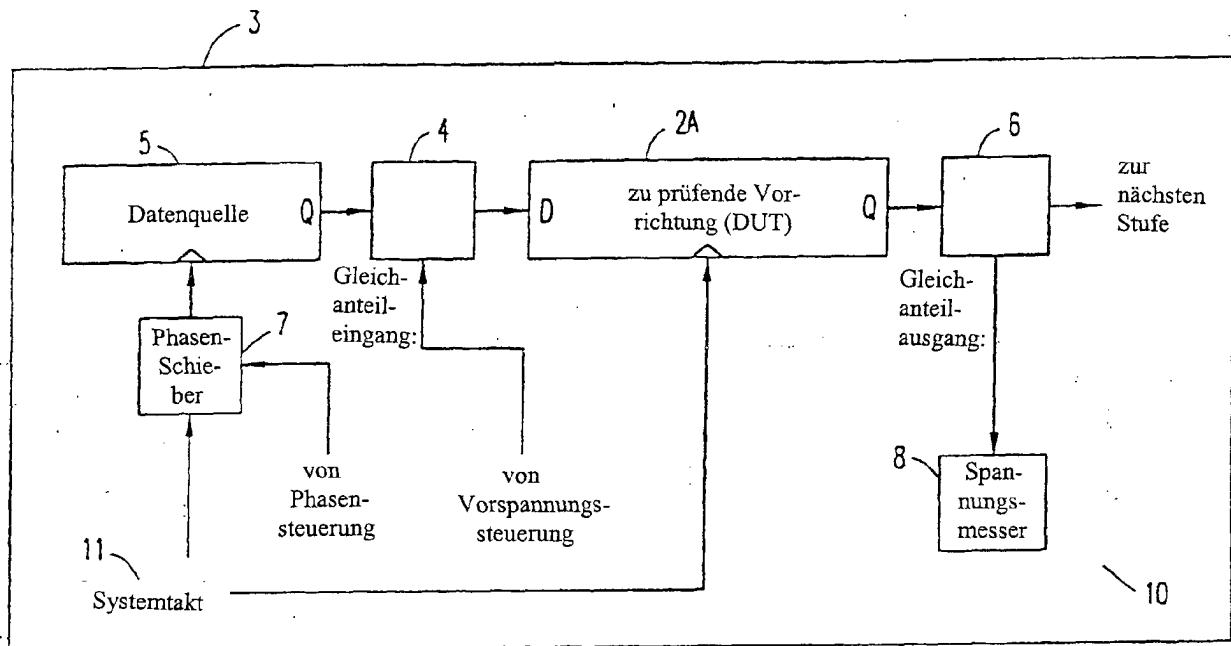

[0019] [Fig. 4](#) ein Blockdiagramm eines Abschnitts eines Kommunikationssystems gemäß einer weiteren beispielhaften Ausführung der vorliegenden Erfindung;

[0020] [Fig. 5](#) ein Blockdiagramm eines Abschnitts eines Kommunikationssystems gemäß einer weiteren beispielhaften Ausführung der vorliegenden Erfindung; und

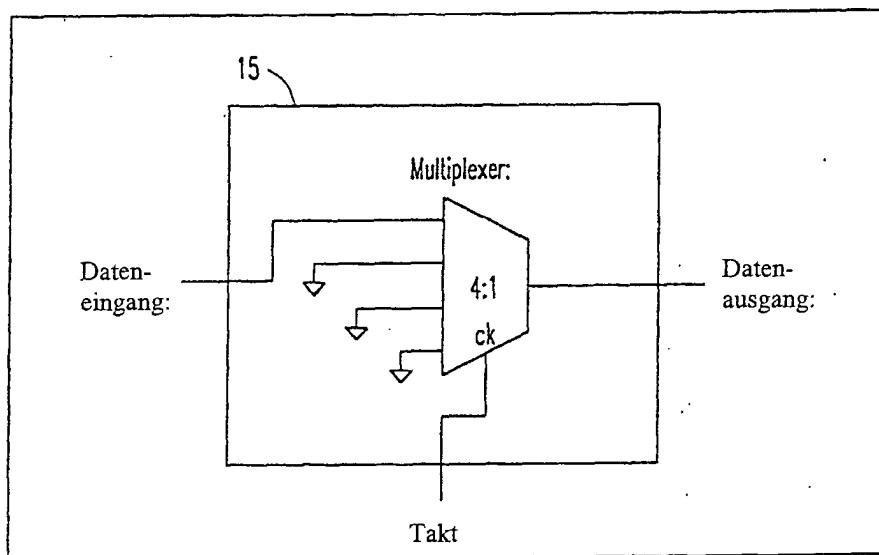

[0021] [Fig. 6](#) ein Diagramm einer zu überprüfenden Vorrichtung mit mehreren Eingängen gemäß einer weiteren beispielhaften Ausführung der vorliegenden Erfindung.

## DETAILLIERTE BESCHREIBUNG DER BEISPIELHAFTEN AUSFÜHRUNGEN DER VORLIEGENDEN ERFINDUNG

[0022] Bezugnehmend auf [Fig. 1](#) ist ein Schaltkreis zum Einstellen des Taktversatzes (clock skew) zwischen den Vorrichtungen **2A** und **2B** in einem System **3**, beispielsweise ein Kommunikationssystem, gemäß einer beispielhaften Ausführung der vorliegenden Erfindung dargestellt. Der Schaltkreis **1** ermöglicht es, daß die Takteingänge der Vorrichtungen **2A** und **2B** des Systems **3** präzise zueinander eingestellt werden können, so daß der Taktversatz zwischen den Takteingängen der Vorrichtungen **2A** und **2B** optimiert wird.

[0023] Es ist ersichtlich, daß die Vorrichtungen **2A** und **2B** Funktionsblöcke oder andere Komponenten innerhalb eines synchronen Systems **3** sein können. Es ist ersichtlich, daß das System **3** in jedem System vorliegen kann, in dem der Taktversatz relativ schwierig genau zu steuern ist. Aus Gründen der Einfachheit wird jede Vorrichtung **2A** und **2B** mit einem einzelnen Takteingang, Dateneingang und Datenausgang be-

schrieben. Es ist jedoch ersichtlich, daß die Vorrichtungen **2** jeweils mehrere Takt- und Dateneingänge sowie Datenausgänge umfassen können.

[0024] Bezugnehmend auf den in [Fig. 1](#) dargestellten Abschnitt des Systems **3** empfängt die zu überprüfende Vorrichtung **2A** (device under test, DUT) Daten von der Vorrichtung **2B** und insbesondere von einer Datenquelle **5** der Vorrichtung **2B**. Gemäß einer beispielhaften Ausführung der vorliegenden Erfindung umfaßt der Schaltkreis **1** einen Vorspannungsschaltkreis bzw. Bias-Schaltkreis **4**, der zwischen einem Datenausgang und einer Datenquelle **5** und einem Dateneingang der Einrichtung **2A** angeschlossen ist. Der Vorspannungsschaltkreis **4**, der üblicherweise als Pegelschieber (level shifter) bezeichnet wird, umfaßt einen ersten Eingang, um ein Eingangssignal zu empfangen, beispielsweise ein Signal mit geringem oder keinem Gleichanteil-Offset, einen zweiten Eingang zum Empfangen einer Gleichanteil-Vorspannung, sowie einen Ausgang. Der Vorspannungsschaltkreis **4** kombiniert die Gleichanteil-Vorspannung, die an seinem zweiten Eingang auftritt, mit dem Signal, das in dem ersten Eingang auftritt, um ein kombiniertes Signal zu erhalten, und legt das kombinierte Signal an den Ausgang des Vorspannungsschaltkreises **4** an. Auf diese Weise wird der Vorspannungsschaltkreis **4** verwendet, um den Gleichanteil-Offset des Datensignals, welches an die Vorrichtung **2A** angelegt wird, zu variieren.

[0025] Es ist ersichtlich, daß die Vorrichtung **2B** eine Gleichanteil-Vorspannung dem digitalen Signal intern hinzufügen kann, das von der Vorrichtung **2B** erzeugt wird. In diesem Fall wäre der Vorspannungsschaltkreis **4** nicht notwendig.

[0026] Üblicherweise umfassen Systeme ein gemeinsames Taktsignal, beispielsweise einen Systemtakt, der mit dem Takteingang jeder Systemvorrichtung in dem System direkt verbunden ist. Gemäß der beispielhaften Ausführung der vorliegenden Erfindung, die in [Fig. 1](#) dargestellt ist, umfaßt jedoch der Schaltkreis **1** einen Phasenschiebeschaltkreis **7**, der zwischen einem Systemtakt **11** des Systems **3** und dem Takteingang der Vorrichtung **2A** angeschlossen ist. Der Phasenschiebeschaltkreis **7** umfaßt einen Takteingang und einen Steuereingang. Das von dem Phasenschiebeschaltkreis erzeugte Ausgangssignal wird relativ zu seinem Takteingang um einen Betrag phasenverschoben, der von dem Steuereingang abhängt. Dadurch, daß die Datenquelle **5** mit dem Systemtakt **11** direkt verbunden ist, und daß die Vorrichtung **2A** über den Phasenschiebeschaltkreis **7** mit dem Systemtakt **11** verbunden ist, kann der Taktversatz zwischen den Eingangstakten der Vorrichtung **2B** und Vorrichtung **2A** auf den gewünschten Betrag eingestellt werden.

[0027] Über einen Teilerschaltkreis **6** ist ein Span-

nungsmesser **8** mit dem Ausgang der Vorrichtung **2A** verbunden. Der Spannungsmesser **8** mißt die Gleichspannung, die an dem Ausgang der Vorrichtung **2A** erscheint und gibt diese visuell an. Der Teilerschaltkreis **6** ermöglicht es, daß der Spannungsmesser **8** das Gleichspannungsniveau gemessen werden kann, das an dem Ausgang der Vorrichtung **2A** erscheint.

**[0028]** Die Vorgehensweise der vorliegenden Erfindung zum Optimieren des Taktversatzes zwischen der Vorrichtung **2B** und der Vorrichtung **2A** in dem System **3**, ist im allgemeinen eine zweistufige Vorgehensweise. Zunächst wird der Taktversatz zwischen der Vorrichtung **2A** und der Vorrichtung **2B** auf ungefähr 180 Grad eingestellt. Als zweites wird der 180 Grad-Taktversatz daraufhin um ungefähr 180 Grad verschoben, um den Taktversatz zwischen den Vorrichtungen **2A** und **2B** auf ungefähr Null Grad einzustellen.

**[0029]** Der Grund für diese Vorgehensweise ergibt sich wie folgt. Ein Gleichanteil-Offset, der dem Eingangsdatenmuster hinzugefügt wird, das an die Vorrichtung **2A** angelegt wird, kann verwendet werden, um zu ermitteln, wenn der Taktversatz zwischen den Vorrichtungen **2A** und **2B** 180 Grad beträgt. Zunächst soll angenommen werden, daß die Datenquelle **5** ein Eingangsdatenmuster an die Vorrichtung **2A** anlegt, das ein bestimmtes Tastverhältnis aufweist, das heißt, ein bestimmtes Verhältnis logischer Eins-Datenbits zu logischen Null-Datenbits. Wenn der Taktversatz zwischen dem Takteingang der Vorrichtung **2A** und dem Takteingang der Datenquelle **5** optimiert ist (das heißt, bei einem Taktversatz, so daß die Eingangsdaten für die Vorrichtung **2A** fehlerfrei interpretiert werden), hat der Ausgang der Vorrichtung **2A** das gleiche Tastverhältnis wie das Eingangsdatenmuster. Die Gleichanteilkomponente der Ausgabe der Vorrichtung **2A** entspricht daher dem bestimmten Tastverhältnis des Eingangsdatenmusters, das der Vorrichtung **2A** zugeführt wird.

**[0030]** Wenn der Taktversatz zwischen den Vorrichtungen **2A** und **2B** Null Grad ist oder in der Nähe davon liegt, wird die Fähigkeit der Vorrichtung **2A**, das Eingangsdatenmuster richtig zu interpretieren, von einem wesentlichen Betrag eines Gleichanteil-Offsets nicht beeinflußt, der dem Eingangsdatenmuster zugefügt wird, welches an die Vorrichtung **2A** angelegt wird. Die Vorrichtung **2A** kann trotzdem das Eingangsdatenmuster bei ausreichender Toleranzspanne interpretieren. Das Tastverhältnis des von Vorrichtung **2A** erzeugten Ausgangsdatenmusters ist daher das gleiche wie das Tastverhältnis des Eingangsdatenmusters, das an die Vorrichtung **2A** angelegt wird. Daher ändert ein Gleichanteil-Offset, welches dem Eingangsdatenmuster hinzugefügt wird, die Gleichanteilkomponente des Ausgangsdatenmusters nicht. Folglich wird bei relativ geringen Taktversatz-Beträgen

nur wenig oder kein Gleichanteil-Offset von dem Eingangsdatenmuster, das an Vorrichtung **2A** angelegt wird, an das von diesem erzeugten Ausgangsdatenmuster übertragen.

**[0031]** Wenn der Taktversatz zwischen den Vorrichtungen **2A** und **2B** 180 Grad beträgt, fällt die Vorrichtung **2A** bei jeder Triggerflanke des Takteingangs der Vorrichtung **2A** idealerweise eine Zufallsentscheidung. Die zufälligen Entscheidungen betreffen die Frage, ob das Eingangsdatenmuster als auszugebende Datenbits (bereits von der Vorrichtung **2A** vorgesehen) oder als hereinkommende Datenbits (welche am Dateneingang der Vorrichtung **2A** erscheinen) zu interpretieren sind. Wenn keine weiteren Bedingungen das Timing bzw. die zeitliche Steuerung oder die Signalpegel der Daten- und Takteingänge der Vorrichtung **2A** beeinflussen, ergibt sich die gleiche Wahrscheinlichkeit, für die Interpretation eines Datenbits mit einer logischen Null als Datenbit mit logischer Eins, wie für die Interpretation eines Datenbits mit einer logischen Eins als Datenbit mit logischer Null. Folglich hat das Tastverhältnis des von der Vorrichtung **2A** erzeugten Ausgangsdatenmusters idealerweise das gleiche Tastverhältnis wie das Eingangsdatenmuster, das an die Vorrichtung **2A** angelegt wird. Ausgehend hiervon ist ersichtlich, daß das an dem Ausgang der Vorrichtung **2A** erscheinende Datenmuster sehr eng dem Tastverhältnis des Eingangsdatenmusters entspricht, welches an die Vorrichtung **2A** angelegt wird, wenn zwischen den Vorrichtungen **2A** und **2B** ein Tastverhältnis von 180 Grad herrscht.

**[0032]** Wenn jedoch ein Gleichanteil-Offset dem an die Vorrichtung **2A** angelegten Eingangsdatenmuster hinzugefügt wird, während der Taktversatz bei 180 Grad verbleibt, ändern sich die von der Vorrichtung **2A** getroffenen Entscheidungen. Die Wahrscheinlichkeit, daß die Vorrichtung **2A** ein Datenbit als logische Null interpretiert, ist dann nicht mehr die gleiche, wie die Wahrscheinlichkeit, daß die Vorrichtung **2A** ein solches als logische Eins interpretiert. Beispielsweise erhöht ein Gleichanteil-Offset, das dem Eingangsdatenmuster hinzugefügt wird und welches in die Richtung eines logischen Eins-Wertes geht, die Wahrscheinlichkeit, daß die Vorrichtung **2A** die Datenbits als logische Eins interpretiert. Die meisten der Eingangsdatenbits des Eingangsdatenmusters, welche einen Übergang haben, werden als Datenbit mit logischer Eins interpretiert. Die dadurch erhöhte Wahrscheinlichkeit einer Interpretation als Datenbit mit logischer Eins erhöht das Tastverhältnis des Datenausgangsmusters, welches von der Vorrichtung **2A** erzeugt wird, auf näherungsweise 100%, und erhöht dadurch die Gleichanteilkomponente des Datenausgangsmusters.

**[0033]** In gleicher Weise erhöht ein in die Richtung eines logischen Null-Werts gehendes Gleichan-

teil-Offset die Wahrscheinlichkeit, daß die Vorrichtung **2A** Datenbits als logische Null interpretiert. Die meisten der Eingangsdatenbits des Eingangsdatenmusters, das einen Übergang aufweist, werden als Datenbit mit logischer Null interpretiert. Die Erhöhung der Interpretation als Datenbit mit logischer Null verringert das Tastverhältnis des von der Vorrichtung **2A** erzeugten Ausgangsdatenmusters auf ungefähr 0% und verringert daher die Gleichanteilkomponente des von der Vorrichtung **2A** erzeugten Datenausgangsmusters.

**[0034]** Ausgehend hiervon ist ersichtlich, daß bei einem Taktversatz von 180 Grad der Gleichanteil in dem Eingangsdatenmuster, das an der Vorrichtung **2A** angelegt wird, eine Änderung in dem Gleichanteil-Offset in dem Ausgangsdatenmuster verursacht, welches von der Vorrichtung **2A** erzeugt wird. Mit anderen Worten besteht eine relativ beträchtliche Übertragung des Gleichanteil-Offsets von dem Eingangsdatenmuster, das an die Vorrichtung **2A** angelegt wird, zu dem Ausgangsdatenmuster, das von diesem erzeugt wird, wenn der Taktversatz zwischen der Vorrichtung **2A** und der Datenquelle **5** 180 Grad beträgt.

**[0035]** Für Taktversatzwerte, die ungefähr, jedoch nicht genau 180 Grad betragen, beispielsweise Taktversätze zwischen 160 Grad und 180 Grad, beeinflußt ein Gleichanteil-Offset, das dem Eingangsdatenmuster der Vorrichtung **2A** hinzugefügt wird, den Gleichanteil-Offset in dem Ausgangsdatenmuster der Vorrichtung **2A**. Jedoch ist dieser Effekt geringer, wenn der Taktversatz 180 Grad beträgt. Bei Taktversatzwerten, die nahe bei 180 Grad liegen, erzeugen Rauschen und Jitter eine statistische Verteilung des Ausgangsdatenmusters, das von der Vorrichtung **2A** erzeugt wird, um das Tastverhältnis des Ausgangsdatenmusters zu ändern, im Vergleich zu dem Tastverhältnis des Ausgangsdatenmusters bei einem Taktversatz von 180 Grad. Wenn das Eingangsdatenmuster eine Gleichanteil-Vorspannung in der Richtung einer logischen Eins hat und ein Tastverhältnis von 50% aufweist, liegt das Tastverhältnis des von der Vorrichtung **2A** erzeugten Ausgangsdatenmusters zwischen 50% und 100%. Wenn das Eingangsdatenmuster eine Gleichanteil-Vorspannung in der Richtung einer logischen Null und ein Tastverhältnis von 50% aufweist, liegt das Tastverhältnis des von der Vorrichtung **2A** erzeugten Ausgangsdatenmusters zwischen 0% und 50%. Die sich ergebende Gleichanteil-Vorspannung in dem Ausgangsdatenmuster hat daher einen geringeren Betrag bei Taktversatzbeträgen, die nahe bei 180 Grad liegen, als die Gleichanteil-Vorspannung in dem Ausgangsdatenmuster bei einem Taktversatz von 180 Grad. Bei Taktversatzbeträgen, die nahe bei 180 Grad liegen, ist die Übertragung des Gleichanteil-Offsets von dem Dateneingang der Vorrichtung **2A** zu dessen Datenausgang daher geringer als die Übertragung des Gleichanteil-Offsets bei einem 180 Grad-Taktversatz.

**[0036]** In der [Fig. 2](#) ist eine Kurve dargestellt, welche das Verhältnis zwischen dem Taktversatz und der Übertragung des Gleichanteil-Offsets von dem Dateneingang der Vorrichtung **2A** an dessen Datenausgang wiedergibt. Die Kurve der [Fig. 2](#) zeigt die auf das Gleichanteil-Offset bezogene Übertragungseigenschaft der Vorrichtung **2A** über einen Bereich von Taktversatzwerten hinweg. Es ist verständlich, daß die Form der Kurve der [Fig. 2](#) teilweise von den Eigenschaften der einzelnen Hardware in dem System **3** abhängen kann.

**[0037]** Der Betrag des Gleichanteil-Offsets, der dem Eingangsdatenmuster der Vorrichtung **2A** hinzugefügt wird, beeinflußt die Form der Kurve der [Fig. 2](#). Insbesondere verbreitert das Erhöhen des Betrags des Gleichanteil-Offsets des an die Vorrichtung **2A** angelegten Eingangsdatenmusters die Kurve von [Fig. 2](#), und das Verringern des Betrags des Gleichanteil-Offsets des Eingangsdatenmusters verschmäler die Kurve. Die [Fig. 2](#) zeigt das Verhältnis des Taktversatzes zu der Übertragung eines Gleichanteil-Offsets bei einem ersten Gleichanteil-Offsetwert (in durchgezogenen Linien) und bei einem zweiten Gleichanteil-Offsetwert, der bezogen auf den ersten Gleichanteil-Offsetwert einen geringeren Betrag aufweist (in gestrichelten Linien).

**[0038]** Bezugnehmend auf die [Fig. 3](#) wird basierend auf dem Verhältnis zwischen dem Taktversatz und der Übertragung des Gleichanteil-Offsets von dem Dateneingang der Vorrichtung **2A** zu dessen Datenausgang der Betrieb des Schaltkreises **1** zur Optimierung des Taktversatzes zwischen der Vorrichtung **2A** und der Datenquelle **5** beschrieben. Zunächst wird bei Schritt **31** der Vorstellungsschaltkreis **4** manipuliert, so daß den Daten ein vorbestimmtes Gleichanteil-Offset hinzugefügt wird, die an den Dateneingang der Vorrichtung **2A** geliefert werden. Der Betrag des vorbestimmten Gleichanteil-Offsets wird derart gewählt, daß er groß genug ist, um einen meßbaren Gleichanteil-Offsetpegel von dem Dateneingang der Vorrichtung **2A** an dessen Datenausgang übertragen zu können, und daß dieser gleichzeitig klein genug ist, um das übertragene Gleichanteil-Offset mit einer Spitze bei einem Taktversatz von 180 Grad vorzusehen, anstatt die Spitze zu verbreitern und so die Spitze vergleichsweise ununterschreitbar zu machen.

**[0039]** Als nächstes wird bei Schritt **32** ein Datenmuster an die Vorrichtung **2A** angelegt. Das Datenmuster kann ein sich wiederholendes Datenmuster sein, so daß die Daten während des Betriebs zur Optimierung des Taktversatzes im wesentlichen kontinuierlich der Vorrichtung **2A** vorgesehen werden.

**[0040]** Der Taktversatz zwischen der Datenquelle **5** und der Vorrichtung **2A** wird daraufhin bei Schritt **33** auf ungefähr 180 Grad eingestellt. Das Einstellen des Taktversatzes wird ausgeführt, indem der Phasen-

schiebeschaltkreis 7 manipuliert bzw. verändert wird, um einen Taktversatz zwischen dem Takteingang der Vorrichtung 2A und dem Takteingang der Datenquelle 5 zu verändern und um den Gleichanteil-Offset in der von der **Fig. 2A** erzeugten Datenausgabe mittels Spannungsmesser 8 abzulesen. Das Verändern und Ablesen wird mehrere Male mit anderen Taktversatzbeträgen wiederholt. Das wiederholte Verändern und Lesen führt zur Identifikation einer Anzahl von Stellen in der in **Fig. 2** dargestellten Funktion, in der die Gleichanteil-Offsetspannung gegenüber der Taktphase aufgetragen ist. Die Taktversatzeinstellung, welche zu einer Gleichanteil-Offsetspannung in der Datenausgabe der Vorrichtung 2A mit dem größten Betrag führt, wird als 180 Grad-Taktversatz gekennzeichnet. Der 180 Grad-Taktversatz führt zu dem größten Gleichanteil-Offsetbetrag in dem Datenausgang aufgrund der Beziehung zwischen dem Taktversatz und der Übertragung des Gleichanteil-Offsets, wie in **Fig. 2** dargestellt ist.

**[0041]** Als nächstes wird daraufhin der 180 Grad-Taktversatz in Schritt 34 um ungefähr 180 Grad verschoben, um somit den Taktversatz zwischen der Datenquelle 5 und der Vorrichtung 2A auf ungefähr Null Grad einzustellen. Der 180 Grad-Taktversatz wird durch Manipulieren des Phasenschiebeschaltkreises 7 verschoben. Die Vorgehensweise zum Verschieben des Taktversatzes ist abhängig von den Merkmalen des Phasenschiebeschaltkreises 7 variabel. Wenn der Phasenschiebeschaltkreis 7 hinsichtlich der Beziehung zwischen Phasenverschiebung und Steuerspannung kalibriert wird, kann auf eine Kalibrierungstabelle Bezug genommen werden, um eine 180 Grad-Phasenverschiebung zu implementieren. Wenn andernfalls der Phasenschiebeschaltkreis linear ist, jedoch eine nicht bekannt Verstärkung (gain) aufweist, kann die Verstärkung ermittelt werden, indem zwei gegenüberliegende Taktversatzeinstellungen ermittelt werden, beispielsweise 180 Grad und -180 Grad. Die zwei gegenüberliegenden Taktversatzeinstellungen können beispielsweise mittels der oben beschriebenen Schritte 31-33 für jede benachbarte Taktversatzeinstellung erreicht werden. Da die zwei benachbarten Taktversatzeinstellungen ungefähr 360 Grad auseinanderliegen, ist die optimale Taktversatzeinstellung (das heißt, die Taktversatzeinstellung, die dazu führt, daß die Eingangsdaten der Vorrichtung 2A fehlerfrei interpretiert werden) der Mittelpunkt zwischen den benachbarten Taktversatzeinstellungen.

**[0042]** Es ist ersichtlich, daß der Taktversatz in dem Schritt 34 um einen Betrag verschoben werden kann, der sich von 180 Grad unterscheidet, um einen gewünschten Taktversatzbetrag zu erreichen, der sich von einem Taktversatz von Null Grad unterscheidet.

**[0043]** Es ist ersichtlich, daß der Phasenschiebeschaltkreis 7 an einer anderen Stelle im Schaltkreis 1

angeordnet sein kann, da der Phasenschiebeschaltkreis 7 in der **Fig. 1** einen Taktversatz zwischen dem Takteingang der Vorrichtung 2A und dem Takteingang der Datenquelle 5 (das heißt, der Systemtakt 11) vorsieht, während gewährleistet bleibt, daß zwischen der Vorrichtung 2A und der Datenquelle 5 ein Taktversatz vorliegt.

**[0044]** Die **Fig. 4** zeigt einen Schaltkreis 10 gemäß einer weiteren beispielhaften Ausführung der vorliegenden Erfindung. Der Phasenschiebeschaltkreis 7 des Schaltkreises 10 ist zwischen dem Systemtakt 11 und dem Takteingang der Datenquelle 5 angeordnet. Der Systemtakt 11 ist in dieser Ausführung direkt mit dem Takteingang der Vorrichtung 2A verbunden. Der Schaltkreis 10 kann verwendet werden, um den Taktversatz zwischen dem Takteingang der Vorrichtung 2A und dem Takteingang der Datenquelle 5 auf den optimalen Wert einzustellen. Die Vorgehensweise zum Einstellen des Taktversatzes auf den optimalen Wert ist im wesentlichen die gleiche, wie sie oben bezüglich Schaltkreis 1 der **Fig. 1** beschrieben wurde.

**[0045]** Die **Fig. 5** zeigt einen Schaltkreis 20 gemäß einer weiteren beispielhaften Ausführung der vorliegenden Erfindung. Anstatt einen Phasenschiebeschaltkreis 7 zu verwenden, um zu einem optimalen Taktversatz zwischen den Takteingängen der Vorrichtung 2A und der Datenquelle 5 zu gelangen, wird zwischen dem Datenausgang der Datenquelle 5 und dem Dateneingang des Vorspannungsschaltkreises 4 eine variable Verzögerungsschaltung 9 angeordnet. Der Systemtakt 11 ist direkt mit den Takteingängen der Vorrichtungen 2A und der Datenquelle 5 verbunden. Die variable Verzögerungsschaltung 9 kann gesteuert werden, um die Verzögerung zwischen dem Dateneingang der variablen Verzögerungsschaltung 9 und deren Datenausgang zu variieren. Durch die Veränderung der Verzögerung der Daten zwischen der Datenquelle 5 und der Vorrichtung 2A können Unterschiede bezüglich der Taktverzögerungen zwischen der Datenquelle 5 und der Vorrichtung 2A korrigiert und optimiert werden. Der Taktversatz wird durch Ausführen der oben genannten Schritte 31-34 wirksam optimiert, unter der Voraussetzung, daß die variable Verzögerungsschaltung 9 manipuliert wird, um die tatsächliche Taktversatzeinstellung auf ungefähr 180 Grad einzustellen, und um danach die 180 Grad-Taktversatzeinstellung um ungefähr 180 Grad zu verschieben.

**[0046]** Es ist ersichtlich, daß Ausführungen der vorliegenden Erfindung verwendet werden können, um das Takttiming zwischen Einrichtungen mit mehreren Eingängen innerhalb eines Systems zu optimieren. Die **Fig. 6** zeigt eine zu untersuchende Vorrichtung 15 (device under test, DUT) mit einer Vielzahl von Dateneingängen. Wenn die Dateneingänge der Vorrichtung 15 das gleiche Timing aufweisen, kann der gewünschte Taktversatz zwischen dem Takteingang

der Vorrichtung **15** und dem Takteingang der Datenquelle erreicht werden, indem alle Dateneingänge der Vorrichtung **15** bis auf einen auf einen statischen oder konstanten Logikpegel gesetzt werden, und indem an den einen Dateneingang ein Datenmuster angelegt wird. Wenn die Dateneingänge der Vorrichtung **15** nicht das gleiche Timing aufweisen, kann das Timing der verschiedenen Datenquellen, welche die Vorrichtung **15** mit Daten versorgen, auf die gewünschte oder optimale Einstellung eingestellt werden.

**[0047]** In der [Fig. 6](#) ist die Vorrichtung **15** nur der beispielhaften Darstellung wegen als Multiplexerschaltkreis dargestellt. Es ist ersichtlich, daß die Vorrichtung **15** jede beliebige getaktete Vorrichtung mit mehreren Eingängen sein kann.

**[0048]** Obwohl zahlreiche Ausführungen des Verfahrens, des Systems und der Vorrichtung der vorliegenden Erfindung in den beigefügten Zeichnungen und der obenstehenden detaillierten Beschreibung dargestellt wurden, ist ersichtlich, daß die Erfindung nicht auf die offensichtlichen Ausführungen beschränkt ist, sondern daß diese zahlreiche Neuanordnungen, Modifikationen und Substitutionen aufweisen kann, ohne das Gebiet der Erfindung zu verlassen, wie es durch die folgenden Ansprüche dargestellt und definiert ist.

### Patentansprüche

1. Verfahren zum Einstellen von Taktsignalen für eine Vorrichtung **(2A)** in einem System **(3)** umfassend:

Einstellen eines Taktversatzes zwischen einem Takteingang der Vorrichtung **(2A)** und einem Takteingang einer Datenquelle **(5)**, die Daten an die Vorrichtung **(2A)** liefert, auf ungefähr 180 Grad, so daß ein 180 Grad-Taktversatz erreicht wird;

Hinzufügen eines Gleichanteil-Offsets zu den Daten, die von der Datenquelle **(5)** vorgesehen werden; und Verschieben des 180 Grad-Taktversatzes um ungefähr 180 Grad.

2. Verfahren nach Anspruch 1, wobei:

der Schritt des Einstellens das Einstellen des Taktversatzes der Vorrichtung **(2A)** auf zwei einzelne Taktversatz-Beträge von ungefähr +180 Grad und -180 Grad umfaßt; und

der Schritt des Verschiebens das Verschieben des Taktversatzes von einem der zwei einzelnen Taktversatz-Beträge auf einen Taktversatz-Betrag umfaßt, der ungefähr in der Mitte zwischen den zwei einzelnen Taktversatz-Beträgen liegt.

3. Verfahren nach Anspruch 1, wobei der Schritt des Einstellens umfaßt:

anfängliches Einstellen des Gleichanteil-Offsets zu mindest eines Dateneingangs der Vorrichtung **(2A)**

auf ein vorbestimmtes Niveau;

Einstellen des Taktversatzes zwischen dem Takteingang der Vorrichtung **(2A)** und dem Takteingang der Datenquelle **(5)** auf ungefähr 180 Grad;

Anlegen eines Datenmusters an zumindest einen Dateneingang der Vorrichtung **(2A)**; Verändern des Taktversatzes;

Überwachen eines Datenausgangs der Vorrichtung **(2A)**; und

Identifizieren des 180 Grad-Taktversatzes als derjenige Taktversatz, welcher die einem maximalen Gleichanteil-Offset entspricht, der an dem Ausgang der Vorrichtung **(2A)** erscheint.

4. Verfahren nach Anspruch 1, wobei der Schritt des Einstellens umfaßt:

anfängliches Einstellen eines Gleichanteil-Offsets zumindest eines Dateneingangs der Vorrichtung **(2A)** auf ein anfängliches Niveau; und

Ermitteln eines Taktversatz-Betrags, der zu einem maximalen Gleichanteil-Offset in einen Datenausgang der Vorrichtung **(2A)** führt, wobei der Taktversatz-Betrag den 180 Grad-Taktversatz umfaßt.

5. Schaltkreis **(1)** zum Einstellen eines Taktsignals für eine Vorrichtung **(2A)** in einem System **(3)**, umfassend:

einen ersten Schaltkreis **(7, 9)**, zum selektiven Einstellen eines Taktversatzes zwischen einem Takteingang der Vorrichtung **(2A)** und einem Takteingang einer Datenquelle **(5)**, welche Daten an einem Dateneingang der Vorrichtung **(2A)** liefert;

einen zweiten Schaltkreis **(4)**, der mit einem Dateneingang der Vorrichtung **(2A)** verbunden ist, um den Gleichanteil-Offset für Signale vorzusehen, die an dem Dateneingang der Vorrichtung **(2A)** erscheinen; und

einen dritten Schaltkreis **(6)**, der mit einem Datenausgang der Vorrichtung **(2A)** verbunden ist, um einen Gleichanteil-Offset des Datenausgangs der Vorrichtung **(2A)** zu messen.

6. Vorrichtung nach Anspruch 5, wobei:

der erste Schaltkreis **(7, 9)** eine Verzögerung zwischen dem Takteingang der Vorrichtung **(2A)** und einem Ausgang der Datenquelle **(5)**, die Daten an die Vorrichtung **(2A)** liefert, selektiv einstellt.

7. Schaltkreis **(1)** nach Anspruch 6, wobei:

der erste Schaltkreis einen Verzögerungsschaltkreis **(9)** umfaßt, der einen ersten Eingang aufweist, welcher mit einem Datenausgang der Datenquelle **(5)** verbunden ist, sowie einen Ausgang aufweist, der mit dem ersten Eingang der Einrichtung **(2A)** verbunden ist, und wobei der erste Schaltkreis eingerichtet ist,

eine beliebige von einer Vielzahl von Verzögerungen zwischen einem Signal, das am Eingang des Verzögerungsschaltkreises **(9)** erscheint, und einem Signal, das an seinem Ausgang erscheint, vorzusehen.

8. Schaltkreis (1) nach Anspruch 5 oder 6, wobei:

der erste Eingang der Vorrichtung (2A) ein Dateneingang ist; und

der erste Ausgang der Datenquelle (5) ein Datenausgang ist.

9. Schaltkreis (1) nach Anspruch 5, 6, 7 oder 8,

wobei:

der zweite Schaltkreis (4) einen Schaltkreis umfaßt,

der eingerichtet ist, für den ersten Eingang der Vorrichtung (2A) einen Gleichanteil-Offset vorzusehen,

der einen beliebigen aus einer Vielzahl von Gleichanteil-Werten aufweist.

10. Schaltkreis (1) nach einem der Ansprüche 5 bis 9, wobei der dritte Schaltkreis umfaßt:

einen Signalaufteilungsschaltkreis (6) mit einem Eingang, der mit einem Datenausgang der Vorrichtung (2A) verbunden ist, und mit einem Ausgang, der eingerichtet ist, ein Signal vorzusehen, das einen Gleichanteil-Offset des Datenausgangs der Vorrichtung (2A) wiedergibt.

Es folgen 4 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6