(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-244788

(P2005-244788A)

(43) 公開日 平成17年9月8日(2005.9.8)

(51) Int.Cl.<sup>7</sup>

**H03K 19/0175**

**H03K 5/26**

**H03K 17/16**

**H03K 17/687**

**H03K 19/0948**

F 1

H03K 19/00

H03K 5/26

H03K 17/16

H03K 17/687

H04L 5/14

101S

G

P

L

テーマコード(参考)

5J039

5J055

5J056

5KO18

審査請求 未請求 請求項の数 8 O L (全 23 頁) 最終頁に続く

(21) 出願番号

特願2004-54179(P2004-54179)

(22) 出願日

平成16年2月27日(2004.2.27)

(71) 出願人

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人

弁理士 上柳 雅善

(74) 代理人

弁理士 藤綱 英吉

(74) 代理人

弁理士 須澤 修

(72) 発明者

笠井 重一

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 5J039 JJ08 JJ13 JJ14 KK01 KK09

KK10 KK20 MM10 NN01

最終頁に続く

(54) 【発明の名称】同時双方向送受信システム

## (57) 【要約】

【課題】送信側の出力回路から受信側の出力回路に流れ

る貫通電流を抑制することができ、低消費電力の同時双

方向送受信システムを得る。

【解決手段】第1及び第2の通信回路101A, 101Bを、伝送線路10を介して、雙方向にデータの送受信

が可能となるように接続し、第1及び第2の通信回路1

01A, 101Bの少なくとも一方は、自己がデータ送

信停止中であることを検出する自送信停止中検出手段1

5Aと、この自送信停止中検出手段15Aにより自己が

データ送信停止中であることを検出したとき、相手の出

力回路12Bから自己の出力回路12Aへ貫通電流が流

れることを防止する貫通電流抑制手段とを有している。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

出力信号を伝送線路を介して相手へ伝送する出力回路と、前記出力信号に応じた参照電位を発生する参照電位発生回路と、前記伝送線路に発生する自出力信号と相手から前記伝送線路へ出力され受信すべき受信信号との混合信号を受け、該混合信号と前記参照電位とを比較して入力信号を判別する入力回路とをそれぞれ有する第1及び第2の通信回路を、前記伝送線路を介して、双方向にデータの送受信が可能となるように接続され、前記第1及び第2の通信回路の少なくとも一方は、自己がデータ送信停止中であることを検出する自送信停止中検出手段と、該自送信停止中検出手段により自己がデータ送信停止中であることを検出したとき、相手の前記出力回路から自己の前記出力回路へ貫通電流が流れることを防止する貫通電流抑制手段とを有していることを特徴とする同時双方向送受信システム。

10

**【請求項 2】**

前記出力回路は、送信するデータに応じて前記出力信号を生成する出力信号生成部を有し、前記貫通電流抑制手段は、前記出力信号生成部に出力信号生成のための電位を供給する信号電位供給端子と前記出力信号生成部との間に設けられ、前記自送信停止中検出手段により自己がデータ送信停止中であることを検出したとき、ディゼーブル信号発生回路から入力されるディゼーブル信号によって、前記信号電位供給端子と前記出力信号生成部と間を電気的に開成状態とするスイッチング素子であることを特徴とする請求項1に記載の同時双方向送受信システム。

20

**【請求項 3】**

前記出力回路は、送信するデータに応じて前記出力信号を生成する出力信号生成部を有し、前記貫通電流抑制手段は、前記出力信号生成部と前記伝送線路との間に設けられ、前記自送信停止中検出手段により自己がデータ送信停止中であることを検出したとき、ディゼーブル信号発生回路から入力されるディゼーブル信号によって、前記出力信号生成部と前記伝送線路との間を電気的に開成状態とするスイッチング素子であることを特徴とする請求項1に記載の同時双方向送受信システム。

20

**【請求項 4】**

前記第1及び第2の通信回路の少なくとも一方は、相手がデータ送信停止中であることを検出する相手送信停止中検出手段と、該相手送信停止中検出手段により相手がデータ送信停止中であることを検出したときに、自出力信号のデータ転送速度を速くする転送速度増加手段とを備えていることを特徴とする請求項1から3のいずれか1項に記載の同時双方向送受信システム。

30

**【請求項 5】**

前記相手送信停止中検出手段は、自己がデータ送信中で、自己の送信データと前記混合信号とを逐次比較し、両者データが所定の判定数連続して一致したときに、相手が送信停止中であると判断することを特徴とする請求項4に記載の同時双方向送受信システム。

**【請求項 6】**

前記第1及び第2の通信回路の少なくとも一方は、前記入力信号との同期を取るために、同期周波数を漸次変化させながら同期する周波数を探す同期周波数検出手段と、相手がデータ送信停止中であることを検出する相手送信停止中検出手段と、該相手送信停止中検出手段により相手がデータ送信停止中となったことを検出したときに、前記同期周波数検出手段の同期周波数を変化させる動作を止める同期動作停止手段とを備えたことを特徴とする請求項1から5のいずれか1項に記載の同時双方向送受信システム。

40

**【請求項 7】**

前記同期周波数検出手段は、前記入力信号と前記同期周波数との位相差を検出する位相周波数比較器と、制御電圧を変化させ該制御電圧に基づいて前記同期周波数を変化させる電圧制御発振器と、前記位相周波数比較器と前記電圧制御発振器との間に設けられ前記位相周波数比較器の出力信号に基づいて前記電圧制御発振器から電流を入出力して前記制御電圧を変化させるチャージポンプ回路とを有し、前記同期動作停止手段は、相手送信中検

50

出手段及び前記自送信停止中検出手段により相手がデータ送信中で自己がデータ送信停止中であるときに、ディゼーブル信号発生回路から入力されるディゼーブル信号に基づいて、前記位相周波数比較器から前記チャージポンプ回路に入力される前記出力信号を消滅するように動作する論理素子であることを特徴とする請求項 6 に記載の同時双方向送受信システム。

#### 【請求項 8】

前記第 1 及び第 2 の通信回路の少なくとも一方は、前記入力信号との同期を取るために、前記同期周波数を漸次変化させながら同期する周波数を探す同期周波数検出手段と、相手がデータ送信停止中であることを検出する相手送信停止中検出手段と、該相手送信停止中検出手段により相手がデータ送信停止中となったことを検出したときに、前記同期周波数検出手段に前記自出力信号を送信するためのクロック信号を入力する入力切り替え手段とを備えたことを特徴とする請求項 1 から 6 のいずれか 1 項に記載の同時双方向送受信システム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

この発明は同時双方向送受信技術に関し、特に 2 個の第 1 及び第 2 の通信回路間を 1 本の伝送線路を用いて接続し同時に信号の送受信を行う同時双方向送受信システムに関する。

##### 【背景技術】

##### 【0002】

近年、伝送線路の両端に接続した 2 個の LSI チップにおいて、双方の LSI チップが同時に相手にデータを送信しても相手方で受信できるという技術が提案されている。たとえば、双方の送受信回路に、参照電位が異なる 2 つの入力バッファ（コンパレータ）を設け、この 2 つの入力バッファを共に動作させておき、自己の送信データに応じて後段のセレクタを切り替えることにより、いずれかの入力バッファを選択し、自己の送信データに応じた参照レベルで判定したデータを取り込むようにした同時双方向インターフェースが提案されている（例えば、特許文献 1 参照）。

##### 【0003】

また、同じように伝送線路の両端に送受信回路を接続した装置であって、制御信号により、入出力回路内の出力回路の出力抵抗値が伝送線路の特性インピーダンスと等しくなるよう制御し、さらに、伝送線路上の信号を差動入力回路の一方の入力端子に入力するとともに、バイアス回路により出力回路の出力信号を分圧して得られる分圧信号を差動入力回路の他方の入力端子に入力し、この差動入力回路により、伝送線路上の信号から自出力信号分を打ち消して受信信号を抽出する装置が提案されている（例えば、特許文献 2 参照）。

##### 【0004】

さらには、半導体集積回路装置の外部との信号の入出力を同時にかつ双方向に行う互いに接続された同時双方向バッファ対を有する半導体集積回路内部の同時双方向インターフェース回路であって、入力 / 出力不一致検出手段と、過半数判定手段と、入出力手段と、出力信号反転手段と、入力信号反転手段と、入力信号生成手段とを有し、半導体集積回路装置の入出力信号の論理値が不一致となる数が同時双方向バッファ対の総数の過半数である場合には、同時双方向バッファ対のうちの一方の出力信号の論理値を反転するインターフェース回路が提案されている（例えば、特許文献 3 参照）。

##### 【0005】

これらの技術においては、双方の送受信回路から送信されたデータに関して、伝送線路上にて排他的論理和をとり、これにより伝送線路に現れた 3 値の電圧値と自己の送信したデータの状態と比較することによって相手から送信されたデータを判別するものである。これにより、双方が任意のタイミングで相手側にデータの転送を行うことが可能になる。

【特許文献 1】特開平 8 - 107346 号公報（第 2 ~ 3 頁、第 3 , 4 図）

10

20

30

40

50

【特許文献 2】特開平 9 - 238095 号公報（第 5 ~ 7 頁、第 1 図）

【特許文献 3】特開平 10 - 303728 号公報（第 4 ~ 5 頁、第 1 図）

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上述のような構成の従来の同時双方向入出力システムにおいては、以下に挙げる未解決の問題点がある。

1) まず、伝送線路の両端に接続された夫々の出力回路の電位が、VDD、VSS 及びその中間電位 3 値をとる。そのため、伝送線路上の電圧が中間電位となる場合に、送信側の VDD とされた出力回路から受信側の VSS とされた出力回路に貫通電流が流れ続け、低消費電力性に欠ける。10

2) また、1) のように伝送線路の両端に接続された出力回路の出力電位が異なるとき、電位の引き合いによって伝送線路が中間電位となるので、電位が安定するまでに所定の時間を必要とする。

3) さらに、伝送線路の電位が安定するまでの期間は、データ信号にジッタが発生し、エラー率が高くなるので、このジッタを考慮してデータの転送速度を遅くしなければならない。20

【0007】

この発明は、上述のような課題を解決するためになされたもので、送信側の出力回路から受信側の出力回路に流れる貫通電流を抑制することができ、低消費電力の同時双方向送受信システムを得ることを目的とする。20

【課題を解決するための手段】

【0008】

第 1 の発明の同時双方向送受信システムは、出力信号を伝送線路を介して相手へ伝送する出力回路と、前記出力信号に応じた参照電位を発生する参照電位発生回路と、前記伝送線路に発生する自出力信号と相手から前記伝送線路へ出力され受信すべき受信信号との混合信号を受け、該混合信号と前記参照電位とを比較して入力信号を判別する入力回路とをそれぞれ有する第 1 及び第 2 の通信回路を、前記伝送線路を介して、双方向にデータの送受信が可能となるように接続され、前記第 1 及び第 2 の通信回路の少なくとも一方は、自分がデータ送信停止中であることを検出する自送信停止中検出手段と、該自送信停止中検出手段により自己がデータ送信停止中であることを検出したとき、相手の前記出力回路から自己の前記出力回路へ貫通電流が流れることを防止する貫通電流抑制手段とを有している。そのため、送信側の出力回路から受信側の出力回路に貫通電流が流れることが抑制され、低消費電力の送受信システムとすることができます。30

【0009】

第 2 の発明の同時双方向送受信システムにおいては、前記出力回路は、送信するデータに応じて前記出力信号を生成する出力信号生成部を有し、前記貫通電流抑制手段は、前記出力信号生成部に出力信号生成のための電位を供給する信号電位供給端子と前記出力信号生成部との間に設けられ、前記自送信停止中検出手段により自己がデータ送信停止中であることを検出したとき、ディゼーブル信号発生回路から入力されるディゼーブル信号によって、前記信号電位供給端子と前記出力信号生成部と間を電気的に開成状態とするスイッチング素子である。そのため、前記出力回路から自己の前記出力回路へ貫通電流が流れることを防止する貫通電流抑制手段を簡単な構成で実現することができる。40

【0010】

第 3 の発明の同時双方向送受信システムにおいては、前記出力回路は、送信するデータに応じて前記出力信号を生成する出力信号生成部を有し、前記貫通電流抑制手段は、前記出力信号生成部と前記伝送線路との間に設けられ、前記自送信停止中検出手段により自己がデータ送信停止中であることを検出したとき、ディゼーブル信号発生回路から入力されるディゼーブル信号によって、前記出力信号生成部と前記伝送線路との間を電気的に開成状態とするスイッチング素子である。そのため、前記出力回路から自己の前記出力回路へ50

貫通電流が流れることを防止する貫通電流抑制手段を簡単な構成で実現することができる。

#### 【0011】

第4の発明の同時双方向送受信システムにおいては、第1及び第2の通信回路の少なくとも一方は、相手がデータ送信停止中であることを検出する相手送信停止中検出手段と、該相手送信停止中検出手段により相手がデータ送信停止中であることを検出したときに、自出力信号のデータ転送速度を速くする転送速度増加手段とを備えている。そのため、相手がデータ送信停止中であるときに自出力信号のデータ転送速度を速くすることができ、システム全体のスループットを向上させることができる。

#### 【0012】

第5の発明の同時双方向送受信システムにおいては、前記相手送信停止中検出手段は、自己がデータ送信中で、自己の送信データと前記混合信号とを逐次比較し、両者自己の送信データとが連続して一致するデータ数が所定の判定数に達しただけ連続して一致したときに、相手が送信停止中であると判断する。そのため、相手がデータ送信停止中であることを簡単な構造にて確実に判断することができる。

#### 【0013】

第6の発明の同時双方向送受信システムにおいては、前記第1及び第2の通信回路の少なくとも一方は、前記入力信号との同期を取るために、同期周波数を漸次変化させながら同期する周波数を探す同期周波数検出手段と、相手がデータ送信停止中であることを検出する相手送信停止中検出手段と、該相手送信停止中検出手段により相手がデータ送信停止中となったことを検出したときに、前記同期周波数検出手段の同期周波数を変化させる動作を止める同期動作停止手段とを備えている。そのため、相手の送信再開時に行われる送信データに対して同期を取る動作が短時間で完了する。

#### 【0014】

第7の発明の同時双方向送受信システムにおいては、前記同期周波数検出手段は、前記入力信号と前記同期周波数との位相差を検出する位相周波数比較器と、制御電圧を変化させ該制御電圧に基づいて前記同期周波数を変化させる電圧制御発振器と、前記位相周波数比較器と前記電圧制御発振器との間に設けられ前記位相周波数比較器の出力信号に基づいて前記電圧制御発振器から電流を入出力して前記制御電圧を変化させるチャージポンプ回路とを有し、前記同期動作停止手段は、相手送信中検出手段及び前記自送信停止中検出手段により相手がデータ送信中で自己がデータ送信停止中であるときに、ディゼーブル信号発生回路から入力されるディゼーブル信号に基づいて、前記位相周波数比較器から前記チャージポンプ回路に入力される前記出力信号を消滅するように動作する論理素子である。そのため、前記同期周波数検出手段の同期周波数を変化させる動作を止める同期動作停止手段を簡単な構成にて実現することができる。

#### 【0015】

第8の発明の同時双方向送受信システムにおいては、前記第1及び第2の通信回路の少なくとも一方は、前記入力信号との同期を取るために、前記同期周波数を漸次変化させながら同期する周波数を探す同期周波数検出手段と、相手がデータ送信停止中であることを検出する相手送信停止中検出手段と、該相手送信停止中検出手段により相手がデータ送信停止中となったことを検出したときに、前記同期周波数検出手段に前記自出力信号を送信するためのクロック信号を入力する入力切り替え手段とを備えている。そのため、相手の送信再開時に行われる送信データに対して同期を取る動作が短時間で完了する。

#### 【発明を実施するための最良の形態】

#### 【0016】

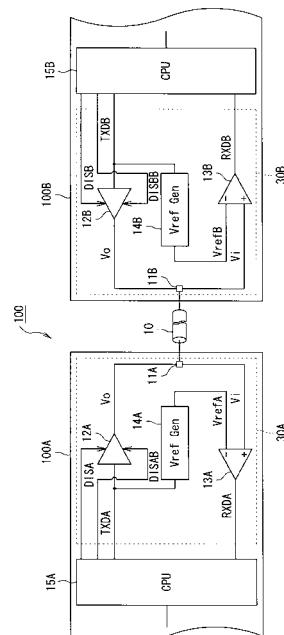

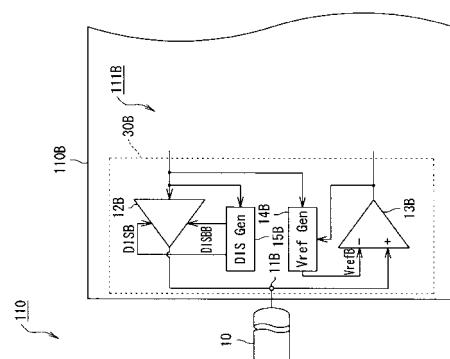

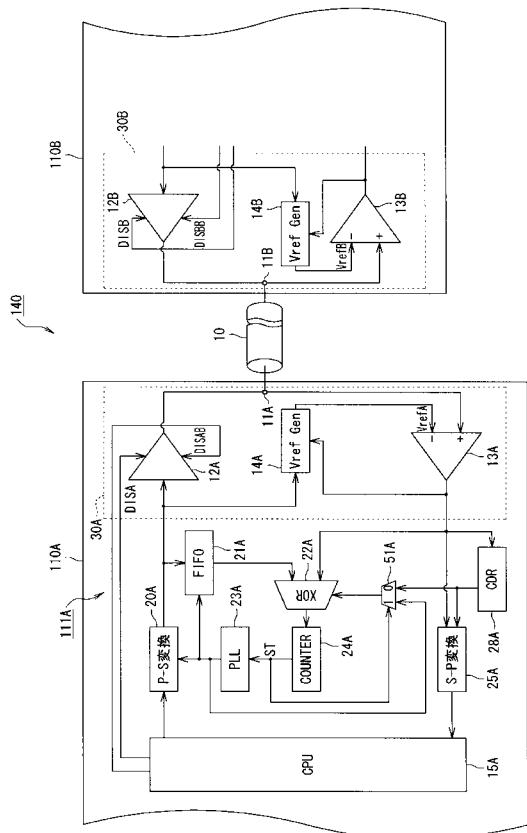

図1はこの発明の同時双方向入出力システムの第1の実施形態のブロック図である。図1において、同時双方向入出力システム100は、1組の伝送線路10によって互いに接続された第1のLSIチップ100Aと第2のLSIチップ100Bとを有している。第1のLSIチップ100A上には、第1の入出力回路部30Aが形成されている。第2のLSIチップ100B上には、第2の入出力回路部30Bが形成されている。第1のLSI

10

20

30

40

50

Iチップ100Aと第2のLSIチップ100Bとは、概略対称の構成を成している。そして、第1のLSIチップ100Aと第2のLSIチップ100Bの互いに対応する構成要素には、末尾に“A”と“B”を付けて対応付させている。このようなことから、主に一側の第1のLSIチップ110Aに関して説明する。

#### 【0017】

出入力回路部30Aは、伝送線路10に接続された外部端子11Aと、外部端子11Aに接続された出力回路としての出力バッファ12Aと、外部端子11Aに入力端子が接続された反転差動増幅回路からなる入力回路としての入力バッファ13Aと、出力バッファ12Aの入力側線路及び入力バッファ13Aの反転入力端子に接続された参照電位発生回路14Aとを有している。

10

#### 【0018】

第1のLSIチップ110Aは、さらに入出力回路部30Aをコントロールして、送信データTXDAを送信するとともに受信データRXDAを受信する送受信処理を行うCPU15Aを有している。このCPU15Aは、送信データTXDAの送信制御、及び受信データRXDAの受信制御を始め、入出力回路部30A全体の動作をつかさどるものであり、自己がデータ送信停止中であるか否は、このCPU自身が認識しており、送受信処理によって自己がデータ送信停止中のときにこのことを表すディゼーブル信号を生成する。

#### 【0019】

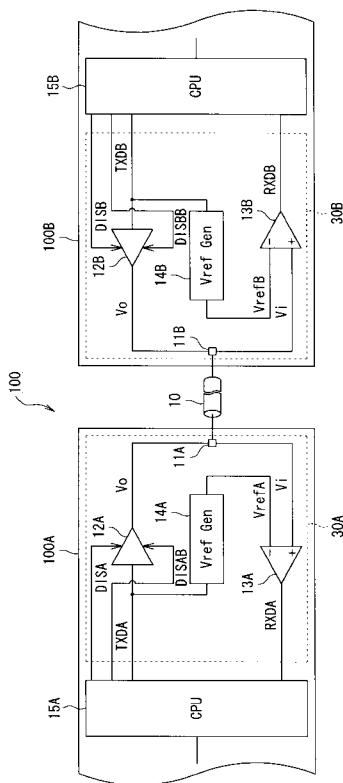

このCPU15Aで実行する送受信処理は、図2に示すように、先ず、ステップS1で、データ送信中であるか否かを判定し、データ送信中であるときには、ステップS2に移行して、ローアクティブのディゼーブル信号DISAとその反転信号であるハイアクティブの反転ディゼーブル信号DISABとを出力バッファ12Aに出力してからステップS3に移行して、送信情報の送信処理をおこなってからステップS4に移行する。

20

#### 【0020】

このステップS4では、相手方からデータを受信中であるか否かを判定し、データ受信中でないときにはそのまま処理を終了して前記ステップS1に戻り、データ受信中であるときには、ステップS5に移行して、受信データの受信処理を行ってからそのまま処理を終了して前記ステップS1に戻る。

また、前記ステップS1の判定結果が、自己がデータ送信中ではない送信停止状態であるときには、ステップS6に移行して、ハイアクティブのディゼーブル信号DISAとその反転信号であるローアクティブのディゼーブル信号DISABとを出力バッファ12Aに出力してから前記ステップS4に移行する。

30

#### 【0021】

この図2の処理において、ステップS1及びS5の初手が自送信停止中検出手段を構成している。

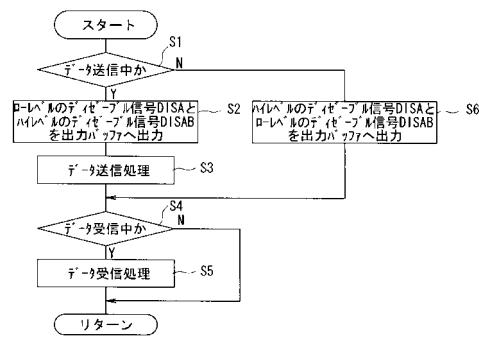

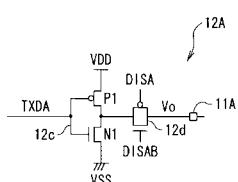

出力バッファ12Aは、図3に示すように、ゲート端子に送信データTXDAがそれぞれ入力されるPMOS型トランジスタP1とNMOS型トランジスタN1とで構成された出力信号生成部としてのCMOSインバータ回路12cと、CMOSインバータ回路12cのトランジスタP1のソース端子と電源電圧端子VDDとの間に接続されたゲート端子にCPU15Aからのディゼーブル信号DISAが入力されるPMOS型トランジスタP2と、CMOSインバータ回路12cのトランジスタN1のソース端子とアース電圧端子VSSとの間に接続されたゲート端子にCPU15Aからの反転ディゼーブル信号DISABが入力されるNMOS型トランジスタN2とを有する。電源電圧端子VDDとアース電圧端子VSSとは、出力信号生成部に、出力信号生成のための電位を供給する信号電位供給端子を構成している。PMOS型トランジスタP2とNMOS型トランジスタN2とは、CMOSインバータ回路12cを介して出力信号を出力可能とするか、或いはCMOSインバータ回路12cを伝送線路10に対してハイインピーダンスにして出力を停止するかのいずれかに切り替えるスイッチング素子を構成している。

40

#### 【0022】

出力バッファ12Aにおいて、ディゼーブル信号DISAがローレベルで反転ディゼー

50

ブル信号 D I S A B がハイレベルのとき、トランジスタ P 2 とトランジスタ N 2 がともにオンする。このとき、送信データ T X D A のビット信号がハイレベルであれば、N M O S 型トランジスタ N 1 がオンし、P M O S 型トランジスタ P 1 がオフとなる。そのため、出力信号 V o は、ほぼ V S S となりローレベルとなる。また、送信データ T X D A のビット信号がローレベルであれば、N M O S 型トランジスタ N 1 がオフし、P M O S 型トランジスタ P 1 がオンとなる。そのため、出力信号 V o は、ほぼ V D D となりハイレベルとなる。

#### 【 0 0 2 3 】

一方、出力バッファ 1 2 A に入力されるディゼーブル信号 D I S A がハイレベルで反転ディゼーブル信号 D I S A B がローレベルのとき、トランジスタ P 2 とトランジスタ N 2 がともにオフするので、インバータ回路 1 2 c は伝送線路 1 0 に対してハイインピーダンスとなり出力を停止する。そして、伝送速度制御部 1 0 1 B の出力バッファ 1 2 B から伝送速度制御部 1 0 1 A の出力バッファ 1 2 A へ貫通電流が流れることが防止される。すなわち、出力バッファ 1 2 A のトランジスタ N 2 , P 2 は、自己がデータ送信停止中であるとき、相手の出力バッファ 1 2 B から自分の出力バッファ 1 2 A へ貫通電流が流れることを防止する貫通電流抑制手段を構成している。

#### 【 0 0 2 4 】

入力バッファ 1 3 A は、相手端末である伝送速度制御部 1 0 1 B からの送信からのデータを V i として入力し、また、参照電位発生回路 1 4 A の生成する参照電位 V r e f A を入力し、両入力の差分を求め、さらにこれを反転して増幅する反転差分增幅回路である。

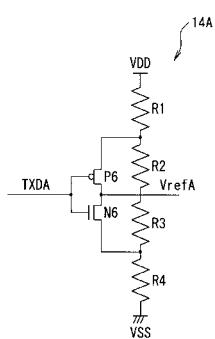

参照電位発生回路 1 4 A は、図 4 に一例として示されるように 4 個の抵抗 R 1 ~ R 4 によって構成された抵抗分割回路であり、送信データ T X D A を入力し、この入力に基づいて P M O S 型トランジスタ P 6 と N M O S 型トランジスタ N 6 のいずれかがオンし、これにより 2 値の参照電位 V r e f A を出力する。つまり、送信データ T X D A がハイレベルのとき、N M O S 型トランジスタ N 6 がオンし、P M O S 型トランジスタ P 6 がオフするので、参照電位 V r e f A は、V D D より抵抗 R 1 , R 2 , R 3 の損失分だけ下がった例えば 0 . 6 V を出力する。一方、送信データ T X D A がローレベルのとき、N M O S 型トランジスタ N 6 がオフし、P M O S 型トランジスタ P 6 がオンするので、参照電位 V r e f A は、V D D より抵抗 R 1 の損失分だけ下がった例えば 1 . 5 V を出力する。

#### 【 0 0 2 5 】

なお、参照電位発生回路 1 4 A は、一例として図 4 に最も簡単な構成を示したが、図 4 に示される抵抗分割による回路に限定されるものではなく、例えばバンドギャップリフアレンス回路等を組み合わせたものでもよい。

ここで、双方の伝送速度制御部 1 0 1 A , 1 0 1 B が同時にデータを送受信可能である動作を、一例として具体的な数値を用いて説明する。第 1 の伝送速度制御部 1 0 1 A が送信データを送信する際、送信データ T X D A がローレベルのとき、出力信号はインバータ回路 1 2 c で反転されて例えば 1 . 8 V であり、一方、送信データ T X D A がハイレベルのとき、例えば 0 V である。送信データ T X D B を出力する第 2 の伝送速度制御部 1 0 1 B においても同様である。

#### 【 0 0 2 6 】

参照電位発生回路 1 4 A , 1 4 B は、参照電位 V r e f A , V r e f B として、それぞれ 0 . 6 V と 1 . 5 V の 2 種類の電圧を生成する。そして、自己の出力バッファの出力信号が 1 . 8 V であるときには、高い方の参照電位 1 . 5 V を入力バッファ 1 3 A , 1 3 B に出力し、自己の出力バッファの出力信号が 0 V であるときには、低い方の参照電位 0 . 6 V を入力バッファ 1 3 A , 1 3 B に出力する。入力バッファ 1 3 A , 1 3 B は、この参照電位と入力信号の電位とを比較して入力信号のローレベル、ハイレベルを判定し、この判定結果を反転する。

#### 【 0 0 2 7 】

例えば、伝送線路 1 0 の電位を外部端子 1 1 A で観測したとすると以下のようになる。伝送速度制御部 1 0 1 A 側の送信データ T X D A の送信ビットがローレベルのとき、第 1

10

20

30

40

50

の伝送速度制御部 101A の出力電位は 1.8V となる。そして、参照電位は 1.5V となる。ここで、伝送速度制御部 101B 側の送信データ TXDB の送信ビットがローレベルのとき、第 2 の伝送速度制御部 101B の出力電位は 1.8V となる。そして、参照電位は 1.5V となる。このとき、伝送線路 10 は、1.8V となり、伝送速度制御部 101A 側の受信データ RXDA は 1.8V となるので、入力バッファ 13A の差動回路によりによりハイレベルと判定され、それが反転されてローレベルと認識される。伝送速度制御部 101B 側の受信データ RXDB も 1.8V となり、同様にハイレベルと判定され、それが反転されてローレベルと認識される。

#### 【0028】

また、伝送速度制御部 101A 側の送信データ TXDA の送信ビットがハイレベルのとき、第 1 の伝送速度制御部 101A の出力電位は 0V となる。そして、参照電位は 0.6V となる。一方、伝送速度制御部 101B 側の送信データ TXDB の送信ビットがローレベルのとき、第 2 の伝送速度制御部 101B の出力電位は 1.8V となる。そして、参照電位は 1.5V となる。このとき、伝送線路 10 は、中間電位の 0.9V となり、伝送速度制御部 101A 側の受信データ RXDA は 0.9V となるので、入力バッファ 13A の差動回路によりによりハイレベルと判定され、それが反転されてローレベルと認識される。伝送速度制御部 101B 側の受信データ RXDB は同じく 0.9V であるが、入力バッファ 13B によりローレベルと判定され、それが反転されてハイレベルと認識される。

#### 【0029】

同様にして、伝送速度制御部 101A 側の送信データ TXDA がローレベルのとき、出力電位は 1.8 であり、参照電位は 1.5V となる。一方、伝送速度制御部 101B 側の送信データ TXDB の送信ビットがハイレベルとき、第 2 の伝送速度制御部 101B の出力電位は 0V であり、参照電位は 0.6V となる。このとき、伝送線路 10 は、中間電位の 0.9V となり、受信データ RXDA は 0.9V となるので、入力バッファ 13A の差動回路によりによりローレベルと判定され、それが反転されてハイレベルとなり、伝送速度制御部 101B 側の受信データ RXDB は同じく 0.9V であるが、入力バッファ 13B によりハイレベルと判定され、それが反転されてローレベルと認識される。

#### 【0030】

同様にして、送信データ TXDA がハイレベルで送信データ TXDB がハイレベルのとき、受信データ RXDA がハイレベルで受信データ RXDB もハイレベルと認識される。

この結果を図 5 に示す。図 5 において、“VrefA” は、第 1 の伝送速度制御部 101A の参照電位を示し、“VrefB” は、第 2 の伝送速度制御部 101B の参照電位を示す。また、“H” はデータのハイレベル、“L” はデータのローレベルを示している。

#### 【0031】

このように、自己の送信データに応じて参照電位を切り替え、切り替えられた参照電位にて受信データを判定するので、双方が任意のタイミングで相手端末にデータの転送を行うことが可能になる。

そして、本実施形態においては、自己がデータ送信停止中である場合、CPU15A が、出力バッファ 12A に、ハイレベルのディセーブル信号 DISA 及びローレベルの反転ディゲーブル信号 DISAB を出力する。これにより、図 3 のトランジスタ P2, N2 が共にオフするので、伝送線路 10 に対して出力バッファ 12A が、ハイインピーダンスとなり、出力バッファ 12B から出力バッファ 12A に貫通電流が流れることがなくなり、低消費電力の送受信システムとすることができます。

#### 【0032】

因みに、トランジスタ P2 と N2 が存在しない場合には、例えば送信側のハイレベルとされた出力バッファ 12A の VDD から、伝送線路 10 を経由して、受信側のローレベルとされた出力バッファ 12B の VSS に貫通電流が流れることになる。

すなわち、本実施形態においては、自己がデータ送信停止中であるとき、相手の出力バッファ 12B から自分の出力バッファ 12A へ貫通電流が流れることを防止する貫通電流抑制手段としてトランジスタ P2, N2 を有している。そのため、送信側の出力バッファ

10

20

30

40

50

から受信側の出力バッファに流れる貫通電流が防止され、低消費電力の同時双方向送受信システムとすることができる。

#### 【0033】

なお、本実施形態の貫通電流抑制手段は、トランジスタ P2, N2 で構成されているが、少なくともトランジスタ N2 を設けておけば、これをオフすることにより貫通電流を抑制することができる。

なお、出力バッファ 12A, 12B は、図 6 に示される回路で構成されてもよい。この回路は、出力信号生成部としての CMOS のインバータ回路 12c とディゼーブル信号 DISA 及び反転ディゼーブル信号 DISAB が PMOS 型トランジスタ及び NMOS 型トランジスタのゲートに入力されるスイッチング素子としてのトランスファーゲート 12d によって構成されている。この回路の場合、信号 DISA がローレベルで信号 DISAB がハイレベルのとき、トランスファーゲート 12d が開くので、インバータ回路 12c の出力は、データ入力側から外部端子 11A 側へと伝達される。一方、信号 DISA がハイレベルで信号 DISAB がローレベルのとき、トランスファーゲート 12d が閉じるので、インバータ回路 12c の出力は遮断される。10

#### 【0034】

また、本実施形態においては、第 1 の LSI チップ 100A と第 2 の LSI チップ 100B とが概略対称の構成を成しているが、必ずしも対称の構成でなくともよく、例えば、第 2 の LSI チップ 100B 側の送信データ量が第 1 の LSI チップ 100A 側の送信データ量に比較して多い場合などでは、第 1 の LSI チップ 100A 側の CPU 15A でのみディゼーブル信号 DISA 及び反転ディゼーブル信号 DISAB を出力バッファ 12A に出力するようにすれば、第 2 の LSI チップ 100B の出力バッファ 12B から第 1 の LSI チップ 100A の出力バッファ 12A へ貫通電流が流れることを防止することができ、低消費電力の同時双方向送受信システムとすることができます。20

#### 【0035】

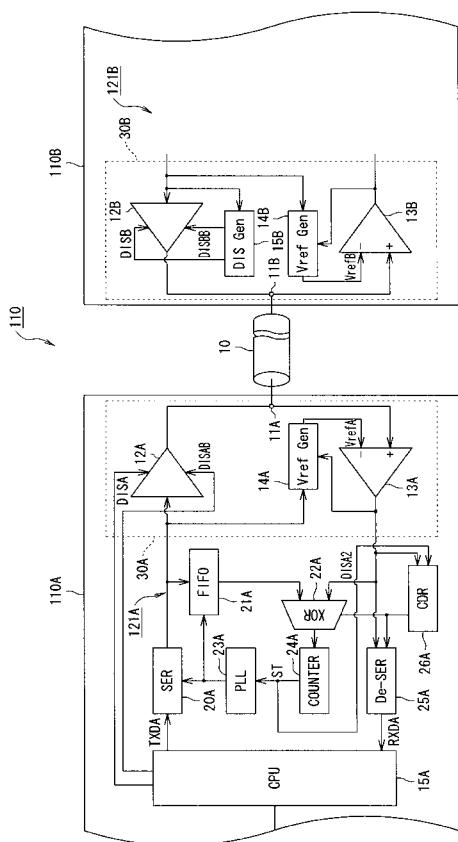

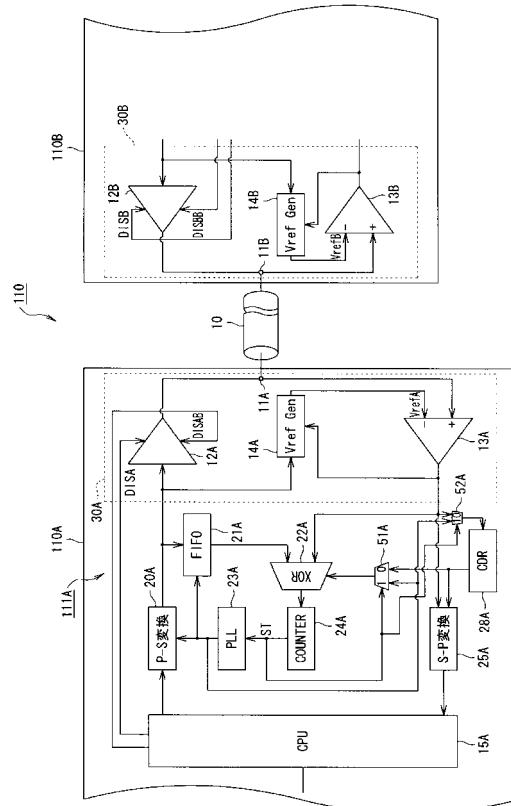

次に、本発明の第 2 の実施形態を図 7 について説明する。

本実施形態は、相手端末がデータ送信停止中であることを検出したときに、自己の送信データの転送速度を速くすることを特徴としている。

図 7 において、同時双方向入出力システム 110 は、伝送線路 10 によって互いに接続された第 1 の LSI チップ 110A と第 2 の LSI チップ 110B とを有している。第 1 の LSI チップ 110A には、前述した第 1 の実施形態と同様の構成を有する入出力回路部 30A と伝送速度制御部 111A とが形成されている。30

#### 【0036】

伝送速度制御部 111A は、入出力回路部 30A の出力バッファ 12A の入力側に接続されたパラレルシリアル変換回路（以下 S-P 変換回路と呼ぶ）20A を有する。S-P 回路 20A は、入力されるクロック信号に基づいてパラレルデータである送信データ TXDA をシリアルデータに変換する。

S-P 変換回路 20A には、フェーズロックループ回路（以下 PLL 回路と呼ぶ）23A で生成される高低 2 種類の周波数のクロック信号が選択的に入力され、入力されたクロック信号の周波数に応じてシリアルデータへの変換速度が決定される。40

#### 【0037】

そして、S-P 回路 20A から出力されるシリアルデータが先入れ先出しメモリ（以下、 FIFO と呼ぶ）21A にも供給される。この FIFO 21A は、入力されたシリアルデータを、このシリアルデータを入出力回路部 30A に入力したときに、その出力バッファ 12A から入力バッファ 13A を経て出力されるまでの遅延時間だけ遅延させた遅延シリアル信号を出力する。

#### 【0038】

この FIFO 21A から出力される遅延シリアル信号と入出力回路部 30A の入力バッファ 13A から出力される混合信号とが排他的論理和回路（以下、XOR 回路と呼ぶ）22A に供給され、この XOR 回路 22A から出力される排他的論理和出力がカウンタ 24

A に入力される。このカウンタ 24 A は、排他的論理和出力が“0”であるときにカウント値をカウントアップし、排他的論理和出力が“1”であるときにカウント値を“0”にクリアするように構成されている。このカウンタ 24 A の所定の判定数に対応する出力段から出力される相手送信停止検出信号 S T が PLL 回路 23 A に供給され、この PLL 回路 23 A で、阿井邸送信停止検出信号が“0”であるときに通常の送信速度を規定する通常クロック信号を S - P 変換回路 20 A に出力し、相手送信停止検出信号 S T が“1”であるときに通常クロック信号より周波数の高い高速クロック信号を S - P 変換回路 20 A に出力する。

#### 【0039】

一方、入出力回路部 30 A の入力バッファ 13 A から出力される混合信号は、シリアルデータをパラレルデータに変換するパラレルシリアル変換回路（P - S 変換回路）25 A に供給されて、この P - S 変換回路 25 A でパラレルデータに変換された混合信号が受信データ RXDA として CPU 15 A に入力される。10

また、入出力回路 30 A の入力バッファ 13 A から出力される混合信号は、この混合信号に含まれるクロック信号を再生するクロックデータリカバリ回路（以下 CDR 回路と呼ぶ）26 A に入力される。この CDR 回路 26 A で再生されたクロック信号は、XOR 回路 22 A にサンプリングクロックとして供給されると共に、P - S 変換回路 25 A に変換クロック信号として供給される。

#### 【0040】

次に上記第 2 の実施形態の動作を説明する。LSI チップ 110 Aにおいて、S - P 回路 20 A は、PLL 回路 23 A が生成したクロックのタイミングに同期して送信すべきパラレルデータ TXDA をシリアルデータに変換する。S - P 回路 20 A にてシリアル変換されたデータは、入出力回路 30 A の出力バッファ 12 A を経て伝送線路 10 に送信される。このとき、出力バッファ 12 A の出力は、ループバックして入力バッファ 13 A にも入力されている。20

#### 【0041】

ここで、相手方の LSI チップ 110 B において、入出力回路 30 B は送信を停止しているものとする。つまり、出力バッファ 12 B は、信号 DISB, DISBB によってハイインピーダンスにされているものとする。そのため、LSI チップ 110 A において、入力バッファ 13 A に入力されるデータは、出力バッファ 12 A から出力されたデータが、そのまま LSI チップ 110 A をループバックしたものとなる。30

#### 【0042】

ループバックした送信データは、CDR 回路 26 A にてクロック信号が抽出され、抽出したクロック信号にてリタイムされ、これが P - S 変換回路 25 A によって、シリアルデータからパラレルデータ RXDA に変換される。

このとき、S - P 回路 20 A から出力されたシリアルビット列を FIFO 21 A にて所定の時間分遅延させ、この遅延されたビット列と入出力回路 30 A の入力バッファ 13 A から出力される混合信号のビット列との排他的論理和を XOR 回路 22 A で取り、両ビット列が一致するデータであるので、カウンタ 24 A がインクリメントされる。

#### 【0043】

そしてさらに、PLL 回路 23 A は、カウンタ 24 A が、所定の判定数までカウントアップしたとき、相手送信停止検出信号 S T が“1”となることにより、相手の LSI チップ 110 B の入出力回路 30 B からの送信が停止しているものと判断することができ、発振周波数を上げ、出力バッファ 12 A からの送信ビットレートを上げるように動作をする。40

#### 【0044】

この高速データ送信状態からデータ送信停止中であった相手側の入出力回路 30 B が再びデータ送信を開始する状態となると、入力バッファ 13 A から出力される混合信号のシリアルデータと S - P 変換回路 20 A から出力されるシリアルデータとが一致しない状態となることにより、XOR 回路 22 A の排他的論理和出力が“1”となり、これによつて50

カウンタ24Aのカウント値がクリアされることにより、カウンタ24Aの所定出力段から出力される相手送信停止検出信号S\_Tが“0”に反転し、これに応じてPLL回路23Aは高速クロック信号を出力している状態から通常クロック信号を出力する状態に切換え、出力バッファ12Aからの送信ビットレートを下げるよう動作をする。

#### 【0045】

このように、本実施形態においては、相手側のLSIチップ110Bにおける入出力回路30Bが送信を停止しているとき、伝送速度制御部111Aが送出しているデータとループバックされたデータが同一であることに着目している。すなわち、S-P回路20Aにてシリアル化されたデータと入力バッファ13Aから出力されるシリアル受信データとが所定のデータ数だけ連続して同一であれば、PLL回路23Aで入出力回路30Bからの送信データが停止していると判断し、送信速度を上げる。10

#### 【0046】

このとき、 FIFO21A、XOR回路22A及びカウンタ24Aは、相手がデータ送信停止中であることを検出する相手送信停止中検出手段を構成している。そして、PLL回路23Aは、この相手出力停止検出手段にて相手がデータ送信停止中であることを検出したときに、自出力信号のデータ転送速度を速くする転送速度増加手段を構成している。

相手側LSIチップ110Bでは、入出力回路30Bがデータ送信停止中のとき、ディゼーブル信号DISB及び反転ディゼーブル信号DISBBによって入出力回路30Bの出力バッファ12Bがハイインピーダンスとされ、その結果、伝送線路10を駆動する回路が、入出力回路30A側の出力バッファ12Aのみとなり、貫通電流が防止されて低消費電力となる動作に関しては、第1の実施形態と同様である。20

#### 【0047】

なお、相手がデータ送信停止中であることを判断するカウンタ24Aのカウント値の判定数は、通信目的に応じたアプリケーションに依存する所定の数とされている。具体的には、例えばチップ110Aからチップ110Bへ送信されるデータと、チップ110Bからチップ110Aへ送信されるデータの量がほぼ同じであるアプリケーションに使用するときは、カウンタ24A及びカウンタ24Bのカウントアップする判定数を同じにする。

#### 【0048】

一方、例えば、チップ110Aからチップ110Bへ8割のデータが送出され、チップ110Bからチップ110Aへ2割のデータが送出されるようなアプリケーションに対しては、大きなデータ量を受信するチップ110B側の判定数を小さなデータ量を受信するチップ110A側の判定数より小さくする。30

実例としては、例えば、チップ110Aからチップ110Bへ大量のデータの送信しつつ、チップ110Bからチップ110Aには、ACK、NAKのみを返すような通信のアプリケーションがそれである。

#### 【0049】

本実施形態においては、チップ110Aとチップ110Bとの間で送信されるデータの量が非対称であるときは、その比率に応じて両カウンタがカウントアップする数の比率を変えている。なぜならば、送信されるデータ量が対称の場合、データが衝突する可能性が同じであるが、非対称であればデータが衝突、つまり同時に双方向で送受信する可能性も非対称となる。そのため、データの衝突の可能性を最も低いものとするために、カウンタ24A及びカウンタ24Bのカウントアップ数を送信するデータ量の大きさ応じて決める効果がある。そして、カウンタ24A及びカウンタ24Bを可変長のカウンタにしており、アプリケーションに応じてカウントアップ数を変更してもよい。40

#### 【0050】

以上のように上記第2の実施形態においては、同時双方向送受信システムの一方の伝送速度制御部が、データ送信停止中のとき他方の伝送速度制御部の送信速度が上ることにより、全体のスループットが向上する。一方、データ送信停止中の伝送速度制御部が再びデータ送信を開始すると、PLL回路23A, 23Bが発振周波数を下げ、これにより出力バッファからの送信ビットレートが下がり、データ転送の速度が遅くなった結果、アイパ50

ターンが開くのでエラー発生率が下がる。

#### 【0051】

このように上記第2の実施形態においては、伝送線路10の通信状態に応じて最大の伝送スピードを得ることができる。また、單一方向への伝送を行っているときの消費電流を下げることができる。

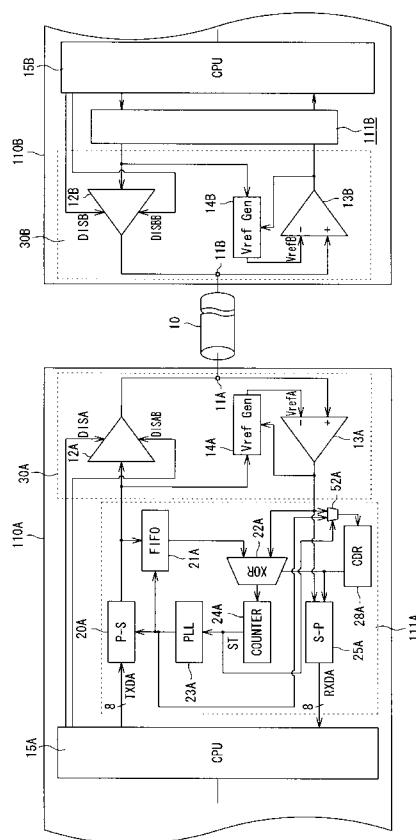

次に、本発明の第3の実施形態を図8について説明する。

本実施形態のLSIチップ120Aにおいては、相手からのデータ送信が一時中断された後に、再びデータ送信が行われるような場合、相手のデータ送信停止中に自己の同期周波数が変化しないように周波数自動追従機能を停止するものである。

#### 【0052】

この第3の実施形態では、LSIチップ110Aにおいて、前述した第2の実施形態におけるカウンタ24Aから出力される相手送信停止検出信号STが受信データからクロック信号を抽出するCDR回路27Aにも供給されることを除いては前述した第2の実施形態における図7と同様の構成を有し、図7との対応部分には同一符号を付し、その詳細説明はこれを省略する。

#### 【0053】

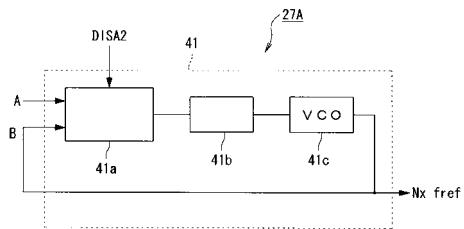

ここで、CDR回路27Aは、受信データからクロック信号を抽出するために受信データに対して同期をとる必要がある。このとき、CDR回路27Aは、自ら持っている同期周波数を漸次変化させながら受信データに追従する動作をする。そして、CDR回路27Aは、自らの同期周波数を変化させるために、図9に示すようにPLL回路41で構成されている。

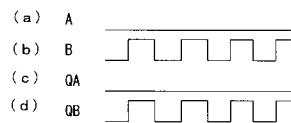

#### 【0054】

このPLL回路41は、位相検出器41aと、ループフィルター41bと、電圧制御発振器(以後、VCOという)41cとから構成されている。PLL回路41は、入力バッファ13Aが入力した受信データを信号Aとして入力し、自ら生成した同期周波数データを信号Bとして入力し、信号Bを信号Aに追従するように変化させて受信データのクロック信号を抽出する。

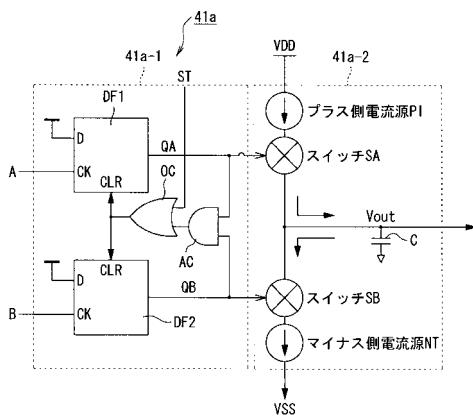

#### 【0055】

位相検出器41aは、図10に示すように、位相周波数比較器41a-1とチャージポンプ回路41a-2とから構成されている。位相周波数比較器41a-1は、信号Aがクロック入力端子に入力され、これに基づいてアップ信号QAを出力するD型フリップフロップDF1と、信号Bがクロック入力端子に入力され、これに基づいてダウン信号QBを出力するD型フリップフロップDF2と、アップ信号QA及びダウン信号QBが入力されるアンド回路ACと、このアンド回路ACの論理積出力信号とカウンタ24Aから出力される相手送信停止検出信号STとが入力され、両者の論理和出力信号をクリア信号としてD型フリップフロップDF1及びDF2のクリア信号入力端子に入力するオア回路OCとを有する。

#### 【0056】

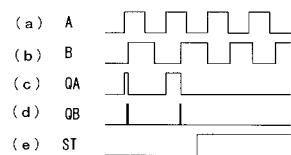

この位相周波数比較器41a-1では、今、相手側LSIチップ110Bがデータ送信状態にあるものとすると、XOR回路22Aの出力が論理値“1”となってカウンタ24Aがリセット状態を維持することから相手送信停止検出信号STが図11(e)に示すように論理値“0”となっている。この相手送信停止検出信号STがオア回路OCに入力されるので、このオア回路OCでは、他方の入力であるアンド回路ACのアップ信号QA及びダウン信号QBの状態に応じた論理積出力信号が出力される状態となる。

#### 【0057】

この状態で、入力バッファ13Aから入力される信号Aが図11(a)に示すように所定周波数でオンオフを繰り返す信号であるものとし、PLL回路41のVCO41cから出力される信号Bが図11(b)に示すように位相ずれを生じているものとする。この状態では、時点 $t_1$ で信号Aがオフ状態からオン状態に反転すると、これに応じてD型フリップフロップDF1から出力されるアップ信号QAが図11(c)に示すようにオフ状態

10

20

30

40

50

からオン状態に反転する。この状態では、D型フリップフロップDF2から出力されるダウン信号QBがオフ状態であるので、アンド回路ACから出力されるクリア信号は論理値“0”を維持している。その後、時点t2で信号Bがオフ状態からオン状態に反転すると、これに応じてD型フリップフロップDF2から出力されるダウン信号QBが図11(d)に示すようにオフ状態からオン状態に反転する。このようにダウン信号QBがオン状態となると、アンド回路ACのクリア信号が論理値“1”となることにより、D型フリップフロップDF1及びDF2が共にクリアされて、これらから出力されるアップ信号QA及びダウン信号QBが共にオフ状態となる。

#### 【0058】

その後、時点t3で信号Aが再度オン状態となると、アップ信号QAもオン状態となり、時点t4で信号Bが再度オン状態となると、ダウン信号QBがオン状態となり、その後にアンド回路ACから出力されるクリア信号が論理値“1”となるので、D型フリップフロップDF1及びDF2が共にクリア状態となる。

このようにして、信号A及びBの位相差に応じたアップ信号QA及びダウン信号QBが形成される。その後、相手側LSIチップ110Bでデータ送信を停止すると、入力バッファ13Aから出力される混合信号が自身の出力バッファ12Aから出力される信号のみとなることにより、XOR回路22Aの出力が“0”となって、カウンタ24Aがカウントを開始し、そのカウント値が所定の判定数に達すると、相手送信停止検出信号STが論理値“1”となり、これがオア回路OCに入力されることにより、このオア回路OCからアンド回路ACの論理積出力信号の状態にかかわらず論理値“1”となるクリア信号がD型フリップフロップDF1及びDF2に入力されるので、これらD型フリップフロップDF1及びDF2が共にクリア状態に保持され、これらから出力されるアップ信号QA及びダウン信号QBが共にオフ状態を維持する状態となる。

#### 【0059】

この位相周波数比較器41a-1で生成されたアップ信号QAとダウン信号QBは、チャージポンプ回路41a-2に入力され、チャージポンプ回路41a-2のオンオフのタイミングとなる。

チャージポンプ回路41a-2は、電源端子に接続されたプラス側電流源PIとスイッチング素子SAとの直列回路と、この直列回路に接続されたスイッチング素子SBとアース端子に接続されたマイナス側電流源NIとの直列回路とで構成され、両直列回路の接続点から出力ラインが導出され、この出力ラインとアース端子との間に充放電用コンデンサCが接続され、充放電用コンデンサCの端子電圧が出力電圧Voutとして出力される構成を有する。そして、スイッチング素子SAにアップ信号QAが入力され、スイッチング素子SBにダウン信号QAが入力されている。

#### 【0060】

そして、アップ信号QAが論理値“1”となるとスイッチング素子SAがオン状態となって、充放電用コンデンサCが充電され、ダウン信号QBが論理値“1”となるとスイッチング素子SBがオン状態となって、充放電用コンデンサCが放電される。

そして、チャージポンプ回路41a-2の出力電圧Voutは、フィルター41bを通してVCO41cに入力される。このVCO41cで、チャージポンプ回路41a-2の出力電圧Voutが高くなるとこれに応じて出力される同期周波数も高くなり、チャージポンプ回路41a-2の出力電圧Voutが低くなるとこれに応じて出力される同期周波数が低くなる。

#### 【0061】

なお、位相周波数比較器41a-1、チャージポンプ回路41a-2及びVCO41cは、同期周波数検出手段を構成している。

次に、上記第3の実施形態の動作を説明する。

今、自LSIチップ110Aがデータを送信しているデータ送信中であると共に、相手LSIチップ110Bでもデータを送信しているデータ送信中であるものとする。

#### 【0062】

10

20

30

40

50

この状態では、次LSIチップ110Aの入力側バッファ13Aから自己の送信データと相手LSIチップ110Bからの送信データとの混合信号Aが出力されるので、XOR回路22Aの排他的論理和出力信号が論理値“0”となり、カウンタ24Aがリセット状態を維持して、相手送信停止検出信号STが論理値“0”を維持する。

一方、CDR回路27Aでは、PLL回路41を構成する位相差検出回路41aの位相周波数比較器41a-1で、相手送信停止検出信号STが論理値“0”であることにより、オア回路OCからはアンド回路ACの論理積出力信号に応じたクリア信号が出力される状態となる。

#### 【0063】

このため、位相周波数比較器41a-1では、入力バッファ13Aから入力される信号AとVCO41cから出力される信号Bとを比較し、図11(a)及び(b)に示すように、信号Aの位相が信号Bの位相に対して進んでいるときに位相差に応じた区間オン状態となるアップ信号QAを出力する。

このアップ信号QAがチャージポンプ回路41a-2に供給されると、スイッチング素子SAがオン状態となり、プラス側電流源PIからの電流が充放電用コンデンサCに流れ、この充放電用コンデンサCを充電することにより、出力電圧Voutが上昇する。

#### 【0064】

この出力電圧Voutがフィルター41bを介してVCO41cに供給されるので、このVCO41cから出力される同期周波数が高くなり、次第に信号Aの周波数に一致するよう修正される。そして、信号Aの周波数と信号Bの周波数が一致したときのVCO41cから出力される同期周波数信号(クロック信号)がCDR回路27AからXOR回路22A及びS-P変換回路25Aにサンプリング信号として供給される。

#### 【0065】

したがって、XOR回路22Aで受信データに応じたサンプリングタイミングで送信データと受信データとの排他的論理和をとり、S-P変換回路25Aでは受信データを正確にパラレル信号に変換してCPU15Aに供給し、CPU15Aで受信処理が行われる。

この相手側LSIチップ110Bのデータ送信状態から相手側LSIチップ110Bでデータ送信を中断する送信停止状態となると、前述した第2の実施形態と同様に、入力バッファ13Aの出力信号Aが自己の送信データのみとなることから、XOR回路22Aの排他的論理和信号が論理値“0”となり、カウンタ24Aがカウントを開始し、そのカウント値が所定の判定数に達すると相手送信停止検出信号STが論理値“1”となり、これがPLL回路23Aに供給されて、データ送信速度が増加される。

#### 【0066】

これと同時に、相手送信停止検出信号STがCDR回路26Aに供給されるので、このCDR回路26Aで相手側LSIチップ110Bのデータ送信時の同期周波数が保持される。すなわち、位相周波数比較器41a-1のオア回路OCに論理値“1”的相手送信停止検出信号STが入力されることにより、このオア回路OCの論理和出力信号がアンド回路ACから供給されるアップ信号QA及びダウン信号QBの状態による論理積出力信号にかかわらず常に論理値“1”となり、D型フリップフロップDF1及びDF2が共にクリア状態に維持され、これらから出力されるアップ信号QA及びダウン信号QBが共にオフ状態となる。

#### 【0067】

このため、チャージポンプ回路41a-2におけるスイッチング素子SA及びSBが共にオフ状態となって充放電用コンデンサCの入力側がハイインピーダンスとなり、この充放電用コンデンサCの充電電圧即ち出力電圧Voutが保持される。

この結果、フィルター41bを介してVCO41cに入力される制御電圧が相手側LSIチップ110Bがデータ送信を停止したときの同期周波数に略近い周波数に応じた電圧に保持されるので、CDR回路26Aで再生されるクロック信号が相手側LSIチップ110Bのデータ送信時に近い周波数に保持される。

#### 【0068】

10

20

30

40

50

その後、自己のデータ送信を停止した場合には、入力バッファ 13A から出力される混合信号 A がローレベルを維持することになるが、 FIFO21A から出力される送信データもローレベルを維持することになるので、XOR回路 22A の排他的論理和出力信号は論理値 “0” を維持することになり、カウンタ 24A でのカウントアップが継続し、これから出力される相手送信停止検出信号 ST は論理値 “1” を維持するので、CDR回路 26A におけるチャージポンプ回路 41a - 2 での出力電圧 Vout の保持状態を継続する。

#### 【0069】

その後、相手側 LSI チップ 110B でデータ送信を再開し、入力バッファ 13A から自己の送信データと相手側 LSI チップ 110B からの受信データとの混合信号 A 又は相手側 LSI チップ 110B からの受信データのみの信号 A が出力される状態となると、XOR回路 22A の排他的論理和出力信号が論理値 “1” となることにより、カウンタ 24A がリセット状態となって、相手送信停止検出信号 ST が論理値 “0” に復帰する。

#### 【0070】

このため、伝送速度制御部 111A で通常の送信速度でのデータ送信状態に復帰すると共に、CDR回路 26A の位相周波数比較器 41a - 1 で混合信号 A と VCO41c の出力信号 B との位相差によるアップ信号 QA 又はダウン信号 QB が出力されることになり、これに応じてチャージポンプ回路 41a - 2 で位相差に応じた出力電圧 Vout が出力されて、VCO41c から出力される周波数同期したクロック信号が XOR 回路 22A 及び S-P 変換回路 25A に供給されて、受信データをパラレル信号に変換して CPU15A に入力し、この CPU15A で受信処理が行われる。

#### 【0071】

このとき、位相比較器 41a のチャージポンプ回路 41a - 2 で、その出力電圧 Vout が前回の相手側 LSI チップ 110B のデータ送信時の同期周波数時の電圧に近い状態に保持されているので、相手側 LSI チップ 110B でのデータ送信開始時に短時間で周波数同期を行うことができ、相手側 LSI チップ 110B からの受信データを迅速に受信処理することができる。

#### 【0072】

因みに、位相周波数比較器 41a - 1 のオア回路 OC を省略して、アンド回路 AC の論理積出力信号をクリア信号として直接 D 型フリップフロップ DF1 及び DF2 に供給するようにした場合には、位相周波数比較器 41a - 1 が常時作動状態に保持されるので、自分がデータ送信中で相手側 LSI チップ回路 110B がデータ送信停止状態となつたときには、入力バッファ 13A から自己の送信データが出力されるので、CDR回路 26A で自己のクロック信号に周波数同期したクロック信号を再生し、自己のクロック信号と相手側 LSI チップ 110B のクロック信号とは通常近い周波数に設定されていることから、大きな周波数変動を生じることはない。しかしながら、自己の送信データがなく、送信停止状態にあるときには、入力バッファ 13A から出力される信号 A がローレベルに維持されることになる。このローレベルの信号 A が CDR回路 26A の位相比較器 41a における位相周波数比較器 41a - 1 の D 型フリップフロップ DF1 に入力される状態となると、この D 型フリップフロップ DF1 から出力されるアップ信号 QA も図 12(c) に示すようにローレベルを維持し、アンド回路 AC の論理積出力信号は論理値 “0” を維持することになり、D 型フリップフロップ DF1 及び DF2 がクリアされることがなくなる。

#### 【0073】

このとき D 型フリップフロップ DF2 には図 12(b) に示すように N 分周回路 41d からの信号 B が入力されているので、この D 型フリップフロップ DF2 から図 12(d) に示すようにし、信号 B と同一のダウン信号 QB が出力されることになる。

このため、チャージポンプ回路 41a - 1 ではスイッチング素子 SB のみがオンオフを繰り返すことになり、このスイッチング素子 SB がオン状態であるときに充放電用コンデンサ C の充電電圧が放電されて、出力電圧 Vout が徐々に低下し、この出力電圧 Vout がフィルター 41b を介して VCO41c に供給されることにより、VCO41c から出

10

20

30

40

50

力される同期周波数が徐々に低くなり、この同期周波数の低下傾向が自己又は相手側 L S I チップ 110B でデータ送信が開始されるまでの間継続されることになり、相手側 L S I チップ 110B のデータ送信時のクロック信号の周波数からかけ離れたものとなる。

#### 【0074】

この結果、相手側 L S I チップ 110B でデータ送信を開始したときに、チャージポンプ回路 41a - 2 での出力電圧  $V_{out}$  が低下した状態から適正状態に復帰するまでに時間がかかり、受信データの受信処理を開始するまでに時間がかかることになる。

しかしながら、上記第 3 の実施形態によれば、相手側 L S I チップ 110B が送信停止状態となると、相手送信停止検出信号 ST が論理値 “1” となり、これによって位相周波数比較器 41a - 1 のアップ信号 QA 及びダウン信号 QB を夫々オフ状態とすることにより、チャージポンプ回路 41a - 2 の充放電用コンデンサ C の入力側をハイインピーダンスとして、出力電圧  $V_{out}$  を保持することにより、VCO 41c での周波数低下を確実に防止することができ、相手側 L S I チップ 110B がデータ送信を再開したときに短時間で周波数同期を行って正確なクロック信号を再生することができる。

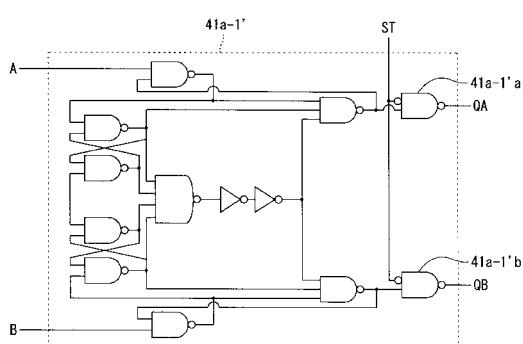

#### 【0075】

なお、上記第 3 の実施形態においては、位相周波数比較器 41a - 1 として図 10 に示す構成を適用した場合について説明したが、これに限定されるものではなく、図 13 に示す位相周波数比較器 41a - 1' を適用するようにしてもよい。図 12 に示す位相周波数比較器 41a - 1' の場合、同期動作停止手段として動作する出力側に設けた論理素子である 2 個の AND 素子 41a - 1' a, 41a - 1' b にカウンタ 24A から出力される相手送信停止検出信号 ST を供給することによって、相手送信停止検出信号 ST が論理値 “1” となったときにアップ信号 QA とダウン信号 QB とを共にオフ状態に制御することができる。

#### 【0076】

また、本実施形態においては、チャージポンプ回路 41a - 2 を一時的に停止させるために、チャージポンプ回路 41a - 2 に接続された位相周波数比較器 41a - 1 の出力を停止させるものであるが、この方法に限定されるものではなく、チャージポンプ回路 41a - 2 を停止できるものであれば他の方法でもよい。

次に、本発明の第 4 の実施形態を図 14 について説明する。

#### 【0077】

この第 4 の実施形態では、相手側 L S I チップ 110B でデータ送信を停止した後にデータ送信を再開したときに、簡易な構成でデータ受信処理を再開するようにしたものである。

すわなち、第 4 の実施形態では、図 14 に示すように、伝送速度制御部 11A における X OR 回路 22 のクロック信号入力端子にセレクタ 51A が接続され、このセレクタ 51A の入力側に C D R 回路 28A から出力されるクロック信号と P L L 回路 23A から出力されるクロック信号が入力され、さらに選択信号としてカウンタ 24A から出力される相手送信停止検出信号 ST が入力されていることを除いては前述した第 2 の実施形態と同様の構成を有する。

#### 【0078】

ここで、セレクタ 51A は、選択信号として入力される相手送信停止検出信号 ST が論理値 “0” であるときに C D R 回路 28A から供給されるクロック信号を選択して X OR 回路 22A に出力し、相手送信停止検出信号 ST が論理値 “1” であるときには P L L 回路 23A から出力されるクロック信号を X OR 回路 22A に供給するように構成されている。

#### 【0079】

この第 4 の実施形態によると、相手側 L S I チップ 110B でデータ送信を行って、入力バッファ 13A から受信データが出力されている状態では、前述したように X OR 回路 22A の排他的論理和出力信号が論理値 “1” となって、カウンタ 24A がリセット状態に維持され、このカウンタ 24A から出力される相手送信停止検出信号 ST が論理値 “0”

10

20

30

40

50

”となっている。

#### 【0080】

このため、セレクタ51Aでは、相手送信停止検出信号STが論理値“0”であるので、CDR回路28Aから入力される受信データのクロック信号を再生したクロック信号をXOR回路に供給するので、このXOR回路22Aが前述した第2及び第3の実施形態と同様に動作される。

この状態から、相手側LSIチップ110Bで、データ送信が停止されると、前述したように、XOR回路22Aから出力される排他的論理和出力信号が論理値“1”に反転し、これによってカウンタ24Aがカウントを開始し、そのカウント値が所定の判定数に達すると、相手送信停止検出信号STが論理値“0”から論理値“1”に反転する。

#### 【0081】

このため、セレクタ51AでCDR回路28Aからのクロック信号に代えてPLL回路23Aから出力されるクロック信号が選択され、これがXOR回路22Aに供給される。したがって、XOR回路22AはPLL回路23Aから出力されるクロック信号に基づいて FIFO21Aの遅延データ及び入力バッファ13Aの出力データのサンプリングを行うことができ、サンプリング用のクロック信号が途切れることなく継続してXOR回路22Aに供給することができる。このため、カウンタ24Aで生成される相手送信停止検出信号STを相手側LSIチップ110Bのデータ送信が停止している期間中論理値“1”に維持することができる。

#### 【0082】

自己が送信停止状態にあり、相手側LSIチップ110Bが送信停止状態にあって、入力バッファ13Aの出力信号Aがローレベルを維持する状態となったときに、前述した第4の実施形態で説明したように、CDR回路28Aから再生クロック信号が得られない状態となった場合でも、XOR回路22AにPLL回路23Aからクロック信号を供給することができ、相手側LSIチップ110Bがデータ送信を開始して、入力バッファ13Aかち受信データが出力される状態となったときに、直ちにXOR回路22Aの排他的論理和出力信号が論理値“0”から論理値“1”に反転して、カウンタ24Aをリセットし、相手送信停止検出信号STを論理値“0”に復帰させることができ、相手側LSI110Bの通信状態に応じた正確な相手送信停止検出信号STを得ることができる。

#### 【0083】

次に、本発明の第6の実施形態を図15について説明する。

この第6の実施形態では、前述した第4の実施形態のように、CDR回路28Aの内部を変更することなく、相手側LSIチップ110Aのデータ送信停止時にVCO41cでの同期周波数低下を抑制するようにしたものである。

すなわち、第6の実施形態においては、前述した第5の実施形態における図14の構成において、CDR回路28Aの入力側にもセレクタ52Aを接続し、このセレクタ52Aの入力側に入力バッファ13Aの出力信号Aと、PLL回路23Aから出力されるクロック信号とを入力し、さらに選択信号としてカウンタ24Aから出力される相手送信停止検出信号STを入力するようにしたことを除いては図14と同様の構成を有し、図14との対応部分には同一符号を付し、その詳細説明はこれを省略する。

#### 【0084】

ここで、セレクタ52Aは、選択信号として入力される相手送信停止検出信号STが論理値“0”であるときには入力バッファ13Aの出力信号Aを選択してCDR回路28Aに供給し、相手送信停止検出信号STが論理値“1”であるときにPLL回路23Aから出力されるクロック信号をCDR回路28Aに供給するように構成されている。

この第6の実施形態によると、相手側LSIチップ110Bでデータ送信を行っているときには、その受信データが入力バッファ13Aから出力されることにより、XOR回路22Aから論理値“1”的排他的論理和出力信号がカウンタ24Aに出力されて、このカウンタ24Aがリセット状態に維持され、相手送信停止検出信号STが論理値“0”に維持される。

10

20

30

40

50

## 【0085】

このため、セレクタ51Aで前述した第5の実施形態と同様にCDR回路28Aのクロック信号を選択してXOR回路22Aに供給すると共に、セレクタ52Aで入力バッファ13Aから出力される受信データ信号Aを選択してCDR回路28Aに供給するので、前述した第1～第4の実施形態と同様に、CDR回路28Aで入力される受信データ信号Aに基づくクロック信号を再生して、これをセレクタ51Aを介してXOR回路22Aに供給すると共にS-P変換回路25Aに供給して、CPU15Aで受信データの受信処理を行う。

## 【0086】

この相手側LSIチップ110Bの送信状態から相手側LSIチップ110Bでデータ送信が停止されると、前述したようにXOR回路22Aの排他的論理和出力信号が論理値“0”に反転し、これによってカウンタ24Aがカウントを開始して、そのカウント値が所定の判定数に達すると、このカウンタ24Aから出力される相手送信停止検出信号STが論理値“1”に反転し、これによってセレクタ51A及び52AでPLL回路23Aから出力されるクロック信号を選択する。 10

## 【0087】

このため、XOR回路22Aでは前述した第5の実施形態と同様の動作を行い、CDR回路28Aでは、PLL回路23Aから出力されるクロック信号にVCO41cから出力されるクロック信号が一致するように動作するので、両者が一致した時点で第4の実施形態における位相周波数比較器41a-1におけるアップ信号QA及びダウン信号QBが幅の殆どないパルスとなり、チャージポンプ回路41a-2の充放電用コンデンサCの充電電圧が略一定となり、VCO41cから出力されるクロック信号がPLL回路23Aから出力されるクロック信号に同期する。 20

## 【0088】

このとき、PLL回路23Aのクロック信号と、相手側LSIチップ110BのPLL回路のクロック信号とは両者の周波数が近いことが予想されるため、この状態で、相手側LSIチップ110Bがデータ送信を再開した場合に、その受信データが入力バッファ13Aから出力された時点で、XOR回路22Aの排他的論理和出力信号を確実に“1”に反転することができ、これによってカウンタ24Aから出力される相手送信停止検出信号STを論理値“0”に確実に復帰させて、通常受信状態に直ちに復帰させることができる。 30

## 【0089】

このように、第6の実施形態においては、CDR回路28Aの構成を変更することなく、入力バッファ13Aの出力信号Aがローレベルを維持する状態でも、クロック信号を形成することができ、既存の同時双方向入出力回路に容易に適用することができる。

次に、本発明の第7の実施形態を図16について説明する。

この第7の実施形態では、上述した第6の実施形態において、入力バッファ13Aの出力信号Aがローレベルを維持している状態で、CDR回路28AでPLL回路23Aのクロック信号に応じたクロック信号を発生することを考慮して、回路構成を簡略化したものである。 40

## 【0090】

すなわち、第7の実施形態では、上述した第6の実施形態における図15の構成において、セレクタ51Aが省略されて、CDR回路28Aから出力されるクロック信号のみがXOR回路22Aに供給されていることを除いては図15と同様の構成を有し、図15との対応部分には同一符号を付し、その詳細説明はこれを省略する。

この第7の実施形態によると、相手側LSIチップ110Bでデータ送信を停止したときに、相手送信停止検出信号STが論理値“0”から論理値“1”に反転し、これによって、セレクタ52AでCDR回路28Aの位相比較器41aにおける位相周波数比較器41a-1にPLL回路23Aから出力されるクロック信号を信号Aとして供給するので、VCO41cからPLL回路23Aのクロック信号と同期したクロック信号を得ることが 50

でき、このクロック信号がXOR回路22Aに供給されるので、前述した第6の実施形態と同様に入力バッファ13Aの出力信号Aがローレベルを維持する状態となってから相手側LSIチップ110Bでデータ送信を開始したときに、これをXOR回路22A及びカウンタ24Aで検出して、直ちに受信処理状態に復帰することができる。

#### 【0091】

なお、上記第1～第7の実施形態においては、CPU15Aで送受信制御処理を行うことにより、ディゼーブル信号DISA及び反転ディゼーブル信号DISABを生成し、これらを出力バッファ12Aに供給する場合について説明したが、これに限定されるものではなく、出力バッファ12Aの入力信号に基づいて送信データの有無を検出し、送信データが無いときに論理値“1”的ディゼーブル信号DISA及び論理値“0”的反転ディゼーブル信号DISABを形成し、送信データが有るときにその信号DISA及びDISABを夫々反転させるディゼーブル信号形成回路を設けるようにしてもよい。10

#### 【図面の簡単な説明】

#### 【0092】

【図1】本発明の同時双方向入出力システムの第1の実施形態のブロック図である。

【図2】CPUの動作を示すフローチャートである。

【図3】図1の出力バッファの回路図である。

【図4】図1の参照電位発生回路の一例を示す回路図である。

【図5】入出力信号と参照電位との関係を示す相関図である。

【図6】出力バッファの他の構成を示す回路図である。

20

【図7】この発明の同時双方向入出力システムの第2の実施形態のブロック図である。

【図8】この発明の同時双方向入出力システムの第3の実施形態のブロック図である。

【図9】図7のCDR回路に内蔵されたPLL回路のブロック図である。

【図10】図8の位相検出器の詳細を示すブロック図である。

【図11】図9の位相周波数比較器の出力信号を示すタイミングチャートである。

【図12】図9の位相周波数比較器の他の例を示すブロック図である。

【図13】本発明の同時双方向入出力システムの第4の実施形態のブロック図である。

【図14】本発明の同時双方向入出力システムの第5の実施形態のブロック図である。

【図15】本発明の同時双方向入出力システムの第6の実施形態のブロック図である。

【図16】本発明の同時双方向入出力システムの第7の実施形態のブロック図である。

30

#### 【符号の説明】

#### 【0093】

12A, 12B 出力バッファ（出力回路）、13A, 13B 入力バッファ（入力回路）、14A, 14B 参照電位発生回路（参照電位発生回路）、21A 先入れ先出しバッファ（相手送信停止中検出手段）、22A 排他的論理和回路（相手送信停止中検出手段）、23A フェーズロックドループ回路（転送速度増加手段）、24A カウンタ（相手送信停止中検出手段）、26A クロックデータリカバリ回路、41a 位相検出器（同期周波数検出手段）、N2, P2 トランジスタ（貫通電流抑制手段）、41a-1a, 41a-1'a, 41a-1'b AND素子（同期動作停止手段）、52A（入力切り替え手段）。

40

【 図 1 】

【 四 2 】

( 3 )

( 4 )

( 义 7 )

【 5 】

| 入出力とリファレンス電圧の関係 |      |      |      |      |       |       |      |      |

|-----------------|------|------|------|------|-------|-------|------|------|

| TXDA            | 電位   | TXDB | 電位   | 路線   | VrefA | VrefB | RXDA | RXDB |

| L               | 1.8V | L    | 1.8V | 1.8V | 1.5V  | 1.5V  | L    | L    |

| H               | OV   | L    | 1.8V | 0.9V | 0.6V  | 1.5V  | L    | H    |

| L               | 1.8V | H    | OV   | 0.9V | 1.5V  | 0.6V  | H    | L    |

| H               | OV   | H    | OV   | 0V   | 0.6V  | 0.6V  | H    | H    |

〔 図 6 〕

The diagram illustrates the internal architecture of the RDR module. It consists of several functional blocks:

- TX/RX Path:** A central block labeled "110A" contains a SER (Serial-to-Parallel converter) and a TX/RX section. The TX path includes a 20A block, a PLL, and a FIFO. The RX path includes a 23A SI block.

- Timing and Control:** A COUNTER block (22A) provides timing signals to various components. A Vref Gen block (11A) generates reference voltages. A DSRB (Digital Signal Register Bank) block (12A) is connected to the TX/RX path.

- Memory and Data Flow:** A CPU block is connected to the TX/RX path via a 30A block. A Do-SER (Data-to-Serial converter) block (24A) converts data from the CPU to the TX path. A CDR (Clock Recovery and Demodulation) block (25A) receives data from the RX path and provides clock recovery to the CPU. A RDRA (Register and Decoder) block (26A) is also connected to the RX path.

- Power Management:** A Vref N block (13A) provides negative voltage regulation to the Vref Gen block.

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

|                          |                |            |

|--------------------------|----------------|------------|

| (51)Int.Cl. <sup>7</sup> | F I            | テーマコード(参考) |

| H 0 4 L 5/14             | H 0 3 K 19/094 | B          |

|                          | H 0 3 K 17/687 | F          |

F ターム(参考) 5J055 AX27 BX16 CX24 DX22 DX56 DX72 DX83 EX02 EY01 EY10

EY21 EZ03 EZ07 EZ10 EZ12 EZ25 EZ28 EZ31 FX18 FX37

GX01 GX02 GX03

5J056 AA01 AA04 BB19 CC01 CC09 CC14 CC16 DD13 DD29 DD51

EE06 EE08 FF07 FF08 GG12 KK00

5K018 AA02 CA02 CA06 DA02 DA06 DA13 EA07