(12) 发明专利申请

(10) 申请公布号 CN 114007024 A

(43) 申请公布日 2022.02.01

(21) 申请号 202111356352.7

H04N 5/378 (2011.01)

(22) 申请日 2017.02.27

H01L 27/146 (2006.01)

(30) 优先权数据

2016-038161 2016.02.29 JP

(62) 分案原申请数据

201780025799.1 2017.02.27

(71) 申请人 株式会社尼康

地址 日本东京都

(72) 发明人 驹井敦

(74) 专利代理机构 北京市金杜律师事务所

11256

代理人 沈静

(51) Int.Cl.

H04N 5/363 (2011.01)

H04N 5/3745 (2011.01)

权利要求书1页 说明书16页 附图13页

(54) 发明名称

摄像元件及摄像装置

(57) 摘要

本发明提供摄像元件及摄像装置。摄像元件具备：多个像素，其具有将从衬底的一侧入射的入射光转换成电荷的光电转换部、和输出基于所述电荷的信号的输出部，并沿第1方向和与所述第1方向交叉的第2方向配置；和蓄积部，其与所述光电转换部层叠地设置在所述衬底的一侧的相反侧，并蓄积所述信号。

1. 一种摄像元件，其特征在于，具备：

光电转换部，其将光转换成电荷；

输出部，其用于输出基于由所述光电转换部转换得到的电荷的信号；

第1信号线，从所述输出部向该第1信号线输出信号；和

第2信号线，其用于保持输出到所述第1信号线的信号。

2. 根据权利要求1所述的摄像元件，其特征在于，

具备用于将所述第1信号线与所述第2信号线电连接的第1连接部。

3. 根据权利要求1或2所述的摄像元件，其特征在于，

具备对所述第2信号线所保持的信号进行处理的处理部，

还具备用于将所述第2信号线与所述处理部电连接的第2连接部。

4. 根据权利要求3所述的摄像元件，其特征在于，

所述处理部是如下电路，该电路输出基于由所述光电转换部转换得到的电荷的信号、

与用于对基于由所述光电转换部转换得到的电荷的信号进行修正的信号的差分。

5. 根据权利要求3所述的摄像元件，其特征在于，

所述处理部是将从所述输出部输出的模拟信号转换成数字信号的AD转换电路。

6. 根据权利要求1～5中任一项所述的摄像元件，其特征在于，

所述第2信号线由被施加规定电位的布线和导体构成。

7. 根据权利要求1～6中任一项所述的摄像元件，其特征在于，

所述第2信号线具有：第3信号线，其保持基于由所述光电转换部转换得到的电荷的信号；和第4信号线，其保持用于对基于由所述光电转换部转换得到的电荷的信号进行修正的信号。

8. 根据权利要求7所述的摄像元件，其特征在于，

具备：

第1布线，其设于所述第1信号线、与所述第3信号线及所述第4信号线之间，并被施加规定电位；和

第2布线，其设于所述第3信号线与所述第4信号线之间，并被施加所述规定电位。

9. 根据权利要求1～8中任一项所述的摄像元件，其特征在于，

具备：

基板，其具有所述光电转换部和所述输出部；以及

布线层，其具有所述第1信号线和所述第2信号线。

10. 一种摄像装置，其特征在于，具备：

权利要求1～9中任一项所述的摄像元件；和

图像生成部，其基于所述摄像元件的所述信号生成图像数据。

## 摄像元件及摄像装置

[0001] 本申请是中国专利申请号为201780025799.1、进入国家阶段日期为2018年10月25日，国际申请日为2017年2月27日、PCT国际申请号为PCT/JP2017/007548、发明名称为“摄像元件及摄像装置”的发明专利申请的分案申请。

### 技术领域

[0002] 本发明涉及摄像元件及摄像装置。

### 背景技术

[0003] 已知一种通过在一个像素列设置多个电容而能够在从某行像素读出信号的期间将来自其它行像素的信号水平传输的摄像元件(专利文献1)。但是，在现有技术中，存在由于设置很多电容而导致摄像元件的芯片面积增大的隐患。

[0004] 现有技术文献

[0005] 专利文献

[0006] 专利文献1：日本特开2001-45375号公报

### 发明内容

[0007] 根据本发明的第1方式，摄像元件具备：多个像素，其具有将从衬底的一侧入射的入射光转换成电荷的光电转换部、和输出基于所述电荷的信号的输出部，并沿第1方向和与所述第1方向交叉的第2方向配置；和蓄积部，其与所述光电转换部层叠地设置在所述衬底的一侧的相反侧，并蓄积所述信号。

[0008] 根据本发明的第2方式，摄像元件具备：第1层，其具有将入射至半导体衬底的第1面的光转换成电荷的光电转换部、和向所述半导体衬底的第2面输出基于所述电荷的信号的输出部；和第2层，其在所述第2面层叠于所述第1层，并具有蓄积由所述输出部输出的信号的蓄积部。

[0009] 根据本发明的第3方式，摄像元件具备：多个像素，其具有将从入射面入射的光转换成电荷的光电转换部，并输出基于所述电荷的信号；和蓄积部，其蓄积从所述像素输出的所述信号，所述蓄积部配置在所述多个像素之间。

[0010] 根据本发明的第4方式，摄像元件具备：多个像素，其具有将从入射面入射的光转换成电荷的光电转换部，并输出基于所述电荷的信号；和蓄积部，其蓄积从所述像素输出的所述信号，所述像素配置在所述入射面与所述蓄积部之间。

[0011] 根据本发明的第5方式，摄像元件具有：多个像素，其具有将所入射的光转换成电荷的光电转换部、被传输由所述光电转换部进行光电转换而得到的电荷的第一蓄积部、和将基于被传输至所述第一蓄积部的电荷的信号输出的输出部；输出控制部，其使基于从所述光电转换部传输至所述第一蓄积部的电荷的像素信号、与将所述第一蓄积部的电荷重置得到的重置信号进行切换并从所述输出部输出；第二蓄积部，其蓄积从所述输出部输出的所述像素信号；和第三蓄积部，其蓄积从所述输出部输出的所述重置信号，所述像素配置在供所述光

入射的面、与所述第2蓄积部或所述第3蓄积部之间。

[0012] 根据本发明的第6方式，摄像装置具备：第1～5中任一方式的摄像元件；和图像生成部，其基于所述摄像元件的所述信号生成图像数据。

## 附图说明

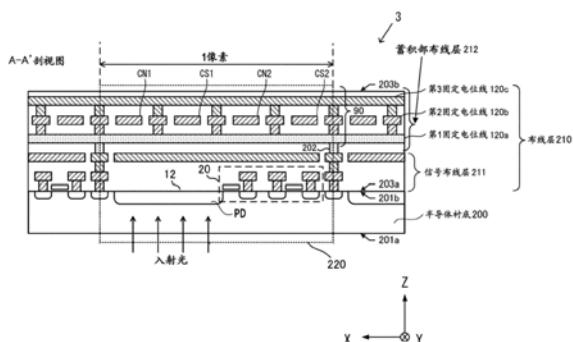

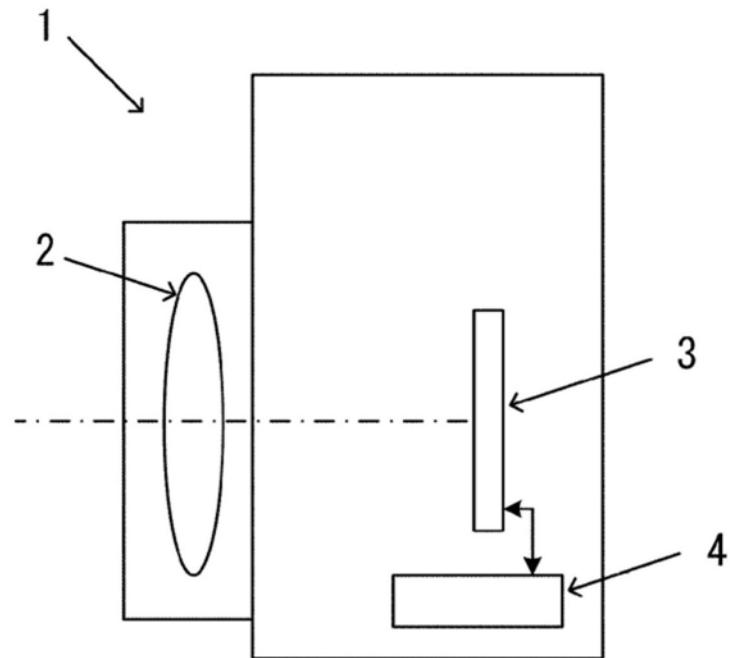

- [0013] 图1是表示第1实施方式的摄像装置的结构的框图。

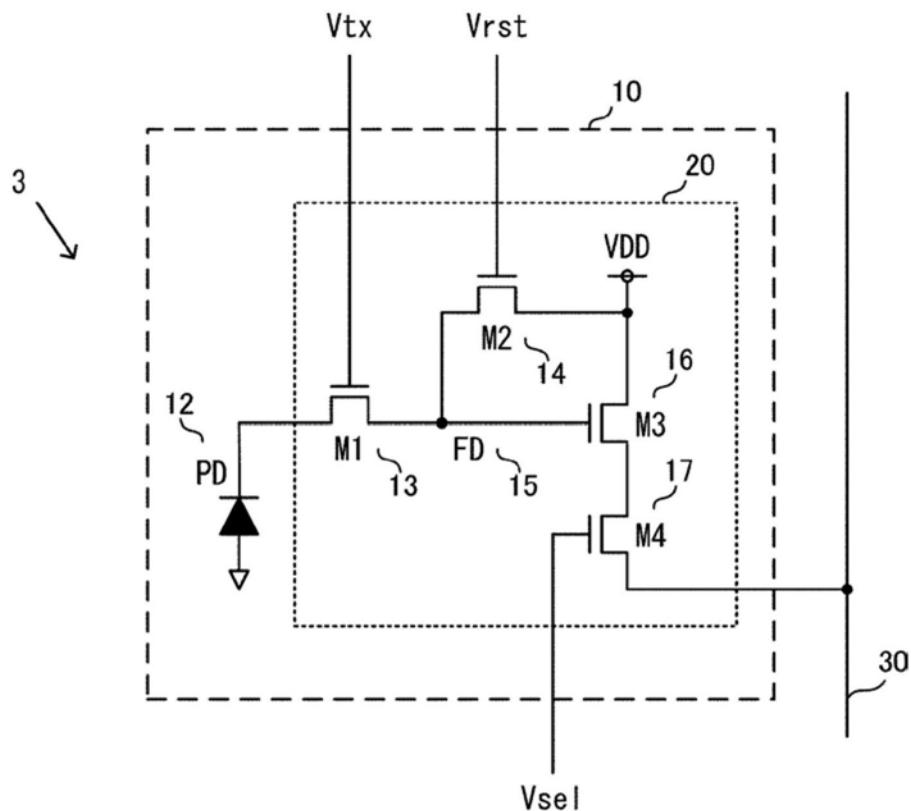

- [0014] 图2是表示第1实施方式的像素的结构的电路图。

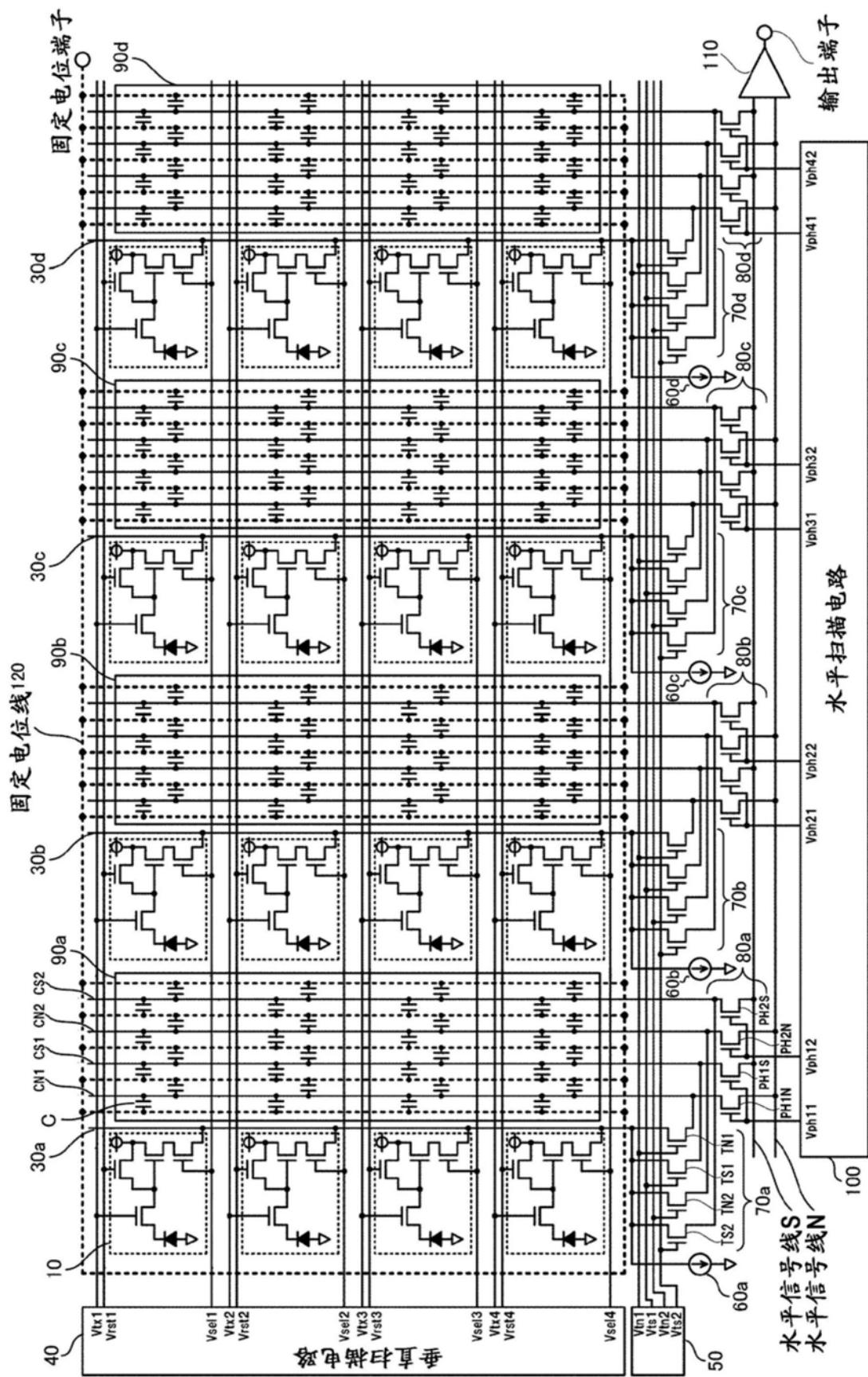

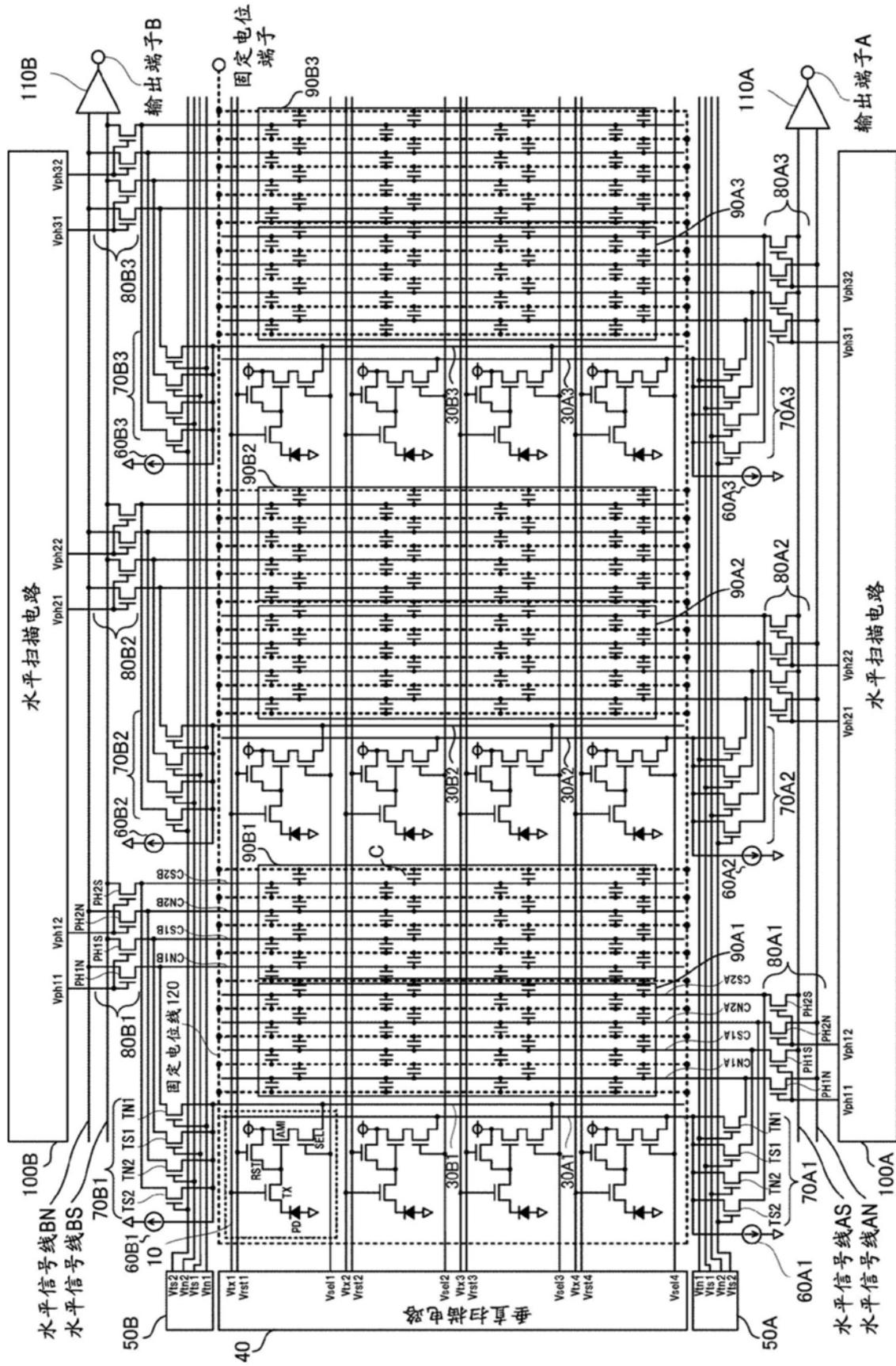

- [0015] 图3是表示第1实施方式的摄像元件的局部结构的电路图。

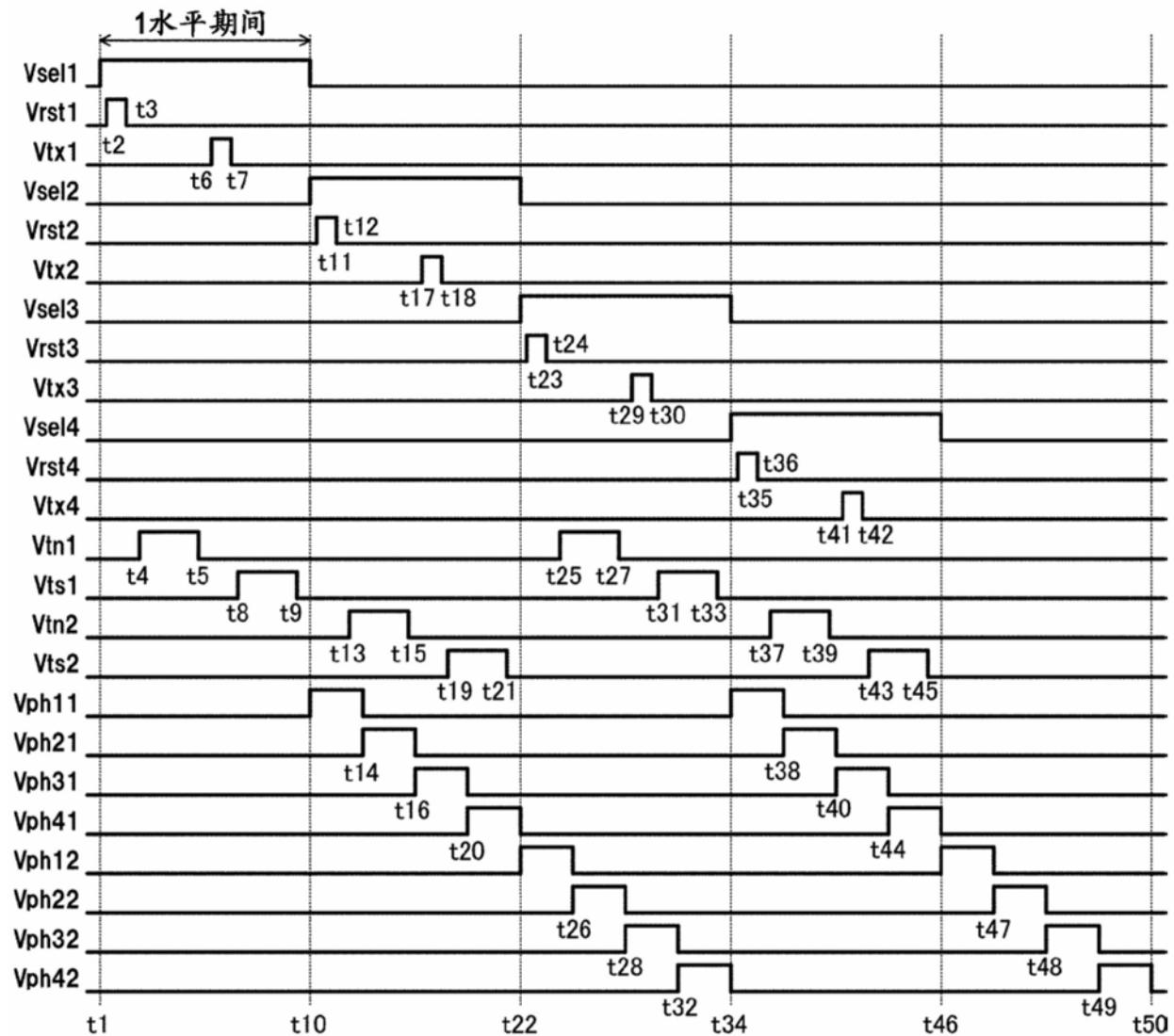

- [0016] 图4是表示第1实施方式的摄像元件的动作例的时序图。

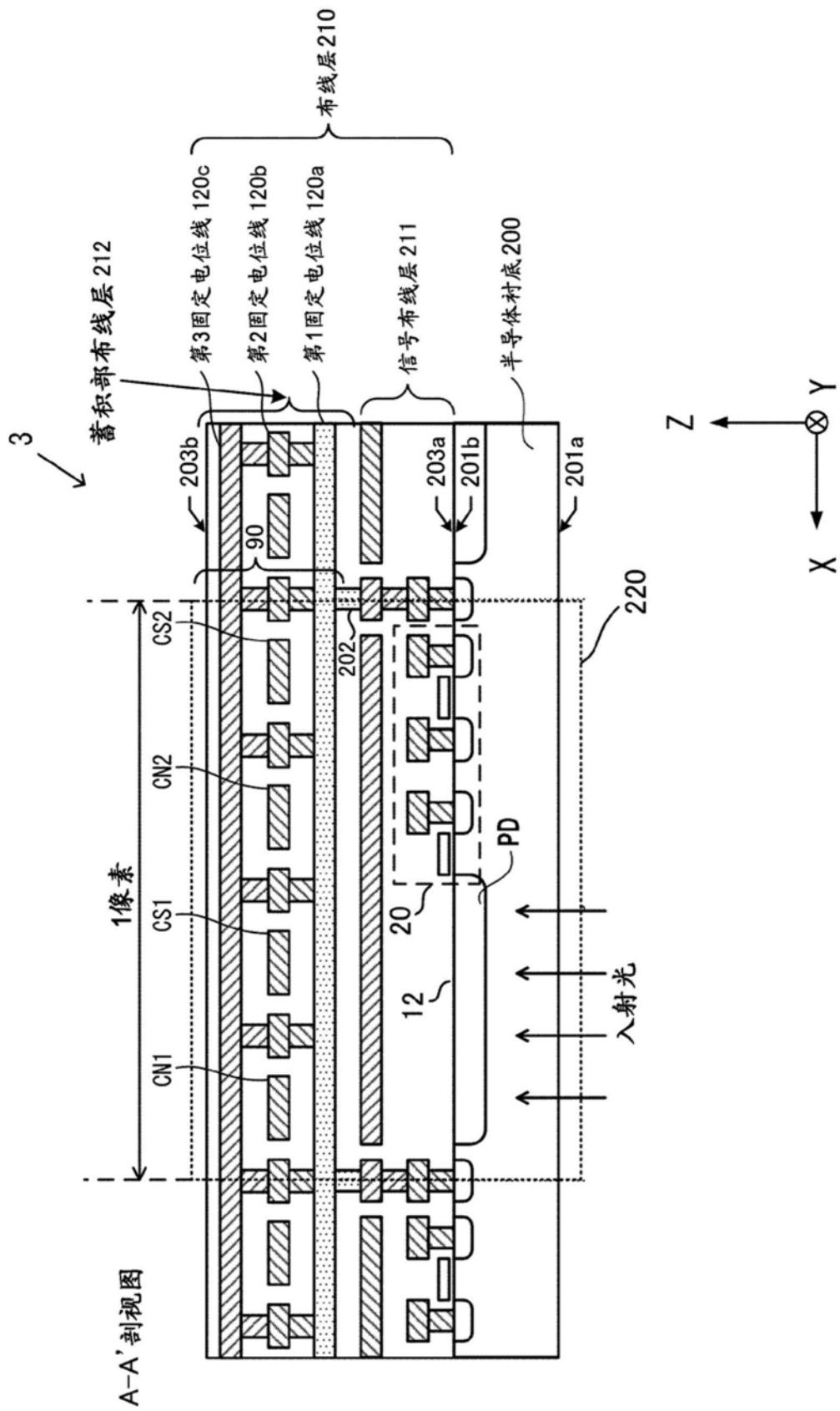

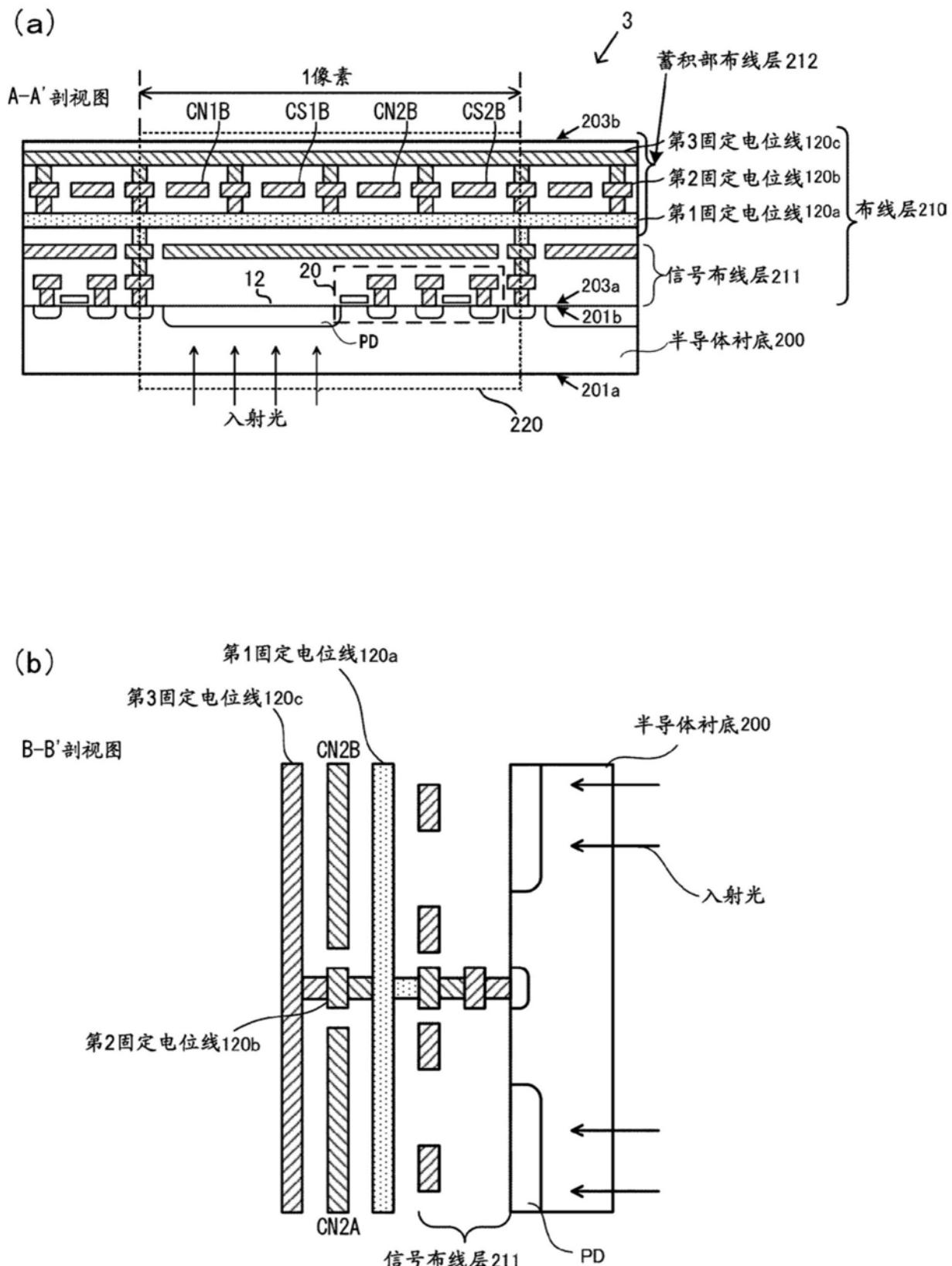

- [0017] 图5是表示第1实施方式的摄像元件的剖面结构的一例的图。

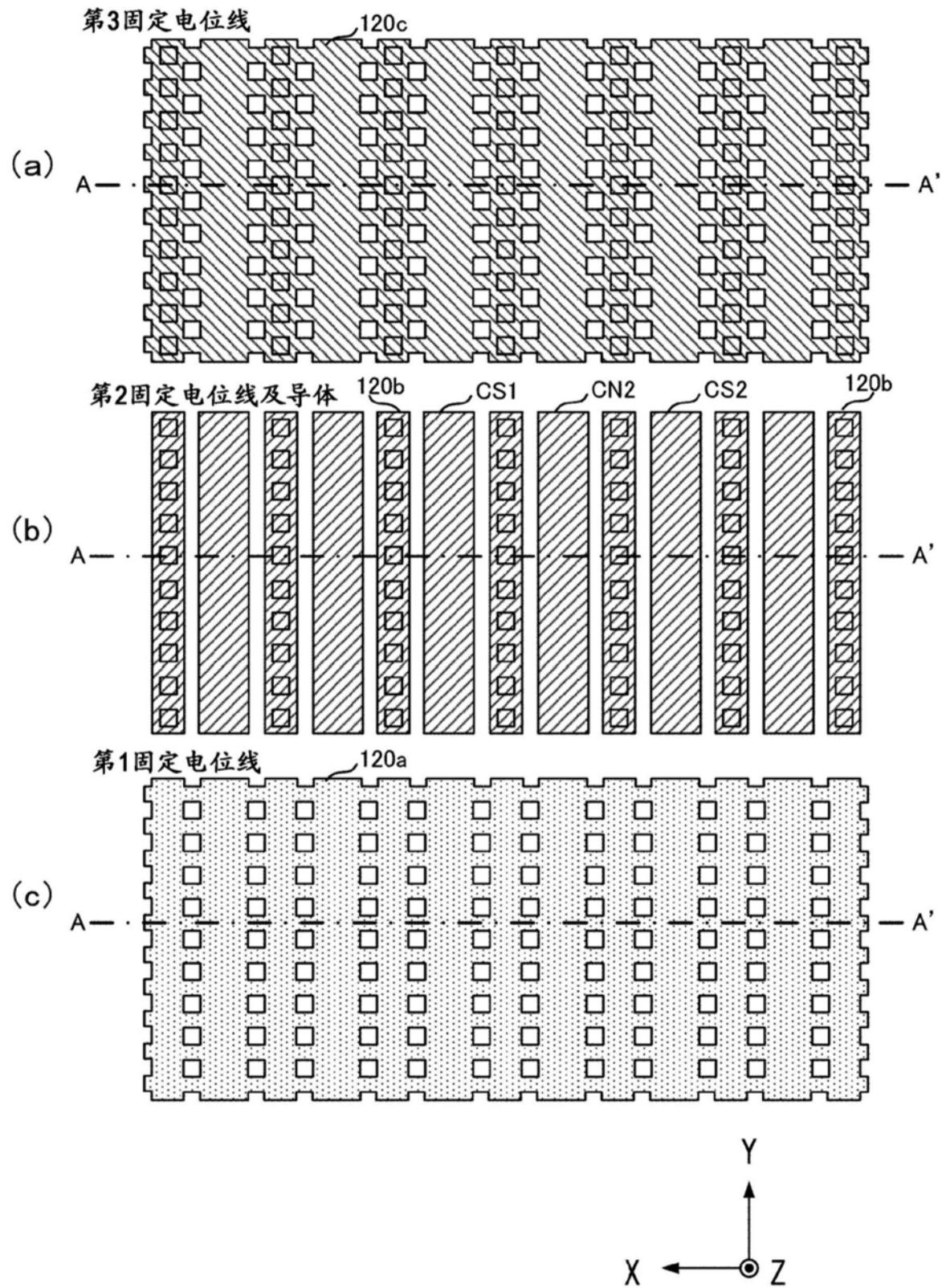

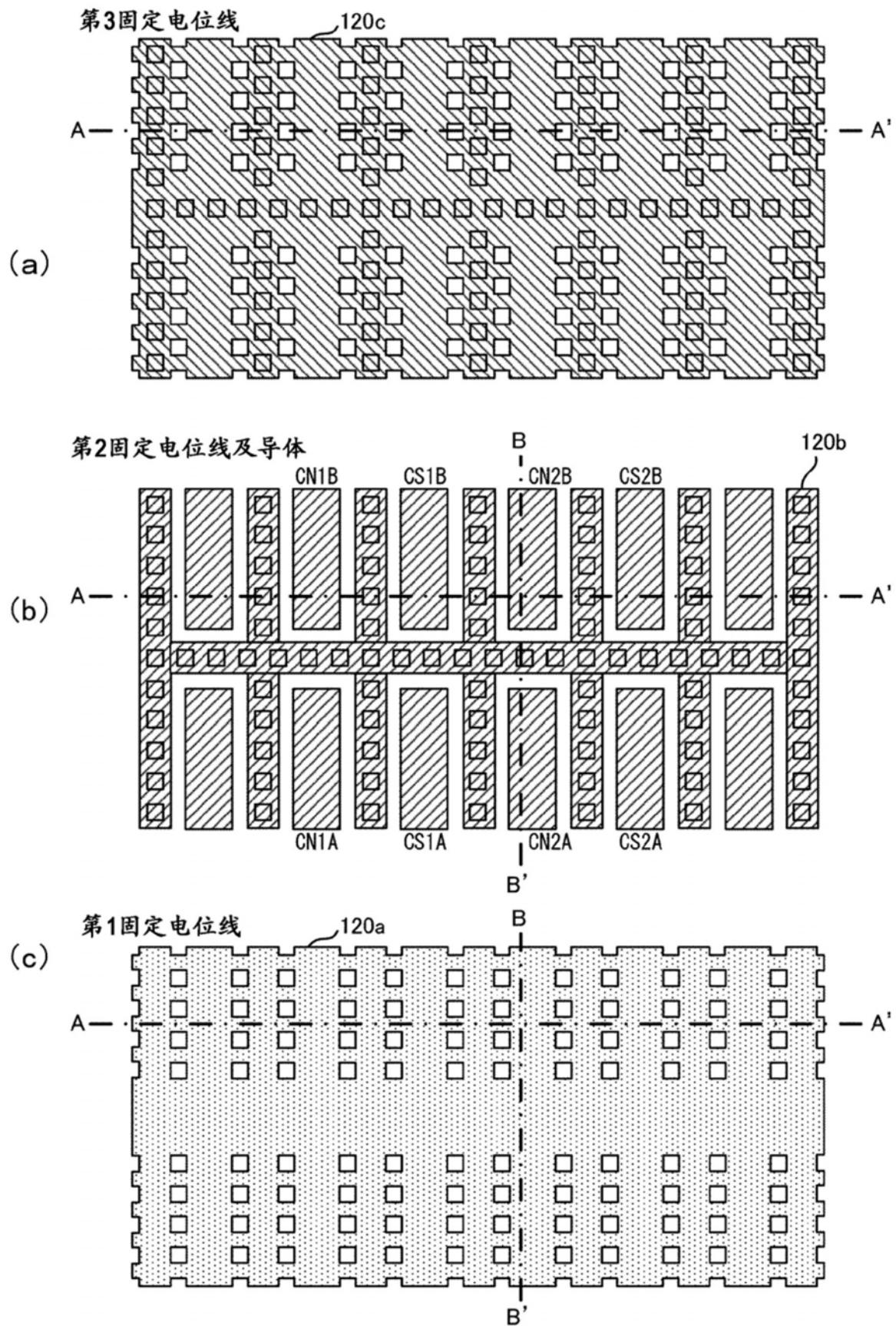

- [0018] 图6是表示第1实施方式的摄像元件的蓄积部布线层的一部分的平面布局例的图。

- [0019] 图7是表示第2实施方式的摄像元件的局部结构的电路图。

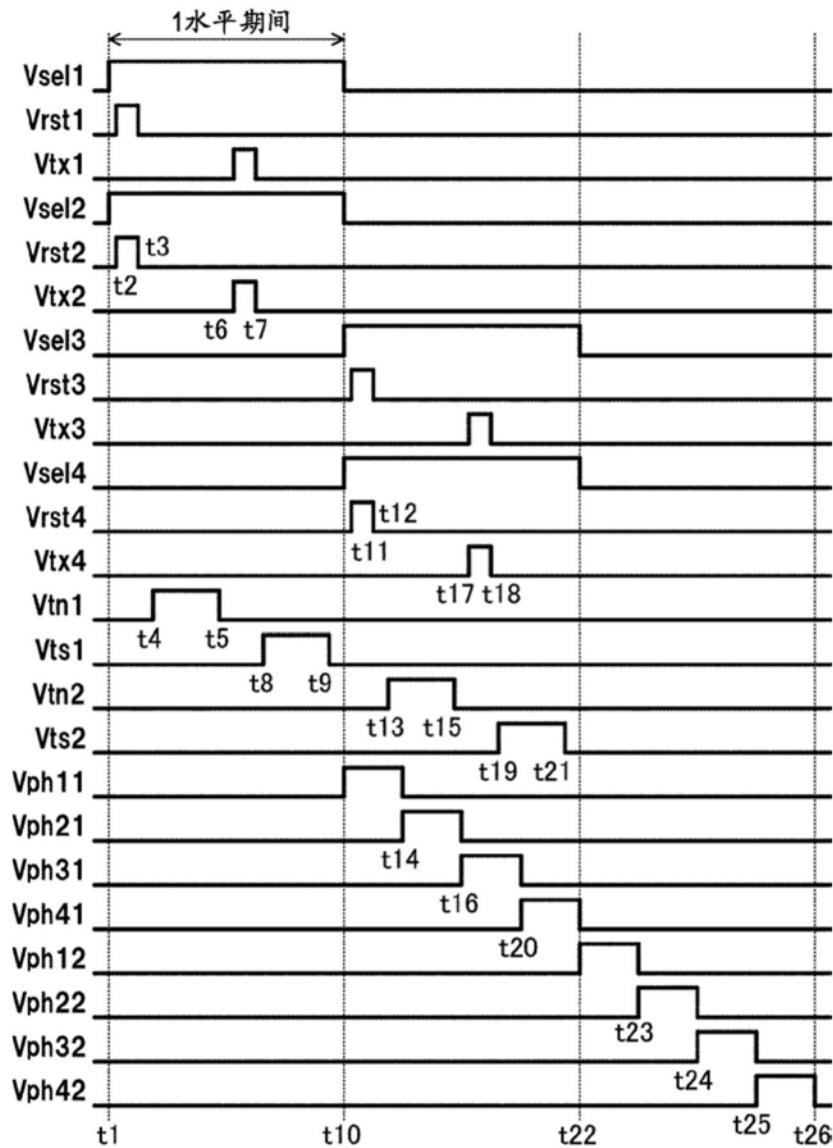

- [0020] 图8是表示第2实施方式的摄像元件的动作例的时序图。

- [0021] 图9是表示第2实施方式的摄像元件的剖面结构的一例的图。

- [0022] 图10是表示第2实施方式的摄像元件的蓄积部布线层的一部分的平面布局例的图。

- [0023] 图11是表示第3实施方式的摄像元件的局部结构的电路图。

- [0024] 图12是表示第3实施方式的摄像元件的剖面结构的一例的图。

- [0025] 图13是表示第3实施方式的摄像元件的蓄积部布线层的一部分的平面布局例的图。

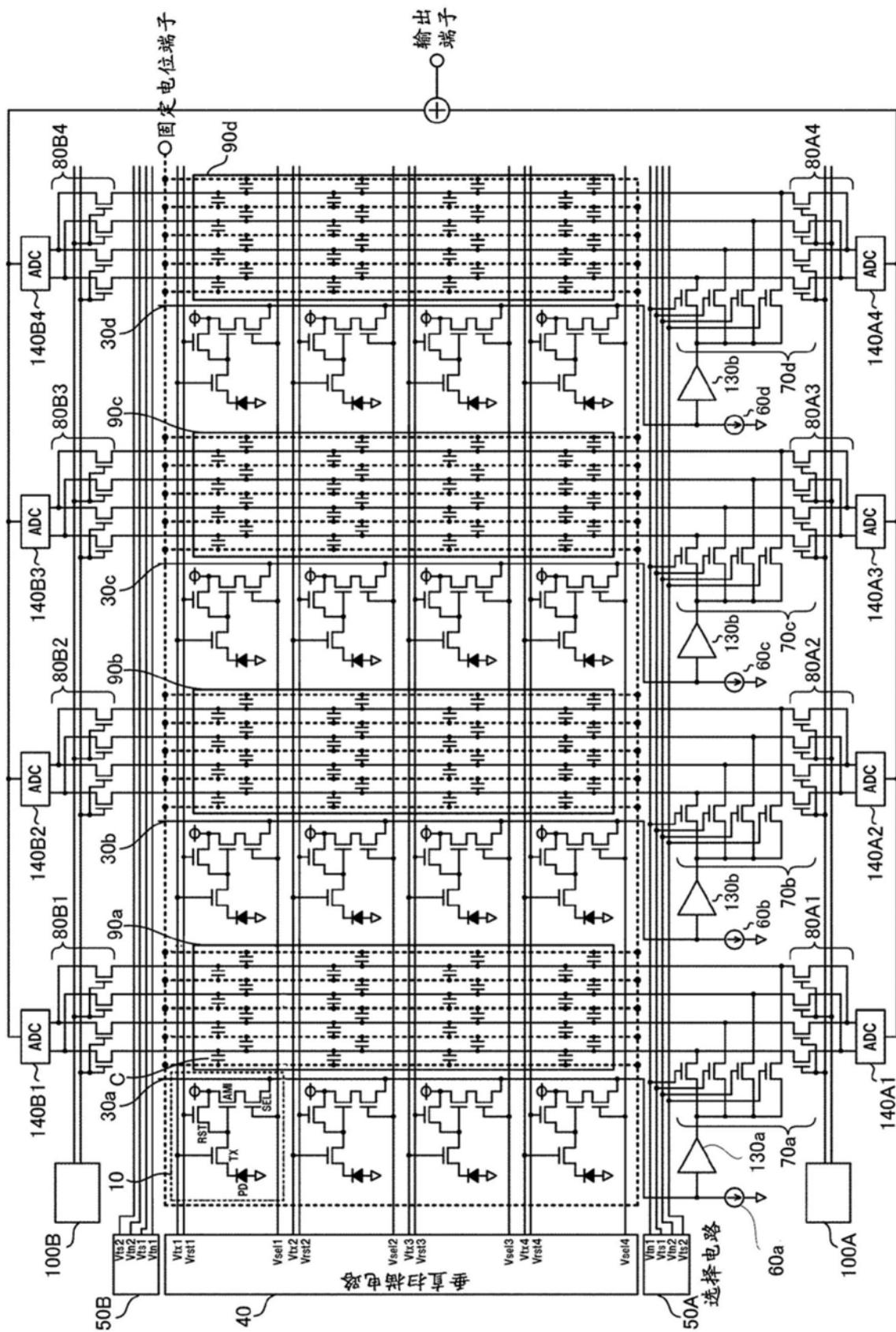

- [0026] 图14是变形例1的摄像元件的局部结构的电路图。

- [0027] 附图标记说明

- [0028] 3:摄像元件, 12:光电转换部, 20:读出部, 90:蓄积部, 200:半导体衬底

## 具体实施方式

[0029] (第1实施方式)

[0030] 图1是表示第1实施方式的摄像装置1的结构的框图。摄像装置1具备摄影光学系统2、摄像元件3、及控制部4。摄像装置1例如是相机。摄影光学系统2使被摄体像在摄像元件3上成像。摄像元件3拍摄由摄影光学系统2形成的被摄体像并生成图像信号。摄像元件3例如是CMOS图像传感器。控制部4将用于控制摄像元件3的动作的控制信号向摄像元件3输出。另外，控制部4作为对从摄像元件3输出的图像信号实施各种图像处理并生成图像数据的图像生成部发挥功能。此外，摄影光学系统2也可以能够相对于摄像装置1拆装。

[0031] 图2是表示第1实施方式的像素10的结构的电路图。摄像元件3具有呈二维状配置的多个像素10。像素10具有例如光电二极管(PD)等光电转换部12及读出部20。光电转换部12具有将入射的光转换成电荷并蓄积光电转换得到的电荷的功能。读出部20具有传输部13、排出部14、浮置扩散部(FD)15、放大部16、和选择部17。

[0032] 传输部13通过信号V<sub>tx</sub>而被控制，将由光电转换部12进行光电转换而得到的电荷向浮置扩散部15传输。即，传输部13在光电转换部12与浮置扩散部15之间形成电荷传输路径。浮置扩散部15保持(蓄积)电荷。放大部16将基于保持于浮置扩散部15的电荷的信号放

大,并经由选择部17向垂直信号线30输出。在图2的示例中,放大部16由漏极端子、栅极端子及源极端子分别与电源VDD、浮置扩散部15及选择部17连接的晶体管M3构成。放大部16的源极端子经由选择部17与垂直信号线30连接。放大部16将后述的电流源60作为负荷电流源而作为源极跟随器电路的一部分发挥功能。

[0033] 排出部(重置部)14通过信号Vrst而被控制,排出浮置扩散部15的电荷,将浮置扩散部15的电位重置成重置电位(基准电位)。选择部17通过信号Vsel而被控制,将来自放大部16的信号向垂直信号线30输出。传输部13、排出部14、及选择部17例如分别由晶体管M1、晶体管M2、晶体管M4构成。

[0034] 读出部20将与通过传输部13从光电转换部12传输至浮置扩散部15的电荷相应的信号(光电转换信号)、和将浮置扩散部15的电位重置成重置电位时的信号(噪声信号)向垂直信号线30读出。噪声信号成为表示相对于光电转换信号而言的基准电平的基准信号。另外,放大部16及选择部17构成将基于蓄积于浮置扩散部15的电荷的信号输出的输出部,输出部将光电转换信号、噪声信号向垂直信号线30输出。

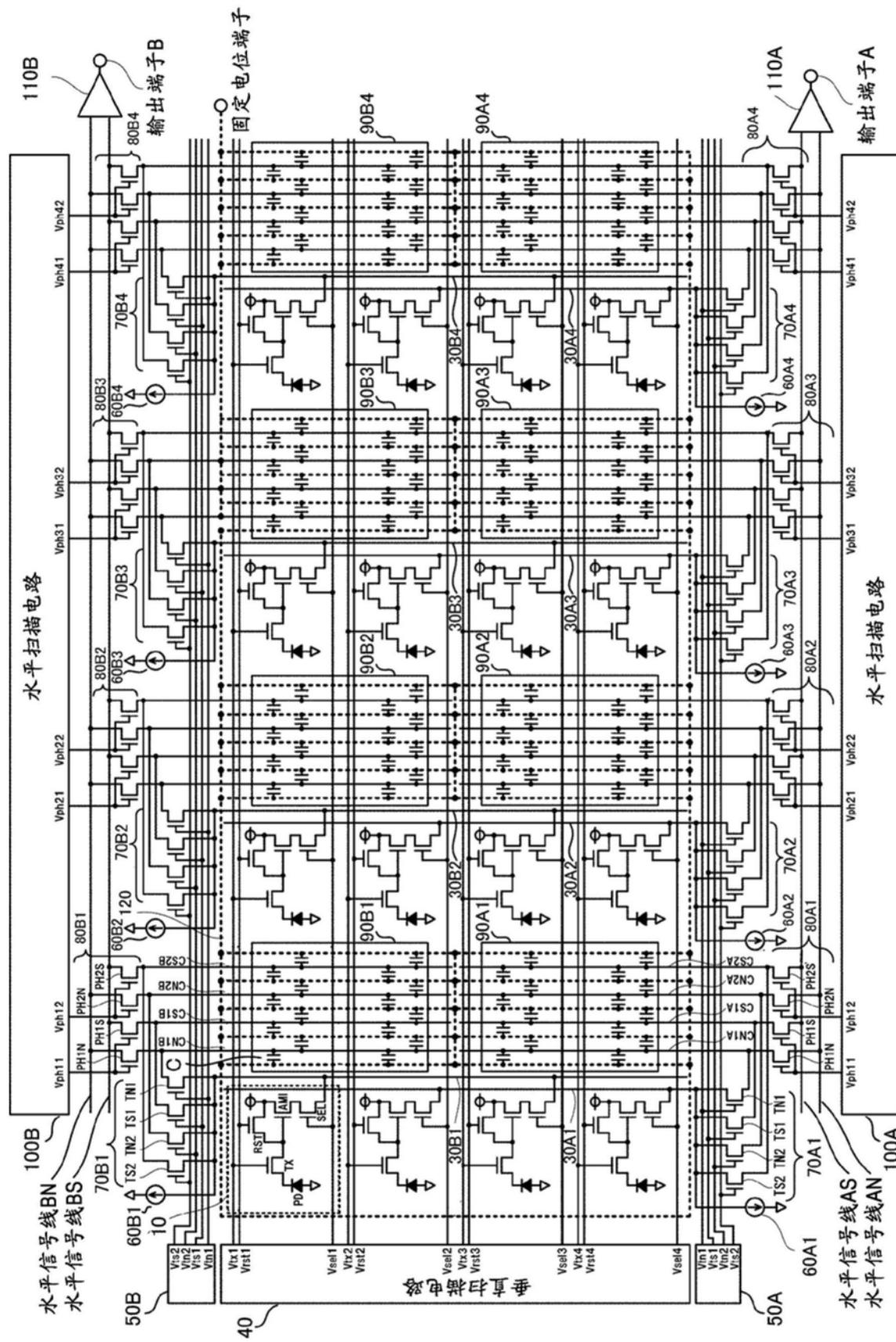

[0035] 图3是表示第1实施方式的摄像元件3的一部分结构的电路图。摄像元件3具有:配置成矩阵状的多个像素10、垂直扫描电路40、选择电路50、电流源60(电流源60a~电流源60d)、第1开关部70(第1开关部70a~第1开关部70d)、第2开关部80(第2开关部80a~第2开关部80d)、蓄积部90(蓄积部90a~蓄积部90d)、水平扫描电路100、和输出放大器部110。在图3中是电路图,为了容易理解而与像素10并置地描绘了蓄积部90,但实际上在像素10呈矩阵状密集配置的像素区域内,蓄积部90层叠于半导体衬底而配置。像素区域是呈二维状配置有多个具有光电转换部12及读出部20的像素10的区域。即,在像素区域内,沿第1方向(例如列方向)及与其交叉的第2方向(例如行方向)配置有多个像素10。在像素区域外配置有周边电路(垂直扫描电路40、水平扫描电路100等)。

[0036] 在图3中左端的配置有第1列像素列的像素区域设有蓄积部90a,在其右侧相邻位置的配置有第2列像素列的像素区域设有蓄积部90b。同样地,与第3列像素列对应地设有蓄积部90c,并与第3列像素列的右侧相邻位置的第4列像素列对应地设有蓄积部90d。在本实施方式中,蓄积部90在像素区域内层叠于半导体衬底。蓄积部90在与半导体衬底层叠的方向上与像素10并置配置。因此,无需使芯片面积增大就能获得大的电容值。

[0037] 针对由沿列方向即纵向排列的多个像素10构成的像素列的每一列设有蓄积部90、电流源60、第1开关部70、及第2开关部80。即,在图3中与左端的第1列像素列对应地设有蓄积部90、电流源60、第1开关部70、及第2开关部80,同样地,与第1列像素列的右侧相邻位置的第2列像素列、第2列像素列的右侧相邻位置的第3列像素列、及第3列像素列的右侧相邻位置的第4列像素列分别对应地设有蓄积部90、电流源60、第1开关部70、及第2开关部80。

[0038] 另外,与像素10的各列对应地设有垂直信号线30(垂直信号线30a~垂直信号线30d)。此外,在图3的示例中,为了简化说明而对于像素10仅图示了水平方向4像素×垂直方向4像素。

[0039] 电流源60a~电流源60d分别与垂直信号线30a~垂直信号线30d对应地设置,并与垂直信号线30a~垂直信号线30d连接。另外,电流源60a~电流源60d分别经由垂直信号线30a~垂直信号线30d与各像素10连接。电流源60a~电流源60d生成用于从各像素10读出光电转换信号及噪声信号的电流。电流源60a~电流源60d分别将所生成的电流向垂直信号线

30a～垂直信号线30d及各像素10供给。

[0040] 垂直扫描电路40将信号Vtxn、信号Vrstn、信号Vsln等控制信号向各像素10供给。垂直扫描电路40将信号Vtxn等向各像素10输出,控制各像素10的动作。此外,Vtxn、Vrstn、Vsln的末尾的n表示像素的行编号。例如,信号Vtx1是控制第1行像素10的传输部13的信号。

[0041] 第1开关部70a～第1开关部70d分别与垂直信号线30a～垂直信号线30d对应地设置,并与垂直信号线30a～垂直信号线30d连接。第1开关部70a～第1开关部70d切换垂直信号线30a～垂直信号线30d与蓄积部90a～蓄积部90d之间的电连接状态。第1开关部70a～第1开关部70d通过从选择电路50输出的控制信号而被控制,将从各像素10输出的光电转换信号及噪声信号分别向蓄积部90a～蓄积部90d传输。第1开关部70a～第1开关部70d分别具有开关TN1、开关TS1、开关TN2、和开关TS2。开关TN1、开关TS1、开关TN2及开关TS2分别由晶体管构成。

[0042] 第2开关部80a～第2开关部80d分别与垂直信号线30a～垂直信号线30d对应地设置。第2开关部80a～第2开关部80d切换蓄积部90a～蓄积部90d与输出放大器部110之间的电连接状态。第2开关部80a～第2开关部80d通过从水平扫描电路100输出的控制信号而被控制,将蓄积于蓄积部90a～蓄积部90d的光电转换信号及噪声信号经由水平信号线S及水平信号线N向输出放大器部110传输。第2开关部80a～第2开关部80d分别具有开关PH1N、开关PH1S、开关PH2N、和开关PH2S。开关PH1N、开关PH1S、开关PH2N及开关PH2S分别由晶体管构成。

[0043] 选择电路50将信号Vtn1、信号Vts1、信号Vtn2、信号Vts2等控制信号向第1开关部70a～第1开关部70d供给。选择电路50输出控制信号,控制第1开关部70a～第1开关部70d的动作。

[0044] 水平扫描电路100将信号Vph11、信号Vph12、信号Vph21、信号Vph22、信号Vph31、信号Vph32、信号Vph41、信号Vph42等控制信号向第2开关部80a～第2开关部80d供给。水平扫描电路100输出控制信号,控制第2开关部80a～第2开关部80d的动作。

[0045] 蓄积部90a～蓄积部90d与各像素10的列对应地设置,并蓄积(存储)从各像素10输出的光电转换信号及噪声信号。蓄积部90a～蓄积部90d具有用于蓄积光电转换信号及噪声信号的电容。电容例如是基于导体的电容,是由相邻的金属形成的电容等。具体而言,例如是在被输入光电转换信号或噪声信号的导体、与被提供规定电位的导体之间形成的电容。此外,稍后使用图5及图6对蓄积部90a～蓄积部90d的具体结构例进行具体说明。

[0046] 在图3的示例中,蓄积部90a～蓄积部90d分别具有被输入噪声信号的导体CN1及CN2、和被输入光电转换信号的导体CS1及CS2。另外,蓄积部90a～蓄积部90d分别具有固定电位线120来作为上述被提供规定电位的导体。此外,在图3中,固定电位线120为了区别于导体CN1、导体CS1、导体CN2、导体CS2而由虚线表示。

[0047] 向图3所示的固定电位端子供给例如电源电位或接地电位,从而对固定电位线120提供电源电位或接地电位。图3所示的表示多个电容的符号C示意性地表示在导体CN1与固定电位线120之间、导体CS1与固定电位线120之间、导体CN2与固定电位线120之间、及导体CS2与固定电位线120之间分别形成有电容。在本实施方式中,导体CN1及CN2作为蓄积噪声信号的噪声用蓄积部发挥功能,导体CS1及CS2作为蓄积光电转换信号的信号用蓄积部发挥

功能。

[0048] 输出放大器部110将基于经由水平信号线N输入的噪声信号与经由水平信号线S输入的光电转换信号的差分得到的信号向图3所示的输出端子输出。例如，输出放大器部110输出将噪声信号与光电转换信号的差分以规定的增益放大后的信号。

[0049] 图4是表示第1实施方式的摄像元件3的动作例的时序图。在图4中，纵轴表示控制信号的电压电平，横轴表示时刻。在图4所示的时序图中，在控制信号为高电平(例如电源电位)的情况下，被输入控制信号的晶体管成为接通(ON，导通)状态，在控制信号为低电平(例如接地电位)的情况下，被输入控制信号的晶体管成为断开(OFF，截止)状态。时刻t1～时刻t10、时刻t10～时刻t22、时刻t22～时刻t34、时刻t34～时刻t46、及时刻t46～时刻t50分别成为一个水平期间(1水平期间)。

[0050] 此外，蓄积于光电转换部12的电荷与浮置扩散部15的电荷的排出、即浮置扩散部15的重置同步地被重置，但在以下说明中，为了简化说明而省略关于光电转换部12的重置的说明。

[0051] 在时刻t1，信号Vsel1变成高电平，从而在第1行的各像素10中选择部17的晶体管M4接通。在时刻t2，信号Vrst1变成高电平，从而在第1行的各像素10中排出部14的晶体管M2接通。由此，浮置扩散部15的电位变成重置电位。另外，第1行的各像素10的噪声信号由放大部16及选择部17分别向垂直信号线30a～垂直信号线30d输出。在时刻t3，信号Vrst1变成低电平，从而晶体管M2断开。在时刻t4，信号Vtn1变成高电平，从而第1开关部70a～第1开关部70d各自的开关TN1接通。由此，来自各像素10的噪声信号被传输至蓄积部90a～蓄积部90d的导体CN1。附加于蓄积部90a～蓄积部90d的导体CN1的电容分别蓄积来自第1行的各像素10的噪声信号。在时刻t5，信号Vtn1变成低电平，从而开关TN1断开。当开关TN1断开时，附加于导体CN1的电容保持(蓄积)噪声信号。

[0052] 在时刻t6，信号Vtx1变成高电平，从而在第1行的各像素10中传输部13的晶体管M1接通。由此，由光电转换部12进行光电转换而得到的电荷被传输至浮置扩散部15。另外，第1行的各像素10的光电转换信号由放大部16及选择部17向垂直信号线30a～垂直信号线30d输出。在时刻t7，信号Vtx1变成低电平，从而晶体管M1断开。在时刻t8，信号Vts1变成高电平，从而第1开关部70a～第1开关部70d各自的开关TS1接通。由此，光电转换信号被传输至蓄积部90a～蓄积部90d的导体CS1。附加于导体CS1的电容蓄积来自第1行的各像素10的光电转换信号。在时刻t9，信号Vts1变成低电平，从而开关TS1断开。当开关TS1断开时，附加于导体CS1的电容保持光电转换信号。

[0053] 在时刻t10，信号Vph11及信号Vsel2变成高电平。由于信号Vph11变成高电平，从而第2开关部80a的开关PH1N及开关PH1S接通。由此，蓄积在与各像素10的第1列对应的蓄积部90a中的来自第1行的像素10的信号被输出至水平信号线S及水平信号线N。即，蓄积在蓄积部90a的导体CS1中的光电转换信号被输出至水平信号线S，蓄积在蓄积部90a的导体CN1中的噪声信号被输出至水平信号线N。输出放大器部110将基于噪声信号与光电转换信号的差分的信号输出。

[0054] 另外，在时刻t10，信号Vsel2变成高电平，从而第2行的各像素10的晶体管M4接通。在时刻t11，信号Vrst2变成高电平，从而晶体管M2接通，浮置扩散部15被重置。另外，第2行的各像素10的噪声信号被输出至垂直信号线30a～垂直信号线30d。在时刻t12，信号Vrst2

变成低电平,从而晶体管M2断开。在时刻t13,信号Vtn2变成高电平,从而开关TN2接通。由此,噪声信号被传输至蓄积部90a~蓄积部90d的导体CN2。附加于导体CN2的电容蓄积来自第2行的各像素10的噪声信号。

[0055] 在时刻t14,信号Vph11变成低电平,且信号Vph21变成高电平。由于信号Vph11变成低电平,从而第2开关部80a的开关PH1N及开关PH1S断开。由于信号Vph21变成高电平,从而第2开关部80b的开关PH1N及开关PH1S接通。由此,蓄积在与各像素10的第2列对应的蓄积部90b中的来自第1行像素10的光电转换信号被输出至水平信号线S,且噪声信号被输出至水平信号线N。输出放大器部110将基于噪声信号与光电转换信号的差分的信号输出。

[0056] 在时刻t15,信号Vtn2变成低电平,从而开关TN2断开。当开关TN2断开时,附加于导体CN2的电容保持噪声信号。

[0057] 在时刻t16,信号Vph21变成低电平,且信号Vph31变成高电平。由于信号Vph21变成低电平,从而第2开关部80b的开关PH1N及开关PH1S断开。由于信号Vph31变成高电平,从而第2开关部80c的开关PH1N及开关PH1S接通。由此,蓄积在与各像素10的第3列对应的蓄积部90c中的来自第1行像素10的光电转换信号被输出至水平信号线S,且噪声信号被输出至水平信号线N。输出放大器部110将基于噪声信号与光电转换信号的差分的信号输出。

[0058] 在时刻t17,信号Vtx2变成高电平,从而在第2行的各像素10中晶体管M1接通。由此,由光电转换部12进行光电转换而得到的电荷被传输至浮置扩散部15。另外,第2行的各像素10的光电转换信号被输出至垂直信号线30a~垂直信号线30d。在时刻t18,信号Vtx2变成低电平,从而晶体管M1断开。在时刻t19,信号Vts2变成高电平,从而第1开关部70a~第1开关部70d各自的开关TS2接通。由此,光电转换信号被传输至蓄积部90a~蓄积部90d的导体CS2。附加于导体CS2的电容蓄积来自第2行的各像素10的光电转换信号。

[0059] 在时刻t20,信号Vph31变成低电平,且信号Vph41变成高电平。由于信号Vph31变成低电平,从而第2开关部80c的开关PH1N及开关PH1S断开。由于信号Vph41变成高电平,从而第2开关部80d的开关PH1N及开关PH1S接通。由此,蓄积在与各像素10的第4列对应的蓄积部90d中的来自第1行像素10的光电转换信号被输出至水平信号线S,且噪声信号被输出至水平信号线N。输出放大器部110将基于噪声信号与光电转换信号的差分的信号输出。

[0060] 在时刻t21,信号Vts2变成低电平,从而开关TS2断开。当开关TS2断开时,附加于导体CS2的电容保持光电转换信号。

[0061] 如以上说明的那样,在从时刻t10到时刻t22期间,在从第2行的各像素10向蓄积部90读出信号的期间,进行将蓄积在蓄积部90中的来自第1行的各像素10的信号向水平信号线S及水平信号线N输出的水平传输。

[0062] 在时刻t22,信号Vph41变成低电平,且信号Vph12及信号Vse13变成高电平。由于信号Vph41变成低电平,从而第2开关部80d的开关PH1N及开关PH1S断开。由于信号Vph12变成高电平,从而第2开关部80a的开关PH2N及开关PH2S接通。由此,蓄积在与各像素10的第1列对应的蓄积部90a中的来自第2行的各像素10的信号被输出至水平信号线S及水平信号线N。即,蓄积在蓄积部90a的导体CS2中的光电转换信号被输出至水平信号线S,蓄积在蓄积部90a的导体CN2中的噪声信号被输出至水平信号线N。输出放大器部110将基于噪声信号与光电转换信号的差分的信号输出。

[0063] 另外,在时刻t22,信号Vse13变成高电平,从而第3行的各像素10的晶体管M4接通。

在时刻t23,信号Vrst3变成高电平,从而晶体管M2接通,浮置扩散部15被重置。另外,第3行的各像素10的噪声信号被输出至垂直信号线30a~垂直信号线30d。在时刻t24,信号Vrst3变成低电平,从而晶体管M2断开。在时刻t25,信号Vtn1变成高电平,从而开关TN1接通。由此,噪声信号被传输至蓄积部90a~蓄积部90d的导体CN1。附加于导体CN1的电容蓄积来自第3行的各像素10的噪声信号。

[0064] 在时刻t26,信号Vph12变成低电平,且信号Vph22变成高电平。由于信号Vph12变成低电平,从而第2开关部80a的开关PH2N及开关PH2S断开。由于信号Vph22变成高电平,从而第2开关部80b的开关PH2N及开关PH2S接通。由此,蓄积在与各像素10的第2列对应的蓄积部90b中的来自第2行的各像素10的光电转换信号被输出至水平信号线S,噪声信号被输出至水平信号线N。输出放大器部110将基于噪声信号与光电转换信号的差分的信号输出。

[0065] 在时刻t27,信号Vtn1变成低电平,从而开关TN1断开。当开关TN1断开时,附加于导体CN1的电容保持噪声信号。

[0066] 在时刻t28,信号Vph22变成低电平,且信号Vph32变成高电平。由于信号Vph22变成低电平,从而第2开关部80b的开关PH2N及开关PH2S断开。由于信号Vph32变成高电平,从而第2开关部80c的开关PH2N及开关PH2S接通。由此,蓄积在与各像素10的第3列对应的蓄积部90c中的来自第2行的各像素10的光电转换信号被输出至水平信号线S,噪声信号被输出至水平信号线N。输出放大器部110将基于噪声信号与光电转换信号的差分的信号输出。

[0067] 在时刻t29,信号Vtx3变成高电平,从而在第3行的各像素10中晶体管M1接通。由此,由光电转换部12进行光电转换而得到的电荷被传输至浮置扩散部15。另外,第3行的各像素10的光电转换信号被输出至垂直信号线30a~垂直信号线30d。在时刻t30,信号Vtx3变成低电平,从而晶体管M1断开。在时刻t31,信号Vts1变成高电平,从而第1开关部70a~第1开关部70d各自的开关TS1接通。由此,光电转换信号被传输至蓄积部90a~蓄积部90d的导体CS1。附加于导体CS1的电容蓄积来自第3行的各像素10的光电转换信号。

[0068] 在时刻t32,信号Vph32变成低电平,且信号Vph42变成高电平。由于信号Vph32变成低电平,从而第2开关部80c的开关PH2N及开关PH2S断开。由于信号Vph42变成高电平,从而第2开关部80d的开关PH2N及开关PH2S接通。由此,蓄积在与各像素10的第4列对应的蓄积部90d中的来自第2行像素10的光电转换信号被输出至水平信号线S,噪声信号被输出至水平信号线N。输出放大器部110将基于噪声信号与光电转换信号的差分的信号输出。

[0069] 在时刻t33,信号Vts1变成低电平,从而开关TS1断开。当开关TS1断开时,附加于导体CS1的电容保持光电转换信号。

[0070] 在时刻t34~时刻t46,与从时刻t10到时刻22的期间和从时刻t22到时刻34的期间的情况同样地,使通过信号Vsel4、Vrst4、Vtn2、Vtx4、Vts2而被控制的晶体管依次接通断开。由此,使附加于导体CN2的电容蓄积来自第4行的各像素10的噪声信号,并使附加于导体CS2的电容蓄积来自第4行的各像素10的光电转换信号。另外,在时刻t34~时刻t46,使通过信号Vph11、Vph21、Vph31、Vph41而被控制的晶体管依次接通断开。由此,使分别蓄积在蓄积部90a~蓄积部90d中的来自第3行的各像素10的噪声信号及光电转换信号依次输出。输出放大器部110将基于从蓄积部90a~蓄积部90d输出的噪声信号与光电转换信号的差分的信号依次输出。

[0071] 在时刻t46~时刻t50,使通过信号Vph12、Vph22、Vph32、Vph42而被控制的晶体管

依次接通断开。由此,使分别蓄积在蓄积部90a~蓄积部90d中的来自第4行的各像素10的噪声信号及光电转换信号依次输出。输出放大器部110将基于从蓄积部90a~蓄积部90d输出的噪声信号与光电转换信号的差分的信号依次输出。

[0072] 如以上说明的那样,在本实施方式中,在从某行像素10向蓄积部90读出信号的期间,进行将蓄积在蓄积部90中的来自其它行像素10的信号向水平信号线S及水平信号线N输出的水平传输。通过在从像素10读出的读出期间内并行地进行水平传输动作,能够缩短从全部像素10读出的读出时间。通过缩短读出时间,能够实现高帧率的读出。

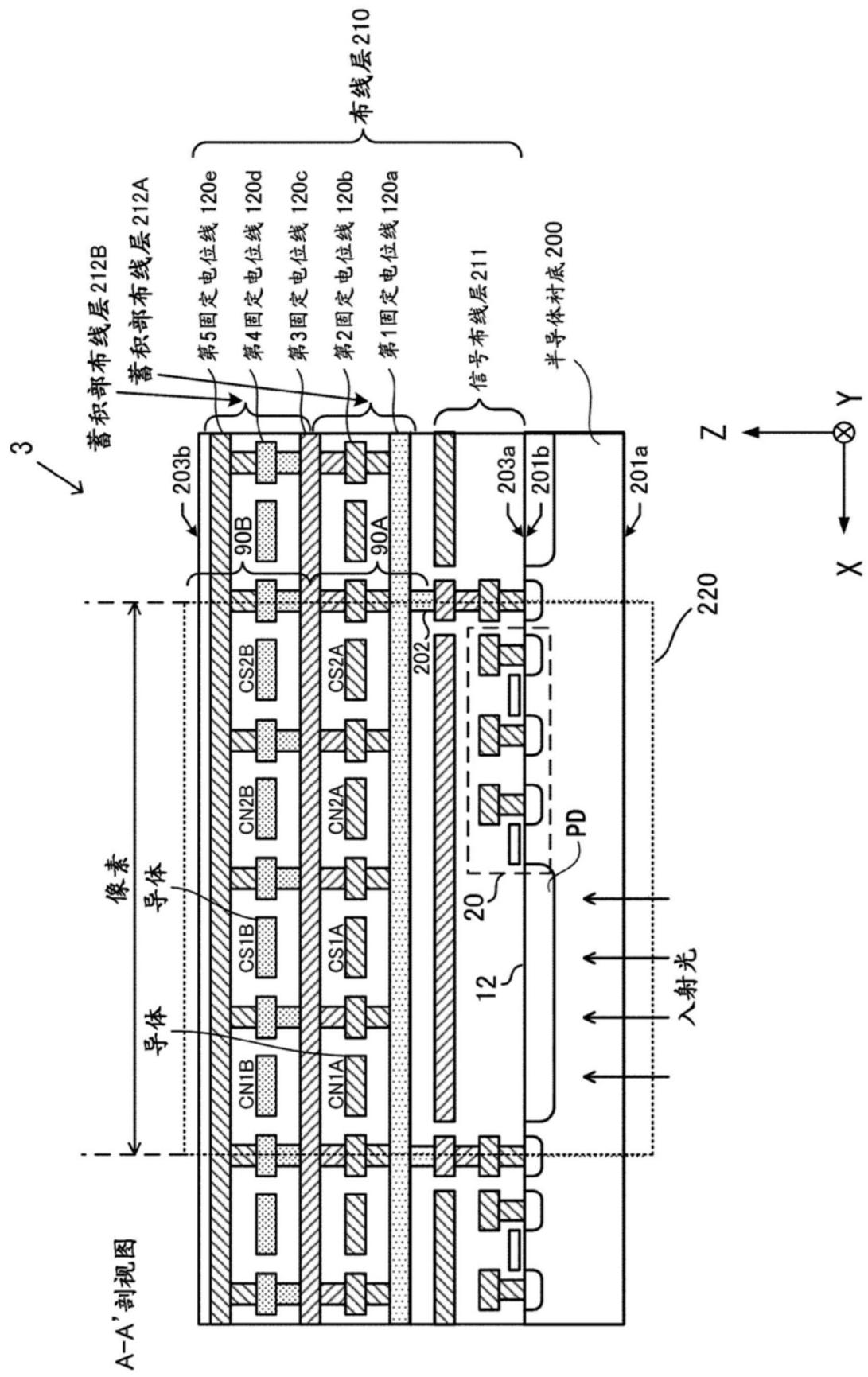

[0073] 图5是表示第1实施方式的摄像元件3的剖面结构的一例的图。图5是后述图6中的A-A'的剖视图。摄像元件3例如是背面照射型摄像元件。如图5所示,入射光主要向着Z轴正方向入射。另外,如坐标轴所示,将与Z轴正交的纸面左方向作为X轴正方向,将与Z轴及X轴正交的纸面里方向作为Y轴正方向。在之后的几幅图中,将图5的坐标轴作为基准来表示坐标轴,以获知各个图的方向。

[0074] 摄像元件3包括由硅等半导体材料构成的半导体衬底200和层叠于半导体衬底200的布线层210而构成。摄像元件3还具有未图示的微透镜层、彩色滤光片层、及钝化层。摄像元件3例如向着Z轴正方向按照微透镜层、彩色滤光片层、钝化层、半导体衬底200、及布线层210的顺序配置。

[0075] 半导体衬底200具有作为供光入射的入射面的第1面201a、及与第1面201a不同的第2面201b。第2面201b位于与第1面201a相反的位置。在本实施方式中,摄像元件3的背面表示位于布线层210的相反侧的第1面201a,背面照射型构成为使光从作为背面的第1面201a入射。布线层210具有半导体衬底200的第2面201b侧的面(第3面203a)、和第3面203a的相反侧的面(第4面203b)。

[0076] 半导体衬底200在第1面201a与第2面201b之间具有光电转换部12及读出部20。具有光电转换部12及读出部20的像素10在X轴方向及Y轴方向上配置有多个。光电转换部12将从半导体衬底200的一侧、即半导体衬底200的第1面201a侧入射的入射光转换成电荷。蓄积部90与光电转换部12层叠地设置在半导体衬底200的一侧的相反侧、即半导体衬底200的第2面201b侧。另外,蓄积部90也可以说是设置在光电转换部12与布线层210的第4面203b之间。

[0077] 在半导体衬底200的第2面201b形成有包括导体膜(金属膜)及绝缘膜的多层布线层210。在布线层210中配置有多个布线和过孔等。对导体膜使用铜、铝等。绝缘膜包括导体膜之间的绝缘膜和栅极绝缘膜等,由氧化膜或氮化膜等构成。

[0078] 布线层210具有:信号布线层211,其设有向各像素10输入的控制信号Vtxn、Vrstn、Vseln等的信号线和垂直信号线30;和蓄积部布线层212,其构成蓄积部90(蓄积部90a~蓄积部90d)。信号布线层211层叠于半导体衬底200的第2面201b,蓄积部布线层212层叠于信号布线层211a。

[0079] 在图3及图5中,蓄积部布线层212在第1列像素列所在的像素区域隔着信号布线层211层叠有与第1列像素列对应的蓄积部90a,并在第2列像素列所在的像素区域隔着信号布线层211层叠有与第2列像素列对应的蓄积部90b,以下同样地,隔着信号布线层211层叠有与第3列像素列、第4列像素列分别对应的蓄积部90c、90d。这样,蓄积部布线层212的蓄积部90a~蓄积部90d分别设置于对应的每个像素列的各像素区域220。蓄积部布线层212的蓄积

部90a～蓄积部90d各自的大小成为与一列像素10对应的大小。蓄积部布线层212的蓄积部90a～蓄积部90d彼此具有相同的结构,图5所示的蓄积部90与蓄积部90a～蓄积部90d中的任一个对应。

[0080] 蓄积部90如上所述具有导体CN1、导体CS1、导体CN2、导体CS2、和固定电位线120。固定电位线120例如如图5所示具有第1固定电位线120a、第2固定电位线120b、及第3固定电位线120c,分别由不同层的导体膜构成。第1固定电位线120a及第3固定电位线120c在布线层210的层叠方向即Z轴方向上彼此分离地配置。第1固定电位线120a及第3固定电位线120c对于全部蓄积部90a、90b、90c、90d是共通的,因此,以覆盖摄像元件3的全部像素10的方式形成。第1固定电位线120a和第3固定电位线120c既可以如上所述对于全部蓄积部共通地构成,也可以针对各蓄积部的每一个分别构成。

[0081] 导体CN1、导体CS1、导体CN2、及导体CS2在构成各像素列的多个像素10的排列方向上延伸。导体CN1、CS1、CN2、CS2在第1固定电位线120a与第3固定电位线120c之间从第1固定电位线120a及第3固定电位线120c分离而配置。第2固定电位线120b配置在导体CN1、CS1、CN2、CS2各自之间,并经由过孔与第1固定电位线120a及第3固定电位线120c连接。导体CN1、CS1、CN2、CS2与第1～第3固定电位线120a～120c之间设有绝缘膜。绝缘膜是氧化膜或氮化膜等。具体为氧化硅膜、氮化硅膜、氮氧化硅膜或这些膜的多层膜等。

[0082] 在蓄积部90,在各个导体CN1、CS1、CN2、CS2与第1～第3固定电位线120a～120c之间形成电容。通过使各个导体CN1、CS1、CN2、CS2与第1～第3固定电位线120a～120c之间的距离缩短,能够增大电容。为了增大电容,也可以使用与氧化硅膜等相比介电常数较高的高介电材料。另外,也可以使用MIM电容。此外,在与不同于固定电位线的布线等之间形成的电容也被附加于导体CN1、CS1、CN2、CS2。

[0083] 第1固定电位线120a、第2固定电位线120b、及第3固定电位线120c被提供电源电位或接地电位等规定电位。第1固定电位线120a作为信号布线层211的垂直信号线30和控制信号线等与导体CN1、CS1、CN2、CS2之间的屏蔽部(shield)来发挥功能。通过设置第1固定电位线120a,能够抑制在垂直信号线30和控制信号线等与导体CN1、CS1、CN2、CS2之间形成大的寄生电容。另外,能够抑制垂直信号线30和控制信号线等与导体CN1、CS1、CN2、CS2之间的串扰(crosstalk)。另外,第1固定电位线120a、第2固定电位线120b、及第3固定电位线120c以包围导体CN1、CS1、CN2、CS2各自的四周的方式设置,从而作为各个导体CN1、CS1、CN2、CS2之间的屏蔽部来发挥功能。能够避免在各个导体CN1、CS1、CN2、CS2之间产生大的寄生电容,能够抑制各个导体CN1、CS1、CN2、CS2之间的串扰。

[0084] 在图5的示例中,第1固定电位线120a被设定为接地电位,并经由过孔202等与半导体衬底200连接。即,第1固定电位线120a作为用于向各像素10供给接地电位的接地线(地线)而与各像素10共通地连接。此外,也可以对第1固定电位线120a提供电源电位而将其作为对各像素10共通的电源线来使用。这样,固定电位线被共用为用于形成基于导体CN1、CS1、CN2、CS2的电容的导体、抑制噪声混入的屏蔽部、和各像素10的电源线或接地线。通过将固定电位线用作各像素10的电源线或接地线,无需再另行设置用于电源线或接地线的布线。因此,能够减少布线层210的层数。

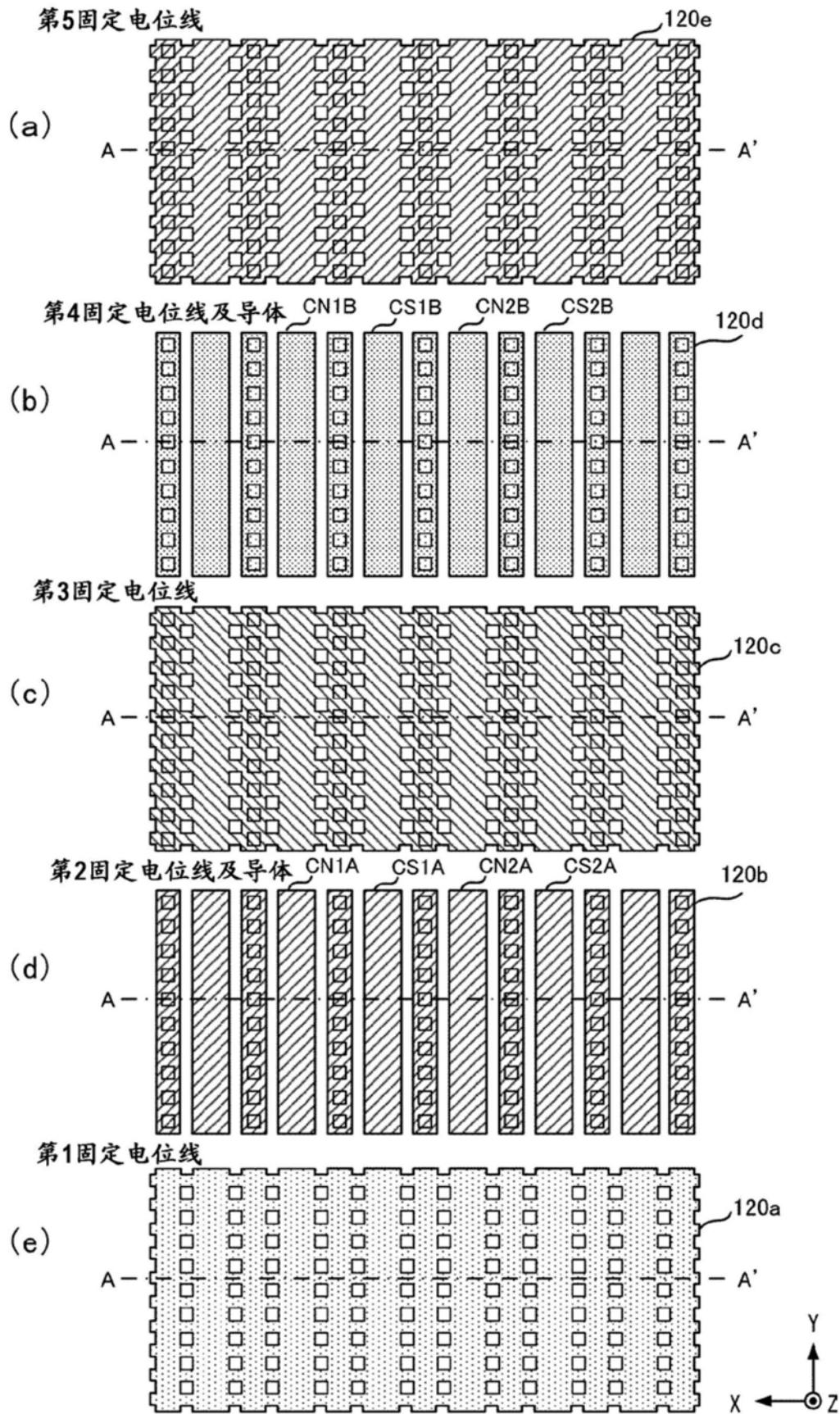

[0085] 图6是表示第1实施方式的摄像元件3的蓄积部布线层212的一部分的平面布局例的图。图6的(a)是表示形成有第3固定电位线120c的层的平面布局的一例的图,图6的(b)是

表示形成有第2固定电位线120b及导体CN1、CS1、CN2、CS2的层的平面布局的一例的图,图6的(c)是表示形成有第1固定电位线120a的层的平面布局的一例的图。

[0086] 第3固定电位线120c及第1固定电位线120a如上所述形成为图6所示的面状。第3固定电位线120c及第1固定电位线120a以覆盖例如呈矩阵状二维配置的全部像素10的方式形成。第2固定电位线120b、导体CN1、导体CS1、导体CN2、导体CS2分别形成为线状。第2固定电位线120b与导体CN1、CS1、CN2、CS2相对地配置。第2固定电位线120b的Y轴方向上的长度成为与导体CN1、CS1、CN2、CS2的Y轴方向上的长度相应的长度。在本实施方式中,由于蓄积部90a～蓄积部90d分别与各像素10的像素列对应地设置,所以第2固定电位线120b及导体CN1、CS1、CN2、CS2的Y轴方向上的长度成为与一个像素列对应的长度。第3固定电位线120c与第2固定电位线120b经由多个过孔连接,第2固定电位线120b与第1固定电位线120a经由多个过孔连接。

[0087] 根据上述实施方式,能够获得如下作用效果。

[0088] (1) 摄像元件3具备:多个像素10,其具有将从衬底200的一侧入射的入射光转换成电荷的光电转换部12、和输出基于电荷的信号的输出部(放大部16及选择部17),并沿第1方向和与第1方向交叉的第2方向配置;和蓄积部90,其与光电转换部12层叠地设置在衬底200的一侧的相反侧,并蓄积信号。在本实施方式中,蓄积部90在像素区域220中层叠设于半导体衬底200的第2面201b。在现有技术中,由于在像素区域220周边的配置模拟/数字转换电路等的区域设置很多电容,所以摄像元件的芯片面积增大。相对于此,在本实施方式中,蓄积部90层叠设置在半导体衬底200的第2面201b。因此,能够抑制芯片面积的增大。另外,通过将蓄积部90设置在像素区域220,能够避免像素区域220周边的配置模拟/数字转换电路等的区域的面积增大。另外,通过与一个像素列等对应地设置电容,能够形成大的电容。

[0089] (2) 摄像元件3具备:光电转换部12,其将入射至半导体衬底200的第1面201a的光转换成电荷;读出部20,其向半导体衬底200的第2面201b输出基于电荷的信号;和蓄积部90,其层叠设于第2面201b的像素区域220,并蓄积由读出部20输出的信号。由此,能够抑制芯片面积的增大。

[0090] (3) 蓄积部90与沿第1方向配置的多个像素10共通地连接。由此,能够与一个像素列等对应地设置电容。

[0091] (4) 摄像元件3还具备信号线(垂直信号线30),该信号线与沿第1方向配置的多个像素10共通地连接,通过读出部20向该信号线输出信号。蓄积部90经由信号线与多个像素10共通地连接。由此,能够使蓄积部90蓄积经由垂直信号线30读出的来自各像素10的信号。

[0092] (5) 读出部20输出基于电荷的信号及噪声信号。蓄积部90具有蓄积基于电荷的信号的信号用蓄积部、和蓄积噪声信号的噪声用蓄积部。由此,能够使蓄积部90分别蓄积从读出部20输出的光电转换信号及噪声信号。

[0093] (6) 具有:第1布线(第2固定电位线120b),其设置在信号用蓄积部与噪声用蓄积部之间,并被施加恒定电位(例如电源电位或接地电位);第2布线(第1固定电位线120a),其设置在读出部20与蓄积部90之间,并被施加恒定电位;和第3布线(第3固定电位线120c),其隔着蓄积部90和绝缘膜设置在光入射的一侧的相反侧,并被施加恒定电位。在本实施方式中,第1固定电位线120a、第2固定电位线120b、及第3固定电位线120c以包围导体CN1、CS1、CN2、CS2各自的四周的方式设置。因此,能够抑制噪声的混入。

[0094] (7) 蓄积部90具有与沿第1方向配置的多个像素10连接的第1蓄积部(例如蓄积部90a)、和与不同于多个像素10的沿第1方向配置的多个像素连接的第2蓄积部(例如蓄积部90b),第1蓄积部和第2蓄积部在第2方向上并排设有多个。由此,例如能够按每个像素列设置蓄积部,能够获得很大的电容。

[0095] (8) 读出部90具有:保持由光电转换部12进行转换而得到的电荷的保持部15、将电荷向保持部15传输的传输部13、将由保持部15保持的电荷排出的排出部14、和将基于由传输部13传输的电荷的信号放大的放大部16。由此,能够从各像素10读出基于由光电转换部12进行光电转换而得到的电荷的光电转换信号。

[0096] (9) 噪声信号是将保持于保持部15的电荷排出时的信号。由此,能够获得成为相对于光电转换信号而言的基准电平的噪声信号。

[0097] (10) 摄像元件3具备:第1层(半导体衬底200),其具有将入射至半导体衬底200的第1面201a的光转换成电荷的光电转换部12、和向半导体衬底200的第2面201b输出基于电荷的信号的读出部20;和第2层(蓄积部布线层212),其在第2面201b层叠于第1层,并具有蓄积由读出部20输出的信号的蓄积部90。由此,无需使芯片面积增大就能获得大的电容值。

[0098] (11) 蓄积部90具有基于导体的电容。由此,与设置扩散电容的情况相比较,能够抑制芯片面积的增大。

[0099] (12) 摄像元件3具有:多个像素10,其具有将所入射的光转换成电荷的光电转换部12、被传输由光电转换部12进行光电转换而得到的电荷的第1蓄积部(浮置扩散部15)、和将基于被传输至第1蓄积部的电荷的信号输出的输出部(放大部16及选择部17);输出控制部(垂直扫描电路40),其使基于从光电转换部12传输至第1蓄积部的电荷的像素信号(光电转换信号)、与将第1蓄积部的电荷重置得到的重置信号(噪声信号)进行切换并从输出部输出;第2蓄积部(信号用蓄积部),其蓄积从输出部输出的像素信号;和第3蓄积部(噪声用蓄积部),其蓄积从输出部输出的重置信号。像素10配置在供光入射的面、与第2蓄积部或第3蓄积部之间。由此,能够抑制芯片面积的增大。另外,无需使芯片面积增大就能获得大的电容值。

[0100] (第2实施方式)

[0101] 第2实施方式的摄像装置具有与第1实施方式的摄像装置1相同的结构。在第2实施方式的摄像元件中,主要在针对每个像素列设置多条垂直信号线来进行多行像素10的同时读出这点上与第1实施方式不同。此外,图中对与第1实施方式相同或相当的部分标注相同的参照编号,并主要说明不同点。

[0102] 图7是表示第2实施方式的摄像元件3的局部结构的电路图。在第2实施方式中,与像素10的各列对应地设有两条垂直信号线(垂直信号线30A及垂直信号线30B)。各列像素10按每一行而与不同的垂直信号线连接。另外,在第2实施方式中,摄像元件3包括选择电路50(选择电路50A及选择电路50B)、电流源60(电流源60A1~电流源60A3、电流源60B1~电流源60B3)、第1开关部70(第1开关部70A1~第1开关部70A3、第1开关部70B1~第1开关部70B3)、第2开关部80(第2开关部80A1~第2开关部80A3、第2开关部80B1~第2开关部80B3)、蓄积部90(蓄积部90A1~蓄积部90A3、蓄积部90B1~蓄积部90B3)、水平扫描电路100(水平扫描电路100A及水平扫描电路100B)、和输出放大器部110(输出放大器部110A及输出放大器部110B)而构成。在图7的示例中,为了简化说明,对于像素10仅图示了水平方向3像素×垂直

方向4像素。

[0103] 图8是表示第2实施方式的摄像元件3的动作例的时序图。在图8中,时刻t1~时刻t10、时刻t10~时刻t22、时刻t22~时刻t26分别成为一个水平期间。

[0104] 在时刻t1,信号Vsel1及信号Vsel2变成高电平,从而在第1行及第2行的各像素10中选择部17的晶体管M4接通。在时刻t2,信号Vrst1及信号Vrst2变成高电平,从而在第1行及第2行的各像素10中排出部14的晶体管M2接通,浮置扩散部15的电位变成重置电位。另外,第1行的各像素10的噪声信号被分别输出至垂直信号线30B1~垂直信号线30B3,第2行的各像素10的噪声信号被分别输出至垂直信号线30A1~垂直信号线30A3。

[0105] 在时刻t3,信号Vrst1及信号Vrst2变成低电平,从而晶体管M2断开。在时刻t4,信号Vtn1变成高电平,从而第1开关部70A1~第1开关部70A3及第1开关部70B1~第1开关部70B3各自的开关TN1接通。由此,来自第1行的各像素10的噪声信号被传输至蓄积部90B1~蓄积部90B3的导体CN1B,来自第2行的各像素10的噪声信号被传输至蓄积部90A1~蓄积部90A3的导体CN1A。在时刻t5,信号Vtn1变成低电平,从而开关TN1断开。当开关TN1断开时,附加于蓄积部90B1~蓄积部90B3的导体CN1B的电容分别保持来自第1行的各像素10的噪声信号。另外,附加于蓄积部90A1~蓄积部90A3的导体CN1A的电容分别保持来自第2行的各像素10的噪声信号。

[0106] 在时刻t6,信号Vtx1及信号Vtx2变成高电平,从而在第1行及第2行的各像素10中传输部13的晶体管M1接通,由光电转换部12进行光电转换而得到的电荷被传输至浮置扩散部15。另外,第1行的各像素10的光电转换信号被分别输出至垂直信号线30B1~垂直信号线30B3,第2行的各像素10的光电转换信号被分别输出至垂直信号线30A1~垂直信号线30A3。在时刻t7,信号Vtx1及信号Vtx2变成低电平,从而晶体管M1断开。

[0107] 在时刻t8,信号Vts1变成高电平,从而第1开关部70A1~第1开关部70A3及第1开关部70B1~第1开关部70B3的开关TS1接通。由此,来自第1行的各像素10的光电转换信号被传输至蓄积部90B1~蓄积部90B3的导体CS1B,来自第2行的各像素10的光电转换信号被传输至蓄积部90A1~蓄积部90A3的导体CS1A。在时刻t9,信号Vts1变成低电平,从而开关TS1断开。当开关TS1断开时,附加于蓄积部90B1~蓄积部90B3的导体CS1B的电容分别保持来自第1行的各像素10的光电转换信号。另外,附加于蓄积部90A1~蓄积部90A3的导体CS1A的电容分别保持来自第2行的各像素10的光电转换信号。

[0108] 如以上说明的那样,在从时刻t1到时刻t10期间,第1行的各像素10的信号被读出至蓄积部90B1~蓄积部90B3,并且第2行的各像素10的信号被读出至蓄积部90A1~蓄积部90A3。

[0109] 在时刻t10~时刻t22,与从时刻t1到时刻t10的情况同样地,使通过信号Vsel3、Vsel4、Vrst3、Vrst4、Vtn2、Vtx3、Vtx4、Vts2而被控制的晶体管依次接通断开。由此,使附加于蓄积部90B1~蓄积部90B3的导体CN2B及导体CS2B的电容分别蓄积来自第3行的各像素10的噪声信号及光电转换信号。另外,使附加于蓄积部90A1~蓄积部90A3的导体CN2A及导体CS2A的电容分别蓄积来自第4行的各像素10的噪声信号及光电转换信号。这样,在本实施方式中,导体CN1A、CN2A、CN1B、及CN2B作为蓄积噪声信号的噪声用蓄积部发挥功能。另外,导体CS1A、CS2A、CS1B、及CS2B作为蓄积光电转换信号的信号用蓄积部发挥功能。

[0110] 另外,在时刻t10,信号Vph11变成高电平,从而第2开关部80A1及第2开关部80B1的

开关PH1N及开关PH1S接通。由此，蓄积在蓄积部90B1中的来自第1行像素10的信号被输出至水平信号线BS及水平信号线BN。另外，蓄积在蓄积部90A1中的来自第2行像素10的信号被输出至水平信号线AS及水平信号线AN。输出放大器部110A及输出放大器部110B分别将基于噪声信号与光电转换信号的差分的信号输出。

[0111] 在时刻t14,信号Vph21变成高电平,从而第2开关部80A2及第2开关部80B2的开关PH1N及开关PH1S接通。由此,蓄积在蓄积部90B2中的来自第1行像素10的信号被水平传输,蓄积在蓄积部90A2中的来自第2行像素10的信号被水平传输。在时刻t16,信号Vph31变成高电平,从而第2开关部80A3及第2开关部80B3的开关PH1N及开关PH1S接通。由此,蓄积在蓄积部90B3中的来自第1行像素10的信号被水平传输,蓄积在蓄积部90A3中的来自第2行像素10的信号被水平传输。

[0112] 在时刻t22~时刻t25,使通过信号Vph12、Vph22、Vph32而被控制的晶体管依次接通断开。由此,使分别蓄积在蓄积部90B1~蓄积部90B3中的来自第3行的各像素10的噪声信号及光电转换信号依次输出。另外,使分别蓄积在蓄积部90A1~蓄积部90A3中的来自第4行的各像素10的噪声信号及光电转换信号依次输出。输出放大器部110A及输出放大器部110B将基于噪声信号与光电转换信号的差分的信号依次输出。

[0113] 图9是表示第2实施方式的摄像元件3的剖面结构的一例的图。图9是后述图10中的A-A'的剖视图。在布线层210中,设有具有蓄积部90A(蓄积部90A1~蓄积部90A3)的蓄积部布线层212A、及具有蓄积部90B(蓄积部90B1~蓄积部90B3)的蓄积部布线层212B。蓄积部布线层212B在半导体衬底200的第2面201b的像素区域220中与蓄积部布线层212A层叠地设置。另外,蓄积部90A及蓄积部90B各自的大小成为与一列像素10对应的大小。

[0114] 如图9所示,固定电位线120具有第1固定电位线120a、第2固定电位线120b、第3固定电位线120c、第4固定电位线120d、及第5固定电位线120e,分别由不同层的导体膜构成。在蓄积部布线层212A中,主要在各个导体CN1A、CS1A、CN2A、CS2A与第1~第3固定电位线120a~120c之间形成电容。另外,在蓄积部布线层212B中,主要在各个导体CN1B、CS1B、CN2B、CS2B与第3~第5固定电位线120c~120e之间形成电容。第3固定电位线120c作为蓄积部90A的导体CN1A、CS1A、CN2A、CS2A与蓄积部90B的导体CN1B、CS1B、CN2B、CS2B之间的屏蔽部发挥功能。

[0115] 图10是表示第2实施方式的摄像元件3的蓄积部布线层212的一部分的平面布局例的图。图10的(a)是表示形成有第5固定电位线120e的层的平面布局的一例的图,图10的(b)是表示形成有第4固定电位线120d及导体CN1B、CS1B、CN2B、CS2B的层的平面布局的一例的图,图10的(c)是表示形成有第3固定电位线120c的层的平面布局的一例的图。另外,图10的(d)是表示形成有第2固定电位线120b及导体CN1A、CS1A、CN2A、CS2A的层的平面布局的一例的图,图10的(e)是表示形成有第1固定电位线120a的层的平面布局的一例的图。

[0116] 第5固定电位线120e与第3固定电位线120c及第1固定电位线120a同样地,以覆盖例如呈矩阵状二维配置的全部像素10的方式形成。第4固定电位线120d与第2固定电位线120b同样地形成为线状。在本实施方式中,蓄积部90A及蓄积部90B分别与各像素10的像素列对应设置,因此第4固定电位线120d、导体CN1B、CS1B、CN2B、CS2B的Y轴方向上的长度成为与一个像素列对应的长度。第5固定电位线120e与第4固定电位线120d经由多个过孔连接,第4固定电位线120d与第3固定电位线120c经由多个过孔连接。

[0117] 根据上述实施方式,除了与第1实施方式相同的作用效果之外,还能获得如下作用效果。

[0118] (13) 蓄积部90具有与沿第1方向配置的多个像素10中的第1多个像素10连接的第一蓄积部90A、和与沿第1方向配置的多个像素10中的第2多个像素10连接的第2蓄积部90B。在本实施方式中,摄像元件3还具备层叠于第2层(蓄积部布线层212A)的第3层(蓄积部布线层212B)。由此,能够抑制芯片面积的扩大,并且能够设置多个蓄积部90。另外,通过针对每个像素列设置多个蓄积部90,能够实现多行像素10的同时读出。

[0119] (第3实施方式)

[0120] 第3实施方式的摄像装置具有与第1实施方式的摄像装置1相同的结构。在第3实施方式的摄像元件中,主要在不将蓄积部90A与蓄积部90B层叠来配置蓄积部90A和蓄积部90B这点上与第2实施方式不同。此外,图中对与第1及第2实施方式相同或相当的部分标注相同的参照编号,并主要说明不同点。

[0121] 图11是表示第3实施方式的摄像元件3的局部结构的电路图。第3实施方式的摄像元件具有与第2实施方式的摄像元件3相同的电路结构。在第2实施方式中,对蓄积部90A及蓄积部90B分别以与一列像素10对应的大小设置的例子进行了说明。相对于此,在第3实施方式中,蓄积部90A及蓄积部90B分别以与一列像素10中的规定数量的像素10对应的大小设置。例如,蓄积部90A及蓄积部90B的大小成为与一列中的一半像素10对应的大小。此外,第3实施方式的摄像元件3的动作与第2实施方式的摄像元件3相同。

[0122] 图12是表示第3实施方式的摄像元件3的剖面结构的一例的图。图12的(a)是后述图13中的A-A'的剖视图,图12的(b)是后述图13中的B-B'的剖视图。在布线层210的蓄积部布线层212中设有蓄积部90A(蓄积部90A1～蓄积部90A4)及蓄积部90B(蓄积部90B1～蓄积部90B4)。在图12的(a)所示的剖视图中示出了蓄积部90B。另外,如图12的(b)所示,蓄积部90A及蓄积部90B利用相同层的导体膜和绝缘膜来形成。

[0123] 图13是表示第3实施方式的摄像元件3的蓄积部布线层210的一部分的平面布局例的图。图13的(a)是表示形成有第3固定电位线120c的层的平面布局的一例的图,图13的(b)是表示形成有第2固定电位线120b及导体CN1A、CS1A、CN2A、CS2A、CN1B、CS1B、CN2B、CS2B的层的平面布局的一例的图,图13的(c)是表示形成有第1固定电位线120a的层的平面布局的一例的图。

[0124] 第2固定电位线120b配置在蓄积部90A的各个导体CN1A、CS1A、CN2A、CS2A之间。另外,第2固定电位线120b配置在蓄积部90B的各个导体CN1B、CS1B、CN2B、CS2B之间。在本实施方式中,由于蓄积部90A及蓄积部90B各自的大小成为与一个像素列中的规定数量的像素10对应的大小,所以导体CN1A、CS1A、CN2A、CS2A及导体CN1B、CS1B、CN2B、CS2B的Y轴方向上的长度成为与一个像素列中的规定数量的像素10对应的长度。另外,第2固定电位线120b作为蓄积部90A的导体CN1A、CS1A、CN2A、CS2A与蓄积部90B的导体CN1B、CS1B、CN2B、CS2B之间的屏蔽部发挥功能。

[0125] 根据上述实施方式,除了与第1实施方式相同的作用效果之外,还能获得如下作用效果。

[0126] (14) 蓄积部90具有与沿第1方向配置的多个像素10中的第1多个像素10连接的第一蓄积部90A、和与沿第1方向配置的多个像素10中的第2多个像素连接的第2蓄积部90B。在本

实施方式中，多个蓄积部90分别与多个像素列的每一个对应，并存储从对应的像素列的像素10读出的信号。多个蓄积部90设置在包含对应的像素列中的规定数量的像素的像素区域200。由此，无需将多个蓄积部90层叠就能进行配置。因此，能够减少布线层210的层数。

[0127] 如下所述的变形也在本发明的范围内，也能将一个或多个变形例与上述实施方式组合。

[0128] (变形例1)

[0129] 图14是表示变形例1的摄像元件3的局部结构的电路图。在变形例1的摄像元件3中，具备与各垂直信号线30连接的放大器(缓冲器)130。放大器130(放大器130a～放大器130d)输出将从像素10读出的信号放大后的信号。因此，能够抑制各像素10与各蓄积部90之间的信号延迟或信号电平的下降。其结果是，例如即使在蓄积部90的电容大的情况下等，也能进行高帧率的读出。

[0130] 另外，在变形例1的摄像元件3中，针对每个像素列设有两个模拟/数字转换电路(AD转换电路140A及AD转换电路140B)。AD转换电路140A及AD转换电路140B分别将基于来自对应像素列的光电转换信号及噪声信号的差分的数字信号输出。从AD转换电路140A输出的数字信号及从AD转换电路140B输出的数字信号被平均化。从AD转换电路140A1输出的数字信号与从AD转换电路140B1输出的数字信号被平均化，且从AD转换电路140A2输出的数字信号与从AD转换电路140B2输出的数字信号被平均化。同样地，从AD转换电路140A3输出的数字信号与从AD转换电路140B3输出的数字信号被平均化，且从AD转换电路140A4输出的数字信号与从AD转换电路140B4输出的数字信号被平均化。平均化后的信号被输出至图14所示的输出端子。在本变形例中，将蓄积在蓄积部90中的来自各像素10的信号分别在AD转换电路140A及AD转换电路140B中转换成数字信号，并进行两个数字信号的平均化。因此，能够向输出端子输出将在从蓄积部90向第2开关部80的传输信号时等混入的噪声降低后的信号。

[0131] (变形例2)

[0132] 在上述实施方式中，对设置基于导体的电容来作为用于蓄积光电转换信号及噪声信号的电容的例子进行了说明。但是，也可以将使用导体以外的材料的电容层叠设于半导体衬底的第2面201b。

[0133] (变形例3)

[0134] 在上述实施方式中，对将信号布线层211层叠于半导体衬底200的第2面201b、并将蓄积部布线层212层叠于信号布线层211的例子进行了说明。但是，也可以将蓄积部布线层212层叠于半导体衬底200的第2面201b，并将信号布线层211层叠于蓄积部布线层212。另外，蓄积部布线层212可以隔着导体膜或绝缘膜而层叠于半导体衬底200的第2面201b，也可以直接层叠于半导体衬底200的第2面201b。

[0135] (变形例4)

[0136] 在上述实施方式中，对摄像元件3为背面照射型结构的例子进行了说明。但是，也可以将摄像元件3设为在供光入射的入射面上设置布线层210的表面照射型结构。在该情况下，摄像元件3成为光向半导体衬底200的第2面201b入射的结构。像素10在第1方向(例如列方向)及与其交叉的第2方向(例如行方向)上配置有多个。也可以将蓄积部90配置在多个像素之间，例如沿第2方向配置的多个像素之间。

[0137] (变形例5)

[0138] 在上述实施方式及变形例中,对蓄积来自像素10的光电转换信号及噪声信号的蓄积部90进行了说明。但是,蓄积部也能作为摄像元件3所包含的其它电路的蓄积部来应用。

[0139] 在上述中说明了各种各样的实施方式及变形例,但本发明并不限定于这些内容。在本发明的技术思想的范围内考虑到的其它方式也包含在本发明的范围内。

[0140] 如下优先权基础申请的公开内容被作为引用文编入于此。

[0141] 日本专利申请2016年第38161号(2016年2月29日申请)。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14