(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4861339号

(P4861339)

(45) 発行日 平成24年1月25日(2012.1.25)

(24) 登録日 平成23年11月11日(2011.11.11)

(51) Int.Cl.

G06F 13/36 (2006.01)

F 1

G06F 13/36 520B

G06F 13/36 310E

G06F 13/36 530A

請求項の数 18 (全 15 頁)

(21) 出願番号 特願2007-555297 (P2007-555297)

(86) (22) 出願日 平成18年2月9日 (2006.2.9)

(65) 公表番号 特表2008-530694 (P2008-530694A)

(43) 公表日 平成20年8月7日 (2008.8.7)

(86) 國際出願番号 PCT/US2006/004936

(87) 國際公開番号 WO2006/086732

(87) 國際公開日 平成18年8月17日 (2006.8.17)

審査請求日 平成19年9月21日 (2007.9.21)

(31) 優先権主張番号 11/055,922

(32) 優先日 平成17年2月10日 (2005.2.10)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100159651

弁理士 高倉 成男

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

最終頁に続く

(54) 【発明の名称】スイッチマトリックス経由のデータ転送を改善するフロー制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

システムオンチップ(SoC)集積回路(IC)であって、

バスコントローラと、

各スレーブデータバスを経由して前記バスコントローラと相互接続している複数のスレーブと、

各マスタデータバスを経由して前記バスコントローラと相互接続している複数のマスタであって、前記複数のマスタのうちの第1のものが、前記複数のスレーブのうちの第1のものと、前記複数のスレーブのうちの第2のものとに対する要求を発行するように構成され、前記複数のマスタのうちの第2のものが、前記複数のスレーブのうちの第1のものに要求を発行するように構成されている複数のマスタとを備え、

前記複数のスレーブのうちの第1及び第2のものは、データを求める前記要求を受信すると同時に、前記複数のマスタのうちの第1のものから発行された要求に応答してデータを提供し、

前記システムオンチップ(SoC)集積回路(IC)は、更に下記を備える：

前記バスコントローラによって前記複数のスレーブの各々に対して発行される制御信号、ただし前記制御信号は、前記複数のマスタの各々が、要求したデータをスレーブから受信する準備ができているか否かを各スレーブに対して示し、そして、前記複数のスレーブうちの第2のものが、前記複数のマスタのうちの第1のものに前記要求されたデータを送ることによって、前記複数のスレーブのうちの第1のものが、前記複数のマスタのうちの

10

20

第1のものによって要求されたデータを、前記複数のマスタのうちの第1のものに送るこ

とが前記バスコントローラによって遅らせられる替わりとして、前記複数のスレーブのう

ちの第1のものが、前記複数のマスタのうちの第2のものによって要求されたデータを、

前記複数のマスタのうちの第2のものに送ることが前記バスコントローラによって引き起

こされ、その結果、前記複数のスレーブのうちの第1のものは、前記複数のマスタのうち

の第1のものによるスレーブからのデータの受信の準備ができるのを待つてアイドル状態

になることが無い。

ただし、前記制御信号は、複数のマスターの各々がスレーブからのデータ受信の準備が

できているか否かに関する状態の変化のたびに、前記状態変化が常に反映されるように更

新される制御信号であり、

前記複数のスレーブの第2のものは、前記複数のスレーブの第1のものよりも前記複数

のマスターの第1のものに対するデータ送信に関し相対的に高い優先度を有するスレーブ

である。

#### 【請求項2】

前記制御信号は、前記複数のうちのどの1又は複数のマスタが、要求したデータを受信

する準備ができていないのかを前記複数のスレーブに対して示す請求項1に記載のシステムオンチップ(SoC)集積回路(I<sub>C</sub>)。

#### 【請求項3】

前記制御信号は更に、どの1又は複数のマスタが、要求したデータを受信する準備が

できているのかを前記複数のスレーブに対して示す請求項2に記載のシステムオンチップ(SoC)集積回路(I<sub>C</sub>)。

#### 【請求項4】

第1のマスタが、要求した第1のデータを受信する準備ができていないことを第1の制

御信号が示す場合、第1のスレーブが、前記第1のマスタによって要求された第1のデ

タを転送することを遅らせる請求項2に記載のシステムオンチップ(SoC)集積回路(I<sub>C</sub>)。

#### 【請求項5】

前記第1の制御信号は更に、前記複数のマスタのうちの第2の1つが、要求した第2の

データを前記第1のスレーブから受信する準備ができていることを示し、前記第1のスレ

ーブは、前記第1の制御信号に応じ、前記要求された第2のデータを前記第2のマスタへ

転送する請求項2に記載のシステムオンチップ(SoC)集積回路(I<sub>C</sub>)。

#### 【請求項6】

前記スレーブの各々はそれぞれバッファを含んでおり、要求元のマスタによって要求さ

れた特定のスレーブからのデータは、対応する制御信号が、前記要求元のマスタが、前記

要求したデータを受信する準備ができていないことを前記特定のスレーブに対して示す場

合には、前記特定のスレーブのバッファ内に保持され、前記要求されたデータは、前記対

応する制御信号が、前記マスタが、前記要求したデータを前記特定のスレーブから受信す

る準備ができていることを前記特定のスレーブに対して示すまで、前記特定のスレーブの

バッファ内に保持される請求項2に記載のシステムオンチップ(SoC)集積回路(I<sub>C</sub>)。

#### 【請求項7】

電子システムであって、

バスコントローラと、

スレーブデータバスを経由して前記バスコントローラと相互接続している複数のスレ

ーブと、

マスタデータバスを経由して前記バスコントローラと相互接続している複数のマスタで

あって、前記複数のマスタのうちの第1のものが、前記複数のスレーブのうちの第1のもの

のと、前記複数のスレーブのうちの第2のものとに対する要求を発行するように構成され

、前記複数のマスタのうちの第2のものが、前記複数のスレーブのうちの第1のものに要

求を発行するように構成されている複数のマスタとを備え、

前記複数のスレーブのうちの第1及び第2のものは、データを求める前記要求を受信すると同時に、前記複数のマスタのうちの第1のものから発行された要求に対するデータを提供するように構成され、

前記電子システムは、更に下記を備える：

前記バスコントローラによって前記複数のスレーブに対して発行される制御信号、ただし、前記制御信号は、前記複数のマスタの各々が、要求されたデータをスレーブから受信する準備ができているか否かを前記スレーブに対して示し、そして、前記複数のスレーブのうちの第2のものが、前記複数のマスタのうちの第1のものに前記要求されたデータを送ることによって、前記複数のスレーブのうちの第1のものが、前記複数のマスタのうちの第2のものによって要求されたデータを、前記複数のマスタのうちの第2のものに送ることが遅らせられる替わりとして、前記複数のスレーブのうちの第1のものが、前記複数のマスタのうちの第2のものによって要求されたデータを、前記複数のマスタのうちの第2のものに送ることが引き起こされ、その結果、前記複数のスレーブのうちの第1のものは、前記複数のマスタのうちの第1のものによるスレーブからのデータの受信の準備ができるのを待ってアイドル状態になることが無い、

ただし、前記制御信号は、複数のマスターの各々がスレーブからのデータ受信の準備ができているか否かに関する状態の変化のたびに、前記状態変化が常に反映されるように更新される制御信号であり、

前記複数のスレーブの第2のものは、前記複数のスレーブの第1のものよりも前記複数のマスターの第1のものに対するデータ送信に関し相対的に高い優先度を有するスレーブである。

#### 【請求項8】

前記制御信号は、前記複数のうちのどの1又は複数のマスタが、要求したデータを受信する準備ができていないのかを前記複数のスレーブに対して示す請求項7に記載の電子システム。

#### 【請求項9】

前記制御信号は、前記複数のうちのどの1又は複数のマスタが、要求したデータを受信する準備ができていないのかを前記複数のスレーブに対して示す請求項8に記載の電子システム。

#### 【請求項10】

第1のマスタが、要求した第1のデータを受信する準備ができていないことを第1の制御信号が示す場合、第1のスレーブが、前記第1のマスタによって要求された第1のデータを転送することを遅らせる請求項8に記載の電子システム。

#### 【請求項11】

前記第1の制御信号は更に、第2のマスタが、要求した第2のデータを前記第1のスレーブから受信する準備ができていることを示し、前記第1のスレーブは、前記第1の制御信号に応じ、前記要求された第2のデータを前記第2のマスタへ転送する請求項8に記載の電子システム。

#### 【請求項12】

前記スレーブの各々はそれぞれバッファを含んでおり、要求元のマスタによって要求された特定のスレーブからのデータは、対応する制御信号が、前記要求元のマスタが、前記要求したデータを受信する準備ができていないことを前記特定のスレーブに対して示す場合には、前記特定のスレーブのバッファ内に保持され、前記要求されたデータは、前記対応する制御信号が、前記マスタが、前記要求したデータを前記特定のスレーブから受信する準備ができていることを前記特定のスレーブに対して示すまで、前記特定のスレーブのバッファ内に保持される請求項8に記載の電子システム。

#### 【請求項13】

システムオンチップ(SoC)集積回路(ASIC)であって、

基板と、

前記基板上に配置されたバスコントローラと、

10

20

30

40

50

前記基板上に配置された複数のスレーブであって、前記基板上に配置された各スレーブデータバスを経由して前記バスコントローラと相互接続している複数のスレーブと、

前記基板上に配置され、前記基板上に配置された各マスタデータバスを経由して前記バスコントローラと相互接続している複数のマスタであって、前記複数のマスタのうちの第1のものは、前記複数のスレーブのうちの第1のものと、前記複数のスレーブのうちの第2のものとに対して、データを求める要求を発行するように構成され、そして、前記複数のマスタのうちの第2のものは、前記複数のスレーブのうちの第1のものに対して要求を発行するように構成されている複数のマスタとを備え、

前記スレーブの少なくとも1つは、データを求める要求を受信するとともに、前記要求されたデータを提供し、

前記システムオンチップ(SoC)集積回路(ICS)は、更に下記を備える：

前記バスコントローラによって前記スレーブへ発行される制御信号、ただし、前記制御信号は、要求したデータを前記複数のマスタの各々が受信する準備ができているか否かを前記スレーブに対して示し、そして、前記複数のスレーブうちの第2のものが、前記複数のマスタのうちの第1のものに前記要求されたデータを送ることによって、前記複数のスレーブのうちの第1のものが、前記複数のマスタのうちの第2のものによって要求されたデータを、前記複数のマスタのうちの第2のものに送ることが遅らせられる替わりとして、前記複数のスレーブのうちの第1のものが、前記複数のマスタのうちの第2のものによって要求されたデータを、前記複数のマスタのうちの第2のものに送ることが引き起こされ、その結果、前記複数のスレーブのうちの第1のものは、前記複数のマスタのうちの第1のものによるスレーブからのデータの受信の準備ができるのを待つアイドル状態になることが無い、

ただし、前記制御信号は、複数のマスターの各々がスレーブからのデータ受信の準備ができているか否かに関する状態の変化のたびに、前記状態変化が常に反映されるように更新される制御信号であり、

前記複数のスレーブの第2のものは、前記複数のスレーブの第1のものよりも前記複数のマスターの第1のものに対するデータ送信に関し相対的に高い優先度を有するスレーブである。

#### 【請求項14】

前記制御信号は、前記複数のうちのどの1又は複数のマスタが、要求したデータを受信する準備ができていないのかを前記複数のスレーブに対して示す請求項13に記載のシステムオンチップ(SoC)集積回路(ICS)。

#### 【請求項15】

前記制御信号は、どの1又は複数のマスタが、要求したデータを受信する準備ができるのかを1又は複数のスレーブに対して示す請求項14に記載のシステムオンチップ(SoC)集積回路(ICS)。

#### 【請求項16】

第1のマスタが、要求した第1のデータを受信する準備ができていないことを第1の制御信号が示す場合、第1のスレーブが、前記第1のマスタによって要求された第1のデータを転送することを遅らせる請求項13に記載のシステムオンチップ(SoC)集積回路(ICS)。

#### 【請求項17】

前記第1の制御信号は更に、第2のマスタが、要求した第2のデータを前記第1のスレーブから受信する準備ができていることを示し、前記第1のスレーブは、前記第1の制御信号に応じ、前記要求された第2のデータを前記第2のマスタへ転送する請求項13に記載のシステムオンチップ(SoC)集積回路(ICS)。

#### 【請求項18】

前記スレーブの各々はそれぞれバッファを含んでおり、要求元のマスタによって要求された特定のスレーブからのデータは、対応する制御信号が、前記要求元のマスタが、前記要求したデータを受信する準備ができていないことを前記特定のスレーブに対して示す場

合には、前記特定のスレーブのバッファ内に保持され、前記要求されたデータは、前記対応する制御信号が、前記マスタが、前記要求したデータを前記特定のスレーブから受信する準備ができていることを前記特定のスレーブに対して示すまで、前記特定のスレーブのバッファ内に保持される請求項 13 に記載のシステムオンチップ (S o C) 集積回路 (I C)。

【発明の詳細な説明】

【技術分野】

【0001】

含まれている技術分野は、一般に、システムオンチップ (S o C) 集積回路 (I C) である。更に詳しくは、含まれている技術分野は S o C I C 内のバス利用度を改善する方法である。

10

【背景技術】

【0002】

システムオンチップ (S o C) I C なる用語は、所望及び / 又は必要な全ての機能が、単一のダイ又は基板上に集積及び製造されたシステムを称する。そのため、一般に S o C I C は、例えばマイクロプロセッサ、デジタルシグナルプロセッサ、メモリアレイ、バッファ等のような様々な機能を持つ回路ブロックを含む。そのような機能を有する回路ブロックは、しばしばコアと称される。コアは、互いにデータを交換する S o C I C 内のシステムバス、及び、バスに接続されているその他任意のデバイスに電気的に接続されている。

20

【0003】

更に詳しくは、S o C I C 内では、別のコアへアクセス (データのライト又はリード) 要求を発行するコアは、イニシエータコア、イニシエータ、又はバスマスターなど様々に称される。イニシエータ又はマスターがアクセスを要求するコア、すなわち、ライトデータを受信したり、あるいは、リードデータを提供するコアは、ターゲット又はスレーブと称される。2 以上のコアがデータを配置したり、あるいは、バスからデータ検索を試みる場合に生じるコンフリクトであるバスコンテンツを回避するために、S o C I C 内にバスコントローラが組み込まれる。

【0004】

バスコントローラは、一般に、与えられた時間におけるスレーブへのアクセスについて、どのマスターが許可されるかを選択するアービタを含む。従って、与えられたアクセス又はデータ転送サイクル内において、唯一のマスターのみが、与えられたスレーブへアクセスすることを保証することによって、バス上のデータ衝突及びバスコンテンツが回避される。このアプローチは、スレーブに対するシーケンシャルなアクセスをマスターに提供する。すなわち、マスターは、スレーブにアクセスする順番を持つ。そのようなシーケンシャルなアクセスは、比較的遅く非能率的であり、システムパフォーマンスに悪影響を及ぼしうる。

30

【0005】

バス利用度を高め、もって、システムパフォーマンスを改善するために、スイッチマトリクスタイルのバスコントローラがしばしば使用される。各スレーブ及び各マスターは、それぞれのマスターバスライン又はスレーブバスラインによって、スイッチマトリクスバスコントローラへ接続される。従って、スイッチマトリクスは、スレーブに対する並列アクセスをマスターに提供する。すなわち、異なるマスターが、それぞれ異なるスレーブに同時にアクセスすることができ、また、その逆も可能である。しかしながら、バスコンテンツは、スイッチマトリクスタイルのバスコントローラの使用によって全て回避されるとは限らない。バスコンテンツ及び / 又はデータ衝突は、例えば、1 つのマスターが、2 以上のスレーブへのアクセスを試みる場合、スイッチマトリクスを有する S o C I C 内でも生じうる。各マスターは、対応する単一のバスラインによってスイッチマトリクスに接続されているので、要求元の単一のマスターの要求に対するデータ返信及び / 又は応答のために 2 以上のスレーブが同時に準備される場合、データ衝突が起こりうる。更に、要求シーケンス

40

50

ンスを作成するマスタは、応答又は終了が、なされた要求と同じ順番で返信されることを要求する。

#### 【0006】

データ衝突を回避するためには、マスタの要求の終了順序を保証することに加えて、スイッチマトリックスは、一般に、要求キューを遅延又は経路付けるロジック、あるいは、データ又は応答を格納するバッファとを含む。この経路付けロジックは、前の応答が正しく終了するまで、他の全ての応答をブロックするか遅らせることによって、単一のデータセットのみがバス上に配置されることを保証する。応答キュー又はバッファは、一般にファーストインファーストアウト方式で、マスタからの複数の要求を格納し、バスがデータを受信する準備ができる、かつ、スレーブがバスへデータを配信する準備ができるか、あるいは、マスタがデータを受信する準備ができるかまで、キューにデータを保持することによってデータ衝突を回避する。また、応答キューは、マスタの要求するプログラム順を維持するために、別のスレーブが古い要求に対する応答又はデータ返信を完了するまで待っている間、新たな要求に対する応答又はデータを保持する。10

#### 【0007】

しかしながら、前の要求が正しく完了するまで1又は複数のペンドィング要求を遅らせるか、又は、キューすることは、特に、前の要求を完了する際の遅れが、要求されたデータをバス上に配置する準備ができていないスレーブ、あるいは、バスからのデータを受信する準備ができていないマスタによる場合には、バスキャパシティーを浪費する。そのような状況では、バスは、データ転送のために使用されていないが、そうするのを待っている。言い換れば、そのような状況では、バスはボトルネックではない。従って、他のコアが前の要求又はデータ転送を完了するのをシステムが待っている間、バスはアイドル状態にあり続けるのではなく、利用可能かつ処理の準備ができているデータの転送のために、より効率的に利用されうる。20

#### 【0008】

従って、当該技術に必要なものは、システムオンチップ集積回路内のバス利用度を改善する方法及び装置である。

#### 【発明の開示】

#### 【0009】

改善されたバス利用度及びより効率的なデータ転送を有するシステムオンチップ（S o C）集積回路（I C）が提供される。更に、バス利用度及びデータ転送を改善する方法が提供される。30

#### 【0010】

1つの実施形態では、バスコントローラを有するS o C I Cが提供される。バスコントローラと相互接続されたマスタは、データを求める要求を発行し、この要求に応じたデータを受信する。バスコントローラと相互接続されたスレーブは、データを求める要求を受信し、要求先のマスタに、この要求されたデータを提供する。バスコントローラによって発行される制御信号は、スレーブから要求したデータを受信する準備ができていないのはどのマスタであるかを各スレーブに示す。スレーブは、要求されたデータに対する準備ができていないマスタへのデータ転送を遅らせ、要求したデータをスレーブから受信する準備ができている別のマスタにデータを提供する。40

#### 【0011】

特定のデータ転送を遅らせる要求がスレーブになされると、スレーブは、他のデータの転送を行うことができるので、バス利用度及びデータ転送効率を高め、バスコンテンツ及びデータ衝突を回避することを助ける。

#### 【0012】

更に、S o C I Cのバスコントローラ内のストレージバッファ／レジスタに対するニーズが低減し、もって、バスコントローラのサイズ及び電力消費もまた低減される。

#### 【発明を実施するための最良の形態】

#### 【0013】

前述又はその他の機能及び特徴、及び、それらを達成する方法は、下記の添付図面と連携した実施形態を参照することによって、より明白にかつより良く理解されるであろう。

#### 【0014】

対応する参照符号は、幾つかの視点について一貫した対応部分を示している。本明細書で示された実例は、1つの好適な実施形態を1つの形式で例示し、そのような実例は、何れにせよ、本明細書のみならず特許請求の範囲のスコープを制限するものとして解釈されるべきではない。

#### 【0015】

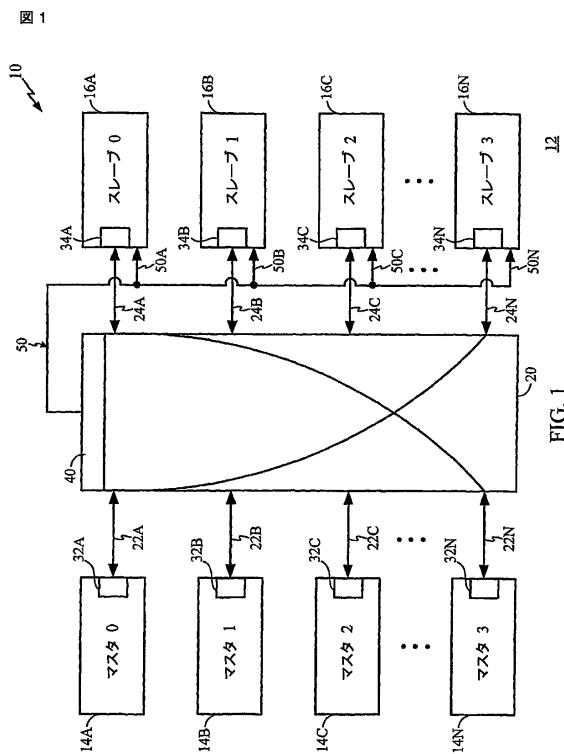

特に図1に示すように、システムオンチップ(SoC)集積回路(1C)10の1つの実施形態が示される。SoC IC 10は、SoC IC 10の全ての回路が製造される基板12を含んでいる。SoC IC 10は、様々な機能を行なうための複数の回路ブロックを含んでいる。

#### 【0016】

更に詳しくは、SoC IC 10は、複数のマスタ14A, 14B, 14C, ..., 14N(以下、集合的にマスタ14と称する)と、複数のスレーブ16A, 16B, 16C, ..., 16N(以下、集合的にスレーブ16と称する)とを含む。マスタ14とスレーブ16は、例えば、マイクロプロセッサとメモリアレイのように、従来式のマスタデバイス及びスレーブデバイスとしてそれぞれ形成される。マスタ14はそれぞれ個別の対応するバス22A, 22B, 22C, ..., 22N(以下、しばしば、マスタ-コントローラバス22、あるいは単にマスタバス22と称する)を介してバスコントローラ20と相互接続されている。同様に、スレーブ16はそれぞれ個別の対応するバス24A, 24B, 24C, ..., 24N(以下、しばしば、スレーブ-コントローラバス22、あるいは単にスレーブバス24と称する)を介してバスコントローラ20と相互接続されている。マスタ14およびスレーブ16はまた一般に、他のバス又は信号ラインを経由して、SoC IC 10内の他のコア(何れも図示せず)と相互接続されている。各マスタ14は好適には、マスタバッファ32A, 32B, 32C, ..., 32Nを含み、同様に、各スレーブ16は好適には、スレーブバッファ34A, 34B, 34C, ..., 34Nを含んでいる。

#### 【0017】

バスコントローラ20は、従来式のスイッチマトリクス形式のバスコントローラの機能を実行することに加えて、スレーブ16A, 16B, 16C, ..., 16Nに制御信号50A, 50B, 50C, ..., 50N(以下、集合的に制御信号50と称する)を発行するロジック回路40を含む。一般に、制御信号50は、各マスタ14がデータを受信する準備ができていることをスレーブ16に示す。更に詳しくは、制御信号50は、マスタ14が、特定のスレーブからのデータを受信する準備ができ、受信することができるのかを各スレーブ16に対して示す。従って、逆の観点から見ると、制御信号50は、マスタ14が「ビジー」である時、あるいは、要求したデータを受信することができず、特定のデータ転送を完了できない時を各スレーブ16に示す。制御信号50は、共有されるか、あるいはバスコントローラ20からスレーブ16へのポイントツーポイントかもしれない。

#### 【0018】

各制御信号50A, 50B, 50C, ..., 50Nは、ステータス、すなわち、マスタ14の動作状態に少なくとも部分的に依存する。マスタ14が、スレーブ16のうちの特定された1つから要求したデータを受信する準備ができている場合、コントローラ20は、特定されたスレーブ16に対して対応する制御信号50を発行し、要求元のマスタ14が、要求したデータを受信する準備ができていることを示す(以下、この制御信号を「レディ」制御信号と称する)。逆に、例えば、要求元のマスタ14が、スレーブ16のうちの別の1つから、前に要求したデータを受信している場合、あるいは「ビジー」である場合のように、マスタ14が、スレーブ16のうちの特定した1つから、要求したデータを受信する準備ができていない場合、コントローラ20は、特定されたスレーブ16に対

10

20

30

40

50

して制御信号 50 を発行し、要求元のマスタ 14 が、前に要求したデータを受信する準備ができていないことを示す（以下、この制御信号 50 を「非レディ」制御信号又は「ビジー」制御信号と称する）。

#### 【0019】

制御信号 50 は、与えられたリードサイクル中に、唯一の要求元マスタのために、唯一のスレーブ 16 のみが、スレーブ - 制御バス 24、コントローラ - マスタバス 22 上にデータを配置することを保証する。従って、制御信号 50 は、2 以上のスレーブ 16 が、同じ要求元マスタ 14 に向けられたデータをコントローラ 20 に与えた場合、コントローラ - マスタバス 22 上で生じうるデータ衝突を回避する。

#### 【0020】

更に、要求元のマスタが、要求したデータを特定のスレーブから受信する準備ができていないことを示す場合、制御信号 50 は、スレーブに対して、もしも準備できているのであれば、別の要求マスタに対して別のデータ転送を行うように指示する。従って、スレーブは、マスタがデータを受信するのに「レディ」になることを待つアイドル状態にはならず、データを受信することが「レディ」である別の要求元マスタに対して別のデータ転送を行う。遅れたデータ転送動作の完了を待つのではなく、別のデータ転送動作を実行することによって、バスによって処理されるデータ効率、すなわち、バス利用度が改善される。他の応答は、バスコンテンツによってコントローラが受け付けることができない応答の陰でブロックされうるので、これはまた、要求のレイテンシ全体をも低減しうる。

#### 【0021】

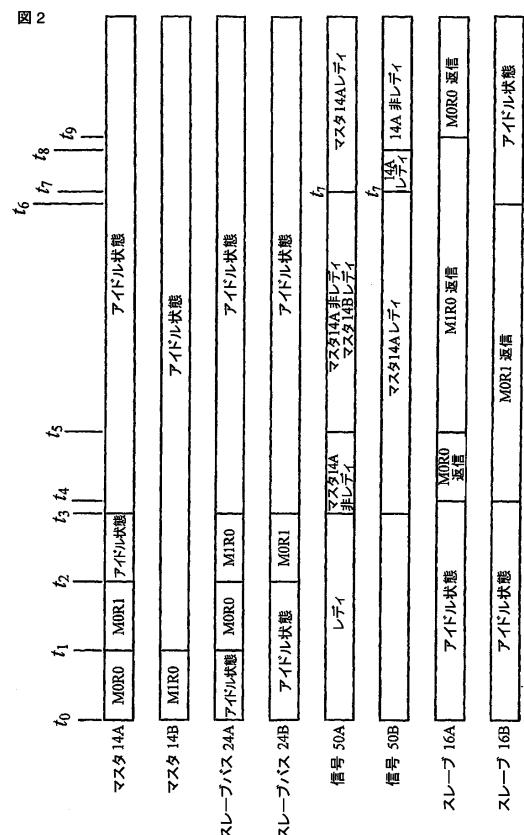

SOC 10 の動作、及び、システムオンチップ集積回路におけるバス利用度を改善する方法を例示する典型的なデータ転送処理が、図 2 に示され、以下に説明される。時間  $t_0$  において、マスタ 14A は、マスタバス 22A を経由してバスコントローラ 20 へ、スレーブ 16A からデータを読み取る要求 M0R0 を発行する。また、時間  $t_0$  の間、マスタ 14B は、マスタバス 22B を経由してバスコントローラ 20 へ、スレーブ A からデータを読み取る要求 M1R0 を発行する。時間  $t_1$  において、マスタ 14A は、マスタバス 22A を経由してバスコントローラ 20 へ、スレーブ 16B からデータを読み取る要求 M0R1 を発行する。従って、2 つのマスタ（マスタ 14A, 14B）が同じスレーブ（スレーブ 16A）からデータを要求し、1 つのマスタ（マスタ 14A）が、2 つの異なるスレーブ（スレーブ 16A, 16B）からデータを要求している。

#### 【0022】

更に、時間  $t_1$  では、バスコントローラ 20 が時間  $t_0$  においてマスタ 14A によって発行されたスレーブ 16A からデータを求める要求 M0R0 を、スレーブバス 24A を経由してスレーブ 16A に渡す。同様に、時間  $t_2$  では、バスコントローラ 20 が時間  $t_0$  においてマスタ 14B によって発行されたスレーブ 16A からデータを求める要求 M1R0 を、スレーブバス 24A を経由してスレーブ 16A に渡す。更に、時間  $t_2$  では、バスコントローラ 20 が時間  $t_1$  においてマスタ 14A によって発行されたスレーブ 16B からデータを求める要求 M0R1 を、スレーブバス 24B を経由してスレーブ 16B に渡す。

#### 【0023】

制御信号 50A, 50B は、図 2 に示すように、時間  $t_0$  において、デフォルト値、又は、例えば「レディ」状態のようなデフォルト状態に初期設定され、全てのマスタ 14 が、データを受信する準備ができていることを示す。時間  $t_3$  では、バスコントローラ 20 が、制御信号 50 を発行又は更新し、要求データのうちの少なくとも 1 セットの転送を可能にする。更に詳しくは、制御信号 50B が更新され、マスタ 14A が、前に要求したデータをスレーブ 16B から受信する準備ができていることが示される。この例では、制御信号 50 は「レディ」状態に初期化されるので、制御信号 50B に対する変更はない。反対に、制御信号 50A, 50C, ..., 50N が更新され、マスタ 14A が「ビジー」動作中であること、すなわち、データを受信する処理をしていることがスレーブ 16A, 16C, ..., 16N にそれぞれ示される。

10

20

30

40

50

**【0024】**

簡潔さと明瞭さの理由で、制御信号 50A, 50B のみが図 2 で示される。更に同じ理由で、当業者であれば、各制御信号 50 は実際には複数の信号であることを認識するであろうが、図 2 は、各制御信号に対して 1 のみの信号ラインを示し、マスタ 14 に関連する信号ラインの適切な条件又は状態を示している。

**【0025】**

時間  $t_4$  では、スレーブ 16A, 16B の各々が、前に要求したマスタであるマスタ 14 A へデータを転送する準備ができる。更に詳しくは、時間  $t_4$  において、スレーブ 16A は、要求 M0R0 に関連するデータをマスタ 14 A へ転送する準備ができ、スレーブ 16B は、要求 M0R1 に関連するデータをマスタ 14 A へ転送する準備ができる。スレーブ 16A, 16B はともにマスタ 14 A へデータを提供する準備ができているが、スレーブ 16B は、上述したように、コントローラ 20 によって発行される制御信号 50 によって優先度が与えられる。与えられた任意の読み取りサイクルにおいても、1 つのマスタ 14 に対してデータを送る準備ができているスレーブ 16 間の相対的な優先度は、当業者に周知の所望あるいは好適な方法に従って予め定められることが特に留意されるべきである。この優先度は、例えば、任意に設定されたり、あるいは、特定のスレーブが、特定の回路又はアプリケーションに照らし合わせて提供しうる予測又は予期された重要度に従って設定される。あるいは、その他任意の所望の基準に従って設定される。

10

**【0026】**

スレーブ 16A は、時間  $t_4$  において、マスタ 14 A に、要求 M0R0 に関連するデータを返すことを試みる。しかしながら、そうすることは、上述したように、マスタ 14 A が「ビジー」であることをスレーブ 16A に示す制御信号 50A によって阻止される。従来技術による SOC IC システムでは、そのような状況は、スレーブ 16A がマスタ 14 A に対してデータを戻すことを試みた場合、戻されているデータをバッファするようコントローラ 20 に要求することであるマスタバス 22A におけるデータ衝突、あるいは、スレーブ 16A が、要求 M0R0 に関連するデータのマスタ 14 A への転送を完了できるまで、スレーブ 16A において、その他全ての要求データのマスタ 14 への転送を遅れることのうちの何れかの結果になるであろう。対照的に、そして以下に更に詳しく説明するように、スレーブ 16A は、要求された他のデータを、他の要求元のマスタ 14 へ転送し、もって、バス 22, 24 をより効率的に利用し、より効率的なデータ転送を達成する。

20

**【0027】**

また、時間  $t_4$  において、スレーブ 16B は、要求 M0R1 に関連したマスタ 14 A へのデータの転送を始める。このデータ転送は、時間  $t_3$  において、マスタ 14 A が、スレーブ 16B からのデータを受信する準備ができていることを示すように制御信号 50B を設定し、マスタ 14 A が「ビジー」であり、スレーブ 16A, 16C, ..., 16N からのデータを受信する準備ができていないことを示すように制御信号 50A を設定するコントローラ 20 によって少なくとも部分的にイネーブルされる。時間  $t_4$  から時間  $t_6$  まで、要求 M0R1 に関連するデータは、スレーブバス 24B を経由してスレーブ 16B からバスコントローラ 20 へ戻され、マスタバス 22A を経由してバスコントローラ 20 からマスタ 14 A へ戻される。

30

**【0028】**

上述したデータ転送方法、すなわち、一般に、対応するスレーブバス 24 を経由したスレーブ 16 からのバスコントローラ 20 への転送、対応するマスタバス 22 を経由したバスコントローラ 20 からのマスタ 14 への転送では、バスコントローラ 20 は、本質的には、マスタとスレーブとの間の関係を単に確立するスイッチマトリックスとして動作することに特に注目されるべきである。転送されるデータは、コントローラ 20 において格納されるのではなく、スレーブ 16 において、あるいは、スレーブ 16 のバッファ 34 内に格納され続ける。従って、バスコントローラ 20 内でのストレージレジスタ又はバッファリングに対するニーズは本質的に低減する。従って、バスコントローラ 20 はサイズを低

40

50

減することができ、かつ、かなりの数のバッファ／ストレージレジスタを必要とする従来式のバスコントローラよりも少ない電力しか消費しない。

#### 【0029】

上述したように、スレープ16、及び、バス22，24の一部に対して、要求元のマスター14がデータを受信する準備ができるまでアイドルになるよう強制するのではなく、本明細書に記載のシステムオンチップ集積回路においてバス利用度を改善する方法及びS0C I C 10は、スレープが、要求された他のデータを、他の要求元のマスター14に対して転送することを可能にするので、バス22，24をより効率的に利用し、より効率的なデータ転送を達成する。この局面は、マスター14Aが、遅れた要求M0R0に関連するデータを受信する準備ができるまで、スレープ16Aが全てのデータの転送を遅らせるのではなく、スレープ16Aが、時間t<sub>5</sub>において、要求M1R0に関連するデータのマスター14Bへの転送を開始する場合として図2に例示されている。要求M1R0に関連したデータの転送は、マスター14Aは「ビジー」であるが、マスター14Bはデータを受信する準備ができていることをスレープ16Aに示す制御信号50によってイネーブルされる。10

#### 【0030】

従って、時間t<sub>4</sub>において、スレープ16Aからマスター14Aへのデータの転送を遅らせることによって、かつ、時間t<sub>5</sub>において、スレープ16Aが、マスター14Bへのデータ転送を開始できるようにすることによって、時間t<sub>4</sub>におけるマスター・コントローラバス22A上のデータ衝突が回避され、時間t<sub>4</sub>におけるマスター・コントローラバス22Aとスレープ・コントローラバス24Aの利用が高められ、もって、データ転送効率が向上する。20

#### 【0031】

スレープ16Aは、時間t<sub>9</sub>において、マスター14Bへの、要求M1R0に関連する転送を完了する。従って、時間t<sub>10</sub>において、制御信号50がコントローラ20によって更新され、スレープ16に対して、マスター14Bが再びデータを受信する準備ができたことを示す（図2には図示せず）。示された例では、更なるデータはマスター14Bに転送されない。

#### 【0032】

時間t<sub>6</sub>において、スレープ16Bは、マスター14Aへの、要求M0R1に関連するデータの転送を完了する。従って、時間t<sub>7</sub>において、制御信号50がコントローラ20によって更新され、スレープ16に対して、マスター14Aが再びデータを受信する準備ができたことを示す。時間t<sub>8</sub>において、制御信号50が再びコントローラ20によって更新され、マスター14Aが再びデータを受信する準備をしていること、あるいは、マスター14Aがデータを受信している途中であることを示す。更に詳しくは、時間t<sub>8</sub>において、制御信号50がコントローラ20によって更新され、制御信号50Aが、スレープ16Aに対して、マスター14Aが、要求M0R0に関連するデータを受信する準備ができるようになる。そして、制御信号50B, 50C, ..., 50Nが更新され、マスター14Aが「ビジー」であることが示される。その後、時間t<sub>9</sub>において、要求M0R0に関連するスレープ16Aからマスター14Aへのデータの転送が始まる。3040

#### 【0033】

上述した説明は、好適な設計を参照しているが、この好適な設計は更に、本開示の範囲及び精神の中で変形することができる。従って、本応用は、本明細書で開示された一般的な原理を用いて、好適な設計のあらゆる変形、利用、又は適応をカバーすることが意図されている。更に、本応用は、関連技術における周知又は慣例的な実施内で見い出され、かつ、特許請求の範囲の制限内にあるような本開示からの新案もカバーすることが意図されている。なお、本願の出願当初の請求項と同一の記載を「その他の実施例」として以下に付記する。

#### [その他の実施例1]

バスコントローラと、

それが、各マスタデータバスを経由して前記バスコントローラと相互接続しており、データを求める要求を発行するとともに、前記要求に対するデータを受信する少なくとも1つのマスタと、

それが、各スレーブデータバスを経由して前記バスコントローラと相互接続しており、データを求める要求を受信するとともに、その要求に対するデータを提供する少なくとも1つのスレーブと、

前記バスコントローラによって発行される制御信号であって、マスタが、要求したデータをスレーブから受信する準備ができていることを各スレーブに対して示す制御信号とを備えるシステムオンチップ（S o C）集積回路（I C）。

[他の実施例 2]

10

前記制御信号は、どのマスタが、要求したデータを受信する準備ができていないのかを各スレーブに対して示す他の実施例1に記載のシステムオンチップ（S o C）集積回路（I C）。

[他の実施例 3]

前記制御信号は更に、どのマスタが、要求したデータを受信する準備ができているのかを各スレーブに対して示す他の実施例2に記載のシステムオンチップ（S o C）集積回路（I C）。

[他の実施例 4]

20

第1のマスタが、要求した第1のデータを受信する準備ができていないことを第1の制御信号が示す場合、第1のスレーブが、前記第1のマスタによって要求された第1のデータを転送することを遅らせる他の実施例2に記載のシステムオンチップ（S o C）集積回路（I C）。

[他の実施例 5]

前記第1の制御信号は更に、第2のマスタが、要求した第2のデータを前記第1のスレーブから受信する準備ができていることを示し、前記第1のスレーブは、前記第1の制御信号に応じ、前記要求された第2のデータを前記第2のマスタへ転送する他の実施例2に記載のシステムオンチップ（S o C）集積回路（I C）。

[他の実施例 6]

30

前記スレーブの各々はそれぞれバッファを含んでおり、要求元のマスタによって要求された特定のスレーブからのデータは、対応する制御信号が、前記要求元のマスタが、前記要求したデータを受信する準備ができていないことを前記特定のスレーブに対して示す場合には、前記特定のスレーブのバッファ内に保持され、前記要求されたデータは、前記対応する制御信号が、前記マスタが、前記要求したデータを前記特定のスレーブから受信する準備ができていることを前記特定のスレーブに対して示すまで、前記特定のスレーブのバッファ内に保持される他の実施例2に記載のシステムオンチップ（S o C）集積回路（I C）。

[他の実施例 7]

バスコントローラと、

それが、各マスタデータバスを経由して前記バスコントローラと相互接続しており、データを求める要求を発行するとともに、前記要求に対するデータを受信する少なくとも1つのマスタと、

それが、各スレーブデータバスを経由して前記バスコントローラと相互接続しており、データを求める要求を受信するとともに、前記要求に対するデータを提供するよう構成された少なくとも1つのスレーブと、

前記バスコントローラによって前記スレーブへ発行される制御信号であって、要求したデータを前記マスタが受信する準備ができていることを前記スレーブに対して示す制御信号と

を備える電子システム。

[他の実施例 8]

50

前記制御信号は、どのマスタが、要求したデータを受信する準備ができていないのかを

前記スレープに対して示すその他の実施例 7 に記載の電子システム。

[他の実施例 9]

前記制御信号は、どのマスタが、要求したデータを受信する準備ができていないのかを前記スレープに対して示すその他の実施例 8 に記載の電子システム。

[他の実施例 10]

第 1 のマスタが、要求した第 1 のデータを受信する準備ができていないことを第 1 の制御信号が示す場合、第 1 のスレープが、前記第 1 のマスタによって要求された第 1 のデータを転送することを遅らせるその他の実施例 8 に記載の電子システム。

[他の実施例 11]

前記第 1 の制御信号は更に、第 2 のマスタが、要求した第 2 のデータを前記第 1 のスレープから受信する準備ができていることを示し、前記第 1 のスレープは、前記第 1 の制御信号に応じ、前記要求された第 2 のデータを前記第 2 のマスタへ転送するその他の実施例 8 に記載の電子システム。

10

[他の実施例 12]

前記スレープの各々はそれぞれバッファを含んでおり、要求元のマスタによって要求された特定のスレープからのデータは、対応する制御信号が、前記要求元のマスタが、前記要求したデータを受信する準備ができていないことを前記特定のスレープに対して示す場合には、前記特定のスレープのバッファ内に保持され、前記要求されたデータは、前記対応する制御信号が、前記マスタが、前記要求したデータを前記特定のスレープから受信する準備ができていることを前記特定のスレープに対して示すまで、前記特定のスレープのバッファ内に保持されるその他の実施例 8 に記載の電子システム。

20

[他の実施例 13]

基板と、

前記基板上に配置されたバスコントローラと、

それぞれが、前記基板上に配置された各マスタデータバスを経由して前記バスコントローラと相互接続しており、データを求める要求を発行するとともに、前記要求に対するデータを受信する少なくとも 1 つのマスタと、

それぞれが、前記基板上に配置された各スレーブデータバスを経由して前記バスコントローラと相互接続しており、データを求める要求を受信するとともに、前記要求に対するデータを提供するように構成された少なくとも 1 つのスレーブと、

30

前記バスコントローラによって前記スレープへ発行される制御信号であって、要求したデータを前記マスタが受信する準備ができていることを前記スレープに対して示す制御信号と

を備えるシステムオンチップ (S o C) 集積回路 (I C)。

[他の実施例 14]

前記制御信号は、どのマスタが、要求したデータを受信する準備ができていないのかを前記スレープに対して示すその他の実施例 13 に記載のシステムオンチップ (S o C) 集積回路 (I C)。

[他の実施例 15]

前記制御信号は、どのマスタが、要求したデータを受信する準備ができているのかを前記スレープに対して示すその他の実施例 14 に記載のシステムオンチップ (S o C) 集積回路 (I C)。

40

[他の実施例 16]

第 1 のマスタが、要求した第 1 のデータを受信する準備ができていないことを第 1 の制御信号が示す場合、第 1 のスレープが、前記第 1 のマスタによって要求された第 1 のデータを転送することを遅らせるその他の実施例 13 に記載のシステムオンチップ (S o C) 集積回路 (I C)。

[他の実施例 17]

前記第 1 の制御信号は更に、第 2 のマスタが、要求した第 2 のデータを前記第 1 のスレープから受信する準備ができていることを示し、前記第 1 のスレープは、前記第 1 の制御

50

信号に応じ、前記要求された第2のデータを前記第2のマスタへ転送するその他の実施例

13に記載のシステムオンチップ(SoC)集積回路(I<sub>C</sub>)。

[その他の実施例18]

前記スレーブの各々はそれぞれバッファを含んでおり、要求元のマスタによって要求された特定のスレーブからのデータは、対応する制御信号が、前記要求元のマスタが、前記要求したデータを受信する準備ができていないことを前記特定のスレーブに対して示す場合には、前記特定のスレーブのバッファ内に保持され、前記要求されたデータは、前記対応する制御信号が、前記マスタが、前記要求したデータを前記特定のスレーブから受信する準備ができていることを前記特定のスレーブに対して示すまで、前記特定のスレーブのバッファ内に保持されるその他の実施例13に記載のシステムオンチップ(SoC)集積回路(I<sub>C</sub>)。

10

[その他の実施例19]

電子システム内でデータを転送する方法であって、

要求したデータを1又は複数のマスタに提供する要求を1又は複数のスレーブに対して発行することと、

1又は複数の第1のマスタが、要求したデータを第1のスレーブから受信する準備ができていない時を前記第1のスレーブに示すことと、

前記第1のスレーブから前記1又は複数の第1のマスタへのデータの転送を遅らせることと

を備える方法。

20

[その他の実施例20]

前記遅らせるステップは更に、要求を行い、前記第1のスレーブからデータを受信する準備ができている第2のマスタへ、前記第1のスレーブからデータを転送することを備えるその他の実施例19に記載のデータ転送方法。

[その他の実施例21]

前記遅らせるステップは、前記第1のマスタによって要求されたデータを、前記第1のスレーブのバッファ内に保持することを含むその他の実施例19に記載のデータ転送方法。

[その他の実施例22]

前記示すステップは、前記1又は複数のスレーブに対して制御信号を発行することを備え、前記制御信号は、前記1又は複数のマスタの各々が、前記1又は複数のスレーブの各々からデータを受信する準備ができているかを示すその他の実施例19に記載のデータ転送方法。

30

[その他の実施例23]

システムオンチップ(SoC)集積回路(I<sub>C</sub>)内のバスコンテンションを低減し、バス利用度を改善する方法であって、前記システムオンチップ(SoC)集積回路(I<sub>C</sub>)は、1又は複数のスレーブから、それぞれのマスタバスを経由してデータを受信するよう構成された1又は複数のマスタを有しており、前記方法は、

要求したデータを、それぞれのマスタバスを経由して前記1又は複数のマスタへ提供する要求を前記1又は複数のスレーブに対して発行することと、

40

前記第1のマスタのうちの1又は複数が、それぞれのマスタバスを経由してデータを受信しており、もって、前記要求したデータを第1のスレーブから受信する準備ができていないときを前記第1のスレーブに示すことと、

それぞれのマスタバスを経由してデータを受信しており、もって、前記第1のスレーブからデータを受信する準備ができていない前記1又は複数の第1のマスタへの、前記第1のスレーブからのデータの転送を遅らせることによって、バスコンテンションを低減することと

を備える方法。

[その他の実施例24]

データを要求し、前記データを前記第1のスレーブから受信する準備ができている第2

50

のマスタへ、前記第1のスレーブからデータを転送することによって、バスコンテンションを改善するステップを更に備えるその他の実施例23に記載の方法。

[その他の実施例25]

前記バスコンテンションを低減するステップは、前記第1のマスタによって要求されたデータを、前記第1のスレーブのバッファ内に保持することを含むその他の実施例24に記載の方法。

【図面の簡単な説明】

【0034】

【図1】図1は、システムオンチップ集積回路の1つの実施形態のブロック図である。

【図2】図2は、システムオンチップ集積回路におけるバス利用度改善方法の1つの実施形態を図示するタイミングブロック図である。 10

【図1】

FIG. 1

【図2】

FIG. 2

---

フロントページの続き

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72)発明者 ガナサン、ジェイ・・プラカシュ・サプラマニアム

アメリカ合衆国、ノース・カロライナ州 27596、ヤングズビル、プレストウッド・ドライブ

35

(72)発明者 リマクラス、ペリー・ウィルマン・ジュニア。

アメリカ合衆国、ノース・カロライナ州 27609、ローリー、イングルウッド・レーン 53

13

審査官 坂東 博司

(56)参考文献 特開平09-069855(JP,A)

特開平09-114735(JP,A)

米国特許第05907485(US,A)

米国特許第06441479(US,B1)

米国特許第05581729(US,A)

(58)調査した分野(Int.Cl., DB名)

G06F 13/36