(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-306167

(P2008-306167A)

(43) 公開日 平成20年12月18日(2008.12.18)

| (51) Int.Cl.          | F 1        | テーマコード (参考) |

|-----------------------|------------|-------------|

| HO1L 29/786 (2006.01) | HO1L 29/78 | 616V 4M104  |

| HO1L 29/417 (2006.01) | HO1L 29/78 | 616U 5F033  |

| HO1L 29/423 (2006.01) | HO1L 29/50 | M 5F110     |

| HO1L 29/49 (2006.01)  | HO1L 29/58 | G           |

| HO1L 21/28 (2006.01)  | HO1L 21/28 | 301R        |

審査請求 有 請求項の数 18 O.L. (全 10 頁) 最終頁に続く

|              |                            |          |                                    |

|--------------|----------------------------|----------|------------------------------------|

| (21) 出願番号    | 特願2008-97547 (P2008-97547) | (71) 出願人 | 507134301<br>北京京東方光電科技有限公司         |

| (22) 出願日     | 平成20年4月3日 (2008.4.3)       |          | 中華人民共和国北京經濟技術開發區西環中                |

| (31) 優先権主張番号 | 200710100342.0             |          | 路8號                                |

| (32) 優先日     | 平成19年6月8日 (2007.6.8)       | (74) 代理人 | 100064908<br>弁理士 志賀 正武             |

| (33) 優先権主張国  | 中国(CN)                     | (74) 代理人 | 100089037<br>弁理士 渡邊 隆              |

|              |                            | (74) 代理人 | 100108453<br>弁理士 村山 靖彦             |

|              |                            | (74) 代理人 | 100110364<br>弁理士 実広 信哉             |

|              |                            | (72) 発明者 | 薛 建設<br>中華人民共和国北京經濟技術開發區西環中<br>路8號 |

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ及びその製造方法

## (57) 【要約】

【課題】薄膜トランジスタ液晶表示装置の薄膜トランジスタ及びその製造方法を提供する。

【解決手段】ゲート電極、ゲート絶縁層、活性層及びソースドレイン電極を有した薄膜トランジスタであって、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられており、該ソースドレイン電極と該活性層のソースドレイン領域は重なり、該活性層と前記ソースドレイン電極間に電子の走行を許容する薄いSiNx又はSiOxNy層が設けられる。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

ゲート電極、ゲート絶縁層、活性層及びソース・ドレイン電極を有する薄膜トランジスタであって、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられ、該ソース・ドレイン電極と該活性層のソース・ドレイン領域は重なり、該活性層と前記ソース・ドレイン電極間に電子がトンネルして通過するのを許容する薄いSiNx層又はSiOxNy層が設けられることを特徴とする薄膜トランジスタ。

**【請求項 2】**

前記SiNx層又はSiOxNy層の厚みは約8～15nmであることを特徴とする請求項1に記載の薄膜トランジスタ。 10

**【請求項 3】**

前記ソース・ドレイン電極の材料はアルミニウム合金であることを特徴とする請求項1に記載の薄膜トランジスタ。

**【請求項 4】**

前記アルミニウム合金は、AlNd、AlTa、AlNi、AlZr、AlCu及びAlNdNiであることを特徴とする請求項3に記載の薄膜トランジスタ。

**【請求項 5】**

前記薄膜トランジスタはボトムゲート型トランジスタであることを特徴とする請求項1に記載の薄膜トランジスタ。 20

**【請求項 6】**

前記薄膜トランジスタはトップゲート型トランジスタであることを特徴とする請求項1に記載の薄膜トランジスタ。

**【請求項 7】**

前記活性層は半導体層とオーム接触層の積層であり、該オーム接触層と前記ソース・ドレイン電極間に電子がトンネルして通過するのを許容する薄いSiNx層又はSiOxNy層が設けられることを特徴とする請求項1に記載の薄膜トランジスタ。

**【請求項 8】**

前記オーム接触層はドーピング半導体層又はシリコンマイクロ結晶層であることを特徴とする請求項7に記載の薄膜トランジスタ。 30

**【請求項 9】**

薄膜トランジスタのゲート電極、ゲート絶縁層、活性層及びソース・ドレイン電極を形成する工程を備える薄膜トランジスタ製造方法であって、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられ、該ソース・ドレイン電極は該活性層のソース・ドレイン領域と重なり、該活性層と前記ソース・ドレイン電極間に電子がトンネルして通過するのを許容する薄いSiNx層又はSiOxNy層が設けられることを特徴とする薄膜トランジスタの製造方法。

**【請求項 10】**

前記SiNx又はSiOxNy層の厚みは約8～15nmであることを特徴とする請求項9に記載の薄膜トランジスタの製造方法。 40

**【請求項 11】**

前記ソース・ドレイン電極の材料はアルミニウム合金であることを特徴とする請求項9に記載の薄膜トランジスタの製造方法。

**【請求項 12】**

前記アルミニウム合金は、AlNd、AlTa、AlNi、AlZr、AlCu及びAlNdNiであることを特徴とする請求項11に記載の薄膜トランジスタ。

**【請求項 13】**

前記活性層は半導体層とオーム接触層の積層であり、該オーム接触層と前記ソース・ドレイン電極間に電子がトンネルして通過するのを許容する薄いSiNx層又はSiOxNy層が設けられることを特徴とする請求項9に記載の薄膜トランジスタの製造方法。 50

## 【請求項 1 4】

前記オーム接触層はドーピング半導体層又はシリコンマイクロ結晶層であることを特徴とする請求項 1 3 に記載の薄膜トランジスタの製造方法。

## 【請求項 1 5】

ゲート電極、ゲート絶縁層、活性層及びソース・ドレイン電極を有した、画素ユニットのスイッチ素子としての薄膜トランジスタを備える薄膜トランジスタ液晶表示装置であって、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられ、該ソース・ドレイン電極と該活性層のソース・ドレイン領域は重なり、該活性層と前記ソース・ドレイン電極間に電子がトンネルして通過するのを許容する薄い  $SiN_x$  層又は  $SiO_xNy$  層が設けられることを特徴とする薄膜トランジスタ液晶表示装置。10

## 【請求項 1 6】

前記ソース・ドレイン電極のうちの一つと接続する画素電極をさらに備える請求項 1 5 に記載の薄膜トランジスタ液晶表示装置。

## 【請求項 1 7】

前記画素電極はビアホールを通して前記ソース・ドレイン電極のうちの一つと電気的に接続されることを特徴とする請求項 1 5 に記載の薄膜トランジスタ液晶表示装置。20

## 【請求項 1 8】

前記画素電極は前記ソース・ドレイン電極のうちの一つに直接ラップされていることを特徴とする請求項 1 5 に記載の薄膜トランジスタ液晶表示装置。20

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本発明は、薄膜トランジスタとその製造方法、及び該薄膜トランジスタを備えた薄膜トランジスタ液晶表示装置 ( TFTLCD ) に関する。30

## 【背景技術】

## 【0 0 0 2】

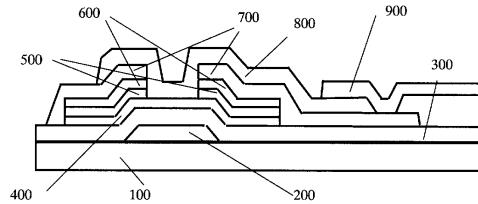

薄膜トランジスタ ( TFT ) は、LCD 表示装置において画素ユニットのスイッチ素子として用いられる。図 1 は、現在殆どの TFT LCD メーカが採用するボトムゲート型 TFT を示している。該ボトムゲート型 TFT は、主にガラス基板 100 と、該ガラス基板上において下から上へ順に形成されたゲート 200 、ゲート絶縁層 300 、半導体層 400 、ドーピング半導体層 500 、ソースドレイン電極 700 、パッシベーション層 800 、画素電極層 900 を備える。また、該ボトムゲート型 TFT は以下の工程を通して製造される。30

## 【0 0 0 3】

1 、マグネットスパッタ方式によって基体 ( 例えば、ガラス又はシリコン単結晶 ) 上に金属薄膜を堆積した後、フォトリソグラフィとエッチングによってゲートラインとゲート電極パターンを形成する。従来、該金属薄膜のターゲット材料として通常 Al と Al 合金が用いられるが、例えば集積回路 ( IC ) を形成する際にはその他の金属及び合金も使える。40

## 【0 0 0 4】

2 、化学気相堆積法 ( CVD ) によって  $SiN_x$  又は  $SiO_xNy$  薄膜層を形成してゲート絶縁層とし、さらに CVD 法で同一工程において該ゲート絶縁層上に半導体層 ( 例えば、 a - Si 層 ) とドーピング半導体層 ( 例えば、 N + a - Si 層 ) を堆積し、その後フォトリソグラフィとドライエッチングによって該半導体層とドーピング半導体層をパターニングして、シリコンアイランドとチャンネル領域を形成する。

## 【0 0 0 5】

3 、マグネットスパッタ法によってドーピング半導体層に金属層を堆積した後、フォトリソグラフィとエッチングによってソース・ドレイン電極及びデータラインをパターニングして形成する。該ソース・ドレイン電極とデータラインの材料として、 Mo 、 Cr 、 Ti 50

とM o Wなどの高融点の金属又は合金を含み、上記形成された該ソース・ドレイン電極はそれぞれドーピング半導体層と良好なオーム接触を実現する。

【0006】

4、CVD法でパッシベーション層（例えば、SiO<sub>x</sub>N<sub>y</sub>）を堆積し、且つフォトリソグラフィとエッティングによってチャネル保護層を形成すると同時に、保護層にピアホールをエッティングする。

【0007】

5、マグネットスパッタ法によって画素電極層（例えば、ITO導電薄膜）を堆積し、且つフォトリソグラフィとエッティングによって画素電極パターンを形成し、該画素電極は前記ピアホールを介して例えばドレイン電極に接続する。

10

【0008】

以上の工程によって形成されたTFT構造は以下の特徴を有する。即ち、構造が簡単で、製造が容易であり、各層のパターン形成工程が簡単である上に、歩どまりが高く、6mask、5mask、4mask、ひいては3mask工程（一つのマスクは1回のフォトリソグラフィとエッティングに対応する）でみな完成でき、且つ設備を変更する必要がない。

【0009】

しかし、TFT LCDテレビ市場の需要が拡大するに従って、生産ラインの数が段々増加し、パネルのサイズも益々大きくなっている。サイズが大きく、テレビに用いられるパネルに対する要求は、サイズが小さく、コンピュータ表示装置に用いられるパネルに対する要求と異なる。パネルサイズの増加により、ゲートラインとデータラインの長さも増加され、これらの導線の総抵抗も増大するため、データ遅延の問題が発生し、これにより、例えば、X方向のクロストーク（cross-talk）及び横方向の輝度が均一でない（H-dim）などの問題を引き起こす。従って、上記工程によって大きいサイズのテレビ用パネルを製造する際に、以上の問題点を解決しなければならない。

20

【0010】

大きいサイズのテレビ用パネルについて、現在、ソース・ドレイン電極に用いられる、例えばMo、Crなどの高抵抗及び高融点金属又は合金を取り替える材料として、Al又はAl合金を含む材料が採用される。しかし、Al層とN+ドーピング半導体層との接触があまりよくないため、仕事関数の差が割合に大きい。よって、まずバッファー層として底層に必ず薄いMo層を堆積しなければならない。また、画素電極とAlの接触不良を解決するため、Al層の上面にさらにもう一層の薄いMo層を堆積する必要がある。これによって、Al層とITO薄膜の接触抵抗が大きい問題を解決するだけではなく、受熱途中における純Alのヒルロック（hilllock）問題を解決できる。しかしながら、このようなサンドイッチ式の構造を採用した場合また以下の問題が生じた。

30

【0011】

1、中間層のAl金属と底部、頂部のMo金属の腐食速度が異なるため、ソース・ドレイン電極が断れたりして、エッティング上の問題を引き起こした。

【0012】

2、二種類の金属を3層堆積しなければならないため、一種類の金属を堆積する場合に比べて堆積時間を増加し、生産能力を低減した。

40

【0013】

3、現在Moの価格がAlの価格を大きく超えているため、生産コストを高めた。

【発明の開示】

【発明が解決しようとする課題】

【0014】

本発明は上記問題点に鑑みてなされたもので、TFT LCDの薄膜トランジスタ及びその製造方法を提供し、ソース・ドレイン電極の構造及びその製造方法を変更することで、ソース・ドレイン電極が断線するなどの欠陥を克服して、生産能力を高めると共に、コストを下げる目的とする。

50

## 【課題を解決するための手段】

## 【0015】

本発明の薄膜トランジスタは、ゲート電極、ゲート絶縁層、活性層及びソース・ドレイン電極を備え、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられ、該ソース・ドレイン電極は該活性層のソース・ドレイン領域と重なり、該活性層と前記ソース・ドレイン電極間に電子がトンネルして通過するのを許容する薄いSiNx又はSiOxNy層が設けられている。

## 【0016】

本発明の薄膜トランジスタの製造方法は、薄膜トランジスタのゲート電極と、ゲート絶縁層と、活性層及びソース・ドレイン電極を形成する工程を有し、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層の間に設置され、該ソース・ドレイン電極は該活性層のソース・ドレイン領域と重なり、該活性層と前記ソース・ドレイン電極の間に電子がトンネルして通過するのを許容する薄いSiNx又はSiOxNy層が設けられている。

10

## 【0017】

本発明の薄膜トランジスタ液晶表示装置は、画素ユニットのスイッチ素子としての薄膜トランジスタを有し、該薄膜トランジスタは、ゲート電極、ゲート絶縁層、活性層及びソース・ドレイン電極を含み、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられており、該ソース・ドレイン電極は該活性層のソース・ドレイン領域と重なり、該活性層と前記ソース・ドレイン電極間に電子がトンネルして通過するのを許容する薄いSiNx又はSiOxNy層が設けられている。

20

## 【発明を実施するための最良の形態】

## 【0018】

以下に、図面と具体的な実施例を参照しながら、本発明についてさらに詳細に説明する。

## 【0019】

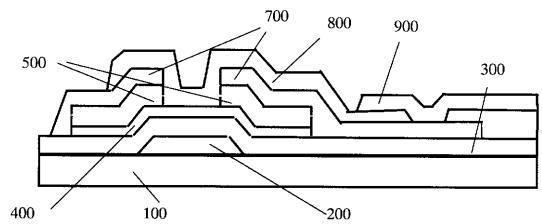

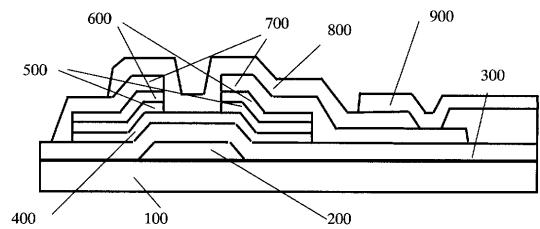

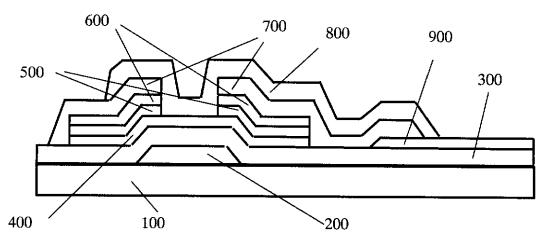

図2は本発明の実施例における薄膜トランジスタの一つの断面図であり、図3は本発明の実施例における薄膜トランジスタの他の断面図である。

## 【0020】

図2に示すように、本発明の実施例における薄膜トランジスタは、基板100と、該基板100上において下から上へ順に形成されたゲート電極200と、ゲート絶縁層300と、半導体層400と、ドーピング半導体層500と、ソース・ドレイン電極700と、パッシベーション層800と、画素電極900とを備え、画素電極900はパッシベーション層800におけるピアホールを介してソース・ドレイン電極700のうちの一つ（例えばドレイン電極）に接続される。半導体層400とドーピング半導体層500は薄膜トランジスタの活性層を形成するために用いられる。ドーピング半導体層500はオーム接觸層とも言え、半導体層とソース・ドレイン電極間の接觸抵抗を減少するためのもので、シリコンマイクロ結晶層で該層を取り替えてよい。図3に示すように、他の実施例において、画素電極900は直接ソース・ドレイン電極700のドレイン電極にラップできる。本発明実施例の薄膜トランジスタにおいて、ソース・ドレイン電極700は活性層のソース・ドレイン領域でそれぞれクロスオーバーし、且つドーピング半導体層500（活性層）とソース・ドレイン電極700との間に例えば8～15nm厚さのSiNx又はSiOxNy層600を設けている。ソース・ドレイン電極の材料は、従来技術においてソース・ドレイン電極の材料として用いられた純Al又はAl/Mo、Mo/Al/Moなどの多層構造を取り替えて、Al合金を採用している。該Al合金は、例えばAlNd、AlTa、AlNi、AlZrとAlCuなどの二元アルミニウム合金であるが、その他の多元アルミニウム合金、例えばAlNdNiであってもよい。

30

## 【0021】

本発明の実施例において、純Al材料の代わりにAl合金が採用されたため、例えばマグネットスパッタ法によってTFTのソース・ドレイン電極を形成し、その頂部にさらに

40

50

Moを堆積しなくてもよい。Al合金層と画素電極(ITO導電薄膜層)の接触が非常によいため、頂部Moの堆積を省略してもよい。以上の技術手段によって、ソース・ドレインエッティングにおける傾斜角などの問題を解決できる。

#### 【0022】

また、本発明の実施例において、底層にもMoを堆積せず、その代わりに厚みが8~15nmのSiNx又はSiOxNy薄膜を採用した。SiNx又はSiOxNy薄膜は絶縁性であるが、その厚みは例えば8~15nmほど薄いため、底層のソース・ドレイン電極が電子のトンネル効果を介して画素電極と接続されて導電を実現できる。以上の技術手段によって、従来技術におけるソース・ドレイン電極を形成する際に多層の金属層を堆積するため、生産能力が下がる問題を解決できる。また、頂部と底部にMo層を堆積しなくて済むため、ソース・ドレイン電極の材料コストを低減できる。且つ、底部のMoの代わりに用いられたSiNx又はSiOxNyはCVD方法によって、ドーピング半導体層が堆積した後、容易に同一反応室内に堆積するため、生産工程を簡単にした。

10

#### 【0023】

また、上記実施例のボトムゲート型薄膜トランジスタは図2と図3に示した構造に限らない。例えば、ソース・ドレイン電極と活性層の順序を逆にしてもよい。即ち、ソース・ドレイン電極をゲート絶縁層上に形成し、半導体層とドーピング半導体層を順次該ソース・ドレイン電極上に形成し、且つドーピング半導体層とソース・ドレイン電極間に厚みが約8~15nmのSiNx又はSiOxNy層を形成できる。ここで、ソース・ドレイン電極の材料はAl合金である。

20

#### 【0024】

本発明の実施例は、トップゲート型薄膜トランジスタであってもよい。この場合、同様に半導体層とドーピング半導体層で活性層を形成し、ドーピング半導体層は中間に設けられ厚みが約8~15nmのSiNx又はSiOxNy層を通してソース・ドレイン電極と接触し、ソース・ドレイン電極の材料はAl合金で構成できる。

#### 【0025】

本発明の実施例は、さらに上記薄膜トランジスタを画素ユニットのスイッチ素子とする薄膜トランジスタ液晶表示装置に係わる。

#### 【0026】

本発明の実施例は、さらに上記薄膜トランジスタの製造方法及びTFT-LCDの製造方法を公開した。以下に、図2と図3に示したボトムゲート型薄膜トランジスタの製造方法を例にして説明する。

30

#### 【0027】

##### [実施例1]

1、マグネットスパッタ法によって基板(例えば、ガラス又はシリコン単結晶ウェハ)上に金属薄膜を堆積し、該金属薄膜のターゲット材としてAl合金を堆積した後、フォトリソグラフィとエッティングによってゲート電極パターンを形成する。

#### 【0028】

2、化学気相堆積法(CVD)によってSiNx又はSiOxNy薄膜層を形成してゲート絶縁層とし、該ゲート絶縁層上において、さらにCVD方法によって、同一工程において半導体層(例えば、a-Si層)とドーピング半導体層(例えば、N+a-Si層)を堆積する。

40

#### 【0029】

3、ステップ2と同様なリアクターにおいて、CVD原理に基づき、厚みが約10nmの薄いSiNx又はSiOxNy層を形成し、フォトリソグラフィとドライエッティングによってチャンネルを形成する。

#### 【0030】

4、マグネットスパッタ法によってステップ3で形成された基板上にAl合金金属層を堆積し、フォトリソグラフィとエッティングによってソース・ドレイン電極を形成し、これで形成された該ソース・ドレイン電極はそれぞれ前記ステップで形成されたSiNx層又は

50

$\text{SiO}_x\text{Ny}$ 層を介して、ドーピング半導体層と良好なオーム接觸を実現する。

【0031】

5、CVD法によってパッシベーション層（例えば、 $\text{SiO}_x\text{Ny}$ ）を堆積し、フォトリソグラフィとエッチングによってチャネル保護層を形成すると共に、保護層上にビアホールをエッチングして形成する。

【0032】

6、マグネットスパッタ法によって透明画素電極薄膜（例えば、ITO）を堆積し、フォトリソグラフィとエッチングによって画素電極パターンを形成すると共に、ビアホールを介して該画素電極をソース・ドレイン電極のうちのドレインに接続する。

これでTFT-LCD画素ユニットの製造を完成し、形成されたその薄膜トランジスタを図2に示している。

【0033】

[実施例2]

以下に、本発明の他の実施例によって、TFT-LCD画素ユニットとその中の薄膜トランジスタの製造方法を説明する。

【0034】

1、マグネットスパッタ方式によって基板（例えば、ガラス又はシリコン単結晶ウェハ）上に金属薄膜を堆積し、該金属薄膜のターゲット材としてAl合金を堆積した後、フォトリソグラフィとエッチングによってゲート電極パターンを形成する。

【0035】

2、化学気相堆積法（CVD）によって $\text{SiN}_x$ 又は $\text{SiO}_x\text{Ny}$ 薄膜層を形成してゲート絶縁層とし、絶縁層上において、さらにCVD法によって、半導体層（例えば、a-Si層）とドーピング半導体層（例えば、N+a-Si層）を同時に堆積する。

【0036】

3、ステップ2と同様なリアクターにおいて、CVD原理に基き、厚みが約10nmの薄い $\text{SiN}_x$ 又は $\text{SiO}_x\text{Ny}$ 層を形成し、フォトリソグラフィとドライエッチングによってシリコンアイランドを形成する。

【0037】

4、マグネットスパッタ法によって画素電極薄膜（例えば、ITO）を堆積し、フォトリソグラフィとエッチングによって画素電極パターンを形成する。

【0038】

5、マグネットスパッタ方式によって上記パターンにおいてAl合金金属層を堆積し、且つフォトリソグラフィとエッチングによってソース・ドレイン電極を形成し、これで形成された該ソース・ドレイン電極はそれぞれ前記ステップ3で形成された $\text{SiN}_x$ 層又は $\text{SiO}_x\text{Ny}$ 層を介して、ドーピング半導体層と良好なオーム接觸を実現すると同時に、画素電極に接続されて良好な接觸を実現する。

【0039】

6、ドーピング半導体層及びその上に形成された $\text{SiN}_x$ 層又は $\text{SiO}_x\text{Ny}$ 層をエッチングしてチャンネルを形成する。

【0040】

7、CVD法によってパッシベーション層（例えば、 $\text{SiO}_x\text{Ny}$ ）を堆積し、且つフォトリソグラフィとエッチングによってチャネル保護層を形成する。

【0041】

これでTFT-LCD画素ユニットの製造を完成し、形成されたその薄膜トランジスタを図3に示している。

【0042】

従来技術に対して、本発明の実施例は常用の多層ソース・ドレイン電極構造を単層に変更して、多層金属によるエッチング問題を解決した。例えば、中間層のAl金属と底部及び頂部のMo金属のエッチング速度が異なって、ソース・ドレイン電極が断線する問題などを解決した。また、従来技術によれば、二種類の金属を3層構造に堆積するため、堆積

10

20

30

40

50

時間が長く、効率が低い問題があった。この問題に対して、本発明はただ1種類の金属を堆積してソース・ドレイン電極を形成することで、生産能力を高めた。且つ、本発明はただ一層の金属を堆積するため、現在のマグネットスパッタ(sputter)設備のチャンバー(chamber)数量を減少して、設備及びそのメンテナンスのコストを節約する。また、本発明は頂部と底部において値段が高いMoの堆積を省略したため、材料コストを低減できる。さらに、本発明はAlの低抵抗の特性を保持できる。

#### 【0043】

以上、最良な実施例を参照しながら本発明について詳細な説明を行ったが、これは本発明の技術案を明らかにするものであって、これらに制限されるのではない。当業者は実際の需要に応じて他の材料と設備によっても同様に本発明を実現できる。従って、本発明の精神と範囲を逸脱しない限り、本願は種々の補正と取替えが可能である。

10

#### 【図面の簡単な説明】

#### 【0044】

【図1】従来技術によるボトムゲート型TFT構造の断面図である。

【図2】本発明実施例における薄膜トランジスタの一つの断面図である。

【図3】本発明実施例における薄膜トランジスタの他の一つの断面図である。

#### 【符号の説明】

#### 【0045】

|     |               |

|-----|---------------|

| 100 | 基板            |

| 200 | ゲート電極         |

| 300 | ゲート絶縁層        |

| 400 | 半導体層          |

| 500 | ドーピング半導体層     |

| 600 | SiNx又はSiOxNy層 |

| 700 | ソース・ドレイン電極    |

| 800 | バッシベーション層     |

| 900 | 画素電極          |

20

【図1】

【図2】

【図3】

## フロントページの続き

(51) Int.CI. F I テーマコード(参考)

H 01 L 21/768 (2006.01) H 01 L 21/90 A

(72) 発明者 林 承武

中華人民共和国北京経済技術開発區西環中路 8 號

(72) 発明者 梁 珂

中華人民共和国北京経済技術開発區西環中路 8 號

F ターム(参考) 4M104 AA09 BB01 BB02 CC01 DD06 DD18 DD55

5F033 HH38 JJ38 KK09 PP15 QQ08 QQ09 QQ37 RR06 RR08 SS11

VV15

5F110 AA16 AA26 BB01 CC03 CC07 DD02 DD05 EE03 EE44 FF02

FF03 FF04 FF29 GG02 GG15 GG44 HK01 HK06 HK09 HK15

HK16 HK17 HK22 HK33 HK34 NN02 NN22 NN35 NN72