(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

**特開2015-99146

(P2015-99146A)**

(43) 公開日 平成27年5月28日(2015.5.28)

(51) Int.Cl.

**G01R 31/28 (2006.01)**

**H01L 21/822 (2006.01)**

**H01L 27/04 (2006.01)**

F 1

G01R 31/28

H01L 27/04

V

T

テーマコード(参考)

2G132

5FO38

審査請求 有 請求項の数 19 O L 外国語出願 (全 16 頁)

(21) 出願番号 特願2014-228018 (P2014-228018)

(22) 出願日 平成26年11月10日 (2014.11.10)

(31) 優先権主張番号 14/083,624

(32) 優先日 平成25年11月19日 (2013.11.19)

(33) 優先権主張国 米国(US)

(71) 出願人 501209070

インフィネオン テクノロジーズ アーベ

イン

INFINEON TECHNOLOGIES AG

ドイツ連邦共和国 85579 ノイビー

ベルク アム カンペオン 1-12

(74) 代理人 100109726

弁理士 園田 吉隆

(74) 代理人 100101199

弁理士 小林 義教

(72) 発明者 リー, チェン ソン

シンガポール共和国 シンガポール 54

2306, アンチャーヴェール リンク

, ブロック 306ビー, 09-69

最終頁に続く

(54) 【発明の名称】遅延故障構造テストのための網羅率向上およびパワーアウェアクロックシステム

## (57) 【要約】

【課題】 遅延故障構造テストのための網羅率向上およびパワーアウェアクロックシステムを提供する。

【解決手段】 遅延故障構造テストに対するテスト網羅率を向上させるため、スキャン回路のクロックシステムに適用される方法およびデバイスが提供される。一態様によれば、1つまたは複数のクロックゲーティングセルを含むスキャンテストのスキャン回路のクロックシステムに適用される方法は、スキャンテストのいかなる段階でも、各クロックゲーティングセルでクロック信号の制御可能な波形を出力するステップと、キャプチャサイクルの間に、各クロックゲーティングセルで部分的イネーブルクロック信号を除去するステップとを含む。

【選択図】 なし

**【特許請求の範囲】****【請求項 1】**

1つまたは複数のクロックゲーティングセルを含むスキャンテストのスキャン回路のクロックシステムに適用される方法であって、

(a) 前記スキャンテストのいかなる段階でも、各クロックゲーティングセルでクロック信号の制御可能な波形を出力するステップと、

(b) キャプチャサイクルの間に、各クロックゲーティングセルで部分的イネーブルクロック信号を除去するステップと

を含む、方法。

**【請求項 2】**

前記部分的イネーブルクロック信号は、前記テストのテスト網羅率を向上させるために除去される、請求項 1 に記載の方法。

**【請求項 3】**

前記スキャンテストは、遅延故障構造テストである、請求項 1 に記載の方法。

**【請求項 4】**

機能上の(非テスト)動作の間の前記1つまたは複数のクロックゲーティングセルは、クロック信号に完全にトランスペアレントである、請求項 1 に記載の方法。

**【請求項 5】**

前記遅延故障テストの間の電力消費量を低減するために電力消費量を制御するステップをさらに含む、請求項 3 に記載の方法。

**【請求項 6】**

前記電力消費量を制御するステップは、スキャンフリップフロップを使用するステップを含む、請求項 5 に記載の方法。

**【請求項 7】**

前記スキャン回路は、部分的に制御可能なまたは/および制御不可能な論理を備える、請求項 1 に記載の方法。

**【請求項 8】**

前記クロックシステムは、いくつかのクロックドメインを備える、請求項 1 に記載の方法。

**【請求項 9】**

自動テストパターン生成(ATPG)ツールによって事前に定義された形式で前記クロック信号を生成するステップをさらに含む、請求項 1 に記載の方法。

**【請求項 10】**

遅延故障スキャン構造テストのキャプチャサイクルの間に、クロック信号の制御可能な波形を出力し、

前記テストの前記キャプチャサイクルの間に、部分的イネーブルクロック信号を除去する

ように構成される、クロックゲーティングセル。

**【請求項 11】**

前記遅延故障スキャンテストの間の電力消費量を低減するように構成された電力消費量制御をさらに備える、請求項 10 に記載のクロックゲーティングセル。

**【請求項 12】**

前記電力消費量制御は、スキャンフリップフロップを備える、請求項 11 に記載のクロックゲーティングセル。

**【請求項 13】**

出力クロック信号を入力クロック信号から導出するように構成された論理をさらに備えるクロックゲーティングセルであって、前記出力クロック信号は、前記入力クロック信号とは異なる、請求項 10 に記載のクロックゲーティングセル。

**【請求項 14】**

マルチプレクサをさらに備える、請求項 10 に記載のクロックゲーティングセル。

10

20

30

40

50

**【請求項 15】**

機能上の（非テスト）動作の間、クロック信号に完全にトランスペアレントになるよう 10

にさらに構成された、請求項10に記載のクロックゲーティングセル。

**【請求項 16】**

自動テストパターン生成（ATPG）ツールによって事前に定義された形式で前記クロック信号を生成するようにさらに構成された、請求項10に記載のクロックゲーティングセル。

**【請求項 17】**

1つまたは複数のクロックゲーティングセルを備えるスキャン回路であって、スキャンテストのために使用されるように構成され、

(a) 前記クロックゲーティングセルの各々は、個別に制御可能であるように構成され、

(b) 前記クロックゲーティングセルの各々は、遅延故障スキャン構造テストのキャプチャサイクルの間にクロック信号の制御可能な波形を出力するように構成され、

(c) 前記クロックゲーティングセルの各々は、前記テストの前記キャプチャサイクルの間に部分的イネーブルクロック信号を除去するように構成される、

スキャン回路。

**【請求項 18】**

前記遅延故障スキャンテストの間の電力消費量を低減するように構成された電力消費量制御をさらに備える、請求項17に記載のスキャン回路。

**【請求項 19】**

前記電力消費量制御は、スキャンフリップフロップを備える、請求項18に記載のスキャン回路。

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示は、例えば遅延故障構造テストの間に使用される、スキャン回路、クロックゲーティングセル、および、スキャン回路のクロックシステムに適用される方法に関する。より具体的には、いくつかの実施形態は、部分的に制御可能なまたは制御不可能な論理がスキャン回路に存在する場合でも、クロック信号を制御可能な状態に維持することに関する。さらなる実施形態は、テストフェーズの間の電力消費量を低減することに関する。

**【背景技術】****【0002】**

ここ10年間にわたる集積回路（IC；チップ、マイクロチップ、電子回路など）の開発における著しい進歩は、サブミクロンまで、ましてや、ナノメートルレジームまでさえも、設計構造の関連スケールを縮小させた。以下、「集積回路」は、例えば、論理ゲート、フリップフロップ、マルチプレクサおよび他の回路を含むデジタル電子回路のセットを含むデジタル集積回路に関連する。そのような小型の構造は、一方では、総合設計の複雑性の増加と併せて、他方では、半導体企業にとって、彼らのチップにおける欠陥を低減するという課題を非常に困難なものにする。集積回路の開発コストを削減するため、企業は、彼らの製品をスキャンテストの対象とする。構造が小さくなるほど、高いテスト網羅率を得るのがより難しくなり、高いテスト網羅率は、より高い品質の製品を含意する。サブミクロンおよびナノメートル構造は、機能上の欠陥（例えば、デバイスの相互接続における短絡または開放）に悩まされるばかりでなく、特に、タイミング関連の遅延欠陥（高インピーダンス短絡、インライン抵抗、信号間のクロストークなど）にも悩まされる。前者は、静的テスト（例えば、縮退故障モデルおよびIDDQ故障モデル）で効果的に検出することができるが、後者は、実動作速度テスト（at-speed test）を通じてのみアクセスすることができる。利用可能な自動テストパターン生成（ATPG）ツールは、遅延欠陥に対処することができる。通常、実動作速度故障モデル（例えば、頻繁に使用される実動作速度テストのいくつかを挙げると、ラウンチオフシフト（launch-

offset-shif t ) またはスキュードロード ( skewed-load ) 方法を使用する遷移遅延故障モデル、ランチオフキャプチャ ( launch-off-capture ) またはブロードサイド ( broadside ) 方法を使用する遷移遅延故障モデル、バス遅延故障モデル ) は、2つの部分からなる。第1の部分の間、検証すべき論理遷移に着手し、第2の部分では、1アプリケーション期間後に応答がキャプチャされ (以下、「キャプチャサイクル」と呼ぶ)、アプリケーション期間は、例えば、クロック周期と同一である。

#### 【0003】

前述のテストモデルのいずれも、集積回路のテスト回路が制御不可能なまたは部分的に制御可能な論理を含む時点で、効果がなくなり、結果的に、低いテスト網羅率をもたらすようになる。多くのチップ製造業者は、彼らのチップ設計に、例えば、いわゆる知的財産 (IP) モジュールを組み込み、その挙動は、テスト動作の間ではなく、機能上の動作の間でのみよく知られている。そのような制御不可能なまたは部分的に制御可能な論理は、テスト動作の間の制御不可能なまたは部分的に制御可能な出力信号の原因となり得、アクセス可能なテストベクトルの数への強い制約を押し付け、低いテスト網羅率をもたらす。実動作速度遅延故障構造テストに関連する以前の技術分野では、そのような問題には未だ対処していない。

10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

本開示の目的は、とりわけ、制御不可能なまたは部分的に制御可能な論理によって遅延故障テストのクロックシステム内で発生する問題の回避によるテスト網羅率の向上を対象とするものであり得る。

20

#### 【課題を解決するための手段】

#### 【0005】

1つまたは複数のクロックゲーティングセルを含むスキャンテストのスキャン回路のクロックシステムに適用される方法が提供される。方法は、スキャンテストのいかなる段階でも、各クロックゲーティングセルでクロック信号の制御可能な波形を出力するステップと、キャプチャサイクルの間に、各クロックゲーティングセルで部分的イネーブルクロック信号を除去するステップとを含む。

30

#### 【0006】

さらに、クロックゲーティングセルが提供される。クロックゲーティングセルは、遅延故障スキャン構造テストのキャプチャサイクルの間に、クロック信号の制御可能な波形を出力し、テストのキャプチャサイクルの間に、部分的イネーブルクロック信号を除去するように適合される。

#### 【0007】

添付の図面は、本開示のさらなる理解を提供するために含まれ、この明細書に組み込まれ、この明細書の一部を構成する。図面は、本開示の実施形態を示し、記述と共に、本開示の原理の説明に役立つ。本開示の他の実施形態および本開示の意図する利点の多くは、以下の発明を実施するための形態を参照することによってより良く理解されるようになるため、容易に理解されよう。

40

#### 【図面の簡単な説明】

#### 【0008】

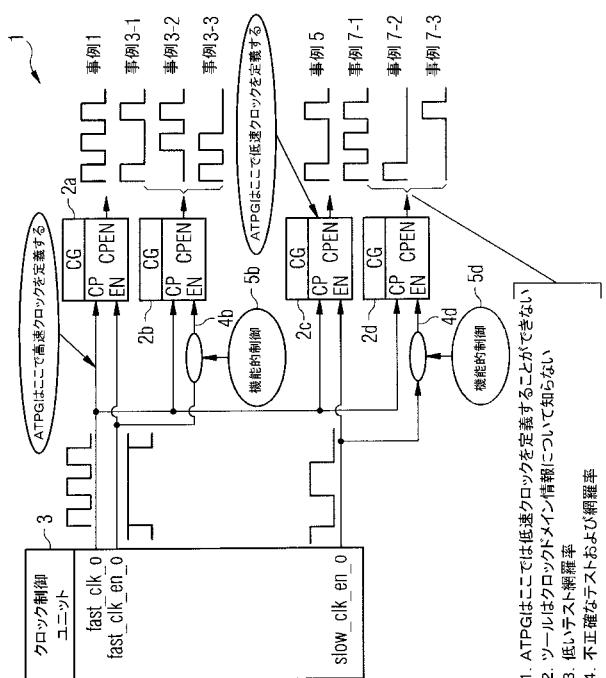

【図1】キャプチャサイクルの間のクロック信号の可能な波形を含む2つのクロックドメインを有するシステムオンチップ (SOC) クロックシステムについて描写する。

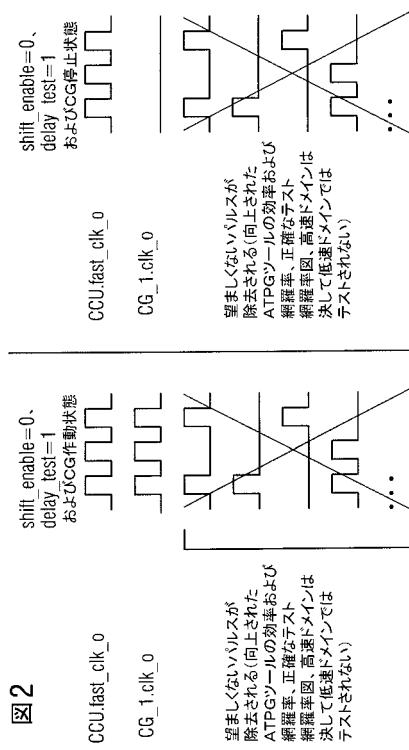

【図2】高速 / マスタクロックドメインに対する、遅延故障テストの間のキャプチャサイクルでの所望の波形について描写する。

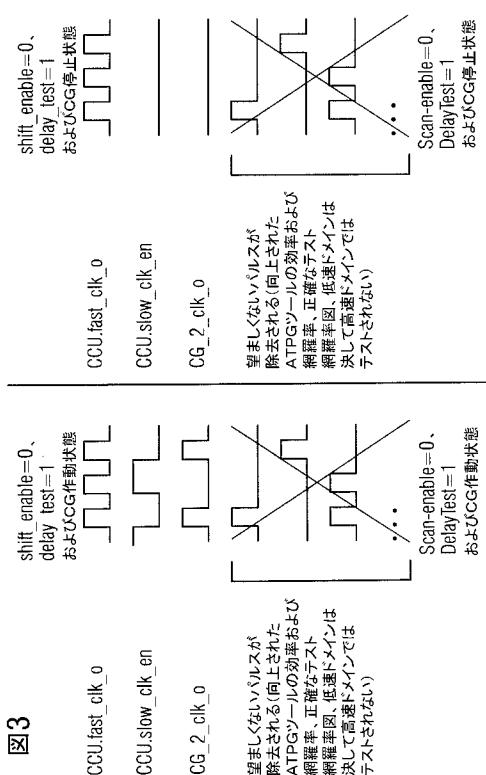

【図3】低速 / 分割クロックドメインに対する、遅延故障テストの間のキャプチャサイクルでの所望の波形について描写する。

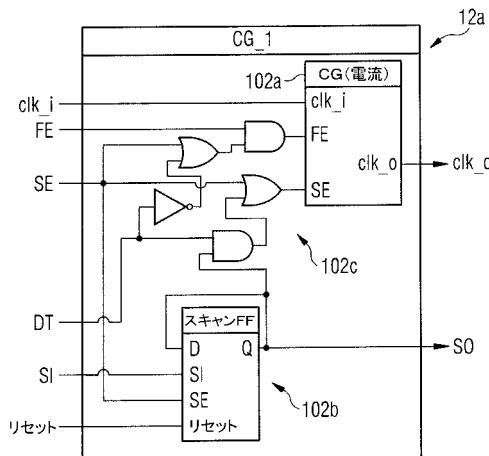

【図4a】更新されたクロックゲーティングセルに対する第1の実装形態例について描写

50

する。

【図4 b】クロックゲーティングセルの1つの可能な実現形態について描写する。

【図5】更新されたクロックゲーティングセルに対する第2の実装形態例について描写する。

【図6】更新されたクロックゲーティングセルを含むIP /トップレベルの実装形態例について描写する。

【発明を実施するための形態】

【0009】

スキャン回路における実動作速度遅延故障構造テストの低い網羅率は周知の問題である。多くの集積回路は、例えば、いわゆる知的財産（IP）モジュール、非スキャンフリップフロップ、内蔵メモリおよび「ブラックボックス」のような制御不可能なまたは部分的に制御可能な論理を含み、その挙動は、個々の機能上の実装形態に依存する。それらの制御不可能なまたは部分的に制御可能な論理は、機能上の（非テスト）動作の間に周知の挙動を呈するが、スキャンテストの間のそれらの挙動は、一般に、前もってアクセスすることはできない。これは、機能上の動作の間にアクセス可能なものより大きなパラメータスペースを網羅する、スキャンテストの間の大多数のテストベクトルが原因である。それは、テスト網羅率を劇的に低減する、スキャン回路における何らかの論理のこの制御不可能なまたは部分的に制御可能な挙動である。

【0010】

実動作速度遅延故障構造テスト（完全なリストを提供せずに、2つの最も重要なものを挙げると、遷移遅延故障テスト、パス遅延故障テスト）の間、テストのキャプチャサイクルの間に、例えば、部分的に制御可能なまたは制御不可能な論理回路に接続され得る各クロックゲーティングセルの出力で、歪みのないクロック信号を維持することが重要である。部分的に制御可能なまたは制御不可能な論理の出力での部分的に制御可能なまたは制御不可能な信号は、クロックゲーティングセルの入力でのクロック信号の部分的イネーブル信号を引き起こす可能性がある。クロックゲーティングセルの出力で恐らく結果として得られる歪みクロック信号は、以降、「部分的イネーブルクロック信号」で示される（以下では、用語「信号」が使用され、網羅的ではなく、周波数、パルスなどや、当業者によく知られている他の表現を含み得る）。制御可能なクロック信号を維持しなければ、自動テストパターン生成（ATPG）ツールは、クロックゲーティングセルの出力でのクロック信号を定義することはできない。これが、不正確なテストおよび結果的に低いテスト網羅率をもたらす理由の1つである。他方では、スキャンテストの間、テストされている経路に関係なく、多くのフリップフロップが切り替わる可能性がある。これは、スキャンテストの間の電力消費量の上昇を引き起こす。問題については図1を要約され、この図は、2つのクロックドメインを含むシステムオンチップ（SOC）1に関連する。*f ast\_c1\_k\_o*は、クロックゲーティングセル2a、2b、2c、2dのクロックパス（CP）入力で終端する高速またはマスタクロックを示す。クロック信号は、クロック制御ユニット3によって提供される。*f ast\_c1\_k\_en\_o*および*s low\_c1\_k\_en\_o*はそれぞれ、入力ENでクロックゲーティングセル2a、2b、2c、2dを制御する高速および低速クロックイネーブル（EN）信号である。クロックゲーティングセル（CG）は、網羅的ではなく、1つまたはいくつかのフリップフロップ、1つまたはいくつかのマルチプレクサ、1つまたはいくつかの論理ゲートから構成され得る。クロックゲーティングセルの出力（CPEN）の可能な形態は、事例1、3、5および7として示されている。スキャンテストの実動作速度キャプチャサイクルの間は、事例1および事例5の波形のみが望ましい。事例3-1は、部分的イネーブルクロック信号の一例を表示し、高速クロックが低速クロックに切り替わり、高速ドメインに現れた故障が低速ドメインでテストされる（不正確なテスト網羅率をもたらす）事例である。事例3-2および3-3では、部分的イネーブルクロック信号のより多くの例が示されている。クロックパルスが欠けており、それにより、ATPGツールの非効率性をもたらすが、その理由は、後者がクロック信号を定義できないためであり、したがって、低いテスト網羅率をもたらす。事例7

10

20

30

40

50

- 1 の部分的イネーブルクロック信号は、低速クロックが高速クロックに切り替わることに相当し、すなわち、低速ドメインに現れた故障が高速ドメインでテストされる（不正確なテスト網羅率をもたらす）。事例 7 - 2 および 7 - 3 は、クロックパルスが欠けた部分的イネーブルクロック信号を表示し、事例 3 - 2 および 3 - 3 に類似して、ATPG ツールの非効率性をもたらし、したがって、低いテスト網羅率をもたらす。望ましくない波形 3 - 1、3 - 2、3 - 3 および 7 - 1、7 - 2、7 - 3 は、機能的制御 5 b および 5 d からそれぞれ生じ、それは、機能上の（非テスト）動作の間でのみ制御可能であるが、スキヤンテストの間は制御不可能であり得る。

#### 【0011】

図 1 はスキヤンテストの間のすべての可能なクロック信号関連問題の限られた簡易化された選択のみを示すことが含意される。しかし、当業者であれば、同じ課題に関連するはるかに多くの関与問題にそれらを一般化することができよう。

10

#### 【0012】

本開示の実施形態による方法は、個々のクロックゲーティングセル CG の出力 C P E N での望ましくない波形（例えば、それらのいくつかは、図 1 で描写される事例 3 - 1、3 - 2、3 - 3、7 - 1、7 - 2、7 - 3 の部分的イネーブルクロック信号）の除去を対象とし、ATPG ツールによる 1 つまたは複数の制御可能なクロック信号の定義を可能にする。望ましくない波形は、例えば、制御不可能なまたは部分的に制御可能な論理回路 5 b、5 d が原因で、クロックゲーティングセルの 1 つの入力（EN）での部分的イネーブル信号 4 b、4 d によって生じる可能性がある。この方法は、クロックゲーティングセルの各々の電力消費量制御によって修正することができる。

20

#### 【0013】

クロックゲーティングセルの設計に対する本方法の影響については、高速 / マスタまたは低速 / 分割クロックレジームでの動作に対してそれぞれ、図 2 および図 3 に示されている。出力信号 CG\_1.c1k\_0 および CG\_2.c1k\_0 は、図 4 および図 5 でそれぞれ参照される実施形態に対して例示的に示されているが、明らかにそれらの実施形態に限定されることはなく、一般的な例として機能する。両方の図では、CCU.fast\_c1k\_0 は、アプリケーションクロックを示し、これに限定されないが、システムクロック信号であり得る。

30

#### 【0014】

図 2 の左のパネルは、オン状態のクロックゲーティングセル（CG 作動状態）の場合の、例えば、高速 / マスタクロックレジームに対する遅延故障テストのキャプチャサイクルの間の、クロックゲーティングセルのうちの 1 つの出力での信号 CG\_1.c1k\_0 の波形を、除去された波形（例えば、望まない部分的イネーブルクロック信号）のいくつかと共に示す。この場合、クロックゲーティングセルは、クロックゲーティングセルの入力でのクロック信号に完全にトランスペアレントである。図 2 の右のパネルでは、クロックゲーティングセルは停止状態（CG 停止状態）であり、結果的に、OFF 信号（CG\_1.c1k\_0）がクロックゲーティングセルの出力に現れる。

#### 【0015】

図 3 は、オン状態のクロックゲーティングセル（CG 作動状態、左のパネル）の場合および停止状態のクロックゲーティングセル（CG 停止状態、右のパネル）の場合の、例えば、低速 / 分割クロックレジームに対する遅延故障テストのキャプチャサイクルの間の、この開示のクロックゲーティングセルのうちの別の出力での信号 CG\_2.c1k\_0 の波形を、除去された波形（例えば、望まない部分的イネーブルクロック信号）のいくつかと共に表示する。CCU.slow\_c1k\_en は、所望の比率に従って CCU.slow\_c1k\_en を分割する低速クロックイネーブル信号である（図 3 では、CCU.slow\_c1k\_en と CCU.slow\_c1k\_en との間の比率は、例示として、2 と等しくなるように選択される）。図 2 と同様に、クロックゲーティングセルが作動状態に設定されている場合（左のパネル）は、クロックゲーティングセルは、クロックゲーティングセルの入力でのクロック信号に完全にトランスペアレントである。右のパネル

40

50

では、クロックゲーティングセルは停止状態（CG停止状態）であり、結果的に、OFF信号（CG\_2.clk\_o）がクロックゲーティングセルの出力に現れる。

#### 【0016】

以下の2つの実施形態は、上記の所望の挙動に通じる2つの例示的なデジタル回路について説明する。以下で説明されるすべての信号は、スキャンテストにおける特定の使用に限定されず、それらは記述においてしばしば言及されることを理解すべきである。当業者であれば、テスト回路以外の回路で提示される実施形態を適合させて適用することができよう。

#### 【0017】

図4aに示される更新されたクロックゲーティングセル12aは、クロックゲーティングセル102a（CG（電流））、スキャンDフリップフロップ102b（スキャンFF）および組合せ論理102cから構成される。クロックゲーティングセルCG（電流）の最も簡単な実現形態は、ANDゲートによって提供される。ここで考慮される場合、1つのイネーブル信号は、クロック信号clk\_iを制御する。図4aの特定の例では、クロックゲーティングセル102a（CG（電流））は、入力として、第1のクロック信号（clk\_i）、機能イネーブル信号（FE）およびシフトイネーブル信号（SE）を使用する。クロックゲーティングセル102a（CG（電流））の出力信号は、clk\_oで示される。例えば、信号clk\_iは、これらに限定されないが、機能上の（非テスト）動作の間の高速／マスタクロック信号、スキャンテストのキャプチャサイクルの間の高速／マスタクロック信号、または、スキャンテストの初期化サイクルの間のスキャンシフトクロック信号（シフトイン、シフトアウト）であり得る。

10

20

30

#### 【0018】

以下では、以前に説明されたクロックゲーティングセル102a（CG（電流））は、「従来のクロックゲーティングセルの一例」で示される。それは、例えば、以下の真理値表によって特徴付けられる（表1では、xは、0または1を示す）。

#### 【0019】

#### 【表1】

| FE | SE | clk_o |

|----|----|-------|

| 0  | 0  | OFF   |

| 1  | x  | clk_i |

| x  | 1  | clk_i |

表1：従来のクロックゲーティングセルの真理値表

#### 【0020】

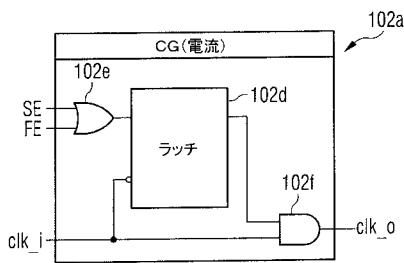

従来のクロックゲーティングセルの1つの特定の実現形態は、制限することなく、図4bに示されている。それは、ORゲート102e、ラッチ102dおよびANDゲート102fによって組み立てられている。この従来のクロックゲーティングセルは、テスト設計に一般的に使用されるが、その理由は、シフトイネーブル信号（SE）の方が、機能イネーブル信号（FE）と比較して、ATPGツールによる制御がはるかに簡単であるためである。具体的には、SE入力の包含により、FE信号とは無関係に、スキャンテスト信号を有効にすることが可能になる。図4bに示される従来のクロックゲーティングセルの特定の実施形態のラッチは、以下の利益のために使用される。クロック信号clk\_i = 0である限り、出力クロック信号（clk\_o）はOFFであり、すなわち、clk\_o = 0である。クロック信号clk\_iが0から1に変化すると、ラッチは、そのD入力で

40

50

状態を保持し、クロックゲーティングセルでのタイミング問題を減少させる。`clk_i` = 1 である限り、出力クロック信号 `clk_o` は、`FE` または `SE` の変化による影響を受けない。

#### 【0021】

本開示では、特定の従来のクロックゲーティングセルは例示として考慮されているが、従来のクロックゲーティングセル `CG` (電流) をテスト設計で頻繁に使用される他の任意のタイプのクロックゲーティングセルに置き換えるかまたは適合させることは当業者にとって造作もないことであるはずである。この意味で、図 4 b のラッチを、例えば、フリップフロップに置き換えることも、従来のクロックゲーティングセルの別の実現形態では、`OR` ゲートをラッチの後方に配置することもできる。従来のクロックゲーティングセルの提示された実現形態(図 4 b)の多くの小規模な変更形態は、本開示で使用することができ、当業者にはよく知られている。

10

#### 【0022】

図 4 a の更新されたクロックゲーティングセルのスキャン D フリップフロップ 102b (スキャン FF) は、スキャンシフト動作の間にシフトイン (SI) 信号によって制御される。これは、特に、一方では、より優れたおよびより簡単な ATPG の可制御性ひいてはより高いテスト網羅率をもたらし、他方では、スキャンテストの間の電力消費量の低減をもたらす。この特定の実施形態では、スキャンフリップフロップの Q 出力は、スキャンシフト出力 (SO) 信号を出力する。

20

#### 【0023】

所定の例の組合せ論理 102c は、1 つのインバータ、2 つの `OR` ゲートおよび 2 つの `AND` ゲートを含み、図 4 a に示されるように接続される。

30

#### 【0024】

本開示の第 1 の例示的な更新されたクロックゲーティングセル 12a (`CG_1`) は、6 つの入力、すなわち、クロック信号 `clk_i`、機能イネーブル信号 `FE`、シフトイネーブル信号 `SE`、遅延テストイネーブル信号 `DT`、スキャンシフト入力信号 `SI`、および、スキャンモードの間にスキャンフリップフロップ (スキャン FF) をリセットするリセット信号 (`reset`) を所有する。更新されたクロックゲーティングセル `CG_1` は、クロック信号 `clk_o` およびスキャンシフト出力 (SO) 信号を出力する。図 4 a の論理を考慮すると、`CG_1` の真理値表は、表 2 で得られるような結果となる。

30

#### 【0025】

#### 【表 2】

| FE | DT | SE | スキャン FF | <code>clk_o</code> | 注                                      |

|----|----|----|---------|--------------------|----------------------------------------|

| 0  | 0  | 0  | x       | OFF                | 低速テストのための機能上の動作/<br>キャプチャサイクル (例えば、縮退) |

| 1  | 0  | 0  | x       | <code>clk_i</code> | 低速テストのための機能上の動作/<br>キャプチャサイクル (例えば、縮退) |

| x  | x  | 1  | x       | <code>clk_i</code> | テスト動作(スキャンシフト)                         |

| x  | 1  | 0  | 0       | OFF                | テスト動作(実動作速度キャプチャ)                      |

| x  | 1  | 0  | 1       | <code>clk_i</code> | テスト動作(実動作速度キャプチャ)                      |

40

表 2 : 更新されたクロックゲーティングセル `CG_1` の真理値表

#### 【0026】

50

表2では、 $x$ は、0または1を示す。その上、表2を考慮すると、 $DT = 0$ 、 $SE = 0$ （例えば、機能上の動作における）によって特徴付けられたフェーズでは、出力クロック信号 $c1k_o$ は、機能イネーブル信号 $FE$ によって完全に制御されることが分かる。 $SE = 1$ （例えば、スキャンテストのシフトフェーズ）によって特徴付けられたフェーズのいずれかの間は、更新されたクロックゲーティングセル $CG_1$ は、クロック入力信号 $c1k_i$ （これに限定されないが、スキャンシフトクロック入力信号であり得る）に完全にトランスペアレントである。 $DT = 1$ 、 $SE = 0$ （例えば、実動作速度キャプチャサイクル）によって特徴付けられたフェーズの間は、出力クロック信号 $c1k_o$ は、例えばスキャンテストのシフトインサイクルにおける信号 $SI$ によって設定されている、スキャンフリップフロップ（スキャンFF）によって制御される。この最終フェーズでは、 $c1k_i$ は、例えば、高速／マスタクロック信号によって得ることができる。スキャンFF = 1の場合は、更新されたクロックゲーティングセル $CG_1$ は、入力クロック信号 $c1k_i$ に完全にトランスペアレントである、すなわち、スキャンFF = 1に関しては、 $c1k_o = c1k_i$ であるが、スキャンFF = 0の場合は常に、 $CG_1$ はオフ（OFF）に切り替わり、例えばスキャンテストのキャプチャサイクルの間の機能イネーブル信号とは無関係である。説明される更新されたクロックゲーティングセル $12a$ （ $CG_1$ ）を用いることで、望ましくない部分的イネーブルクロック信号は、 $CG_1$ の出力 $c1k_o$ で除去される。

10

20

30

40

## 【0027】

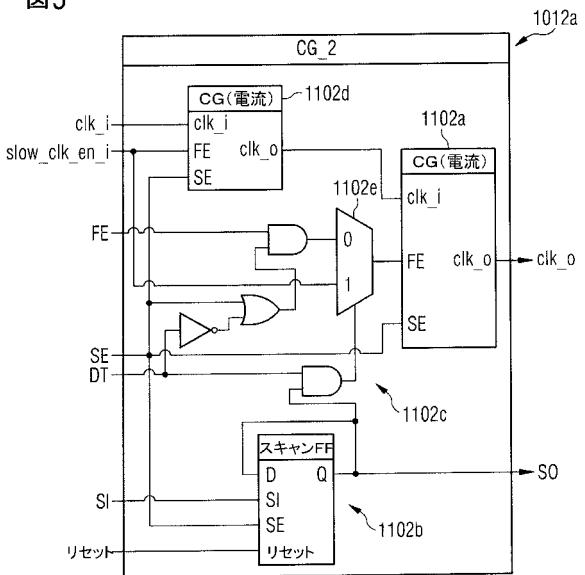

図5に示される第2の例示的な実施形態は、図4aの更新されたクロックゲーティングセル $CG_1$ の文脈で導入された入力信号 $c1k_i$ 、 $FE$ 、 $SE$ 、 $DT$ 、 $SI$ 、リセットに加えて、入力信号 $s1ow_c1k_en_i$ （これに限定されないが、デジタル回路の低速クロックイネーブル信号であり得る）を含む。更新されたクロックゲーティングセル $1012a$ （ $CG_2$ ）は、更新されたクロックゲーティングセル $12a$ （ $CG_1$ ）の文脈で説明されるような、第1および第2の従来のクロックゲーティングセル $1102d$ 、 $1102a$ （ $CG$ （電流）、例えば、図4bに示されるような）、マルチブレクサ $1102e$ 、スキャンDフリップフロップ $1102b$ （スキャンFF）、ならびに、組合せ論理 $1102c$ から構成される。システムマルチブレクサ／クロックゲーティングセルは、「マルチブレクサタイプのクロックゲーティングセル」で一般的に示される。更新されたクロックゲーティングセル $CG_2$ は、出力クロック信号 $c1k_o$ およびスキャンシフト出力信号 $SO$ を出力する。

## 【0028】

更新されたクロックゲーティングセル $CG_2$ は、例えば、 $s1ow_c1k_en_i$ 信号（例えば、図3の $CCU.s1ow_c1k_en$ ）の使用によって、第2のクロック信号が高速／マスタクロック信号（例えば、図3の $CCU.fast_c1k_o$ ）から導出される場合に使用することができる。 $c1k_i$ 入力が $c1k_i$ 信号と接続され、 $FE$ 入力が $s1ow_c1k_en_i$ 信号と接続される、図5の第1の従来のクロックゲーティングセル $1102d$ （ $CG$ （電流））は、所望のクロック信号を生成する。マルチブレクサ $1102e$ の出力は、第2の従来のクロックゲーティングセル $1102a$ （ $CG$ （電流））の入力 $FE$ に接続される。マルチブレクサの入力信号（0または1）に応じて、マルチブレクサの出力信号は、マルチブレクサの「0」入力での信号またはマルチブレクサの「1」入力での信号のそれぞれによって得られる。スキャンフリップフロップ $1102b$ （スキャンFF）は、図4aの更新されたクロックゲーティングセル $CG_1$ の文脈で説明されるようなものである。

## 【0029】

図5の組合せ論理を考慮すると、2つのANDゲート、1つのORゲートおよび1つのインバータを備える $CG_2$ の真理値表は、表3の通り得られる。

## 【0030】

【表3】

| FE | DT | SE | slow_clk_en | スキャン FF | clk_o | 注                                     |

|----|----|----|-------------|---------|-------|---------------------------------------|

| 0  | 0  | 0  | x           | x       | OFF   | 低速テストのための機能上の動作/<br>キャプチャサイクル(例えば、縮退) |

| 1  | 0  | 0  | x           | x       | clk_i | 低速テストのための機能上の動作/<br>キャプチャサイクル(例えば、縮退) |

| x  | x  | 1  | x           | x       | clk_i | テスト動作(スキャンシフト)                        |

| x  | 1  | 0  | 0           | x       | OFF   | テスト動作(実動作速度キャプチャ)                     |

| x  | 1  | 0  | 1           | 0       | OFF   | テスト動作(実動作速度キャプチャ)                     |

| x  | 1  | 0  | 1           | 1       | clk_i | テスト動作(実動作速度キャプチャ)                     |

表3：更新されたクロックゲーティングセルCG\_2の真理値表

10

20

30

40

50

## 【0031】

表2と同様に、表3のxは、0または1を示す。DT = 0、SE = 0(例えば、機能上の動作における)によって特徴付けられたフェーズでは、出力クロック信号clk\_oは、機能イネーブル信号FEによって完全に制御される。SE = 1(例えば、スキャンテストのシフトフェーズ)によって特徴付けられたフェーズのいずれかの間は、更新されたクロックゲーティングセルCG\_2は、クロック入力信号clk\_i(これに限定されないが、スキャンシフトクロック入力信号であり得る)に完全にトランスペアレントである。DT = 1、SE = 0(例えば、実動作速度キャプチャサイクル)によって特徴付けられたフェーズの間は、出力クロック信号clk\_oは、例えばスキャンテストのシフトインサイクルにおける信号SIによって設定されている、slow\_clk\_en信号とスキャンフリップフロップ(スキャンFF)の両方によって制御される。slow\_clk\_en信号が存在しない、すなわち、slow\_clk\_en = 0である限り、更新されたクロックゲーティングセルCG\_2はOFFであり、スキャンフリップフロップ(スキャンFF)の状態とは無関係である。slow\_clk\_en = 1の場合、更新されたクロックゲーティングセルCG\_2は、スキャンFFが設定されている、すなわち、スキャンFF = 1の場合は、クロック信号clk\_iに完全にトランスペアレントであるが、スキャンFF = 0の場合は、CG\_2はOFFである。更新されたクロックゲーティングセルCG\_2の一応用では、CG\_2は、ATPGツールによる更新されたクロックゲーティングセルCG\_2の出力での低速/分割クロック信号の定義を可能にする。

## 【0032】

同じまたは他の応用では、更新されたクロックゲーティングセルCG\_1またはCG\_2の各々は、SI信号に応じて、スキャンモードごとに一度、個別にオンにすることも、オフに切り替えることもできる。この個別の制御を用いることで、スキャンテストの間の電力消費量の低減が可能である。

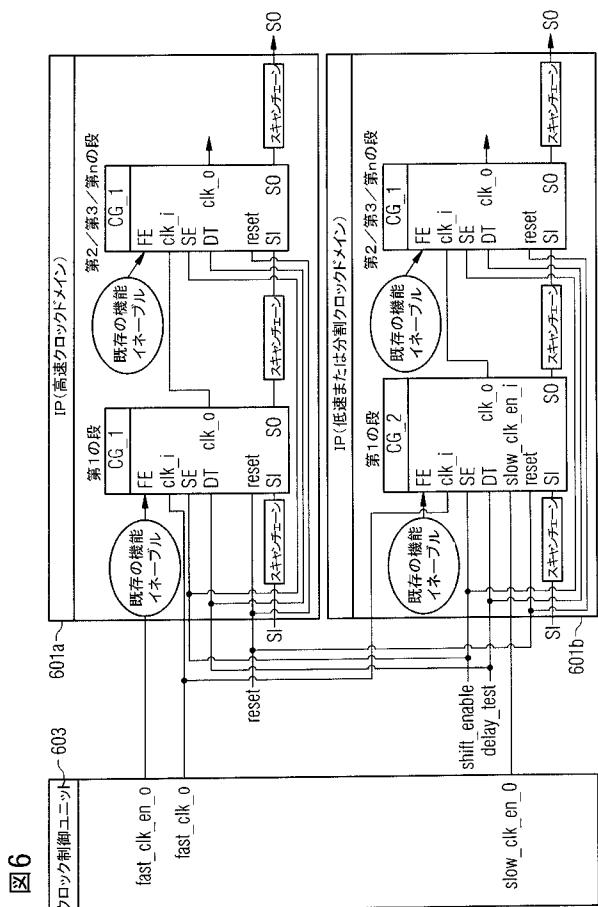

## 【0033】

図6は、上記で提供される説明による、更新されたクロックゲーティングセルCG\_1またはCG\_2を含むトップレベルの実装形態の一例を示す。具体的に示すため、しかし適用性を制約することなく、第1(例えば、高速)のクロックドメインで動作する第1の知的財産(IP)モジュール601aおよび第2(例えば、低速または分割)のクロックドメインで動作する第2のIPモジュール601bが示されている。クロック信号のいずれも、クロック制御ユニット603によって生成される。高速クロック信号は、fast

c l k \_ o で与えられ、第 1 の I P モジュール 6 0 1 a および第 2 の I P モジュール 6 0 1 b に対するクロックイネーブル信号は、f a s t \_ c l k \_ e n \_ o および s l o w \_ c l k \_ e n \_ o のそれぞれで示される。

#### 【 0 0 3 4 】

第 1 の I P モジュール 6 0 1 a は、例示として、回路のいかなる段でも、従来のクロックゲーティングセルのいくつかまたはすべてを置き換えた、タイプ C G \_ 1 の更新されたクロックゲーティングセルを含む。従来のクロックゲーティングセルの入力に既に存在する入力信号 c l k \_ i、F E および S E に加えて、第 1 の I P モジュールにおける更新されたクロックゲーティングセルの各々は、遅延テストイネーブル信号 (d e l a y \_ t e s t)、スキャンシフト入力信号 (S I) およびリセット信号 (r e s e t) を受信する。d e l a y \_ t e s t = 1 は、遅延故障テストの実動作速度キャプチャサイクルを定義する。スキャンシフト入力信号は、特に、例えば、内部スキャンフリップフロップを制御することによって、更新されたクロックゲーティングセルをオンにするかまたはオフに切り替えるために使用される。最終的に、リセット信号 (r e s e t) は、異なるスキャンモードの間に既存のシステムをリセットするために使用される。

10

#### 【 0 0 3 5 】

第 2 の I P モジュール 6 0 1 b は、具体的に示すため、しかし制限することなく、一次段のクロックゲーティングセルとして、上記で詳述されるようなタイプ C G \_ 1 の 1 つの更新されたクロックゲーティングセル、および、第 2 およびそれ以上の段のクロックゲーティングセルとして、上記で説明されるようなタイプ C G \_ 2 の更新されたクロックゲーティングセルから構成される。タイプ C G \_ 1 の更新されたクロックゲーティングセルの入力に存在し、既に論じられた c l k \_ i、F E、S E、D T、S I およびリセット入力信号に加えて、第 2 の I P モジュールにおけるタイプ C G \_ 2 の更新されたクロックゲーティングセルの各々は、入力 s l o w \_ c l k \_ e n \_ i で低速クロックイネーブル信号（例えば、s l o w \_ c l k \_ e n \_ o）を受信する。上記で説明されるように、s l o w \_ c l k \_ e n \_ i の入力は、d e l a y \_ t e s t = 1 の場合の更新されたクロックゲーティングセルの挙動にのみ影響を及ぼす。この場合、s l o w \_ c l k \_ e n \_ i の入力は、更新されたクロックゲーティングセルが ON であるという条件の下、出力クロック信号 c l k \_ o の波形を決定する。クロック信号の所望の波形が生成された時点で、スキャンチェーン内の高次段（第 2 およびそれ以上）の更新されたクロックゲーティングセルがタイプ C G \_ 1 のものであるということは、必須ではなく、十分である。

20

#### 【 0 0 3 6 】

表 2 および表 3 で与えられる更新されたクロックゲーティングセル C G \_ 1 および C G \_ 2 のそれぞれの挙動のため、機能上の動作およびテスト動作の両方の各フェーズでの出力クロック信号 c l k \_ o は、個々の更新されたクロックゲーティングセルの各々での入力信号による制御が可能である。具体的には、D T = 1（これに限定されないが、実動作速度遅延故障テストのキャプチャサイクルを含む）でのフェーズの間の出力クロック信号 c l k \_ o は、スキャンチェーンの各段での入力クロック信号 (f a s t \_ c l k \_ o) およびクロックイネーブル信号（例えば、f a s t \_ c l k \_ e n \_ o、s l o w \_ c l k \_ e n \_ o）によって完全に制御される。図 6 に示される例示的な実施形態によれば、一次クロックゲーティングセルの出力 c l k \_ o で定義されたフェーズ D T = 1 の間のクロック信号は、ON に設定された高次段（第 2 およびそれ以上）のクロックゲーティングセルでは変化しない。その上、クロック信号の歪み波形（図 1 に例示的に示されるよう、事例 3 - 1、3 - 2、3 - 3、7 - 1、7 - 2、7 - 3 の部分的イネーブルクロック信号）を除去することができる。更新されたクロックゲーティングセルの各々での明確に定義された出力クロック信号のため、A T P G ツールは、入力 F E での機能イネーブル信号に関わらず、キャプチャフェーズの間のこれらのクロックゲーティングセルの各々の出力でのクロック信号を定義することができるようになる。本開示による更新されたクロックゲーティングセルの使用のこの最後の含意は、結果的に、テスト網羅率の増加をもたらす。その上、更新されたクロックゲーティングセルの応用により、特に、各 I P モジュール

30

40

50

に対する制御可能なクロック信号の定義が可能になるため、テスト網羅率をさらに増加することができるが、その理由は、クロックコードメインスイッチングを除去することも、抑制することもできるためである。具体的には、高速ドメインに発生した故障が低速ドメインでテストされること（テスト回避を招く；クロック信号の歪み波形は、図1の事例3-1に示される）およびその逆（過度のテストを招く；クロック信号の歪み波形は、図1の事例5-1に示される）を除去することができる。

#### 【0037】

更新されたクロックゲーティングセルの使用の別の利益は、スキャンフリップフロップによるそれらの個々の可制御性により生じ得る。スキャンテストの間の電力消費量は、減少させた数の更新されたクロックゲーティングセルのみをオンに切り替えることによって低減することができる。スキャンテストの間の電力消費量を低減するため、ATPGツールには、閾値として、スキャンテストの間にオンにするべき最大数の更新されたクロックゲーティングセルを与えることができる。

10

#### 【0038】

本開示のさらなる利益は、例えば、回路、回路要素、システム要素、モジュールなどにおけるその高速のおよび簡単な実装形態であり得る。従来のクロックゲーティングセルの各々は、更新されたクロックゲーティングセルのうちの1つ（例えば、CG\_1、CG\_2）に置き換えることができる。従来のクロックゲーティングセルを更新されたクロックゲーティングセルに置き換えることは、例えば、自動設計変更指示（ECO）スクリプトによって達成することができる。

20

#### 【0039】

本開示はある実施形態を参照して説明してきたが、当業者であれば、本開示の範囲から逸脱することなく、様々な変更を行うことができ、均等物を代用できることが理解されよう。それに加えて、特定の状況または材料を本開示の教示に適合させるため、その範囲から逸脱することなく、多くの修正を行うことができる。したがって、本開示は開示される特定の実施形態に限定されないが、本開示は添付の特許請求の範囲内に収まるすべての実施形態を含むことが意図される。

#### 【符号の説明】

#### 【0040】

- 1 システムオンチップ（SOC）

- 2 a、2 b、2 c、2 d クロックゲーティングセル

- 3 クロック制御ユニット

- 4 b、4 d 部分的イネーブル信号

- 5 b、5 d 機能的制御

- 1 2 a クロックゲーティングセル

- 1 0 2 a クロックゲーティングセル

- 1 0 2 b スキャンDフリップフロップ

- 1 0 2 c 組合せ論理

- 1 0 2 d ラッチ

- 1 0 2 e ORゲート

- 1 0 2 f ANDゲート

- 6 0 1 a IP（高速クロックドメイン）

- 6 0 1 b IP（低速または分割クロックドメイン）

- 6 0 3 クロック制御ユニット

- 1 0 1 2 a クロックゲーティングセル

- 1 1 0 2 a、1 1 0 2 d クロックゲーティングセル

- 1 1 0 2 b スキャンDフリップフロップ

- 1 1 0 2 c 組合せ論理

- 1 1 0 2 e マルチプレクサ

30

40

【 図 1 】

1

【 図 2 】

2

【 図 3 】

【 図 4 a 】

図4A

【図4b】

図4B

【図5】

図5

【図6】

---

フロントページの続き

F ターム(参考) 2G132 AA01 AB01 AB07 AC03 AC14 AD06 AG08 AK11 AK14 AK27

AL00 AL11

5F038 CD06 CD09 DF08 DT06 EZ20

【外國語明細書】

2015099146000001.pdf

2015099146000002.pdf

2015099146000003.pdf

2015099146000004.pdf