(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3854839号

(P3854839)

(45) 発行日 平成18年12月6日(2006.12.6)

(24) 登録日 平成18年9月15日(2006.9.15)

(51) Int.C1.

F 1

H01L 27/105 (2006.01)

H01L 27/10 447

H01L 21/8246 (2006.01)

H01L 43/08 Z

H01L 43/08 (2006.01)

請求項の数 1 (全 20 頁)

(21) 出願番号

特願2001-306540 (P2001-306540)

(22) 出願日

平成13年10月2日 (2001.10.2)

(65) 公開番号

特開2003-110162 (P2003-110162A)

(43) 公開日

平成15年4月11日 (2003.4.11)

審査請求日

平成16年6月18日 (2004.6.18)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090538

弁理士 西山 恵三

(74) 代理人 100096965

弁理士 内尾 裕一

(72) 発明者 小金井 昭雄

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 松田 成正

最終頁に続く

(54) 【発明の名称】磁気抵抗素子を用いた不揮発固体メモリ

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、垂直磁化膜である、第1磁性層と第2磁性層と、前記磁性層間に非磁性層が配された磁気抵抗素子と、を有し、前記磁気抵抗素子の周囲が絶縁体で覆われているM R A Mにおいて、

前記第1磁性層の保磁力は前記第2の磁性層の保磁力よりも大きく、前記第1磁性層の底面積S 1と、前記第2磁性層の底面積S 2とが、S 1 > S 2であり、

前記磁気抵抗素子の断面形状がテーパー角を有した台形形状であり、該テーパー角が30度から60度の範囲であり、

前記第1磁性層が前記基板に配された電界効果トランジスタと電気的に接続され、前記第2磁性層がビット線と電気的に接続されていることを特徴とするM R A M。 10

## 【発明の詳細な説明】

## 【0 0 0 1】

## 【発明の属する技術分野】

磁気抵抗効果素子を用いた不揮発固体メモリ素子、およびメモリとそれらの記録再生方法に関するものである。

## 【0 0 0 2】

## 【従来の技術】

昨今では、携帯電話、P D Aを中心としてモバイル端末の開発が盛んになっている。モバイル機器においては格納用メモリとして、大容量の不揮発性高速アクセスメモリの必要性

が叫ばれている。近年、非磁性層を強磁性層の間にはさみ込んだ磁気抵抗膜で巨大磁気抵抗効果 (Giant Magnet Resistance) が発見され、この現象を利用した磁気センサー、磁気メモリ素子 (以下MRAM) が注目を集めている。強磁性層 / 非磁性絶縁層 / 強磁性層と積層された薄膜の膜垂直方向に電流を流したときの電気抵抗の変化は、強磁性層のスピニ分極率の差により、非磁性絶縁層をトンネルバリア層としたトンネル電流の変化として検知され、トンネル磁気抵抗効果 (TMR効果) と呼ばれている。TMR素子では高い磁気抵抗比が得られることから、MRAMや磁気ヘッドの実用化に向け開発が加速している。

## 【0003】

MRAMでは2つの強磁性層とその間に挟んだ薄い非磁性層が情報を記憶する基本構造となる。非磁性層をはさみ込んだ強磁性層の磁化方向がそろっている場合と反平行な場合とで抵抗値が異なる現象を利用して、“0”、“1”の状態を記憶する。

10

## 【0004】

情報の読み出しへは、抵抗の絶対値で判断する絶対検出方式と、書き込みの際より弱い磁場を印加して、保磁力が低い方の強磁性層だけ磁化反転させて“0”、“1”の状態を読み出す差動検出方式が知られている。

## 【0005】

情報の書き込みは、絶対検出方式では、2つの強磁性層のうち、保磁力が低い一方の磁化方向を外部磁界で変化させることで行う。差動検出方式では2つの強磁性層のうち、保磁力が高い一方の磁化方向を外部磁界で変化させることで行う。磁気抵抗素子の近傍に配置した配線に電流を流し、発生する磁界を利用する方法が知られている。

20

## 【0006】

MRAMは磁気的に記憶されるため放射線耐性に優れ、原理的に不揮発であり高速で書き込み回数の制限がない利点がある。既存の半導体技術を流用する事で高密度記録が容易に行えるので、将来的にはDRAMの置き換えが期待される。

## 【0007】

MRAMに使われる磁性材料を磁化方向で分類すると、膜面に平行な磁化成分を持つ面内磁化膜型と、膜面に垂直な磁化成分を持つ垂直磁化膜型とに分けられる。NiFe, Co等の強磁性体は、磁化方向が膜面に平行な面内磁化膜型であるが、この面内磁化膜では磁性体の微細化が進むと磁極同士が近づいて反磁界が大きくなるため、磁化のカーリング現象が起きるという問題がある。カーリングが発生すると、磁化の方向を判別することが困難になる。そのため、面内磁化膜を用いたMRAMでは形状異方性をつけるため、メモリセルとなる強磁性層を平面的に見て長軸を持つ形状 (長方形など) とする必要がある。長方形の長軸と短軸の比は、少なくとも2倍以上必要だと予想される。従って、カーリング現象防止のために、メモリセルのサイズが制約を受け、集積度向上の阻害要因となる。

30

## 【0008】

一方、強磁性層としてTbFe, TbFeCo, GdFe等の希土類 - 遷移金属からなるフェリ磁性体を用いる場合、これら磁性体の垂直磁気異方性が高いため、膜厚と組成によっては、磁化を膜面に対し垂直方向に持つ垂直磁化膜となる。垂直磁化膜の場合には、磁化の方向は、形状的に最も反磁界が大きい膜面垂直方向を向いており、垂直磁気異方性を示す時点で既に最大の反磁界係数に打ち勝つことになる。つまり、面内磁化膜のようにメモリセルを長方形とする必要がなく、メモリセルの幅と長さを等しくすることができる。さらに、素子を微細化すると、磁化容易軸である膜厚方向と比べ、平面的な面積が小さくなるので、形状異方性の観点では、磁化のカーリングがより起きにくい方向になる。そのため、垂直磁化膜型は、メモリセル部の集積度を向上する上では、面内磁化膜型と比べ有利である。垂直磁化膜を用いた磁気抵抗効果膜としては、特開平11-213650号公報に詳述されている。

40

## 【0009】

このような磁気抵抗効果素子をメモリセルとして用いた磁気メモリセルは、2つの磁性層が薄い非磁性層を挟んで積層されているため、磁気メモリセル内の一方の磁性層から発生

50

する漏洩磁界が他方の磁性層に印加し、外部磁界が無い場合においても磁界が印加された状態になる。

【0010】

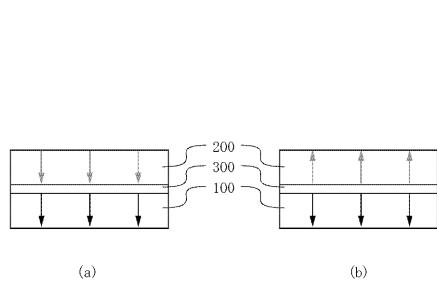

図23には、垂直磁化膜の磁気抵抗素子について、磁化方向の例を示している。低い保磁力をを持つ磁性層200と高い保磁力をを持つ磁性層100とがトンネル絶縁膜300を挟む形で構成されており、(a), (b)どちらも磁性層100は下向きに磁化されており、磁性層200は(a)では下向き、(b)では上向きに磁化しており、抵抗値は(b)が(a)より大きい。

【0011】

この状態は、絶対値検出方式を用いた構成、すなわち磁性層100がピン層で、磁性層200がメモリ層で、(a)が0を記録した状態、(b)が1を記録した状態と考えても良いし、差動検出方式を用いた構成、すなわち磁性層100がメモリ層、磁性層200が検出層で、検出時に外部磁界で(a)から(b)へ磁化反転させたと考えても良い。

【0012】

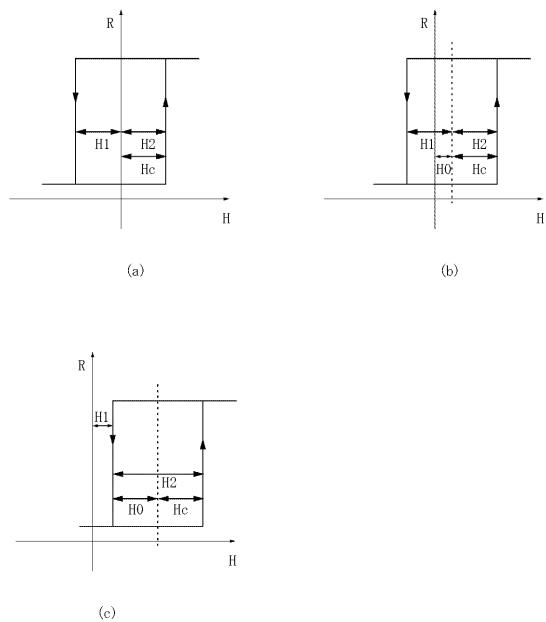

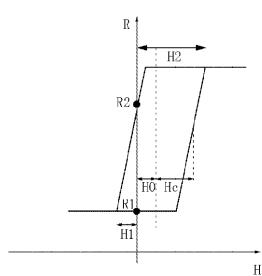

図24(a)には、この素子のMRカーブ(抵抗と印加磁界の関係を示した図)を角型比1で磁性膜からの漏洩磁界がないと仮定して示した。磁性層100は磁化方向を変えないため、磁性層200の磁化方向に対応した抵抗変化が現れている。オフセット磁界がなければ、保磁力Hcと同じ大きさの反転磁界H1もしくはH2を印加するだけで、メモリ層に記録を行うことが出来る、もしくは、検出層の磁化反転を行うことが出来る。

【0013】

しかし実際には、磁性層100からは下向きの磁界が磁性層200に印加されているため、MRカーブは図24(b)に示すようにオフセット磁界H0分シフトする。この場合には、反転磁界は $H2 = Hc + H0$ ,  $H1 = Hc - H0$ となり、図23(b)から図23(a)の状態に書き換えるに必要な磁界はH0分小さくなり、逆に図23(a)から図23(b)に書き換える場合には必要磁界がH0分だけ大きくなる。これは、書き込み線に流す電流値が大きくなることを意味し、消費電流が大きくなるか、書き込み配線の許容電流密度を超える場合には書き込みが出来なくなるといった問題を生じてしまう。また、この場合、メモリセルは、記録された情報に応じて反転磁界が異なるため、マトリクス状に配置されたメモリセルを直交する2本の書き込み線で記録する場合に、例えば、反転磁界H2を要するメモリセルの情報を書き換えるとすると、その隣にある反転磁界H1を要するメモリセルの情報も書き換ってしまうといった、誤記録動作が発生する可能性が高くなる。さらに図24(c)に示したようにオフセット磁界H0が保磁力Hcよりも大きくなると、磁界が0の状態で一つの抵抗値しか取り得なくなるため、絶対検出が出来なくなる。

【0014】

さらに角型比が1でない場合については、図25に示すように、無磁界の状態での抵抗値R2が反平行磁化状態の最大抵抗値Rmaxよりも小さくなる。この場合には、読み出しの抵抗値の差R2 - R1が小さくなつて、検出感度が悪化してしまう。

【0015】

以上は、主に絶対値検出方式を想定して述べたが、差動検出方式を用いた場合でも同様である。

【0016】

また以上のような課題は、従来MRAMに用いられている面内磁化膜では特に顕著である。理由は面内磁化膜を利用したMRAMに用いられるNiFe, Co等の材料の磁化が大きいことと、前述のカーリングの影響を回避するために細長い形状にして形状異方性をつける必要があるためである。垂直磁化膜を利用したMRAMに用いられるTbFeCo, GdFeCo等のフェリ磁性体は組成調整により磁化の大きさを小さく出来るため、本質的にオフセット磁界は小さく設計できる方向にある。しかしながら、記録磁化の保存性や耐熱性、耐食性などの要求事項を満足させる上では完全にオフセットを無くすることは困難である。

【0017】

10

20

30

40

50

## 【発明が解決しようとする課題】

本発明が解決しようとする第1の課題は、このような一方の磁性層からの静磁界により、もう一方の磁性層の反転磁界がオフセットする問題を解決することである。

第2の課題は、反転磁界のオフセットにより記録磁界が増加する問題と誤記録を発生する問題を解決することである。

第3の課題は、第1の課題を達成する上で生じるコストアップを可能な限り低減することである。

第4の課題は、メモリ素子の記録再生動作の安定性を高め、高速に記録再生可能な不揮発固体メモリを実現することである。

## 【0018】

10

本発明は上記課題の少なくとも一つを解決するためのものである。

## 【0019】

## 【課題を解決するための手段】

本発明者は鋭意検討の結果、以下の手段が課題を解決できることを見出した。

## 【0020】

すなわち、基板と、垂直磁化膜である、第1磁性層と第2磁性層と、前記磁性層間に非磁性層が配された磁気抵抗素子と、を有し、前記磁気抵抗素子の周囲が絶縁体で覆われているMRAMにおいて、前記第1磁性層の保磁力は前記第2の磁性層の保磁力よりも大きく、前記第1磁性層の底面積S1と、前記第2磁性層の底面積S2とが、S1 > S2であり、前記磁気抵抗素子の断面形状がテーパー角を有した台形形状であり、該テーパー角度が30度から60度の範囲であり、前記第1磁性層が前記基板に配された電界効果トランジスタと電気的に接続され、前記第2磁性層がビット線と電気的に接続されていることを特徴とする。

20

## 【0027】

## 【発明の実施の形態】

本発明は、垂直磁化膜からの漏洩磁界が膜の周辺端部で強く、中央部では比較的小さいことに着目し、膜の周辺端部を避ける形で積層すれば、一方の磁性層からの漏洩磁界の影響が軽減出来ること、ひいては磁気抵抗素子の反転磁界のオフセットを少なく出来ることを見出して発案したものである。

## 【0028】

30

本発明の実施形態を、図面を用いて説明する。

## 【0029】

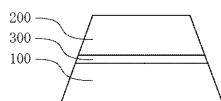

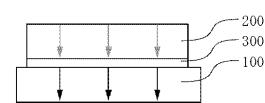

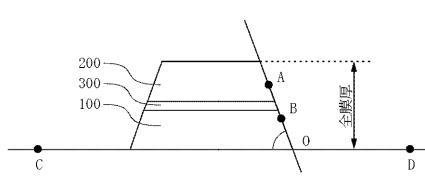

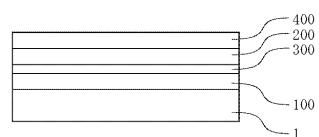

図1に本発明の磁気抵抗素子の断面構造を示す。低い保磁力を有する第2磁性層200と高い保磁力を有する第1磁性層100とがトンネル絶縁膜300を挟む形で構成されており、第1磁性層100が基板に近い側になっている。

## 【0030】

40

本発明の磁気抵抗素子は断面形状が台形となっている。従って、保磁力が大きい第1磁性層100の方が、保磁力が小さい第2磁性層200と比べサイズが大きくなっている。すなわち底面積が保磁力の大きい第1磁性層のほうが大きくなっている。従って、第2磁性層200が第1磁性層100から受ける漏洩磁界の影響は軽微である。このため、第2磁性層200の反転磁界にオフセットが生じないことになる。

## 【0031】

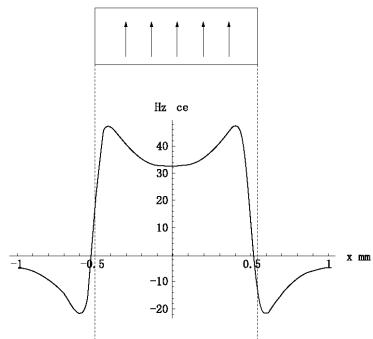

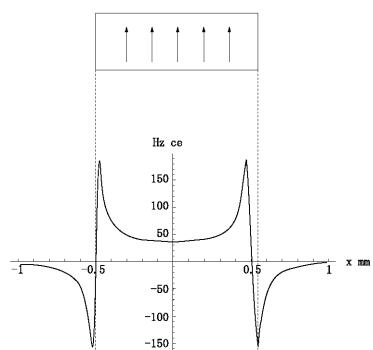

図2は垂直磁化膜からの漏洩磁界の強さを示す模式図である。本発明の基礎検討として計算した。垂直磁化膜はMsが100emu/cc、長さ1μm、幅1μm、厚さ30nmで、膜表面から75nm離れた地点の値を計算した。横軸が面内方向の距離Xで、縦軸が漏洩する垂直磁界の垂直(Z)成分を表している。図2から明らかのように、垂直磁界の強さは膜辺の端部(x = ±0.5μm)で強いのに対し、中央部(x = 0μm)は端部の約65%と非常に小さい。膜面からの距離がより近くなると、この差はより顕著になり、膜表面から2nm離れた地点では端部と比べて約19%程度まで小さくなる。(図3)

## 【0032】

50

磁気抵抗素子の非磁性層の厚さは数 nm のオーダーなので、図 3 のケースに相当する。すなわち、膜辺の周辺端部の強い漏洩磁界を避けることが非常に有効である。

【0033】

従って、図 1 のような構成にすると、第 2 磁性層 200 は第 1 磁性層 100 からの漏洩磁界の強い部分を避けることになるため、第 1 磁性層 100 からの漏洩磁界による第 2 磁性層 200 の反転磁界のオフセットを非常に小さくすることが可能になる。

【0034】

上記の効果は、本質的に磁性層のサイズ差に依存するため、例えば図 4 に示すように、各磁性層を独立してバーニングして磁性層 100 を大きくしてもよいが、しかしながら、非磁性層 300 が非常に薄いことやプロセスが煩雑になることを考えると得策ではない。図 1 のように断面形状を台形とすることで、一度のプロセスで加工が可能になるためにプロセスが煩雑になることなく再現性良く加工することが可能になる。

【0035】

第 1 磁性層 100 からの漏洩磁界を極力さける観点では、第 2 磁性層 200 と第 1 磁性層 100 のサイズ差は大きいことが望ましく、換言すれば台形の底面と側面のなす角度は低斜度であることが望ましい。しかしながら、側壁角度が小さすぎるとメモリセルの実効的な面積が増大するためメモリ集積度を上げる観点では好ましくない。また、加工プロセス上も極端な低斜度を実現することは困難であるから、30 度から 90 度の範囲が好ましく、30 度から 60 度がより望ましい。

【0036】

ここで、側壁角度とは、磁気抵抗素子の全膜厚の 70 % の高さの点 A と、40 % の高さの点 B を結ぶ直線 AB と、基板面 CD との交点 O を頂点とした AOC と便宜上定義する。(図 5) また、局所的な分布を持つことから測定個所の 5 点平均とし、誤差として ± 5 度を見積もることとする。

【0037】

なお、実際の磁気抵抗素子の断面形状は幾何学的な台形にはならず直線と曲線が混在している。また局所的に不規則な形態が含まれる。

【0038】

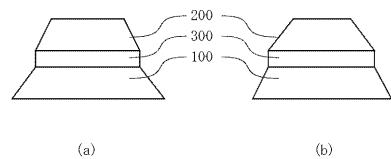

例えばエッティング加工によって台形状とする際、第 1 磁性層と第 2 磁性層のエッティングレートが異なる場合には図 6 (a) や (b) に示すように側壁の傾斜が異なる形状が得られる。このような形状においても、第 1 磁性層の底面積に比べて第 2 磁性層の底面積の方が小さくなっているため、漏洩磁界の大きな領域を避けることが可能となる。

【0039】

また図 1 は磁気抵抗素子のみを表記しているが、実施形態においては周囲を絶縁性の材料で囲まれ、信号の取り出しに必要な電極膜が形成され、保持するための基板が設けられていることは言うまでもない。

【0040】

断面形状を台形とする構造を作成するプロセスは各種微細加工技術で可能である。

【0041】

エッティングによって台形とする場合には、ウェットエッティングのような等方的な加工プロセスが容易である。非平衡プラズマを利用した異方性エッティングを実施する場合においても、あらかじめ作成したレジストマスクに傾斜角を設けておけば、レジスト形状をトレースして膜形状が形成されるため、台形状とすることが可能である。レジストマスクの作成条件やエッティングパラメータの調整は当該業者であれば容易に実行可能である。

【0042】

また、FIB (集束イオンビーム) やイオンミリングのようなイオンビームを利用した加工プロセスの場合には、基板面を傾けてビーム方向を所望の角度に傾斜させることで台形状とすることが可能である。

【0043】

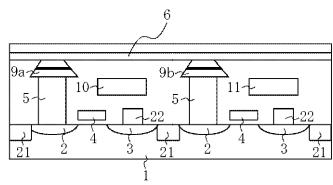

図 7 に磁気抵抗素子を用いたメモリ素子の断面構造を示す。なお、記号の記載のない部分

10

20

30

40

50

は基本的に絶縁体を示す。図7ではメモリ素子2つ分を表示しており、機能が同一でそれぞれに固有な部分についてはa, bと分けて表示している。半導体基板1には、ドレイン領域2、ソース領域3が形成され、さらに絶縁膜を介してゲート電極4が形成され、これらでMOSFET(電界効果型トランジスタ)が構成されている。各電界効果トランジスタ間はLOCOSフィールド酸化膜21によって絶縁されている。

#### 【0044】

電界効果トランジスタのドレイン領域2には、プラグ電極5を介して、ドレイン領域2の直上の位置に、膜面垂直方向に磁化した磁気抵抗素子9が接続され、さらにビット線6に接続されている。ソース電極22には、図示していないが接地配線が設けられている。また、磁気抵抗素子9a(9b)の側部下方には、絶縁体を介して書き込み線10、11が磁気抵抗膜9a(9b)の脇に設けられている。書き込み線10、11、ゲート線4、ソース電極に接続された接地配線は、紙面の垂直方向に伸びている。ビット線6は紙面平行方向に伸びている。

#### 【0045】

基板には、Siウエハ、石英、SOI等平坦性の高い非磁性材料基板が用いられる。SOI基板の作製方法はELTRAN法、SIMOX法など各種方式が適用できる。その際、基板表面のSiの結晶方位は(100)が好ましい。

#### 【0046】

前記基板上に磁気抵抗膜を形成する際、バッファ層は、第1磁性膜より下面の表面自由エネルギーを調整し、より平坦性の高い界面構造を実現する目的で挿入される。Ta, Cu, Cr等の各種金属やSiN, SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>等の絶縁体が用いられるが、基板材料と磁気抵抗膜の材料の選び方によっては、挿入しなくてもよい。バッファ層の膜厚は、2~10nmの範囲が好適である。これは、成膜方法によって2nmより薄いと島状成長による膜質不均一の問題があり、一方、10nmより厚いと生産性低下の問題があるためである。

#### 【0047】

スピントンネル膜の場合、非磁性層としては導体が用いられる。Cu、Ag、Au、Al、Mg等が用いられるが、より好適にはCuが用いられる。非磁性層の膜厚は、1~10nmの範囲が好適である。これは、成膜方法によって1nm未満では、島状成長によるピンホール発生の恐れがあり、両磁性層の相互作用により磁気抵抗が発現しない場合があり、一方、10nmを超える場合には、両磁性層間の間隔が電子の平均自由行程に対し広すぎてスピントンネル膜の効率が減るため磁気抵抗が小さくなるためである。

#### 【0048】

スピントンネル膜の場合、非磁性層としては絶縁体が用いられる。絶縁体としては、Al、Si、Cu、Mg等の酸化物や窒化物が用いられるが、フェルミ準位が他の磁性層に近いAl酸化物がより好適に用いられる。非磁性層の膜厚は、0.5~5nmの範囲が好適である。これは、成膜方法によって0.5nm未満では、島状成長によるピンホール発生の恐れがあり、両磁性層の相互作用により磁気抵抗が発現しない場合があり、一方、5nmを超える場合には、両磁性層間の間隔が電子の平均自由行程に対し広すぎてトンネリング確率が減るため磁気抵抗が小さくなるためである。

#### 【0049】

磁気抵抗膜の構成要素である第1磁性層と第2磁性層の組み合わせは軟磁性材料と硬磁性材料からなり、第1磁性層が硬磁性層、第2磁性層が軟磁性層とする組み合わせとする。差動検出方式においては、軟磁性材料は容易に磁化が反転するため再生層として機能する。硬磁性材料は軟磁性材料と比べ、磁化が反転しにくいためメモリ層として機能する。なお、本発明において、軟磁性材料と硬磁性材料の区別は2つの強磁性層間における保磁力の大小関係で定義されるもので、相対的に保磁力が大きいものを硬磁性材料とする。

#### 【0050】

また、第1磁性層、第2磁性層とは機能を示すもので、各磁性層自体は单一元素から成る単層の場合もあるが各種合金の多層構造でも良い。例えば、硬磁性材料として機能させる

10

20

30

40

50

ために第1（あるいは第2）磁性層として、厚さ5nmのCoと厚さ30nmのFeMnの二層構造としてピン止めしたものを用いることができる。第1磁性層および第2磁性層としては、TbFe、TbFeCo、GdFe等のフェリ磁性体が用いられる。これら二磁性層の組成は、その保磁力が異なるよう適宜調整される。第1磁性層、第2磁性層の膜厚は、2~100nmの範囲に選択するのが好適である。

#### 【0051】

上述したように磁気抵抗膜の積層方向の抵抗は、第1磁性層と第2磁性層の磁化の相対角度によって決まる。両者が平行な場合には抵抗が低くなり、反平行な場合には抵抗は高くなる。アップスピンとダウンスピンの状態密度の差が大きい方が磁気抵抗が大きくなり、再生信号が大きくなるため、第1磁性層と第2磁性層の間の絶縁層の界面近傍にはスピン分極率の高い磁性材料を用いることが望ましい。具体的には、FeやCo等でこれらを主成分とする磁性材料を界面近傍にはさむことで理論上は50%に到達する抵抗変化が得られる。

#### 【0052】

FeとCoを含むこれらの磁性材料は面内磁化膜であるものが多いが、膜厚を数nm程度以下と薄くすることで垂直磁化膜からなる第1磁性層及び第2磁性層と交換結合して垂直磁化膜として機能する。従って、磁化の方向は膜面垂直方向で統一されることになり、信号が小さくなることはない。

#### 【0053】

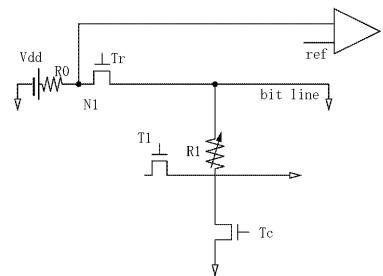

次に記録再生方法を図8を用いて説明する。図8はメモリ素子1つ分に相当する回路図で、実際にはマトリクス上に多数のメモリ素子を基板上に配置して使用する形態となる。

#### 【0054】

磁気抵抗膜R1の一端には電界効果型トランジスタTcが接続されており、もう一端はビット線に接続している。ビット線は一端を接地電位、もう一端を電源電圧Vddに負荷R0と選択トランジスタTrを介して接続されている。選択トランジスタと負荷R0の間のノードN1はセンスアンプSAに接続されており、センスアンプのもう一端はレファレンスとなる参照抵抗（不図示）に接続されている。また、磁気抵抗膜R1の近傍には書き込み線がトランジスタT1を介して接続されている。

#### 【0055】

まずははじめに再生動作について説明する。電界効果型トランジスタTcを選択し、併せてビット線の選択トランジスタTrをオン状態にすると電源電圧Vddが負荷R0を介して磁気抵抗膜R1に流れる。このとき磁気抵抗膜R1の抵抗が高抵抗状態か低抵抗状態かを、ノードN1の電位を参照抵抗と比較することで判定する。参照抵抗の大きさは磁気抵抗膜R1の高低2種類の抵抗値の中間値となるように設定しておく。

#### 【0056】

次に記録動作について説明する。情報を記録する磁気抵抗膜R1を選択するために電界効果型トランジスタTcと選択トランジスタTr、さらには書き込み線の選択トランジスタT1をオン状態とした上でビット線及び書き込み線に電流を流して、それらの合成磁界により磁気抵抗膜の記録層の磁化方向を変化させることで記録を行う。電流方向を逆転させれば磁化方向を反転させることが出来るため、“0”、“1”に対応する信号を任意に記録することが出来る。

#### 【0057】

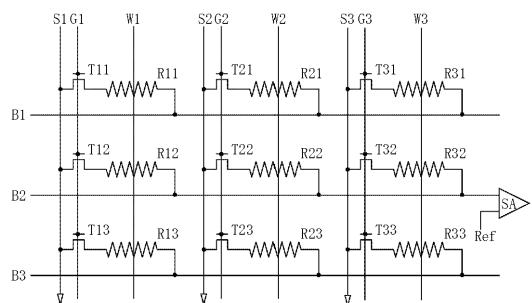

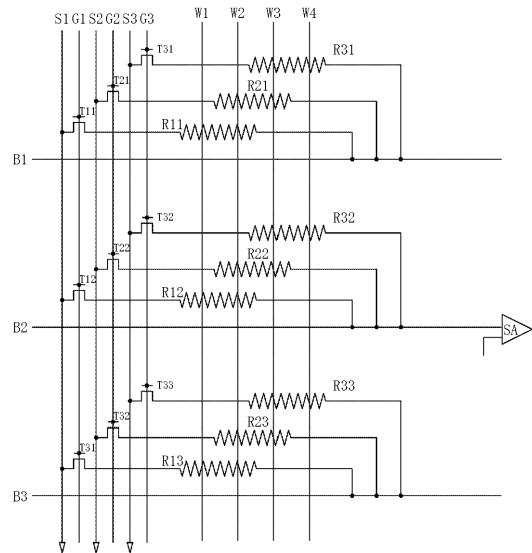

次に本発明の記録再生方法を図9のメモリセルをマトリクス状に配置したメモリアレイ回路を例に説明する。中央にある電界効果トランジスタ（T22）と磁気抵抗膜（R22）から構成されたメモリセルに注目すると、ビット線B2は、書き込み線を兼ね、セル中央の磁気抵抗素子（R22）の一方の端子に結合され、センスアンプ（SA）の一方の端子に接続される。磁気抵抗素子（R22）のもう一方の端子は電界効果型トランジスタ（T22）のドレイン端子に結合され、該電界効果型トランジスタ（T22）のソース端子は接地される。ワード線（G2）は該電界効果型トランジスタ（T22）のゲート端子に接続される。また、書き込み線（W2）は、ビット線と直交するように、磁気抵抗素子R2

10

20

30

40

50

2の近傍に配置される。

【0058】

初めに読み出し動作について説明する。まずビット線B2の左端に電源電圧Vddを印加し、ワード線G2に電圧を印加し、トランジスタT22をオン状態とすることで、磁気抵抗素子R22に定常電流が流れ、ビット線B2の右端のセンスアンプ(SA)の端子に磁気抵抗素子R22の抵抗に応じた電位が生じる。センスアンプSAのもう一方の端子には、磁気抵抗素子R22の2つの抵抗値の中間の電位を入れる。これにより、refとR22のどちらが高抵抗かによってセンスアンプの出力がVddまたは0Vのどちらかが選択されることになる。

【0059】

次に書き込み動作について説明する。磁気抵抗素子R22に情報を書き込む場合には、ビット線B2とW2に電流を流すことによって、配線が交差する場所での磁場が強めあい、R22の磁化が書き換えられる。B2とW2の電流方向を逆転させれば逆方向の磁界を印加することが可能になる。このような操作によって、情報の書き込みを行う。

【0060】

書き込み線は磁気抵抗膜に垂直に磁界がかかるように配置する。書き込み線と磁気抵抗膜の間には絶縁膜が設けられる。絶縁膜を設けるのは、書き込み線と磁気抵抗膜が短絡するのを防ぐためである。これは、再生時に書き込み線の電流が再生信号に混入して信号が劣化するのを防ぐため必要である。

【0061】

書き込み線と磁気抵抗膜の間隔は長い場合は十分な磁界を印加することが出来ず、短い場合は書き込み線と磁気抵抗膜の間で絶縁破壊が生じたり漏洩電流が流れたりするため、少なくとも1nm以上500nm以下で、望ましくは5nm以上100nm以下とするのが良い。

【0062】

ここで記録方法に関して更に詳細に説明する。記録時には書き込み線に電流を流して、そこから発生する磁界を用いて磁気抵抗膜の磁性層の磁化を情報に応じて適宜配向することで行う。書き込み線には紙面垂直方向に電流が流れる。例えば、紙面に向かって電流を流すと書き込み線に対して右回りに磁界が発生する。図7の構成では、書き込み線10に紙面に向かう電流を流し、書き込み線11に紙面から飛び出す方向に電流を流すと磁気抵抗素子9bに対し下向きの垂直磁界が印加される。この書き込み線と同時にビット線6に電流を流す。ビット線電流によって、磁気抵抗膜の面内方向に磁界が印加される。書き込み線とビット線各々からの磁界は複数のメモリセルに印加されるが、これら書き込み線とビット線からの合成磁界は電流を流した導体線の密集点に位置する磁気抵抗膜にしか磁化反転を引き起こすような磁界が印加されない。これにより、所定のメモリセルのみに対し記録が出来る。電流の向きに応じて書き込む情報を調整できることは言うまでもない。

【0063】

次に再生方法に関して詳細に説明する。既に述べた通り、絶対検出法と差動検出法に大別されるがまず、絶対検出法について述べる。絶対検出における磁気抵抗膜の構成は、一方の磁性層を磁化情報が保存されるメモリ層、もう一方の磁性層を常に決められた一定の方向に磁化が配向したピン層とする。例えば"0", "1"のデータをメモリ層の磁化の上向き、下向きに対応させる。記録時は書き込み線に流す電流の発生する磁界によってメモリ層の磁化を情報に合わせて配向させる。再生時は磁性層の磁化反転は行わずに抵抗値の絶対値で情報の検出を行う。このため、再生時に抵抗値の変化を検出するための磁化反転を行う必要がないため高速かつ低消費電力で再生を行うことが出来る。

【0064】

次に差動検出法について説明する。差動検出における磁気抵抗膜の構成は、一方の磁性層を磁化反転が容易な検出層、もう一方の磁性層を磁化情報が保存されるメモリ層とする。記録時は書き込み線に流す電流の発生する磁界によってメモリ層の磁化を情報に合わせて配向させる。再生時は書き込み線により発生する磁界を記録時より弱めて印加して検出層

10

20

30

40

50

のみの磁化方向を反転させる。こうすることで、弱い磁界の印加に伴って小 大、もしくは大 小の抵抗値変化により記録情報を検出することが出来る。この方法では絶対検出ほど高速での読み出しが出来ないが、微分検出法などを用いて小さな信号でも感度良く再生を行うことが出来る。

【0065】

【実施例】

(実施例1)

本発明の効果を確認する目的で、FIB(集束イオンビーム加工装置)を用いて側壁の傾斜角度が異なるハードマスクを作成し、このハードマスクを用いてトンネル磁気抵抗効果(TMR)素子を作成してMRカーブのオフセット磁界の量を調べた。

10

【0066】

素子の作成手順は図10～14に示す通りである。図10～14では、前工程から変化した注目すべき個所を随時、斜線表示している。まず、Siウエハ上にTMR構成の膜とハードマスク材料を成膜する。成膜にはマグネトロンスパッタ装置を用いた。また、トンネル膜はスパッタ膜を形成後に、プラズマ酸化処理を行っている。膜構成は表1に示す。

【0067】

【表1】

| 材料                             | 膜厚 (nm) |

|--------------------------------|---------|

| Al(上部電極)                       | 50      |

| W(ハードマスク)                      | 60      |

| Pt                             | 2       |

| Tb <sub>2</sub> 0Fe            | 30      |

| Al <sub>2</sub> O <sub>3</sub> | 1.5     |

| Gd <sub>2</sub> 2Fe            | 50      |

| Al <sub>8</sub> 0Cu            | 25      |

| SiO <sub>2</sub>               | 1000    |

| Si wafer                       |         |

20

30

40

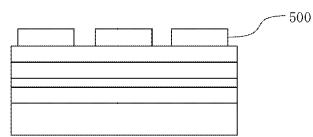

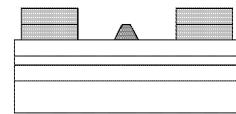

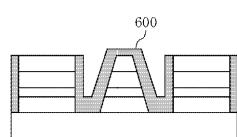

【0068】

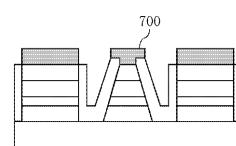

図10は、ベタ膜の成膜が終了した状態を模式的に表したもので、基板1、第1磁性層100、非磁性層300、第2磁性層200、ハードマスク400以外は省略している。次にフォトリソグラフィを使ってレジストパターンをベタ膜上に形成する(図11)。図11において、中央部のレジストマスク500がトンネル接合部を形成するための場所で、両脇は電極パッド用である。次にFIB装置にレジスト付ウエハを投入し、レジストマスクとハードマスク材料を加工する。メモリセルに相当するトンネル接合部を加工する際はサンプルをビームに対して傾けて設置し、所望の側壁角度を持つ形状にする(図12)。次にイオンミリング装置に投入し、素子加工を行う。加工後にレジストマスクがついたままマグネトロンスパッタ装置に再投入し、絶縁膜600を形成する。絶縁膜とレジストマスクを同時にリフトオフする。図13は、絶縁膜600を形成後にリフトオフまで終えた状態を示している。トンネル接合部の絶縁膜をFIBで穴あけ後、新たに上部電極パターンのレジストマスクを形成し、上部電極700を成膜後、リフトオフで磁気抵抗素子を完

50

成させた(図14)。

【0069】

FIBを用いて側壁角度の異なる素子を作成した理由は、他の条件が揃う形で角度のみ異なる素子を作成するのが容易であるためである。また、ハードマスク400はFIBで使用するGaイオンビームの磁性層に対する注入ダメージを防止する役割も果たしている。

【0070】

完成した素子は着磁後にMR測定装置を用いて膜面垂直方向の磁界を印加しながら四端子測定で評価を行った。作成した素子サイズは1μm角で接合部の側壁形状はハードマスクにおいて30度から15度刻みに90度まで作成した。ウエハ間のばらつきを考慮し、同一ウエハ上に同じ角度の素子を複数個作成した。側壁角度の特定にはAFMを用いた。

10

【0071】

作成した素子はいずれも角型比1のMRカーブを示しMRが約25%、規格化抵抗値が0.5M $\mu$ m<sup>2</sup>であった。

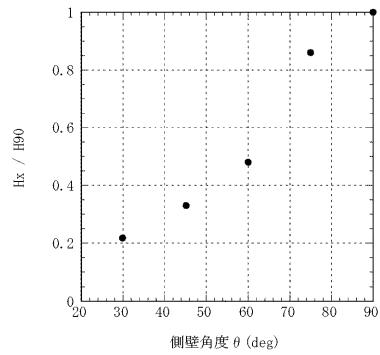

【0072】

図15は磁気抵抗素子の側壁角度とMRカーブのオフセット磁界の関係を示す測定結果である。オフセット磁界とは、図25(b)におけるH0に相当する。縦軸Hx/H90は側壁が90度の時のオフセット磁界の大きさで規格化した無次元量である。図15から側壁角度が低斜度なほど、オフセット磁界が少なくなることがわかった。すなわち、本発明の効果により、磁気抵抗素子において一方の磁性層からの静磁界の影響を低減できることが明らかになった。

20

【0073】

(実施例2)

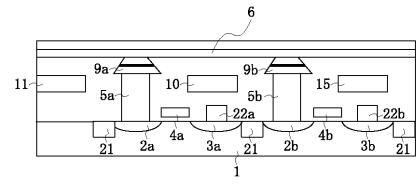

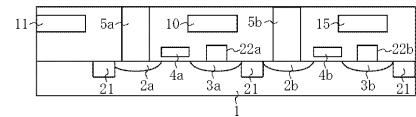

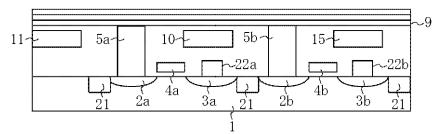

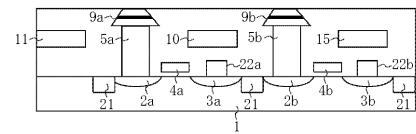

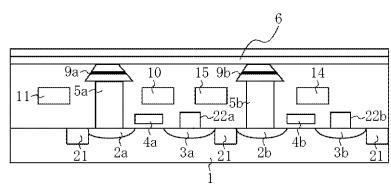

図16は本実施例の断面構造を示す。隣接するメモリセルと書き込み線を共用化している。なお、記号の記載のない部分は基本的に絶縁体を示す。図ではメモリ素子2つ分を表示しており、機能が同一でそれぞれに固有な部分についてはa, bと分けて表示している。半導体基板1には、ドレイン領域2、ソース領域3が形成され、さらに絶縁膜を介してゲート電極4が形成され、これらでMOSFET(電界効果型トランジスタ)が構成されている。各電界効果トランジスタ間はLOCOSフィールド酸化膜21によって絶縁されている。

30

【0074】

電界効果トランジスタのドレイン領域2には、プラグ電極5を介して、ドレイン領域2の直上の位置に、膜面垂直方向に磁化した磁気抵抗素子9が接続され、さらにビット線6に接続されている。ソース電極22には、図示していないが接地配線が設けられている。また、磁気抵抗素子9a(9b)の側部下方には、絶縁体を介して書き込み線10, 11(10, 15)が磁気抵抗素子9a(9b)の両脇に設けられている。書き込み線10, 11, 15、ゲート線4、ソース電極に接続された接地配線は、紙面の垂直方向に伸びている。ビット線6は紙面平行方向に伸びている。

【0075】

図16に示す実施例では、書き込み線10が、左側の磁気抵抗素子9aと右側の磁気抵抗素子9bの両者に対して使える構造となっている。従って、磁気抵抗素子9aに対し情報を記録する場合には書き込み線10, 11を使用し、磁気抵抗素子9bに対し情報を記録する場合には書き込み線10, 15を使用する。書き込み線をそれぞれ独立に2本づつ設ける場合と比べ、書き込み線本数が減るため、集積度が向上可能である。

40

【0076】

図17は図16のメモリセルをマトリクス状に配置したメモリアレイ回路を示している。中央にある電界効果トランジスタ(T22)と磁気抵抗膜(R22)から構成されたメモリセルに注目すると、ビット線B2は、書き込み線を兼ね、セル中央の磁気抵抗素子(R22)の一方の端子に結合され、センスアンプ(SA)の一方の端子に接続される。磁気抵抗素子(R22)のもう一方の端子は電界効果型トランジスタ(T22)のドレイン端子に結合され、該電界効果型トランジスタ(T22)のソース端子は接地される。ワード

50

線 (G 2) は該電界効果型トランジスタ (T 2 2) のゲート端子に接続される。また、書き込み線 (W 2, W 3) は、ビット線と直交するように、磁気抵抗素子 R 2 2 の近傍に配置される。

【0077】

2本の書き込み線 W 2, W 3 は磁気抵抗素子 R 2 1, R 2 2, R 2 3 に対して作用する。このうち、書き込み線 W 2 は書き込み線 W 1 と共に磁気抵抗素子 R 1 1, R 1 2, R 1 3 に対して作用する。書き込み線 W 3 は書き込み線 W 4 と共に磁気抵抗素子 R 3 1, R 3 2, R 3 3 に対して作用する。

【0078】

初めに読み出し動作について説明する。まずビット線 B 2 の左端に電源電圧 V d d を印加し、ワード線 G 2 に電圧を印加し、トランジスタ T 2 2 をオン状態とすることで、磁気抵抗素子 R 2 2 に定常電流が流れ、ビット線 B 2 の右端のセンスアンプ (S A) の端子に磁気抵抗素子 R 2 2 の抵抗に応じた電位が生じる。センスアンプ S A のもう一方の端子には、磁気抵抗素子 R 2 2 の2つの抵抗値の中間の電位を入れる。これにより、ref と R 2 2 のどちらが高抵抗かによってセンスアンプの出力が V d d または 0 V のどちらかが選択されることになる。

10

【0079】

次に書き込み動作について説明する。磁気抵抗素子 R 2 2 に情報を書き込む場合には、ビット線 B 2 と W 2, W 3 に電流を流すことによって、配線が交差する場所での磁場が強めあい、R 2 2 の磁化が書き換えられる。B 2 と W 2, W 3 の電流方向を逆転させれば逆方向の磁界を印加することが可能になる。このような操作によって、情報の書き込みを行う。

20

【0080】

図 18 ~ 20 は図 16 に示す本実施例のメモリを作成するプロセス工程図である。

【0081】

まず始めに図 18 に示す MOSFET を半導体プロセスを用いて作成する。半導体基板 1 には、ドレイン領域 2、ソース領域 3 が形成され、さらに絶縁膜を介してゲート電極 4 が形成され、これらで MOSFET (電界効果型トランジスタ) が構成されている。各電界効果トランジスタ間は LOCOS フィールド酸化膜 2 1 によって絶縁されている。

30

【0082】

電界効果トランジスタのドレイン領域 2 には、プラグ電極 5 が形成され、また、その側部下方には、絶縁体を介して書き込み線 1 0, 1 1, 1 5 がプラグ電極 5 a (5 b) の両脇に設けられている。

【0083】

次にマグネットロンスパッタを用いて磁気抵抗膜 9 を成膜する (図 19)。途中、非磁性層である Al<sub>2</sub>O<sub>3</sub> はプラズマ酸化を行って調質する。

【0084】

さらに、プラグ電極と接続するメモリセルとなる領域を規定する加工を行い、周囲を絶縁層で電気的に隔離する (図 20)。磁気抵抗素子の加工にあたっては使用するレジストの形状をプロセス的に低斜度のテーパーが形成できるように調整した。側壁斜度はおよそ 45 度である。加工は、従来通りイオンミリングを用いている。磁気抵抗素子 9 a, 9 b と接続するように紙面平行方向にビット線 6 を形成し、絶縁層で埋め込む (図 16) とプロセス完了である。

40

【0085】

本実施例の構成とすることで、書き込み線の電流密度を大幅に下げながら、一方で高集積化を実現することが出来た。また磁気抵抗素子の形状は断面構造が台形となることから、反転磁界のオフセットが生じず消費電力を抑制することができた。さらには、従来プロセスにほとんど手を加えずに反転磁界のオフセットを抑制出来たことから、非常に低コストであることが明らかになった。

【0086】

50

**(実施例 3 )**

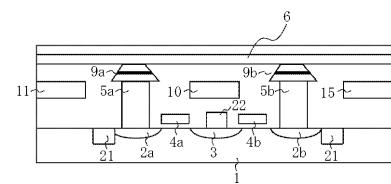

図 2 1 は本発明の実施例を示すもので断面構造を示す。図 7 と比べ、各メモリセルに対し書き込み線を 2 本づつ配している。上記の構成により、メモリセル 9 a , 9 b に対して同時に書き込み線に電流を流して記録することが可能なため高速化することが可能になる。また磁気抵抗素子の形状は本発明の断面が台形となる構造であることから、反転磁界のオフセットが生じず消費電力を抑制することができた。

**【0087】****(実施例 4 )**

図 2 2 は本発明の実施例を示すもので断面構造を示す。隣接するメモリセルと書き込み線を共用化している。また、ソース領域 3 が磁気抵抗膜 9 a と 9 b で共有化される構造となっている。本実施例の構成により、ソース領域を共有化することによって配線本数が減り、デバイス構造が簡略化するために、メモリ素子を小型化できる。また磁気抵抗素子の形状は本発明の断面が台形となる構造であることから、反転磁界のオフセットが生じず消費電力を抑制することができた。

10

**【0088】****【発明の効果】**

本発明の適用により、磁気抵抗素子において、一方の磁性層からの静磁界により、もう一方の磁性層の反転磁界がオフセットする問題を解消することが出来た。また、このような磁気抵抗素子を不揮発固体メモリ、MRAM に用いることによって記録電流を低減できることから、書き込み線の電流密度を大幅に下げながら、一方で高集積化を実現し、コストの上昇を抑制することが可能になる。また、メモリ素子の記録再生動作の安定性を高め、高速に記録再生可能な不揮発固体メモリを実現することができる。

20

**【図面の簡単な説明】**

【図 1】本発明の磁気抵抗素子の断面構造の一例を示す図である。

【図 2】膜表面から 75 nm 離れた地点における垂直磁化膜からの漏洩磁界を説明する図である。

【図 3】膜表面から 2 nm 離れた地点における垂直磁化膜からの漏洩磁界を説明する図である。

【図 4】本発明の磁気抵抗素子の一例を示すための概略的断面図である。

30

【図 5】側壁角度を定義するための模式図である。

【図 6】磁気抵抗素子の断面形状に対するエッチングレートの影響を説明する模式図である。

【図 7】本発明の磁気抵抗素子を用いたメモリ素子を示す断面図である。

【図 8】本発明のメモリの一実施形態を示すための等価回路図である。

【図 9】メモリ素子をマトリックス状に配したメモリの等価回路図である。

【図 10】実施例 1 のメモリ素子を作成するプロセスを説明する図である。

【図 11】実施例 1 のメモリ素子を作成するプロセスを説明する図である。

【図 12】実施例 1 のメモリ素子を作成するプロセスを説明する図である。

【図 13】実施例 1 のメモリ素子を作成するプロセスを説明する図である。

【図 14】実施例 1 のメモリ素子を作成するプロセスを説明する図である。

40

【図 15】傾斜角度とオフセット磁界の大きさの関係を示すための図である。

【図 16】実施例 1 のメモリ素子を作成するプロセスを説明する図である。

【図 17】実施例 1 のメモリ素子を基板上にマトリックス配置したメモリの等価回路図である。

【図 18】実施例 2 のメモリを作製するプロセスを説明するための図である。

【図 19】実施例 2 のメモリを作製するプロセスを説明するための図である。

【図 20】実施例 2 のメモリを作製するプロセスを説明するための図である。

【図 21】実施例 3 のメモリの概略的な断面図である。

【図 22】実施例 4 のメモリの概略的な断面図である。

【図 23】磁気抵抗素子の磁化状態を説明するための模式図である。

50

【図24】角型比1のMRカーブにおいてオフセット磁界H0を説明するためのR-Hカーブである。

【図25】角型比1以下のMRカーブにおいてオフセット磁界H0を説明するためのR-Hカーブである。

【符号の説明】

|     |         |    |

|-----|---------|----|

| 1   | 基板      |    |

| 2   | ドレイン領域  |    |

| 3   | ソース領域   |    |

| 4   | ゲート電極   |    |

| 5   | プラグ     | 10 |

| 6   | ビット線    |    |

| 9   | 磁気抵抗膜   |    |

| 10  | 書き込み線   |    |

| 11  | 書き込み線   |    |

| 15  | 書き込み線   |    |

| 21  | LOCOS領域 |    |

| 22  | ソース電極   |    |

| 100 | 第1磁性層   |    |

| 200 | 第2磁性層   |    |

| 300 | 非磁性層    | 20 |

| 400 | ハードマスク材 |    |

| 500 | レジストマスク |    |

| 600 | 絶縁膜     |    |

| 700 | 上部電極    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2-3】

【図2-4】

【図2-5】

---

フロントページの続き

(56)参考文献 国際公開第01/024289 (WO, A1)

特開2000-306374 (JP, A)

特開2000-353791 (JP, A)

特開2000-132961 (JP, A)

特開2000-306375 (JP, A)

特開2002-111096 (JP, A)

特開平10-004227 (JP, A)

特開2000-195251 (JP, A)

特開2001-101859 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/105

H01L 43/08