(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6072432号

(P6072432)

(45) 発行日 平成29年2月1日(2017.2.1)

(24) 登録日 平成29年1月13日(2017.1.13)

(51) Int.Cl.

F 1

**H01L 29/78 (2006.01)**

**H01L 21/336 (2006.01)**

**H01L 29/12 (2006.01)**

H01L 29/78 652B

H01L 29/78 658B

H01L 29/78 658A

H01L 29/78 652T

H01L 29/78 652Q

請求項の数 16 (全 25 頁) 最終頁に続く

(21) 出願番号

特願2012-1111272 (P2012-1111272)

(22) 出願日

平成24年5月15日 (2012.5.15)

(65) 公開番号

特開2013-239554 (P2013-239554A)

(43) 公開日

平成25年11月28日 (2013.11.28)

審査請求日

平成26年10月9日 (2014.10.9)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 三浦 成久

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 日野 史郎

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板上に形成された第1導電型のドリフト層と、

前記ドリフト層の表層部に選択的に形成された第2導電型のウェル領域と、

前記ウェル領域内の表層部に少なくとも一部が形成された第1導電型のソース領域と、

前記ウェル領域に隣接する前記ドリフト層の部分であるJFET領域と、

前記ソース領域と前記JFET領域とに挟まれた前記ウェル領域の部分であるチャネル領域と、

前記ドリフト層上にゲート絶縁膜を介して配設され、前記ソース領域、前記チャネル領域および前記JFET領域に跨って延在するゲート電極と、 10

前記ソース領域に接続するソース電極と、

前記半導体基板の裏面に形成されたドレイン電極とを備え、

前記ソース領域は、

前記ウェル領域内の表層部に形成され、前記ソース電極に接続する第1導電型のソースコンタクト領域と、

前記ウェル領域内の表層部に形成され、前記チャネル領域に隣接する第1導電型のソースエクステンション領域と、

前記ソースエクステンション領域と前記ソースコンタクト領域との間に接続し、第2導電型の不純物が導入されていない第1導電型のソース抵抗制御領域とを含む

10

20

ことを特徴とする半導体装置。

【請求項 2】

半導体基板と、

前記半導体基板上に形成された第1導電型のドリフト層と、

前記ドリフト層の表層部に選択的に形成された第2導電型のウェル領域と、

前記ウェル領域内の表層部に少なくとも一部が形成された第1導電型のソース領域と、

前記ウェル領域に隣接する前記ドリフト層の部分であるJ F E T領域と、

前記ソース領域と前記J F E T領域とに挟まれた前記ウェル領域の部分であるチャネル領域と、

前記ドリフト層上にゲート絶縁膜を介して配設され、前記ソース領域、前記チャネル領域および前記J F E T領域に跨って延在するゲート電極と、

前記ソース領域に接続するソース電極と、

前記半導体基板の裏面に形成されたドレイン電極とを備え、

前記ソース領域は、

前記ウェル領域内の表層部に形成され、前記ソース電極に接続する第1導電型のソースコンタクト領域と、

前記ウェル領域内の表層部に形成され、前記チャネル領域に隣接する第1導電型のソースエクステンション領域と、

前記ソースエクステンション領域と前記ソースコンタクト領域との間に接続し、第2導電型の不純物が導入されていない第1導電型のソース抵抗制御領域とを含み、

前記ウェル領域は、前記ソース領域の下方全体に形成されている

ことを特徴とする半導体装置。

【請求項 3】

前記半導体基板は、炭化珪素を含む請求項1または請求項2に記載の半導体装置。

【請求項 4】

前記ソース抵抗制御領域は、前記ウェル領域内の表層部における前記ソースエクステンション領域と前記ソースコンタクト領域との間の領域に形成されている

請求項1から請求項3のいずれか一項に記載の半導体装置。

【請求項 5】

前記ソース抵抗制御領域の第1導電型の不純物濃度は、前記ドリフト層の表層部の第1導電型の不純物濃度と同等である

請求項4に記載の半導体装置。

【請求項 6】

前記ソース抵抗制御領域は、前記ドリフト層上に、前記ソースエクステンション領域と前記ソースコンタクト領域との間を跨ぐように形成されている

請求項1から請求項3のいずれか一項に記載の半導体装置。

【請求項 7】

前記ソース抵抗制御領域は、前記チャネル領域および前記J F E T領域上にまで延在し、

前記ゲート絶縁膜及び前記ゲート電極は、前記ソース抵抗制御領域上に形成されている

請求項6に記載の半導体装置。

【請求項 8】

前記ソース抵抗制御領域は、前記第1ウェル領域とのp n接合による空乏層で当該ソース抵抗制御領域が分断されない程度の第1導電型の不純物濃度を有する

請求項6または請求項7に記載の半導体装置。

【請求項 9】

前記ゲート電極の端は、前記ソースエクステンション領域の上方の領域にある

請求項1から請求項8のいずれか一項に記載の半導体装置。

【請求項 10】

前記ドリフト層の表層部の第1導電型の不純物濃度は、当該ドリフト層の他の部分の第

10

20

30

40

50

1 導電型の不純物濃度よりも低い

請求項 1 から請求項 9 のいずれか一項に記載の半導体装置。

**【請求項 1 1】**

前記 J F E T 領域に形成され、前記ドリフト層よりも第 1 導電型の不純物濃度が高い電流制御領域をさらに備える

請求項 1 から請求項 10 のいずれか一項に記載の半導体装置。

**【請求項 1 2】**

前記ソース抵抗制御領域の第 1 導電型の不純物濃度は、前記ソースエクステンション領域またはソースコンタクト領域の第 1 導電型の最大不純物濃度の 1 / 1 0 0 0 以下であることを特徴とする

請求項 1 から請求項 11 のいずれか一項に記載の半導体装置。

**【請求項 1 3】**

前記ソース抵抗制御領域における前記ソースエクステンション領域から前記ソースコンタクト領域までの長さは、0 . 1 ~ 1 . 0 μm の範囲である

請求項 6 から請求項 8 のいずれか一項に記載の半導体装置。

**【請求項 1 4】**

( a ) 第 1 導電型の半導体層の表層部に、第 2 導電型の不純物をイオン注入することによりウェル領域を形成する工程と、

( b ) 前記ウェル領域内の表層部に第 1 導電型の不純物をイオン注入することよりソース領域を形成する工程と、

( c ) 前記ウェル領域に隣接する前記半導体層の部分である J F E T 領域、前記ソース領域と前記 J F E T 領域とに挟まれた前記ウェル領域の部分であるチャネル領域および前記ソース領域に跨るように、前記半導体層上にゲート絶縁膜を介してゲート電極を形成する工程と、

( d ) 前記ソース領域に接続するソース電極を形成する工程とを備え、

前記工程 ( b ) で形成される前記ソース領域は、

前記ソース電極に接続する第 1 導電型のソースコンタクト領域と、

前記チャネル領域に隣接する第 1 導電型のソースエクステンション領域と、

前記ソースエクステンション領域と前記ソースコンタクト領域との間に形成され、イオン注入が施されていない第 1 導電型のソース抵抗制御領域とを含み、

前記工程 ( a ) 及び ( b ) は、前記ソース抵抗制御領域の形成領域を覆う要素マスクを含むマスクを用いて行われ、

前記工程 ( a ) では、イオン注入した不純物の横方向の散乱により、前記要素マスクの下方の深い位置で接続した形状のウェル領域が形成され、

前記工程 ( b ) では、前記要素マスクの下で分離した前記ソースコンタクト領域及びソースエクステンション領域が形成されると共に、前記要素マスクの下にソース抵抗制御領域が形成される

ことを特徴とする半導体装置の製造方法。

**【請求項 1 5】**

前記工程 ( a ) は、

前記工程 ( b ) と同じマスクを用いる第 1 のイオン注入工程と、

前記チャネル領域となる部分を形成する第 2 のイオン注入工程とを含む

請求項 1 4 に記載の半導体装置の製造方法。

**【請求項 1 6】**

( a ) 第 1 導電型の半導体層の表層部に、第 2 導電型の不純物をイオン注入することによりウェル領域を形成する工程と、

( b ) 前記ウェル領域内の表層部及び表面上に第 1 導電型のソース領域を形成する工程と、

( c ) 前記ウェル領域に隣接する前記半導体層の部分である J F E T 領域、前記ソース領域と前記 J F E T 領域とに挟まれた前記ウェル領域の部分であるチャネル領域および前

10

20

30

40

50

記ソース領域に跨るように、前記半導体層上にゲート絶縁膜を介してゲート電極を形成する工程と、

(d) 前記ソース領域に接続するソース電極を形成する工程とを備え、

前記工程(b)で形成される前記ソース領域は、

前記ウェル領域内の表層部に形成され、前記ソース電極に接続するソースコンタクト領域と、

前記ウェル領域内の表層部に形成され、前記チャネル領域に隣接するソースエクステンション領域と、

前記半導体層の表面上に前記ソースエクステンション領域と前記ソースコンタクト領域との間を跨ぐように形成されたソース抵抗制御領域とを含み、

10

前記工程(b)は、

前記ウェル領域の表層部への選択的なイオン注入により、前記ソースコンタクト領域及び前記ソースエクステンション領域を形成する工程と、

前記半導体層の表面上にエピタキシャル成長層を形成してパターニングすることにより、前記ソース抵抗制御領域を形成する工程とを含むことを特徴とする半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は半導体装置の構造及びその製造方法に関するものである。

20

##### 【背景技術】

##### 【0002】

炭化珪素(SiC)半導体を母材とした半導体素子は、高耐圧・低損失を実現できるデバイスとして注目されている。特に、金属/絶縁体/半導体接合の電界効果型トランジスタ(Metal-Oxide Semiconductor Field Effect Transistor; MOSFET)は、パワー・エレクトロニクスへの応用の観点から高信頼性化が求められている。

##### 【0003】

例えば、そのような半導体素子を、インバータ回路などに適用し、誘導性負荷や抵抗性負荷を動作させているときに、アーム短絡などの負荷短絡が生じて、オン状態の素子のドレインに電源電圧である高電圧が印加されると、当該素子に大電流が流れる状態になる。この状態では、素子には定格電流の数倍から数十倍のドレイン電流が誘起され、適切な保護機能を有していなければ素子破壊に至る。

30

##### 【0004】

これを未然に防ぐためには、素子破壊が発生する前に、過剰なドレイン電流(過電流)を検知し、それに応じてゲート電極へのオフ信号を入力してドレイン電流を遮断する必要がある。そのため、素子には、負荷短絡等の発生から過電流を検知してゲート電極へのオフ信号入力までの時間以上に渡って、素子破壊が発生しないロバスト性が求められる。すなわち、短絡耐量が高いことが強く望まれる。なお、短絡耐量は、負荷短絡等が生じてから素子破壊に至るまでに要する時間として定義される。

##### 【0005】

40

特許文献1には、典型的なパワーデバイスであるIGBT(Insulated Gate Bipolar Transistor)の短絡耐量の向上させる技術が開示されている。特許文献1のIGBTでは、オン電流の経路となるエミッタ層が、高抵抗なエミッタ層(高抵抗領域)と低抵抗なエミッタ層(低抵抗領域)とがエミッタ電極とチャネル領域との間に互いに並列接続するよう交差に配設された構造となっている。この構成によれば、負荷短絡が生じたときにエミッタ層を流れる電子電流による電圧降下が大きくなり、飽和電流値が下がるため、短絡耐量を向上する。さらに、低抵抗領域が、エミッタ電極とのエミッタ層との間のコンタクト抵抗を低くするため、低いオン電圧も実現される。

##### 【先行技術文献】

##### 【特許文献】

50

**【0006】**

【特許文献1】特開2003-332577号公報

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

特許文献1のようにエミッタ層を並列接続した高抵抗領域及び低抵抗領域で構成すると、エミッタ層全体の抵抗値はおよそ低抵抗領域の抵抗値によって支配される。そのため、チャネル領域からエミッタ電極までの電圧降下があまり大きくならず、飽和電流を下げる効果が充分に得られない場合も考えられる。さらに、エミッタ電極は低抵抗領域だけではなく高抵抗領域にも接続されるため、実効的なコンタクト抵抗は、低抵抗領域だけの場合に比べると高くなる。

**【0008】**

本発明は以上のような問題を解決するためになされたものであり、チャネル領域からソース電極までの電圧降下を大きくして短絡耐量の向上を図ることができ、且つ、ソース電極とソース領域とのコンタクト抵抗を低く維持できる半導体装置を提供することを目的とする。

**【課題を解決するための手段】****【0009】**

本発明に係る半導体装置は、半導体基板と、前記半導体基板上に形成された第1導電型のドリフト層と、前記ドリフト層の表層部に選択的に形成された第2導電型のウェル領域と、前記ウェル領域内の表層部に少なくとも一部が形成された第1導電型のソース領域と、前記ウェル領域に隣接する前記ドリフト層の部分であるJFET領域と、前記ソース領域と前記JFET領域とに挟まれた前記ウェル領域の部分であるチャネル領域と、前記ドリフト層上にゲート絶縁膜を介して配設され、前記ソース領域、前記チャネル領域および前記JFET領域に跨って延在するゲート電極と、前記ソース領域に接続するソース電極と、前記半導体基板の裏面に形成されたドレイン電極とを備え、前記ソース領域は、前記ウェル領域内の表層部に形成され、前記ソース電極に接続する第1導電型のソースコンタクト領域と、前記ウェル領域内の表層部に形成され、前記チャネル領域に隣接する第1導電型のソースエクステンション領域と、前記ソースエクステンション領域と前記ソースコンタクト領域との間に接続し、第2導電型の不純物が導入されていない第1導電型のソース抵抗制御領域とを含むものである。

**【発明の効果】****【0010】**

本発明に係る半導体装置によれば、チャネル領域とソース電極との間に、ソース抵抗制御領域が直列に挿入された構造を有するため、半導体装置の負荷短絡時にソース領域の電圧降下を調整できる。その電圧降下を大きくすると、半導体装置の飽和電流値が下がり、短絡耐量が向上する。ソース抵抗制御領域は、イオン注入がなされておらず第1導電型の不純物濃度が低いので、その抵抗値の温度依存性が大きい。そのため、負荷短絡時には、発熱によってソース抵抗制御領域における電圧降下が特に増加して、高い短絡耐量が得られる。また、ソース領域におけるソース電極との接続部分には、低抵抗なソースコンタクト領域が形成されているので、ソース電極とソース領域とのコンタクト抵抗を低く維持できる。すなわち、本発明に係る半導体装置によれば、短絡耐量を向上させつつ定格のオン動作時の導通損失を抑制することができる。

**【図面の簡単な説明】****【0011】**

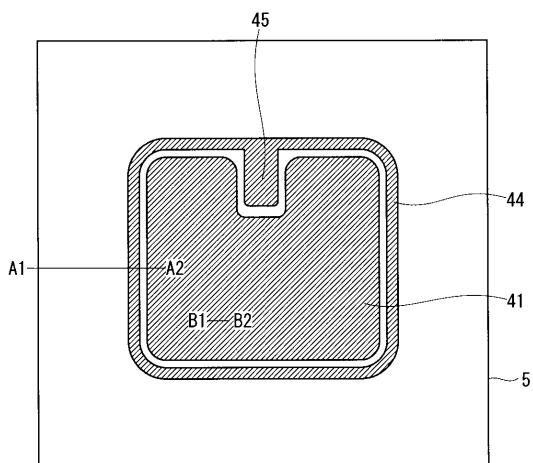

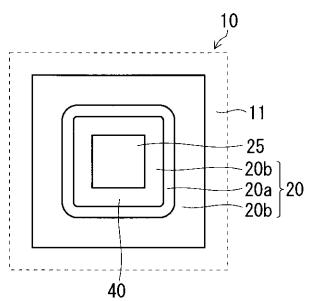

【図1】実施の形態1及び2に係る半導体装置の上面図である。

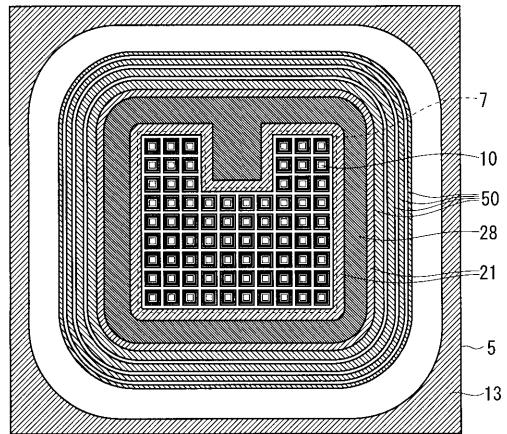

【図2】実施の形態1及び2に係る半導体装置のドリフト層の表面構造を示す上面図である。

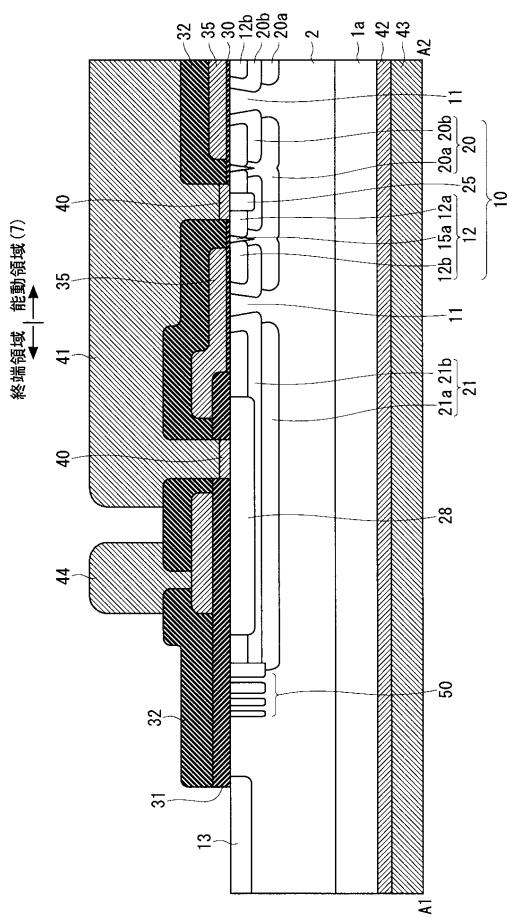

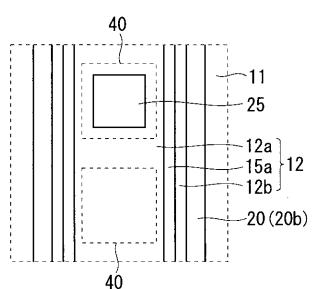

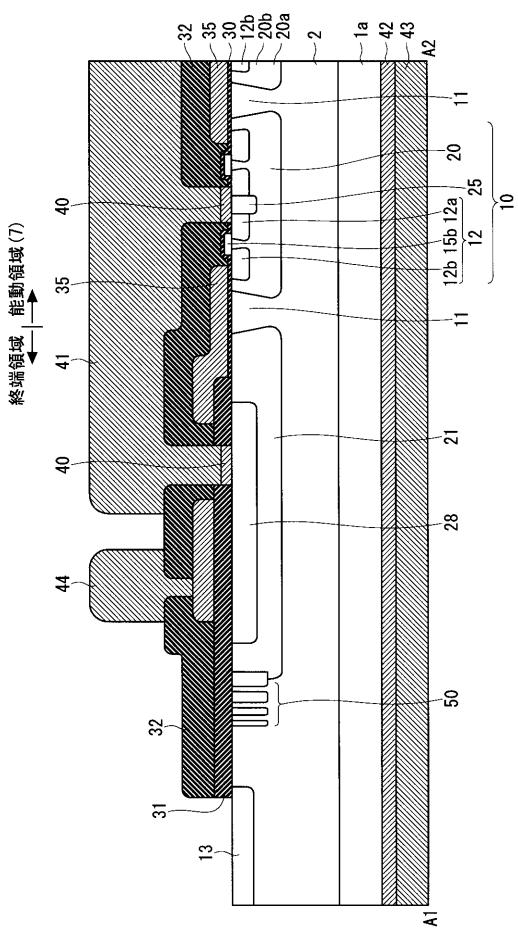

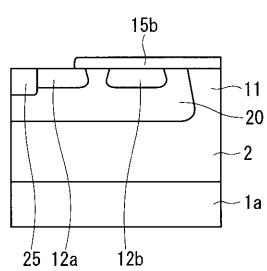

【図3】実施の形態1に係る半導体装置の周辺部における縦断面図である。

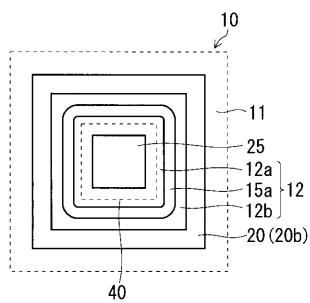

【図4】実施の形態1に係る半導体装置のユニットセルのドリフト層の表面構造を示す上

10

20

30

40

50

面図である。

【図5】実施の形態1に係る半導体装置のユニットセルのドリフト層の表層部におけるソース領域よりも若干深い位置の構造を示す横断面図である。

【図6】実施の形態1に係る半導体装置のユニットセルの変形例を示す上面図である。

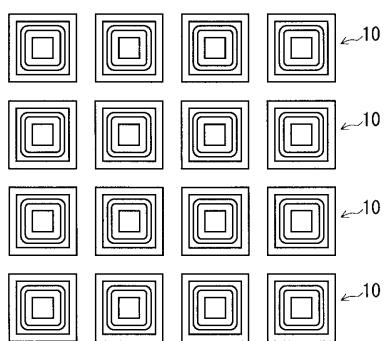

【図7】実施の形態1に係る半導体装置のユニットセルのレイアウトを示す上面図である。

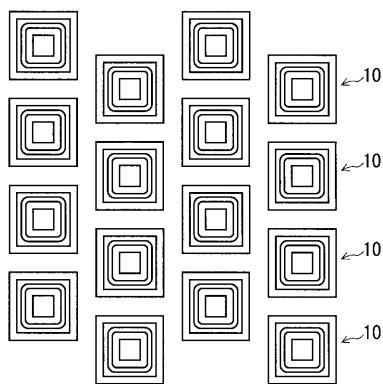

【図8】実施の形態1に係る半導体装置のユニットセルのレイアウトの変形例を示す上面図である。

【図9】実施の形態1に係る半導体装置のユニットセルのレイアウトの変形例を示す上面図である。

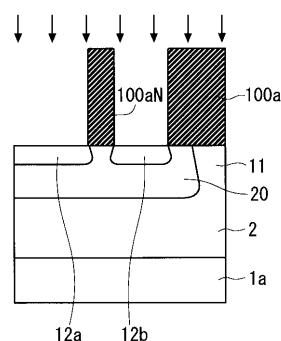

【図10】実施の形態1に係る半導体装置の製造方法を示す縦断面図である。

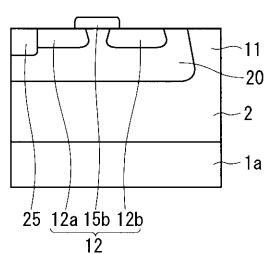

【図11】実施の形態1に係る半導体装置の製造方法を示す縦断面図である。

【図12】実施の形態1に係る半導体装置の製造方法を示す縦断面図である。

【図13】実施の形態1に係る半導体装置の製造方法を示す縦断面図である。

【図14】実施の形態1に係る半導体装置の製造方法を示す縦断面図である。

【図15】実施の形態1に係る半導体装置の製造方法を示す縦断面図である。

【図16】実施の形態1に係る半導体装置のウェル領域における第2導電型の不純物濃度分布の数値計算結果を示す図である。

【図17】実施の形態1に係る半導体装置のソース領域における第1導電型の不純物濃度分布の数値計算結果を示す図である。

【図18】実施の形態1に係る半導体装置のソース領域における第1導電型の不純物濃度分布の数値計算結果を示す図である。

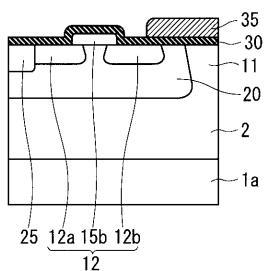

【図19】実施の形態2に係る半導体装置の周辺部における縦断面図である。

【図20】実施の形態2に係る半導体装置の製造方法を示す縦断面図である。

【図21】実施の形態2に係る半導体装置の製造方法を示す縦断面図である。

【図22】実施の形態2に係る半導体装置の製造方法を示す縦断面図である。

【図23】実施の形態2に係る半導体装置の製造方法を示す縦断面図である。

【図24】実施の形態2に係る半導体装置の製造方法を示す縦断面図である。

【図25】実施の形態2に係る半導体装置の製造方法を示す縦断面図である。

【発明を実施するための形態】

【0012】

以下の実施の形態では、不純物の導電型の定義として、「第1導電型」をn型、「第2導電型」をp型とするが、この定義は逆でもよい。つまり「第1導電型」をp型、「第2導電型」をn型としてもよい。

【0013】

また、本明細書では、個々の半導体素子を狭義の意味で「半導体装置」と称しているが、例えば、リードフレーム上に、半導体素子のチップ、当該半導体素子に逆並列に接続するフリーホイールダイオード及び当該半導体素子のゲート電極に電圧を印加する制御回路と搭載して、一体的に封止して成る半導体モジュール（例えば、インバータモジュールなどのパワーモジュール）も、広義の意味で「半導体装置」に含まれる。

【0014】

<実施の形態1>

図1は、実施の形態1に係る半導体装置である炭化珪素MOSFETの上面構成を模式的に示す図である。また図2は、当該半導体装置の半導体層の最表面の構成を示す図である。つまり、当該半導体装置は、図2に示す半導体層の上に、図1に示す各要素が形成されて構成されている。

【0015】

図1のように、半導体装置のチップ5の上面には、ソースパッド（ソース電極）41、ゲート配線44及びゲートパッド45が形成されている。ゲートパッド45は、チップ5の1辺の中央近傍に配設される。ゲート配線44はゲートパッド45に接続しており、ソ

10

20

30

40

50

ースパッド 4 1 の周囲を囲むように形成される。

**【 0 0 1 6 】**

図 2 の点線で囲まれた領域 7 は、MOSFET の複数のユニットセル 10 が並列配置される能動領域 7 であり、ソースパッド 4 1 は、その能動領域 7 の上方を覆うように形成されている。

**【 0 0 1 7 】**

ゲートパッド 4 5 には、ゲート配線 4 4 を介してユニットセル 10 のゲート電極が接続しており、外部の制御回路（不図示）からゲートパッド 4 5 に印加されたゲート電圧は、各ユニットセル 10 のゲート電極に伝達される。同様に、ソースパッド 4 1 には、各ユニットセル 10 のソース領域が接続している。

10

**【 0 0 1 8 】**

図 2 に示すように、能動領域 7 の外側の領域（終端領域）には、後述する終端ウェル領域 21、終端低抵抗領域 28、FLR (Field Limiting Ring) 領域 50 が、能動領域 7 を取り囲むように形成されている。終端低抵抗領域 28 は終端ウェル領域 21 の内部に形成されており、FLR 領域 50 は終端ウェル領域 21 の外端に形成されている。さらに、FLR 領域 50 から離間して、FLR 領域 50 の外側を囲むように、フィールドストップ領域 13 が形成されている。フィールドストップ領域 13 の外周は、チップ 5 の端部にまで及んでいる。

**【 0 0 1 9 】**

なお、半導体装置の実際の製品では、チップ 5 に、外部の保護回路を動作させるための温度センサや電流センサ用の各電極が配設されることが多いが、それらの電極は本発明との関連が薄いため、本実施の形態では省略している。また、ゲートパッド 4 5、ゲート配線 4 4 及びソースパッド 4 1 のレイアウトは図 1 に示したものに限られない。それらの形状、個数等は、製品によって多種多様である。温度センサ及び電流センサ用の電極の有無や、各電極のレイアウトは本発明の効果にあまり影響しないため任意でよい。

20

**【 0 0 2 0 】**

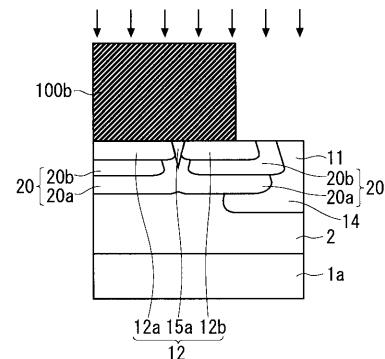

図 3 は、実施の形態 1 に係る半導体装置（炭化珪素 MOSFET）の周辺部の構成を模式的に示す縦断面図であり、図 1 に示す A 1 - A 2 断面に対応している。同図には、最外周のユニットセル 10 と、その外側の終端領域が示されている。

**【 0 0 2 1 】**

30

図 3 に示すように、当該 MOSFET は、第 1 導電型（n 型）の炭化珪素で形成された半導体基板 1a と、その表面上にエピタキシャル成長させた第 1 導電型のドリフト層 2（炭化珪素半導体層）とから成るエピタキシャル基板を用いて形成されている。半導体基板 1a の裏面側には、半導体基板 1a とオーミック接続するオーミック電極 4 2 を介して、ドレイン電極 4 3 が形成されている。

**【 0 0 2 2 】**

ドリフト層 2 において、能動領域 7 の表層部には、第 2 導電型（p 型）の複数のウェル領域 20 が選択的に形成されている。図 3 に示すように、本実施の形態では、ウェル領域 20 は、部分的に重複して形成された第 1 ウェル領域 20a と第 2 ウェル領域 20b とかく構成されている。ドリフト層 2 の表層部におけるウェル領域 20 に隣接する部分 11 は「JFET 領域」と呼ばれる。

40

**【 0 0 2 3 】**

ウェル領域 20 の表層部には、第 1 導電型のソース領域 12 が選択的に形成されている。ウェル領域 20 におけるソース領域 12 と JFET 領域 11 との間の部分は MOSFET がオンするときにチャネルが形成される領域であり、「チャネル領域」と呼ばれる。

**【 0 0 2 4 】**

本実施の形態において、ウェル領域 20 を構成する第 1 ウェル領域 20a は、ソース領域 12 の下方全体に形成されている。第 2 ウェル領域 20b は、少なくとも、ソース領域 12 と JFET 領域 11 との間の領域（チャネル領域）を含むように形成されている。

**【 0 0 2 5 】**

50

図3に示すように、ソース領域12は、いずれも第1導電型のソースコンタクト領域12a、ソースエクステンション領域12b及びソース抵抗制御領域15aから成っている。ソースコンタクト領域12aは、それとオーミック接続するオーミック電極40を介してソースパッド41に接続される。ソース抵抗制御領域15aは、ソースコンタクト領域12aの外側を囲むように形成される。ソースエクステンション領域12bは、ソース抵抗制御領域15aの外側を囲むように形成される。ソースエクステンション領域12bはソース領域12の再外周部であり、チャネル領域に隣接する。

#### 【0026】

ソース抵抗制御領域15aは、上記の第1ウェル領域20a及び第2ウェル領域20bを形成する第2導電型の不純物が直接的にイオン注入されていない領域である。つまりソース抵抗制御領域15aは、ドリフト層2と同じ第1導電型の不純物濃度を有する。よって、ソース抵抗制御領域15aは、ソースコンタクト領域12a及びソースエクステンション領域12bよりも不純物濃度が低い。ソースコンタクト領域12aの不純物濃度とソースエクステンション領域12bの不純物濃度は同程度でよい。後述するように、ソースコンタクト領域12aとソースエクステンション領域12bは、同時に形成することができ、その場合、両者は同じ不純物分布を持つことになる。

#### 【0027】

ソースコンタクト領域12aの内側には、オーミック電極40を介してソースパッド41に接続する第2導電型のウェルコンタクト領域25が形成されている。ウェルコンタクト領域25は、ソースコンタクト領域12aを貫通して、ウェル領域20に達しており、ソースパッド41とウェル領域20とを電気的に接続している。

#### 【0028】

ゲート電極35は、ドリフト層2上にゲート絶縁膜30を介して形成され、ソースエクステンション領域12b、ウェル領域20(チャネル領域)及びJ F E T領域11に跨って延在する。ソース領域12を構成する3つの領域のうち、ソースエクステンション領域12bが、ゲート絶縁膜30及びゲート電極35と共にMOS構造を形成する。

#### 【0029】

一方、能動領域7の外側の領域(終端領域)には、ドリフト層2の表層部に、第2導電型の終端ウェル領域21が形成されている。本実施の形態では、終端ウェル領域21も、ウェル領域20と同様に、部分的に重複して形成された第1ウェル領域20aと第2ウェル領域20bとからなっている。

#### 【0030】

終端ウェル領域21の表層部には、オーミック電極40を介してソースパッド41に接続する、第2導電型の終端低抵抗領域28が形成される。よって、ソースパッド41は、ソースコンタクト領域12aと接続されると共に、ウェルコンタクト領域25及び終端低抵抗領域28を介してウェル領域20及び終端ウェル領域21にも電気的に接続される。なお、終端ウェル領域21とウェル領域20とは同時に形成することができ、その場合、両者は同じ不純物分布を持つことになる。

#### 【0031】

終端ウェル領域21の外周部には、第2導電型のF L R領域50が、ドリフト層2の表層部に形成される。さらに、F L R領域50の外側を囲むように、第1導電型のフィールドストップ領域13が、終端ウェル領域21から離間した位置に形成される。

#### 【0032】

ドリフト層2における終端領域の表面には、ゲート絶縁膜30が形成されない部分にフィールド酸化膜31が形成されている。ゲート電極35の一部は、フィールド酸化膜31上にまで延在しており、その部分でゲート電極35とゲート配線44との接続がなされる。

#### 【0033】

ゲート電極35上は層間絶縁膜32で覆われており、ソースパッド41、ゲート配線44及びゲートパッド45はその上に形成される。そのため、層間絶縁膜32には、ソース

10

20

30

40

50

パッド41をソースコンタクト領域12a、ウェルコンタクト領域25及び終端低抵抗領域28に接続させるコンタクトホール(ソースコンタクトホール)、並びに、ゲート配線44をゲート電極35に接続させるコンタクトホール(ゲートコンタクトホール)が形成される。

#### 【0034】

図4は、ユニットセル10の最表面部の平面構造を模式的に示す図である。先に述べたように、ユニットセル10は、ソース領域12が、ソースコンタクト領域12a、ソースエクステンション領域12b及びその間のソース抵抗制御領域15aという3つの領域から構成されている。

#### 【0035】

また、図5は、ユニットセル10の表層部におけるソース領域12よりも若干深い位置の構造を模式的に示す横断面図である。先に述べたように、ソース抵抗制御領域15aは、第1ウェル領域20a及び第2ウェル領域20bを形成するためのイオン注入が行われていない領域であるが、それが存在するのはウェル領域20の表層部のみである。すなわち、ソース抵抗制御領域15aの下方には第1ウェル領域20aが形成されており、ソース領域12の下方全体が第2導電型の領域となっている。

10

#### 【0036】

図4のソースコンタクト領域12a内に示されている点線は、ソースパッド41をユニットセル10に接続させるオーミック電極40の形成領域(コンタクトホール)を示している。オーミック電極40は、上記3つの領域のうち、ソースコンタクト領域12aのみに接触している。よって、ソースコンタクト領域12a、ソース抵抗制御領域15a及びソースエクステンション領域12bは、オーミック電極40とウェル領域20のチャネル領域(第2ウェル領域20b)との間に直列接続されることになる。なお、ソースコンタクト領域12aは、不純物濃度が高いため、オーミック電極40との間でコンタクト抵抗の低いオーミック接触を実現している。

20

#### 【0037】

MOSFETのオン動作時もしくは負荷短絡時において、ドレイン電極43からドリフト層2に流れ込むドレイン電流(オン電流)は、JFET領域11及び第2ウェル領域20bの表面部(チャネル領域)に形成されたチャネル領域を通り、ソースエクステンション領域12b、ソース抵抗制御領域15a及びソースコンタクト領域12aを通ってオーミック電極40からソース電極41へと抜けるという経路を流れる。

30

#### 【0038】

各ユニットセル10において、ソース抵抗制御領域15aは、オン電流が流れる方向、すなわちソースエクステンション領域12bからソースコンタクト領域12aに向かう方向の長さ(電流の経路長)が均一になるように形成される。特に、ソースコンタクト領域12aの外周(ソース抵抗制御領域15aの内周)及びソースエクステンション領域12bの内周(ソース抵抗制御領域15aの外周)の各コーナー部がラウンド形状になっており、ソースコンタクト領域12aの外周曲率半径中心と、ソースエクステンション領域12bの内周曲率半径中心とが同じになっている。このようにユニットセル10内でソース抵抗制御領域15aの長さを均一にすると、ソース抵抗のバラツキが抑えられる。それにより、短絡電流などの過剰の電流が瞬時に印加されたときに特定の部分に電流が集中することが防止でき、半導体装置の信頼性を高めることができる。

40

#### 【0039】

また、ソースエクステンション領域12bの外周コーナー部もラウンド形状にし、その曲率半径中心を、ソースコンタクト領域12aの外周曲率半径中心及びソースエクステンション領域12bの内周曲率半径中心と同じにしてもよい。この場合は、ソースエクステンション領域12bの寄生抵抗がユニットセル10内で均一化される。

#### 【0040】

さらに、第2ウェル領域20bの外周コーナー部もラウンド形状にし、その曲率半径中心を、ソースコンタクト領域12aの外周曲率半径中心及びソースエクステンション領域

50

12b の内周曲率半径中心と同じにして、チャネル長を均一化してもよい。この場合、チャネル抵抗が均一化され、素子特性及び電流分布のバラツキが抑制され、一層信頼性の高いユニットセル 10 構造となる。

#### 【0041】

なお、図 4 では、四角形の平面構造を有するユニットセル 10 を示したが、ユニットセル 10 の形状は任意でよく、例えば六角形や八角形、円形などでもよい。また MOSFET は複数のユニットセル 10 から成るセル構造でなくてもよく、例えば図 6 に示すような櫛形の構造であってもよい。一般的に、櫛形構造は形成が容易であるが、セル構造に比べてチャネル幅密度が低いため、素子のオン抵抗が比較的高くなる。

#### 【0042】

また、本実施の形態では、複数のユニットセル 10 が、図 7 のようにマトリクス状に配置されるものと仮定するが、例えば、図 8 のようにユニットセル 10 を互い違いに（千鳥状に）配置してもよい。

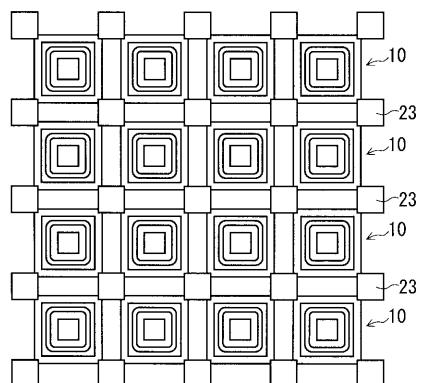

#### 【0043】

また図 7 の配置では、MOSFET のドレイン電極に逆バイアスが印加されたとき、各ウェル領域 20（第 2 ウェル領域 20b）のコーナー部上のゲート絶縁膜に高電界が発生しやすく、半導体装置の信頼性に影響を与える場合がある。そこで、図 9 のように、ウェル領域 20 のコーナー部同士間を橋渡しするように、第 2 導電型のウェルブリッジ領域 23 を形成してもよい。ウェルブリッジ領域 23 はウェル領域 20 とは個別の工程で形成してもよいが、ウェル領域 20 を形成するイオン注入で同時に形成すればマスクパターン形成工程及びイオン注入工程の増加が抑えられる。

#### 【0044】

次に、実施の形態 1 に係る半導体装置（炭化珪素 MOSFET）の製造方法を説明する。図 10～図 15 は当該製造方法を説明するための工程図である。図 10～図 15 は、能動領域 7 内に複数配設されたユニットセル 10 のうちの一つの右側半分の縦断面に相当する。つまり、図 10～図 15 は終端領域を含んでおらず、能動領域 7 内の領域の任意の位置の断面（図 1 の B1-B2 線に沿った断面）を示している。

#### 【0045】

まず、第 1 導電型の炭化珪素からなる半導体基板 1a を用意する。半導体基板 1a には炭化珪素の他、珪素に比べてバンドギャップの大きい他のワイドバンドギャップ半導体を用いても良い。ワイドバンドギャップ半導体としては、炭化珪素の他、例えば窒化ガリウム、窒化アルミニューム、ダイヤモンド等がある。半導体基板 1a の面方位は任意でよく、例えば、その表面垂直方向が c 軸方向に対して 8° 以下に傾斜されていてもよいし、或いは傾斜していないくともよい。半導体基板 1a の厚みも任意でよく、例えば 350 μm 程度でもよいし、100 μm 程度でもよい。

#### 【0046】

続いて、半導体基板 1a 上に、エピタキシャル結晶成長により、第 1 導電型のドリフト層 2 を形成する。ドリフト層 2 の第 1 導電型の不純物濃度は  $1 \times 10^{13} \text{ cm}^{-3}$  ~  $1 \times 10^{17} \text{ cm}^{-3}$  程度とし、その厚みは 3 μm ~ 200 μm とした。

#### 【0047】

ドリフト層 2 の不純物濃度分布は厚み方向に一定であることが望ましいが、一定でなくともよく、例えば表面近傍で不純物濃度を意図的に低くしてもよい。その場合、素子に逆バイアスが印加されたときにゲート絶縁膜 30 に生じる電界が低減され、素子の信頼性が向上する他、素子のしきい値電圧を高く設定することができる。また、ドリフト層 2 の表層部の不純物濃度は、ソース抵抗制御領域 15a の不純物濃度を規定するため、それを低くすると、特に高温下でソース抵抗制御領域 15a の抵抗増加が期待され、短絡耐量の向上に寄与できる。

#### 【0048】

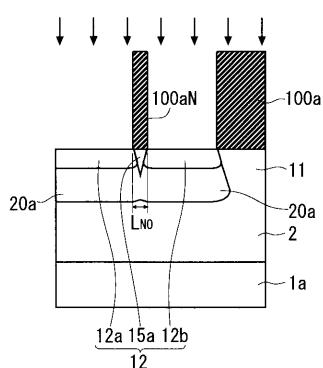

その後、図 10 のように、写真製版処理により、ソースコンタクト領域 12a 及びソースエクステンション領域 12b の形成領域が開口された注入マスク 100a, 100aN

10

20

30

40

50

(例えはレジストやシリコン酸化膜)を形成する。注入マスク 100aN(要素マスク)は、ソース抵抗制御領域 15a となる領域上に形成されている。注入マスク 100a, 100aN を用いた選択的なイオン注入により、第 2 導電型の第 1 ウェル領域 20a を形成する。またこれと同時に、終端領域(不図示)に終端ウェル領域 21 の第 1 ウェル領域 21a が形成する。

#### 【0049】

ここで、注入マスク 100aN の幅 ( $L_{N_0}$ ) は、第 1 ウェル領域 20a 形成のためにイオン注入する注入種の横方向散乱長の 2 倍よりも短くする。また、注入マスク 100a 及び 100aN は、その側面がドリフト層 2 の表面に対して垂直に近い形状であることが望ましい。そうすることにより、注入マスク 100aN の直下のドリフト層 2 最表面には不純物が注入されないが、ドリフト層 2 の深い位置では不純物の横方向散乱によって注入マスク 100aN の下方にも不純物が導入される。その結果、第 1 ウェル領域 20a の上層部に、第 1 導電型の領域が局所的に残存することになり、それがソース抵抗制御領域 15a となる。

10

#### 【0050】

例えは、注入マスク 100aN の幅 ( $L_{N_0}$ ) を注入種の横方向散乱長の 2 倍以上に設定すると、図 11 のように、第 1 ウェル領域 20a が注入マスク 100aN の下で分離されるため好ましくない。

#### 【0051】

本実施の形態では、このような第 1 ウェル領域 20a の分離が生じないように、注入マスク 100aN の幅  $L_{N_0}$  及び、注入種の加速エネルギーを設定する。例えは、注入マスク 100aN の幅  $L_{N_0}$  を  $0.1 \mu\text{m} \sim 0.5 \mu\text{m}$  程度とし、注入種を A1 としてその注入種の加速エネルギーを  $350 \text{ keV} \sim 2 \text{ MeV}$  程度とした。

20

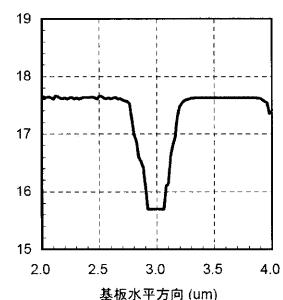

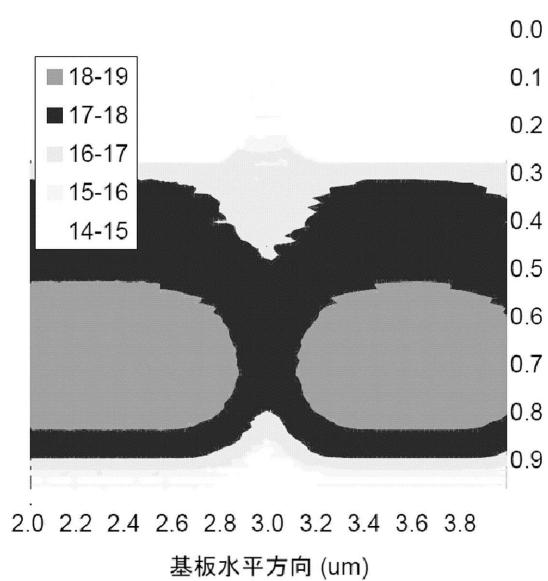

#### 【0052】

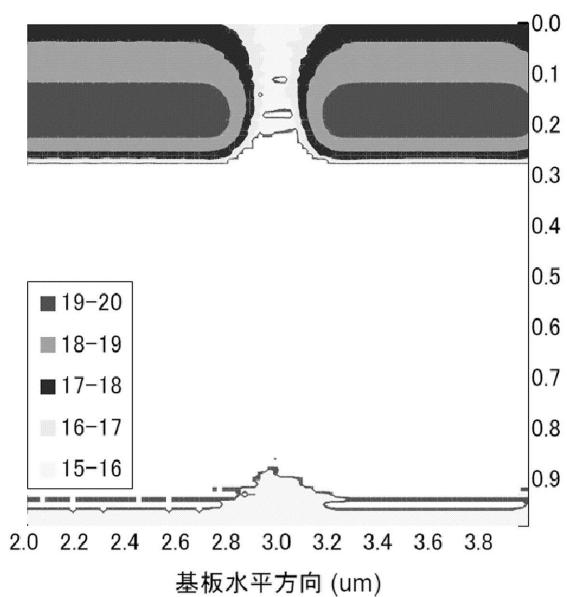

図 16 は、注入種 A1、加速エネルギー  $700 \text{ keV}$ 、注入量  $3 \times 10^{14} \text{ cm}^{-2}$  の条件のイオン注入で形成した第 1 ウェル領域 20a における A1 濃度分布の数値計算結果である。ドリフト層 2 に相当する基板の第 1 導電型の不純物濃度は  $5 \times 10^{15} \text{ cm}^{-3}$  であり、注入マスク 100aN の幅  $L_{N_0}$  は  $0.4 \mu\text{m}$  とした。注入マスク 100aN は、図 16 における基板水平方向の  $2.8 \sim 3.2 \mu\text{m}$  の部分に形成されている。

#### 【0053】

30

図 16 のように、注入された A1 は、基板のやや深い位置で横方向に広がり、注入マスク 100aN の下方にも導入されることが分かる。具体的には、注入マスク 100aN の下方の深さ  $0.5 \sim 0.8 \mu\text{m}$  の領域に、 $10^{17} \text{ cm}^{-3}$  以上の不純物濃度を有する第 2 導電型の第 1 ウェル領域 20a が形成されている。

#### 【0054】

このように、注入時の横方向散乱を利用してソース抵抗制御領域 15a 直下にも第 1 ウェル領域 20a を形成した場合、その部分の第 2 導電型の不純物濃度は他の部分よりも低くなる(例えは図 16 においても、ソース抵抗制御領域 15a 直下に相当する部分には、 $10^{18} \text{ cm}^{-3}$  以上の領域は形成されていない)。そのため、MOSFET に逆バイアスが印加されたとき、その低不純物濃度な部分を起点にパンチスルーを起こしやすくなり、耐圧劣化に繋がる懸念がある。そのため、ソース抵抗制御領域 15a の直下の第 1 ウェル領域 20a でも、素子の仕様以上の耐圧を持つように第 2 導電型の不純物濃度を定める必要がある。イオン注入時には、半導体基板 1a は  $100 \sim 800$  で加熱されが好ましいが、過熱されてもよい。また、イオン注入する不純物(ドーパント)は、n 型の不純物としては窒素やリンが好適であり、p 型の不純物としてはアルミニウムや硼素が好適である。

40

#### 【0055】

第 1 ウェル領域 20a の底の深さは、ドリフト層 2 の底を超えないように設定する必要があり、例えは  $0.2 \mu\text{m} \sim 2.0 \mu\text{m}$  程度とする。また、第 1 ウェル領域 20a の最大不純物濃度はドリフト層 2 の不純物濃度を超えるものとし、例えは  $1 \times 10^{15} \text{ cm}^{-3}$

50

$\sim 1 \times 10^{-9} \text{ cm}^{-3}$  の範囲内に設定される。

#### 【0056】

続いて、上記の注入マスク 100a, 100aN を用いた選択的なイオン注入により、第1導電型のソースコンタクト領域 12a と、第1導電型のソースエクステンション領域 12b を形成する。

#### 【0057】

ソースコンタクト領域 12a 及びソースエクステンション領域 12b の底の深さは、第1ウェル領域 20a の底を超えないように設定される。またそれらの不純物濃度は、各領域内で第1ウェル領域 20a の不純物濃度を超えており、例えばその最大不純物濃度は  $1 \times 10^{-8} \text{ cm}^{-3} \sim 1 \times 10^{-2} \text{ cm}^{-3}$  程度に設定される。

10

#### 【0058】

ソースコンタクト領域 12a 及びソースエクステンション領域 12b は、第1ウェル領域 20a とほぼ同じ位置に形成されるが、不純物の注入深さが浅く、横方向散乱による広がりは小さいので、注入マスク 100aN の下で互いに分離される。

#### 【0059】

ここで、ソースコンタクト領域 12a とソースエクステンション領域 12b は、共にソース抵抗制御領域 15a と接続するように形成されるが、注入条件によってはそれらの界面に第2導電型の領域（第1ウェル領域 20a の一部）が残る可能性がある。これを防ぐために、ソースコンタクト領域 12a 及びソースエクステンション領域 12b を形成するイオン注入の直前に、酸素プラズマ処理などによるエッチングにより、注入マスク 100a 及び 100aN を若干トリミングして細らせててもよい。あるいは、トリミング加工をせずに、斜め方向からのイオン注入によりソースコンタクト領域 12a 及びソースエクステンション領域 12b を形成してもよい。これにより、ソースコンタクト領域 12a とソースエクステンション領域 12b をソース抵抗制御領域 15a に確実に接続させることができる。

20

#### 【0060】

図 17 は、窒素を注入エネルギー  $110 \text{ keV}$ 、注入量  $3 \times 10^{-4} \text{ cm}^{-2}$  の条件でイオン注入して形成したソースコンタクト領域 12a 及びソースエクステンション領域 12b における窒素濃度分布の数値計算結果である。また、図 18 は、そのときのドリフト層 2 表面からの深さ  $0.02 \mu\text{m}$  における窒素濃度分布を示している。 $10^{-7} \text{ cm}^{-3}$  台の不純物濃度を有するソースコンタクト領域 12a 及びソースエクステンション領域 12b の間に、ドリフト層 2 の不純物濃度に相当する  $5 \times 10^{-5} \text{ cm}^{-3}$  台の不純物濃度を有するソース抵抗制御領域 15a が形成されていることが分かる。

30

#### 【0061】

特に、炭化珪素における不純物の熱拡散係数はパワー・デバイス用として従来より用いられている珪素における不純物の熱拡散係数に比べて非常に小さく、活性化アニールなどの高温熱処理によっても熱拡散による注入不純物の再分布はほとんど発生せず、注入時の分布をほとんど維持する。従って、図 16 ~ 図 18 に示すような急峻な不純物分布を素子の最終形状として容易に得ることができる。

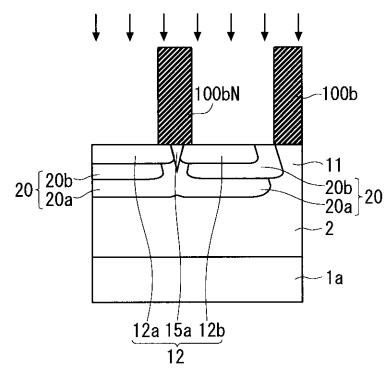

#### 【0062】

40

次に、写真製版処理により加工された注入マスク 100b（レジストまたはシリコン酸化膜）を用いて不純物のイオン注入を行い、第2導電型の第2ウェル領域 20b を形成する。第2ウェル領域 20b は、第1ウェル領域 20a よりも横方向に広い範囲に、ソース抵抗制御領域 15a の部分を避けて形成される。第2ウェル領域 20b において、第1ウェル領域 20a の端部から J F E T 領域 11 側に拡張した部分、すなわちソースエクステンション領域 12b と J F E T 領域 11 との間の部分がチャネル領域となる。

#### 【0063】

第2ウェル領域 20b の最大不純物濃度はドリフト層 2 の表面近傍の不純物濃度を超え、例えば  $1 \times 10^{-5} \text{ cm}^{-3} \sim 1 \times 10^{-9} \text{ cm}^{-3}$  の範囲内に設定される。但し、ドリフト層 2 の最表面近傍に限っては、チャネル領域の導電性を高めるために、第2ウェル

50

領域 20 b の第 2 導電型の不純物濃度がドリフト層 2 の第 1 導電型の不純物濃度を下回るようにしてよい。

#### 【 0 0 6 4 】

第 2 ウェル領域 20 b の底の深さは、ドリフト層 2 の底面を超えない様に設定する必要があり、例えば  $0.2 \mu m \sim 2.0 \mu m$  とする。また、第 2 ウェル領域 20 b の底の深さは、第 1 ウェル領域 20 a の底面に対しては浅くても、同じ深さでも、深くてもよいが、図 12 のように第 1 ウェル領域 20 a より浅い方が好ましい。その場合、MOSFET のオン動作時に JFET 領域 11 端でのドレイン電流広がりの効果を得やすく、オン抵抗の低減に繋がる。また、第 2 ウェル領域 20 b は、ソースコンタクト領域 12 a の下方にも形成しておくことが望ましい。

10

#### 【 0 0 6 5 】

このようにウェル領域 20 における第 2 導電型の不純物濃度を高めることで、そのシート抵抗を低減し、炭化珪素 MOSFET におけるスイッチング動作時の電荷輸送の遅延によるスイッチング損失の増大、信頼性劣化などを抑制することが出来る。

#### 【 0 0 6 6 】

続いて、終端領域（不図示）に第 2 導電型の F LR 領域 50 と、第 1 導電型のフィールドストップ領域 13 をそれぞれ形成する。これらも、写真製版処理により加工したマスク（レジストまたはシリコン酸化膜など）用いた選択的なイオン注入によって形成される。

#### 【 0 0 6 7 】

次に、ウェル領域 20 とソースパッド 41 との間の良好な接続を得るために、第 1 ウェル領域 20 a 及び第 2 ウェル領域 20 b よりも第 2 導電型の不純物濃度が高いウェルコンタクト領域 25 を選択的なイオン注入により形成する。このイオン注入は、150 以上の基板温度で実行されることが望ましい。そうすることで、シート抵抗の低いウェルコンタクト領域 25 を形成できる。ウェルコンタクト領域 25 は、その底が第 2 導電型の第 1 ウェル領域 20 a 又は第 2 ウェル領域 20 b に達するように形成する。

20

#### 【 0 0 6 8 】

また、ウェルコンタクト領域 25 の形成と同時に、終端領域（不図示）のウェルコンタクト領域 25 に第 2 導電型の終端低抵抗領域 28 を形成する。終端低抵抗領域 28 は、ウェルコンタクト領域 25 の寄生抵抗を減少させることができ、例えば  $dV/dt$  耐量の優れた終端領域の構造とすることができます。もちろん、終端低抵抗領域 28 は、ウェルコンタクト領域 25 とは別の工程で形成してもよい。

30

#### 【 0 0 6 9 】

ここで、ドリフト層 2 を形成した際にその表面近傍の不純物濃度を意図的に低くした場合には、JFET 領域 11 における抵抗が増加することが考えられる。そこで、その場合には、JFET 領域 11 に第 1 導電型の不純物をイオン注入することにより、図 13 のように、第 1 導電型の電流制御領域 14 を形成することが望ましい。JFET 領域 11 に電流制御領域 14 を設けることにより、JFET 領域 11 の抵抗の増加が抑えられ、ひいてはさらに減少させることができる。

#### 【 0 0 7 0 】

電流制御領域 14 は、少なくとも JFET 領域 11 内に形成されればよいが、図 13 のように、第 1 ウェル領域 20 a よりも深く、さらに第 1 ウェル領域 20 a の下面の一部を包含するように形成されているとより好ましい。この場合、JFET 領域 11 からドリフト層 2 に広がる、広がり抵抗を低減できる。但し、電流制御領域 14 がソース抵抗制御領域 15 a の下方まで伸びないようにしておくことが、耐圧劣化を抑える上で好ましい。なお、ドリフト層 2 の表面近傍の不純物濃度を低くしていない場合にも、電流制御領域 14 を設けてよい。

40

#### 【 0 0 7 1 】

その後、ドリフト層 2 に注入した不純物を電気的に活性化させるための熱処理を行う。この熱処理は、アルゴン又は窒素等の不活性ガス雰囲気、若しくは、真空中で、1500 ~ 2200 の温度、0.5 分 ~ 60 分の時間で行うとよい。この熱処理時では、ドリ

50

フト層 2 の表面を炭素からなる膜で覆った状態、若しくは、ドリフト層 2 の表面、半導体基板 1 の裏面、並びに半導体基板 1 a 及びドリフト層 2 の各端面を炭素からなる膜で覆った状態で行っても良い。それにより、熱処理時における装置内の残留水分や残留酸素との反応によるエッティングでドリフト層 2 の表面が荒れることを抑止できる。

#### 【 0 0 7 2 】

続いて、熱酸化によりドリフト層 2 の表面にシリコン酸化膜（犠牲酸化膜）を形成し、フッ酸により当該酸化膜の除去することにより、表面の変質層を除去して清浄な面を得る。そして、CVD (Chemical Vapor Deposition) 法などによりドリフト層 2 上にシリコン酸化膜を形成し、当該シリコン酸化膜に対して能動領域 7 上を開口するパターニングを行うことにより、能動領域 7 の外側の領域にフィールド酸化膜 3 1 を形成する。フィールド酸化膜 3 1 の厚さは、0.5 μm ~ 2 μm あればよい。10

#### 【 0 0 7 3 】

次に、ドリフト層 2 の表面上にシリコン酸化膜のゲート絶縁膜 3 0 を形成する。ゲート絶縁膜 3 0 の形成手法としては、例えば、熱酸化法や堆積法が挙げられる。また、熱酸化法や堆積法によりシリコン酸化膜を形成した後に、窒化酸化ガス (NO や N<sub>2</sub>O など) 霧囲気やアンモニア霧囲気での熱処理や、不活性ガス (アルゴンなど) 霧囲気での熱処理を行ってもよい。

#### 【 0 0 7 4 】

そして、ゲート絶縁膜 3 0 上に多結晶シリコンや多結晶炭化珪素を CVD 法により堆積し、写真製版処理及びエッティングによるパターニングを行うことにより、ゲート電極 3 5 を形成する。その結果、図 14 に示す構造が得られる。20

#### 【 0 0 7 5 】

ゲート電極 3 5 に用いる多結晶シリコンや多結晶炭化珪素は、リンや硼素やアルミニュームなどを含み、n 形もしくは p 形の低シート抵抗を有するものであることが望ましい。多結晶シリコンや多結晶炭化珪素に含まれるリンや硼素やアルミニュームは、その成膜中に取り込ませてもよいし、成膜後にイオン注入して活性化熱処理を行ってもよい。さらに、ゲート電極 3 5 の材料は、金属や金属間化合物またはそれらの多層膜であってもよい。

#### 【 0 0 7 6 】

次に、ドリフト層 2 上に CVD 法などによって層間絶縁膜 3 2 を形成する。そして、例えばドライエッティング法により、ソースパッド 4 1 をソースコンタクト領域 1 2 a、ウェルコンタクト領域 2 5 及び終端低抵抗領域 2 8 に接続させるためのコンタクトホール (ソースコンタクトホール) を、層間絶縁膜 3 2 に形成する。また、ゲート配線 4 4 をゲート電極 3 5 に接続させるためのコンタクトホール (ゲートコンタクトホール) をこれと同時に形成してもよい。それにより、プロセス工程が簡略化され、製造コストを削減できる。30

#### 【 0 0 7 7 】

続いて、ソースコンタクトホールの底に露出したドリフト層 2 の表面にオーミック電極 4 0 を形成する。オーミック電極 4 0 は、ソースコンタクト領域 1 2 a、ウェルコンタクト領域 2 5 および終端低抵抗領域 2 8 とのオーミック接触を実現する。オーミック電極 4 0 の形成方法としては、ソースコンタクト内を含むドリフト層 2 の全面に Ni を主成分とする金属膜を成膜し、600 ~ 1100 °C の熱処理により炭化珪素と反応させてオーミック電極 4 0 となるシリサイド膜を形成し、その後、層間絶縁膜 3 2 上に残留した未反応の金属膜を、硝酸、硫酸または塩酸あるいはそれらの過酸化水素水との混合液などを用いたウェットエッティングにより除去する、という方法が挙げられる。層間絶縁膜 3 2 上に残留した金属膜を除去した後に、再度熱処理を行っても良い。この場合は、先の熱処理よりも高温で行うことで、さらに低コンタクト抵抗なオーミック接触が形成される。40

#### 【 0 0 7 8 】

なお、先の工程でゲートコンタクトホールが形成されていれば、ゲートコンタクトホール底にもシリサイドからなるオーミック電極が形成される。先の工程でゲートコンタクトホールが形成されていなければ、引き継いで写真製版処理とエッティングによって、ゲート配線 4 4 によりその後に充填されるべきゲートコンタクトホールを形成する。50

## 【0079】

オーミック電極40は、その全体が同一の金属間化合物からなっていてもよいし、p型領域に接続する部分とn型領域に接続する部分とが、それぞれに適した別々の金属間化合物からなっていてもよい。オーミック電極40が第1導電型のソースコンタクト領域12aに対して十分低いオーミックコンタクト抵抗を有することがMOSFETのオン抵抗低減に重要である。一方、オーミック電極40が第2導電型のウェルコンタクト領域25に対して充分低いオーミックコンタクト抵抗を有することは、ウェル領域20のアース電位への固定や、MOSFETに内蔵されるボディーダイオードの順方向特性改善の観点から好ましい。オーミック電極40においてp型領域に接続する部分とn型領域に接続する部分を作り分けることにより、この両方を実現できる。これは、写真製版処理を用いて、シリサイド膜を形成するための金属膜のパターニングをそれぞれで行うことで実現可能である。10

## 【0080】

また、ドリフト層2上にオーミック電極40を形成する過程で、半導体基板1の裏面にも同様の手法で、オーミック電極42となるシリサイド膜を形成する。オーミック電極42は半導体基板1aにオーミック接触し、この後形成するドレイン電極43と半導体基板1aとの間で良好な接続を実現する。

## 【0081】

続いて、スパッタ法や蒸着法により所定の金属膜を形成し、それをパターニングすることによって、層間絶縁膜32上にソースパッド41、ゲート配線44およびゲートパッド45を形成する。上記金属膜としては、Al、Ag、Cu、Ti、Ni、Mo、W、Ta、それらの窒化物、それらの積層膜、それらの合金膜などが考えられる。さらに、半導体基板1aの裏面のオーミック電極42上に、Ti、Ni、AgまたはAuなどの金属膜を形成してドレイン電極43を形成することにより、図15に示される構成のMOSFETが完成する。20

## 【0082】

図示は省略するが、形成されたMOSFET上は、シリコン窒化膜やポリイミドなどの保護膜で覆っていてもよい。この保護膜には、ゲートパッド45及びソースパッド41上に開口が設けられ、ゲートパッド45及びソースパッド41と外部の制御回路とが接続可能なようにされる。30

## 【0083】

さらに、保護膜を形成した後に、半導体基板1aを裏面側から研削して100μm程度の厚みまで薄板化してもよい。この場合は、薄板化後に研削面の清浄化を行い、裏面全面にNiを主とした金属膜を成膜した後に、レーザーアニールなどの局所加熱法によって半導体基板1aの裏面にシリサイド膜を形成することで、オーミック電極42を形成する。そして上記の工程と同様に、オーミック電極42上に、TiやNiやAgやAuなどの金属膜から成るドレイン電極43を形成する。

## 【0084】

本実施の形態では、本発明が適用される半導体装置の例として、MOSFETを示したが、半導体基板1aの導電型を第2導電型に変更した構造を持つIGBTに対しても適用可能である。IGBTにおいては、ソース領域12は「エミッタ領域」、ウェル領域20は「ベース領域」、半導体基板1aは「コレクタ領域」となる。エミッタ領域(ソース領域12)内に、高抵抗な抵抗制御領域(ソース抵抗制御領域15a)を設けることにより、エミッタ抵抗を高くすることができるため、エミッタ領域(ソース領域12)、ベース領域(ウェル領域20)およびドリフト層2からなる寄生トランジスタにおける電流利得を小さくすることができ、その結果、IGBTの寄生サイリスタが動作することによるラッチアップを防止できるという効果が得られる。40

## 【0085】

実施の形態1によれば、ウェル領域20のチャネル領域から、オーミック電極40及びソース電極41に至る経路に、ソースコンタクト領域12aおよびソースエクステンション50

ン領域 12 b よりも低い不純物濃度（ドリフト層 2 と同程度の不純物濃度）のソース抵抗制御領域 15 a が直列に挿入されるので、素子のオン抵抗に影響を及ぼすほどの実効的なソース抵抗にすることができ、特に高温での抵抗増加率が大きいという効果が得られる。

#### 【 0 0 8 6 】

短絡耐量の大きさに影響を及ぼすドレイン飽和電流は、チャネルに印加されるゲート／ソース間電圧の 2 乗に比例するが、本発明のように有意なソース抵抗が存在する場合、実効的なゲート／ソース間電圧は、ソース抵抗とドレイン電流の積の分だけ減じたものとなる。そのため、ソース抵抗を大きくすれば、飽和電流は小さくなり、短絡耐量を高くできる。

#### 【 0 0 8 7 】

しかし、ソース抵抗を過大に大きくすると、定格のオン動作時における導通損失を増大させることになり好ましくない。さらに、従来の M O S F E T のように、ソース領域における第 1 導電型の不純物濃度が横方向に略一様である場合、ソース抵抗を高くすると、ソース領域とソースパッド（オーミック電極）とのコンタクト抵抗が増大することになり、素子の損失がさらに増大する。本発明では、ソースパッド 41 に接続するオーミック電極 40 は、低抵抗なソースコンタクト領域 12 a にのみ接触し、高抵抗なソース抵抗制御領域 15 とは接触しない。よって、オーミック電極 40 とソース領域 12 とのコンタクト抵抗を低く維持される。従って、オン抵抗の過大な増大を抑えつつ、飽和電流が小さくなるようにソース抵抗を設計することができる。

#### 【 0 0 8 8 】

また、ソース抵抗制御領域 15 a における伝導キャリア（電子または正孔）の移動度は、格子散乱の影響を強く受けて高温ほど低くなることが知られている。すなわち、高温ほど電気抵抗は大きくなる。ソース抵抗制御領域 15 a は、ソースコンタクト領域 12 a 及びソースエクステンション領域 12 b よりも第 1 導電型の不純物濃度が低いので、高温での電気抵抗の増加率はそれよりも大きい。

#### 【 0 0 8 9 】

発明者らの実験によれば、 $1 \times 10^{19} \text{ cm}^{-3}$  程度の n 型の不純物濃度を有する炭化珪素層の抵抗は、温度の約 0.6 乗に比例して増加する一方、 $5 \times 10^{15} \text{ cm}^{-3}$  程度の n 型の不純物濃度を有する炭化珪素層の抵抗は、温度の約 2.7 乗に比例して増加する結果を得た。すなわち、前者はソースエクステンション領域 12 b やソースコンタクト領域 12 a を想定した不純物濃度、後者はソース抵抗制御領域 15 a やドリフト層 2 を想定した不純物濃度である。炭化珪素半導体では、ドナーやアクセプタの活性化エネルギーが大きいために、電子（正孔）濃度は温度と共に増加するため、抵抗の温度依存性は高ドナー（アクセプタ）濃度ほど小さくなると考えられる。

#### 【 0 0 9 0 】

一方、素子短絡時には、高ドレイン電流による発熱（ジュール熱）によって破壊直前には 1000 K にも及ぶことを本発明者らは確認している。

#### 【 0 0 9 1 】

本発明では、ソース抵抗制御領域 15 a がドリフト層 2 と同じ（ドリフト層 2 の表面近傍で不純物濃度を意図的に低くした場合はドリフト層 2 よりも低い）第 1 導電型の不純物濃度を有するため、ソース抵抗制御領域 15 a の抵抗の温度依存性が大きい。そのため、高温になるにつれてソース抵抗制御領域 15 a の抵抗が大きくなり（例えば温度の 2.7 乗に比例する場合、1000 K での抵抗は室温時の 28 倍の抵抗になる）、チャネル領域に印加される実効的なゲート電圧が徐々に減少してドレイン電流を低減させる、いわば負帰還の機能が働く。従って、1000 K 程度まで温度上昇するまでの時間を伸ばすことができ、短絡耐量を大幅に向上できる。

#### 【 0 0 9 2 】

また、実施の形態 1 におけるソース抵抗制御領域 15 a には不純物、特に第 2 導電型の不純物が直接的に注入されておらず、横方向散乱によって非常に少ない量が浸入している程度である。

10

20

30

40

50

**【0093】**

実効的な第1導電型の不純物濃度を下げるには、第2導電型の不純物を注入して補償する手法が考えられる。しかし、例えばドリフト層2として想定する $1 \times 10^{-3} \text{ cm}^{-3}$ ～ $1 \times 10^{-7} \text{ cm}^{-3}$ 程度の第1導電型の不純物濃度に対して、第2導電型の不純物を注入して第1導電型の実効不純物濃度を大きく減することは、注入種の活性化率や深さ方向分布、極めて低いドーズ量の注入制御などの課題があり極めて困難である。

**【0094】**

それに対し、実施の形態1では、ソース抵抗制御領域15aをエピタキシャル成長時の層（領域）をそのまま用いることにより、ソースエクステンション領域12bやソースコンタクト領域12aにおける第1導電型の不純物濃度よりも、十分小さく設定することができる。10

**【0095】**

さらに、ソース抵抗制御領域15aには直接的な注入による結晶へのダメージや注入欠陥が存在せず（または非常に少なく）、せいぜい非常に少ない量が横方向散乱によって若干浸入しているのみであるため、ドリフト層2と同様な温度感度を持つ層が得られる一方、短絡などの過電流が印加されたときの高電流ストレスや熱ストレスなどに対する結晶としてのロバスト性が維持され、信頼性の高い素子を実現することが可能となる。

**【0096】**

以上のように、実施の形態1に係る半導体装置によれば、ソース領域12が、ソースパッド41に接続するオーミック電極40に接触するソースコンタクト領域12aと、チャネル領域に隣接するソースエクステンション領域12bと、その間のソース抵抗制御領域15aとが直列に接続した構造を有するため、ソース抵抗制御領域15aのシート抵抗に応じたソース抵抗によって、飽和電流を制御することができる。ソース抵抗制御領域15aは、不純物のイオン注入が直接的になされていないドリフト層表面の一部からなっているため、負荷短絡時などの高温環境下における抵抗増加が大きくなり、実効的なゲート電圧が減少して飽和電流が減少することで、短絡耐量が増加する。20

**【0097】**

また、ドリフト層2の表層部において、第1導電型の不純物濃度を低くすると、ソース抵抗制御領域15aにおける第1導電型の不純物濃度がさらに減少するために、上記の効果が大きくなる。30

**【0098】**

さらに、図13に示したように、JFET領域11にドリフト層2よりも第1導電型の不純物濃度が高い電流制御領域14を形成すれば、上記の効果を得ながら、JFET領域11の抵抗を減少させることができる。

**【0099】**

また、ソース抵抗制御領域15aは、ソースエクステンション領域12bからソースコンタクト領域12aに向かう方向の距離がユニットセル10で均一であるので、ユニットセル10内における電流分布及び負荷短絡時における発熱分布が一様となり、負荷短絡時などの発熱を伴う素子破壊に対する信頼性が向上する。

**【0100】**

また、本実施の形態では、ソース抵抗制御領域15aの長さ、すなわち、ソースコンタクト領域12aからソースエクステンション領域12bまでの長さ（図10の注入マスク100aNの幅 $L_{N0}$ ）を $0.1 \sim 0.5 \mu\text{m}$ に設定し、第1ウェル領域20aを形成する第2導電型のイオン注入を、ソース抵抗制御領域15aの形成領域上に形成した注入マスク100aNを用いて行った。このイオン注入時の注入種の横方向散乱によって、第1ウェル領域20aを、上層部にソース抵抗制御領域15aを残存させつつ、一体的に形成することができる。40

**【0101】**

さらに、本実施の形態では、ソース抵抗制御領域15a内の第1導電型の不純物濃度を、ソースエクステンション領域12bまたはソースコンタクト領域12a内の第1導電型50

の最大不純物濃度よりも3桁以上小さく(1/1000以下に)している。より具体的には、ソース抵抗制御領域15aにおける第1導電型の不純物濃度を $1 \times 10^{-3} \text{ cm}^{-3}$ ～ $1 \times 10^{-7} \text{ cm}^{-3}$ とした。これにより、負荷短絡時などの高温環境下におけるソース抵抗制御領域15aの抵抗増加が大きくなることで実効的なゲート電圧が減少して飽和電流が減少することで、短絡耐量が増加する。

#### 【0102】

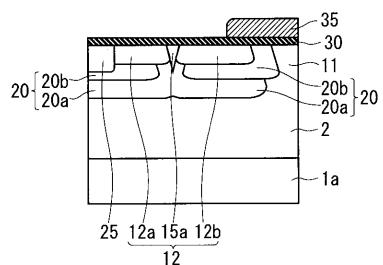

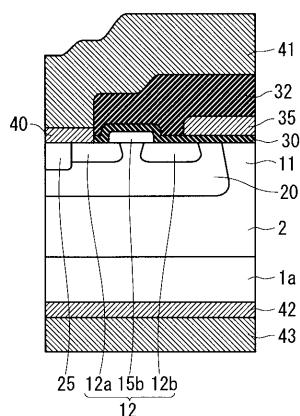

<実施の形態2>

図19は、実施の形態2に係る半導体装置である炭化珪素MOSFETの構成を示す縦断面図である。なお、当該半導体装置のチップ5の全体構造は、図1及び図2に示したものと同様であり、図19は図1のA1-A2線に沿った断面に対応している。ここで、図19において、図3に示したものと同様の機能を有する要素には同一符号を付してあるので、ここではそれらの説明は省略する。10

#### 【0103】

実施の形態2に係るMOSFETにおいても、ソース領域12は、ソースコンタクト領域12aと、ソースエクステンション領域12bと、その間に接続し、イオン注入がなされていないソース抵抗制御領域15bとの3つの領域から構成される。但し、図19に示すように、ソース抵抗制御領域15bは、ドリフト層2の内部ではなく、ドリフト層2の表面上に形成されている。

#### 【0104】

また、実施の形態2では、ウェル領域20は単一の領域(1回の写真製版およびイオン注入で形成される領域)で構成されている。20

#### 【0105】

ソース抵抗制御領域15bは、ドリフト層2の表面上に、炭化珪素半導体をエピタキシャル成長させ、それをパターニングして形成したものである。ソース抵抗制御領域15bをドリフト層2上に配設することで、ソース抵抗制御領域15bの長さ( $L_{N0}$ )及び第1導電型の不純物濃度を他の領域(例えば第1ウェル領域20a)とは独立して設定することができる。

#### 【0106】

実施の形態2に係る半導体装置(炭化珪素MOSFET)の製造方法を説明する。図20～図23は当該製造方法を説明するための工程図である。図20～図23は、能動領域7内に複数配設されたユニットセル10のうちの一つの右側半分の縦断面に相当する。つまり、図20～図23は終端領域を含んでおらず、能動領域7内の領域の任意の位置の断面(図1のB1-B2線に沿った断面)を示している。30

#### 【0107】

まず、実施の形態1と同様に、半導体基板1aを用意してその上にドリフト層2を形成する。そしてドリフト層2に対して、写真製版処理により加工された注入マスク(レジストまたはシリコン酸化膜)を用いて、不純物を選択的にイオン注入し、第2導電型のウェル領域20を形成する。このとき終端領域の終端ウェル領域21も同時に形成する。

#### 【0108】

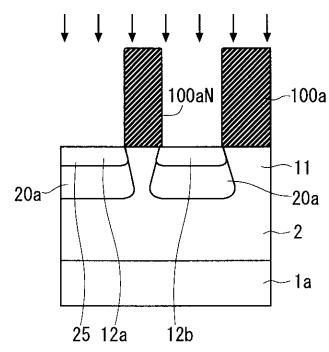

続いて、図20に示すように、ソースコンタクト領域12a及びソースエクステンション領域12bの形成領域を開口した注入マスク100aN及び100aNを用いて、不純物を選択的にイオン注入し、第1導電型のソースコンタクト領域12a及び第1導電型のソースエクステンション領域12bを形成する。このとき終端領域のフィールドストップ領域13も同時に形成する。40

#### 【0109】

ソースコンタクト領域12aの形成領域とソースエクステンション領域12bの形成領域との間に形成された注入マスク100aNの幅が、その後に形成されるソース抵抗制御領域15bの実質的な長さ( $L_{N0}$ )となる。

#### 【0110】

続いて、写真製版処理により加工されたレジストマスクまたはシリコン酸化膜マスクな50

どを用いて、不純物の選択的なイオン注入を行い、終端領域に第2導電型のF L R領域50を形成する。

#### 【0111】

同様に、注入マスクを用いた選択的なイオン注入により、第2導電型の不純物濃度を有するウェルコンタクト領域25を、ソースコンタクト領域12aを貫通するように形成する。またそれと同時に終端低抵抗領域28を形成する。

#### 【0112】

その後、ドリフト層2に注入した不純物を電気的に活性化させるための熱処理を行う。この熱処理は、アルゴン又は窒素等の不活性ガス雰囲気、若しくは、真空中で、1500～2200の温度、0.5分～60分の時間で行うとよい。

10

#### 【0113】

次に、ドリフト層2表面を清浄化させたのちに、ドリフト層2上に第1導電型の炭化珪素をエピタキシャル成長させる。形成する炭化珪素層（以下「エピタキシャル成長層」と称す）の膜厚は0.05μmから1μmあればよく、第1導電型の不純物濃度は例えば $1 \times 10^{13} \text{ cm}^{-3}$ ～ $1 \times 10^{17} \text{ cm}^{-3}$ 程度とする。但し、エピタキシャル成長層がウェル領域20との間で形成するp n接合により、当該エピタキシャル成長層の厚さ全体が空乏化しないように、その膜厚と第1導電型の不純物濃度を設定する必要がある。

#### 【0114】

そして、写真製版処理により加工されたレジストマスクを用いたエッチングにより、ドリフト層2上のエピタキシャル成長層をパターニングして、ソース抵抗制御領域15bを形成する。図21に示すように、ソース抵抗制御領域15bは、ソースコンタクト領域12aとソースエクステンション領域12bとの間に直列に接続するように、ソースコンタクト領域12aとソースエクステンション領域12bとを跨ぐように配設される。つまり、ソース抵抗制御領域15bは、ソースコンタクト領域12a及びソースエクステンション領域12bとそれぞれオーバーラップして接しており、ソース領域12の一部として電流経路を形成する。

20

#### 【0115】

またソース抵抗制御領域15b（エピタキシャル成長層）は、ウェル領域20との間で形成するp n接合によりその厚さ全体が空乏化されない程度の第1導電型の不純物濃度に設定される。ソース抵抗制御領域15bの厚さ全体に空乏層が形成されて、空乏層によってソース抵抗制御領域15bがソースコンタクト領域12a側とソースエクステンション領域12b側とに分断されると、オン抵抗が過度に増加するため好ましくない。

30

#### 【0116】

その後は、実施の形態1と同様の手法で、ゲート絶縁膜30及びゲート電極35を形成し（図22）、さらに層間絶縁膜32、オーミック電極40, 42、ソースパッド41およびドレイン電極43を形成することにより、図23に示されるMOSFETの構成が完成する。

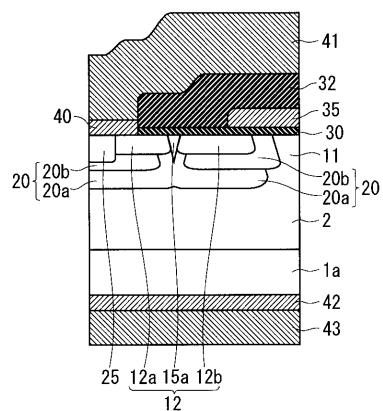

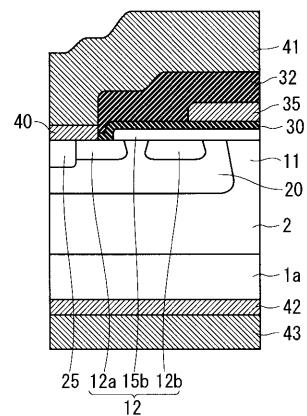

#### 【0117】

なお、ソース抵抗制御領域15bのパターニング工程において、図24に示すように、ソース抵抗制御領域15bをチャネル領域およびJ F E T領域にまで延在させてもよい。図25はその場合のMOSFETの構造を示している。

40

#### 【0118】

第1導電型のソース抵抗制御領域15bが、チャネル領域及びJ F E T領域11上に形成された場合、チャネルが形成される場所はウェル領域20内ではなく、その上のソース抵抗制御領域15b（エピタキシャル成長層）になる。ソース抵抗制御領域15bは、エッチングやイオン注入によるダメージが無いため、良質なチャネルが形成され、MOSFETの信頼性を向上させることができる。

#### 【0119】

実施の形態2においては、ソース抵抗制御領域15bをドリフト層2上に形成するため、ソース抵抗制御領域15bの実質的な長さ（L<sub>N0</sub>）及び第1導電型の不純物濃度を他

50

の領域形成とは独立に設定することができる。ソース抵抗制御領域 15 b をドリフト層 2 よりも低い不純物濃度にすれば、抵抗値の温度依存性がさらに大きくなり、短絡耐量をより高めることができる。

#### 【 0 1 2 0 】

また、ウェル領域 20 は、1 回の写真製版と注入処理で形成することができ、また、実施の形態 1 とは異なりイオン注入時の横方向散乱を考慮する必要がない。よって、横方向散乱長が短くなるような低加速エネルギーでのイオン注入によってウェル領域 20 を形成可能となる。これは、主接合の浅接合化による J F E T 抵抗の低減効果を奏する。

#### 【 0 1 2 1 】

また実施の形態 2 においても、ウェル領域 20 のチャネル領域から、オーミック電極 40 及びソース電極 41 に至る経路に、ソースコンタクト領域 12 a およびソースエクステンション領域 12 b よりも低い不純物濃度のソース抵抗制御領域 15 b が直列に挿入されるので、素子のオン抵抗に影響を及ぼすほどの実効的なソース抵抗にすることができ、特に高温での抵抗増加率が大きいという効果が得られる。

#### 【 0 1 2 2 】

また、上記したように、ソース抵抗制御領域 15 b は、エッチングやイオン注入によるダメージを受けていないので、良質なチャネルを形成することができ、半導体装置の信頼性を向上させることができる。

#### 【 0 1 2 3 】

さらに、ソース抵抗制御領域 15 b は、ウェル領域 20 との p n 接合による空乏層で領域が分断されない程度の第 1 導電型の不純物濃度を有するので、オン抵抗の過度の増加を招かない。

#### 【 0 1 2 4 】

また本実施の形態では、ソース抵抗制御領域 15 b 内の第 1 導電型の不純物濃度を、 $1 \times 10^{13} \text{ cm}^{-3}$  ~  $1 \times 10^{17} \text{ cm}^{-3}$  とし、ソース抵抗制御領域 15 b の長さは、 $0.1 \sim 1.0 \mu\text{m}$  の範囲とした。これにより、負荷短絡時などの高温環境下におけるソース抵抗制御領域 15 a の抵抗増加が大きくなることで実効的なゲート電圧が減少して飽和電流が減少することで、短絡耐量が増加する。

#### 【 0 1 2 5 】

なお、上記の実施の形態 1, 2 に示した半導体装置の構造から得られる効果は、その構造を有する限り、他の製造方法で形成されたとしても同様に得られる。また、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

#### 【 符号の説明 】

#### 【 0 1 2 6 】

1 a 半導体基板、2 ドリフト層、5 チップ、7 能動領域、10 ユニットセル、11 J F E T 領域、12 ソース領域、12 a ソースコンタクト領域、12 b ソースエクステンション領域、13 フィールドストップ領域、14 電流制御領域、15 a, 15 b ソース抵抗制御領域、20 ウェル領域、20 a 第 1 ウェル領域、20 b 第 2 ウェル領域、21 終端ウェル領域、21 a 第 1 ウェル領域、22 b 第 2 ウェル領域、23 ウェルブリッジ領域、25 ウェルコンタクト領域、28 終端低抵抗領域、30 ゲート絶縁膜、31 フィールド酸化膜、32 層間絶縁膜、35 ゲート電極、40 オーミック電極、42 オーミック電極、41 ソースパッド、43 ドレン電極、44 ゲート配線、45 ゲートパッド、50 F L R 領域、100 a, 100 a N, 100 b 注入マスク。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図11】

【図13】

【図14】

【図18】

【図15】

【図19】

【図20】

【図21】

【図22】

【図24】

【図23】

【図25】

【図16】

【図17】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 2 F |

| H 01 L | 29/78 | 6 5 2 S |

| H 01 L | 29/78 | 6 5 8 E |

| H 01 L | 29/78 | 6 5 2 J |

(72)発明者 古川 彰彦

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 阿部 雄次

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 中田 修平

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 今泉 昌之

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

審査官 小川 将之

(56)参考文献 特開平02-106073 (JP, A)

特表2006-509355 (JP, A)

特開平05-211294 (JP, A)

特開昭60-229373 (JP, A)

特開昭57-042164 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 21 / 336

H 01 L 29 / 12