(12)

## Patentschrift

(21) Aktenzeichen: **10 2017 223 241.2**

(51) Int Cl.: **H03K 19/0185** (2006.01)

(22) Anmeldetag: **19.12.2017**

(43) Offenlegungstag: **31.10.2018**

(45) Veröffentlichungstag der Patenterteilung: **19.12.2024**

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

|                                                                                     |            |    |                                                                                            |

|-------------------------------------------------------------------------------------|------------|----|--------------------------------------------------------------------------------------------|

| (30) Unionspriorität:<br><b>2017-087490</b>                                         | 26.04.2017 | JP | (72) Erfinder:<br><b>Yoshida, Hiroshi, Fukuoka-shi, Fukuoka, JP</b>                        |

| (73) Patentinhaber:<br><b>Mitsubishi Electric Corporation, Tokyo, JP</b>            |            |    | (56) Ermittelter Stand der Technik:<br><b>JP 3 838 083 B2</b><br><b>JP 2010- 161 753 A</b> |

| (74) Vertreter:<br><b>Hoefer &amp; Partner Patentanwälte mbB, 81543 München, DE</b> |            |    |                                                                                            |

(54) Bezeichnung: HOCHSPANNUNGS-PEGELVERSCHIEBUNGSSCHALTUNG UND TREIBERVORRICHTUNG

(57) Hauptanspruch: Hochspannungs-Pegelverschiebungsschaltung umfassend:

ein Gate-Potential der ersten PMOS-Stromspiegelschaltung (CM1) angesteuert wird.

- einen ersten hochspannungsfesten NMOS-Transistor (T1), der durch einen Ein-Befehl angesteuert wird;

- einen zweiten hochspannungsfesten NMOS-Transistor (T2), der durch einen Aus-Befehl angesteuert wird;

- eine erste PMOS-Stromspiegelschaltung (CM1), die einen Drain-Strom des ersten hochspannungsfesten NMOS-Transistors (T1) in eine Referenzseite einspeist;

- eine zweite PMOS-Stromspiegelschaltung (CM2), die einen Drain-Strom des zweiten hochspannungsfesten NMOS-Transistors (T2) in eine Referenzseite einspeist;

- eine erste NMOS-Stromspiegelschaltung (CM3), die einen Ausgangsstrom der zweiten PMOS-Stromspiegelschaltung (CM2) in eine Referenzseite einspeist;

- eine I/V-Signalwandlungsschaltung (1), die einen Ausgang der ersten PMOS-Stromspiegelschaltung (CM1) und einen Ausgang der ersten NMOS-Stromspiegelschaltung (CM3) aufnimmt, um ein Ausgangs-Steuerspannungssignal zu erhalten;

- einen ersten PMOS-Transistor (PMOS10), der parallel zu einer Source und einem Drain eines PMOS-Transistors einer Referenzseite der ersten PMOS-Stromspiegelschaltung (CM1) geschaltet ist; und

- einen zweiten PMOS-Transistor (PMOS11), der parallel zu einer Source und einem Drain eines PMOS-Transistors einer Referenzseite der zweiten PMOS-Stromspiegelschaltung (CM2) geschaltet ist,

- wobei ein Gate des ersten PMOS-Transistors (PMOS10) durch ein Gate-Potential der zweiten PMOS-Stromspiegelschaltung (CM2) angesteuert wird, und

- ein Gate des zweiten PMOS-Transistors (PMOS11) durch

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft eine Treibervorrichtung, die eine Leistungsvorrichtung wie einen IGBT oder einen MOSFET ansteuert, und eine Hochspannungs-Pegelverschiebungsschaltung, die für die Treibervorrichtung verwendet wird.

### Hintergrund

**[0002]** Aus der JP 3 838 083 B2 ist eine Pegelverschiebungsschaltung bekannt.

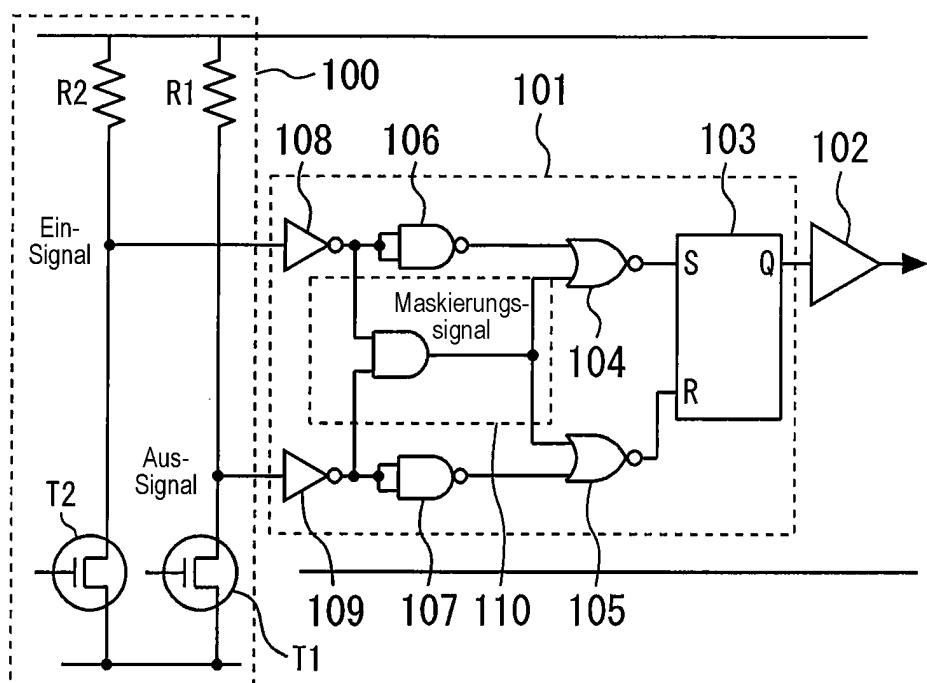

**[0003]** **Fig. 9** ist ein Diagramm, das eine herkömmliche Treiberschaltung veranschaulicht. Die Treiberschaltung verfügt über eine Hochspannungs-Pegelverschiebungsschaltung 100, eine Übertragungsschaltung 101 und eine Treiberschaltung 102. Die Hochspannungs-Pegelverschiebungsschaltung 100 umfasst die Widerstände R1 und R2 und die hochspannungsfesten Feldeffekttransistoren (im Folgenden als „HMOS-Transistoren“ bezeichnet) T1 und T2. Die Übertragungsschaltung 101 umfasst ein RS-Typ Flip-Flop 103, die NOR-Gatter 104 und 105, die NAND-Gatter 106 und 107, die I/V-Signalwandlungsschaltungs-Gatter 108 und 109, und eine Maskierungssignalschaltung 110, die aus einem AND-Gatter besteht. Die Treiberschaltung 102 ist mit einer Leistungsvorrichtung verbunden und steuert die Leistungsvorrichtung durch ihr Ausgangssignal an.

**[0004]** Ein Signal einer Hochpotentialseite wird in die Hochspannungs-Pegelverschiebungsschaltung 100 zur Steuerung einer Ein/Aus-Operation der Leistungsvorrichtung eingespeist. Das Signal der Hochpotentialseite ist ein gepulstes Signal, das in T1 und T2 der Hochspannungs-Pegelverschiebungsschaltung 100 eingespeist und zu einem Hochpotential-pegelverschoben wird. Das pegelverschobene Ein-Signal oder Aus-Signal wird über die Übertragungsschaltung 101 von der Treiberschaltung 102 zur Leistungsvorrichtung übertragen.

**[0005]** Allgemein ist eine Last einer Leistungsvorrichtung, die mittels einer Treiberschaltung angesteuert wird, oft eine induktive Last wie ein Motor. Unter Einflüssen einer parasitären Induktivitätskomponente aufgrund einer induktiven Last durch Leitungen einer Leiterplatte oder dergleichen, schwankt ein Referenzpotential VS der Hochpotentialseite zum Schaltzeitpunkt zu einer negativen Seite in Bezug zu einer Masse GND einer Niedrigpotentialseite. Das Signal der Hochpotentialseite wird zu einem Fehlersignal, wenn die Referenz der Hochpotentialseite, die zur negativen Seite hin schwankt, zu einer Referenz der Niedrigpotentialseite zurückgesetzt wird. Des Weiteren kann dieses Fehlersignal auch durch  $dV/dt$  erzeugt werden, wenn das Referenzpo-

tential der Hochpotentialseite von einem niedrigen Potential zu einem hohen Potential übergeht.

**[0006]** Das Fehlersignal veranlasst einen Strom in die Pegelverschiebungswiderstände R1 und R2 zu fließen, die über die parasitären Kapazitäten oder parasitären Dioden des T1 und des T2 mit einer Spannungsversorgung der Hochpotentialseite verbunden sind. Dies verursacht einen Spannungsabfall und veranlasst eine Übertragung des Fehlersignals in die Übertragungsschaltung 101 in der Folgestufe, was eine Fehlfunktion der Leistungsvorrichtung hervorrufen kann.

**[0007]** Als eine Gegenmaßnahme für diese Fehlfunktion wird in einer herkömmlichen Treiberschaltung eine Logik-Filter-Anordnung eingesetzt. D.h., es wird eine Maskierungssignalschaltung 110 bereitgestellt, die ein Signal zur Aufhebung eines Fehlersignals erzeugt. Genauer erzeugt die Maskierungssignalschaltung 110 ein Maskierungssignal zur Maskierung dieser Signale, wenn sowohl ein Ein-Signal, als auch ein Aus-Signal aktiv werden, so dass sie nicht zum RS-Typ Flip-Flop 103 übertragen werden. Dieses Maskierungssignal wird eingesetzt, um Hauptsignale zu maskieren, die von den NAND-Gattern 106 und 107 ausgegeben werden. Zu diesem Zeitpunkt kann, wenn eine Schwankung in jedem der Operationsbereiche eintritt, ein Fehlersignal zur Übertragungsschaltung 101 in der folgenden Stufe übertragen werden, obwohl das Hauptsignal und das Maskierungssignal auf den gleichen Operationsbereich eingestellt sind.

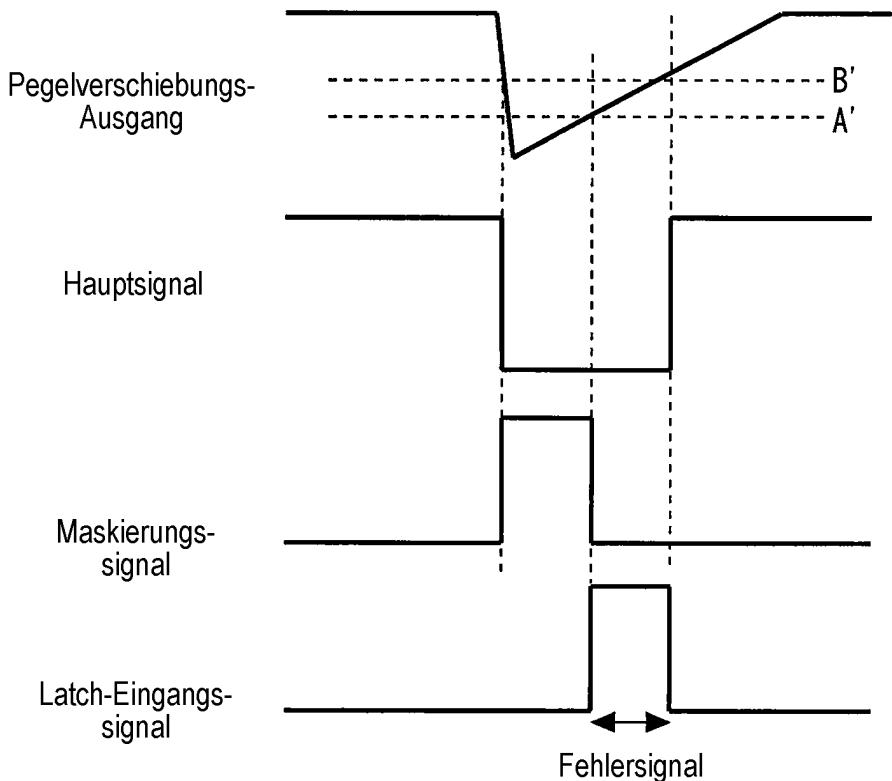

**[0008]** **Fig. 10** ist ein Zeitdiagramm, das den Betrieb einer herkömmlichen Treiberschaltung veranschaulicht. Es wird hier ein Fall angenommen, in dem ein Ein-Signal oder ein Aus-Signal, welches ein Ausgang der Hochspannungs-Pegelverschiebungsschaltung 100 ist, abrupt unter dem Einfluss von  $dV/dt$  oder dergleichen abfällt und eine Schwelle des NAND-Gatters 106 oder 107 aufgrund einer Schwankung oder dergleichen unterschiedlich zu einer Schwelle der Maskierungssignalschaltung 110 ist. Die Schwelle der NAND-Gatter 106 oder 107 wird durch eine gestrichelte Linie B' gezeigt und die Schwelle des AND-Gatters der Maskierungssignalschaltung 110 wird durch eine gestrichelte Linie A' gezeigt. In diesem Fall ist ein Bereich, in dem das Maskierungssignal aktiv (high) ist, schmäler, als ein Bereich, in dem das Hauptsignal aufgrund einer Störung inaktiv (low) wird. Aus diesem Grund wird das Fehlersignal, welches das Hauptsignal ist, das fälschlicherweise inaktiviert wird, nicht ausreichend maskiert. Somit wird ein Fehlersignal in einem Latch-Eingangssignal erzeugt, das ein Set-Eingangssignal des RS-Typ Flip-Flops 103 ist.

**[0009]** Demgegenüber ist eine Pegelverschiebungsschaltung offenbart (siehe z.B.

JP 2010-161753 A), die einen stabilen Betrieb zur Verfügung stellt. Zusätzlich jedoch zu einem HVN MOS, der einen Verschiebungsstrom erzeugt, wird für einen stabilen Betrieb ein Strom durch eine weitere Konstantstromquelle veranlasst stationär in eine Pegelverschiebungsschaltung zu fließen.

### Zusammenfassung

**[0010]** In dem Fall, in dem eine Pegelverschiebung in einem Hochspannungssystem wie einem 600-V oder 1200-V System durchgeführt wird, muss ein Strom, der an einer Hochspannungs-Pegelumsetzung beteiligt ist, auf das Äußerste unterbunden werden, um einen Heizwert zu reduzieren. Deshalb gibt es einen Bedarf für eine Hochspannungs-Pegelverschiebungsschaltung, die einen Strom ohne den Einsatz einer separaten Konstantstromquelle reduziert, die im Stand der Technik unverzichtbar wäre.

**[0011]** Die vorliegende Erfindung wurde umgesetzt, um das oben beschriebene Problem zu lösen und es ist eine Aufgabe der vorliegenden Erfindung eine Hochspannungs-Pegelverschiebungsschaltung und eine Treiberschaltung bereitzustellen, die in der Lage sind, einen Strom zu reduzieren, während die Übertragung eines Fehlersignals verhindert wird.

**[0012]** Die Lösung dieser Aufgabe erfolgt durch die Merkmale des unabhängigen Anspruchs. Die Untersprüche haben vorteilhafte Ausgestaltungen der Erfindung zum Inhalt.

**[0013]** Gemäß Aspekten der vorliegenden Erfindung umfasst eine Hochspannungs-Pegelverschiebungsschaltung: einen ersten hochspannungsfesten NMOS-Transistor, der durch einen Ein-Befehl angesteuert wird; einen zweiten hochspannungsfesten NMOS-Transistor, der durch einen Aus-Befehl angesteuert wird; eine erste PMOS-Stromspiegelschaltung, die einen Drain-Strom des ersten hochspannungsfesten NMOS-Transistors in eine Referenzseite einspeist; eine zweite PMOS-Stromspiegelschaltung, die einen Drain-Strom des zweiten hochspannungsfesten NMOS-Transistors in eine Referenzseite einspeist; eine erste NMOS-Stromspiegelschaltung, die einen Ausgangsstrom der zweiten PMOS-Stromspiegelschaltung in eine Referenzseite einspeist; und eine I/V-Signalwandlungsschaltung, die einen Ausgang der ersten PMOS-Stromspiegelschaltung und einen Ausgang der ersten NMOS-Stromspiegelschaltung aufnimmt, um ein Ausgangs-Steuerspannungssignal zu erhalten.

**[0014]** In der vorliegenden Erfindung speisen die erste und die zweite PMOS-Stromspiegelschaltung jeweils die Drain-Ströme der ersten und der zweiten hochspannungsfesten NMOS-Transistoren in die Referenzseite ein, die erste NMOS-Stromspiegelschaltung speist den Ausgangsstrom der zweiten

PMOS-Stromspiegelschaltung in die Referenzseite ein, und die I/V-Signalwandlungsschaltung nimmt den Ausgang der ersten PMOS-Stromspiegelschaltung und den Ausgang der ersten NMOS-Stromspiegelschaltung auf, um das Ausgangs-Steuerspannungssignal zu erhalten. Dies erlaubt es, einen Strom zu reduzieren, während die Übertragung eines Fehlersignals verhindert wird.

**[0015]** Weitere Einzelheiten, Vorteile und Merkmale der vorliegenden Erfindung ergeben sich aus nachfolgender Beschreibung von Ausführungsbeispielen anhand der Zeichnungen.

### Kurze Beschreibung der Zeichnungen

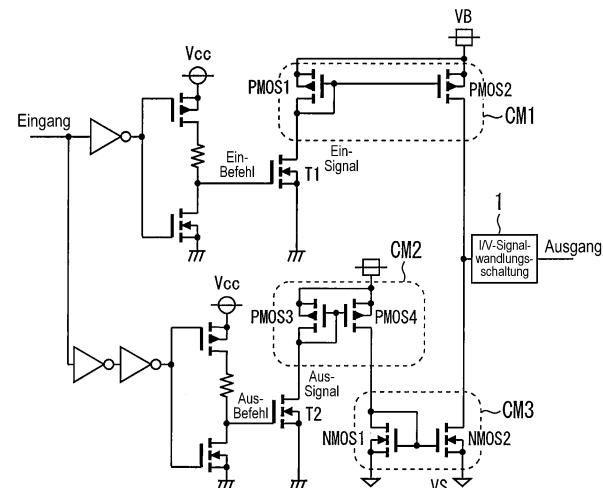

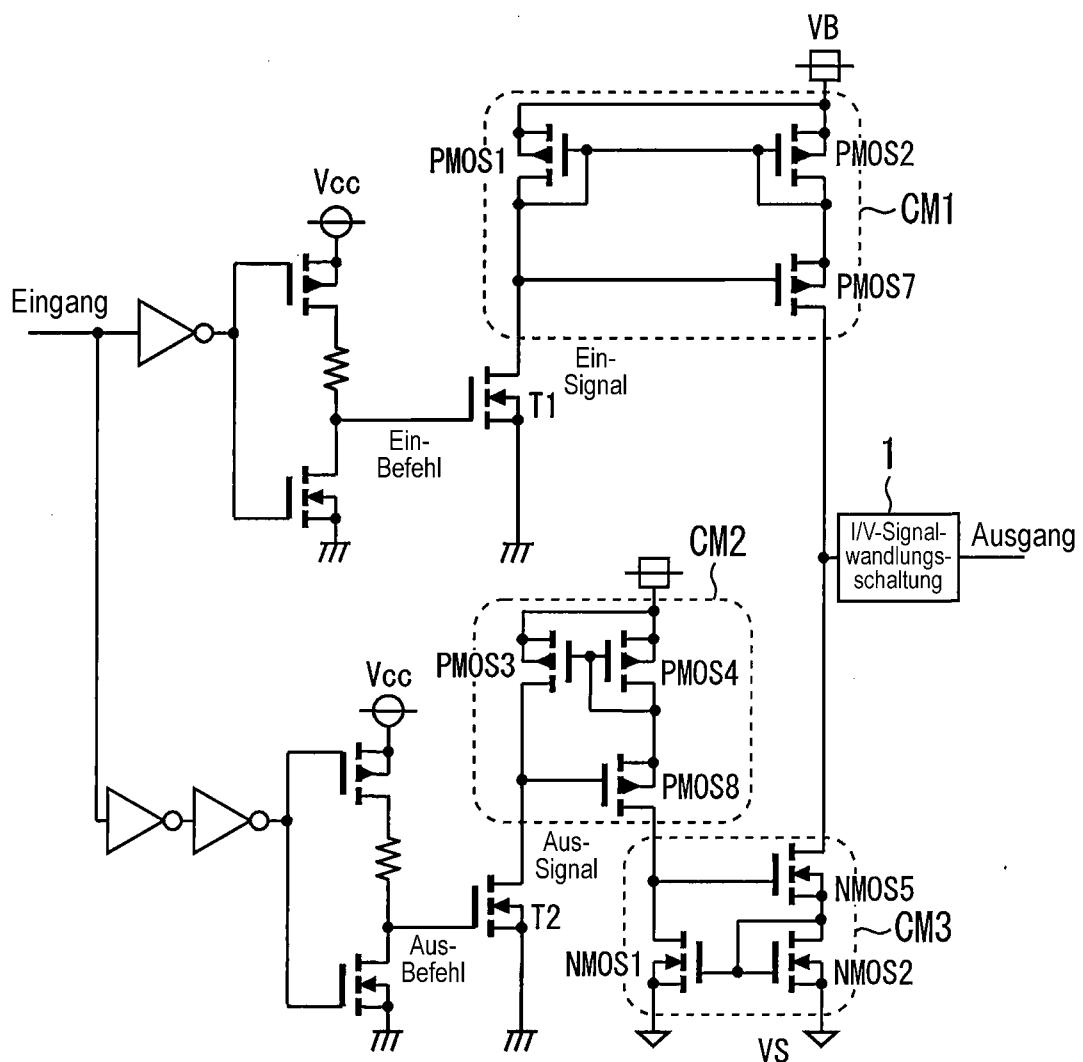

**Fig. 1** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einem ersten Vergleichsbeispiel der vorliegenden Erfindung veranschaulicht.

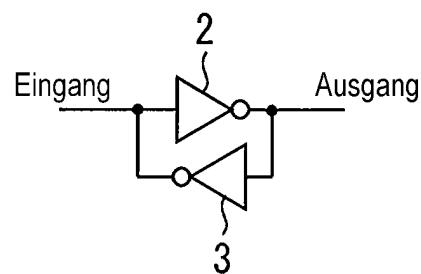

**Fig. 2** ist ein Diagramm, das die I/V-Signalwandlungsschaltung gemäß dem ersten Vergleichsbeispiel veranschaulicht.

**Fig. 3** ist ein Diagramm, das eine Modifikation der I/V-Signalwandlungsschaltung gemäß dem ersten Vergleichsbeispiel veranschaulicht.

**Fig. 4** ist ein Diagramm, das eine Modifikation der Hochspannungs-Pegelverschiebungsschaltung gemäß dem ersten Vergleichsbeispiel veranschaulicht.

**Fig. 5** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einem zweiten Vergleichsbeispiel veranschaulicht.

**Fig. 6** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einem dritten Vergleichsbeispiel veranschaulicht.

**Fig. 7** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einem vierten Vergleichsbeispiel veranschaulicht.

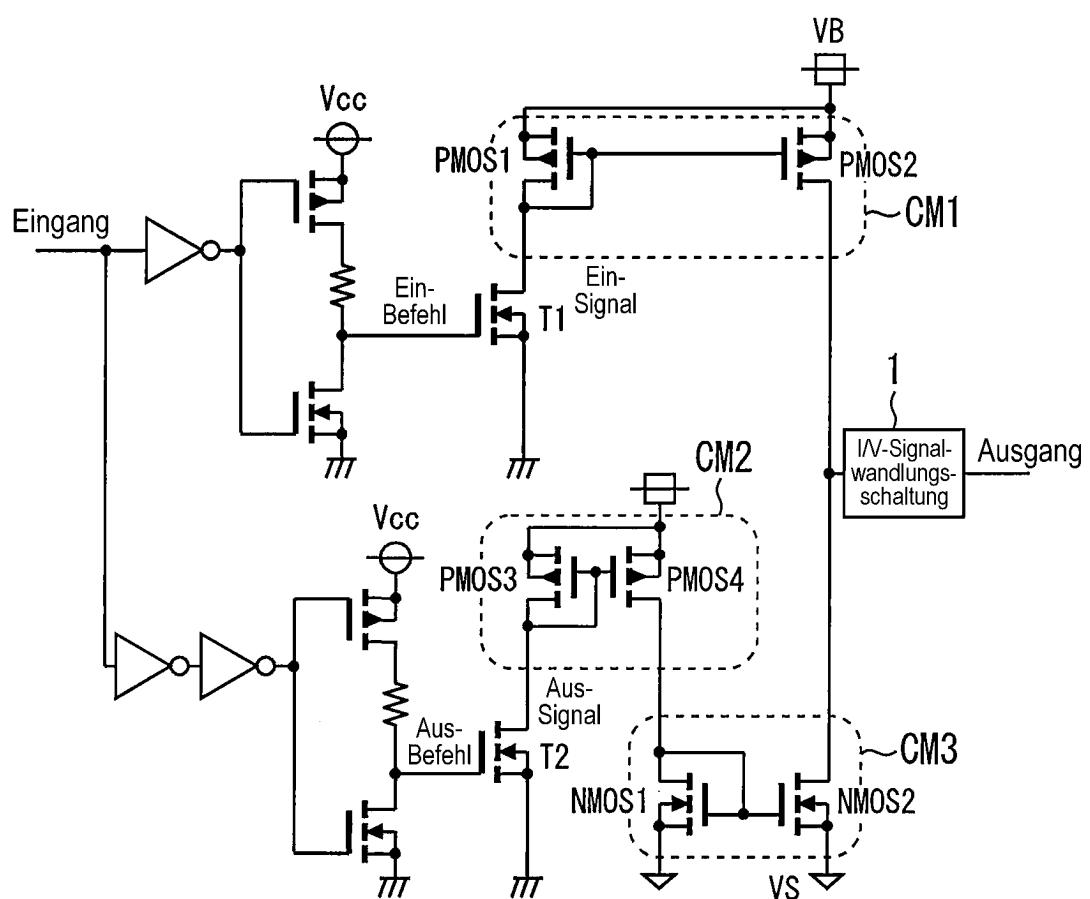

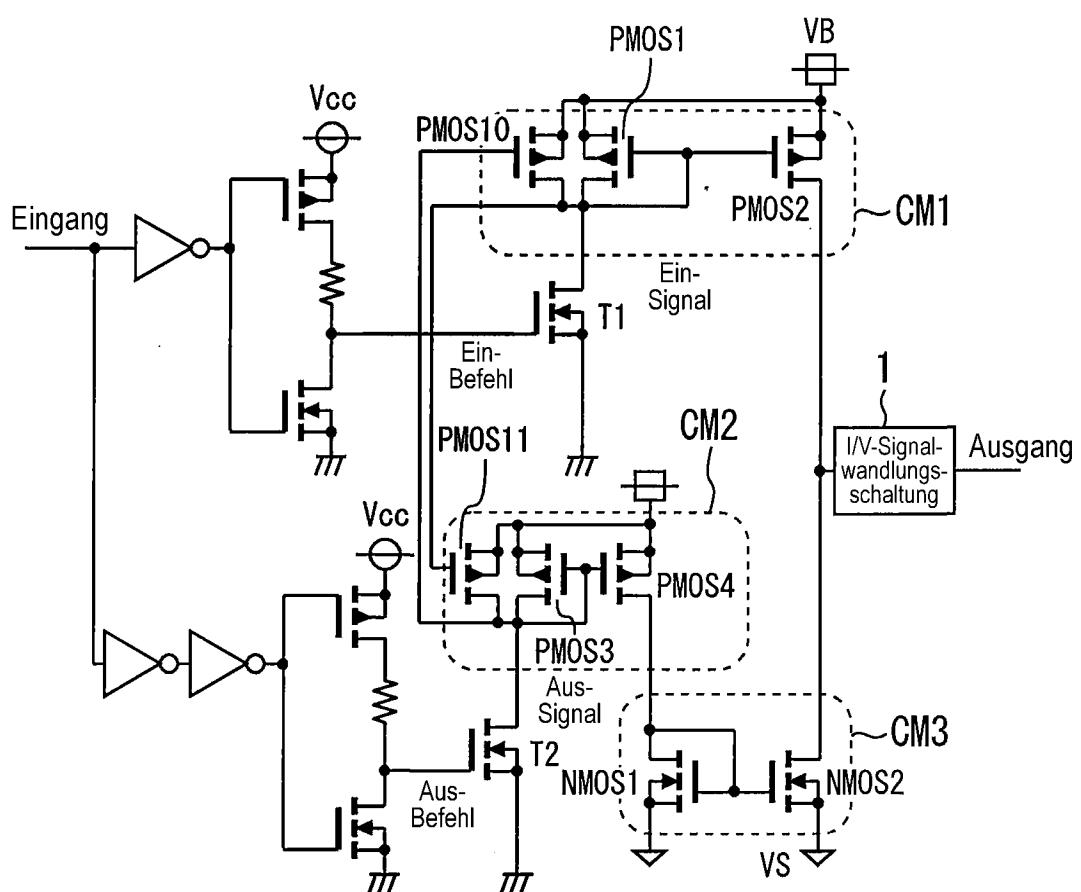

**Fig. 8** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einer Ausführungsform der vorliegenden Erfindung veranschaulicht.

**Fig. 9** ist ein Diagramm, das eine herkömmliche Treiberschaltung veranschaulicht.

**Fig. 10** ist ein Zeitdiagramm, das den Betrieb einer herkömmlichen Treiberschaltung veranschaulicht.

## Beschreibung der Vergleichsbeispiele und der Ausführungsform

**[0016]** Eine Hochspannungs-Pegelverschiebungsschaltung und eine Treiberschaltung gemäß den Vergleichsbeispielen und der Ausführungsform der vorliegenden Erfindung werden mit Bezug zu den Zeichnungen beschrieben. Dieselben Komponenten werden durch dieselben Bezugszeichen gekennzeichnet, und deren wiederholte Beschreibung kann ausgelassen werden.

### Erstes Vergleichsbeispiel

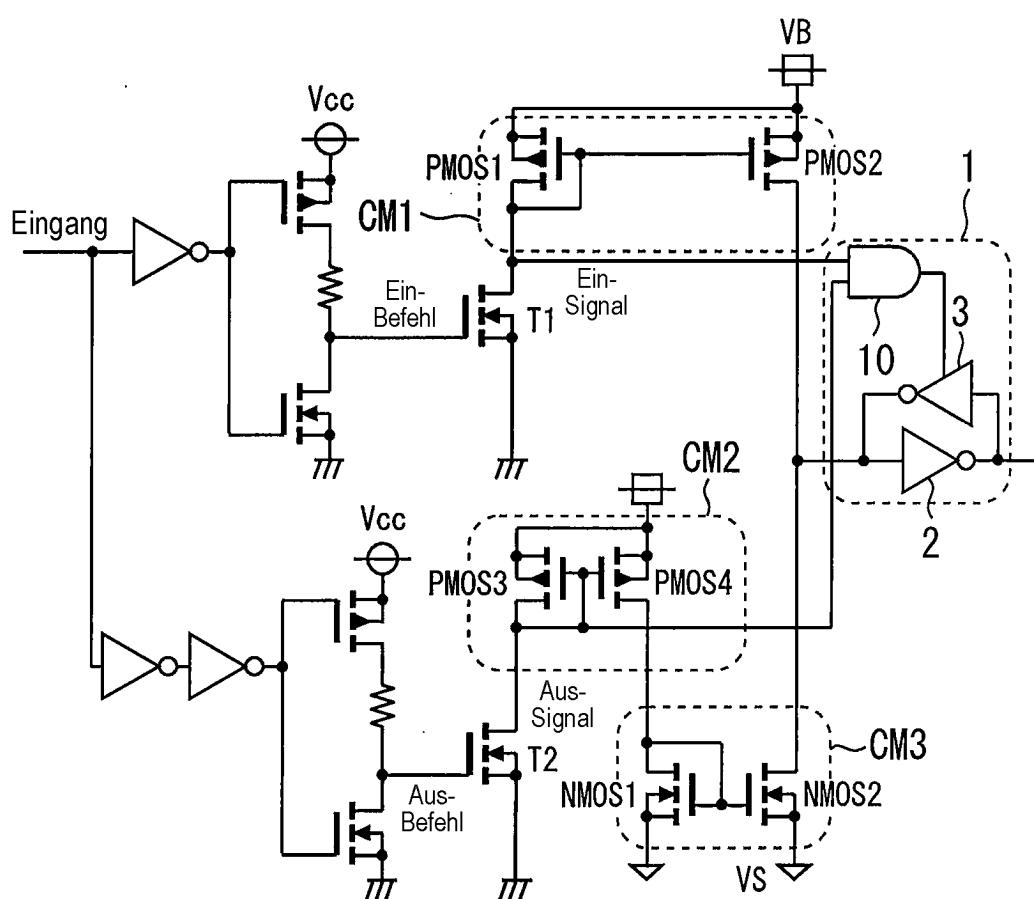

**[0017]** **Fig. 1** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einem ersten Vergleichsbeispiel veranschaulicht. Ein Signal der Hochpotentialseite zur Ausführung einer Ein/Aus-Operation einer Leistungsvorrichtung wird in eine Hochspannungs-Pegelverschiebungsschaltung eingespeist. Dieses Signal der Hochpotentialseite, das ein DC-Signal ist und in T1 und T2 eingespeist wird, die jeweils hochspannungsfeste Feldeffekttransistoren (HNMOS) sind, wird zu einem Stromsignal und wird zu einem Hochpotential pegelverschoben. Das heißt, der T1 wird durch einen Ein-Befehl angesteuert und gibt ein Ein-Signal zur Steuerung der Leistungsvorrichtung aus, um diese einzuschalten. Der T2 wird durch einen Aus-Befehl gesteuert und gibt ein Aus-Signal zur Steuerung der Leistungsvorrichtung aus, so dass diese ausgeschaltet wird. Das Ein-Signal und das Aus-Signal werden allgemein als „Hauptsignale“ bezeichnet.

**[0018]** Eine Stromspiegelschaltung CM1 umfasst einen PMOS1 und einen PMOS2, die PMOS-Transistoren sind, und speist einen Drain-Strom des T1 in eine Referenzseite ein. Das Gate und das Drain des PMOS1 sind miteinander verbunden und sind darüber hinaus mit dem Gate des PMOS2 verbunden. Der PMOS2 veranlasst einen Drain-Strom entsprechend einem vordefinierten Verhältnis des Drain-Stroms des PMOS1 zu fließen.

**[0019]** Eine Stromspiegelschaltung CM2 umfasst einen PMOS3 und einen PMOS4, die PMOS-Transistoren sind, und speist einen Drain-Strom des T2 in eine Referenzseite ein. Das Gate und das Drain des PMOS3 sind miteinander verbunden und sind darüber hinaus mit dem Gate des PMOS4 verbunden. Der PMOS4 veranlasst einen Drain-Strom entsprechend einem vordefinierten Verhältnis des Drain-Stroms des PMOS3 zu fließen.

**[0020]** Eine Stromspiegelschaltung CM3 umfasst einen NMOS1 und einen NMOS2, die NMOS-Transistoren sind, und speist einen Ausgangstrom der Stromspiegelschaltung CM2 in eine Referenzseite ein. Das Gate und das Drain des NMOS1 sind mit-

einander verbunden und sind darüber hinaus mit dem Drain des PMOS4 verbunden.

**[0021]** Ein Knoten zwischen dem Drain des PMOS2 und dem Drain des NMOS2 ist mit einem Eingang einer I/V-Signalwandlungsschaltung 1 verbunden. Die I/V-Signalwandlungsschaltung 1 nimmt einen Ausgang der Stromspiegelschaltung CM1 und einen Ausgang der Stromspiegelschaltung CM3 auf, um ein Ausgangs-Steuerspannungssignal zu erhalten.

**[0022]** Als Nächstes wird der Betrieb der Hochspannungs-Pegelverschiebungsschaltung gemäß dem vorliegenden Beispiel beschrieben. Das Ein-Signal, das erzeugt wird, wenn T1 eingeschaltet ist, veranlasst den PMOS2 einen Drain-Strom in einem vordefinierten Verhältnis durch die Operation der Stromspiegelschaltung CM1 fließen zu lassen. In diesem Fall befindet sich der T2 in einem Aus-Zustand und es fließt kein Strom durch den PMOS3, den PMOS4 oder den NMOS1, und der NMOS2 verbleibt in einem Zustand hoher Impedanz, in dem kein Strom fließen darf. Deshalb fließt kein stationärer Strom in den Knoten zwischen dem Drain des PMOS2 und dem Drain des NMOS2, und eine diesbezügliche Spannung wird im Wesentlichen äquivalent zu der einer Spannungsversorgung. Die I/V-Signalwandlungsschaltung 1 gibt dies als ein Ausgangs-Steuerspannungssignal des Ein-Signals aus. Andererseits, wenn sich der T2 in einem Ein-Zustand befindet, versucht der NMOS2 einen vordefinierten Strom fließen zu lassen, aber da der PMOS2 eine hohe Impedanz besitzt, fließt nach wie vor kein stationärer Strom in den Knoten zwischen dem Drain des PMOS2 und dem Drain des NMOS2 und die I/V-Signalwandlungsschaltung 1 gibt ein Ausgangs-Steuerspannungssignal eines Aus-Signals aus.

**[0023]** Es wird das Verhalten beschrieben, wenn Ströme trotz der Tatsache, dass weder T1 noch T2 aufgrund eines Hochspannungs-Potentialübergangs oder dergleichen ein Hauptsignal empfangen, gleichzeitig durch den PMOS1 und den PMOS3 fließen. Wenn Ströme sowohl durch den PMOS1, als auch durch den PMOS3 fließen, werden Ströme veranlasst jeweils durch den PMOS2 und den NMOS2 zur fließen durch die Operationen der Stromspiegelschaltungen CM1, CM2 und CM3.

**[0024]** In einem stationären Zustand befinden sich der T1 oder der T2 in einem Ein-Zustand und der jeweils andere in einem Aus-Zustand. Wenn sich zum Beispiel der T1 in einem Ein-Zustand befindet, besitzt der PMOS2 eine niedrige Impedanz im Vergleich zum NMOS2, und ein Eingang der I/V-Signalwandlungsschaltung 1 ist auf einem H-Pegel. Selbst wenn Ströme in diesem Zustand aufgrund eines Hochspannungs-Potentialübergangs oder dergleichen sowohl durch den PMOS1, als auch durch den

PMOS3 fließen, ist der Strom, der durch den PMOS1 fließt um den Strom eines Hauptsignals größer, als der Strom, der durch den PMOS3 fließt. Das heißt, der Strom des PMOS2 ist größer als der Strom des NMOS2, und somit wird der Eingang der I/V-Signalwandlungsschaltung 1 auf einem H-Level gehalten und die Ausgangslogik wird niemals fehlerhaft invertiert. Andererseits, wenn sich der T2 in einem Ein-Zustand befindet, ist der Strom des NMOS2 im Gegensatz zum oben beschrieben Fall größer als der Strom des PMOS2, und somit wird der Eingang der I/V-Signalwandlungsschaltung 1 auf einem L-Level gehalten und die Ausgangslogik wird immer noch nicht fehlerhaft invertiert.

**[0025]** Ähnliche Effekte können auch erzielt werden, wenn das Hauptsignal impulsgesteuert ist. Im Fall einer Impulssteuerung besitzen sowohl der PMOS2, als auch der NMOS2 in einem stationären Zustand hohe Impedanzen und die Eingangsspannung der I/V-Signalwandlungsschaltung 1 wird abhängig davon bestimmt, ob ein Ein-Signal oder ein Aus-Signal in die Hochspannungs-Pegelverschiebungsschaltung eingespeist wird. Wenn Ströme in diesem Zustand veranlasst werden gleichzeitig durch den PMOS1 und den PMOS3 zu fließen, findet ein Potentialübergang an der Eingangsspannung der I/V-Signalwandlungsschaltung 1 aufgrund eines Unterschieds in der Impedanz zwischen dem PMOS2 und dem NMOS2 statt. Daher wird im Vergleich zu einem Schaltbild, das wie im Stand der Technik unabhängig vom Unterschied ist, ein Fehlersignal selbst abgeschwächt und das Auftreten einer fehlerhaften Ausgangs-Inversion ist unwahrscheinlich. Anders ausgedrückt kann eine Kopplung, die im Stand der Technik ein Problem darstellt und notwendig ist für die Erzeugung eines Maskierungssignals, aus einem Ein-Signal und einem Aus-Signal, gelockert werden.

**[0026]** Wenn das Potential der Spannungsversorgung der Hochspannungsseite aufgrund eines Schaltvorgangs oder dergleichen der Leistungsvorrichtung zu einem niedrigeren Potential wird, als das Referenzpotential der Niedrigspannungsseite, haben der PMOS1, der PMOS2, der PMOS3, der PMOS4, der NMOS1 und der NMOS2 allesamt hohe Impedanzen. Da die Eingangsspannung der I/V-Signalwandlungsschaltung 1 ihren unmittelbar vorherigen Zustand aufrechterhält, ist es immer noch möglich, eine fehlerhafte Ausgangs-Inversion zu verhindern. Die vorliegende Erfindung ermöglicht es, den Signalübertragungsbereich im Vergleich zum Stand der Technik auf einfache Weise zu erweitern, wenn das Referenzpotential der Hochspannungsseite unter das Referenzpotential der Niedrigspannungsseite fällt.

**[0027]** In der Annahme, dass die Spannungsversorgung der Hochspannungsseite fest ist, wenn das

Referenzpotential der Hochspannungsseite unter das Referenzpotential der Niedrigspannungsseite fällt, wird eine Potentialdifferenz zwischen den beiden Enden der Hochspannungs-Pegelverschiebungsschaltung, d.h. eine Potentialdifferenz zwischen der Spannungsversorgung der Hochspannungsseite und dem Referenzpotential der Niedrigspannungsseite verringert, wodurch ein Fließen von ausreichenden Strömen in den T1 und den T2 verhindert wird. Dies liegt darin begründet, dass eine Gate-Drain-Spannung, die für einen MOS-Transistor erforderlich ist, um einen Strom fließen zu lassen, in dem vorliegenden Beispiel generell niedriger ist, als eine Schwelle der I/V-Signalwandlungsschaltung, die ein hochspannungsgegenschobenes Hauptsignal als ein Spannungssignal aufnimmt, wie es im Stand der Technik der Fall ist. Daher ist es möglich, ein Fehlersignal zu entfernen, das basierend auf einem Verschiebungstrom erzeugt wird, wenn ein Hochspannungsübergang oder dergleichen stattfindet, und eine unbeabsichtigte Inversion der Ausgangslogik zu verhindern.

**[0028]** Wie oben gemäß der vorliegenden Erfindung beschrieben, speisen die Stromspiegelschaltungen CM1 und CM2 die jeweiligen Drain-Ströme des T1 und des T2 in die Referenzseite ein, die Stromspiegelschaltung CM3 speist den Ausgangsstrom der Stromspiegelschaltung CM2 in die Referenzseite ein, und die I/V-Signalwandlungsschaltung 1 nimmt den Ausgang der Stromspiegelschaltung CM1 und den Ausgang der Stromspiegelschaltung CM3 auf, und ein Ausgangs-Steuerspannungssignal wird dadurch erhalten. Dies erlaubt es, einen Strom zu reduzieren, während die Übertragung eines Fehlersignals verhindert wird.

**[0029]** **Fig. 2** ist ein Diagramm, das die I/V-Signalwandlungsschaltung gemäß dem ersten Vergleichsbeispiel veranschaulicht. Die I/V-Signalwandlungsschaltung 1 ist eine Latch-Schaltung in der zwei Inverter 2 und 3 umgekehrt parallel zueinander geschaltet sind. Selbst wenn der oben beschriebene Hochimpedanz-Zustand anhält, verhindert dieser Latch-Effekt, dass der Eingang zur I/V-Signalwandlungsschaltung 1 instabil wird.

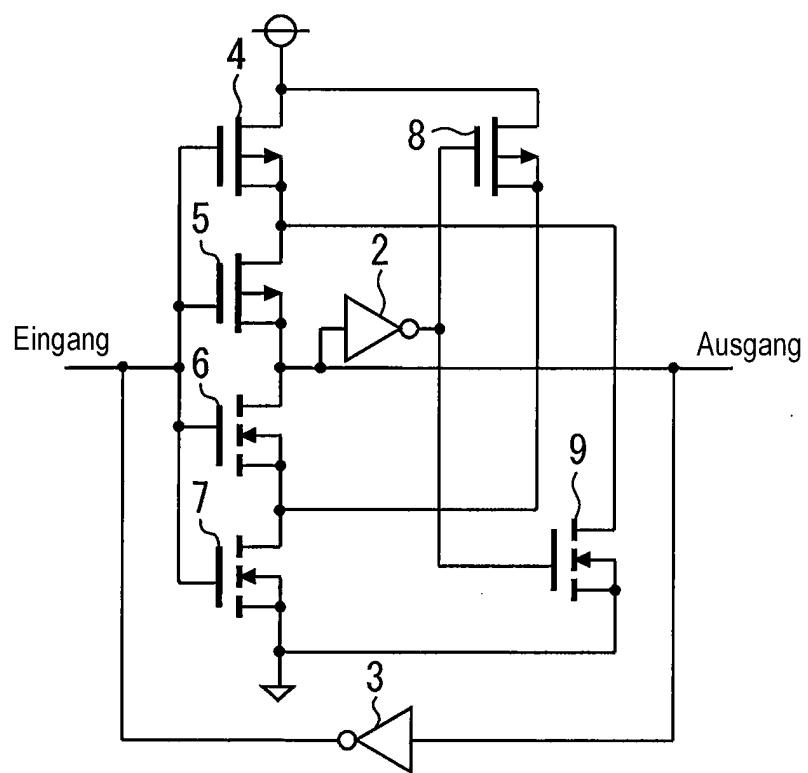

**[0030]** **Fig. 3** ist ein Diagramm, das eine Modifikation der I/V-Signalwandlungsschaltung gemäß dem ersten Vergleichsbeispiel veranschaulicht. Die I/V-Signalwandlungsschaltung 1 ist eine Schmitt-Trig-ger-Schaltung, welche die Inverter 2 und 3 und die Transistoren 4 bis 9 umfasst. Da die Schmitt-Trig-ger-Schaltung eine Hysterese in einer Eingangs-schwellenspannung besitzt, wird die Stabilität erhöht.

**[0031]** **Fig. 4** ist ein Diagramm, das eine Modifikation der Hochspannungs-Pegelverschiebungsschaltung gemäß dem ersten Vergleichsbeispiel veranschaulicht. Der Inverter 3 auf der

Rückkopplungsseite der I/V-Signalwandlungsschaltung 1 ist aus einem Drei-Zustand-Puffer aufgebaut. Der Inverter 3 wird durch eine AND-Schaltung 10 gesteuert, welche die Drain-Spannungen des T1 und des T2 aufnimmt, um die I/V-Signalwandlungsschaltung 1 nur dann zu veranlassen eine Latch-Operation auszuführen, wenn kein Signal eingespeist wird, wodurch eine hohe Impedanz verursacht wird. Wenn die Hochspannungs-Pegelverschiebungsschaltung impulsgesteuert ist, ist es auf diese Weise möglich, eine Störung des Ausgangs bei der Übertragung eines Ein-Signals und eines Aus-Signals durch die Latch-Schaltung zu verhindern und den Ausgang durch das Latchen zu stabilisieren, wenn kein Signal einspeist wird. Es ist auch möglich den Stromverbrauch zu reduzieren. Es ist auch möglich den Ausgang zu stabilisieren, selbst wenn kein Strom mehr veranlasst wird durch den DC-Antrieb zu fließen.

#### Zweites Vergleichsbeispiel

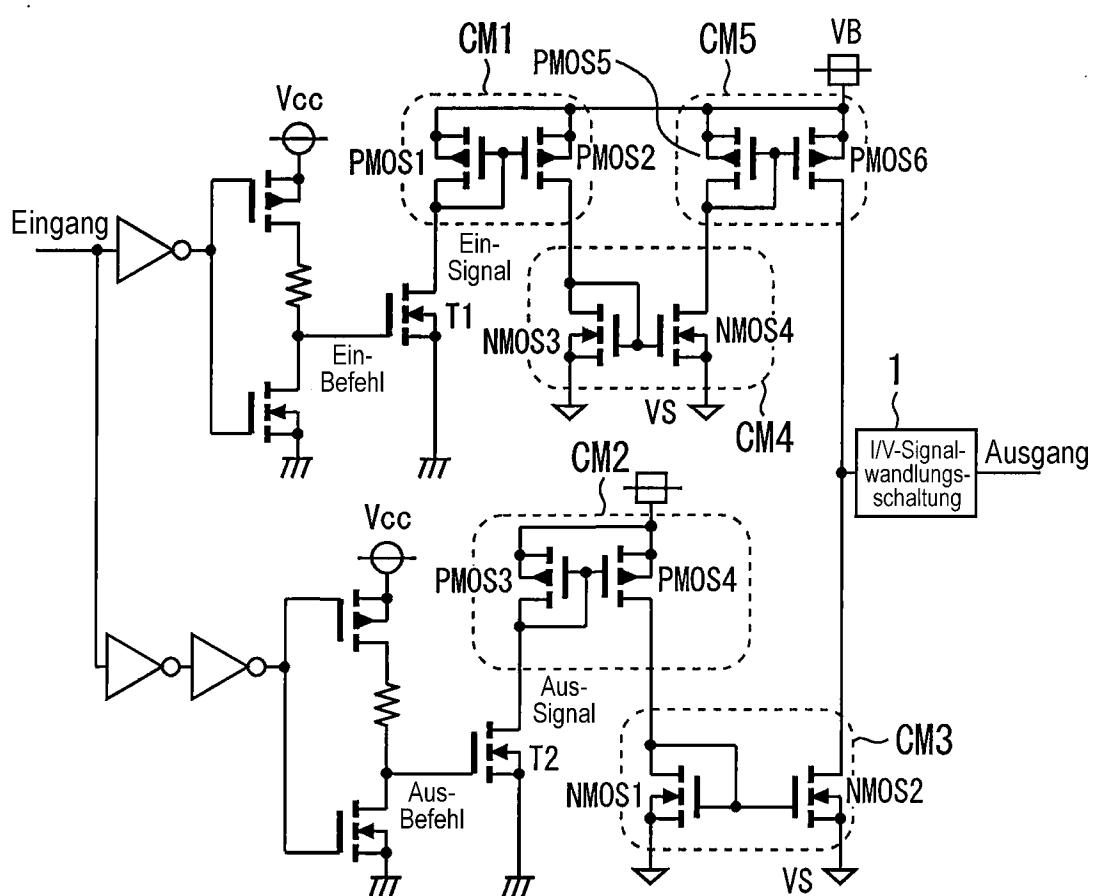

**[0032]** **Fig. 5** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einem zweiten Vergleichsbeispiel veranschaulicht. Die Stromspiegelschaltungen CM4 und CM5 werden zur Konfiguration des ersten Beispiels hinzugefügt. Die Stromspiegelschaltung CM4 umfasst einen NMOS3 und einen NMOS4, die NMOS-Transistoren sind und speist den Ausgangstrom der Stromspiegelschaltung CM1 in die Referenzseite ein. Die Stromspiegelschaltung CM5 umfasst einen PMOS5 und einen PMOS6, die PMOS-Transistoren sind und speist den Ausgangstrom der Stromspiegelschaltung CM4 in die Referenzseite ein. Die I/V-Signalwandlungsschaltung 1 empfängt den Ausgang der Stromspiegelschaltung CM3 und den Ausgang der Stromspiegelschaltung CM5 und erzeugt ein Ausgangssteuerspannungssignal.

**[0033]** Wenn ein Fehlersignal in den PMOS1, PMOS3, und T1 und T2 oder dergleichen fließt, werden ein Gate-Potential und ein Drain-Potential des PMOS1 und des PMOS3 entsprechend der Stromstärke angelegt. Zu diesem Zeitpunkt ist es möglich, wenn die Stromdichten des NMOS1 und des NMOS2 durch eine Erhöhung der Größe des NMOS1 und des NMOS2 reduziert werden und das Stromverhältnis zwischen dem PMOS3 und dem PMOS4 weiter unterdrückt wird, das Gate-Potential und das Drain-Potential des NMOS1 und des NMOS2 im Vergleich zu einem Fall zu reduzieren, in dem die Stromdichten hoch sind. Außerdem können das Gate-Potential und die Drain-Spannung des PMOS3 und des PMOS4 so festgelegt werden, dass ein größerer Strom fließt, während das Verhältnis zwischen dem Drain-Strom des PMOS3 und dem Drain-Strom des PMOS4 als Stromspiegelschaltung beibehalten wird.

**[0034]** In der Konfiguration gemäß dem ersten Vergleichsbeispiel ist das Drain des PMOS2 direkt verbunden mit dem Drain des NMOS2. Aus diesem Grund kann die an den PMOS2 angelegte Drain-Spannung entsprechend dem Stromwert eines Fehlersignals exzessiv ansteigen, wenn ein Strom, der basierend auf dem Fehlersignal erzeugt wird, vom PMOS2 zum NMOS2 fließt, und die Eingangsspannung der I/V-Signalwandlungsschaltung 1 kann abnehmen, wodurch der Ausgang fehlerhaft invertiert wird.

**[0035]** Im Gegensatz dazu werden gemäß dem vorliegenden Vergleichsbeispiel die Stromspiegelschaltungen CM4 und CM5 hinzugefügt. Somit können der PMOS1 und der PMOS2 auch Eingangssignale der I/V-Signalwandlungsschaltung 1 für einen größeren Strom speichern, als in den Fällen des PMOS3 und des PMOS4. Deshalb ist es möglich, dass ein falsches Stromsignal, das während eines Hochspannungs-Potentialübergangs oder dergleichen erzeugt wird, stärker als in dem ersten Vergleichsbeispiel fließt, und dadurch die Funktion zur Verhinderung einer Fehlfunktion verbessert wird.

#### Drittes Vergleichsbeispiel

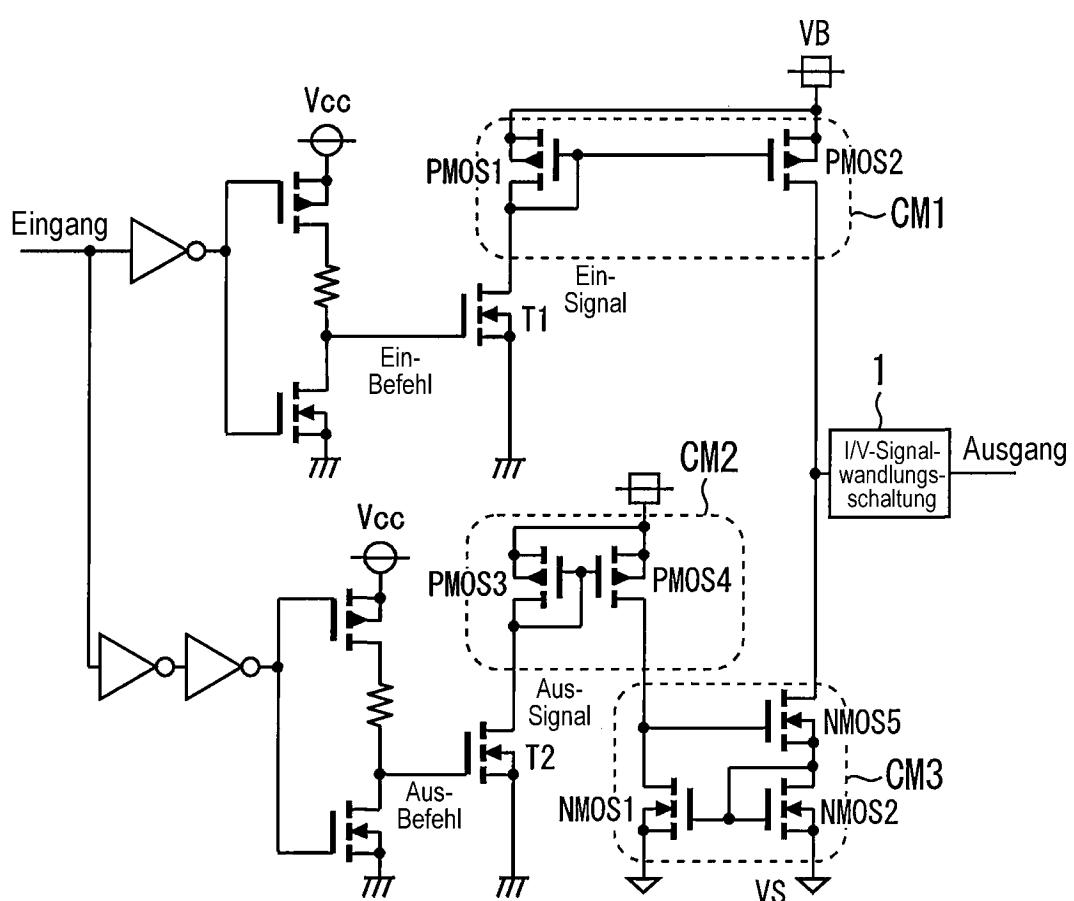

**[0036]** **Fig. 6** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einem dritten Vergleichsbeispiel veranschaulicht. Entgegen der ersten Ausführungsform ist die Stromspiegelschaltung CM3 eine Wilson-Stromspiegelschaltung mit einem NMOS5, der ein NMOS-Transistor ist, der zum NMOS1 und zum NMOS2 hinzugefügt wird. In der Wilson-Stromspiegelschaltung wird ein Ausgangstrom in einen Strom der Referenzseite rückgekoppelt. Da eine Gate-Vorspannung an den NMOS1 und den NMOS2 auf der Ausgangsseite angelegt wird, fließt auf der Referenzseite auch kein Strom, wenn kein Strom auf der Ausgangsseite fließt.

**[0037]** Wenn ein DC-Signal gemäß dem ersten und zweiten Vergleichsbeispiel pegelverschoben wird, gibt es einen Zustand, in dem ein stationärer Strom durch Teile des PMOS4 und des NMOS1 fließt. Andererseits ist es gemäß dem vorliegenden Vergleichsbeispiel möglich, stationäre Ströme in diesen Teilen zu eliminieren, da die Wilson-Stromspiegelschaltung eingesetzt wird. Wenn sich das Innere der Hochspannungsseite in einem Zustand niedriger Spannung befindet, wird eine Ladung in einem Kondensator aufgeladen, der parallel zu einer Spannungsversorgung der Hochspannungsseite von einer Spannungsversorgung der Niedrigspannungsseite geschaltet ist. Die Ladung wird häufig dazu verwendet dem Inneren der Hochspannungsseite einen Strom zu liefern. Das vorliegende Vergleichsbeispiel erlaubt es einen Stromverbrauch im Inneren der Hochspannungsseite zu reduzieren.

## Viertes Vergleichsbeispiel

**[0038]** **Fig. 7** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einem vierten Vergleichsbeispiel veranschaulicht. Die Stromspiegelschaltung CM1 ist eine Wilson-Stromspiegelschaltung mit einem PMOS7, der ein PMOS-Transistor ist, der zusätzlich zur Konfiguration des dritten Vergleichsbeispiels zum PMOS1 und zum PMOS2 hinzugefügt wird. Die Stromspiegelschaltung CM2 ist ebenfalls eine Wilson-Stromspiegelschaltung mit einem PMOS8, der ein PMOS-Transistor ist, der zum PMOS3 und PMOS4 hinzugefügt wird. T1 und T2 werden mit einem Strom einer Spannungsquelle einer Hochspannungsseite versorgt, aber dieser stationäre Strom kann in dem vorliegenden Vergleichsbeispiel auch reduziert werden. Wenn zum Beispiel eine Diode hinzugefügt wird, deren Anode mit der Spannungsversorgung der Hochspannungsseite verbunden ist und deren Kathode mit dem Drain des T1 und des T2 verbunden ist, ist es möglich, den Stromverbrauch der Spannungsversorgung der Hochspannungsseite zu reduzieren, während verhindert wird, dass eine übermäßige Spannung an die Vorrichtungen der Hochspannungsseite angelegt wird.

## Ausführungsform

**[0039]** **Fig. 8** ist ein Diagramm, das eine Hochspannungs-Pegelverschiebungsschaltung gemäß einer Ausführungsform der vorliegenden Erfindung veranschaulicht. Ein PMOS10 und ein PMOS11, die PMOS-Transistoren sind, werden zur Konfiguration des ersten Vergleichsbeispiels hinzugefügt. Der PMOS10 ist parallel zur Source und zum Drain des PMOS1 geschaltet, der ein PMOS-Transistor der Referenzseite der Stromspiegelschaltung CM1 ist. Der PMOS11 ist parallel zur Source und zum Drain des PMOS3 geschaltet, der ein PMOS-Transistor der Referenzseite der Stromspiegelschaltung CM2 ist. Das Gate des PMOS10 ist mit dem Drain und dem Gate des PMOS3 verbunden und wird durch ein Gate-Potential der Stromspiegelschaltung CM2 angesteuert. Das Gate des PMOS11 ist mit dem Drain und dem Gate des PMOS1 verbunden und wird durch ein Gate-Potential der Stromspiegelschaltung CM1 angesteuert.

**[0040]** Wenn zum Beispiel ein Ein-Signal in die Hochspannungs-Pegelverschiebungsschaltung eingespeist wird, sind das Gate und das Drain des PMOS1 vorgespannt und der PMOS11 ist ebenfalls vorgespannt. Da jedoch kein Aus-Signal in den T2 eingespeist wird, fließt über den PMOS11 kein Strom.

**[0041]** Wenn ein Fehlersignal aufgrund eines Hochspannungspotentialübergangs oder dergleichen erzeugt wird, fließt gemäß dem ersten Vergleichsbei-

spiel ein Strom durch den PMOS3 als ein Fehlersignal und dieser Fehlersignalstrom wird durch den PMOS2 und den NMOS2 in einem Teil aufgehoben, der mit der I/V-Signalwandlungsschaltung 1 verbunden ist. Andererseits fließt gemäß der vorliegenden Ausführungsform ein Teil des Fehlersignalstroms über den Gate-vorgespannten PMOS11 in den T2 oder dergleichen. Aus diesem Grund ist der über den PMOS3 an den NMOS2 übertragene Fehlersignalstrom bereits in einem Teil des PMOS3 reduziert. Andererseits ist der PMOS10 nicht Gate-vorgespannt, bis ein Fehlersignalstrom veranlasst wird in den PMOS11 oder den PMOS3 zu fließen und der vollständige Fehlersignalstrom veranlasst wird über den PMOS1 in den T1 oder dergleichen zu fließen. Da ein Ein-Signal in den T1 und den PMOS1 eingespeist wird, fließt weiterhin ein Strom, um das Ein-Signal zu verstärken. Das heißt, da nur der Fehlersignalstrom durch den PMOS11 abgeschwächt wird, ist es möglich, eine Verhinderung einer fehlerhaften Ausgangs-Inversion zu verstärken. Es sei darauf hingewiesen, dass die Verhinderung der fehlerhaften Ausgangs-Inversion ebenfalls verstärkt wird, wenn ein Aus-Signal in die Hochspannungs-Pegelverschiebungsschaltung eingespeist wird.

**[0042]** In der vorliegenden Erfindung kann die Übertragungsgeschwindigkeit des Hauptsignals erhöht werden, obwohl die Logik-Übertragung zu einem Zeitpunkt einer normalen Ansteuerung der Leistungsvorrichtung ähnlich des der ersten Vergleichsbeispiels ist. Das heißt, wenn der T1 und der T2 von einem Ein-Zustand in einen Aus-Zustand übergehen, ist es notwendig, eine parasitäre Kapazität wie eine Back-Gate-Kapazität zwischen dem Drain und der Source des T1 und des T2 aufzuladen, aber dieses Aufladen kann durch die vorgespannten PMOS 10 und PMOS 11 durchgeführt werden, und somit wird die Reaktionszeit verbessert.

**[0043]** Es wird darauf hingewiesen, dass der PMOS10 und der PMOS11 gemäß der vorliegenden Erfindung parallel geschaltet sind zum PMOS1 und zum PMOS3, aber selbst wenn eine ähnliche Konfiguration bezüglich der anderen Stromspiegelschaltungen wie der NMOS1 und der NMOS2 eingesetzt wird, können ähnliche Effekte erzielt werden.

**[0044]** Als die durch die Treiberschaltung angesteuerte Leistungsvorrichtung besitzt ein aus einem SiC-Material hergestellter MOSFET eine höhere Operationsgeschwindigkeit als ein IGBT oder ein MOSFET, die aus einem Si-Material hergestellt sind, und eine stärkere  $dV/dt$ . Aus diesem Grund wird zur Verhinderung einer Fehlfunktion bevorzugt die Hochspannungs-Pegelverschiebungsschaltung gemäß der Vergleichsbeispiele und der Ausführungsform zusammen mit der Treibervorrichtung eingesetzt, welche die Leistungsvorrichtung ansteuert,

die aus einem SiC-Material hergestellt ist, wie ein SiMOSFET.

|       |                                           |                                                                                                                                                                                                                                                                                         |                                             |

|-------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

|       | Bezugszeichenliste                        | PMOS2                                                                                                                                                                                                                                                                                   | PMOS-Transistor                             |

| 1     | Signalwandlungsschaltung                  | PMOS3                                                                                                                                                                                                                                                                                   | PMOS-Transistor                             |

| 2     | Inverter                                  | PMOS4                                                                                                                                                                                                                                                                                   | PMOS-Transistor                             |

| 3     | Inverter                                  | PMOS5                                                                                                                                                                                                                                                                                   | PMOS-Transistor                             |

| 4     | Transistor                                | PMOS6                                                                                                                                                                                                                                                                                   | PMOS-Transistor                             |

| 5     | Transistor                                | PMOS7                                                                                                                                                                                                                                                                                   | PMOS-Transistor                             |

| 6     | Transistor                                | PMOS8                                                                                                                                                                                                                                                                                   | PMOS-Transistor                             |

| 7     | Transistor                                | PMOS10                                                                                                                                                                                                                                                                                  | erster PMOS-Transistor                      |

| 8     | Transistor                                | PMOS11                                                                                                                                                                                                                                                                                  | zweiter PMOS-Transistor                     |

| 9     | Transistor                                | R1                                                                                                                                                                                                                                                                                      | Pegelverschiebungswiderstände               |

| 10    | AND-Schaltung                             | R2                                                                                                                                                                                                                                                                                      | Pegelverschiebungswiderstände               |

| 100   | Hochspannungs-Pegelverschiebungsschaltung | T1                                                                                                                                                                                                                                                                                      | erster hochspannungsfester NMOS-Transistor  |

| 101   | Übertragungsschaltung                     | T2                                                                                                                                                                                                                                                                                      | zweiter hochspannungsfester NMOS-Transistor |

| 102   | Treiberschaltung                          | <b>Patentansprüche</b>                                                                                                                                                                                                                                                                  |                                             |

| 103   | RS-Typ Flip-Flop                          | 1. Hochspannungs-Pegelverschiebungsschaltung umfassend:                                                                                                                                                                                                                                 |                                             |

| 104   | NOR-Gatter                                | • einen ersten hochspannungsfesten NMOS-Transistor (T1), der durch einen Ein-Befehl angesteuert wird;                                                                                                                                                                                   |                                             |

| 105   | NOR-Gatter                                | • einen zweiten hochspannungsfesten NMOS-Transistor (T2), der durch einen Aus-Befehl angesteuert wird;                                                                                                                                                                                  |                                             |

| 106   | NAND-Gatter                               | • eine erste PMOS-Stromspiegelschaltung (CM1), die einen Drain-Strom des ersten hochspannungsfesten NMOS-Transistors (T1) in eine Referenzseite einspeist;                                                                                                                              |                                             |

| 107   | NAND-Gatter                               | • eine zweite PMOS-Stromspiegelschaltung (CM2), die einen Drain-Strom des zweiten hochspannungsfesten NMOS-Transistors (T2) in eine Referenzseite einspeist;                                                                                                                            |                                             |

| 108   | I/V-Signalwandlungsschaltung-Gatter       | • eine erste NMOS-Stromspiegelschaltung (CM3), die einen Ausgangsstrom der zweiten PMOS-Stromspiegelschaltung (CM2) in eine Referenzseite einspeist;                                                                                                                                    |                                             |

| 109   | I/V-Signalwandlungsschaltung-Gatter       | • eine I/V-Signalwandlungsschaltung (1), die einen Ausgang der ersten PMOS-Stromspiegelschaltung (CM1) und einen Ausgang der ersten NMOS-Stromspiegelschaltung (CM3) aufnimmt, um ein Ausgangs-Steuerspannungssignal zu erhalten;                                                       |                                             |

| 110   | Maskierungssignalschaltung                | • einen ersten PMOS-Transistor (PMOS10), der parallel zu einer Source und einem Drain eines PMOS-Transistors einer Referenzseite der ersten PMOS-Stromspiegelschaltung (CM1) geschaltet ist; und                                                                                        |                                             |

| CM1   | erste PMOS-Stromspiegelschaltung          | • einen zweiten PMOS-Transistor (PMOS11), der parallel zu einer Source und einem Drain eines PMOS-Transistors einer Referenzseite der zweiten PMOS-Stromspiegelschaltung (CM2) geschaltet ist, wobei ein Gate des ersten PMOS-Transistors (PMOS10) durch ein Gate-Potential der zweiten |                                             |

| CM2   | zweite PMOS-Stromspiegelschaltung         |                                                                                                                                                                                                                                                                                         |                                             |

| CM3   | erste NMOS-Stromspiegelschaltung          |                                                                                                                                                                                                                                                                                         |                                             |

| CM4   | zweite NMOS-Stromspiegelschaltung         |                                                                                                                                                                                                                                                                                         |                                             |

| CM5   | dritte PMOS-Stromspiegelschaltung         |                                                                                                                                                                                                                                                                                         |                                             |

| NMOS1 | NMOS-Transistor                           |                                                                                                                                                                                                                                                                                         |                                             |

| NMOS2 | NMOS-Transistor                           |                                                                                                                                                                                                                                                                                         |                                             |

| NMOS3 | NMOS-Transistor                           |                                                                                                                                                                                                                                                                                         |                                             |

| NMOS4 | NMOS-Transistor                           |                                                                                                                                                                                                                                                                                         |                                             |

| NMOS5 | NMOS-Transistor                           |                                                                                                                                                                                                                                                                                         |                                             |

| PMOS1 | PMOS-Transistor                           |                                                                                                                                                                                                                                                                                         |                                             |

PMOS-Stromspiegelschaltung (CM2) angesteuert wird, und

- ein Gate des zweiten PMOS-Transistors (PMOS11) durch ein Gate-Potential der ersten PMOS-Stromspiegelschaltung (CM1) angesteuert wird.

2. Hochspannungs-Pegelverschiebungsschaltung nach Anspruch 1, weiter umfassend:

- eine zweite NMOS-Stromspiegelschaltung (CM4), die einen Ausgangsstrom der ersten PMOS-Stromspiegelschaltung (CM1) in eine Referenzseite einspeist; und

- eine dritte PMOS-Stromspiegelschaltung (CM5), die einen Ausgangsstrom der zweiten NMOS-Stromspiegelschaltung (CM4) in eine Referenzseite einspeist;

- wobei die I/V-Signalwandlungsschaltung (1) einen Ausgang der ersten NMOS-Stromspiegelschaltung (CM3) und einen Ausgang der dritten PMOS-Stromspiegelschaltung (CM5) aufnimmt, um ein Ausgangs-Steuerspannungssignal zu erhalten.

3. Hochspannungs-Pegelverschiebungsschaltung nach Anspruch 1 oder 2, wobei die erste NMOS-Stromspiegelschaltung (CM3) eine Wilson-Stromspiegelschaltung ist, in der ein Ausgangstrom in einen Strom einer Referenzseite rückgekoppelt wird.

4. Hochspannungs-Pegelverschiebungsschaltung nach einem der Ansprüche 1 bis 3, wobei die erste und die zweite PMOS-Stromspiegelschaltung (CM1, CM2) Wilson-Stromspiegelschaltungen sind, in denen ein Ausgangsstrom in einen Strom einer Referenzseite rückgekoppelt wird.

5. Hochspannungs-Pegelverschiebungsschaltung nach einem der Ansprüche 1 bis 4, wobei die I/V-Signalwandlungsschaltung (1) eine Latch-Schaltung ist.

6. Hochspannungs-Pegelverschiebungsschaltung nach Anspruch 5, wobei die I/V-Signalwandlungsschaltung (1) eine Latch-Operation nur dann ausführt, wenn kein Signal eingespeist wird.

7. Treibervorrichtung umfassend die Hochspannungs-Pegelverschiebungsschaltung nach einem der Ansprüche 1 bis 6, wobei die Treibervorrichtung eine Leistungsvorrichtung treibt, die aus einem SiC-Material hergestellt ist.

Es folgen 8 Seiten Zeichnungen

## Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9 Stand der Technik

FIG. 10 Stand der Technik