(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-141685

(P2010-141685A)

(43) 公開日 平成22年6月24日(2010.6.24)

(51) Int.Cl.

HO3M 1/50 (2006.01)

F 1

HO3M 1/50

テーマコード(参考)

5 J 0 2 2

審査請求 未請求 請求項の数 10 O L (全 13 頁)

(21) 出願番号

特願2008-316969 (P2008-316969)

(22) 出願日

平成20年12月12日 (2008.12.12)

(71) 出願人 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 110000578

名古屋国際特許業務法人

(72) 発明者 渡辺 高元

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

F ターム(参考) 5J022 AA11 BA01 CD03 CD04 CE04

CE05 CF02 CG01

(54) 【発明の名称】 パルス遅延回路およびA/D変換回路

## (57) 【要約】

【課題】 均等な時間間隔の遅延パルスが得られるパルス遅延回路、及び、A/D変換データの分解能が均一なA/D変換回路を提供する。

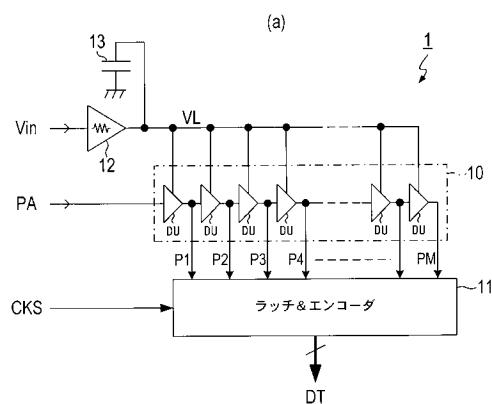

【解決手段】 パルス信号PAを遅延させて出力する遅延ユニットDUをM(Mは正整数)段直列接続してなるパルス遅延回路10と、サンプリングクロックCKSのタイミングで、パルス遅延回路10内でのパルス信号PAの到達位置を検出(ラッチ)し、その検出結果を、パルス信号PAが通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ11とを備えたA/D変換回路1において、各遅延ユニットDUには、バッファ12を介して、A/D変換対象となる入力信号Vinを駆動電圧として印加すると共に、バッファ12の出力を各遅延ユニットDUに供給する信号ラインとグランドラインとの間にコンデンサ13を設ける。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

入力信号の電圧レベルに応じた遅延時間でパルス信号を遅延させる複数の遅延ユニットを直列又はリング状に接続してなり、パルス信号を各遅延ユニットの遅延時間にて順次遅延させながら伝送するパルス遅延回路において、

前記入力信号を前記遅延ユニットに供給する信号ラインに、前記遅延ユニットの反転動作時に消費される電力の供給源となる容量素子を設けたことを特徴とするパルス遅延回路。

## 【請求項 2】

前記信号ラインは、抵抗分を有するバッファ回路を介して前記入力信号の入力端子に接続されていることを特徴とする請求項 1 に記載のパルス遅延回路。

## 【請求項 3】

前記容量素子が有する容量分は、該容量分と前記バッファ回路が有する抵抗分とから算出される時定数が前記入力信号について予め規定された最大周波数の逆数より小さな値となるように設定されていることを特徴とする請求項 2 に記載のパルス遅延回路。

## 【請求項 4】

前記容量素子は、CMOSプロセスによって形成されたものであることを特徴とする請求項 1 乃至請求項 3 のいずれかに記載のパルス遅延回路。

## 【請求項 5】

前記遅延ユニットは、前記入力信号を駆動電圧として動作するCMOSインバータゲート回路からなることを特徴とする請求項 1 乃至請求項 4 のいずれかに記載のパルス遅延回路。

## 【請求項 6】

前記遅延ユニットは、電源ラインとの間に電流制御用のトランジスタが付加されたCMOSインバータゲート回路からなり、前記入力信号は前記電流制御用のトランジスタの駆動電圧として印加されることを特徴とする請求項 1 乃至請求項 4 のいずれかに記載のパルス遅延回路。

## 【請求項 7】

前記遅延ユニットは、標準セルを用いて構成されていることを特徴とする請求項 1 乃至請求項 4 のいずれかに記載のパルス遅延回路。

## 【請求項 8】

請求項 1 乃至請求項 8 のいずれかに記載のパルス遅延回路と、

予め設定された測定時間の間に前記パルス遅延回路内で前記パルス信号が通過した前記遅延ユニットの段数に対応する数値データを生成する符号化回路と、

を備え、前記符号化回路が生成する前記数値データを前記入力信号の電圧レベルを表すA/D変換データとして出力することを特徴とするA/D変換回路。

## 【請求項 9】

前記パルス遅延回路は、前記符号化回路を構成するトランジスタよりサイズの大きいトランジスタを用いて構成されていることを特徴とする請求項 8 に記載のA/D変換回路。

## 【請求項 10】

前記パルス遅延回路は、前記遅延ユニットをリング状に接続してなるリングディレイラインからなり、

前記符号化回路は、

前記パルス遅延回路を前記パルス信号が周回した回数をカウントする周回数カウンタと、

前記パルス遅延回路内での前記パルス信号の位置を符号化した値を前記数値データの下位ビットとして出力する下位符号化回路と、

前記周回数カウンタのカウント値を前記数値データの上位ビットとして出力する上位符号化回路と、

を備えることを特徴とする請求項 8 又は請求項 9 に記載のA/D変換回路。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、入力信号の電圧レベルに応じた遅延時間でパルス信号を遅延させる複数の遅延ユニットで構成されたパルス遅延回路、及びそのパルス遅延回路を用いて構成されたA/D変換回路に関する。

**【背景技術】****【0002】**

従来より、全ての部分がデジタル回路により構成されたパルス遅延型（TAD方式）のA/D変換回路が知られている。

10

**【0003】**

このTAD方式のA/D変換回路は、入力信号の電圧レベルに応じた遅延時間でパルス信号を遅延させて出力する遅延ユニットを複数段直列又はリング状に接続してなるパルス遅延回路を用いて構成され、予め設定された測定時間の間に、パルス遅延回路内でパルス信号が通過した遅延ユニットの段数に対応する数値データを、A/D変換データとして出力する。また、TAD方式のA/D変換回路は、デジタル回路のみで構成されているため、CMOSデジタル回路IC製造技術だけを用いて安価かつ容易に製造することができる。

**【0004】**

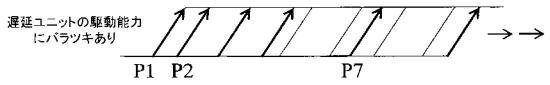

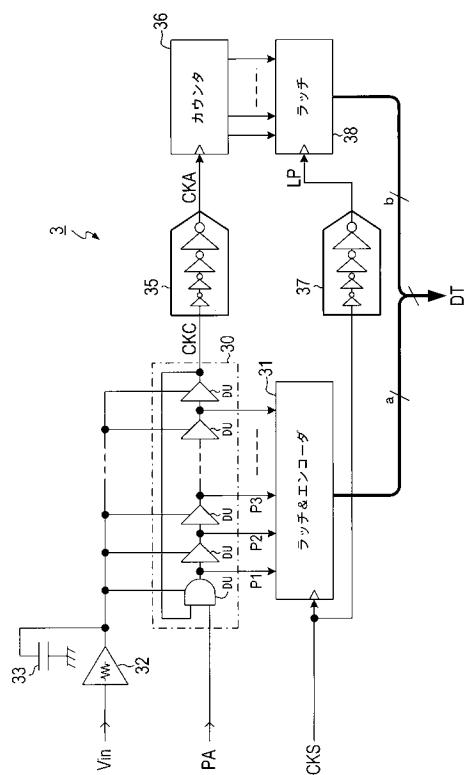

ところで、TAD方式のA/D変換回路を安定に動作させるには、パルス遅延回路を構成する全ての遅延ユニットでの遅延を均一にして、パルスを均等な速度で遅延伝播させる必要がある（図6（a）上段参照）。なお、図6は、パルス遅延回路にパルス信号を入力した場合における各遅延ユニットの出力の変化を模式的に示した説明図であり、図中のPiはi段目の遅延ユニットの出力であることを示す。

20

**【0005】**

しかし、CMOSデジタル回路の微細化に伴い、トランジスタ加工時における加工誤差や微細ゴミの影響は相対的に大きくなっている。これらの影響で、遅延ユニットを構成する各トランジスタの駆動能力がばらつくと、図6（b）に示すように、各遅延ユニットの遅延時間にばらつきが生じ、A/D変換データの分解能（1 LSBに対応する入力電圧幅）のバラツキが大きくなってしまう。

30

**【0006】**

これに対して、A/D変換データの精度に影響を与えるパルス遅延回路を構成するトランジスタのサイズを、パルス遅延回路以外の部分と比較して大きくすることで、加工誤差や微細ゴミ等の影響を相対的に軽減することも行われている（例えば、特許文献1参照）。

【特許文献1】特開2007-6369号公報

**【発明の開示】****【発明が解決しようとする課題】****【0007】**

また、パルス遅延回路を構成する遅延ユニットは、通常、CMOSインバータゲート回路を用いて構成されているため、遅延ユニットの出力信号が反転する毎に、遅延ユニットに貫通電流が流れ、遅延ユニットの電源ライン、即ち、入力信号が印加される信号ラインに、スイッチングノイズが重畳されてしまう。

40

**【0008】**

しかも、上述したようにパルス遅延回路を構成するトランジスタのサイズを大きくすると、各遅延ユニットで消費される電力も増大するため、スイッチングノイズが大きくなってしまう。

**【0009】**

その結果、入力信号の信号レベルがスイッチングノイズによって変動することになるため、その変動によって各遅延ユニットでの遅延にバラツキが発生してしまい（図6（b））

50

参照)、パルス遅延回路は、均等な時間間隔の遅延パルスを発生させることができず、ひいては、A/D変換データの精度を劣化させてしまうという問題があった。

【0010】

本発明は、上記問題点を解決するために、均等な時間間隔の遅延パルスが得られるパルス遅延回路、及び、A/D変換データの分解能が均一なA/D変換回路を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記目的を達成するためになされた請求項1に記載のパルス遅延回路は、入力信号の電圧レベルに応じた遅延時間でパルス信号を遅延させる複数の遅延ユニットを直列又はリンク状に接続してなり、パルス信号を各遅延ユニットの遅延時間にて順次遅延させながら伝送するように構成されている。

10

【0012】

そして、入力信号を遅延ユニットに供給する信号ラインには、遅延ユニットの反転動作時に消費される電力の供給源となる容量素子が設けられている。

【0013】

このように構成された本発明のパルス遅延回路によれば、遅延ユニットが反転動作をする際に、容量素子から電力が供給されるため、信号ライン上のスイッチングノイズの発生を抑制することができ、その結果、各遅延ユニットから均一な時間間隔の遅延パルスを発生させることができる。

20

【0014】

ところで、信号ラインは、請求項2に記載のように、抵抗分を有するバッファ回路を介して入力信号の入力端子に接続されていることが望ましい。

【0015】

この場合、入力端子からバッファ回路を介して入力信号を取り込むことになるため、入力端子を介して外部より侵入するノイズの影響を軽減することができると共に、遅延ユニットの反転動作により信号ラインに重畠されたスイッチングノイズ(電圧変動)が入力端子を介して外部に与える影響を軽減することができる。

【0016】

なお、請求項3に記載のように、容量素子が有する容量分は、その容量分とバッファ回路が有する抵抗分とから算出される時定数が入力信号について予め規定された最大周波数の逆数より小さな値となるように設定されていることが望ましい。

30

【0017】

但し、最大周波数とは、入力信号の信号成分として供給される可能性のある周波数のうち最大のもののことである。従って、本発明のパルス遅延回路によれば、入力信号よりも高い周波数を有する不要ノイズを除去することができる。

【0018】

また、請求項4に記載のように、容量素子は、CMOSプロセスによって形成されたものであることが望ましい。

【0019】

この場合、容量素子を、同じくCMOSプロセスによって形成可能なパルス遅延経路と同じICチップ上に形成することができる。

40

【0020】

ところで、遅延ユニットは、請求項5に記載のように、入力信号を駆動電圧として動作するCMOSインバータゲート回路で構成されていてもよいし、請求項6に記載のように、電源ラインとの間に電流制御用のトランジスタが付加されたCMOSインバータゲート回路からなり、入力信号は電流制御用のトランジスタの駆動電圧として印加されるように構成されていてもよい。

【0021】

また、遅延ユニットは、請求項7に記載のように、標準セルを用いて構成されていても

50

よい。このように標準セルを用いることによって、パルス遅延回路を搭載したICを設計する際の手間を軽減することができる。なお、標準セルとしては、AND, OR, NAND, NOR等の論理回路を用いることができる。

【0022】

次に、請求項8に記載のA/D変換回路は、請求項1乃至請求項8のいずれかに記載のパルス遅延回路と、予め設定された測定時間の間にパルス遅延回路内でパルス信号が通過した遅延ユニットの段数に対応する数値データを生成する符号化回路とを備え、符号化回路が生成する数値データを入力信号の電圧レベルを表すA/D変換データとして出力する。

【0023】

このように構成された本発明のA/D変換回路によれば、パルス遅延回路を構成する各遅延ユニットから均一な時間間隔の遅延パルスが得られるため、1 LSBの値が均一な精度の高いA/D変換データを得ることができる。

【0024】

なお、請求項9に記載のように、パルス遅延回路は、符号化回路を構成するトランジスタよりサイズの大きいトランジスタを用いて構成されていることが望ましい。

【0025】

この場合、トランジスタ加工時における加工誤差や微細ゴミがA/D変換データに与える影響を抑制することができ、より精度の高い遅延パルスやA/D変換データを得ることができる。

【0026】

また、請求項10に記載のように、パルス遅延回路は、遅延ユニットをリング状に接続してなるリングディレイラインからなり、符号化回路が、パルス遅延回路をパルス信号が周回した回数をカウントする周回数カウンタと、パルス遅延回路内のパルス信号の位置を符号化した値を数値データの下位ビットとして出力する下位符号化回路と、周回数カウンタのカウント値を数値データの上位ビットとして出力する上位符号化回路とで構成されているてもよい。

【0027】

このようにパルス遅延回路をリング状に構成することによって、容量素子が電力供給をすべき遅延ユニットの数を大幅に削減することが可能となり、容量素子を挿入することによる安定効果（スイッチングノイズの除去能力）を向上させることができる。

【発明を実施するための最良の形態】

【0028】

以下に本発明の実施形態を図面と共に説明する。

【第1実施形態】

<全体構成>

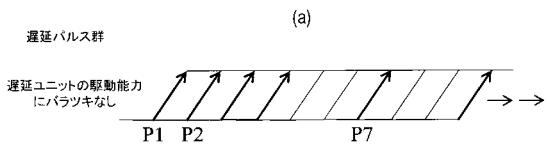

図1(a)は、本発明が適用されたA/D変換回路1の全体構成図である。

【0029】

A/D変換回路1は、図1(a)に示すように、パルス信号PAを所定の遅延時間だけ遅延させて出力する遅延ユニットDUをM(Mは正整数)段直列接続してなるストレートディレイライン(SDL)として構成されたパルス遅延回路10と、サンプリングクロックCKSの立ち上がりタイミングで、パルス遅延回路10内のパルス信号PAの到達位置を検出(ラッチ)し、その検出結果を、パルス信号PAが通過した遅延ユニットDUが先頭から何段目にあるかを表す所定ビットのデジタルデータ(A/D変換データ)DTに変換して出力する符号化回路としてのラッチ&エンコーダ11とから構成されている。なお、図中の符号Pi(i=1, 2, ..., M)は、i段目の遅延ユニットDUの出力を示す。

【0030】

また、パルス遅延回路10を構成する各遅延ユニットDUは、図1(b)に示すように、CMOSインバータゲート回路INVを2段直列接続してなり、入力信号を遅延させて出力するように構成されている。

10

20

30

40

50

## 【0031】

そして、各遅延ユニットDUには、バッファ12を介して、A/D変換対象となる入力信号Vinが駆動電圧として印加されている。従って、各遅延ユニットDUの遅延時間は、入力信号Vinの電圧レベルに対応した時間となり、サンプリングクロックCKSの一周期、即ちサンプリング周期（測定時間）TS内にパルス遅延回路10内のパルス信号PAが通過する遅延ユニットDUの段数は、入力信号Vinの電圧レベル（測定時間TSの間の平均電圧レベル）に比例したものとなる。

## 【0032】

また、バッファ12の出力を各遅延ユニットDUに供給する信号ラインとグランドラインとの間には、コンデンサ13が設けられている。但し、バッファ12の出力抵抗をR、コンデンサ13の容量をCとして、これらR, Cから算出される時定数が、入力信号Vinとして許容される信号成分の最大周波数の逆数（最大周波数となる信号成分の1波長分の周期）より小さな値となるように、コンデンサ13の容量Cは設定されている。

10

## 【0033】

一方、ラッチ&エンコーダ11は、パルス遅延回路10を構成する各遅延ユニットDUの出力P1～PMをラッチするラッチ回路、そのラッチ回路の出力をデジタルデータDTに変換するエンコーダを少なくとも備えており、これらはいずれも一定の電源電圧で駆動されるように構成されている。

## 【0034】

ところで、A/D変換回路1は、コンデンサ13も含めた全ての部位が、CMOS製造プロセスを使用して半導体基板（ICチップ）上の半導体集積回路として構成される。

20

## 【0035】

但し、A/D変換回路1のうち、論理演算回路であるラッチ&エンコーダ11は、当該半導体集積回路に適用するCMOSデジタル回路設計ルールの最小サイズ（例えば最小線幅が90nm）で設計されたトランジスタを用いて構成され、また、各遅延ユニットDUでの遅延を均一にすべきパルス遅延回路10は、ラッチ&エンコーダ11を構成するトランジスタより、大きなサイズに設計されたトランジスタを用いて構成されている。

## 【0036】

また、バッファ12やコンデンサ13は、バッファ12の出力抵抗及びバッファ12の出力から各遅延ユニットDUに至る信号ラインの配線抵抗の合計が、遅延ユニットDUのオン抵抗に対して1/10程度（望ましくは1/100程度）となるように配置されている。具体的には、パルス遅延回路10から1mm（望ましくは100μm）以内に配置される。

30

## 【0037】

## &lt;動作&gt;

このように構成されたA/D変換回路1では、初段の遅延ユニットDUにパルス信号PAを供給すると共に、このパルス信号PAの入力後、サンプリング周期TSが経過した時点で立ち上がるサンプリングクロックCKSを供給すると、ラッチ&エンコーダ11からは、入力信号Vinの電圧レベルを表すデジタルデータ（A/D変換データ）DTが出力される。

40

## 【0038】

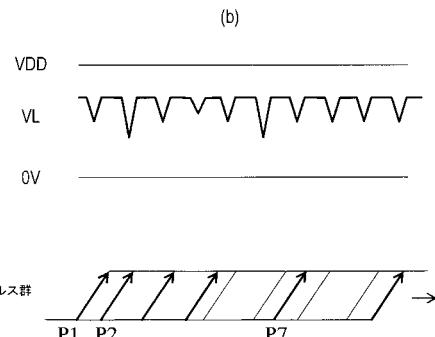

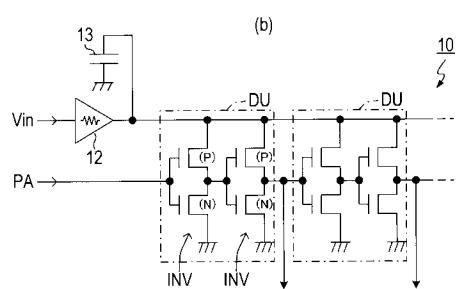

ここで、図2は、バッファ12の出力を各遅延ユニットDUに供給する信号ラインでの電圧レベルVLの変化を示す模式図である。なお、図中の電圧レベルVLを示す線のうち、点線はコンデンサ13が存在しない場合（従来装置）、実線はコンデンサ13が存在する場合（本発明）を示す。

## 【0039】

図2に示すように、コンデンサ13が存在しない場合、遅延ユニットDUを構成するインバータゲート回路INVが反転動作（スイッチング動作）する毎に、インバータゲート回路INV（ひいては遅延ユニットDU）に瞬時的な動作電流が流れる。その動作電流によって、バッファ12の出力抵抗Rや配線抵抗に比例した電圧降下が生じることにより、

50

電圧レベル $V_L$ は一時的に低下する。しかし、コンデンサ13が存在する場合、遅延ユニットDUのスイッチング動作時に、コンデンサ13から電流が供給され、その分、バッファ12を流れる電流が減少するため、出力抵抗Rの影響による電圧レベル $V_L$ の降下が軽減されることになる。

【0040】

<効果>

以上説明したように、A/D変換回路1では、遅延ユニットDUのスイッチング動作時に、瞬時的な動作電流が流れても、コンデンサ13が必要な電流を供給することによって、バッファ12の出力抵抗Rやバッファ12の入力側の配線抵抗には、殆ど電流がながれないため、遅延ユニットDUに供給される電圧レベル $V_L$ の降下が大幅に軽減される。

10

【0041】

その結果、A/D変換回路1によれば、各遅延ユニットDUの遅延を精度よく均一にすることができる、分解能のバラツキが小さく精度の良いA/D変換データDTを生成することができる。

【0042】

また、A/D変換回路1では、コンデンサ13の容量分Cが、バッファ12の抵抗分Rと共にローパスフィルタを形成し、入力信号 $V_{in}$ の許容最大周波数より周波数の高いノイズ成分をカットするように設定されているため、A/D変換データDTからノイズ成分の影響（誤差）を除去することができる。

20

【0043】

更に、A/D変換回路1では、パルス遅延回路10を構成するトランジスタのサイズが、他の部分（ラッチ&エンコーダ11）を構成するトランジスタのサイズより大きいため、製造時に加工誤差が生じたり微細ゴミが付着したりする等しても、パルス遅延回路10を構成するトランジスタでは、ゲートのパターン面積が設計値から外れてしまう割合が小さく、設計した所望の特性（駆動能力等）を得ることができる。

【0044】

その結果、遅延特性が均一な遅延ユニットDUを製造することができ、上述の電圧レベル $V_L$ の降下に対する対策（コンデンサ13）との相乗効果によって、より一層、A/D変換データDTの分解能のバラツキ、即ち微分非直線製誤差（DNL）を小さくすることができ、更には、製造時の歩留まりも向上させることができる。

30

【0045】

また、パルス遅延回路10は、ラッチ&エンコーダ11と比較して、A/D変換回路1全体の中で占める回路規模が小さいため、パルス遅延回路10を構成するトランジスタのサイズを大きくしても、A/D変換回路1全体から見れば、回路規模の増大を極めて小さく抑えることができる。

[第2実施形態]

次に、第2実施形態について説明する。

【0046】

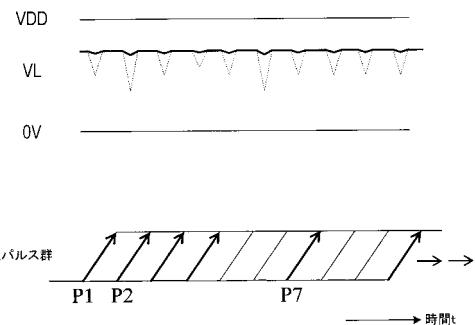

図3は、本実施形態のA/D変換回路3の全体構成図である。図3に示すように、A/D変換回路3は、パルス信号PAを所定の遅延時間だけ遅延させて出力するM（=2a：aは正整数）個の遅延ユニットDUをリング状に連結することにより、パルス信号PAを周回させることができるリングディレイライン（RDL）として構成されたパルス遅延回路30と、サンプリングクロックCKSの立ち上がりタイミングで、パルス遅延回路30内のパルス信号PAの到達位置を検出（ラッチ）し、その検出結果を、パルス信号PAが通過した遅延ユニットDUが先頭から何段目にあるかを表すaビットのデジタルデータ（A/D変換データ）に変換して出力するラッチ&エンコーダ31とを備えている。

40

【0047】

なお、パルス遅延回路30は、初段の遅延ユニットDUは、一方の入力端子を起動用端子とするアンドゲート回路にて構成され、初段以外の他の遅延ユニットDUは、第1実施

50

形態のものと同様に構成されている。そして、初段の遅延ユニットDUの起動用端子とは異なるもう一つの入力端子と、最終段の遅延ユニットDUの出力端子とを接続することでリング状にされている。また、パルス遅延回路30は、図示しないが、パルス遅延回路30内でのパルス信号の周回が継続して行われるように、初段の遅延ユニットDUの入力端子の信号レベルを操作するように構成されている。このようなパルス遅延回路30の具体的な構成は、例えば、特開平6-216721号等に詳述されているため、ここではその詳細についての説明を省略する。

【0048】

そして、各遅延ユニットDUには、バッファ32を介して、A/D変換対象となる入力信号Vinが駆動電圧として印加されている。従って、各遅延ユニットDUの遅延時間は、入力信号Vinの電圧レベルに対応した時間となり、サンプリングクロックCKSの一周期、即ちサンプリング周期（測定時間）TS内にパルス遅延回路30内でのパルス信号PAが通過する遅延ユニットDUの段数は、入力信号Vinの電圧レベル（測定時間TSの間の平均電圧レベル）に比例したものとなる。

10

【0049】

また、バッファ32の出力を各遅延ユニットDUに供給する信号ラインとグランドラインとの間には、コンデンサ33が設けられている。但し、バッファ32の出力抵抗をR、コンデンサ33の容量をCとして、これらR, Cから算出される時定数が、入力信号Vinとして許容される信号成分の最大周波数の逆数（最大周波数となる信号成分の1波長分の周期）より小さな値となるように、コンデンサ33の容量Cは設定されている。

20

【0050】

また、A/D変換回路3は、動作クロックCKAに従ってカウント動作するb（bは正整数）ビットの同期式カウンタからなる周回数カウンタ36と、周回数カウンタ36によるカウント値をラッチパルスLPの立ち上がりタイミングでラッチするラッチ回路38と、パルス遅延回路30を構成する最終段の遅延ユニットDUの出力（周回クロック）CKCを入力とし、出力を動作クロックCKAとして周回数カウンタ36に供給する駆動用バッファ回路35と、サンプリングクロックCKSを入力とし、出力をラッチパルスLPとしてラッチ回路38に供給する遅延用バッファ回路37とを備えている。

【0051】

なお、駆動用バッファ回路35は、CMOSインバータゲート回路を複数段直列接続してなり、その最終段のインバータゲート回路は、周回数カウンタ36のクロックラインの入力容量に対して十分な駆動能力を有する大きさに構成され、他のインバータゲート回路は、初段から最終段に向けて段階的に駆動能力が大きくなるように構成されている。

30

【0052】

また、遅延用バッファ回路37は、駆動用バッファ回路35と同様に構成されており、駆動用バッファ回路35での遅延時間と遅延用バッファ回路37での遅延時間とが等しくなるようにされている。

【0053】

ところで、A/D変換回路3は、第1実施形態のものと同様に、コンデンサ33も含めた全ての部位が、CMOS製造プロセスを使用して半導体基板（ICチップ）上の半導体集積回路として構成される。

40

【0054】

そして、A/D変換回路3のうち、ラッチ&エンコーダ31、周回数カウンタ36、ラッチ回路38は、当該半導体集積回路に適用するCMOSデジタル回路設計ルールの最小サイズで設計されたトランジスタを用いて構成されている。また、各遅延ユニットDUでの遅延を均一にすべきパルス遅延回路30、及び互いの遅延を同一にすべき駆動用バッファ回路35と遅延用バッファ回路37は、ラッチ&エンコーダ31、周回数カウンタ36、ラッチ回路38を構成するトランジスタより大きなサイズに設計されたトランジスタを用いて構成されている。

【0055】

50

また、バッファ32やコンデンサ33は、バッファ32の出力抵抗及びバッファ32の出力から各遅延ユニットDUに至る信号ラインの配線抵抗の合計が、遅延ユニットDUのオン抵抗に対して1/10程度（望ましくは1/100程度）となるように配置されている。具体的には、パルス遅延回路30から1mm（望ましくは100μm）以内に配置されている。

【0056】

＜動作＞

このように構成されたA/D変換回路3では、ラッチ&エンコーダ31は、第1実施形態におけるラッチ&エンコーダ11と同様に動作する。周回数カウンタ36は、動作クロックCKAに従って、パルス遅延回路30内のパルス信号PAの周回回数をカウントし、ラッチ回路38は、ラッチパルスLPに従って、周回数カウンタ36のカウント値をラッチする。

10

【0057】

また、周回数カウンタ36は、駆動用バッファ回路35を介して動作クロックCKAが供給されるため、周回数カウンタ36のビット数が多く、クロックラインの入力容量が大きい場合でも、安定した動作をする。

【0058】

但し、周回数カウンタ36の動作は、動作クロックCKAが駆動用バッファ回路35にて遅延する分だけ、パルス遅延回路30が outputする周回クロックCKCのタイミングより遅れ、また、ラッチ回路38の動作も、ラッチパルスLPが遅延用バッファ回路37にて遅延する分だけ、サンプリングクロックCKSのタイミングより遅れる。

20

【0059】

つまり、周回数カウンタ36の動作が遅れる分だけ、カウント値のラッチタイミングも遅らせることにより、ラッチ回路38がラッチパルスLPに従って周回数カウンタ36のカウント値をラッチするタイミングと、ラッチ&エンコーダ31が、サンプリングクロックCKSに従って、パルス遅延回路30からの遅延パルス（各遅延ユニットDUの出力）をラッチするタイミングとの整合がとれるようにされている。

【0060】

そして、パルス信号PAと、このパルス信号PAの入力後、予め設定されたサンプリング周期TSが経過した時点で立ち上がるサンプリングクロックCKSとが入力されたA/D変換回路3は、ラッチ&エンコーダ31から出力されるaビットのデジタルデータを、入力信号Vinの電圧レベルを表す下位ビットデータ、ラッチ回路38から出力されるbビットのカウント値を、入力信号Vinの電圧レベルを表す上位ビットデータとするa+bビットのデジタルデータ（A/D変換データ）DTを出力する。

30

【0061】

＜効果＞

このように構成されたA/D変換回路3では、バッファ32の出力を各遅延ユニットDUに供給する信号ラインとグランドラインとの間にコンデンサ33が設けられているため、第1実施形態のA/D変換回路1と同様の効果を得ることができる。

40

【0062】

また、A/D変換回路3では、パルス遅延回路30としてリングディレイラインを使用し、パルス遅延回路30でのパルス信号PAの周回数を周回数カウンタ36でカウントするようにされているため、パルス遅延回路30を構成する遅延ユニットDUの段数を大幅に削減でき、回路規模を削減することができる。

【0063】

また、A/D変換回路3では、パルス遅延回路30、駆動用バッファ回路35、遅延用バッファ回路37を構成するトランジスタのサイズが、他の部分（ラッチ&エンコーダ31、周回数カウンタ36、ラッチ回路38）より大きいため、製造時に加工誤差が生じたり微細ゴミが付着する等したとしても、パルス遅延回路30、駆動用バッファ回路35、遅延用バッファ回路37を構成するトランジスタでは、ゲートのパターン面積が設計値か

50

ら外れてしまう割合が小さく、設計した所望の特性を得ることができる。

【0064】

その結果、遅延特性が均一な遅延ユニットDUを製造することができ、上述の電圧レベルVLの降下に対する対策(コンデンサ33)との相乗効果によって、A/D変換データの分解能のバラツキ、即ち微分非直線製誤差(DNL)を小さくすることができると共に、駆動用バッファ回路35と遅延用バッファ回路37の遅延も精度よく一致するため、A/D変換データの上位ビットと下位ビットとの整合性も確保することができ、更には、製造時の歩留まりも向上させることができる。

【第3実施形態】

次に、第3実施形態について説明する。

10

【0065】

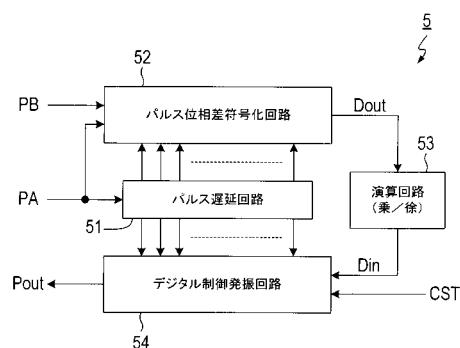

図1は、外部から入力される基準信号PBを分周又は遙倍して所定周波数の出力信号(パルス信号)P<sub>out</sub>を生成する、周波数変換装置5の全体構成図である。

【0066】

図1に示すように、周波数変換装置5は、リング状に連結した多数の遅延ユニットからなり、外部から制御信号PAが入力されているときに各遅延ユニットがパルス信号を順次遅延させて周回させるリングオシレータとして構成されたパルス遅延回路51と、このパルス遅延回路51を構成する各遅延ユニットから順次出力される遅延信号に基づき、基準信号PBの立ち上がりから次の立ち上がりまでの位相差(つまり周期)を2進デジタル値D<sub>out</sub>に変換するパルス位相差符号化回路52と、このパルス位相差符号化回路52にて得られた2進デジタル値D<sub>out</sub>に所定値を乗・除してパルス信号P<sub>out</sub>の出力周期を表わす制御データD<sub>in</sub>を生成する演算回路53と、この演算回路53から出力される制御データD<sub>in</sub>とパルス遅延回路51から順次出力される遅延信号とにに基づき、基準信号PBを分周又は遙倍した周期でパルス信号P<sub>out</sub>を出力するデジタル制御発振回路54とを備え、パルス位相差符号化装置と発振装置との複合装置として構成されている。

20

【0067】

なお、パルス遅延回路51は、第2実施形態におけるパルス遅延回路30、バッファ32、コンデンサ33と同様に構成されている。

【0068】

また、パルス位相差符号化回路52、演算回路53、デジタル制御発振回路54は、例えば、特開平7-183800号公報に詳述された周知のものであるため、ここでは説明を省略する。

30

【0069】

つまり、遅延ユニットDUに対して入力信号V<sub>in</sub>を供給する信号ラインとグランドラインとの間にコンデンサを挿入した構成は、このような周波数変換装置5等に適用してもよい。

【他の実施形態】

以上、本発明のいくつかの実施形態について説明したが、本発明は上記実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において、様々な態様にて実施することが可能である。

40

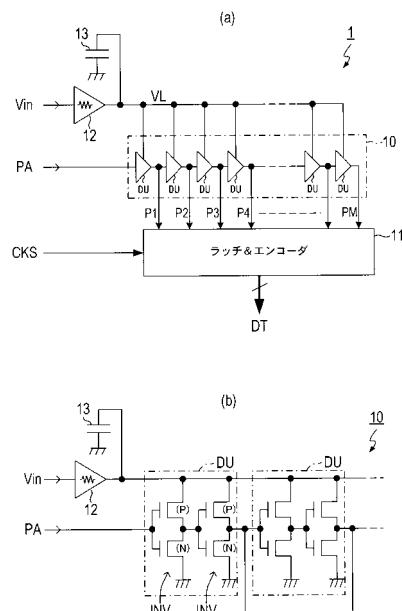

【0070】

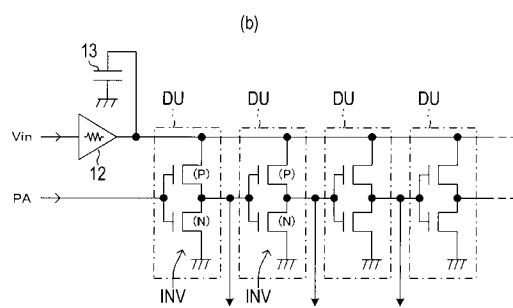

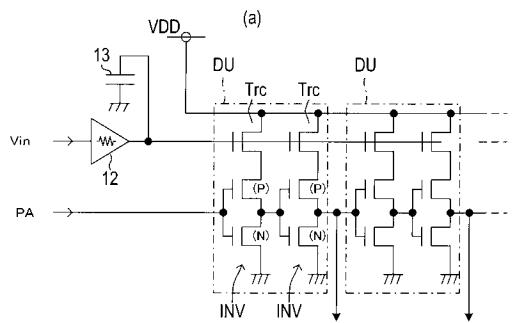

例えば、上記実施形態では、パルス遅延回路10(パルス遅延回路30も同様)を構成する遅延ユニットDUを、Pチャネルトランジスタ(FET)とNチャネルトランジスタ(FET)とからなるCMOSインバータゲート回路INVを2段直列接続することで構成し、入力信号V<sub>in</sub>を駆動電圧として各遅延ユニットDUに印加するものとして説明したが、図5(a)に示すように、遅延ユニットDUを構成する各CMOSインバータゲート回路INVに、駆動電流を外部から制御するための制御トランジスタ(FET)Tr<sub>c</sub>が設けられている場合には、この制御トランジスタの制御端子(ゲート)に、制御信号として、入力信号V<sub>in</sub>を入力するようにしてもよい。但し、この場合、入力信号V<sub>in</sub>を各遅延ユニットDUの制御トランジスタTr<sub>c</sub>に供給する信号ラインにバッファ12(3

50

2) , コンデンサ 13 (33) を接続する。

【0071】

つまり、インバータ INV 等のゲート回路は、直流電源から供給される駆動電流によつても、その動作時間が変化することから、その駆動電流を入力信号 Vin に基づき制御するようにして、上記と同様の効果を得ることができる。

【0072】

また、この場合、入力信号 Vin の対する遅延ユニット DU の入力インピーダンスが高くなるため、バッファ 12 (32) を省略してもよい。

【0073】

また、パルス遅延回路 10, 30 を構成する遅延ユニット DU は、必ずしも 2 段のインバータゲート回路 INV で実現する必要はなく、図 5 (b) に示すように、1 段のインバータゲート回路 INV で実現してもよいし、3 段以上のインバータゲート回路で実現してもよい。

【0074】

更に、遅延ユニット DU は、必ずしもインバータゲート回路 INV で実現する必要はなく、AND, OR, NAND, NOR 等の論理回路の標準セルを用いて実現してもよい。

【0075】

また、バッファ 12, 32 としては、単なる抵抗器を用いてもよい。

【図面の簡単な説明】

【0076】

【図 1】第 1 実施形態の A / D 変換回路の全体構成図。

【図 2】コンデンサの作用を示す模式図。

【図 3】第 2 実施形態の A / D 変換回路の全体構成図。

【図 4】第 3 実施形態の周波数変換装置の全体構成図。

【図 5】遅延ユニットの他の構成例を示す回路図。

【図 6】従来装置の問題点を示す説明図。

【符号の説明】

【0077】

1, 3 ... A / D 変換回路 5 ... 周波数変換装置 10, 30, 51 ... パルス遅延回路

11, 31 ... エンコーダ 12, 32 ... バッファ 13, 33 ... コンデンサ 35 ... 駆動用バッファ回路 36 ... 周回数カウンタ 37 ... 遅延用バッファ回路 38 ... ラッチ回路

52 ... パルス位相差符号化回路 53 ... 演算回路 54 ... デジタル制御発振回路 DU

... 遅延ユニット INV ... CMOS インバータゲート回路 Trc ... 制御トランジスタ

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】