(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7452101号

(P7452101)

(45)発行日 令和6年3月19日(2024.3.19)

(24)登録日 令和6年3月11日(2024.3.11)

(51)国際特許分類

|         |                 |     |         |       |       |

|---------|-----------------|-----|---------|-------|-------|

| G 0 2 F | 1/133 (2006.01) | F I | G 0 2 F | 1/133 | 5 0 5 |

| G 0 2 F | 1/13 (2006.01)  |     | G 0 2 F | 1/13  | 5 0 5 |

| G 0 3 B | 21/00 (2006.01) |     | G 0 3 B | 21/00 | D     |

| G 0 3 B | 21/14 (2006.01) |     | G 0 3 B | 21/14 | Z     |

| H 0 4 N | 5/74 (2006.01)  |     | H 0 4 N | 5/74  | K     |

請求項の数 3 (全21頁)

(21)出願番号 特願2020-35409(P2020-35409)

(22)出願日 令和2年3月3日(2020.3.3)

(65)公開番号 特開2021-139968(P2021-139968)

A)

(43)公開日 令和3年9月16日(2021.9.16)

審査請求日 令和5年3月1日(2023.3.1)

(73)特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74)代理人 100125689

弁理士 大林 章

(74)代理人 100128598

弁理士 高田 聖一

(74)代理人 100121108

弁理士 高橋 太朗

(72)発明者 保坂 宏行

長野県諏訪市大和3丁目3番5号 セイ

コーエプソン株式会社内

審査官 植田 裕美子

最終頁に続く

(54)【発明の名称】 液晶プロジェクター

## (57)【特許請求の範囲】

## 【請求項1】

複数のパネル画素を含む液晶パネルと、

前記複数のパネル画素の投射位置をシフトさせるシフトデバイスと、

前記液晶パネルおよび前記シフトデバイスを制御する表示制御回路と、

を含み、

前記表示制御回路は、

前記液晶パネルを制御して、

非隣接の関係にある  $k$  ( $k$  は 3 以上の整数) 個の表示画素を、1 つのパネル画素によつ

て一のフレーム期間における  $k$  個の単位期間で表現させ、

前記シフトデバイスを制御して、

前記  $k$  個の単位期間毎に、前記投射位置を異ならせ、

前記表示画素および前記パネル画素は、

第 1 軸および第 2 軸に沿ってマトリクス状に配列し、

前記  $k$  個の表示画素は、

前記第 1 軸に沿って隣り合わず、かつ、前記第 2 軸に沿って隣り合わず、

第 1 単位期間に対応する表示画素と第 2 単位期間に対応する表示画素とは、

前記第 1 軸または前記第 2 軸の一方の軸に沿って表示画素で 1 画素以上離間し、かつ、前

記第 1 軸または前記第 2 軸の他方の軸に沿って表示画素で 2 画素以上離間し、

前記第 1 単位期間の投射位置から前記第 2 単位期間の投射位置へのシフト量と、

前記第2単位期間の投射位置から第3単位期間の投射位置へのシフト量と、

前記第3単位期間の投射位置から次の単位期間の投射位置へのシフト量と、

—を同じに制御する

液晶プロジェクター。

【請求項2】

前記表示制御回路は、

前記シフトデバイスを、

前記第1単位期間の投射位置から前記第2単位期間の投射位置にシフトさせる際の第1

方向と、前記第2単位期間の投射位置から前記第3単位期間の投射位置にシフトさせる際

の第2方向とのなす角度、および、前記第2方向と、前記第3単位期間の投射位置から次

の単位期間の投射位置にシフトさせる際の第3方向とのなす角度、

10

を同じに制御する

請求項1に記載の液晶プロジェクター。

【請求項3】

前記液晶パネルは、

第1色に対応した第1液晶パネルと、

前記第1色とは異なる第2色に対応した第2液晶パネルと、

前記第1色および第2色とは異なる第3色に対応した第3液晶パネルと、

を含み、

前記第1液晶パネルにおけるパネル画素と、

20

前記第2液晶パネルにおけるパネル画素と、

前記第3液晶パネルにおけるパネル画素と、

を合成する

請求項1または2に記載の液晶プロジェクター。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶プロジェクターに関する。

【背景技術】

【0002】

液晶プロジェクターでは、液晶パネルで表示される画素の解像度を擬似的に高めるために、スクリーン等へ投射される投射画素を、シフトデバイスによってシフトさせる技術が知られている（例えば特許文献1参照）。この技術によって、液晶パネルの画素数よりも多くの画素数が投射されているかのようにユーザに視認させることができる。

30

【先行技術文献】

【特許文献】

【0003】

【文献】特開2008-203626号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記技術では、表示させる画像によっては、表示品位が低下する、とい

う課題があった。

【課題を解決するための手段】

【0005】

上記課題を解決するために、本開示の一態様に係る液晶プロジェクターは、複数のパネ

ル画素を含む液晶パネルと、前記複数のパネル画素の投射位置をシフトさせるシフトデバ

イスと、前記液晶パネルおよび前記シフトデバイスを制御する表示制御回路と、を含み、

前記表示制御回路は、前記液晶パネルを制御して、非隣接の関係にあるk（kは3以上の

整数）個の表示画素を、1つのパネル画素によって一のフレーム期間におけるk個の単位

40

10

20

30

40

50

期間で表現させ、前記シフトデバイスを制御して、前記k個の単位期間毎に、前記投射位置を異ならせる。

【図面の簡単な説明】

【0006】

【図1】第1実施形態に係る液晶プロジェクターを示す図である。

【図2】液晶プロジェクターの構成を示すブロック図である。

【図3】液晶プロジェクターにおける液晶パネルの構成を斜視図である。

【図4】液晶パネルの構造を示す断面図である。

【図5】液晶パネルの電気的な構成を示すブロック図である。

【図6】液晶パネルにおける画素回路の構成を示す図である。

10

【図7】表示画素配列とパネル画素配列との関係等を示す図である。

【図8】液晶プロジェクターにおけるフレーム期間と単位期間とを示す図である。

【図9】表示画素とパネル画素の投射位置との関係を示す図である。

【図10】シフトデバイスの動作を示す図である。

【図11】液晶パネルにおける液晶素子の電圧 - 透過率特性の一例を示す図である。

【図12】配向不良の発生例を説明するため図である。

【図13】映像データによる表示画素配列の例を示す図である。

【図14】配向不良の発生例を説明するため図である。

【図15】シフトデバイスの他の動作を示す図である。

【図16】第2実施形態における表示画素とパネル画素の投射位置との関係を示す図である。

20

【図17】シフトデバイスの動作を示す図である。

【図18】シフトデバイスの他の動作を示す図である。

【図19】シフトデバイスの他の動作を示す図である。

【図20】比較例における表示画素配列とパネル画素配列との関係等を示す図である。

【図21】比較例に係る表示画素とパネル画素の投射位置との関係を示す図である。

【図22】比較例におけるシフトデバイスの動作を示す図である。

【図23】比較例における配向不良の発生例を説明するため図である。

【発明を実施するための形態】

【0007】

30

以下、実施形態に電気光学装置について図面を参照して説明する。なお、各図において、各部の寸法および縮尺は、実際のものと適宜に異ならせてある。また、以下に述べる実施の形態は、好適な具体例であるから、技術的に好ましい種々の限定が付されているが、本開示の範囲は、以下の説明において特に本開示を限定する旨の記載がない限り、これらの形態に限られるものではない。

【0008】

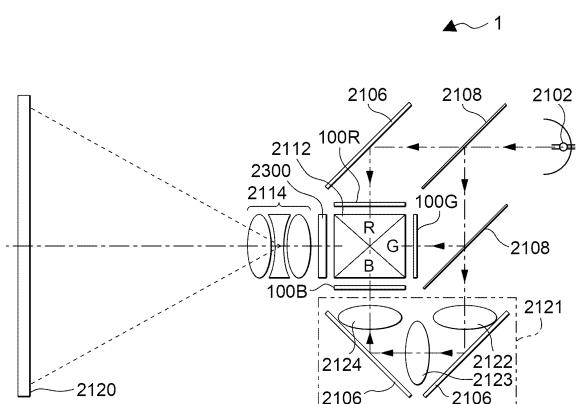

図1は、第1実施形態に係る液晶プロジェクター1の光学的な構成を示す図である。図に示されるように、液晶プロジェクター1は、液晶パネル100R、100Gおよび100Bを含む。また、液晶プロジェクター1の内部には、ハロゲンランプ等の白色光源からなるランプユニット2102が設けられている。このランプユニット2102から射出された投射光は、内部に配置された3枚のミラー2106および2枚のダイクロイックミラー-2108によって、赤(R)、緑(G)および青(B)の3原色に分離される。このうち、Rの光は液晶パネル100Rに、Gの光は液晶パネル100Gに、Bの光は液晶パネル100Bに、それぞれ入射する。

40

なお、Bの光路は、他の赤や緑と比較して長い。そこで、Bの光は、光路での損失を防ぐために、入射レンズ2122、リレーレンズ2123および出射レンズ2124からなるリレーレンズ系2121を介して液晶パネル100Bに導かれる。

【0009】

液晶パネル100Rは、マトリクス状に配列する複数の画素回路を有する。画素回路は液晶素子を含み、液晶パネル100Rの液晶素子は、後述するRに対応するデータ信号に

50

基づいて駆動されて、当該データ信号の電圧に応じた透過率となる。このため、液晶パネル 100R において、液晶素子の透過率を個別に制御することによって、R の透過像を生成することができる。同様に、液晶パネル 100G は、G に対応するデータ信号に基づいて G の透過像を生成し、液晶パネル 100B は、B に対応するデータ信号に基づいて B の透過像を生成する。

#### 【0010】

液晶パネル 100R、100G および 100B によってそれぞれ生成された各色の透過像は、ダイクロイックプリズム 2112 に三方向から入射する。そして、ダイクロイックプリズム 2112 において、R および B の光は 90 度に屈折する一方、G の光は直進する。したがって、ダイクロイックプリズム 2112 が各色の画像を合成する。ダイクロイックプリズム 2112 による合成像はシフトデバイス 2300 を介して投射レンズ 2114 に入射する。

#### 【0011】

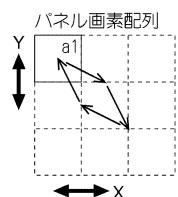

シフトデバイス 2300 は、ダイクロイックプリズム 2112 から出射され、スクリーン 2120 に至る合成像の光軸を、当該光軸に直交する二軸に沿ってシフトさせる。詳細には、シフトデバイス 2300 は、スクリーン 2120 に投射される合成像の位置を、投射面をみたときに横の X 軸と縦の Y 軸との二軸に沿った方向にシフト可能となっている。投射レンズ 2114 は、シフトデバイス 2300 を介した合成像を、スクリーン 2120 に拡大して投射する。

なお、液晶パネル 100R、100B による透過像は、ダイクロイックプリズム 2112 により反射した後に投射されるのに対し、液晶パネル 100G による透過像は直進して投射される。したがって、液晶パネル 100R、100B による各透過像は、液晶パネル 100G の透過像に対して左右反転した関係となる。

また、説明の便宜のため、シフトデバイス 2300 を介して投射レンズ 2114 によってスクリーン 2120 に投射される合成像を構成する画素を投射画素と呼び、スクリーン 2120 に投射された投射画素の位置を投射位置と呼ぶことにする。

#### 【0012】

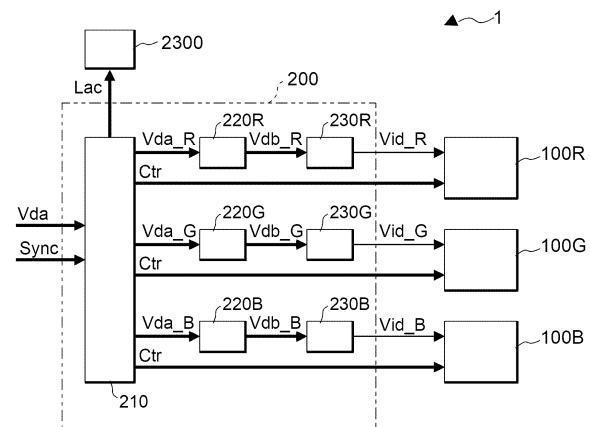

図 2 は、液晶プロジェクター 1 の電気的な構成を示すブロック図である。図に示されるように、液晶プロジェクター 1 は、表示制御回路 200 と、上述した液晶パネル 100R、100G および 100B と、シフトデバイス 2300 とを含む。

#### 【0013】

図示省略されたホスト装置等の上位装置から、映像データ Vda が同期信号 Sync に同期して供給される。映像データ Vda は、表示すべき画像における画素の階調レベルを、例えば R GB 毎に 8 ビットで指定する。

なお、映像データ Vda により階調レベルが指定される画像の画素を表示画素と呼び、液晶パネル 100R、100G および 100B の画素回路で表現される画素をパネル画素と呼ぶことにする。

#### 【0014】

液晶パネル 100R、100G または 100B の単体では、パネル画素が縦軸および横軸に沿ってマトリクス状に配列する。本実施形態において、スクリーン 2120 に投射されるカラー画像は、液晶パネル 100R、100G および 100B の各透過像を合成することで、すなわち重ね合わせることで表現される。

したがって、カラー画像の最小単位である画素は、液晶パネル 100R による赤の副画素、液晶パネル 100G による緑の副画素、および、液晶パネル 100B による青の副画素に分けることができる。ただし、液晶パネル 100R、100G および 100B における副画素について、色について特定する必要がない場合、および、単に明暗のみを問題とする場合等では、副画素と敢えて表記する必要がない。そこで本説明では、液晶パネル 100R、100G および 100B における表示単位についても、画素（パネル画素）として説明する。

一方、映像データ Vda で階調レベルが指定される表示画素の配列密度は、液晶パネル 1

10

20

30

40

50

00R、100Gまたは100Bを合成したパネル画素の配列密度と比較して、例えば縦軸で2倍、横軸で2倍となっている。

#### 【0015】

同期信号Syncには、映像データVdaの垂直走査開始を指示する垂直同期信号や、水平走査開始を指示する水平同期信号、および、映像データVdaにおいて1つの表示画素が供給されるタイミングを示すクロック信号が含まれる。

#### 【0016】

表示制御回路200は、映像制御回路210、処理回路220R、220Gおよび220B、変換回路230R、230Gおよび230Bを含む。

映像制御回路210は、上位装置からの映像データVdaのうち、1または複数フレーム期間分を蓄積する。そして、映像制御回路210は、後述のシフトデバイス2300によって1つのフレーム期間での投射位置のシフト数に対応させて、フレーム期間分の映像データVdaを分割してRGB別に出力する。なお、映像制御回路210が出力する映像データVdaのうち、Rの成分を映像データVda\_Rと表記し、Gの成分を映像データVda\_Gと表記し、Bの成分を映像データVda\_Bと表記し、色を特定しないで説明する場合には映像データVdaと表記する。

10

#### 【0017】

第1実施形態では、投射位置のシフト数が4つである。このため、映像制御回路210は、4つの単位期間に対応させ、フレーム期間分の映像データVdaを4つに分割する。そして、映像制御回路210は、4つ単位期間毎に、映像データをRGBごとに分割して出力し、スクリーン2120への投射画素が単位期間に対応する投射位置となるように、シフトデバイス2300を単位期間毎に制御する。

20

#### 【0018】

なお、単位期間毎の投射位置について、また、各投射位置において液晶パネル100のパネル画素が、映像データVdaで指定される表示画素のうち、どの表示画素を表現するかについては後述する。

#### 【0019】

処理回路220Rは、映像データVda\_Rに後述する補正処理を施し、映像データVdb\_Rとして出力し、変換回路230Rは、映像データVdb\_Rをアナログ電圧のデータ信号Vid\_Rに変換して液晶パネル100Rに供給する。なお、処理回路220Rは、映像データVda\_Rを遅延させるための遅延回路や、階調レベル同士を比較したり、階調レベルを演算したりするための中央演算処理装置(プロセッサ)などを含む。

30

同様に、処理回路220Gは、映像データVda\_Gに補正処理を施して映像データVdb\_Gとして出力し、変換回路230Gは、映像データVdb\_Gをアナログ電圧のデータ信号Vid\_Gに変換して液晶パネル100Gに供給する。処理回路220Bは、映像データVda\_Bに補正処理を施して映像データVdb\_Bとして出力し、変換回路230Bは、映像データVdb\_Bをアナログ電圧のデータ信号Vid\_Bに変換して液晶パネル100Bに供給する。

処理回路220G、220Bについても、同様に遅延回路やプロセッサを有するが、遅延回路やプロセッサについては、処理回路220R、220Gおよび220Bについて共用してもよい。

40

#### 【0020】

次に、液晶パネル100R、100Gおよび100Gについて説明する。液晶パネル100R、100Gおよび100Gについては、入射する光の色、すなわち波長だけが異なり、構造的には共通である。そこで、液晶パネル100R、100Gおよび100Gについては、符号を100として、色を特定しないで一般的に説明する。

#### 【0021】

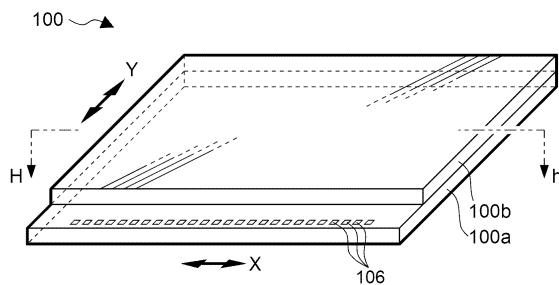

図3は、液晶パネル100の要部を示す図であり、図4は、図3におけるH-h線で切断した断面図である。

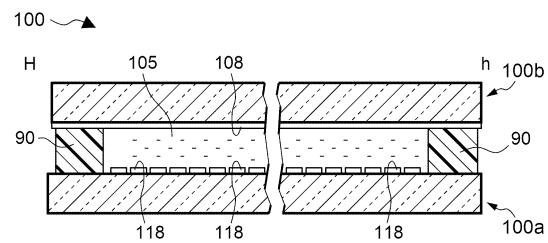

これらの図に示されるように、液晶パネル100では、画素電極118が設けられた素子基板100aと、コモン電極108が設けられた対向基板100bとが、一定の間隙を

50

保ちつつ、互いに電極形成面が対向するようにシール材 90 によって貼り合わせられ、この間隙に液晶 105 が封入されている。

【0022】

素子基板 100a および対向基板 100b としては、それぞれガラスや石英などの光透過性を有する基板が用いられる。図 3 に示されるように、素子基板 100a における一辺は、対向基板 100b から張り出している。この張り出した領域に、図における X 軸に沿って複数の端子 106 が設けられている。複数の端子 106 には、図示省略された FPC (Flexible Printed Circuits) 基板の一端が接続される。

なお、当該 FPC 基板の他端は、表示制御回路 200 に接続されて、上述した各種の信号などが液晶パネル 100 に供給される。

10

【0023】

素子基板 100a において対向基板 100b に向かう面には、画素電極 118 が、例えば ITO (Indium Tin Oxide) などの透明性を有する導電層のパターニングによって形成される。

なお、素子基板 100a の対向面および対向基板 100b の対向面には、電極以外にも様々な要素が設けられるが、図では省略されている。

【0024】

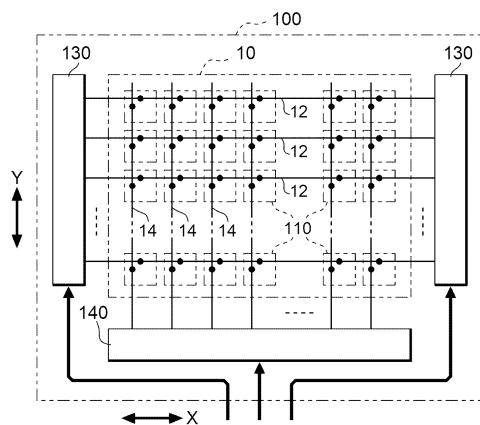

図 5 は、液晶パネル 100 の電気的な構成を示すブロック図である。液晶パネル 100 には、表示領域 10 の周縁に、走査線駆動回路 130 およびデータ線駆動回路 140 が設けられる。

20

【0025】

液晶パネル 100 の表示領域 10 においては、画素回路 110 がマトリクス状に配列される。詳細には、表示領域 10 において、複数本の走査線 12 が図において X 軸に沿って延在して設けられ、また、複数本のデータ線 14 が Y 軸に沿って延在し、かつ、走査線 12 と互いに電気的な絶縁を保って設けられる。そして、複数本の走査線 12 と複数本のデータ線 14 との交差に対応して画素回路 110 がマトリクス状に設けられる。

【0026】

走査線 12 の本数を m とし、データ線 14 の本数を n とした場合、画素回路 110 は、縦 m 行 × 横 n 列でマトリクス状に配列する。m、n は、いずれも 2 以上の整数である。走査線 12 と画素回路 110 とにおいて、マトリクスの行を区別するために、図において上から順に 1、2、3、…、(m - 1)、m 行と呼ぶ場合がある。同様にデータ線 14 および画素回路 110 において、マトリクスの列を区別するために、図において左から順に 1、2、3、…、(n - 1)、n 列と呼ぶ場合がある。

30

【0027】

走査線駆動回路 130 は、映像制御回路 210 による制御にしたがって、走査線 12 を例えば 1、2、3、…、m 行目という順番で 1 本ずつ選択し、選択した走査線 12 への走査信号を H レベルとする。なお、走査線駆動回路 130 は、選択した走査線 12 以外の走査線 12 への走査信号を L レベルとする。

データ線駆動回路 140 は、処理回路 220R、220G または 220B のうち、対応する色の回路から供給されたデータ信号を 1 行分ラッチするとともに、走査線 12 への走査信号が H レベルとなった期間において、当該走査線 12 に位置する画素回路 110 に、データ線 14 を介して出力する。

40

【0028】

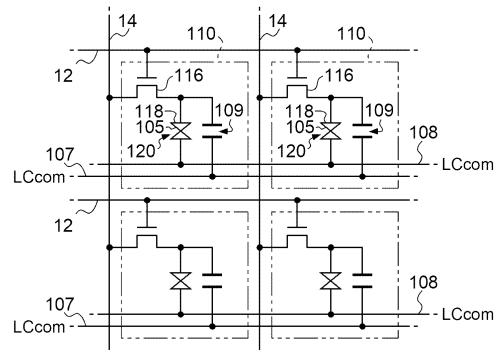

図 6 は、隣り合う 2 本の走査線 12 と、隣り合う 2 本のデータ線 14 との交差に対応する 2 行 2 列の計 4 個の、画素回路 110 の等価回路を示す図である。

図に示されるように、画素回路 110 は、トランジスター 116 と液晶素子 120 とを含む。トランジスター 116 は、例えば n チャネル型の薄膜トランジスターである。画素回路 110 において、トランジスター 116 のゲートノードは、走査線 12 に接続される一方、そのソースノードはデータ線 14 に接続され、そのドレインノードは、平面視で略正方形の画素電極 118 に接続される。

50

## 【0029】

画素電極 118 に対向するようにコモン電極 108 が全画素に対して共通に設けられる。コモン電極 108 には電圧  $L\ C_{com}$  が印加される。そして、画素電極 118 とコモン電極 108 との間には上述したように液晶 105 が挟持される。したがって、画素回路 110 每に、画素電極 118 およびコモン電極 108 によって液晶 105 を挟持した液晶素子 120 が構成される。

また、液晶素子 120 に対して並列に蓄積容量 109 が設けられる。蓄積容量 109 において、一端が画素電極 118 に接続され、他端が容量線 107 に接続されている。容量線 107 は、時間的に一定の電圧、例えばコモン電極 108 への印加電圧と同じ電圧  $L\ C_{com}$  が印加される。画素回路 110 は、走査線 12 が延在する X 軸とデータ線 14 が延在する Y 軸とに沿ってマトリクス状に配列するので、画素回路 110 に含まれる画素電極 118 についても Y 軸および X 軸に沿って配列する。

## 【0030】

走査信号が H レベルとなった走査線 12 では、当該走査線 12 に対応して設けられる画素回路 110 のトランジスター 116 がオンする。トランジスター 116 のオンにより、データ線 14 と画素電極 118 とが電気的に接続された状態となるので、データ線 14 に供給されたデータ信号が、オンしたトランジスター 116 を介して画素電極 118 に到達する。走査線 12 が L レベルになると、トランジスター 116 はオフになるが、画素電極 118 に到達したデータ信号の電圧は、液晶素子 120 の容量性および蓄積容量 109 によって保持される。

## 【0031】

周知のように、液晶素子 120 では、画素電極 118 およびコモン電極 108 によって生じる電界に応じて液晶分子の配向が変化する。したがって、液晶素子 120 は、印加された電圧の実効値に応じた透過率となる。

なお、液晶素子 120 においてパネル画素として機能する領域、すなわち、電圧の実効値に応じた透過率となる領域は、素子基板 100a および対向基板 100b を平面視したときに、画素電極 118 とコモン電極 108 とが重なる領域である。画素電極 118 は、平面視で略正方形であるので、液晶パネル 100 によるパネル画素の形状も略正方形となる。

また、本実施形態では、液晶素子 120 への印加電圧が高くなるにつれて、透過率が高くなるノーマリーブラックモードであるとする。

## 【0032】

液晶素子 120 の画素電極 118 にデータ信号を供給する動作が、1、2、3、…、m 行目という順番で実行されることによって、m 行 n 列で配列する画素回路 110 の液晶素子 120 の各々にデータ信号に応じた電圧が保持される。このような電圧の保持によって各液晶素子 120 が目的とする透過率となり、m 行 n 列で配列するパネル画素によって、対応する色の透過像が生成される。

## 【0033】

次に、表示すべき画像における表示画素と、液晶パネル 100 のパネル画素と、シフトデバイス 2300 による光軸のシフトと、の関係について説明する。なお、シフトデバイス 2300 については、上述したようにダイクロイックプリズム 2112 からの出射方向の光軸をシフトさせるが、便宜的に当該シフト量については、パネル画素における一辺の長さに換算して説明する。

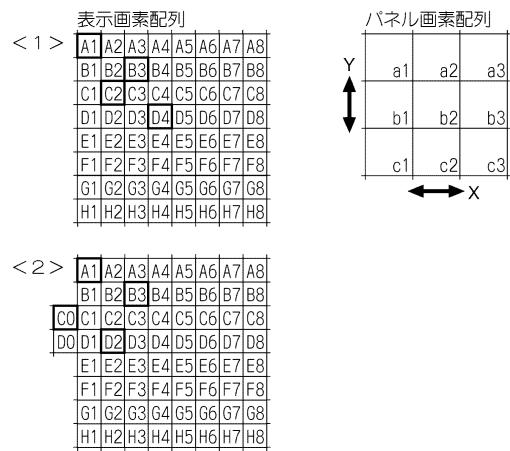

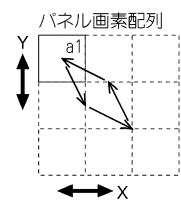

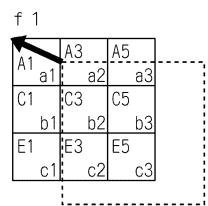

## 【0034】

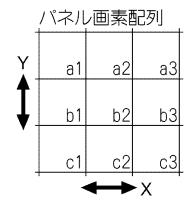

図 7 は、表示画素配列とパネル画素配列との関係等を説明するための図である。ここで、表示画素配列とは、映像データ  $V_{da}$  により階調レベルが指定される表示画素の配列をいう。パネル画素配列とは、液晶パネル 100 の画素回路 110、すなわち、パネル画素の配列をいう。なお、図 7 における表示画素配列は、映像データ  $V_{da}$  で指定され、表示すべき表示画素の配列のうち、一部だけが抜き出されて示される。また、図 7 におけるパネル画素配列は、液晶パネル 100 の画素回路の配列のうち、表示画素配列の一部に対応する

配列が抜き出されて示される。

【0035】

なお、映像データVdaで指定される画像に含まれる複数の表示画素を、液晶パネル100のパネル画素と区別するために、表示画素毎に、符号として1行目にA1、A2、…、A8が、2行目にB1、B2、…、B8が、3行目にC1、C2、…、C8が、以下同様に、8行目にH1、H2、…、H8が、付与されている。

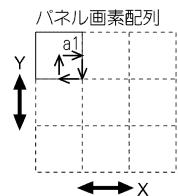

また、液晶パネル100に含まれる複数のパネル画素を、表示画素と区別するために、パネル画素毎に、符号として1行目にa1、a2、a3が、2行目にb1、b2、b3が、3行目にc1、c2、c3が、付与されている。

【0036】

上述したように、本実施形態では、映像データVdaで階調レベルが指定される表示画素の配列密度が、液晶パネル100におけるパネル画素の配列密度と比較して、縦軸で2倍、横軸で2倍となっている。このため、液晶パネル100における1つのパネル画素は、映像データVdaで指定される4つの表示画素を時分割で表現する。詳細には、本実施形態では、フレーム期間を4つの単位期間に分割し、当該4つの表示画素を、単位期間毎に投射位置をシフトしながら、液晶パネル100における1つのパネル画素が表現する。

【0037】

なお、パネル画素が表示画素を表現するとは、映像データVdaで指定される表示画素に対応し、当該映像データVdaにより指定される階調レベルに対応するデータ信号をパネル画素に供給することによって、当該パネル画素が表示画素の階調レベルに対応した透過率となることをいう。

また、フレーム期間とは、映像データVdaで指定される画像の1コマを表示するのに要する期間をいう。換言すれば、1つのパネル画素が、4つの表示画素を時分割で表現するのに要する期間をいう。1つのフレーム期間の長さは、垂直同期期間と同じ場合、例えば同期信号Syncに含まれる垂直同期信号の周波数が60Hzであれば、当該垂直同期信号の1周期分に相当する16.7ミリ秒となる。

【0038】

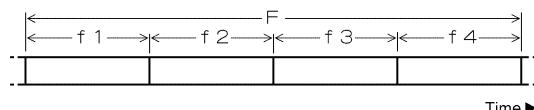

図8は、第1実施形態におけるフレーム期間と単位期間とを説明するための図である。

この図に示されるように、本実施形態においてフレーム期間Fは、4つの単位期間に分割される。フレーム期間Fにおける4つの単位期間を便宜的に区別するために符号が、時間の順にf1、f2、f3、f4と付与されている。

【0039】

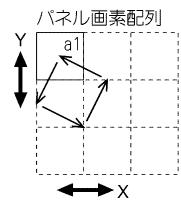

本実施形態では、フレーム期間Fにおいて、図7の<1>において太枠で示される4つの表示画素A1、C2、D4およびB3が、液晶パネル100における1つのパネル画素a1で表現される。

なお、図7の<1>の太枠は、パネル画素a1が表現する4つの表示画素A1、C2、D4およびB3について便宜的に着目しているが、他のパネル画素が他の表示画素を同様に表現する。例えば、パネル画素a2は、4つの表示画素A3、C4、D6およびB5を表現し、パネル画素b1は、4つの表示画素C1、E2、F4およびD3を表現する。

【0040】

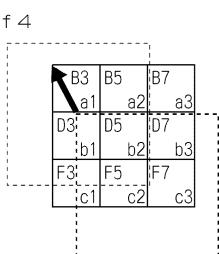

図9は、第1実施形態において、液晶パネル100のパネル画素と、パネル画素が表現する表示画素と、表示画素の投射位置との関係を単位期間毎に示す図である。詳細には、図9は、図7における液晶パネル100の9つのパネル画素が、単位期間毎に、どの表示画素を表現し、投射位置がどのようにシフトするのかを示す図である。また、図10は、シフトデバイス2300による投射位置のシフトを、パネル画素a1を基準にとって説明するための図である。

【0041】

フレーム期間Fの単位期間f1において、液晶パネル100のパネル画素a1、a2、a3、b1、b2、b3、c1、c2およびc3は、順に表示画素A1、A3、A5、C1、C3、C5、E1、E3およびE5を表現する。

10

20

30

40

50

単位期間  $f_2$  において、シフトデバイス 2300 は、投射位置を、太い破線で示される単位期間  $f_1$  の投射位置から、X 軸で右に右方向にパネル画素の 0.5 画素および Y 軸で下にパネル画素の 1.0 画素シフトさせる。また、単位期間  $f_2$  では、パネル画素 a1、a2、a3、b1、b2、b3、c1、c2 および c3 は、順に表示画素 C2、C4、C6、E2、E4、E6、G2、G4 および G6 を表現する。

単位期間  $f_3$  において、シフトデバイス 2300 は、投射位置を、太い破線で示される単位期間  $f_2$  の投射位置から、X 軸で右にパネル画素の 1.0 画素および Y 軸で下にパネル画素の 0.5 画素シフトさせる。なお、細い破線は、単位期間  $f_1$  におけるシフト位置である。また、単位期間  $f_3$  では、パネル画素 a1、a2、a3、b1、b2、b3、c1、c2 および c3 は、順に表示画素 D4、D6、D8、F4、F6、F8、H4、H6 および H8 を表現する。10

単位期間  $f_4$  において、シフトデバイス 2300 は、投射位置を、太い破線で示される単位期間  $f_3$  の投射位置から、X 軸で左にパネル画素の 0.5 画素および Y 軸で上にパネル画素の 1.0 画素シフトさせる。また、単位期間  $f_4$  では、パネル画素 a1、a2、a3、b1、b2、b3、c1、c2 および c3 は、順に表示画素 B3、B5、B7、D3、D5、D7、F3、F5 および F7 を表現する。

単位期間  $f_4$  の後の次のフレーム期間 F の単位期間  $f_1$  において、シフトデバイス 2300 は、投射位置を、破線で示される単位期間  $f_4$  の投射位置から、X 軸で左にパネル画素の 1.0 画素および Y 軸で上にパネル画素の 0.5 画素シフトさせて単位期間  $f_1$  における位置に戻す。20

#### 【0042】

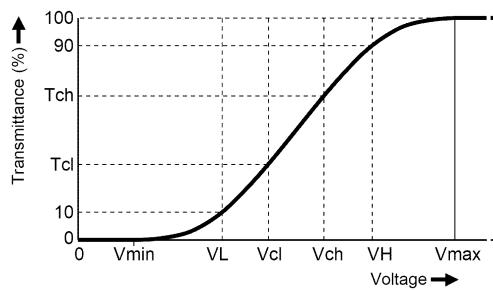

配向不良による表示品位の低下について説明する。

図 11 は、ノーマリーブラックモードにおける液晶素子 120 の印加電圧 - 透過率の特性 (V-T 特性) の一例を示す図である。ノーマリーブラックモードにおいて、高い階調レベルが指定されて、透過率が高くなるパネル画素 (明画素) では、液晶素子 120 における印加電圧が高い。一方、低い階調レベルが指定されて、透過率が低くなるパネル画素 (暗画素) では、液晶素子 120 における印加電圧が低い。このような明画素と暗画素について、便宜的に次のように定義する。

明画素は、階調レベルに応じた電圧が画素電極 118 に印加された場合に、当該画素電極 118 を含む液晶素子 120 への印加電圧が VH を上回る画素であり、暗画素は、液晶素子 120 への印加電圧が VL を下回る画素である。ここで、VH、VL については、30

$$VH > VL$$

の関係にある。また、液晶素子 120 の印加電圧が電圧 VL である場合、例えば相対透過率が 10 % となり、電圧 VH である場合、例えば相対透過率が 90 % となる。ただし、VL および VH については、他の相対透過率に対応した電圧であってもよい。

#### 【0043】

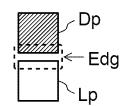

図 12 に示されるように、液晶パネル 100 において、明画素 Lp と暗画素 Dp とが隣り合うと、画素電極 118 同士の電圧差が大きくなり、2 つの画素の境界 Edg 付近における横電界によって液晶分子の配向不良が発生しやすくなる。一般に、画素電極 118 同士の電圧差が大きくなるほど、隣り合う 2 つの画素の境界付近で発生する配向不良の程度が大きくなる。配向不良が発生した画素は、階調レベルに対応した透過率とはならないので、表示品位を低下させる。40

#### 【0044】

本実施形態における配向不良により表示品位の低下が抑えられる点を説明する前に、便宜的に比較例について説明する。

#### 【0045】

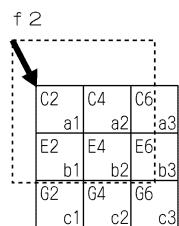

図 20 は、比較例における表示画素配列とパネル画素配列との関係等を説明するための図である。比較例では、フレーム期間 F において、図の表示画素配列において太枠で示される 4 つの表示画素 A1、A2、B2 および B1 が、液晶パネル 100 における 1 つのパネル画素 a1 で表現される。50

**【 0 0 4 6 】**

図21は、比較例において、液晶パネル100のパネル画素と、パネル画素が表現する表示画素と、表示画素の投射位置との関係を単位期間毎に示す図である。また、図22は、シフトデバイス2300による投射位置のシフトを、パネル画素a1を基準にとって説明するための図である。

**【 0 0 4 7 】**

比較例では、フレーム期間Fの単位期間f1において、液晶パネル100のパネル画素a1、a2、a3、b1、b2、b3、c1、c2およびc3は、順に表示画素A1、A3、A5、C1、C3、C5、E1、E3およびE5を表現する。

単位期間f2において、シフトデバイス2300は、投射位置を、破線で示される単位期間f1の投射位置から、X軸で右にパネル画素の0.5画素シフトさせる。また、単位期間f2では、パネル画素a1、a2、a3、b1、b2、b3、c1、c2およびc3は、順に表示画素A2、A4、A6、C2、C4、C6、E2、E4およびE6を表現する。

単位期間f3において、シフトデバイス2300は、投射位置を、単位期間f2の投射位置から、Y軸で下にパネル画素の0.5画素シフトさせる。また、単位期間f3では、パネル画素a1、a2、a3、b1、b2、b3、c1、c2およびc3は、順に表示画素B2、B4、B6、D2、D4、D6、E2、E4およびE6を表現する。

単位期間f4において、シフトデバイス2300は、投射位置を、破線で示される単位期間f3の投射位置から、X軸で左にパネル画素の0.5画素シフトさせる。また、単位期間f4では、パネル画素a1、a2、a3、b1、b2、b3、c1、c2およびc3は、順に表示画素B1、B3、B5、D1、D3、D5、F1、F3およびF5を表現する。

単位期間f4の後の次のフレーム期間Fの単位期間f1において、シフトデバイス2300は、投射位置を、破線で示される単位期間f4の投射位置から、Y軸で上にパネル画素の0.5画素シフトさせて単位期間f1における位置に戻す。

**【 0 0 4 8 】**

比較例によれば、実施形態と同様に、パネル画素の配列密度に対して、縦軸で2倍、横軸で2倍とした配列密度の表示画素を表現することが可能である。しかしながら、比較例では、次のような場合に、表示品位が低下する。具体的には、映像データVdaで指定される画像の一部が図13の表示画素配列で示されるように、明るい表示画素を背景として表示画素C1～C8が暗く指定される場合に、表示品位が低下する。

**【 0 0 4 9 】**

比較例では、図23に示されるように、単位期間f1において液晶パネル100のパネル画素b1、b2およびb3が、暗画素に指定される表示画素C1、C3およびC5をこの順で表現する。次に、単位期間f2において液晶パネル100のパネル画素b1、b2およびb3が、暗画素に指定される表示画素C2、C4およびC6をこの順で表現する。他の単位期間f3、f4については特に説明を要しないであろう。

**【 0 0 5 0 】**

比較例において、液晶パネル100のパネル画素によって、図13に示されるような表示画素を表現する場合、図23に示されるように、連続する単位期間f1、f2において明画素と暗画素とが隣り合うので、隣り合う部分の境界付近において破線で示されるように配向不良が発生する。詳細には、単位期間f1においてパネル画素b1～b3とパネル画素c1～c3との境界で配向不良が発生し、引き続き単位期間f2においても同じパネル画素同士の境界で発生する。

なお、配向不良は、パネル画素b1～b3とパネル画素c1～c3との境界付近のみ示しているが、実際には、パネル画素b1～b3とパネル画素a1～a3との境界付近でも発生する。

**【 0 0 5 1 】**

単位期間f3、f4では、パネル画素が、暗画素に指定された表示画素C1～C6を表

10

20

30

40

50

現せず、明画素のみを表現する。ただし、パネル画素 b<sub>1</sub> ~ b<sub>3</sub> とパネル画素 c<sub>1</sub> ~ c<sub>3</sub>との境界で発生した配向不良は、連続する 2 つの単位期間 f<sub>1</sub>、f<sub>2</sub> で発生しているので、配向不良の程度が大きい。このため、単位期間 f<sub>3</sub> において、パネル画素 b<sub>1</sub> ~ b<sub>3</sub> が明画素に変化しても、発生した配向不良は直ちに消失せずに、残留する。単位期間 f<sub>4</sub>においても、単位期間 f<sub>3</sub> よりも程度は小さくなるが、配向不良は引き続き残留する。

#### 【 0 0 5 2 】

これに対して、本実施形態では、映像データ V<sub>da</sub> で指定される画像の一部が図 1 3 の表示画素配列で示される場合、液晶パネル 100 における 9 つのパネル画素は、単位期間毎に、図 1 4 に示されるように表示画素を表現する。

本実施形態においても、単位期間 f<sub>1</sub> では、比較例と同様に、暗画素であるパネル画素 b<sub>1</sub> ~ b<sub>3</sub> と明画素であるパネル画素 c<sub>1</sub> ~ c<sub>3</sub> とが隣り合うので、この境界付近において破線で示されるように配向不良が発生する。

また、単位期間 f<sub>2</sub> においても、暗画素であるパネル画素 a<sub>1</sub> ~ a<sub>3</sub> と明画素であるパネル画素 b<sub>1</sub> ~ b<sub>3</sub> とが隣り合うので、この境界付近において破線で示されるように配向不良が発生する。

#### 【 0 0 5 3 】

ただし、本実施形態では、単位期間 f<sub>1</sub> においてパネル画素 b<sub>1</sub> ~ b<sub>3</sub> とパネル画素 c<sub>1</sub> ~ c<sub>3</sub>との境界で発生した配向不良は、当該単位期間 f<sub>1</sub> のみで発生するので、配向不良の程度が小さい。このため、単位期間 f<sub>2</sub> において、パネル画素 b<sub>1</sub> ~ b<sub>3</sub> が明画素に変化したとき、程度が小さくなる。

単位期間 f<sub>2</sub> においてパネル画素 a<sub>1</sub> ~ a<sub>3</sub> とパネル画素 b<sub>1</sub> ~ b<sub>3</sub>との境界で発生した配向不良は、当該単位期間 f<sub>2</sub> のみで発生するので、配向不良の程度が小さい。このため、単位期間 f<sub>3</sub> において、パネル画素 a<sub>1</sub> ~ a<sub>3</sub> が明画素に変化したとき、程度が小さくなる。

したがって、本実施形態では、図 1 3 の表示画素配列を液晶パネル 100 における 9 つのパネル画素が表現する場合に、ある単位期間で発生した配向不良は、当該単位期間経過後では、消滅に向かう。このため、本実施形態では、比較例と比べると、配向不良が発生する程度が結果的に小さいので、表示品位の低下を抑えることができる。

#### 【 0 0 5 4 】

換言すれば、本実施形態では、図 7 の <1> で示されるように、1 つフレーム期間 F において 1 つのパネル画素が表現する 4 つの表示画素は、X 軸に沿って隣り合わず、かつ、Y 軸に沿って隣り合わない。すなわち、本実施形態では、1 つのパネル画素が表現する 4 つの表示画素は、X 軸および Y 軸で非隣接の関係にある。このため、表示画素が図 1 3 に示されるように、暗い表示画素と明るい表示画素とが Y 軸に沿って隣り合い、かつ、X 軸に沿って連続する配列の場合に、液晶パネル 100 では、ある単位期間において、2 つの隣り合うパネル画素の一方が暗画素となり、他方が明画素となる状態になるものの、次の単位期間では、当該状態が解消される。

したがって、本実施形態では、表示画素が上記配列の場合に、暗画素と明画素とが隣り合う状態は、2 以上の単位期間で継続して発生しないので、表示品位の低下を抑えることができる。

なお、実施形態では、表示画素が図 1 3 に示されるような配列を例にとって説明したが、暗い表示画素と明るい表示画素とが X 軸に沿って隣り合い、かつ、Y 軸に沿って連続する場合でも同様である。

#### 【 0 0 5 5 】

本実施形態では、シフトデバイス 2300 が、いずれかの単位期間から次の単位期間までにおいて、投射位置を、X 軸または Y 軸の一方をパネル画素の 0.5 画素、および、X 軸または Y 軸の他方をパネル画素の 1.0 画素シフトする。すなわち、いずれかの単位期間から次の単位期間まで、シフトデバイス 2300 のシフト量（大きさ）は、パネル画素でみて  $1.12 (\{0.5^2 + 1.0^2\}^{1/2})$  画素で揃っている。

したがって、本実施形態では、シフトデバイス 2300 におけるシフト動作が緩慢であ

10

20

30

40

50

る場合に現れる影響が各単位期間においてほぼ均等となるので、当該影響に起因する表示品位の低下を目立たなくすることができる。

【0056】

なお、第1実施形態では、パネル画素a1が表示画素A1、C2、D4、B3という順番で表現したが、表示画素A1、B3、D4、C2という逆の順番で表現してもよい。逆の順番で表現する場合、シフトデバイス2300によるシフト動作は、パネル画素a1を基準にとってみれば、図15に示される通りとなる。

【0057】

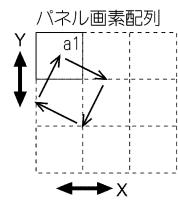

次に、第2実施形態に係る液晶プロジェクター1について説明する。

第2実施形態は、第1実施形態とは、1つのパネル画素が表現する4つの表示画素およびシフトデバイス2300によるシフト動作が異なるのみであり、液晶プロジェクターの構造や構成については第1実施形態と同様である。そこで、第2実施形態については、第1実施形態との相違点を中心に説明する。

10

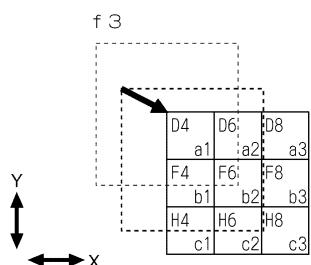

【0058】

図16は、第2実施形態において、液晶パネル100のパネル画素と、パネル画素が表現する表示画素と、表示画素の投射位置との関係を単位期間毎に示す図である。また、図17は、シフトデバイス2300による投射位置のシフトを、パネル画素a1を基準にとって説明するための図である。

【0059】

第2実施形態では、フレーム期間Fにおいて、図7の<2>において太枠で示される4つの表示画素A1、C0、D2およびB3が、液晶パネル100における1つのパネル画素a1で表現される。

20

【0060】

フレーム期間Fの単位期間f1において、液晶パネル100のパネル画素a1、a2、a3、b1、b2、b3、c1、c2およびc3が、順に表示画素A1、A3、A5、C1、C3、C5、E1、E3およびE5を表現する。

単位期間f2において、シフトデバイス2300は、投射位置を、破線で示される単位期間f1の投射位置から、X軸で左にパネル画素の0.5画素およびY軸で下にパネル画素の1.0画素シフトさせる。また、単位期間f2では、パネル画素a1、a2、a3、b1、b2、b3、c1、c2およびc3は、順に表示画素C0、C2、C4、E0、E2、E4、G0、G2およびG4を表現する。

30

単位期間f3において、シフトデバイス2300は、投射位置を、破線で示される単位期間f2の投射位置から、X軸で右にパネル画素の1.0画素およびY軸で下にパネル画素の0.5画素シフトさせる。また、単位期間f3では、パネル画素a1、a2、a3、b1、b2、b3、c1、c2およびc3は、順に表示画素D2、4、D6、F2、F4、F6、H2、H4およびH6を表現する。

単位期間f4において、シフトデバイス2300は、投射位置を、破線で示される単位期間f3の投射位置から、X軸で右にパネル画素の0.5画素およびY軸で上にパネル画素の1.0画素シフトさせる。また、単位期間f4では、パネル画素a1、a2、a3、b1、b2、b3、c1、c2およびc3は、順に表示画素B3、B5、B7、D3、D5、D7、F3、F5およびF7を表現する。

40

単位期間f4の後の次のフレーム期間Fの単位期間f1において、シフトデバイス2300は、投射位置を、破線で示される単位期間f4の投射位置から、X軸で左にパネル画素の1.0画素およびY軸で上にパネル画素の0.5画素シフトさせて単位期間f1における位置に戻す。

【0061】

第2実施形態では、図7の<2>で示されるように、1つフレーム期間Fにおいて1つのパネル画素が表現する4つの表示画素は、X軸に沿って隣り合わず、かつ、Y軸に沿って隣り合わない。このため、第2実施形態においても、第1実施形態と同様に、表示画素が図13に示されるように、暗い表示画素と明るい表示画素とがY軸に沿って隣り合い、

50

かつ、X軸に沿って連続する配列の場合に、液晶パネル100では、特に図示しないが、ある単位期間において、2つの隣り合うパネル画素の一方が暗画素となり、他方が明画素となる状態になるものの、次の単位期間では、当該状態が解消される。

#### 【0062】

第2実施形態では、第1実施形態と同様に、シフトデバイス2300が、いずれかの単位期間から次の単位期間までにおいて、投射位置を、X軸またはY軸の一方をパネル画素の0.5画素、および、X軸またはY軸の他方をパネル画素の1.0画素シフトする。したがって、第2実施形態では、シフトデバイス2300におけるシフト動作が緩慢である場合に現れる影響が各単位期間においてほぼ均等となるので、当該影響に起因する表示品位の低下を目立たなくすることができる。

10

#### 【0063】

さらに、第2実施形態では、シフトデバイス2300が、ある単位期間の投射位置から次の単位期間の投射位置までのシフト方向と、当該次の単位期間の投射位置から次の次の単位期間の投射位置までのシフト方向とがなす角度は、いずれも90度である。

例えば単位期間f1の投射位置から単位期間f2の投射位置へのシフト方向と、単位期間f2の投射位置から単位期間f3の投射位置へのシフト方向とのなす角度は90度であり、単位期間f2の投射位置から単位期間f3の投射位置へのシフト方向と、単位期間f3の投射位置から単位期間f4の投射位置へのシフト方向とのなす角度についても90度である。また、単位期間f3の投射位置から単位期間f4の投射位置へのシフト方向と、単位期間f4の投射位置から次フレームの単位期間f1の投射位置へのシフト方向とのなす角度についても90度である。

20

このため、第2実施形態では、単位期間の遷移時におけるシフト角度が揃うので、シフト動作が緩慢であることの影響を受けにくい。

#### 【0064】

なお、第2実施形態では、パネル画素a1が表示画素A1、C0、D2、B3という順番で表現したが、表示画素A1、B3、D2、C0という逆の順番で表現してもよい。逆の順番で表現する場合、シフトデバイス2300によるシフト動作は、パネル画素a1を基準にとてみれば、図18に示される通りとなる。

#### 【0065】

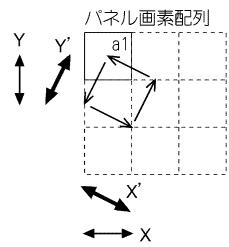

また、第2実施形態において、シフトデバイス2300によってシフト動作させる二軸を、横のX軸および縦のY軸ではなく、図19に示されるように、例えばX軸およびY軸を時計回りに $26.6$ ( $\tan^{-1}(0.5/1.0)$ )度回転させたX'軸およびY'軸としてもよい。このようにシフトデバイス2300によるシフト動作させる二軸をX'軸およびY'軸にすると、単位期間の遷移時におけるシフト量は、X'軸またはY'軸の一方のみに沿った1.0画素で済むので、シフトデバイス2300の制御が簡易かつ容易となる。

30

#### 【0066】

実施形態では、フレーム期間を4つの単位期間に分けた構成とした。すなわち、フレーム期間Fで表現される表示画素の個数kを「4」として説明した。ただし、kは、「4」に限られず、1つのフレーム期間で1つのパネル画素が表現する表示画素がX軸で隣り合わず、かつ、Y軸で隣り合わなければ、「3」以上であればよい。

40

また、実施形態における最大のシフト量については、例えばX軸でパネル画素の0.5画素シフトし、Y軸でパネル画素の1.0画素シフトしたときの、1.12画素であるが、シフトデバイス2300における応答性が良ければ、これ以上としてもよい。

#### 【0067】

また、上述した実施形態等では、ノーマリーブラックモードで説明したが、ノーマリーホワイトモードとしてもよい。また、液晶パネル100R、100G、100Bを透過型としたが、反射型としてもよい。

#### 【0068】

以上に例示した形態から、例えば以下の態様が把握される。

#### 【0069】

50

ひとつの態様（態様 1）に係る液晶プロジェクターは、複数のパネル画素を含む液晶パネルと、前記複数のパネル画素の投射位置をシフトさせるシフトデバイスと、前記液晶パネルおよび前記シフトデバイスを制御する表示制御回路と、を含み、前記表示制御回路は、前記液晶パネルを制御して、非隣接の関係にある  $k$  ( $k$  は 3 以上の整数) 個の表示画素を、1 つのパネル画素によって一のフレーム期間における  $k$  個の単位期間で表現させ、前記シフトデバイスを制御して、前記  $k$  個の単位期間毎に、前記投射位置を異ならせる。

この態様によれば、暗い表示画素と明るい表示画素とが連続する場合に、液晶パネルでは、2 つのパネル画素が暗画素と明画素とに別れ、かつ、2 つの単位期間で連続する状態を回避することができる。このため、暗画素と明画素とが隣り合うことによって生じる表示品位の低下を低減することが可能となる。

10

#### 【0070】

態様 1 の具体的な態様（態様 2）では、前記表示画素および前記パネル画素は、第 1 軸および第 2 軸に沿ってマトリクス状に配列し、前記  $k$  個の表示画素は、前記第 1 軸に沿って隣り合はず、かつ、前記第 2 軸に沿って隣り合わない。

なお、X 軸が第 1 軸の一例であり、Y 軸が第 2 軸の一例である。

#### 【0071】

態様 1 または態様 2 の具体的な態様（態様 3）では、前記表示制御回路は、前記シフトデバイスを、第 1 単位期間の投射位置から第 2 単位期間への投射位置のシフト量と、前記第 2 単位期間の投射位置から第 3 単位期間への投射位置のシフト量と同じに制御する。

この態様によれば、単位期間の遷移時におけるシフトデバイスのシフト量が揃うので、シフトデバイスにおけるシフト動作が緩慢であっても、その影響を受けにくい。

20

なお、単位期間  $f_1$  が第 1 单位期間の一例であり、単位期間  $f_2$  が第 2 单位期間の一例であり、単位期間  $f_3$  が第 3 单位期間の一例である。

#### 【0072】

態様 3 の具体的な態様（態様 4）では、前記表示制御回路は、前記シフトデバイスを、前記第 1 単位期間の投射位置から前記第 2 単位期間の投射位置にシフトさせる際の第 1 方向と、前記第 2 単位期間の投射位置から前記第 3 単位期間の投射位置にシフトさせる際の第 2 方向とのなす角度、および、前記第 2 方向と、前記第 3 単位期間の投射位置から次の単位期間の投射位置にシフトさせる際の第 3 方向とのなす角度、同じに制御する。

この態様によれば、単位期間の遷移時におけるシフト角度が揃うので、シフト動作が緩慢であることの影響を受けにくい。

30

#### 【0073】

態様 1 乃至 4 のいずれかの具体的な態様（態様 5）では、前記液晶パネルは、第 1 色に対応した第 1 液晶パネルと、前記第 1 色とは異なる第 2 色に対応した第 2 液晶パネルと、前記第 1 色および第 2 色とは異なる第 3 色に対応した第 3 液晶パネルと、を含み、前記第 1 液晶パネルにおけるパネル画素と、前記第 2 液晶パネルにおけるパネル画素と、前記第 3 液晶パネルにおけるパネル画素と、を合成する。

この態様によれば、カラー画像において暗画素と明画素とが隣り合うことによって生じる表示品位の低下を低減することが可能となる。

なお、赤（R）が第 1 色の一例であり、緑（G）が第 2 色の一例であり、青（B）が第 3 色の一例である。

40

#### 【符号の説明】

#### 【0074】

1 ... 液晶プロジェクター、100R、100G、100B ... 液晶パネル、110 ... 画素回路、118 ... 画素電極、120 ... 液晶素子、200 ... 表示制御回路、210 ... 映像制御回路、220R、220R、220G ... 処理回路。

50

## 【図面】

## 【図 1】

## 【図 2】

10

## 【図 3】

## 【図 4】

20

30

40

50

【図 5】

【図 6】

10

【図 7】

20

【図 8】

30

40

50

【図 9】

【図 10】

10

【図 11】

【図 12】

20

30

40

50

【図 1 3】

| 表示画素配列 |    |    |    |    |    |    |    |

|--------|----|----|----|----|----|----|----|

| A1     | A2 | A3 | A4 | A5 | A6 | A7 | A8 |

| B1     | B2 | B3 | B4 | B5 | B6 | B7 | B8 |

| C1     | C2 | C3 | C4 | C5 | C6 | C7 | C8 |

| D1     | D2 | D3 | D4 | D5 | D6 | D7 | D8 |

| E1     | E2 | E3 | E4 | E5 | E6 | E7 | E8 |

| F1     | F2 | F3 | F4 | F5 | F6 | F7 | F8 |

| G1     | G2 | G3 | G4 | G5 | G6 | G7 | G8 |

| H1     | H2 | H3 | H4 | H5 | H6 | H7 | H8 |

Y

↔ X

【図 1 4】

| f 1 |    |    |

|-----|----|----|

| A1  | A3 | A5 |

| C1  | C3 | C5 |

| E1  | E3 | E5 |

| F1  | F3 | F5 |

| G1  | G3 | G5 |

| H1  | H3 | H5 |

| f 2 |    |    |

|-----|----|----|

| C2  | C4 | C6 |

| E2  | E4 | E6 |

| F2  | F4 | F6 |

| G2  | G4 | G6 |

| H2  | H4 | H6 |

f 3

| f 3 |    |    |

|-----|----|----|

| D4  | D6 | D8 |

| F4  | F6 | F8 |

| H4  | H6 | H8 |

| c1  | c2 | c3 |

f 4

| f 4 |    |    |

|-----|----|----|

| B3  | B5 | B7 |

| D3  | D5 | D7 |

| F3  | F5 | F7 |

| c1  | c2 | c3 |

10

【図 1 5】

【図 1 6】

| f 1 |    |    |

|-----|----|----|

| A1  | A3 | A5 |

| C1  | C3 | C5 |

| E1  | E3 | E5 |

| F1  | F3 | F5 |

| G1  | G3 | G5 |

| H1  | H3 | H5 |

| f 2 |    |    |

|-----|----|----|

| C0  | C2 | C4 |

| E0  | E2 | E4 |

| F0  | F2 | F4 |

| G0  | G2 | G4 |

| H0  | H2 | H4 |

f 3

| f 3 |    |    |

|-----|----|----|

| D2  | D4 | D6 |

| F2  | F4 | F6 |

| H2  | H4 | H6 |

| c1  | c2 | c3 |

f 4

| f 4 |    |    |

|-----|----|----|

| B3  | B5 | B7 |

| D3  | D5 | D7 |

| F3  | F5 | F7 |

| c1  | c2 | c3 |

20

30

40

50

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

| 表示画素配列 |    |    |    |    |    |

|--------|----|----|----|----|----|

| A1     | A2 | A3 | A4 | A5 | A6 |

| B1     | B2 | B3 | B4 | B5 | B6 |

| C1     | C2 | C3 | C4 | C5 | C6 |

| D1     | D2 | D3 | D4 | D5 | D6 |

| E1     | E2 | E3 | E4 | E5 | E6 |

| F1     | F2 | F3 | F4 | F5 | F6 |

【図 2 1】

| f 1 |    |    |

|-----|----|----|

| A1  | A3 | A5 |

| a1  | a2 | a3 |

| C1  | C3 | C5 |

| b1  | b2 | b3 |

| E1  | E3 | E5 |

| c1  | c2 | c3 |

| f 2 |    |    |

|-----|----|----|

| A2  | A4 | A6 |

| a1  | a2 | a3 |

| C2  | C4 | C6 |

| b1  | b2 | b3 |

| E2  | E4 | E6 |

| c1  | c2 | c3 |

【図 2 2】

f 3

| f 4 |    |    |

|-----|----|----|

| B2  | B4 | B6 |

| a1  | a2 | a3 |

| D2  | D4 | D6 |

| b1  | b2 | b3 |

| E2  | E4 | E6 |

| c1  | c2 | c3 |

10

20

30

40

50

【図 2 3】

|       |       |       |

|-------|-------|-------|

| A1    | A3    | A5    |

| a1    | a2    | a3    |

| C1    | C3    | C5    |

| ..... | ..... | ..... |

| E1    | E3    | E5    |

| c1    | c2    | c3    |

|       |       |       |

|-------|-------|-------|

| A2    | A4    | A6    |

| a1    | a2    | a3    |

| C2    | C4    | C6    |

| ..... | ..... | ..... |

| E2    | E4    | E6    |

| c1    | c2    | c3    |

f 3

|       |       |       |

|-------|-------|-------|

| B2    | B4    | B6    |

| a1    | a2    | a3    |

| D2    | D4    | D6    |

| ..... | ..... | ..... |

| F2    | F4    | F6    |

| c1    | c2    | c3    |

f 4

|       |       |       |

|-------|-------|-------|

| B1    | B3    | B5    |

| a1    | a2    | a3    |

| D1    | D3    | D5    |

| ..... | ..... | ..... |

| F1    | F3    | F5    |

| c1    | c2    | c3    |

10

20

30

40

50

---

フロントページの続き

(56)参考文献

特開2019-039995 (JP, A)

特開2004-070365 (JP, A)

特開2005-057457 (JP, A)

特開平4-63332 (JP, A)

米国特許出願公開第2019/0101807 (US, A1)

中国特許出願公開第106385575 (CN, A)

(58)調査した分野 (Int.Cl., DB名)

G02F 1/133

G02F 1/13

G03B 21/00 - 21/64

H04N 5/66 - 5/74

G09G 3/18, 3/36

G09G 3/00 - 3/08, 3/12, 3/16

G09G 3/19 - 3/26, 3/30, 3/34, 3/38