(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5027605号

(P5027605)

(45) 発行日 平成24年9月19日(2012.9.19)

(24) 登録日 平成24年6月29日(2012.6.29)

(51) Int.Cl.

H01L 21/60 (2006.01)

H01L 21/66 (2006.01)

F 1

H01L 21/60 301N

H01L 21/66 E

請求項の数 12 (全 11 頁)

(21) 出願番号 特願2007-246576 (P2007-246576)

(22) 出願日 平成19年9月25日 (2007.9.25)

(65) 公開番号 特開2009-76808 (P2009-76808A)

(43) 公開日 平成21年4月9日 (2009.4.9)

審査請求日 平成22年1月27日 (2010.1.27)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 110001427

特許業務法人前田特許事務所

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

プローブ領域と非プローブ領域とからなる電極パッドを備え、

前記プローブ領域の直下には、前記電極パッドと接続部を介して接続されたパッドメタルが配置され、

前記非プローブ領域の直下には、配線が配置され、

前記パッドメタルと前記配線とは同一層に形成されたことを特徴とする半導体装置。

## 【請求項 2】

前記電極パッドは、2列以上の千鳥状に配置されたことを特徴とする請求項1に記載の半導体装置。

## 【請求項 3】

前記プローブ領域は、前記電極パッドのうち、前記配線が延びる方向に対して略平行に延びる前記電極パッドの中心線より20μm以内の領域に配置されており、

前記非プローブ領域は、前記電極パッドのうちプローブ領域以外の領域に配置されていることを特徴とする請求項1に記載の半導体装置。

## 【請求項 4】

前記接続部は、前記電極パッドと前記パッドメタルとの間の空間を埋める金属で構成されていることを特徴とする請求項1に記載の半導体装置。

## 【請求項 5】

前記接続部は、複数のビア形状の金属体で構成されていることを特徴とする請求項1に

記載の半導体装置。

**【請求項 6】**

1つの前記接続部を構成する前記金属体同士は、平面的に見て互いに等間隔且つ均一に配置されていることを特徴とする請求項5に記載の半導体装置。

**【請求項 7】**

前記プローブ領域と前記非プローブ領域との境界線を光学的に区別可能な目印が形成されていることを特徴とする請求項1～6のうちいずれか1つに記載の半導体装置。

**【請求項 8】**

前記目印は、前記電極パッドのトップメタル層によって形成されていることを特徴とする請求項7に記載の半導体装置。 10

**【請求項 9】**

前記目印は、前記電極パッド周辺部上に設けられた保護膜によって形成されていることを特徴とする請求項7に記載の半導体装置。

**【請求項 10】**

前記電極パッドと、前記パッドメタル及び前記配線が形成された層との間には層間絶縁膜が形成されていることを特徴とする請求項1～9のうちいずれか1つに記載の半導体装置。

**【請求項 11】**

前記プローブ領域及び前記非プローブ領域は外部接続が可能であることを特徴とする請求項1～10のうちいずれか1つに記載の半導体装置。 20

**【請求項 12】**

前記配線は、内部回路と電気的に接続されていることを特徴とする請求項1～11のうちいずれか1つに記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体集積回路装置における外部接続用の電極パッドに関するものであり、特に千鳥状に配置された電極パッドとその直下を通過する引き出し配線との配置ならびに電極パッドの断面構造に関するものである。

**【背景技術】**

**【0002】**

近年、デジタル化社会が進展するに従って、半導体装置の高機能化、小型化、低コスト化の要望が高まってきている。半導体装置の低コスト化のためには1ウエハあたりの半導体チップの採れ数を増やすことが有効であり、そのため微細化とともにチップ面積が縮小化している。このチップ面積の縮小化と多機能化に伴う多ピン化が相伴って、半導体チップの外周部分に存在する外部接続用の電極パッドを高密度に配置する必要が出てきた。電極パッドのサイズは外部接続の際に用いるワイヤボンドやバンプなどの接続性やピッチ、信頼性さらには検査に用いるプローブのピッチなどの要因でもはやこれ以上小さくできない領域に有る。このため、半導体チップ外周部の電極パッドを1列でなく千鳥状に配置する半導体装置が実現されている（例えば、特許文献1参照）。 40

**【0003】**

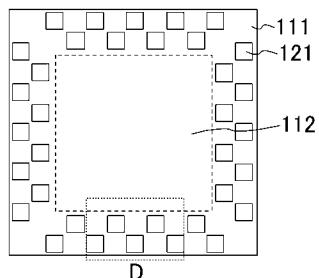

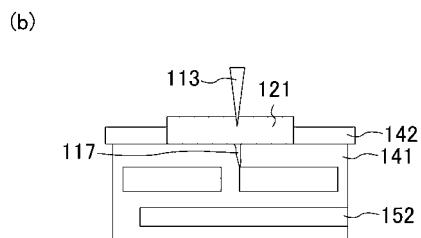

図9(a)、(b)は、それぞれ第1の従来例に係る半導体装置の電極パッドの構造を示す平面図および断面図であり、図10(a)は、第2の従来例に係る半導体装置の電極パッドの構造を示す断面図であり、(b)は、第2の従来例に係る半導体装置におけるクラックの発生を模式的に示す断面図である。

**【0004】**

図9(a)、(b)に示すように、第1の従来例の半導体装置では、半導体チップ111の外周部に電極パッドが千鳥状に配置され、電極パッドのうち外列パッド121bは、引き出し配線152を介して内部回路112に接続されている。ただし、第1の従来例においては、引き出し配線152の幅だけ内列パッド121a同士の間隔を離す必要がある

10

20

30

40

50

ため、単位面積当たりに配置可能な電極パッドの数が減ってしまう。

#### 【0005】

そこで、図10(a)に示すように、内列パッド121a直下の配線層に外列パッド121bに接続される引き出し配線152を配置する構造をとることで、内列パッド121aと引き出し配線152の一部とを平面的に見て重複させることができとなり、単位面積当たりに配置可能な電極パッドの数を増やすことが可能となる。

#### 【特許文献1】特開平10-74790号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

10

しかし、第2の従来例に係る半導体装置では、図10(b)に示すように、プローブ検査工程において電極パッド121上にプローブ113をコンタクトする際に応力がかかり、その結果パッド121と引き出し配線152との間の層間絶縁膜141にクラック117が発生し、ショート不良が発生することで信頼性に大きな問題が生じうる。

#### 【0007】

前記に鑑み、本発明は、単位面積あたりに配置可能な電極パッド数を減らすことなく、プローブ検査により生じるクラックの影響を抑制し、信頼性を向上させた半導体装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

20

上記課題を解決するために、本発明では次のような半導体装置を採用した。

#### 【0009】

本発明の半導体装置は、内部回路と、引き出し配線と、前記引き出し配線によって前記内部回路に電気的に接続され、2列以上の千鳥状に配置された電極パッドとを備えた半導体装置であって、前記電極パッドは、プローブの接触及び外部接続が可能なプローブ領域と、プローブの接触が不可であり外部接続が可能な非プローブ領域とを有し、前記プローブ領域直下に前記引き出し配線が形成されておらず、且つ前記非プローブ領域直下に前記引き出し配線が形成されている。

#### 【0010】

30

この構成によれば、プローブ領域直下には引き出し配線が設けられていないので、プローブ領域下の層間絶縁膜を厚くすることができ、プローブの応力によるクラックの発生を抑えることができる。また、引き出し配線は電極パッドの非プローブ領域と平面的に見て重ねて配置されているので、引き出し配線を設けることによって単位面積当たりに配置可能な電極パッド数を減らす必要がなくなり、細密なパッド配置が可能となる。

#### 【0011】

また、本発明の半導体装置において、前記プローブ領域は、前記電極パッドのうち、前記引き出し配線が延びる方向に対して略平行に延びる前記電極パッドの中心線より20μm以内の領域に配置されており、前記非プローブ領域は、前記電極パッドのうちプローブ領域以外の領域に配置されていてもよい。これは、プローブの太さバラツキとコンタクト位置の精度バラツキを考慮すると、プローブ検査時にプローブが接触する領域は、パッド中心線から20μm以内の領域に収まっているからである。

40

#### 【0012】

また、本発明の半導体装置は、前記プローブ領域の直下に設けられ、直上の前記電極パッドに接続され、前記引き出し配線と同一配線層に形成されたパッドメタルをさらに備えていてもよい。これにより、プローブ応力による層間絶縁膜のクラックによって電極パッドと配線間のショートが発生するのを抑制することができる。さらに、外部回路への接続工程にて発生する、チップ平面に対して垂直上向きの応力に対して電極パッドが剥離するのを防ぐことができる。

#### 【発明の効果】

#### 【0013】

50

本発明の係る半導体装置によれば、プローブ応力による層間絶縁膜のクラックによって電極パッドと引き出し配線との間のショート不良の発生を防止することができ、かつ引き出し配線を電極パッドの非プローブ領域下に配置することができるため、引き出し配線によって単位面積あたりに配置可能な電極パッド数は減らすことなく細密なパッド配置が可能となる。この結果、チップサイズ縮小による低コスト化、多ピン化による高機能化、信頼性の向上を同時に実現する半導体装置を提供することができる。

**【発明を実施するための最良の形態】**

**【0014】**

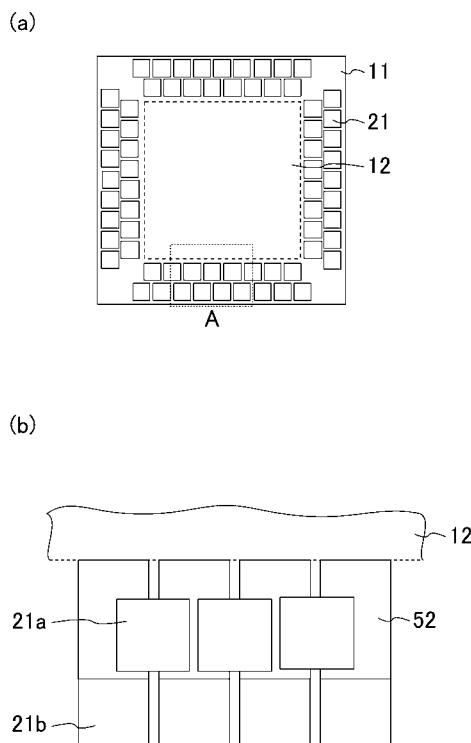

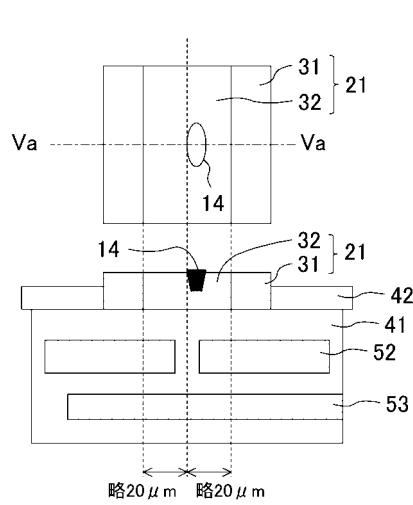

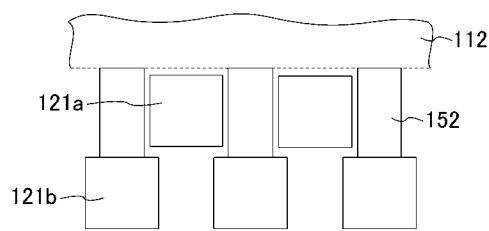

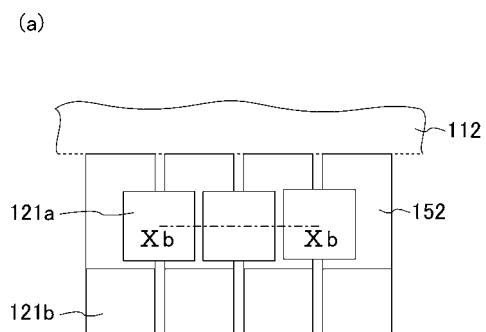

以下に、本発明の各実施形態を説明する前提として、本願明細書で用いる用語の定義について、図1～図2を参照しながら説明する。

10

**【0015】**

図1(a)は、一般的な半導体チップを示す平面図であり、(b)は、(a)に示す領域Aを拡大した断面図である。半導体チップ11には複数のトランジスタを用いて形成された内部回路12と、半導体チップ11の外周部に配置され、外部回路等と電気的なやり取りをするのに用いる電極パッド21とが設けられている。近年、チップ面積の縮小化と多機能化に伴う多ピン化が相伴って電極パッドを高密度に配置する必要性が発生し、図1(a)に示すように電極パッド21が千鳥状に配置されるようになった。

**【0016】**

ここで、本願では電極パッド21のうち、最も外側に配置された電極パッドのことを「外列パッド」(符号21b)と定義し、それより内側に配置された電極パッドのことを「内列パッド」(符号21a)と定義する。図1(a)、(b)では2列千鳥配置の電極パッドを例として示しているが、本願では3列以上の千鳥配置の電極パッドであっても本質は変わらず、差し支えはない。例えばN列千鳥配置の電極パッドでは外側から数えて1列目が「外列パッド」と定義され、2列目～N列目までが「内列パッド」と定義される。電極パッド21は外部から内部回路に電源を供給したり電気的な信号を入出力する役割を担っており、電極パッド21と内部回路12とは通常電気的に接続しなければならない。この電極パッド21と内部回路12とを接続させる配線のことを本願では「引き出し配線」(符号52)と定義する。

20

**【0017】**

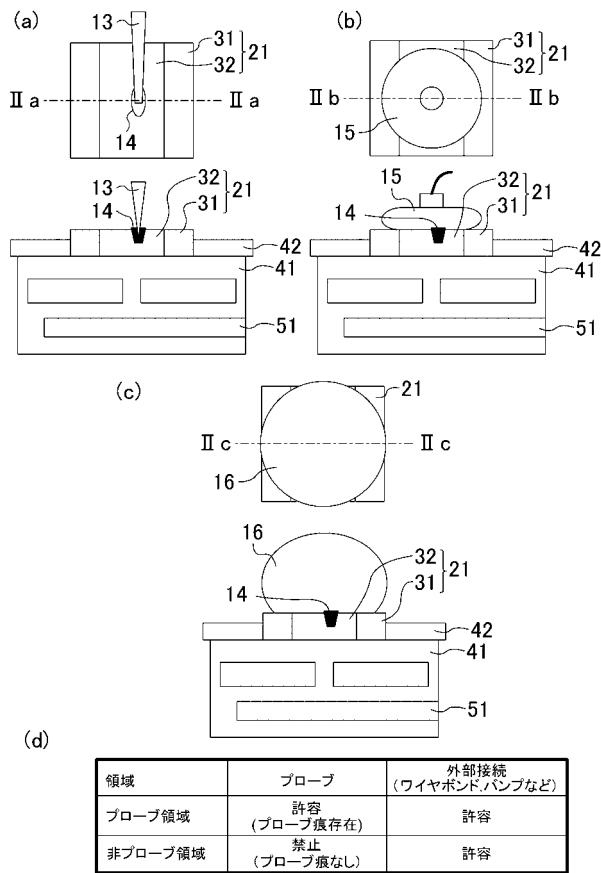

図2(a)～(d)は本願で使用する「プローブ領域」及び「非プローブ領域」について示したものである。

30

**【0018】**

図2(a)は、ウエハ内の不純物拡散工程後にプローブ13を電極パッド21に接触させて検査を行なう、いわゆるプローブ検査工程でのプローブ13のコンタクト状態を示したものである。プローブ13は、電極パッド21に接触する際、電極パッド21の表面に引っかき傷、すなわちプローブ痕14を残す。本願では電極パッド21のうち検査時にプローブ13が接触する領域のことを「プローブ領域」(符号32)、プローブ13が電極パッド21のうち検査時にプローブ13に接触しない(接触が禁止された)領域のことを「非プローブ領域」(符号31)とそれぞれ定義する。換言すれば「プローブ領域」32はプローブ痕14が存在しうる領域であり、「非プローブ領域」31はプローブ痕14が存在しない領域として定義できる。なお、電極パッド21の下方には層間絶縁膜41内に埋め込まれた配線51が設けられている。

40

**【0019】**

図2(b)は、電極パッド21を外部とワイヤを用いて接続するいわゆるワイヤボンド工程を示したものである。一般的にはプローブ痕14よりもワイヤボール15の接続面積の方が10倍以上大きい。本願では、図2(b)に示すように「プローブ領域」32と「非プローブ領域」31の区別なくワイヤボンドの接続は可能である。図2(b)に示す工法以外にもウエッジボンドとよばれる手法の接続工法があるが、同様に定義する。

**【0020】**

図2(c)は、電極パッド21を外部回路等とバンプ16を用いて接続する工程を示し

50

たものである。電極パッド 2 1 はバンプ 1 6 を介してパッケージ基板に向かい合わせになる形で接続される。この場合も「プローブ領域」3 2 と「非プローブ領域」3 1 の区別なくバンプの接続は可能である。なお、バンプにも Au バンプや半田バンプなど様々な種類や形状、製造工法があるが、全て同様に定義する。以上の「プローブ領域」と「非プローブ領域」の定義をまとめたのが図 2 ( d ) に示す表である。すなわち「プローブ領域」とはプローブの接触と外部接続が許容である領域として定義し、「非プローブ領域」とはプローブは禁止だが外部接続が許容である領域として定義する。

#### 【 0 0 2 1 】

##### ( 第 1 の実施形態 )

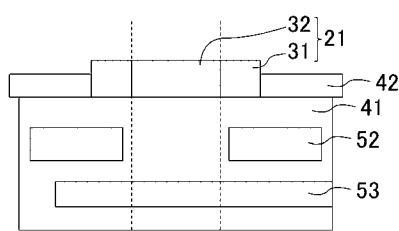

図 3 は、本発明の第 1 の実施形態に係る半導体装置の構成を示す断面図である。

10

#### 【 0 0 2 2 】

同図に示すように、本実施形態の半導体装置は、内部回路と、引き出し配線 5 2 と、内部回路の外側に、2 列以上の千鳥状に配置された電極パッド 2 1 と、電極パッド 2 1 の周囲に設けられた保護膜 4 2 とを備えている。また、電極パッド 2 1 には先に定義したプローブ領域 3 2 と非プローブ領域 3 1 とが存在し、引き出し配線 5 2 は非プローブ領域 3 1 の直下の領域に配置されるが、プローブ領域 3 2 直下には配置されない。この引き出し配線 5 2 は、その直上に位置する電極パッド 2 1 と電気的に独立しており、お互いがショートすると半導体装置は正常に動作ができない状態に陥る。発明者らの評価結果によると、プローブ検査工程の時に応力がかかり、電極パッドとその直下の配線の間の層間絶縁膜 4 1 にチップ面に対して垂直の方向にクラックが発生することがわかっている。換言すれば、プローブ痕の直下の領域のみクラックが発生する。また、ワイヤボンドやバンプなどで電極パッド 2 1 と外部に接続する際には、プローブ時よりも電極パッド 2 1 への接触面積は 10 倍以上とはるかに大きいため、ワイヤボンドやバンプでの応力によって電極パッド 2 1 とその直下の配線の間の層間絶縁膜 4 1 のクラックが発生しないことがわかっている。さらに電極パッドと配線の距離を大きくし層間絶縁膜を厚くするほど、層間絶縁膜自体が強化されその結果クラックの発生頻度は低減することもわかっている。

20

#### 【 0 0 2 3 】

以上のことから、本発明の第 1 の実施形態に係る半導体装置によると、プローブ領域 3 2 直下には引き出し配線 5 2 がなく配線の代わりに層間絶縁膜 4 1 が形成されているので、クラックの発生するチップ面に対して垂直な方向の層間絶縁膜 4 1 は従来に比べて厚くなる効果があり、その結果、プローブ応力による層間絶縁膜 4 1 内でのクラック発生を防止することができる。さらに、非プローブ領域 3 1 直下に引き出し配線を有しているので、この場合ワイヤボンドやバンプでの応力がかかるが、上述のように、層間絶縁膜 4 1 にクラックは発生しにくくなっている。また、引き出し配線 5 2 を電極パッド 2 1 の非プローブ領域 3 1 と平面的に見て重複させて配置することが可能なため、引き出し配線 5 2 を設けつつも、単位面積あたりに配置可能な電極パッド数を減らすことなく細密な電極パッド 2 1 を配置することが可能となる。なお、通常の配線 5 3 は電極パッド 2 1 との距離が大きいため、プローブ領域 3 2 の下方に設けられていても問題ない。

30

#### 【 0 0 2 4 】

なお、本願発明は、各構成部材の材質や電極パッド 2 1 の構造、保護膜 4 2 の有無、配線層数や膜厚構成は特に関係なく実現可能である。例えば、図 4 は近年よく用いられている半導体装置の断面構造を示しているが、このように保護膜 4 2 a ~ 4 2 c など、保護膜が複数存在し、電極パッドも電極パッド 2 4 a 、 2 4 b の 2 層構造をとり、引き出し配線 5 2 以外の配線 5 3 が複数の層で構成されていても、非プローブ領域 3 1 直下に引き出し配線 5 2 が配置され、且つプローブ領域 3 2 直下に引き出し配線 5 2 が配置されなければ、本発明の第 1 の実施形態に係る半導体装置に該当し、これと同様の効果が期待できる。これは、本発明の他の実施形態においても同様である。

40

#### 【 0 0 2 5 】

##### - 第 1 の実施形態の変形例 -

図 5 ( a ) は、第 1 の実施形態の変形例に係る半導体装置の構成を示す平面図および断

50

面図である。本変形例の半導体装置は、基本的に第1の実施形態と同様の構成を有しているが、プローブ領域32が電極パッド21の中心線より略20μm以内の領域で定義され、電極パッド21のうちプローブ領域32以外の領域を非プローブ領域31と定義されていることを特徴とする。ここで、電極パッド21の中心線とは、引き出し配線52が延びる方向に対して略平行に延びる電極パッド21の中心線のことを意味する。

#### 【0026】

本変形例の半導体装置においても、引き出し配線52は非プローブ領域31の直下の領域に配置されるとともに、プローブ領域32直下には配置されない。

#### 【0027】

ここで、プローブの接触箇所はプローブ痕14を観測すれば掌握可能であり、図5(b)は、あるプローブカードを用いてプローブ検査を行った際のプローブ痕14の幅及び終点を実際に評価したデータである。このデータよりプローブ痕14はパッド中心線より{プローブ痕幅(a)+プローブ痕バラツキ(b)+プローブ終点位置平均(c)+バラツキ(d)}/2=19.3μmの範囲に存在することになる。以上より、電極パッド21の中心線より略20μm以内の領域として定義されたプローブ領域32にはプローブ痕14が存在する可能性があることが分かる。本変形例ではプローブ領域32直下に引き出し配線52は存在していないので、プローブ領域32直下の層間絶縁膜41を厚くすることができるため、クラックの発生が抑制される。仮に、クラックが発生したとしても、引き出し配線52がプローブ領域32の直下には配置されていないため、電極パッド21と引き出し配線52とがショートを起こすことはない。

#### 【0028】

また、電極パッド21の中心線より略20μm以上外側の非プローブ領域31にはプローブ痕が存在しないので、電極パッド21と引き出し配線52間の層間絶縁膜41にクラックは発生しない。

#### 【0029】

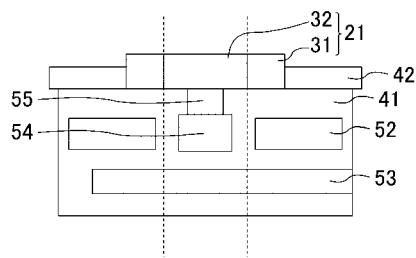

##### (第2の実施形態)

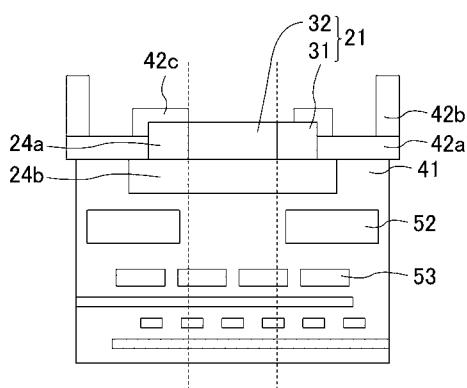

図6は、本発明の第2の実施形態に係る半導体装置の構成を示す断面図である。

#### 【0030】

同図に示すように、本実施形態の半導体装置は、内部回路と、引き出し配線52と、内部回路の外側に、2列以上の千鳥状に配置された電極パッド21と、電極パッド21の周囲に設けられた保護膜42とを備えている。また、電極パッド21には先に定義したプローブ領域32と非プローブ領域31とが存在し、引き出し配線52は非プローブ領域31の直下の領域に配置されるが、プローブ領域32直下には配置されない。この引き出し配線52は、その直上に位置する電極パッド21と電気的に独立している。

#### 【0031】

本実施形態の半導体装置の特徴は、プローブ領域32の直下であって、引き出し配線52と同じ配線層内に設けられたパッドメタル54と、電極パッド21とパッドメタル54とを接続させる接続部55とが設けられることにある。

#### 【0032】

本発明の第2の実施形態に係る半導体装置によると、プローブ領域32の直下には引き出し配線52がなく、接続部55を介して電極パッド21と電気的に接続されたパッドメタル54を含む多層パッド構造が形成されているので、プローブ応力による層間絶縁膜41のクラックが例え発生しても、電極パッド21と引き出し配線52との間や、電極パッド21と配線53との間にショートが発生することがない。さらに、外部回路との接続工程においては、チップ平面に対して垂直上向きの応力が加わるため、従来の半導体装置では電極パッドからの剥離が発生することがあったが、本実施形態の半導体装置では、これを防止することができる。また、非プローブ領域31直下に引き出し配線52を配置しているので、引き出し配線52を平面的に見て電極パッド21と重ねて配置することが可能であり、引き出し配線52の存在によって単位面積あたりに配置可能な電極パッド数を減らすことなく細密なパッド配置が可能となる。なお、本実施形態に係る半導体装置では、

10

20

30

40

50

図6に示すように、接続部55は電極パッド21当たり1つのみ設けられており、電極パッド21とパッドメタル54との間の空間はほぼすべて金属で埋められている。この構成によると、電極パッド21とパッドメタル54との間の電気抵抗を最低限に抑えることができる。また、第1の実施形態の变形例と同様にプローブ領域32は電極パッド21の中心線から略 $20\mu m$ 以内の領域と定義し、電極パッド21のプローブ領域32以外の領域を非プローブ領域31と定義してもよい。

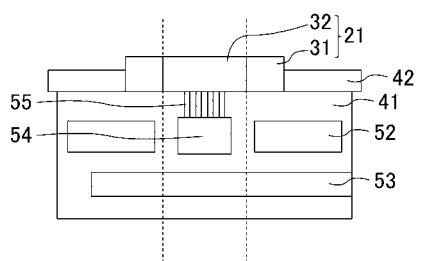

#### 【0033】

- 第2の実施形態の变形例 -

図7は、本発明の第2の実施形態の变形例に係る半導体装置の構成を示す断面図である。同図に示すように、電極パッド21とパッドメタル54とを接続する接続部55はピア形状であって、1つの電極パッド21当たり複数設けられてもよい。一般的には、接続部55を形成する際に層間絶縁膜41をエッチングするが、この際にピアを掘ることのできる大きさはプロセスによって制限される。本变形例に係る半導体装置によると、従来の接続ピア形成手法を用いて接続部55を形成し、電極パッド21とパッドメタル54とを電気的に接続することができる。また、このピア形状を複数形成することで抵抗を抑えることができる。またこの際、図7に示すように接続部55を構成するピア形状の金属対が平面的に見て等間隔かつ均一に配置されていることが好ましい。この方法によれば、電極パッド21にかかるプローブ応力が均一にパッドメタルに伝わり、応力を分散することができる所以有用である。

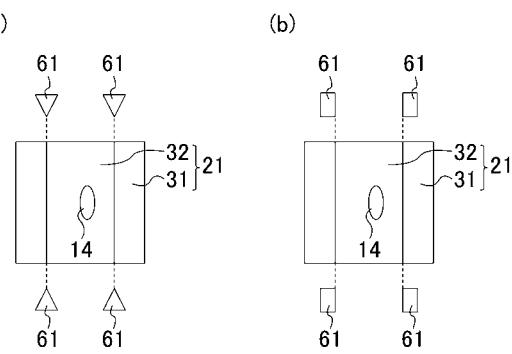

#### 【0034】

(第3の実施形態)

図8(a)～(d)は、本発明の第3の実施形態に係る半導体装置を示す平面図である。本実施形態の半導体装置の構成は基本的には第1および第2の半導体装置と同様であるので、以下特徴部分のみの説明を行う。

#### 【0035】

本実施形態の半導体装置においては、図8(a)に示すように、電極パッド21中のプローブ領域32と非プローブ領域31との境界線の延長上に、光学的に区別可能な目印61がついている。このような目印61を配置することで、プローブの許容領域、または禁止領域が目視あるいは光学的な濃淡を判別可能なアライメント装置を用いることでプローブ領域32と非プローブ領域31とを容易に分別することが可能となる。さらにプローブ痕14も光学的に分別が可能なため、光学的な濃淡で目印61およびプローブ痕14を判別可能なアライメント装置を用いると、プローブ検査工程ごとにプローブ痕14が非プローブ領域31に入っていないかどうかを監視でき、工程管理が飛躍的に容易になる。なお、目印61の形状は境界線の境目が分別できればどのような形状でもよく、例えば図8(b)に示すように長方形であってもよい。図8(b)の例では長方形の目印61の各内側の辺を判別することで、プローブ領域32と非プローブ領域31を分別することが可能である。

#### 【0036】

また、図8(c)に示すように、電極パッド21のトップメタル層によってプローブ領域32と非プローブ領域31の分別が可能のように目印が形成されていてもよい。この場合、従来プロセスの工程変更なしに目印を形成することが可能である。図8(c)の例では、プローブ領域32のトップメタルと非プローブ領域31のトップメタルとに平面的に見て段差を設けることによってその境界を光学的に判断することが可能となる。

#### 【0037】

また、図8(d)に示すように、電極パッド21上の保護膜42によってプローブ領域32と非プローブ領域31の分別が可能のように目印が形成されていてもよい。この場合も電極パッド21上に保護膜42を形成するプロセスにおいて、従来プロセスから工程変更することなく目印を形成することが可能である。図8(d)の例では、保護膜42の開口の形状に段差をつけることでプローブ領域32と非プローブ領域31の境界を光学的に判断することが可能となる。例えば、保護膜42の上面位置をプローブ領域32上よりも

10

20

30

40

50

非プローブ領域31上で高くすることで、プローブ領域32と非プローブ領域31との境界を光学的に判断することが可能となる。なお、保護膜42の形状についてはプローブ領域32と非プローブ領域31の境界線を示すことが可能な形状であればどのような形状であってもよい。

**【産業上の利用可能性】**

**【0038】**

本発明は、小チップサイズでかつ多くの端子を必要とする半導体装置にとって有用である。

**【図面の簡単な説明】**

**【0039】**

**【図1】**(a)は、一般的な半導体チップを示す平面図であり、(b)は、(a)に示す領域Aを拡大した断面図である。

**【図2】**(a)～(d)は、本願で定義する「プローブ領域」と「非プローブ領域」を示す平面図及び断面図である。

**【図3】**本発明の第1の実施形態に係る半導体装置の構成を示す断面図である。

**【図4】**本発明の第1の実施形態に係る半導体装置の別例を示す断面図である。

**【図5】**(a)は、第1の実施形態の変形例に係る半導体装置の構成を示す平面図および断面図であり、(b)は、第1の実施形態の変形例の有用性を立証する実験データである。

**【図6】**本発明の第2の実施形態に係る半導体装置の構成を示す断面図である。

**【図7】**本発明の第2の実施形態の変形例に係る半導体装置を示す断面図である。

**【図8】**(a)～(d)は、本発明の第3の実施形態に係る半導体装置を示す平面図である。

**【図9】**(a)、(b)は、それぞれ第1の従来例に係る半導体装置の電極パッドの構造を示す平面図および断面図である。

**【図10】**(a)は、第2の従来例に係る半導体装置の電極パッドの構造を示す断面図であり、(b)は、第2の従来例に係る半導体装置におけるクラックの発生を模式的に示す断面図である。

**【符号の説明】**

**【0040】**

1 1 半導体チップ

1 2 内部回路

1 3 プローブ

1 4 プローブ痕

1 5 ワイヤボール

1 6 バンプ

2 1、2 4 a、2 4 b 電極パッド

2 1 a 内列パッド

2 1 b 外列パッド

3 1 非プローブ領域

3 2 プローブ領域

4 1 層間絶縁膜

4 2、4 2 a～4 2 c 保護膜

5 2 引き出し配線

5 3 配線

5 4 パッドメタル

5 5 接続部

6 1 目印

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

(b)

|           | 平均値              | バラツキ $3\sigma$   |

|-----------|------------------|------------------|

| プローブ痕幅    | 12.8 $\mu m$ (a) | 5.8 $\mu m$ (b)  |

| プローブ痕終点位置 | 0.0 $\mu m$ (c)  | 20.0 $\mu m$ (d) |

※評価サンプル数 N=48Pad

※プローブ痕終点位置の座標=0がパッド中心線を示す

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(74)代理人 100115691

弁理士 藤田 篤史

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 高橋 昌男

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 竹村 康司

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 阪下 俊彦

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 三村 忠昭

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 越本 秀幸

(56)参考文献 特開平09-246314 (JP, A)

特開2005-252230 (JP, A)

特開2005-243907 (JP, A)

特開2007-109917 (JP, A)

特開2006-222147 (JP, A)

特開2007-318014 (JP, A)

特開2002-016069 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60

H01L 21/66