(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4323663号

(P4323663)

(45) 発行日 平成21年9月2日(2009.9.2)

(24) 登録日 平成21年6月12日(2009.6.12)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| HO4N 5/213 (2006.01) | HO4N 5/213     |

| G06T 5/20 (2006.01)  | G06T 5/20 A    |

| HO4N 1/409 (2006.01) | HO4N 1/40 101C |

請求項の数 16 (全 14 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2000-53736 (P2000-53736)    |

| (22) 出願日  | 平成12年2月29日 (2000.2.29)        |

| (65) 公開番号 | 特開2001-245180 (P2001-245180A) |

| (43) 公開日  | 平成13年9月7日 (2001.9.7)          |

| 審査請求日     | 平成19年2月20日 (2007.2.20)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (72) 発明者  | 大塚 克己<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】 画像フィルタ回路及び画像フィルタリング方法

## (57) 【特許請求の範囲】

## 【請求項 1】

原画像における注目画素とその周辺画素を含む領域内の各画素の値を入力して、前記注目画素の値を前記領域内における所定の昇順番目の画素値で置き換えるフィルタを移動させて1フレームの画像データを得る画像フィルタ回路であって、

前記領域内における画素の上位ビットデータによる第1のヒストグラムを作成する第1のヒストグラム作成手段と、

前記第1のヒストグラムに基づいて、前記所定の昇順番目に相当する画素値を含む階級を目標階級として検索する第1の検索手段と、

前記目標階級に含まれる画素の下位ビットデータによる第2のヒストグラムを作成する第2のヒストグラム作成手段と、

前記第2のヒストグラムに基づいて、前記領域内における前記所定の昇順番目の画素値を検索する第2の検索手段と、

を有することを特徴とする画像フィルタ回路。

## 【請求項 2】

更に、前記領域内の画素を上位ビットデータと下位ビットデータとに分割してそれぞれ遅延させる遅延手段を有し、

前記第1及び第2のヒストグラム作成手段はそれぞれ、前記遅延手段によって遅延された前記上位ビットデータ及び前記下位ビットデータに基づいて、前記第1及び第2のヒストグラムを作成することを特徴とする請求項1記載の画像フィルタ回路。

**【請求項 3】**

前記第1の検索手段は、

前記第1のヒストグラムにおける階級毎の画素数を累積加算することによって、前記所定の昇順番目に相当する画素値を含む階級を目標階級として検出し、該目標階級の値及び該目標階級までの累積加算画素数を出力することを特徴とする請求項2記載の画像フィルタ回路。

**【請求項 4】**

前記第2のヒストグラム作成手段は、

前記遅延手段から出力された前記上位ビットデータと前記目標階級値とを比較することによって前記目標階級に含まれる画素を候補画素として選択し、該候補画素の前記下位ビットデータを出力する領域選択手段と、

前記候補画素に対応する前記下位ビットデータによって前記第2のヒストグラムを作成する作成手段と、

を有することを特徴とする請求項3記載の画像フィルタ回路。

**【請求項 5】**

前記第2の検索手段は、

前記第2のヒストグラムにおける階級毎の画素数を累積加算し、該累積加算画素数を前記第1の検索手段より出力された累積加算画素数と比較することによって、前記領域内における前記所定の昇順番目の画素値を検索することを特徴とする請求項4記載の画像フィルタ回路。

10

20

**【請求項 6】**

前記遅延手段は、前記フィルタの移動によって前記領域に新たに加えられた画素値をLビット精度で入力し、

該画素値の上位Pビットデータを遅延させる第1の遅延パスと、

該画素値の下位L-Pビットデータをデコードして $2^{L-P}$ ビットのデータに変換した後に遅延させる第2の遅延パスと、

を有することを特徴とする請求項5記載の画像フィルタ回路。

**【請求項 7】**

前記第1及び第2の遅延パスは、前記領域のサイズに応じた複数画素分を遅延し、1画素分遅延毎の遅延データを全て出力することを特徴とする請求項6記載の画像フィルタ回路。

30

**【請求項 8】**

前記第1及び第2の遅延パスは、前記領域に新たに加えられた画素が、前記フィルタの移動によって前記領域より除外された画素となるまでの期間に相当する画素数分を遅延させることを特徴とする請求項7記載の画像フィルタ回路。

**【請求項 9】**

前記第1のヒストグラム作成手段は、

前記フィルタの移動によって前記領域に新たに加えられた新規画素の上位Pビットデータと、前記第1の遅延パスより出力された上位Pビットの遅延データに基づいて、 $2^P$ 階級を有する前記第1のヒストグラムを作成することを特徴とする請求項6記載の画像フィルタ回路。

40

**【請求項 10】**

前記第1のヒストグラム作成手段は、

前記新規画素の上位Pビットデータを前記第1のヒストグラムに加える加算手段と、

前記第1の遅延パスより出力された上位Pビットの遅延データを前記第1のヒストグラムから減じる減算手段と、

を有することを特徴とする請求項9記載の画像フィルタ回路。

**【請求項 11】**

前記領域選択手段は、

前記第1の遅延パスから出力された前記上位Pビットの遅延データと前記目標階級値と

50

を比較することによって前記候補画素を選択し、該候補画素に対応する前記第2の遅延バスから出力された前記下位L-Pビットの遅延データを出力することを特徴とする請求項6記載の画像フィルタ回路。

【請求項12】

前記第2のヒストグラム作成手段は、

前記候補画素の前記下位L-Pビットの遅延データに基づいて、 $2^{L-P}$ 階級を有する第2のヒストグラムを作成することを特徴とする請求項6記載の画像フィルタ回路。

【請求項13】

前記所定の昇順番目は、前記領域内における中央番目であることを特徴とする請求項1記載の画像フィルタ回路。

10

【請求項14】

前記領域は、マトリクス状の矩形であることを特徴とする請求項1記載の画像フィルタ回路。

【請求項15】

前記注目画素は、前記領域の中央に位置することを特徴とする請求項1記載の画像フィルタ回路。

【請求項16】

原画像における注目画素とその周辺画素を含む領域内の各画素の値を入力して、前記注目画素の値を前記領域内における所定の昇順番目の画素値で置き換えるフィルタを移動させて1フレームの画像データを得る画像フィルタ回路における画像フィルタリング方法であって、

20

第1のヒストグラム作成手段が、前記領域内における画素の上位ビットデータによる第1のヒストグラムを作成する第1のヒストグラム作成工程と、

第1の検索手段が、前記第1のヒストグラムに基づいて、前記所定の昇順番目に相当する画素値を含む階級を目標階級として検索する第1の検索工程と、

第2のヒストグラム作成手段が、前記目標階級に含まれる画素の下位ビットデータによる第2のヒストグラムを作成する第2のヒストグラム作成工程と、

第2の検索手段が、前記第2のヒストグラムに基づいて、前記領域内における前記所定の昇順番目の画素値を検索する第2の検索工程と、

を有することを特徴とする画像フィルタリング方法。

30

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は画像フィルタ回路及び画像フィルタリング方法に関し、特にデジタル画像からスパイク状の雑音を除去する画像フィルタ回路及び画像フィルタリング方法に関する。

【0002】

【従来の技術】

画像におけるスパイク状の孤立点雑音を除去する非線形フィルタとして、メディアンフィルタが知られている。

【0003】

40

メディアンフィルタとは、原画像上の注目画素に対して、その周辺に任意のサイズのマトリクスを作成し、そのマトリクス内の画素値を大きい順にソーティングした際に丁度中央番目となる画素値を、注目画素の値とするフィルタである。

【0004】

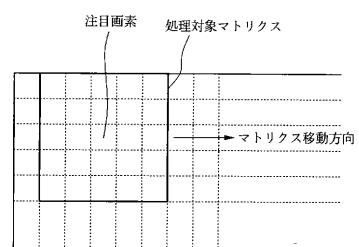

以下、図2及び図3を参照して、一般的なメディアンフィルタについて詳細に説明する。

【0005】

図2に示すように、原画像上においてマトリクスを水平もしくは垂直方向に順次移動する事により、原画像上のすべての画素に対してフィルタ処理を施すことができる。

【0006】

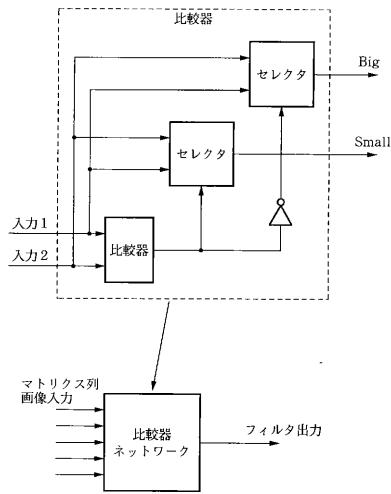

図3は、メディアンフィルタを実現する回路構成を示す図である。即ち、メディアンフィ

50

ルタを回路として実現するためには、ソーティング処理を行うための比較器として、コンパレータ回路とセレクタ回路をソーティング時の比較回数分用意し、これらを順次組み合わせてネットワークを構成すればよい。

#### 【0007】

例えば、 $M \times M$  サイズ ( $M$  は自然数) マトリクスに対するソーティング処理を、コンパレータ回路とスイッチ回路、及びデータラッチによって実現する技術が、ソーティング・アンド・サーチング、ザ・アート・オブ・コンピュータ・プログラミングに示されている。

#### 【0008】

##### 【発明が解決しようとする課題】

上記ソーティング・アンド・サーチング、ザ・アート・オブ・コンピュータ・プログラミングに示されているマージソート技術によれば、例えば  $M = 3$  の場合には、25個のコンパレータとセレクタ回路、及び72個のデータラッチによって、メディアンフィルタ回路が構成される。ただし、これをデジタル回路として構成するためにクロック同期型で実現しようとすると、更に90個のデータラッチと3個のロード付きデータラッチが必要となる。

10

#### 【0009】

更に、 $M = 4$  の場合についてメディアンフィルタ回路を構成すると、54個のコンパレータとセレクタ回路、及び176個のデータラッチと4個のロード付きデータラッチが必要となってしまう。

#### 【0010】

20

このように、上記技術によって、メディアンフィルタをハードウェアとして実現すると、処理対象とするマトリクスサイズ  $M$  の値が大きくなるに従い、回路規模が急激に増大してしまうという問題があった。

#### 【0011】

例えば、上記技術を用いて  $M = 7$  のマトリクスサイズによってメディアンフィルタ回路を構成する場合について考えると、データ間の同期を考慮すると、デジタル回路として実現するには回路規模があまりに大きいため、その実現は困難である。

#### 【0012】

更に、特開平5-233802号によれば、比較回路によるソーティング処理を行わずに、画素値のテーブルを作成してメディアンフィルタを構成するという技術が示されている。しかしながら、その処理の具体的手法、及びハードウェアでの実現性に対しては何ら言及されておらず、現実的ではなかった。

30

#### 【0013】

本発明は上記問題を解決するためになされたものであり、大規模メディアンフィルタをデジタル回路として実現可能な画像フィルタ回路及び画像フィルタリング方法を提供することを目的とする。

#### 【0014】

##### 【課題を解決するための手段】

上記目的を達成するための一手段として、本発明の画像フィルタ回路は以下の構成を備える。

40

#### 【0015】

即ち、原画像における注目画素とその周辺画素を含む領域内の各画素の値を入力して、前記注目画素の値を前記領域内における所定の昇順番目の画素値で置き換えるフィルタを、所定方向に移動させて1フレームの画像データを得る画像フィルタ回路であって、前記領域内における画素の上位ビットデータによる第1のヒストグラムを作成する第1のヒストグラム作成手段と、前記第1のヒストグラムに基づいて、前記所定の昇順番目に相当する画素値を含む階級を目標階級として検索する第1の検索手段と、前記目標階級に含まれる画素の下位ビットデータによる第2のヒストグラムを作成する第2のヒストグラム作成手段と、前記第2のヒストグラムに基づいて、前記領域内における前記所定の昇順番目の画素値を検索する第2の検索手段と、を有することを特徴とする。

50

## 【0016】

## 【発明の実施の形態】

以下、本発明に係る一実施形態について、図面を参照して詳細に説明する。

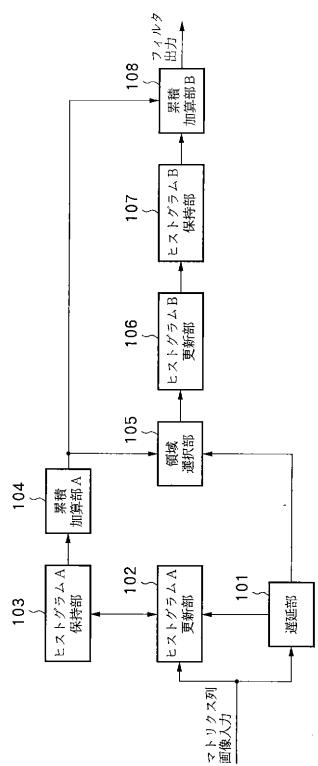

## 【0017】

図1は、本実施形態におけるメディアンフィルタを実現するデジタル回路（以下、単にフィルタ回路と称する）のロック構成を示す図である。尚、本実施形態におけるフィルタ回路は、クロック同期を可能とするデジタル回路構成をなす。

## 【0018】

以下、同図を参照して、マトリクスサイズ $M = 5$ 、原画像の画像データのビット精度 $L = 8$ ビットの場合を例として説明する。

10

## 【0019】

原画像上において、 $5 \times 5$ のマトリクスが水平方向に、クロック毎に1画素分移動したとする。この時、新たにマトリクスの構成要素となった列の画素が、遅延部101及びヒストグラムA更新部102に入力される。

## 【0020】

## [遅延部101]

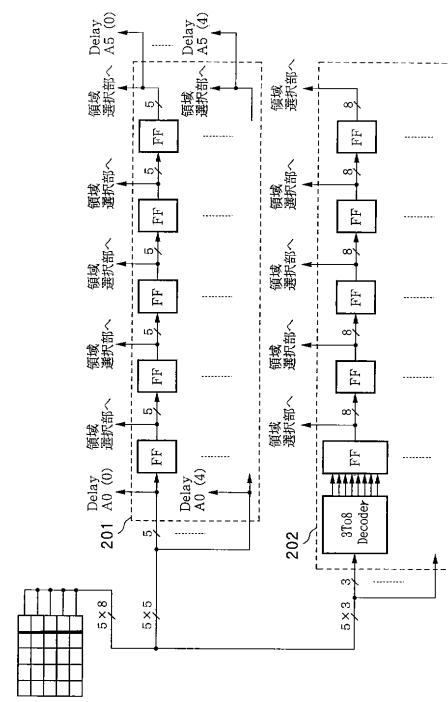

図4は、遅延部101の回路構成を示す図である。

## 【0021】

遅延部101は、2つのデータバス（遅延バスA201、遅延バスB202）から構成されている。これら遅延バスA201及び遅延バスB202は共に、図示される回路を並列に5つ備えており、列データがそれぞれ同一タイミングで入力される。

20

## 【0022】

一方の遅延バスA201は、画素データの上位5ビット（ $P = 5$ ）について、クロック毎に入力されるマトリクスの5つの列構成データ $Delay A0(0) \sim Delay A0(4)$ を、フリップフロップ（以下、FFと表記）にて5クロック、即ち、マトリクスの水平サイズである5画素相当分を遅延させ、最終的に $Delay A5(0) \sim Delay A5(4)$ を出力する。尚、各FFからの1クロック毎の遅延出力をそれぞれ、 $Delay A1(0) \sim Delay A1(4)$ ,  $Delay A2(0) \sim Delay A2(4)$ ,  $Delay A3(0) \sim Delay A3(4)$ ,  $Delay A4(0) \sim Delay A4(4)$ として、 $Delay A5(0) \sim Delay A5(4)$ と共に、後述する領域選択部105へ出力する。遅延バスA201は即ち、マトリクスの1行分を遅延しているに過ぎない。

30

## 【0023】

他方の遅延バスB202は、画素データの下位3ビット（ $L - P = 3$ ）について、列構成データの値を3T08デコーダを介して8ビット（ $2L - P = 8$ ）のFFに入力し、同様に5クロック遅延させる。そして、各FFからの1クロック毎の遅延出力をそれぞれ、 $Delay A1\_Low(0) \sim Delay A1\_Low(4)$ ,  $Delay A2\_Low(0) \sim Delay A2\_Low(4)$ ,  $Delay A3\_Low(0) \sim Delay A3\_Low(4)$ ,  $Delay A4\_Low(0) \sim Delay A4\_Low(4)$ ,  $Delay A5\_Low(0) \sim Delay A5\_Low(4)$ として、後述する領域選択部105へ出力する。

## 【0024】

遅延バスA201及び遅延バスB202はそれぞれ、各FFによる遅延データによって、画像データの各列に対する上位5ビットデータ及び下位3ビットデータのヒストグラム（詳細は後述する）を生成している。

40

## 【0025】

## [ヒストグラムA更新部102]

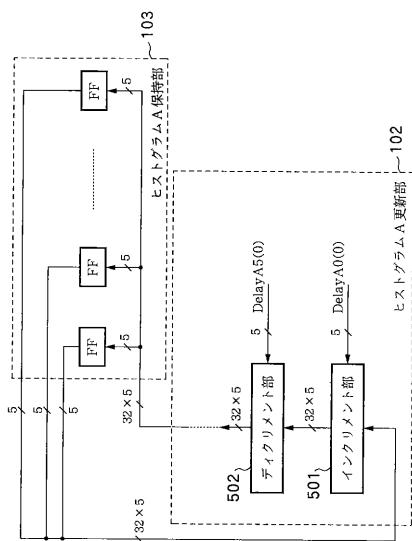

図5は、ヒストグラムA更新部102及びヒストグラムA保持部103の回路構成を示す図である。

## 【0026】

ヒストグラムA保持部103は、画像データの各列に対する上位5ビットデータのヒストグラムAを保持するレジスタ群であり、マトリクス内の画素要素数 $25 (M^2)$ 個を表現可能な、5ビット幅をもつFF群を $32 (2^P)$ 個並列に並べることによって構成されている。この32個のFFそれが、ヒストグラムAにおける各階級に相当し、各階級の

50

度数は即ち画素数である。

【0027】

ヒストグラムA保持部103の出力はヒストグラムA更新部102へ入力されて、各階級毎に5（マトリクス列サイズMに相当）段のインクリメント部501と、同じく5段のディクリメント部502を通すことによって、ヒストグラムAが更新される。即ち、マトリクスを移動する事によって新規マトリクス構成要素なる5個の画素データ（Delay A0(0)～Delay A0(4)）と、マトリクス外要素となる5個の画素データ（Delay A5(0)～Delay A5(4)）に基づいて、ヒストグラムAを更新する。

【0028】

インクリメント部501へは、遅延部101の遅延バスA201への入力と同様の列データDelay A0(0)～Delay A0(4)が入力され、ディクリメント部502へは、遅延部101にてマトリクスの水平サイズ分遅延した列データDelay A5(0)～Delay A5(4)が、それぞれ入力される。このインクリメンタとディクリメンタの組み合わせ回路がシリアルに5段接続され、ヒストグラムA保持部103における各FFに入力される。

10

【0029】

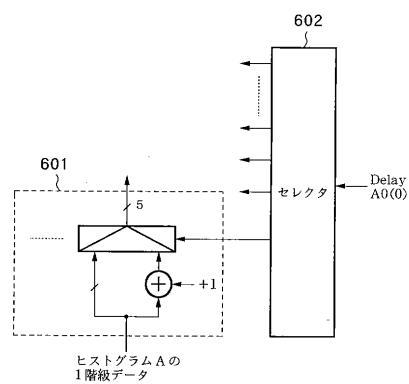

図6は、インクリメント部501の詳細構成を示す図である。以下、Delay A0(0)～Delay A0(4)はマトリクスの列を構成する5画素を束ねたデータバスであるが、その中の一つであるDelay A0(0)がインクリメント部501に入力される場合について、以下説明する。

【0030】

20

セレクタ602によって、5ビットデータであるDelay A0(0)を32（ $2^5$ ）ビットにデコードした各出力、即ちヒストグラムAの32階級値をそれぞれ、データ更新部601における32個のユニットに接続する。データ更新部601は、入力データに対してインクリメントを行うバスと、入力データ値に処理を加えずにそのまま出力するバスとを備えたユニットを32個備えており、各ユニットにおいては、Delay A0(0)の値に相当する階級についてはインクリメンタ出力のバスが選択され、それ以外の場合にはそのまま出力するバスが選択される。

【0031】

尚、デクリメント部502の構成は、図6に示したインクリメント部501の構成において、データ更新部601内のインクリメンタをデクリメンタに置き換えたものとなる。

30

【0032】

【累積加算部A104】

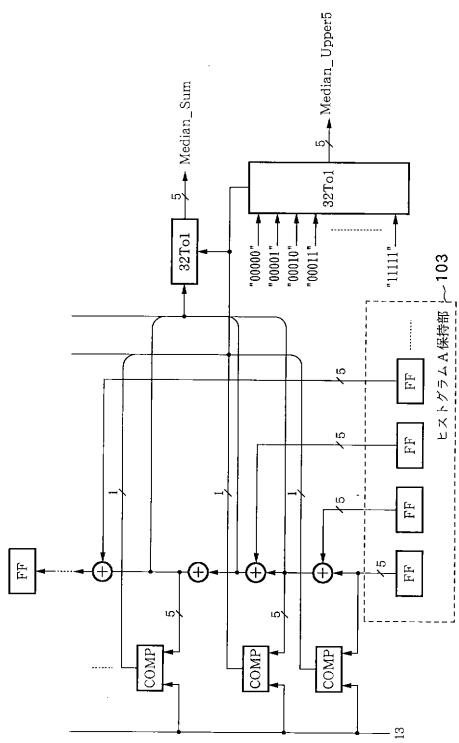

図7は、累積加算部A104の回路構成を示す図である。

【0033】

累積加算部A104においては、ヒストグラムA保持部103に保持されたヒストグラムAから、その中央値を含む階級（以下、目標階級と称する）を検索するために、階級毎の度数（画素数）を累積加算する。

【0034】

マトリクスサイズが $5 \times 5$ であるから、ヒストグラムAの中央値は昇順で13番目の画素値となる。従って、ヒストグラムA保持部103からの各5ビットのFF出力が階級毎に昇順で加算器に入力され、その各出力はコンパレータによって、それぞれ固定値「13」と比較される。このコンパレータ出力により、ヒストグラムにおいて階級毎の累積度数（累積画素数）が最初に13を超えた階級が目標階級であり、即ち中央値が含まれている階級であると判定することができる。

40

【0035】

全32個のコンパレータ出力は、中央値の上位5ビット（P=5）出力（図中、Median\_Upper5）と、ヒストグラムにおける該中央値を含む階級までの合計画素数（図中、Median\_Sum）の、選択信号として使用される。即ち、累積加算部A104から出力されるMedian\_Upper5が目標階級を示し、Median\_Sumが該目標階級までの合計画素数を示す。

【0036】

50

## [領域選択部 105]

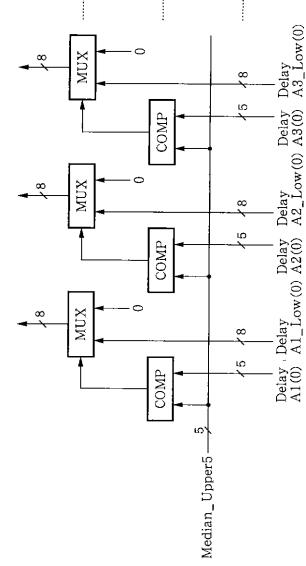

図8は、領域選択部105の回路構成を示す図である。

## 【0037】

領域選択部105においては、ヒストグラムAの目標階級を構成する画素データのみを選択する。

## 【0038】

領域選択部105においては、累積加算部A104から入力されるMedian\_Upper5信号と、遅延部101の遅延パスA201から入力された25個の上位5ビットの遅延データ(Delay A1(0~5)~Delay A5(0~5))とをそれぞれ比較することによって、マトリクス要素である25個の画素からMedian\_Upper5と同一値を有するものを選択する。

10

## 【0039】

領域選択部105には更に、遅延パスB202から出力された下位3ビットをデコードした8ビット信号(Delay A1\_Low(0~5)~Delay A5\_Low(0~5))が、マトリクス内の全ての画素に対応する形で入力される。

## 【0040】

これにより領域選択部105からは、マトリクスを構成する全25画素について、Median\_Upper5と同一の上位5ビット値を有する画素、即ち目標階級内にある画素については下位3ビットをデコードした8ビット信号が、それ以外の画素については全て0である8ビット信号が出力される。即ち、目標階級内にある画素のみが選択され、該画素のみについて、下位3ビットのデコード結果が出力される。

20

## 【0041】

このように、本実施形態においてはまずヒストグラムAを作成し、該ヒストグラムAにおいて中央値を含む階級を目標階級として絞り込む。そして、該目標階級に含まれる画素のみによって次にヒストグラムBを作成し、更にその中央値を絞り込む。即ち、2つのヒストグラムに基づく2段検索によって、マトリクス内の中央値を検索する。

## 【0042】

## [ヒストグラムB更新部106]

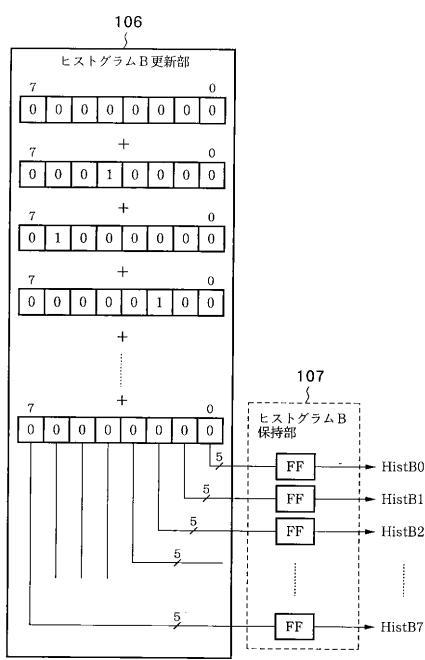

図9は、ヒストグラムB更新部106及びヒストグラムB保持部107の回路構成を示す図である。

## 【0043】

ヒストグラムB保持部107は、目標階級内にある画素の下位3ビットデータのデコード結果のヒストグラムBを保持するレジスタ群であり、5ビット幅をもつFF群を8個並列に並べることによって構成されている。この8個のFFそれぞれが、ヒストグラムBにおける各階級に相当する。即ちヒストグラムBは8つの階級を有し、各階級内の度数(画素数)はクロック毎に新たに更新される。

30

## 【0044】

ヒストグラムB更新部106においては、領域選択部105によって目標階級内にあるとして選択された画素の下位3ビットの8ビットデコード結果と、それ以外の8ビットが全て0である信号とが、計25本入力される。

## 【0045】

この領域選択部105から入力された25画素分の8ビット信号は、目標階級内にある画素については、下位3ビットの8ビットデコードであるため、いずれか1ビットのみに「1」が立っており、その他の画素については、8ビットが全て「0」である。従ってヒストグラムB更新部106においては、この「1」の立っているビット位置により、ヒストグラムBを作成する。即ち、ヒストグラムBの8階級は各ビット位置を示すものであるが、言い替えれば、画素値の下位3ビットによって表現可能な8つの値毎に、その画素数を示すものである。

40

## 【0046】

従ってヒストグラムB更新部106においては、図9に示す様に、8ビット信号の各ビット位置毎に25画素分の累積加算を行うことによって、ヒストグラムBを構成してヒスト

50

グラム B 保持部 107 に格納する。

【0047】

[累積加算部 B 108]

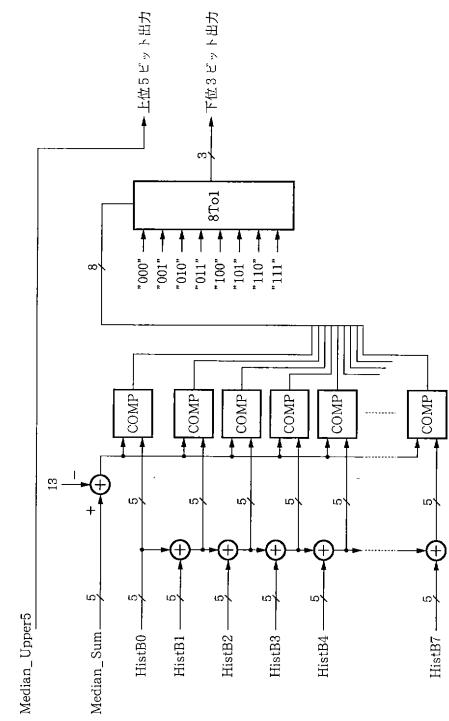

図 10 は、累積加算部 B 108 の回路構成を示す図である。

【0048】

累積加算部 B 108 においては、ヒストグラム B に基づいてマトリクスの中央値を検索する。

【0049】

累積加算部 B 108 には、ヒストグラム B 保持部 107 より各 FF の出力 (Hist B0~Hist B7)、即ちヒストグラム B における階級毎の度数 (画素数) が入力され、昇順に累積加算される。

【0050】

また、累積加算部 A 104 より入力された、ヒストグラム A における目標階級までの合計画素数を示す Median\_Sum 信号から、中央番目を表す固定値「13」が減算される。この減算結果は即ち、ヒストグラム A において絞り込まれた目標階級内の画素における、中央値の昇順の順位を表す。従って累積加算部 B 107 においては、ヒストグラム B における階級毎の画素数を昇順で累積加算していく、上記減算結果と順次比較することによって、マトリクス内の中央値における下位 3 ビットを判定することができる。そして、得られたコンパレータ出力をデコードして、下位 3 ビット出力を得る。

【0051】

そして、得られた下位 3 ビット出力と、累積加算部 A 104 より出力された Median\_Upper 5 信号とを連結することによって、マトリクス内の中央値を示す 8 ビット信号が、本実施形態におけるフィルタ回路の出力値として最終的に出力される。

【0052】

[処理フローチャート]

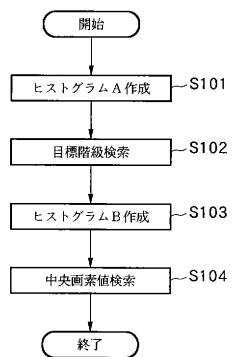

ここで、以上説明した本実施形態におけるフィルタ回路におけるフィルタリング処理を簡単にまとめて、図 11 のフローチャートを参照して説明する。

【0053】

まずステップ S101 において、マトリクス内における画素の上位ビットデータによるヒストグラム A を作成する。この処理は、主にヒストグラム A 更新部 102 によって実現される。

【0054】

次にステップ S102 において、ヒストグラム A に基づいて、中央番目に相当する画素値を含む階級を目標階級として検索する。この処理は、主に累積加算部 A 104 によって実現される。

【0055】

次にステップ S103 において、ヒストグラム A の目標階級に含まれる画素の下位ビットデータによるヒストグラム B を作成する。この処理は、主に領域選択部 105 及びヒストグラム B 更新部 106 によって実現される。

【0056】

そして最後にステップ S104 において、ヒストグラム B に基づいて、マトリクス内における中央番目の画素値を検索する。この処理は、主に累積加算部 B 108 によって実現される。

【0057】

以上のように、マトリクス内における画素の上位ビットのヒストグラムと、下位ビットのヒストグラムを作成し、2 段階による検索を行うことによって、マトリクス内の中央値を検出することができる。

【0058】

以上説明したように、本実施形態のフィルタ回路によれば、マトリクスサイズ M が増加しても回路規模はほぼ M に比例して増加するだけあるため、回路規模が劇的に増加すること

10

20

30

40

50

はない。従って、メディアンフィルタをデジタル回路にて実現することが可能となる。

【0059】

また、クロック同期設計を行う際にも、パイプラインFFの挿入を容易に可能とする構成であるため、従来の様に1クロック内での処理フローにおいて多段のコンパレータ及びセレクタ回路をシリアルに接続する必要がない。従って、データ逐次性についても整合が取れ、回路の高速化が期待できる。

【0060】

＜変形例＞

尚、本実施形態においてはフィルタ回路の出力をマトリクスの中央値とする例について説明したが、本発明はこの例に限定されない。例えば、マトリクス内の画素値の昇順でK番目を出力する場合には、図7に示す累積加算部Aにおいて累積加算値との比較対象である固定値「13」と、図10に示す累積加算部B108においてMedian\_Sumの減算量である固定値「13」を、それぞれ「K」とするのみで良い。従って、この固定値に代えて出力昇順番目を示すパラメータを設定することにより、任意の昇順番目の画素値を出力としたフィルタを構成することが容易に可能となる。

10

【0061】

尚、本発明のフィルタ回路は、複数の機器（例えばホストコンピュータ、インターフェイス機器、リーダ、プリンタなど）から構成されるシステムに適用しても、一つの機器からなる装置（例えば、複写機、ファクシミリ装置など）に適用してもよい。

20

【0062】

【発明の効果】

以上説明したように本発明によれば、大規模メディアンフィルタをデジタル回路として実現することができる。

【図面の簡単な説明】

【図1】本発明にかかる一実施形態におけるフィルタ回路のブロック構成を示す図である。

【図2】原画像に対するフィルタ処理対象マトリクスを説明するための図である。

【図3】従来のメディアンフィルタの回路構成を示す図である。

【図4】本実施形態における遅延部の回路構成を示す図である。

30

【図5】本実施形態におけるヒストグラムA更新部の回路構成を示す図である。

【図6】図5におけるインクリメント部の詳細な回路構成を示す図である。

【図7】本実施形態における累積加算部Aの回路構成を示す図である。

【図8】本実施形態における領域選択部Aの回路構成を示す図である。

【図9】本実施形態におけるヒストグラムB更新部の回路構成を示す図である。

【図10】本実施形態における累積加算部Bの回路構成を示す図である。

【図11】本実施形態のフィルタ回路における処理を示すフローチャートである。

【符号の説明】

101 遅延部

102 ヒストグラムA更新部

40

103 ヒストグラムA保持部

104 累積加算部A

105 領域選択部

106 ヒストグラムB更新部

107 ヒストグラムB保持部

108 累積加算部B

201 遅延バスA

202 遅延バスB

501 インクリメント部

502 ディクリメント部

601 データ更新部

50

602 セレクタ

【図1】

【図2】

【図3】

【 図 4 】

【 図 5 】

【 四 6 】

【図7】

【 四 8 】

【図9】

【 図 1 0 】

【図11】

---

フロントページの続き

審査官 西谷 憲人

(56)参考文献 特開平05-233802(JP, A)

特開平09-027030(JP, A)

特開平01-184587(JP, A)

特開昭58-222341(JP, A)

米国特許第06731820(US, B1)

特開2000-293681(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/14-5/217, 1/409

G06T 5/20