(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5979781号

(P5979781)

(45) 発行日 平成28年8月31日(2016.8.31)

(24) 登録日 平成28年8月5日(2016.8.5)

(51) Int.Cl.

F 1

**G02F 1/1368 (2006.01)**

**H01L 29/786 (2006.01)**

**H01L 21/336 (2006.01)**

**G02F 1/13 (2006.01)**

GO2F 1/1368

H01L 29/78 618B

H01L 29/78 612C

H01L 29/78 619B

GO2F 1/13 1O1

請求項の数 6 (全 13 頁)

(21) 出願番号

特願2012-130258 (P2012-130258)

(22) 出願日

平成24年6月7日(2012.6.7)

(65) 公開番号

特開2013-254121 (P2013-254121A)

(43) 公開日

平成25年12月19日(2013.12.19)

審査請求日

平成26年12月18日(2014.12.18)

(73) 特許権者 506087819

パナソニック液晶ディスプレイ株式会社

兵庫県姫路市飾磨区妻鹿日田町1-6

(74) 代理人 110000154

特許業務法人はるか国際特許事務所

(72) 発明者 河内 玄士朗

兵庫県姫路市飾磨区妻鹿日田町1-6 パ

ナソニック液晶ディスプレイ株式会社内

審査官 小林 俊久

最終頁に続く

(54) 【発明の名称】表示装置及び表示装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

アレイ基板を用意する工程と、

前記アレイ基板上に走査信号線を形成する工程と、

前記アレイ基板上にゲート絶縁膜を形成する工程と、

前記アレイ基板上に酸化物半導体の層を形成する工程と、

前記アレイ基板上に映像信号線を形成する工程であって、平面視において、前記映像信号線のうち前記走査信号線と直交する方向に延伸する部分と、前記走査信号線とが重なる領域内において前記酸化物半導体の層の一部分と重なり合うように映像信号線を形成する工程と、前記酸化物半導体の層の一部分にエネルギー線を照射して画素電極を形成する工程と、

を有する表示装置の製造方法。

## 【請求項 2】

前記酸化物半導体の層は、平面視において、その一部分が前記ゲート絶縁膜を介して前記走査信号線と重なり合うように形成される請求項1記載の表示装置の製造方法。

## 【請求項 3】

前記エネルギー線を照射して画素電極を形成する工程は、前記アレイ基板とカラーフィルタ基板を液晶層を挟持するよう貼り合わせた後に実施される請求項1または2記載の表示装置の製造方法。

## 【請求項 4】

アレイ基板と、

前記アレイ基板上に形成された映像信号線と走査信号線により区画された複数の画素と

、

前記画素内に配置された透明電極によって構成された共通電極と、

前記画素毎に配置されるTFTと、

前記画素内に前記共通電極上に絶縁層を介して重畳するように配置された画素電極と、

前記映像信号線上に絶縁層を介して重畳する遮蔽電極を有し、

前記TFTのチャネル半導体層と前記画素電極は一続きに連続する酸化物半導体の層であり、

平面視において、前記映像信号線のうち前記走査信号線と直交する方向に延伸する部分

と、前記走査信号線とが重なる領域内において前記チャネル半導体層と前記映像信号線と

が接する表示装置。 10

【請求項5】

前記酸化物半導体は、In、Ga, Zn、Sn、Cu、Cdから選択された1つ乃至複数の金属元素を含む金属酸化物である請求項4記載の表示装置。

【請求項6】

平面視において、前記チャネル半導体層は、ゲート絶縁膜を介して前記走査信号線と重なり合い、

前記走査信号線は、前記TFTのゲート電極として機能する請求項4又は5記載の表示装置。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は液晶表示装置及び液晶表示装置の製造方法に関する。

【背景技術】

【0002】

近年、TAOS (Transparent Amorphous Oxide Semiconductor) の一種であるIGZO (Indium-Gallium-Zinc-Oxide) が、その電気伝導率の高さから注目を集めており、アクティブマトリクス型の液晶表示装置や、有機EL表示装置に用いられるTFT (Thin Film Transistor) の構成材料としての検討がなされている。 30

【0003】

引用文献1には、IGZOからなるTFTの半導体層の上にゲート絶縁膜を介して遮光性を備えるゲート電極を形成し、紫外線を該ゲート電極の側から該半導体層に向けて照射することにより照射前よりも導電率の高いアモルファスのソース領域及びドレイン領域を構成する薄膜トランジスタの製造方法が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010-263064号公報

40

【発明の概要】

【発明が解決しようとする課題】

【0005】

液晶表示装置を製造するにあたり、TFTの構造を単純化することができれば、製造コストの低減や、TFTが占める領域を縮小することによる開口率の向上あるいは画素の高精細化といった有利な効果が期待できる。

【0006】

本発明は、IGZO或いはそれに類する材料の性質に注目することによりなされたものであり、その課題は、液晶表示装置に用いられるTFTの構造を単純化することである。

【課題を解決するための手段】

50

**【0007】**

本出願において開示される発明は種々の側面を有しており、それら側面の代表的なものの概要は以下のとおりである。

**【0008】**

(1) アレイ基板と、前記アレイ基板上に形成された映像信号線と走査信号線により区画された複数の画素と、前記画素毎に配置されるTFTと、前記画素内に配置される画素電極と、を有し、前記TFTのチャネル半導体層と前記画素電極は一続きに連続する酸化物半導体の層であり、ゲート電圧が印加されていない状態において、前記チャネル半導体層の電気伝導率より前記画素電極の電気伝導率が大きい液晶表示装置。

**【0009】**

(2) (1)において、前記酸化物半導体は、In、Ga、Zn、Sn、Cu及びCdから選択された1つ乃至複数の金属元素を含む金属酸化物である液晶表示装置。

**【0010】**

(3) (1)又は(2)において、平面視において、前記チャネル半導体層は、ゲート絶縁膜を介して前記走査信号線と重なり合い、前記走査信号線は、前記TFTのゲート電極として機能する液晶表示装置。

**【0011】**

(4) アレイ基板を用意する工程と、前記アレイ基板上に走査信号線を形成する工程と、前記アレイ基板上にゲート絶縁膜を形成する工程と、前記アレイ基板上に酸化物半導体の層を形成する工程と、前記酸化物半導体の層の一部分と重なり合うように映像信号線を形成する工程と、前記酸化物半導体の層の一部分にエネルギー線を照射して画素電極を形成する工程と、を有する液晶表示装置の製造方法。

**【0012】**

(5) (4)において、前記酸化物半導体の層は、平面視において、その一部分が前記ゲート絶縁膜を介して前記走査信号線と重なり合うように形成される液晶表示装置の製造方法。

**【0013】**

(6) (4)又は(5)において、前記エネルギー線を照射して画素電極を形成する工程は、前記アレイ基板とカラーフィルタ基板を液晶層を挟持するよう貼り合わせた後に実施される液晶表示装置の製造方法。

**【0014】**

(7) アレイ基板と、前記アレイ基板上に形成された映像信号線と走査信号線により区画された複数の画素と、前記画素内に配置された透明電極によって構成された共通電極と、前記画素毎に配置されるTFTと、前記画素内に前記共通電極上に絶縁層を介して重畳するように配置された画素電極と、前記映像信号線上に絶縁層を介して重畳する遮蔽電極を有し、前記TFTのチャネル半導体層と前記画素電極は一続きに連続する酸化物半導体の層である液晶表示装置。

**【発明の効果】****【0015】**

上記本発明の(1)、(2)又は(7)の側面によれば、液晶表示装置においてTFTの構造を単純化できる。

**【0016】**

上記本発明の(3)の側面によれば、画素の開口率の向上、又は画素の開口率を低下させることなく画素の高精細化ができる。

**【0017】**

上記本発明の(4)の側面によれば、TFTの構造を単純化した液晶表示装置が製造できる。

**【0018】**

上記本発明の(5)の側面によれば、紫外線を遮るための別途の遮光層あるいはマスクを用意することなく、画素電極を形成することができる。

10

20

30

40

50

## 【0019】

上記本発明の(6)の側面によれば、TFTのチャネル部分の導電率に影響を与えることなく、画素電極部の導電率だけを選択的に増大させることができることが可能となる。また、液晶セル組み立て後に行うことでの、増大した画素電極部の導電率を安定に保つことができる。

## 【図面の簡単な説明】

## 【0020】

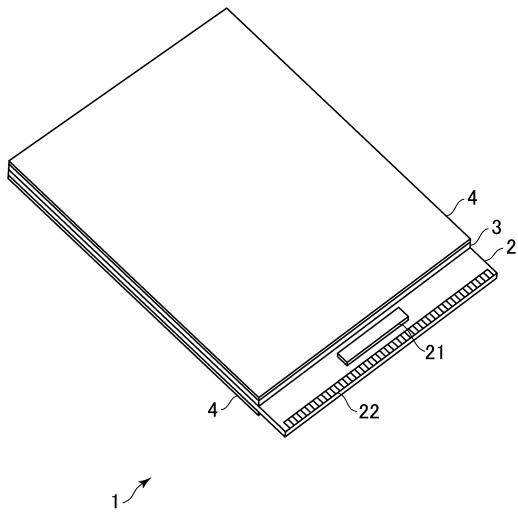

【図1】本発明の実施形態に係る液晶表示装置の外観斜視図である。

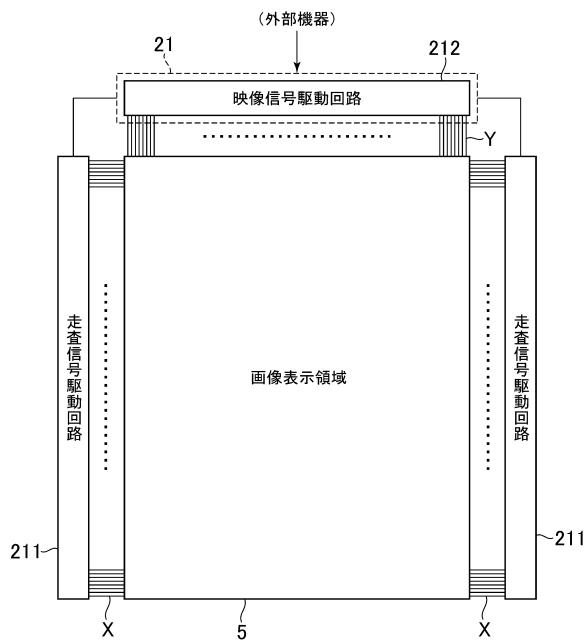

【図2】本発明の実施形態に係る液晶表示装置のアレイ基板上に形成された回路の構成を示す図である。

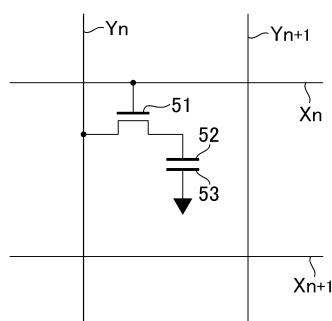

【図3】画像表示領域に形成される画素の一つを回路図により示した図である。 10

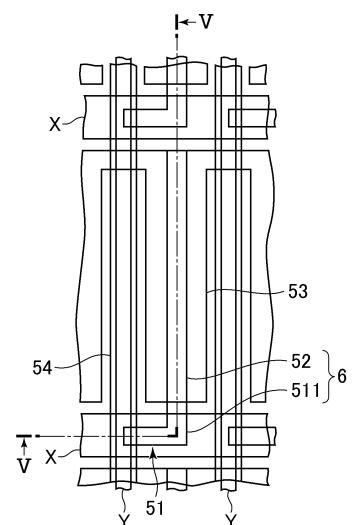

【図4】アレイ基板上の画像表示領域に含まれる画素の平面構造を示す部分拡大図である。

。

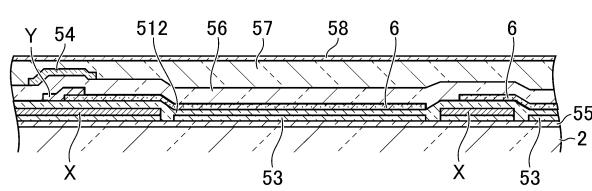

【図5】図4のV-V線による断面図である。

【図6A】液晶表示装置の製造方法を説明する図である。

【図6B】液晶表示装置の製造方法を説明する図である。

【図6C】液晶表示装置の製造方法を説明する図である。

【図6D】液晶表示装置の製造方法を説明する図である。

【図6E】液晶表示装置の製造方法を説明する図である。

【図6F】液晶表示装置の製造方法を説明する図である。

【図6G】液晶表示装置の製造方法を説明する図である。 20

## 【発明を実施するための形態】

## 【0021】

以下、本発明の実施形態を図面を参照しつつ説明する。

## 【0022】

図1は、本発明の実施形態に係る液晶表示装置1の外観斜視図である。液晶表示装置1は、アレイ基板2とカラーフィルタ基板3の間に数マイクロメートル程度の厚みの液晶材料を挟み込んだ構造であり、カラーフィルタ基板3の外周に沿って設けられるシール材により、アレイ基板2とカラーフィルタ基板3が接着されるとともに、液晶材料が漏れ出ることが無いよう封止される。 30

## 【0023】

アレイ基板2は、その前面に多数のスイッチング素子や画素電極を格子状に形成したガラス基板であり、スイッチング素子としてTFTを用いていることから、TFT基板とも呼ばれる。アレイ基板2は、図示のようにカラーフィルタ基板3より外形が大きく、その少なくとも一辺がカラーフィルタ基板3から飛び出していることにより、前面が露出している。アレイ基板2の前面の露出部分には、多数のTFTのオン/オフや、各画素電極に印加される映像信号の制御を行う制御回路であるドライバIC21が実装されているとともに、液晶表示装置1を例えばFPC(Flexible Printed Circuit)等により外部の機器と電気的に接続するための接続端子22が形成されている。 40

## 【0024】

カラーフィルタ基板3は、液晶表示装置1が画像を形成する際の単位となる画素毎に赤、緑、青に塗り分けられた色付き薄膜が形成されたガラス基板であり、かかる色付き薄膜はアレイ基板2に形成された画素電極に対応する位置に設けられる。

## 【0025】

また、アレイ基板2の背面及びカラーフィルタ基板3の前面には、偏光フィルム4が貼り付けられる。

## 【0026】

なお、以上示した実施形態では、液晶表示装置1は、いわゆる透過型であり、アレイ基板2及びカラーフィルタ基板3はガラス等の透明基板であるが、反射型とする場合には、必ずしも透明である必要はなく、その材質もガラスに限定されない。また、ここで示した実施形態では、液晶表示装置1はフルカラー表示が可能なものであるため、カラーフィル 50

タ基板 3 には赤、緑及び青の色付き薄膜が設けられているが、この色の組み合わせは異なるものとしてもよく、また、液晶表示装置 1 をモノクロ表示のものとして色付き薄膜を単色のものとし、あるいは省略してもよい。

#### 【 0 0 2 7 】

図 2 は、本発明の実施形態に係る液晶表示装置 1 のアレイ基板 2 上に形成された回路の構成を示す図である。

#### 【 0 0 2 8 】

アレイ基板 2 上には、多数の画素が格子状に配置された矩形の画像表示領域 5 が形成されている。なお、画像表示領域 5 の解像度や、左右方向及び上下方向の長さは、液晶表示装置 1 の用途に応じて定められる。本実施形態で例示する液晶表示装置 1 は縦長形状（左右方向の長さが上下方向の長さより短い）であるが、これは、液晶表示装置 1 がいわゆるスマートホン等の携帯情報端末向けの表示装置としての用途を想定しているためであり、用途によっては、画像表示領域 5 が横長形状（左右方向の長さが上下方向の長さより長い）であっても、左右方向と上下方向の長さが等しくともよい。

10

#### 【 0 0 2 9 】

アレイ基板 2 上には、画像表示領域 5 を貫くように複数の走査信号線 X と複数の映像信号線 Y が形成されている。走査信号線 X と映像信号線 Y は互いに直交しており、画像表示領域 5 を格子状に区画する。そして隣接する 2 つの走査信号線 X と隣接する 2 つの映像信号線 Y によって囲まれた領域が 1 つの画素となっている。

#### 【 0 0 3 0 】

20

図 3 は、画像表示領域 5 に形成される画素の一つを回路図により示した図である。図中に示した、走査信号線 X<sub>n</sub> 及び X<sub>n + 1</sub> 並びに映像信号線 Y<sub>n</sub> 及び Y<sub>n + 1</sub> に囲まれた領域が一つの画素となっている。ここで注目する画素は、映像信号線 Y<sub>n</sub> 及び走査信号線 X<sub>n</sub> により駆動されるものとする。各画素には、TFT51 が設けられている。TFT51 は走査信号線 X<sub>n</sub> から入力される走査信号によってオン状態となる。映像信号線 Y<sub>n</sub> は当該画素の画素電極 52 に、オン状態の TFT51 を介して電圧（各画素の階調値を表す信号）を加える。

#### 【 0 0 3 1 】

また、画素電極 52 に対応して、アレイ基板 2 とカラーフィルタ基板 3 間に挟まれて封入されている液晶層を介して容量を形成するように共通電極 53 が形成されている。共通電極 53 は、共通電位に電気的に接続される。そのため、画素電極 52 に印加された電圧に応じて、画素電極 52 と共通電極 53 の間の電界が変化し、それにより液晶層中の液晶の配向状態が変化し、画像表示領域 5 を透過する光線の偏光状態を制御する。この液晶層により制御される偏光方向と、アレイ基板 2 とカラーフィルタ基板 3 に貼り付けられた偏光フィルム 4 の偏光方向との関係により、液晶表示装置 1 を透過する光線の透過率が決まり、各画素は光の透過率を制御する素子として機能する。そして、各画素の光の透過率を入力された画像データに応じて制御することにより画像が表示される。従って、液晶表示装置 1 において、画素が形成されている領域が、画像が表示される画像表示領域 5 となる。

30

#### 【 0 0 3 2 】

40

なお、共通電極 53 が形成される基板は、液晶の駆動方式により異なっており、例えば IPS (In Plane Switching) と呼ばれる方式であればアレイ基板 2 に、また、例えば VA (Vertical alignment)、TN (Twisted Nematic) と呼ばれる方式であればカラーフィルタ基板 3 に共通電極が形成される。本発明において、液晶の駆動方式は特段限定されないが、本実施形態においては、IPS 方式を用いるものとする。

#### 【 0 0 3 3 】

図 2 に戻り、画像表示領域 5 の走査信号線 X と平行な辺の少なくとも一方の側、図示の例では画像表示領域の上側にドライバ IC 21 が設けられる。ドライバ IC 21 には、外部機器より電源電圧、接地電圧、タイミング信号や映像信号等の各種信号が入力される。

50

また、ドライバICには映像信号駆動回路212が含まれており、映像信号線Yと接続されている。なお、本実施形態では、共通電位は接地電位に等しいが、必ずしもこれに限定するものではない。また、ドライバIC21は必ずしも図1に示したようなチップ型集積回路をアレイ基板2上に実装したものとせずともよく、いわゆるSOG(System On G1ass)の手法により、アレイ基板2上に直接形成したものとしてもよい。

#### 【0034】

走査信号駆動回路211は画像表示領域の映像信号線Yと平行な辺のそれぞれの外側に設けられ、走査信号線Xと接続される。走査信号駆動回路211は外部機器から入力されるタイミング信号に応じたタイミングにより走査接続線61を順番に選択し、選択した走査接続線61にTFT51(図3参照)をオンとする電圧(以降、オン電圧という。)を印加する。走査信号線Xにオン電圧が印加されると、当該走査信号線Xに接続されたTFT51がオン状態となる。10

#### 【0035】

また、映像信号駆動回路212は映像信号線Yに接続されている。映像信号駆動回路212は走査信号駆動回路211による走査信号線Xの選択に合わせて、当該選択された走査信号線Xに接続されるTFT51のそれぞれのソース電極に、各画素の階調値を表す映像信号に応じた電圧を印加する。

#### 【0036】

図4は、アレイ基板2上の画像表示領域5に含まれる画素の平面構造を示す部分拡大図である。同図は、格子状に多数配置される画素の内の1つを示しており、走査信号線X及び映像信号線Yに囲まれた矩形の領域が1つの画素となっている。なお、同図では、各部分の位置関係及び形状を明らかとするため重なり合う部分についてもその外形を示している。20

#### 【0037】

走査信号線Xは、図中横方向に連続して延びるストリップ線であり、本実施形態では、ITO(Indium-Tin-Oxide)と銅の積層膜である。そのため、走査信号線Xは遮光性を有している。また、映像信号線Yは、走査信号線24と直交するように図中縦方向に連続して延びる銅薄膜によるストリップ線である。

#### 【0038】

画素内部には、画素電極52と、画素電極52に重なり合う位置に形成される共通電極53が配置される。画素電極52は、図示のように画素の中心部を映像信号線Yと平行な方向に延びるストリップ形状であるか、又は櫛歯形状のパターンを持つ電極であり、適宜の電圧を印加された際に、共通電極53との間に水平電界を形成するようになっている。共通電極53は、画素全体を覆うベタパターンのITO薄膜であり、走査信号線Xと平行な方向に隣接する共通電極53同士は互いに接続されている。また、映像信号遮蔽電極54は、映像信号線Yの直上に平行かつ重畠するように形成されるITO薄膜によるストリップ線である。映像信号遮蔽電極54は共通電位に接続され、映像信号線Yからのノイズ電界が画素電極52に到達しないように、映像信号線Yを電気的に遮蔽する役割を有している。これにより、画像表示時における、映像信号のクロストークによる画像の劣化を防ぐ。なお、映像信号遮蔽電極26は必須の構成ではなく、不要であれば省略してもよい。30

#### 【0039】

また、走査信号線Xと重なり合う位置には、チャネル半導体層511が形成されている。チャネル半導体層511は、その一部が映像信号線Yと重なり合うとともに、画素電極52に連続的に接続している。そのため、チャネル半導体層511の形状は、走査信号線Xと映像信号線Yが重なり合う部分から走査信号線Xに沿って延び、その後折れ曲がって画素電極52に接続するよう、L字状となっている。このチャネル半導体層511は、電界効果トランジスタのチャネルとして働く部分である。従って、チャネル半導体層511の外形で示される部分がTFT51として機能することになる。なお、後述するように、画素電極52とチャネル半導体層511は一続きに連続する酸化物半導体層6であり、本実施形態では、TAOSの一種であるIGZOである。40

## 【0040】

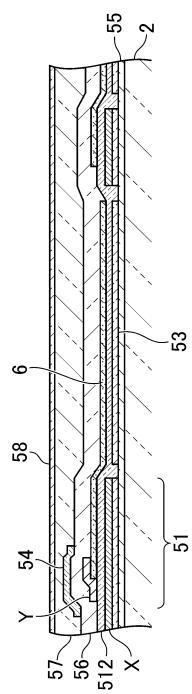

図5は、図4のV-V線による断面図である。同図は、TFT51及び画素電極52を含む断面である。アレイ基板2上に絶縁層である下地層55を形成し、かかる下地層55の上面にITO等による透明導電膜により、共通電極53及び、走査信号線Xの下地が形成される。走査信号線Xは、透明導電膜上にさらに銅を積層したものである。共通電極53と走査信号線Xはゲート絶縁膜512により覆われ、その上部に走査信号線X及び共通電極53と絶縁した状態で酸化物半導体層6が設けられる。この酸化物半導体層6のうち、走査信号線Xとゲート絶縁膜512をはさんで向き合う部分はチャネル半導体層511として、また、それ以外の部分は画素電極52として機能する(図4参照)。さらに、酸化物半導体層6のうち、チャネル半導体層511として機能する部分の一部分に重なり合い、導電接続される状態で映像信号線Yが設けられる。酸化物半導体層6、映像信号線Yは絶縁層である保護層56に覆われる。さらに、保護層56の上部に、平面視において映像信号線Yを覆うように、ITO等による透明導電膜により映像信号遮蔽電極54が設けられる。以上の構造の更に上部には、必要に応じて絶縁層である平坦化層57が設けられ、さらに配向膜58が設けられる。

## 【0041】

この構造では、酸化物半導体層6のチャネル半導体層511と向き合う部分における走査信号線Xは、TFTのゲート電極として機能する。また、チャネル半導体層511の一部分と接続される映像信号線Yはソース(又はドレイン)電極として機能する。そして、一般的なTFTでは、チャネル半導体層511の他の部分にソース電極と絶縁された形でドレイン電極が設けられるのであるが、本実施形態で示した構造では、チャネル半導体層511に連続的に連なる酸化物半導体層6の画素電極52として機能する部分が、ドレイン電極としての機能を果たすことになる。かかる構造においては、映像信号線Yとソース電極を接続するためのスルーホール及び、画素電極52とドレイン電極を接続するためのスルーホールを設ける必要がなく、画素を構成する各部材を接続するスルーホールが不要とされている。そのため、TFT51の構造が単純化され、また、スルーホールを形成するために必要とされるスペースが必要ないため、画素の開口率の向上、又は開口率を低下させることなく画素のサイズを縮小して高精細化を図ることができる。さらに、画素を形成する際に、ドレイン電極を作成する工程や、スルーホールを作成する工程が不要となるため、製造コストの低減が見込まれる。

## 【0042】

ところで、酸化物半導体層6は、電界効果トランジスタのチャネルであるから、ゲート電極からの電界が作用しない状態では抵抗が大きく、キャリアを流すことができない。そして、酸化物半導体層6の画素電極52として機能する部分には、ゲート電極として機能する部分は存在しないため、このままでは画素電極52としての性能を得ることができない。そこで、図5の下側、すなわち、アレイ基板2の背面から紫外線、電子線等のエネルギー線を照射することにより、酸化物半導体層6のエネルギー線が照射された部分にキャリアを形成し、電気伝導率を高めることにより、画素電極52として機能し得る程度に抵抗を下げる所以である。このとき、走査信号線Xは銅の層を有しており、遮光性を持つため、チャネル半導体層511の特性が変化することはない。なお、本実施形態での酸化物半導体層6の材質であるIGZOは紫外線により電気伝導率を高めることができる。酸化物半導体層6として使用し得る材料はIGZOに限定されないが、遮蔽可能なエネルギー線の照射によりその電気伝導率を上昇させることができる材料であることが必要である。このような材料として、In、Ga、Zn、Sn、Cu及びCdから選択された1つ乃至複数の金属元素を含む金属酸化物が挙げられる。また、酸化物半導体層6としてIGZOを用いる場合には、IGZOに接する絶縁層(本実施形態では、ゲート絶縁膜512及び保護層56があたる)として窒化膜を使用することができないので、SiO<sub>2</sub>膜等窒素を含まない絶縁膜を用いる必要がある。

## 【0043】

本実施形態のように、TFT51が、ゲート電極(すなわち、走査信号線X)が下層に

10

20

30

40

50

配置されるボトムゲート型のものである場合にはエネルギー線をアレイ基板2の背面から照射し、逆の構造であるトップゲート型のものである場合にはエネルギー線をアレイ基板2の前面から照射するようにすると、遮光のための構造を別異に作成する必要がなく有利である。また、ボトムゲート型のものでは、アレイ基板2とカラーフィルタ基板3とを貼り合わせ、その間に液晶層を狭持させた後にエネルギー線を照射することができる。

#### 【0044】

アレイ基板2とカラーフィルタ基板3とを貼り合わせて液晶セルを組み立てた後には200以上高い温度での熱処理工程がない。IGZOのような酸化物半導体の導電率は紫外光照射により増大し低抵抗状態となるが、熱処理工程を経ることにより元の高抵抗状態に回復する性質を持つ。したがって、画素電極の電導率を大きくした状態を安定に保つためには、紫外線照射後に高温での熱処理工程がないことが必要である。そのため、現在一般的に用いられている液晶表示装置1の製造工程においては、アレイ基板2の製造工程後ではなく、液晶セルの組み立て工程後に紫外光照射を行うことが望ましい。10

#### 【0045】

なお、図5で示した断面構造は、液晶表示装置1がいわゆるIPS方式のものであるため共通電極53が画素電極52の下層に配置されるものとされているが、液晶の駆動方式が他の方式、例えば、VA方式あるいはTN方式の場合には、共通電極53はカラーフィルタ基板3側に作成されるため、アレイ基板2上には形成されない。

#### 【0046】

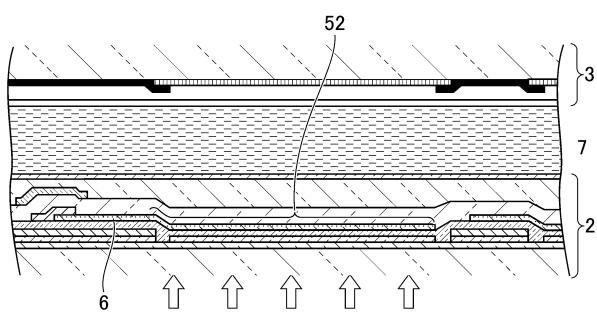

続いて、液晶表示装置1の製造方法を、アレイ基板2を中心に図6A乃至図6Gを参照しつつ説明する。なお、図6A乃至図6Gは、図5と同じ位置における断面を示している。20

#### 【0047】

まず、アレイ基板2を用意する。

#### 【0048】

続いて、アレイ基板2上に絶縁層である下地層55を形成する(図6A)。

#### 【0049】

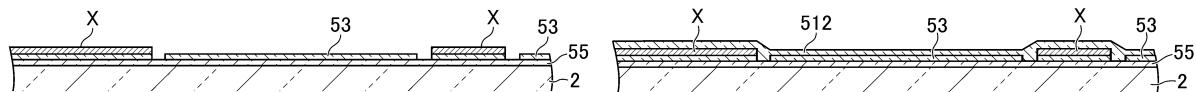

さらに、下地層55上に共通電極53と走査信号線Xを形成する(図6B)。この工程は、まず、透明導電膜(この場合はITO)により共通電極53と、走査信号線Xの下地を形成し、さらに走査信号線Xとなるべき部分に銅膜を積層する工程である。なお、液晶表示装置1の液晶の駆動方式がIPS方式でない場合には、共通電極53の形成が省略される場合がある。30

#### 【0050】

次に、ゲート絶縁膜512を形成する(図6C)。ゲート絶縁膜512は共通電極53及び走査信号線Xを含む、画像表示領域5の全面を覆う。

#### 【0051】

さらに、ゲート絶縁膜512上に酸化物半導体層6を形成する(図6D)。この時点では、酸化物半導体層6の電気伝導率に部分による差異はない。

#### 【0052】

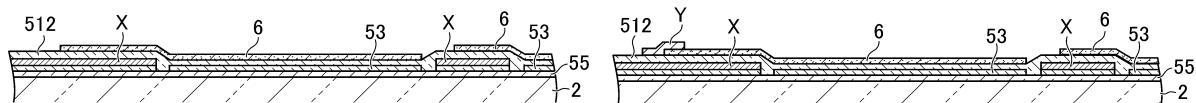

続いて、酸化物半導体層6の一部分、特に将来的にチャネル半導体層511として機能する部分と重なり合うように映像信号線Yを形成する(図6E)。映像信号線Yは、銅やアルミ等の金属膜である。なお、将来的にチャネル半導体層511として機能する部分は、走査信号線Xと重なり合う部分であるから、映像信号線Yは、酸化物半導体層6と走査信号線Xが重なり合う領域の一部分において、酸化物半導体層6と重なり合い接続されることになる。40

#### 【0053】

次に、保護層56を形成し、さらにその上部に映像信号遮蔽電極54を形成し、必要に応じて平坦化層57を設けた後、配向膜58を形成する(図6F)。配向膜58の配向処理は、いわゆるラビングによるものであっても、光配向処理によるものであってもよいが、光配向処理を行う場合、同処理において用いられる偏光紫外線によりチャネル半導体層50

511の特性が変化するこがないように紫外線の波長や照射エネルギー総量を選択しなければならない。

#### 【0054】

以上の処理によりアレイ基板2と、別の工程において制作したカラーフィルタ基板3とを液晶層7を挟んで貼り合わせた後、アレイ基板2の背面からエネルギー線を照射して酸化物半導体層6の一部の特性を変化させ、画素電極52を形成する(図6G)。

#### 【0055】

なお、以上の説明では、液晶表示装置1を製造する上で必要ではあるが本発明と直接の関係が薄い部分、例えば、液晶層の封止の工程や、走査信号駆動回路211等の周辺回路を形成する工程、ドライバIC21を実装する工程等の説明は省略した。 10

#### 【0056】

なお、以上説明した各実施形態において化体された具体的な構成は、本発明を説明する上で例示されたものであり、本発明の技術的範囲をかかる具体的な構成に限定するものではない。当業者は、上記各実施形態において開示された内容を適宜変形乃至最適化することができ、例えば、各部材の配置位置、数、形状等は必要に応じ任意に変更してよい。

#### 【符号の説明】

#### 【0057】

1 液晶表示装置、2 アレイ基板、3 カラーフィルタ基板、4 偏光フィルム、5 画像表示領域、6 酸化物半導体層、21 ドライバIC、22 接続端子、23 機能膜、31 機能膜、51 TFT、52 画素電極、53 共通電極、54 映像信号遮蔽電極、55 下地層、56 保護層、57 平坦化層、58 配向膜、211 走査信号駆動回路、212 映像信号駆動回路、511 チャネル半導体層、512 ゲート絶縁膜。 20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 6 E】

【図6F】

【図6G】

---

フロントページの続き

(56)参考文献 特開2003-050405(JP,A)

特開2010-230744(JP,A)

特開2010-147351(JP,A)

国際公開第2013/115052(WO,A1)

特開昭63-097919(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 13

G 02 F 1 / 1368