(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5077789号

(P5077789)

(45) 発行日 平成24年11月21日(2012.11.21)

(24) 登録日 平成24年9月7日(2012.9.7)

(51) Int.Cl.

F 1

G02F 1/1337 (2006.01)

G02F 1/1337 505

G02F 1/1343 (2006.01)

G02F 1/1343

G02F 1/1368 (2006.01)

G02F 1/1368

請求項の数 4 (全 17 頁)

(21) 出願番号

特願2005-280555 (P2005-280555)

(22) 出願日

平成17年9月27日 (2005.9.27)

(65) 公開番号

特開2006-106739 (P2006-106739A)

(43) 公開日

平成18年4月20日 (2006.4.20)

審査請求日

平成20年9月22日 (2008.9.22)

(31) 優先権主張番号

093129719

(32) 優先日

平成16年9月30日 (2004.9.30)

(33) 優先権主張国

台湾(TW)

(73) 特許権者 510134581

奇美電子股▲ふん▼有限公司

Chime i Innolux Corp

oration台灣苗栗縣竹南鎮科學路160號 新竹

科學工業園區No. 160 Kesyue Rd., C

hu-Nan Site, Hsinchu

Science Park, Chu-N

an 350, Miao-Li Coun

ty, Taiwan,

(74) 代理人 110000110

特許業務法人快友國際特許事務所

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

垂直配向処理が施されている第1基板および第2基板と、

前記第1基板と第2基板の間に介在している液晶層と、

前記第2基板に設けられており、互いに略平行に伸びている複数のゲート線と、

前記第2基板に設けられており、互いに略平行に伸びているとともに前記ゲート線に直

交しており、前記ゲート線とともに複数の画素領域をマトリクス状に画定している複数の

データ線と、

前記第1基板に設けられている共通電極と、

前記第2基板に設けられており、それぞれが前記画素領域のそれぞれに対応して位置し

ている複数の画素電極と、

前記第1基板に設けられており、互いに略平行に伸びており、前記画素電極から液晶層

に電圧が印加されたときに液晶層の液晶分子が配向する方向を画素領域における位置に応

じて変化するように調整する複数の第1調整手段と、

前記第2基板に設けられており、前記第1調整手段に略平行に伸びてあり、前記画素電

極から液晶層に電圧が印加されたときに液晶層の液晶分子が配向する方向を画素領域にお

ける位置に応じて変化するように調整する複数の第2調整手段を備え、

前記第1調整手段と前記第2調整手段は交互に配置されており、前記第1調整手段と前

記第2調整手段との間隔が30マイクロメートル以上であり、

前記第1調整手段は、前記第1基板に設けられている線状突起であり、

10

20

前記第2調整手段は、前記画素電極に設けられているスリットであり、

前記スリットには、鋸歯状に配列している複数の第2スリットが形成されており、

隣接する線状突起とスリットとの間隔をcとし、第2スリットの最小深さをaとし、最

小深さaを有する第2スリットと線状突起との間の距離をbとすると、間隔cは最小深さ

aに距離bを加えたものに等しいことを特徴とする液晶表示装置。

**【請求項2】**

前記スリットと前記線状突起との間隔が50マイクロメートル以下であることを特徴と

する請求項1の液晶表示装置。

**【請求項3】**

垂直配向処理が施されている第1基板および第2基板と、 10

前記第1基板と第2基板の間に介在している液晶層と、

前記第2基板に設けられており、互いに略平行に伸びている複数のゲート線と、

前記第2基板に設けられており、互いに略平行に伸びているとともに前記ゲート線に直

交しており、前記ゲート線とともに複数の画素領域をマトリクス状に画定している複数の

データ線と、

前記第1基板に設けられている共通電極と、

前記第2基板に設けられており、それぞれが前記画素領域のそれぞれに対応して位置し

ている複数の画素電極と、

前記第1基板に設けられており、互いに略平行に伸びており、前記画素電極から液晶層 20

に電圧が印加されたときに液晶層の液晶分子が配向する方向を画素領域における位置に応

じて変化するように調整する複数の第1調整手段と、

前記第2基板に設けられており、前記第1調整手段に略平行に伸びてあり、前記画素電

極から液晶層に電圧が印加されたときに液晶層の液晶分子が配向する方向を画素領域にお

ける位置に応じて変化するように調整する複数の第2調整手段を備え、

前記第1調整手段と前記第2調整手段は交互に配置されており、前記第1調整手段と前

記第2調整手段との間隔が30マイクロメートル以上であり、

前記第1調整手段は、前記共通電極に設けられているスリットであり、

前記第2調整手段は、前記第2基板に設けられている線状突起であり、

前記スリットには、鋸歯状に配列している複数の第2スリットが形成されており、

隣接する線状突起とスリットとの間隔をcとし、第2スリットの最小深さをaとし、最 30

小深さaを有する第2スリットと線状突起との間の距離をbとすると、間隔cは最小深さ

aに距離bを加えたものに等しいことを特徴とする液晶表示装置。

**【請求項4】**

垂直配向処理が施されている第1基板および第2基板と、

前記第1基板と第2基板の間に介在している液晶層と、

前記第2基板に設けられており、互いに略平行に伸びている複数のゲート線と、

前記第2基板に設けられており、互いに略平行に伸びているとともに前記ゲート線に直

交しており、前記ゲート線とともに複数の画素領域をマトリクス状に画定している複数の

データ線と、

前記第1基板に設けられている共通電極と、

前記第2基板に設けられており、それぞれが前記画素領域のそれぞれに対応して位置し

ている複数の画素電極と、

前記第1基板に設けられており、互いに略平行に伸びてあり、前記画素電極から液晶層 40

に電圧が印加されたときに液晶層の液晶分子が配向する方向を画素領域における位置に応

じて変化するように調整する複数の第1調整手段と、

前記第2基板に設けられており、前記第1調整手段に略平行に伸びてあり、前記画素電

極から液晶層に電圧が印加されたときに液晶層の液晶分子が配向する方向を画素領域にお

ける位置に応じて変化するように調整する複数の第2調整手段を備え、

前記第1調整手段と前記第2調整手段は交互に配置されており、前記第1調整手段と前

記第2調整手段との間隔が30マイクロメートル以上であり、

10

20

30

40

50

前記第1調整手段は、前記共通電極に設けられているスリットであり、

前記第2調整手段は、前記画素電極に設けられているスリットであり、

前記スリットには、鋸歯状に配列している複数の第2スリットが形成されており、隣接するスリットとスリットとの間隔をcとし、第2スリットの最小深さをaとし、最小深さaを有する第2スリットとスリットとの間の距離をbとすると、間隔cは最小深さaに距離bを加えたものに等しいことを特徴とする液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置(Liquid Crystal Display)に関する。特に、マルチドメイン垂直配向(Multi-domain Vertically Aligned, MVA)型の液晶表示装置に関する。 10

【背景技術】

【0002】

液晶表示装置は、液晶ディスプレイパネルを備えている。液晶ディスプレイパネルは、対向配置されている2枚のガラス基板と、その2枚のガラス基板の間に挟持されている液晶層を備えている。

垂直配向(Vertically Aligned, VA)型の液晶表示装置では、ネガ型液晶材料と、垂直配向処理が施されているガラス基板が用いられる。一般に、ガラス基板への垂直配向処理には、ガラス基板に垂直配向膜を附加することで行われる。ガラス基板に施された垂直配向処理は、液晶層に電圧が印加されていないときに、液晶層の液晶分子をガラス基板の主表面に対して垂直に配向させる。液晶層の液晶分子がガラス基板の主表面に対して垂直に配向していると、入射光が液晶ディスプレイパネルを透過できなくなり、画面は黒表示となる。一方、液晶層に所定の電圧が印加されると、液晶層の液晶分子は水平方向に向けて傾斜することから、入射光が液晶ディスプレイパネルを透過できるようになる。このとき、画面は白表示となる。 20

【0003】

垂直配向型の液晶表示装置では、見る人の視線が表示画面に対する垂直方向から変化すると、コントラストが低下したりコントラストが反転したりする問題が生じる。これは、光と液晶ディスプレイ内の液晶分子の相互作用の結果であり、光が非垂直の入射角で液晶ディスプレイパネルを通過したときと、光が垂直の入射角で液晶ディスプレイパネルを通過したときでは、光と液晶分子との相互作用の形態が異なることに起因する。表示画面を斜視したときに光の透過状態(白)と非透過状態(黒)とのコントラストが顕著に低下してしまうことは、表示装置の様々な応用(例えば、テレビ受像機のフラット画面およびパーソナルコンピュータの大型ディスプレイ)における障壁となっている。 30

【0004】

上記の問題に対して、マルチドメイン垂直配向(Multi-domain Vertically Aligned, MVA)型の液晶表示装置が開発されている。マルチドメイン垂直配向型液晶表示装置は、電圧印加時の液晶分子の配向方向を画素領域における位置によって変化させることによって、視野角特性が改善されたものである。

特許文献1には、視野角特性を改善するために、液晶分子の配向方向を調整する調整手段を備えたマルチドメイン垂直配向型液晶表示装置が開示されている。この調整手段は、典型的には、カラーフィルタ基板の共通電極上に設けられている複数の線状突起と、薄膜トランジスタ基板の画素電極に設けられている複数のスリットによって構成されている。複数の線状突起と複数のスリットは交互に配列されている。液晶分子の配向方向は、線状突起とスリットの配置パターンによって生じるフリンジ・フィールド(fringe field)効果により決定される。 40

特許文献1の液晶表示装置の駆動では、外部から駆動電圧を印加することで各々の画素内の液晶分子を回転させ、液晶分子の回転によって各々の画素の光透過率を変えることで、各々の画素に異なる輝度を表示している。

【特許文献1】欧州特許出願公開第0884626号明細書

50

20

30

40

50

## 【0005】

一般に、液晶表示装置では、初期電圧が固定されている場合、外部から高電圧が印加されるほど、応答時間は短くなる。しかしながら、一部の液晶表示装置では、このことが完全に当てはまらない。

例えば非特許文献1には、パターンニングされた垂直配向(Patterned Vertical Alignment, PVA)型の液晶表示装置では、ある条件下において、外部から高電圧が印加されたときに、応答時間が逆に遅くなることが報告されている。同様の事象は、マルチドメイン垂直配向型の液晶表示装置にも発生する。

【非特許文献1】「DCCII: Novel Method for Fast Response in PVA Mode」、情報ディスプレイ協会(SID)、2004年

10

## 【0006】

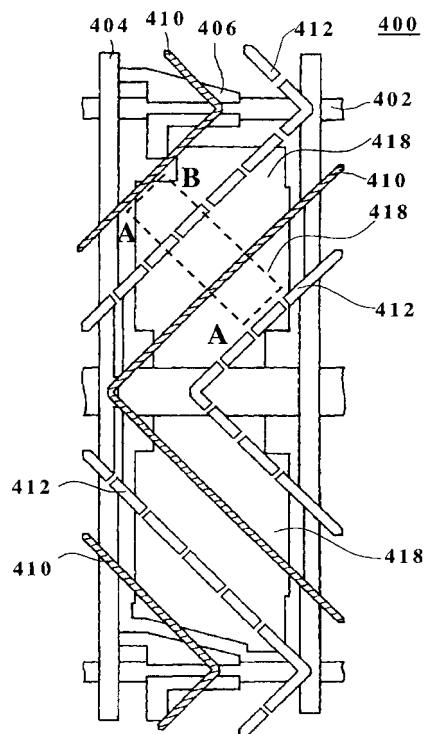

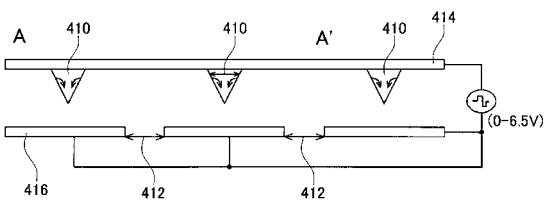

図9Aは従来のマルチドメイン垂直配向型液晶表示装置の画素領域における線状突起とスリットの配置を示す図であり、図9Bは図9AのA-A線の断面を示す図である。図9Aに示すように、液晶表示装置の画素領域400はゲート線402とデータ線404によって画定されている。画素領域400には、ゲート線402とデータ線404とに接続されている薄膜トランジスタ406が設けられているとともに、薄膜トランジスタ406に接続されている画素電極408が配設されている。図9Bに示すように、画素領域400には、線状突起410とスリット412が配設されている。線状突起410はカラーフィルタ基板414に形成されており、スリット412は薄膜トランジスタ基板416に形成されている。線状突起410とスリット412は、液晶分子の方向と上下の偏光板(図示しない)を貫通する軸とが45度をなすように配設されており、光がマルチドメイン垂直配向型の液晶表示装置を通過したときに、最大の中間調の明るさを表現できるようになっている。しかしながら、液晶分子の配向に異常が生じると、線状突起410とスリット412による調整の下でも、液晶分子の方向と上下の偏光板を貫通する軸とが45度とならなくなる。このとき、光が液晶表示装置を通過しても、最大の中間調の明るさを表現することはできない。

20

## 【0007】

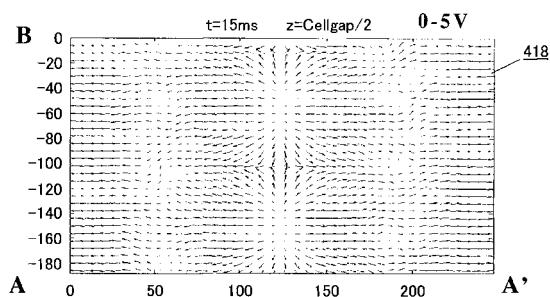

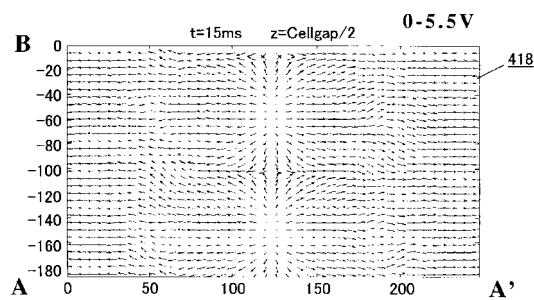

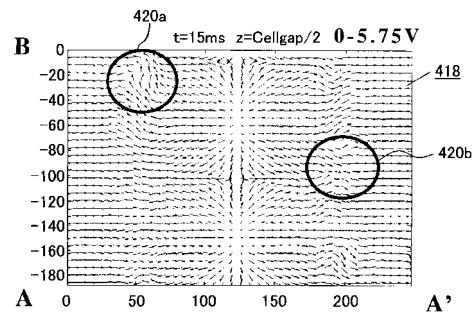

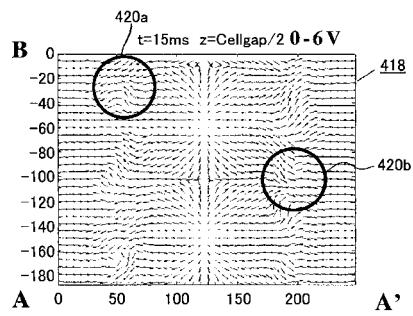

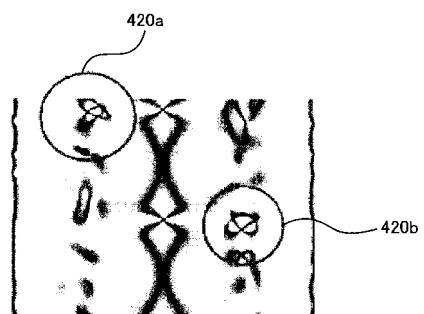

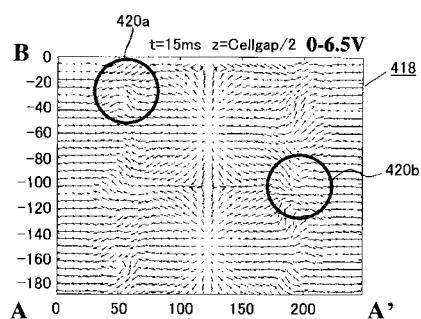

図10Aから図10Eは、図9Aに示す領域418の液晶分子に所定時間に亘って駆動電圧を印加したときに、線状突起とスリットによるフリンジ・フィールド効果によって生じる液晶分子の配列方向を、異なる駆動電圧毎に示すものである。図10A～10Eの横軸A-A'は、図9AのA-A方向に対応しており、図10Aから10Eの縦軸A-Bは、図9AのA-B方向に対応している。図10A、図10Bに示すように、外部印加電圧がそれぞれ5Vおよび5.5Vである場合、領域418の液晶分子は、フリンジ・フィールド効果によって正常に配向する。しかしながら、図10Cから図10Eに示すように、外部印加電圧が5.75V、6.0V、6.5Vまで上昇した場合、領域418内の一部の領域420a、420bの液晶分子は、フリンジ・フィールド効果に抗して、異常な方向に配向してしまう。特に、図10Eに示す場合では、範囲420a、420bにおける液晶分子の異常な配向が、液晶表示装置に深刻な問題を引き起こすものになりうる。

30

## 【0008】

液晶分子の異常配向をもたらす要因の1つとして、線状突起410とスリット412との間隔が挙げられる。線状突起410やスリット412の近傍に位置する液晶分子は、線状突起410やスリット412によるフリンジ・フィールド効果によって、配向方向が所定の方向に調整される。線状突起410とスリット412の間に位置する液晶分子は、線状突起410やスリット412側に隣接する液晶分子に追従しながら所定の方向に配向していく。そのことから、線状突起410とスリット412とが離れていると、線状突起410とスリット412との間に位置する領域420a、420bの液晶分子は、隣接する液晶分子に追従して所定の方向に配向するのに長い時間が必要となる。その結果、液晶分子の配向方向が正しく調整されず、液晶分子が異常な方向に配向してしまう。

40

## 【0009】

また、液晶分子の異常な配向の要因として、瞬間に高電圧が印加されたときに、線状

50

突起 410 とスリット 412 との略中間に位置する領域 420a、420b の液晶分子が、隣接する液晶分子の傾斜に追従して配向していくよりも前に、印加された垂直電界によって異常な方向に傾斜してしまうことが考えられる。その結果、図 10C から図 10E に示すように、線状突起 410 とスリット 412 との略中間に位置する領域 420a、420b の液晶分子は、フリンジ・フィールド効果による配向方向の調整を受けることなく、異常な方向に配向することとなる。そして、図 11 に示すように、図 10E の異常配向している領域 420a、420b の液晶分子を光学顕微鏡で観察した場合、グレイスポット (gray spot) やブラックスポット (black spot) が観察される。

#### 【0010】

上記したグレイスポットやブラックスポットは、勝手な方向に傾斜した液晶分子の方位と上下の偏光板を貫通する軸とがなす角が 45 度となっていないことに起因して発生するものである。異常に配向している液晶分子は、この後、隣接する液晶分子の影響を受けながら正常な配向方向へと復帰していく。この配向方向の復帰に長い時間を要することから、液晶分子の応答時間が長くなってしまう。また、隣接する液晶分子の駆動によっても、異常に配向している液晶分子が正常な配向方向に復帰しない場合もある。液晶分子はグレイスポットやブラックスポットを示すようになり、本来の明るさを取り戻すことができなくなる可能性がある。

#### 【0011】

上記から理解できるように、マルチドメイン垂直配向型の液晶表示装置では、駆動時における閾値電圧が存在する。印加電圧がこの閾値電圧を超えててしまうと、上記した液晶分子の異常配向が生じてしまう。従来の液晶表示装置では、設計上、応答時間が長くならないように、駆動バイアス電圧がこの閾値電圧を超えないように制限しなければならない。さらに従来の液晶表示装置の設計では、異常配向という問題を回避するために、線状突起とスリットとの間隔をある程度狭く設定する必要がある。それにより、閾値電圧を高めて、駆動電圧の使用可能範囲を広げるようになっている。しかしながら、線状突起とスリットとの間隙を狭く設定すると、1つの画素内に設ける線状突起とスリットの数が増大してしまう。線状突起やスリットが設けられている範囲は表示領域とはならないことから、線状突起やスリットを多数設けると、画素領域の開口率が低下してしまい、液晶表示装置の明るさが低下してしまう。

#### 【0012】

特許文献 2 に開示されているマルチドメイン垂直配向型の液晶表示装置では、画素電極のスリットに鋸歯状の第 2 スリットがさらに形成されている。この液晶表示装置では、鋸歯状の第 2 スリットを設けることにより、液晶の応答時間を維持しながら、線状突起とスリットとの間隔の拡大を図っている。しかしながら、液晶分子の異常配向という問題を完全に解決することはできず、依然として線状突起とスリットとの間にある程度の間隔を確保する必要があり、開口率の向上にも限りがある。

#### 【特許文献 2】米国特許出願公開第 2002 / 0159018 号明細書

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0013】

本発明の主な目的は、上記の従来技術における問題を克服または少なくとも改善可能であって、マルチドメイン垂直配向型の液晶表示装置の開口率を向上するための技術を提供することである。

#### 【課題を解決するための手段】

#### 【0014】

本発明によって具現化される液晶表示装置は、垂直配向処理が施されている第 1 基板および第 2 基板と、第 1 基板と第 2 基板の間に介在している液晶層と、第 2 基板に設けられており、互いに略平行に伸びている複数のゲート線と、第 2 基板に設けられており、互いに略平行に伸びているとともに前記ゲート線に直交しており、ゲート線とともに複数の画素領域をマトリクス状に画定している複数のデータ線と、第 1 基板に設けられている共通

10

20

30

40

50

電極と、第2基板に設けられており、それぞれが前記画素領域のそれぞれに対応して位置している複数の画素電極を備えている。即ち、この液晶表示装置は、いわゆる垂直配向型の液晶表示装置である。液晶層の液晶分子は、第1基板や第2基板に施された垂直配向処理によって、液晶層に電圧が印加されていないときに、第1基板の主表面に略垂直となるように配向する。

また、この液晶表示装置は、第1基板に設けられており、互いに略平行に伸びている複数の第1調整手段と、第2基板に設けられており、第1調整手段に略平行に伸びている複数の第2調整手段を備えている。第1調整手段や第2調整手段は、画素電極から液晶層に電圧が印加されたときに液晶層の液晶分子が配向する方向を調整するものであり、液晶分子が配向する方向を画素領域における位置に応じて変化するように調整する。そして、この液晶表示装置では、第1調整手段と第2調整手段が交互に配置されており、前記第1調整手段と前記第2調整手段との間隔が30マイクロメートル以上であることを特徴とする。

10

#### 【0015】

上記の液晶表示装置では、第1調整手段は、第1基板に設けられている線状突起であることが好ましい。このとき、線状突起は、共通電極上に設けることができる。また、第2調整手段は、画素電極に設けられているスリットであることが好ましい。

あるいは、第1調整手段は、共通電極にスリットを設けることによって構成することができる。また、第2調整手段は、第2基板に線状突起を設けることによって構成することもできる。第1調整手段と第2調整手段は、線状突起やスリットを様々に組み合わせて構成することもできる。

20

スリットには、鋸歯状に配列している複数の第2スリットが形成することができる。この場合、隣接する線状突起（スリット）とスリットとの間隔をcとし、第2スリットの最小深さをaとし、最小深さaを有する第2スリットと線状突起（スリット）との間の距離をbとすると、間隔cは最小深さaに距離bを加えたものに等しいことが好ましい。

#### 【0016】

上記の液晶表示装置では、駆動電圧を液晶層の画素領域に印加する際に、駆動電圧を少なくとも2段階に分けて上昇させることができることが好ましい。この駆動電圧を印加する方式を採用すると、高い駆動電圧を印加することが可能となる。その結果、第1調整手段と第2調整手段との間隔が $25\mu m$ 以上であっても、液晶分子が異常な方向に配向することを抑止することができる。

30

なお、駆動電圧を段階的に上昇させるという技術は、本願出願人が創作し、2004年8月20日に台湾において特許出願（台湾特許出願第93123879号）されている。

#### 【0017】

第1調整手段が線状突起であり、第2調整手段がスリットである場合、そのスリットに鋸歯状に配列している複数の第2スリットが形成されていることが好ましい。この場合、駆動電圧を段階的に上昇させる前記の駆動方法を採用することによって、第1調整手段である線状突起と第2調整手段であるスリットとの間隔を $30\mu m$ から $50\mu m$ の間に設定しても、液晶分子が異常に配向することを抑制することができる。

40

#### 【0018】

前記マルチドメイン垂直配向型の液晶表示装置において、線状突起とスリットとが比較的広いピッチを有するように配置できるため、線状突起やスリットが配置される密度を効果的に減らし、これにより開口率（つまり光が透過可能な領域の比率）を効果的に高め、液晶表示装置の明るさを向上させることができる。

#### 【0019】

線状突起には、画素電極の縁部に対向する位置に、少なくとも一つの分岐部が設けられていることが好ましい。

#### 【0020】

画素電極は、スリットによって複数の部分電極に分割されているとともに、隣接する2つの部分電極同士を接続する少なくとも1つの接続部を有していることが好ましい。この

50

とき、接続部は、第1部分と第2部分とを有しており、その第1部分は線状突起に対して略垂直に伸びており、その第2部分はデータ線に略平行に伸びていることが好ましい。そして、接続部の第2部分は、線状突起の分岐部と完全に重なる位置に形成されていることが好ましい。

#### 【0021】

上記の液晶表示装置では、画素領域に、2つのサイド部とその2つのサイド部を接続している中央部とを有する「H」字形状のキャパシタ電極が設けられていることが好ましい。この場合、キャパシタ電極の各サイド部は、その画素領域を画定している各データ線の近傍にそれぞれ位置しており、キャパシタ電極と画素電極が、蓄電ユニットを形成していることが好ましい。

10

#### 【発明の効果】

#### 【0022】

本発明によると、線状突起やスリットからなる液晶分子の配向方向を調整する手段を、比較的に広い間隔で設けることが可能となる。それにより、液晶表示装置の開口率を高めることが可能となる。

#### 【発明を実施するための最良の形態】

#### 【0023】

本発明の目的、特徴、利点をさらに明瞭にするために、本発明を実施する好適な実施形態について、図面を参照しながら詳細に説明する。

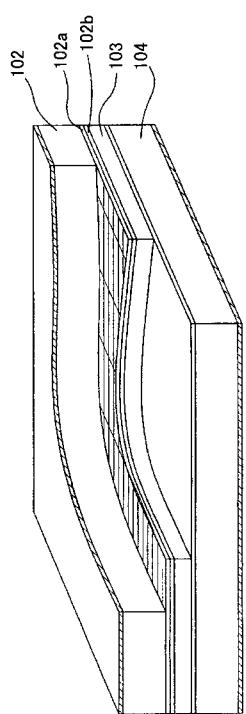

図8に示すように、本発明を実施したマルチドメイン垂直配向型の液晶表示装置は、垂直配向処理が施されている第1基板102および第2基板104と、第1基板102と第2基板104の間に介在している液晶層103を備えている。液晶層103に含まれている液晶分子は、液晶層103に駆動電圧が印加されていないときに、第1基板の主表面に略垂直となっている。

20

詳しくは後述するが、第1基板102上には、第1調整手段が設けられている。また、第2基板104上には、第2調整手段が設けられている。第1調整手段と第2調整手段は、液晶層103に駆動電圧が印加されたときの液晶分子の配向方向を調整するものである。第1調整手段と第2調整手段により、液晶層103の液晶分子は、画素内の領域（ドメイン）毎に、所定の方向へと傾斜配向する。このマルチドメイン垂直配向型の液晶表示装置では、画素内の液晶分子の配向方向が互いに異なる複数の方向に調整されることにより、視野角特性が改善されている。

30

本発明の技術は、例えば、薄膜トランジスタ液晶表示装置（Thin film transistor liquid crystal display；TFT LCD）に有效地に実施することができる。

図8に示すように、第1基板102には、例えば遮光層である遮光アレイ（図8中には図示しない）や、複数枚のカラーフィルタ102aや、共通電極102bが設けられている。

#### 【0024】

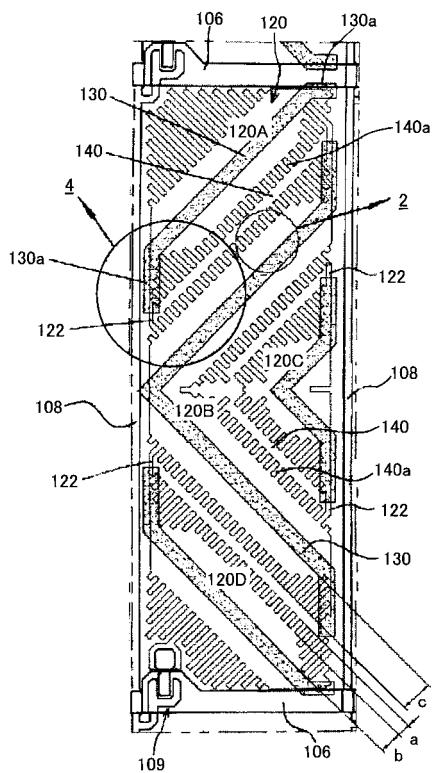

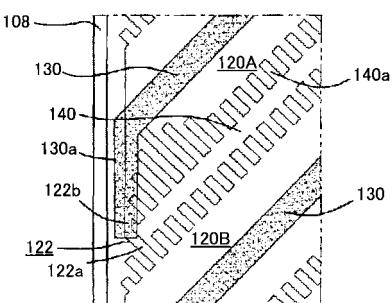

図1は、第2基板104（104は図1に図示しない）の一つの画素領域を示している。第2基板104には、互いに平行な複数本のゲート線106と、ゲート線106に直交してあり互いに平行な複数本のデータ線108と、複数の薄膜トランジスタ109と、画素電極120とが設けられている。薄膜トランジスタ109と画素電極120は、マトリックス状に配置されている。薄膜トランジスタ109は、ゲート線106とデータ線108との交差部分に配置されている。

40

第1基板102には、カラーフィルタが設けられていることから、カラーフィルタ基板とも称することができる。また、第2基板104には薄膜トランジスタが設けられていることから、薄膜トランジスタ基板と称することができる。第1基板102と第2基板104との間には、通常、2つの基板102、104の間の間隔を規定するためのスペーサ（図示しない）が設けられている。

#### 【0025】

50

図1を参照されたい。画素電極120は、隣接する2本のゲート線106と隣接する2本のデータ線108で画定された画素領域内に設けられている。本実施形態では、第1調整手段は、例えば第1基板に設けられており、互いに平行に伸びている複数の線状突起130によって構成されている。一方、第2調整手段は、例えば画素電極120に設けられており、互いに平行に伸びている複数のスリット140によって構成されている。線状突起130およびスリット140は、互いに略平行であって、交互に配列されている。

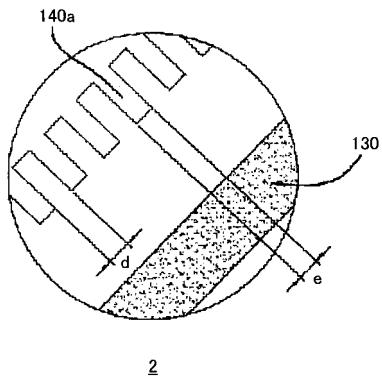

各々のスリット140には鋸歯状に配列されている複数の第2スリット140aが設けられている。隣接する2つの線状突起130とスリット140との間隔をcとし、第2スリット140aの最小深さをaとし、最小深さaを有する第2スリット140aと線状突起130との間の距離をbとすると、間隔cは最小深さaに距離bを加えたものに等しい。

#### 【0026】

スリット140に第2スリット140aが設けられていない液晶表示装置に従来の駆動方法を採用した場合、駆動電圧の瞬間的で過大な変化(バイアス)によって、隣接する線状突起130とスリット140との間の略中間に位置する液晶分子が異常な方向に配向するという事象が生じやすい。そのことから、液晶分子の異常配向という問題を抑制するためには、線状突起130とスリット140との間隔cを25μm未満に設定する必要がある。従来の液晶表示装置では、線状突起130とスリット140との間隔cが25μm以上となると、画素の応答時間が長くなってしまったり、表示画面に残像が生じるという問題を招いたりしてしまう。

#### 【0027】

本願出願人が2004年8月20日に出願した台湾特許出願第93123879号明細書に記載されている駆動方法を用いた場合、駆動電圧を段階的に上昇させることによって、画素の駆動電圧が閾値電圧(初期電圧+閾値電圧)の制限を超えて、高い目標電圧へと到達させることが可能となる。詳しくは、第1の時点t1のとき、閾値電圧未満の第1のバイアス電圧を供給し、初期電圧に第1の電圧を加えた中間電圧まで上昇させる。続いて、第2の時点t2のとき、第2の電圧を供給し、駆動電圧をさらに中間電圧から目標電圧まで上昇させる。この駆動方法によると、閾値電圧の限界を超えて駆動電圧を印加することが可能となり、液晶分子が異常な方向に配向するという問題を解決することができる。それにより、線状突起130とスリット140との間隔cが25μm未満に制限されることがなく、その間隔を25μm以上に設計することが可能となる。

#### 【0028】

線状突起130とスリット140との間隔cが25μm以上に設定できることから、1つの画素領域に存在する線状突起130やスリット140の数を減らすことができ、液晶表示装置の開口率を効果的に高め、輝度を顕著に向上することが可能となる。

#### 【0029】

スリット140に第2スリット140aが設けられている液晶表示装置において従来の駆動方法を用いる場合、第2スリット140aによって応答時間が改善されていることから、線状突起130とスリット140との間隔cは通常30μm未満に設計されている。一方、本願出願人の研究によって、駆動電圧を段階的に上昇させる前記の駆動方法を採用した場合、線状突起130と第2スリット140aが設けられているスリット140との間隔cを30μm以上に設計しても、液晶の異常配向という問題の発生が抑制されることが確認された。

スリット140に第2スリット140aを設けた場合、線状突起130とスリット140との間隔cを最大50μmに設計しても、液晶の異常配向という問題の発生を抑制することが可能となる。

#### 【0030】

本願出願人は、スリット140の第2スリット140aの間隔dとその幅e(図2を参考のこと)と、透過率との関係を研究し、表1に示す結果を得ている。ここで、線状突起130とスリット140との間隔cは35μmに設定されており、第2スリット140a

10

20

30

40

50

の最小深さ  $a$  は  $14 \mu\text{m}$  に設定されている。

表 1 に示すように、第 2 スリット  $140a$  は、その間隔  $d +$  幅  $e = 7 \sim 9 \mu\text{m}$  に設計するのが好ましく、それにより良好な透過率を得ることが可能となる。

### 【0031】

【表 1】

| $d (\mu\text{m})$ | $e (\mu\text{m})$ | 透過率 | $d / (d + e)$ | $(d + e)$ |

|-------------------|-------------------|-----|---------------|-----------|

| 4.5               | 2.5               | ◎   | 64.3%         | 7.0       |

| 4                 | 3                 | ◎   | 57.1%         | 7.0       |

| 3.75              | 3.25              | ◎   | 53.6%         | 7.0       |

| 4                 | 3.5               | ○   | 53.3%         | 7.5       |

| 4                 | 4                 | ○   | 50.0%         | 8.0       |

| 4.5               | 4                 | ○   | 52.9%         | 8.5       |

| 5                 | 4                 | ○   | 55.6%         | 9.0       |

◎：最良 ○：良好

10

20

### 【0032】

本願出願人は、スリット  $140$  の第 2 スリット  $140a$  の間隔  $d$  とその幅  $e$  と、従来の駆動方法で得られる応答時間との間の関係を研究し、表 2 に示す結果を得ている。ここで、線状突起  $130$  とスリット  $140$  との間隔  $c$  は  $35 \mu\text{m}$  に設定されており、第 2 スリット  $140a$  の最小深さ  $a$  は  $14 \mu\text{m}$  に設定されている。

表 2 に示すように、第 2 スリット  $140a$  の間隔  $d$  は  $4.5 \mu\text{m}$  以下に設計するのが好ましく、第 2 スリット  $140a$  の幅  $e$  は  $3 \mu\text{m}$  以下に設計するのが好ましい。それにより、応答時間を有意に改善することができる。

上記した透過率と応答時間を併せて考慮すると、第 2 スリット  $140a$  は、間隔  $d +$  幅  $e = 7 \sim 8.5 \mu\text{m}$  に設計するのが好ましい。

### 【0033】

【表 2】

| $d (\mu\text{m})$ | $e (\mu\text{m})$ | 応答時間 |

|-------------------|-------------------|------|

| 4.5               | 2.5               | ○    |

| 4                 | 3                 | ◎    |

| 3.75              | 3.25              | ◎    |

| 4                 | 3.5               | ◎    |

| 4                 | 4                 | ◎    |

| 4.5               | 4                 | ◎    |

| 5                 | 4                 | △    |

◎：最良 ○：良好 △：劣る

40

50

## 【0034】

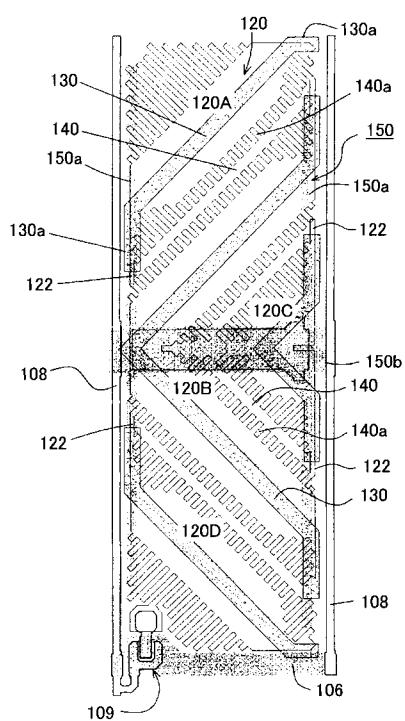

図3は、本実施形態のマルチドメイン垂直配向型の液晶表示装置の画素領域の変形例を示している。図3に示すように、この変形例の液晶表示装置では、各々の画素領域に「H」字形状のキャパシタ電極150が設けられている。キャパシタ電極150は、中央部150bと、中央部150bを介して互いに接続されている2つのサイド部150aを備えている。図3に示すように、キャパシタ電極150の2つのサイド部150aは、画素領域内においてデータ線108の近傍位置に設けられている。従来の液晶表示装置では、通常、キャパシタ電極は中央部150bのみを備えるように設計されている。それに対して、本変形例のキャパシタ電極150では、2つのサイド部150aが付加されており、サイド部150aと画素電極120とが対向する箇所で追加的なキャパシタが構成されている。キャパシタ電極150は、通常、ゲート線106やゲート電極とともに、ゲート金属層のパターンニングによって形成される。そのことから図3では、キャパシタ電極150やゲート線106を網掛け表示し、識別しやすくしている。ゲート金属層は、通常、例えばアルミニウム(aluminum)、クロム(chromium)、タンタル(tantalum)モリブデン(molybdenum)等の光を透過しない導電性金属で形成される。それにより、キャパシタ電極150の2つのサイド部150aは、光漏れを抑制する補助的な遮光層としても機能する。

## 【0035】

図1に示すように、本実施形態の液晶表示装置では、第1基板に設ける各線状突起130dには、画素電極120の縁部と対向する位置に、複数の分岐部130aが設けられている。液晶分子の長軸は、分岐部130aとスリット140の垂直方向に沿って配向することから、分岐部130aとスリット140とがなす角度が45度以下になっていると、分岐部130aとスリット140との境目近傍における液晶分子の長軸の配向方向の差を、最大でも45度となるまで大幅に低下させることができる。それにより、スリット140と画素電極120の縁部との境目近傍の領域において液晶分子が異常に配向するのを効果的に抑制することができる。しかしながら、線状突起130と画素電極120は、それぞれ異なる基板102、104上に形成される。そのことから、基板102、104同士の位置合わせの誤差により、分岐部130aが画素電極120の縁部に正しく対向しないことがしばしば起こる。この場合、液晶分子の異常な配向によって暗く表示される領域が、スリット140と画素電極の縁部の境目近傍に発生してしまう。

## 【0036】

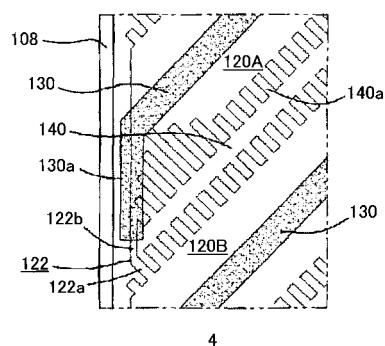

図1および図4に示すように、画素電極120は、複数のスリット140によって、4つの部分電極120Aと、120Bと、120Cと、120Dとに分割されている。隣接する2つの部分電極は、接続部122によって互いに接続されている。図4に示すように、各接続部122は、第1の部分122aと第2の部分122bを有している。第1の部分122aが伸びている方向は、線状突起130が伸びている方向に垂直となっている。第2の部分122bが伸びている方向は、データ線108に平行になっている。本実施形態では、各接続部122の第2の部分122bが、線状突起130の分岐部130aと完全に重なっていない。即ち、第2の部分122bと分岐部130aは、基板平面に対して同じ領域に投影されない。

本願出願人の研究により、第2の部分122bが分岐部130aと重なっていない領域に、表示が暗くなるという不具合が起こることが見出された。そして、この暗く表示される領域では、駆動電圧が印加されたときに、液晶分子の配向の変化が遅いことが見出された。その結果、コントラストや応答時間が低下し、表示品質が悪化してしまう。さらに、2枚の基板102、104の位置合わせに誤差が生じると、第2の部分122bと分岐部130aとの間に位置ズレが生じてしまい、その位置ズレが生じた領域も暗く表示されるといふ不具合が発生してしまう。

## 【0037】

図5は、本実施形態のマルチドメイン垂直配向型液晶表示装置の画素領域の他の変形例

10

20

30

40

50

を示している。この変形例では、各接続部 122 の第 2 の部分 122b が、線状突起 130 の分岐部 130a に完全に重なっている。この変形例の設計によると、暗く表示される領域を顕著に縮小することが可能となる。さらに、2 枚の基板 102、104 を位置合せする際に、図 5 における上下方向に位置ズレが生じた場合でも、この設計では暗く表示される領域の発生を効果的に抑制することができる。

#### 【0038】

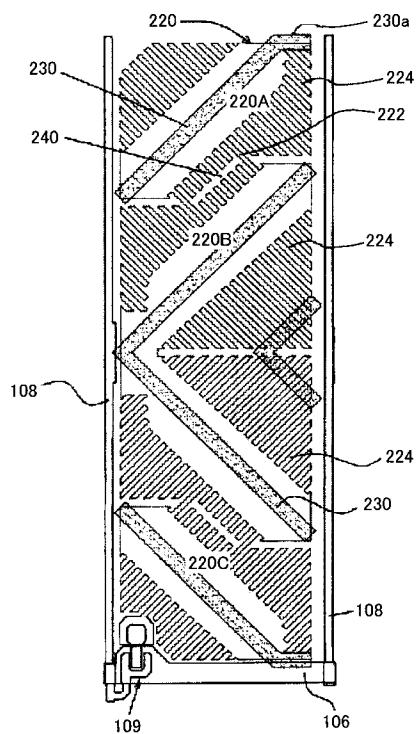

図 6 は、本実施形態のマルチドメイン垂直配向型液晶表示装置の画素領域の他の変形例を示している。この変形例では、第 1 調整手段は、第 1 基板 102 に設けられており、アレイ状に配列されている複数の線状突起 230 によって構成されている。また、第 2 調整手段は、画素電極 220 に設けられており、アレイ状に配列されている複数のスリット 240 によって構成されている。線状突起 230 とスリット 240 は、実質的に交互に配列されている。また、隣接する 2 つの線状突起 230 に介在しているスリット 240 は、「之」字状に屈曲している。図 6 に示すように、画素電極 220 は、スリット 240 によって、3 つの部分電極 220A と、220B と、220C とに分割されている。隣接する 2 つの部分電極は、少なくとも 1 つの接続部 222 を介して接続されている。部分電極 220A と、220B と、220C のそれぞれは、複数の突出部 224 を有している。突出部 224 が延びる方向は、線状突起 230 が延びる方向に垂直となっている。留意すべきは、線状突起 230 には、画素電極やデータ線の縁部に対向する位置に、分岐部も設けられていないことである。それにより、基板 102、104 との位置合せの際に誤差が生じた場合でも、暗く表示される領域の発生を顕著に低減することが可能となる。

#### 【0039】

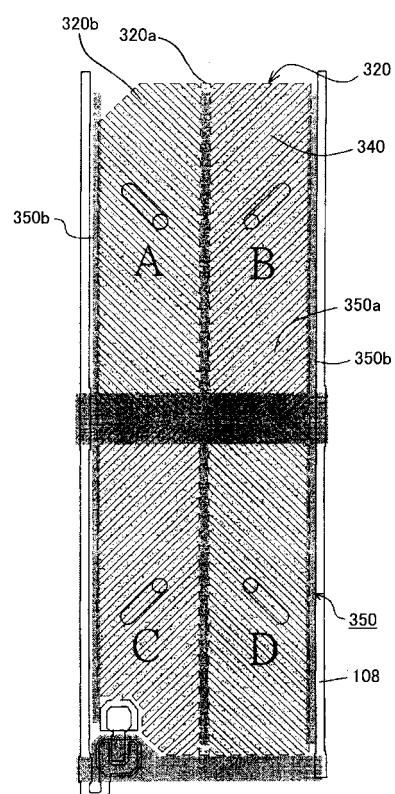

図 7 は、本実施形態のマルチドメイン垂直配向型液晶表示装置の画素領域のまた別の変形例を示している。図 1～図 6 に例示する画素領域と比べて、図 7 に示す変形例では、第 1 調整手段が設けられておらず、画素電極 320 にアレイ状に配列されている複数のスリット 340 によって構成された第 2 調整手段のみが設けられている。図 7 に示すように、画素電極 320 は、十字形状の本体 320a と、十字形状の本体 320a から延出している複数の突出部 320b を有している。画素領域は、4 つの領域 A、B、C、D に分割されており、これらの分割領域 A、B、C、D 毎に液晶分子の配向方向が異なるようになっている。それにより、線状突起等による第 1 調整手段を設けることなく、液晶表示装置の視野角特性が顕著に改善されている。

#### 【0040】

図 7 に示すように、各画素領域には、十字形状の中央部 350a と、2 つのサイド部 350b を備えたキャパシタ電極 350 が設けられている。キャパシタ電極 350 の十字形状の中央部 350a は、画素電極 320 の十字形状の本体 320a に対向する位置に形成されている。2 つのサイド部 350b は、十字形状の中央部 350a を介して互いに接続されている。2 つのサイド部 350b のそれぞれは、画素領域内のデータ線 108 の近傍に設けられている。

従来の液晶表示装置のキャパシタ電極は、通常、十字形状の中央部 350a の幅方向（図 7 中の左右方向）部分のみを備えるように設計されている。それに対して、本変形例のキャパシタ電極 350 では、中央部 350a の長手方向（図 7 中の上下方向）部分と 2 つのサイド部 350b が付加されており、追加的なキャパシタが構成されている。キャパシタ電極 350 は、通常、ゲート線 106 やゲート電極とともに、ゲート金属層のパターンニングによって形成される。そのことから図 7 では、キャパシタ電極 350 やゲート線 106 を網掛け表示し、識別しやすくしている。ゲート金属層は、通常、アルミニウム、クロム、タンタル、モリブデンなどの光を透過しない導電性金属で形成することができる。従って、キャパシタ電極 350 の中央部 350a の長手方向部分や 2 つのサイド部 350b は、光漏れを抑制する補助的な遮光層として機能する。

#### 【0041】

図 1～図 6 に示す液晶表示装置では、第 1 調整手段が、第 1 基板に設けられており、アレイ状に配列されている複数の線状突起によって構成されている。また、第 2 調整手段は

10

20

30

40

50

、第2基板の画素電極に設けられており、アレイ状に配列されている複数のスリットによって構成されている。しかしながら、第1調整手段や第2調整手段は、この形態に限定されない。

例えば、第1調整手段を、第1基板の共通電極に設けられているスリットや、それに第2基板上に設けられている線状突起を組み合わせて構成することもできる。また、第2調整手段を、第2基板に設けられている線状突起や、それに第1基板の共通電極に設けられているスリットを組み合わせて構成することもできる。あるいは、第1調整手段と第2調整手段の両者を、複数の線状突起と複数のスリットのいずれかによって構成することもできる。

#### 【0042】

10

次に、調整手段を構成する線状突起を形成するための製造工程を以下に説明する。線状突起をカラーフィルタ基板に形成する場合、先ず、カラーフィルタ基板の表面にフォトレジストを塗布し、所定のパターンを転写する（図1～図7に示す線状突起の配置パターンを参照）。次いで現像することによって、線状突起を形成することができる。この製造工程は、従来の技術によって容易に実施することができる。また、スリットは従来の画素電極を形成する工程を用いて、画素電極の形成時に形成することができる。

#### 【0043】

以上、本発明の具体例を詳細に説明したが、これらは例示にすぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

20

本明細書または図面に説明した技術要素は、単独であるいは各種の組み合わせによって技術的有用性を發揮するものであり、出願時請求項記載の組み合わせに限定されるものではない。本明細書または図面に例示した技術は複数の目的を同時に達成するものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

#### 【図面の簡単な説明】

#### 【0044】

【図1】マルチドメイン垂直配向型の液晶表示装置の画素領域の一例を示す図。

【図2】スリットの第2スリットを拡大して示す図。

【図3】マルチドメイン垂直配向型の液晶表示装置の画素領域の一例を示す図。

【図4】線状突起の分岐部近傍の一例を拡大して示す図。

30

【図5】線状突起の分岐部近傍の一例を拡大して示す図。

【図6】マルチドメイン垂直配向型の液晶表示装置の画素領域の一例を示す図。

【図7】マルチドメイン垂直配向型の液晶表示装置の画素領域の一例を示す図。

【図8】液晶表示装置の構成を模式的に示す図。

【図9A】従来の線状突起とスリットの配置パターンを示す図。

【図9B】図9A中のA-A線断面図。

【図10A】電圧を印加したときの液晶の配向方向を示す図（電圧5ボルト）。

【図10B】電圧を印加したときの液晶の配向方向を示す図（電圧5.5ボルト）。

【図10C】電圧を印加したときの液晶の配向方向を示す図（電圧5.75ボルト）。

【図10D】電圧を印加したときの液晶の配向方向を示す図（電圧6ボルト）。

40

【図10E】電圧を印加したときの液晶の配向方向を示す図（電圧6.5ボルト）。

【図11】図10Eに示す液晶分子を光学顕微鏡で観察した結果を示す図。

#### 【符号の説明】

#### 【0045】

102…基板

102a…カラーフィルタ

102b…共通電極

104…基板

106…ゲート線

108…データ線

50

|      |                 |                        |

|------|-----------------|------------------------|

| 109  | ・・薄膜トランジスタ      |                        |

| 120  | 、220、320        | ・・画素電極                 |

| 120a | 、120b           | ・・異常領域                 |

| 130  | 、230            | ・・線状突起                 |

| 130a | ・・              | 分岐部                    |

| 140  | 、240、340        | ・・スリット                 |

| 140a | ・・              | 第2スリット                 |

| 150  | 、350            | ・・キャパシタ電極              |

| 150a | ・・              | キャパシタ電極のサイド部           |

| 150b | ・・              | キャパシタ電極の中央部            |

| 120A | 、120B、120C、120D | ・・部分電極                 |

| 122  | ・・              | 接続部                    |

| 122a | ・・              | 接続部の第1の部分              |

| 122b | ・・              | 接続部の第2の部分              |

| 220A | 、220B、220C      | 、部分電極                  |

| 224  | ・・              | 突出部                    |

| 320a | ・・              | 画素電極の十字形状の本体           |

| 320b | ・・              | 画素電極の突出部               |

| 350a | ・・              | キャパシタ電極の中央部            |

| 350b | ・・              | キャパシタ電極のサイド部           |

| 400  | ・・              | 画素領域                   |

| 402  | ・・              | ゲート線                   |

| 404  | ・・              | データ線                   |

| 406  | ・・              | 薄膜トランジスタ               |

| 408  | ・・              | 画素電極                   |

| 410  | ・・              | 線状突起                   |

| 412  | ・・              | スリット                   |

| 414  | ・・              | カラーフィルタ基板              |

| 416  | ・・              | 薄膜トランジスタ基板             |

| 420a | 、420b           | ・・スリットと線状突起の略中間に位置する領域 |

| a    | ・・              | スリットの第2スリットの最小深さ       |

| b    | ・・              | 線状突起とスリットの第2スリットとの間の距離 |

| c    | ・・              | スリットと線状突起との間隔          |

| d    | ・・              | スリットの第2スリット同士の間隔       |

| e    | ・・              | スリットの第2スリットの幅          |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図 9 B】

【図 10 A】

【図 10 B】

【図 10 C】

【図 10 D】

【図 11】

【図 10 E】

---

フロントページの続き

(72)発明者 チエ - ミン , ス

台湾 744 タイナン サイエンス - ベースト インダストリアル パーク タイナン カウン

ティー チー - イエ - ロード ナンバー1 チー メイ オプトエレクトロニクス コーポレー

ション内

(72)発明者 ミン - フエン , シエ

台湾 744 タイナン サイエンス - ベースト インダストリアル パーク タイナン カウン

ティー チー - イエ - ロード ナンバー1 チー メイ オプトエレクトロニクス コーポレー

ション内

(72)発明者 チン - ユン , シエ

台湾 744 タイナン サイエンス - ベースト インダストリアル パーク タイナン カウン

ティー チー - イエ - ロード ナンバー1 チー メイ オプトエレクトロニクス コーポレー

ション内

(72)発明者 チエン - ホン , チエン

台湾 744 タイナン サイエンス - ベースト インダストリアル パーク タイナン カウン

ティー チー - イエ - ロード ナンバー1 チー メイ オプトエレクトロニクス コーポレー

ション内

審査官 磯野 光司

(56)参考文献 特開2003-255305 (JP, A)

特開2004-093846 (JP, A)

特開2002-229038 (JP, A)

特開2000-267102 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1337

G 02 F 1 / 1343