(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4357844号

(P4357844)

(45) 発行日 平成21年11月4日(2009.11.4)

(24) 登録日 平成21年8月14日(2009.8.14)

(51) Int.Cl.

F 1

|               |           |              |         |

|---------------|-----------|--------------|---------|

| HO 1 L 27/14  | (2006.01) | HO 1 L 27/14 | K       |

| HO 1 L 27/146 | (2006.01) | HO 1 L 27/14 | C       |

| HO 1 L 31/09  | (2006.01) | HO 1 L 31/00 | A       |

| HO 1 L 29/786 | (2006.01) | HO 1 L 29/78 | 6 1 2 C |

| HO 4 N 5/335  | (2006.01) | HO 4 N 5/335 | Z       |

請求項の数 5 (全 14 頁) 最終頁に続く

(21) 出願番号

特願2003-5051 (P2003-5051)

(22) 出願日

平成15年1月10日 (2003.1.10)

(65) 公開番号

特開2004-221207 (P2004-221207A)

(43) 公開日

平成16年8月5日 (2004.8.5)

審査請求日

平成18年1月10日 (2006.1.10)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(73) 特許権者 000001993

株式会社島津製作所

京都府京都市中京区西ノ京桑原町1番地

(74) 代理人 110000338

特許業務法人原謙三国際特許事務所

(74) 代理人 100080034

弁理士 原 謙三

(74) 代理人 100113701

弁理士 木島 隆一

(74) 代理人 100116241

弁理士 金子 一郎

最終頁に続く

(54) 【発明の名称】 電磁波検出器

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、信号線、走査線が格子状に配設され、単位格子毎にスイッチング素子と画素電極が形成されたアクティブマトリクスと、

上記アクティブマトリクス基板の上面に形成された半導体膜と、

上記半導体膜の上面に形成されたバイアス電極とを備えた電磁波検出器において、

上記信号線及び/又は走査線の上記信号線と上記走査線とが重なっていない領域に、開口部が形成されていると共に、

上記アクティブマトリクス基板の上記半導体膜が形成された面とは反対の面側に、上記アクティブマトリクス基板を照射し得る光源を備えていることを特徴とする電磁波検出器

。

## 【請求項 2】

上記開口部は、上記信号線及び/又は上記走査線の延伸方向に沿って設けられたスリットであることを特徴とする請求項1に記載の電磁波検出器。

## 【請求項 3】

上記信号線及び/又は上記走査線は、上記信号線と上記走査線との交差部において線幅が細くなるように形成されていることを特徴とする請求項1に記載の電磁波検出器。

## 【請求項 4】

上記信号線及び/又は走査線と上記画素電極との間には、層間絶縁膜が介在していることを特徴とする請求項1に記載の電磁波検出器。

**【請求項 5】**

上記アクティブマトリクス基板と上記光源との間に、上記光源からの照射光を拡散光に変換する拡散手段を備えていることを特徴とする請求項 1 に記載の電磁波検出器。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、X線等の放射線、可視光、赤外線等の電磁波による画像を検出できる電磁波検出器に関し、特にアクティブマトリクス基板を読み出し回路基板に用いた電磁波検出器に関する。

**【0002】**

10

**【従来の技術】**

従来、電磁波検出器の一種として、例えば、X線等の電磁波を感知して電荷（電子 - 正孔対）を発生する半導体膜、すなわち電磁波導電性（光導電性とも呼ぶ）を有する半導体膜と、該半導体膜中で生成された電荷を収集する電荷収集電極とを行方向および列方向の二次元状に配置するとともに、画素毎にスイッチング素子を設けて、各行毎にスイッチング素子を順次オンにして各列毎に上記電荷を読み出す二次元の電磁波検出器が知られている。

**【0003】**

上記二次元の電磁波検出器は、例えば、下記の非特許文献 1 等にその構造や原理が解説されている。上記非特許文献 1 に記載されている従来の電磁波検出器の構成および原理について以下に簡単に説明する。

20

**【0004】**

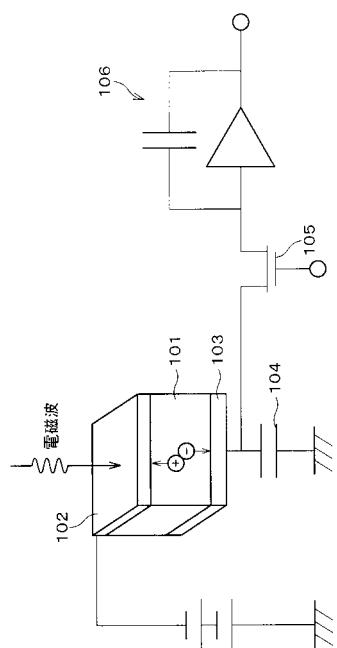

図 9 は、電磁波検出器の検出原理を示す断面図である。電磁波検出器は、例えば a - Se に代表される電磁波導電性を示す半導体膜 101 を備え、該半導体膜 101 の上層にバイアス電極 102 が、下層に電荷収集電極 103 が形成されている。電荷収集電極 103 は、蓄積容量 (Cs) 104 に接続されており、蓄積容量 104 は FET (TFT) などのスイッチング素子 105 を介して電荷検出アンプ 106 に接続されている。

**【0005】**

このような電磁波検出器に X 線等の電磁波が入射すると、半導体膜 101 内で電荷（電子 - 正孔対）が発生する。この時、バイアス電極 102 と電荷収集電極 103 との間に印加されるバイアス電圧により、半導体膜 101 で発生した電子は + 電極側に、正孔は - 電極側に移動し、その結果、蓄積容量 104 に電荷が蓄積される仕組みになっている。蓄積容量 104 に蓄積された電荷は、スイッチング素子 105 をオンにすることで電荷検出アンプ 106 に取り出される。こうして、電荷検出アンプ 106 により検出された電荷量から、半導体膜 101 に入射した電磁波の強度を検知することができる。

30

**【0006】**

また、このような電磁波検出器の構成要素（電荷収集電極、蓄積容量、スイッチング素子）を二次元状にマトリクス配置し、線順次に電荷を読み出していくことで、検出対象である電磁波の二次元情報を得ることが可能となる。ここで、二次元のマトリクスアレイとしては、薄膜トランジスタ (TFT) をスイッチング素子として使用したアクティブマトリクスアレイを用いることができる。

40

**【0007】**

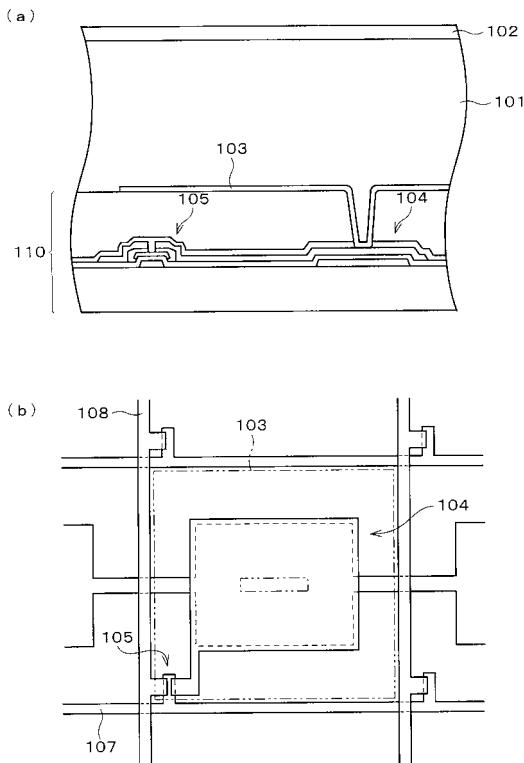

図 10 (a) は、スイッチング素子 105、蓄積容量 104、電荷収集電極 103、およびそれらを駆動するための配線（走査線（ゲート配線）107、信号線（ソース配線）108 等：図 7 (b) 参照）を備えたアクティブマトリクスアレイ 110 と、その上に設けられた半導体膜 101 と、さらにその上に設けられたバイアス電極 102 によって構成される電磁波検出器の断面構造（1 画素分）を示すものである。図 10 (b) は、図 10 (a) に示すアクティブマトリクスアレイを上側から見た平面図であり、1 画素当たりのレイアウトを示すものである。

**【0008】**

50

ところで、上述の電磁波検出器において、電荷収集電極 103 はその上の半導体膜 101 にて発生した電荷を収集する役割を果たすが、隣接する電荷収集電極 103 同士の間隙には電荷がトラップされやすいことが知られている。

#### 【0009】

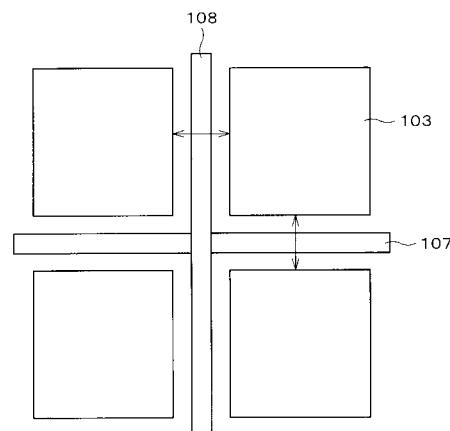

ここで、電荷収集電極同士の間隙とは、図 11 に示される模式図において矢印の部分を指す。また、電荷トラップ発生のメカニズムについては、例えば、非特許文献 2 で説明されている。この電荷トラップは、アクティブマトリクス基板 110 と半導体膜 101 の界面や、半導体膜 101 内の該界面に近接した部分で生じやすいと考えられる。電荷収集電極 103 間に過剰に電荷がトラップされると、画像を撮像する際に、残像や感度低下などの悪影響を与える。

10

#### 【0010】

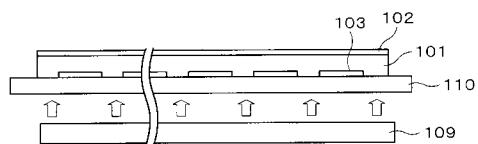

このようなトラップ電荷に対しては、該トラップ電荷を発生する半導体膜 101 の領域に光を照射してトラップ電荷を解消する方法が、例えば特許文献 1 に開示されている。このため、例えば図 12 に示すように、アクティブマトリクス基板 110 の裏面に光源 109 を設置し、アクティブマトリクス基板 110 を介して半導体膜 101 に光を照射することで、上述のトラップ電荷を減少させることができる。

#### 【0011】

##### 【非特許文献 1】

S. O. Kasap, J. A. Rowlands, "Direct-Conversion Flat-Panel X-Ray Image Sensors for Digital Radiography", Proceedings of the IEEE, 米国, April, 2002, Vol. 90, No. 4, pp.591-604」

20

#### 【0012】

##### 【非特許文献 2】

W. Zhao, G. DeCrescenzo, J. A. Rowlands, "Investigation of lag and ghosting in a morphous selenium flat-panel x-ray detectors", Proceedings of SPIE, 米国, May, 2002, Vol. 4682, pp. 9-20」

#### 【0013】

##### 【特許文献 1】

特開平 9 - 9153 号公報 (公開日 1997 年 1 月 10 日)

#### 【0014】

30

##### 【発明が解決しようとする課題】

上記従来の構成では、隣接する電荷収集電極 103 の間には、図 11 に示すように、金属膜によって形成された信号線 108 や走査線 107 が存在する。尚、電磁波検出器において、上述のように走査線および信号線の各配線と電荷収集電極とが平面的に重畳しない設計とすることは、各配線のそれぞれにおける時定数 (配線抵抗値 × 配線容量) をできるだけ小さくし、高い周波数で精度良く電気信号を伝送する能力を得るために有用な構成である。

#### 【0015】

ところが、隣接する電荷収集電極 103 の間に金属膜によって形成された配線が存在する構成では、アクティブマトリクス基板 110 の裏面から半導体膜 101 に光を照射し、電荷トラップを解消する方法を採用する場合に以下のようないわゆる問題が生じる。すなわち、これらの配線が配設された領域については、配線によって照射光が遮られるため、電荷がトラップされている領域に効率良く光を照射することができず、電荷トラップの発生を十分に抑制できないといった問題がある。

40

#### 【0016】

もちろん、信号線 108 や走査線 107 の線幅を狭くすることで、配線によって遮光される面積を小さくする方法も考えられるが、これらの配線はそこを流れる電気信号の遅延を抑え、かつ S/N の優れた画像信号を検出する必要があることから配線抵抗の低減が求められ、線幅を細くするにも限界があった。

#### 【0017】

50

本発明は、上記の問題点を解決するためになされたもので、その目的は、電荷収集電極の隙間に効率良く光を照射してトラップ電荷を解消することのできるデバイス構造を有したアクティブマトリクス基板および電磁波検出器を提供することにある。

【0018】

【課題を解決するための手段】

本発明のアクティブマトリクス基板は、上記の課題を解決するために、基板上に、信号線、走査線が格子状に配設され、単位格子毎にスイッチング素子と画素電極が形成されたアクティブマトリクス基板において、上記信号線及び／又は走査線に、開口部が形成されていることを特徴としている。

【0019】

上記アクティブマトリクス基板を用いた電磁波検出器では、該アクティブマトリクス基板上に半導体膜およびバイアス電極が形成される。このような電磁波検出器において、アクティブマトリクス基板における画素電極はその上の半導体膜にて発生した電荷を収集する役割を果たすが、隣接する画素電極同士の間隙には電荷がトラップされやすい。

【0020】

そして、上記アクティブマトリクス基板を用いた電磁波検出器では、このトラップ電荷の発生を解消するために、アクティブマトリクス基板の裏面に光源を設置し、該アクティブマトリクス基板を介して半導体膜に光を照射する構成を取ることが前提とされる。

【0021】

このような前提のもと、上記の構成によれば、光源から発せられた光は、信号線や走査線の配線に設けられた開口部を通過する。そして、上記開口部を通過する光の回折により、配線に対して光の照射側と反対側にも光を回り込ませることができる。

【0022】

これにより、配線に開口部を持たない従来構成に比べ、実質的な配線幅が同じであっても、配線の裏側にある半導体膜に効率よく光を照射することができ、配線抵抗を上げることなく、電荷がトラップされている場所に効率良く光を照射することができる。

【0023】

また、上記アクティブマトリクス基板においては、上記開口部は、上記信号線及び／又は上記走査線の延伸方向に沿って設けられたスリットである構成とすることができます。

【0024】

上記の構成によれば、格子状に形成された画素電極同士の間隙に効率良く光を照射することができる。

【0025】

また、上記アクティブマトリクス基板においては、上記信号線及び／又は上記走査線は、上記信号線と上記走査線との交差部において線幅が細くなるように形成されている構成とすることができます。

【0026】

上記の構成によれば、信号線と走査線との交差部の面積が小さくなり、信号線と走査線との配線容量（主に交差部に発生する寄生容量）を低減することができる。これにより、配線の時定数を小さくすることができ、S/Nの優れた電磁波検出器を実現できる。

【0027】

また、上記アクティブマトリクス基板においては、上記信号線及び／又は走査線と上記画素電極との間には、層間絶縁膜が介在している構成とすることができます。

【0028】

上記の構成によれば、光源から発せられた光は、配線の内部の開口部を通過した後、層間絶縁膜の内部を通過する間に、回折によって信号線や走査線の裏側により光が回り込み易くなるといった効果をもたらす。これにより、電荷がトラップされている場所にさらに効率良く光を照射することができる。

【0029】

また、本発明の電磁波検出器は、上記の課題を解決するために、上記アクティブマトリク

10

20

30

40

50

ス基板と、上記アクティブマトリクス基板の上面に形成された半導体膜と、上記半導体膜の上面に形成されたバイアス電極とを備えており、上記アクティブマトリクス基板の上記半導体膜が形成された面とは反対の面側に、上記アクティブマトリクス基板を照射し得る光源を備えている構成である。

【0030】

上記の構成によれば、アクティブマトリクス基板において配線に開口部を持たない従来構成に比べ、実質的な配線幅が同じであっても、配線の裏側にある半導体膜に効率よく光を照射することができ、配線抵抗を上げることなく、電荷がトラップされている場所に効率良く光を照射することができる。

【0031】

また、上記電磁波検出器においては、上記アクティブマトリクス基板と上記光源との間に、上記光源からの照射光を拡散光に変換する拡散手段を備えている構成とすることができる。

【0032】

上記の構成によれば、光源から発せられた光がアクティブマトリクス基板への入射前に拡散手段によって拡散され、斜め方向への入射光が生成される。これにより、信号線や走査線の上部に光が回り込み易いといった効果をもたらし、半導体膜において電荷がトラップされている場所にさらに効率良く光を照射することができる。

【0033】

【発明の実施の形態】

本発明の実施の一形態について図1ないし図8に基づいて説明すれば、以下の通りである。尚、以下の説明においては、検出される画像の1画素分に相当する電磁波検出素子を複数備えており、それが2次元に配列されたものを電磁波検出器とする。

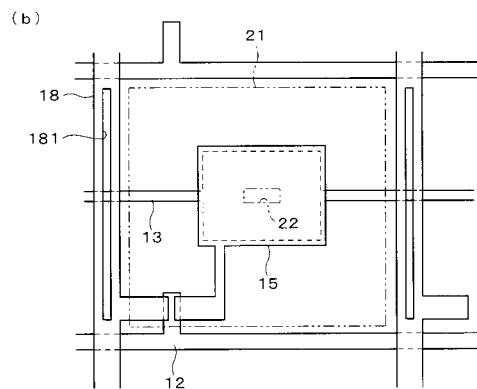

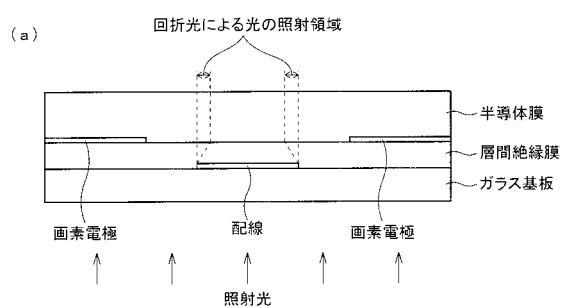

【0034】

図1(a)は、上記電磁波検出器の1画素単位の構造を示す断面図、図1(b)はその平面図である。図1(a)および(b)に示す1画素のサイズは、0.1mm×0.1mm～0.3mm×0.3mm程度であり、電磁波検出器全体としてはこの画素(電磁波検出器)がXYマトリクス状に500×500～3000×3000画素程度配列されたものが一般的である。サイズとしては、X線の胸部撮影を想定すると、17"×17"程度のものが要求される。

【0035】

図1(a)および(b)に示すように、上記電磁波検出器は、アクティブマトリクス基板1上に、電磁波導電性を有する半導体膜2、および図示しない電源に接続されたバイアス電極(共通電極)3が順次形成されている。半導体膜2は、X線などの電磁波が照射されることにより、内部に電荷(電子・正孔)を発生するものである。つまり、半導体膜2は電磁波導電性を有し、X線などの電磁波画像情報を電荷情報に変換するためのものである。

【0036】

また、半導体膜2は、例えば、セレンを主成分とする(50%以上の含有率を有する)非晶質のa-Se(アモルファスセレン)からなる。この他に、CdTe、CdZnTe、PbI<sub>2</sub>、HgI<sub>2</sub>、GaAs、Siなどを半導体膜2として使用することもできる。

【0037】

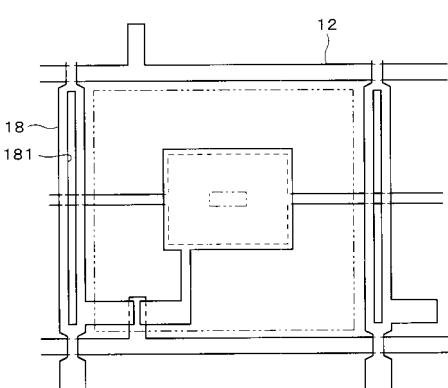

以下に、アクティブマトリクス基板1について詳しく説明する。アクティブマトリクス基板1は、ガラス基板11、走査線(ゲート電極)12、蓄積容量線(蓄積容量電極)13、ゲート絶縁膜14、接続電極15、チャネル層16、コンタクト層17、信号線(ソース電極)18、絶縁保護膜19、層間絶縁膜20、画素電極(電荷収集電極)21とを有している。アクティブマトリクス基板1では、ガラス基板11上に信号線18および走査線12が格子状に配設され、その単位格子毎にスイッチング素子であるTFT(Thin Film Transistor)4と画素電極21とが形成されている。

【0038】

10

20

30

40

50

また、アクティブマトリクス基板1においては、走査線12、ゲート絶縁膜14、信号線18、接続電極15、チャネル層16、およびコンタクト層17等によりTFT4が構成されており、蓄積容量線13、ゲート絶縁膜14、接続電極15等により蓄積容量(CS)5が構成されている。

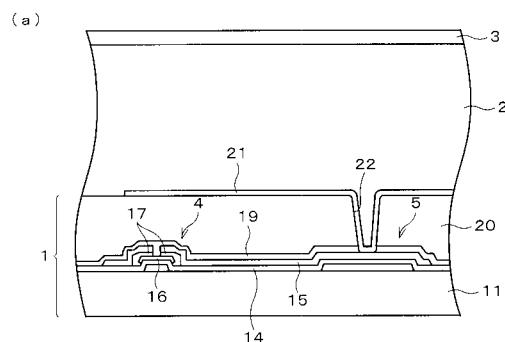

【0039】

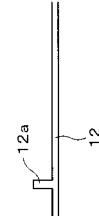

尚、ここでは、図2(a)~(c)に示すように、走査線12のうちTFT4を構成する部分をゲート電極12a、信号線18のうちTFT4を構成する部分をソース電極18a、蓄積容量線13のうち蓄積容量5を構成する部分を蓄積容量電極13aと呼ぶこととする。

【0040】

また、本実施の形態1では、ゲート電極12a、ソース電極18a、蓄積容量電極13aが、それぞれ走査線12、信号線18、蓄積容量線13の一部を兼用して構成される構成を例示しているが、ゲート電極12a、ソース電極18a、蓄積容量電極13aを、それぞれ走査線12、信号線18、蓄積容量線13とは別に構成しても構わない。

【0041】

ガラス基板11は支持基板であり、ガラス基板11としては、例えば、無アルカリガラス基板(例えば、コーニング社製#1737等)を用いることができる。走査線12および信号線18は、格子状に配列された電気配線(金属配線)であり、その各交点にはTFT4が形成されている。

【0042】

TFT4はスイッチング素子であり、そのソースおよびドレインのそれぞれは、信号線18および接続電極15に接続されている。つまり、信号線18は、信号線としての直線部分と、TFT4を構成するための延長部分(すなわち、ソース電極18a)とを備えており、接続電極15は、TFT4のドレイン電極を構成しながらTFT4と蓄積容量5とをつなぐように設けられている。

【0043】

ゲート絶縁膜14には、SiNxやSiO<sub>x</sub>等が使用可能である。ゲート絶縁膜14は、ゲート電極12aおよび蓄積容量電極13aを覆うように設けられており、ゲート電極12a上に位置する部位がTFT4におけるゲート絶縁膜として作用し、蓄積容量電極13a上に位置する部位は蓄積容量5における誘電体層として作用する。つまり、蓄積容量5は、ゲート電極2と同一層に形成された蓄積容量電極13aと接続電極15との重畳領域によって形成されている。尚、ゲート絶縁膜14としては、SiNxやSiO<sub>x</sub>に限らず、ゲート電極14aおよび蓄積容量電極13aを陽極酸化した陽極酸化膜を併用することもできる。

【0044】

また、チャネル層(i層)16はTFT4のチャネル部であり、ソース電極18aと接続電極15とを結ぶ電流の通路となる。コンタクト層(n<sup>+</sup>層)17は、チャネル層16とソース電極18aとのコンタクト、およびチャネル層16と接続電極15とのコンタクトを図る。

【0045】

絶縁保護膜19は、信号線18および接続電極15上、つまり、ガラス基板11上に、ほぼ全面(ほぼ全領域)にわたって形成されている。これにより、接続電極15とソース電極18aとを保護すると共に、これらの電極の電気的な絶縁分離を図っている。また、絶縁保護膜19は、その所定位置、つまり、接続電極15において蓄積容量5を介して蓄積容量電極13aと対向している部分上に位置する部位に、コンタクトホール22を有している。

【0046】

絶縁保護膜19の上方には、層間絶縁膜20が設けられている。層間絶縁膜20は1~5μmの厚みを有する透光性の樹脂からなり、TFT4の平坦化を図っている。層間絶縁膜20の上層、すなわちアクティブマトリクス基板1の最上層には、ITOやAlなどの導

10

20

30

40

50

電膜からなる画素電極 2 1 が設けられている。層間絶縁膜 2 0 においても、絶縁保護膜 1 9 と同一箇所にコンタクトホール 2 2 が貫通しており、画素電極 2 1 は該コンタクトホール 2 2 を介して接続電極 1 5 に接続されている。

【 0 0 4 7 】

さらに、画素電極 2 1 上には、半導体膜 2 とバイアス電極 3 とがアクティブマトリクス基板 1 の略全面を覆うように形成されている。尚、半導体膜 2 の上層および / 又は下層には、電荷ブロッキング層や緩衝層を設ける場合もあるが、本実施の形態 1 に係る電磁波検出器ではこれらの層を含めて半導体膜 2 と定義する。電荷ブロッキング層や緩衝層の例としては、 $A_s$  や  $T_e$  を含有した  $S_e$  層、ハロゲンやアルカリ金属等を微量ドープした  $S_e$  層、もしくは  $Sb_2S_3$ 、 $CeO_2$ 、 $CdS$  等の高抵抗半導体層等が挙げられる。

10

【 0 0 4 8 】

バイアス電極 3 と蓄積容量電極 1 3 a との間には、半導体膜 2 に対して電圧が印加できるように、図示しない電源が接続されている。これにより、蓄積容量 5 を介してバイアス電極 3 と画素電極 2 1 との間に電界を発生させることができる。このとき、半導体膜 2 と蓄積容量 5 とは、電気的に直列に接続された構造になっているので、バイアス電極 3 にバイアス電圧を印加した状態で、X 線等の電磁波の吸収によって半導体膜 2 内に電荷（電子 - 正孔対）が生成すると、生成した電子は + 電極側に、正孔は - 電極側に移動する。その結果、蓄積容量 5 に電荷が蓄積される。

【 0 0 4 9 】

電磁波検出器全体において画素電極 2 1 は 1 次元または 2 次元に複数配列されていると共に、該電磁波検出器は、画素電極 2 1 に個別に接続された蓄積容量 5 と蓄積容量 5 に個別に接続された TFT 4 とを複数備えている。これにより、1 次元または 2 次元の電磁波情報を一旦蓄積容量 5 に蓄積し、TFT 4 を順次走査していくことで、1 次元または 2 次元の電荷情報を簡単に読み出すことができる。尚、上記電荷情報を読み出すために、各信号線 1 8 の端部には電荷検出アンプが接続されている（図 9 参照）。

20

【 0 0 5 0 】

以上、本実施の形態に係る電磁波検出器の基本的な構造について説明してきたが、続いて上記電磁波検出器の特徴点について説明する。

【 0 0 5 1 】

本実施の形態に係る電磁波検出器では、特に、信号線 1 8 および走査線 1 2 の形状にその特徴を有するものである。例えば、上記電磁波検出器で用いる信号線 1 8 は、図 1 ( b ) に示すように、配線の略中央部に該配線の延設方向に沿った開口部 1 8 1 が設けられている。例えば、 $13 \mu m$  の線幅の信号線に対して、 $3 \mu m$  の幅を有する開口部 1 8 1 がスリット状に設けられている。この開口部 1 8 1 は、信号線 1 8 をパターニングする際に同時に形成されるもので、そこから光が透過できるようになっている。

30

【 0 0 5 2 】

さらに、上記電磁波検出器は、アクティブマトリクス基板 1 の裏面側（すなわち、アクティブマトリクス基板 1 に対する画素電極 2 1 の形成側と反対側）に光源（例えば LED (Light Emitting Diode) などから構成される平面光源）を備えている。これは、従来技術の記載でも述べたように、アクティブマトリクス基板 1 の裏面側から光を照射し、その光を半導体膜 2 に当てることで、画素電極 2 1 間の半導体膜 2 において発生するトラップ電荷を放出させ、電磁波検出器の特性を安定させるためである（Lag (残像) や感度低下といった問題を抑制する）。

40

【 0 0 5 3 】

ここで、従来の構成では、画素電極間の隙間に光を照射するにあたって、画素電極間に配設される配線によって光が遮られ、上記隙間の半導体膜に効率よく光を照射できないといった問題があった。これに対し、本実施の形態に係る電磁波検出器の構成では、図 1 ( b ) に示すように、信号線 1 8 にスリット状の開口部 1 8 1 が設けられているので、信号線 1 8 上の半導体膜 2 における電荷トラップ領域にも効率良く光を照射させることができる。したがって、本願の電磁波検出器では、Lag (残像) や感度低下といった問題を実用

50

上問題の無いレベルまで抑えることが可能になる。

【0054】

尚、アクティブマトリクス基板1では、信号線18と半導体膜2との間に、透光性を有する層間絶縁膜20が介在する構成をとっている。ここでは、層間絶縁膜20は1~5μmの厚みを有するものとする。この構成では、アクティブマトリクス基板1の裏面から照射された光が層間絶縁膜20の内部を通過する際の光の回折によって、信号線18の上部に光が回り込み易いといった効果も得られる。このため、本実施の形態に係る電磁波検出器では、信号線18と半導体膜2との間に、層間絶縁膜20を備えた構成が好ましいといえる。

【0055】

但し、層間絶縁膜20を備えず信号線18と半導体膜2とが保護絶縁膜19のみを介して近接している場合であっても、半導体膜2に入射した光はその内部で回折を生じる。また、半導体膜2内で生じるトラップ電荷は、アクティブマトリクス基板1と半導体膜2との界面以外に、半導体膜2内の該界面に近接した部分でも生じると考えられる。したがって、本願発明は、層間絶縁膜20を備えないアクティブマトリクス基板1への適用を否定するものではない。

【0056】

また、層間絶縁膜20の厚みとしては、該厚みが1μm未満の場合は光の回折効果が急激に悪くなるために有用でなく、5μmより厚い場合は厚みの制御(均一性)が困難になる、或いはコンタクトホールの形成が困難になるといったプロセス的な問題が生じるため好ましくない。

【0057】

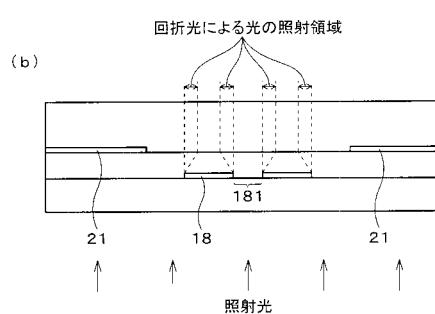

また、層間絶縁膜が介在することによる光の回折効果については、図3(a)に示すように、配線に開口部が形成されていない従来の構成においても相応の効果をもたらす。但し、本実施の形態に係る電磁波検出器は、信号線18に開口部181を設けることによって、図3(b)に示すように、回折光による半導体膜2への光の照射領域を広げており、これによって、実質的な配線幅を細くすることなく(すなわち、配線抵抗を増加させることなく)画素電極21の隙間に効率良く光を照射することができるものである。

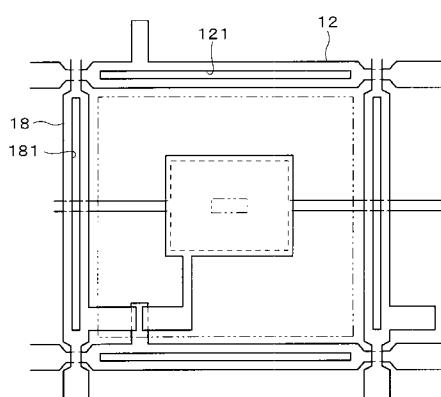

【0058】

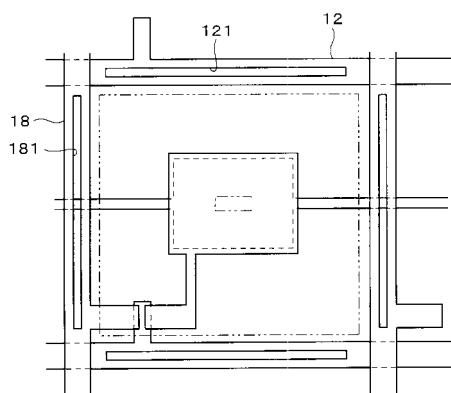

以上の説明においては、信号線18において開口部181を設けた場合の構成について例示している。しかしながら、走査線12においても開口部を設けることで信号線18の場合と同様の効果が得られる。図4は、信号線18に加えて走査線12にも開口部121を設けた例を示す。これによって、縦方向および横方向の画素間電荷トラップを解消することが可能になる。

【0059】

また、上記電磁波検出器においては、信号線18および走査線12のどちらか一方にのみ開口部を設ける構造であっても良い。但し、走査線12と信号線18との線幅が大きく異なる場合、太い線幅を有する配線の方に優先的に開口部を設けることが好ましい。

【0060】

また、信号線18や走査線12が、金属膜だけでなく、金属膜と透明導電膜の積層膜(例えばTaとITOの積層膜)から形成される場合には、金属膜と透明導電膜の両者に開口部を設けても良いし、金属膜にのみ開口部を設ける構成としても良い。また、上記の各例では、信号線18と走査線12との交差部には開口部を設けない図を示したが、該交差部にも開口部を延設させてもよい。

【0061】

さらに、上述のように配線に開口部を設ける構成のアクティブマトリクス基板において、以下の変形例をとり得ることが可能である。

【0062】

図5は、信号線18にスリット状の開口部181を設けつつ、信号線18と走査線12の交差部において、信号線18の線幅を狭くする構成をとっている。これによって、信号線

10

20

30

40

50

18と走査線12との交差部の面積が小さくなり、信号線18と走査線12との間の配線容量（主に交差部に発生する寄生容量）を低減することができる。これにより、配線の時定数を小さくすることができるとともに、S/Nの優れた電磁波検出器を実現できる。尚、信号線18から読み出される信号の雑音のゲインは、C<sub>d</sub>/C<sub>f</sub>（C<sub>d</sub>：信号線の配線容量、C<sub>f</sub>：電荷検出アンプのフィードバック容量）で表されるため、信号線の配線容量は、読み出しがS/Nに直接作用する。

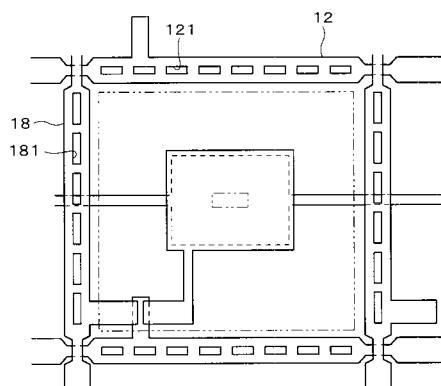

#### 【0063】

図6は、図5の構成に加えて、走査線12にもスリット状の開口部121を設けつつ、信号線18と走査線12の交差部において、走査線12の線幅をも狭くする構成を示す。これによって、縦方向と横方向の画素間電荷トラップを解消し、かつ、信号線18と走査線12との交差部の面積が小さくなり、信号線18や走査線12の配線容量を低減することができる。10

#### 【0064】

さらに、図7では、図6の構成において信号線18や走査線12に形成する開口部を、複数の開口部から構成した例を示している。このように、配線上の領域における半導体膜に對しての光照射効率を向上させるものであれば、開口部の大きさ、形状、配置間隔等は、特に限定されるものではない。

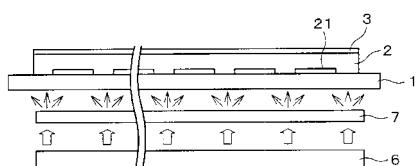

#### 【0065】

また、本実施の形態に係る電磁波検出器では、光の回折を利用して配線に對して光の照射側と反対側に光を効率よく回り込ませ、半導体膜2への光照射効率を向上させている。このような光の回り込み効果をより向上させるために、図8に示すように、アクティブマトリクス基板1とその背後に設置された光源6との間に拡散板7を設ける構成とすることができる。20

#### 【0066】

このように、拡散板7を配置することによって、アクティブマトリクス基板1に照射される光において、基板の法線方向に對し斜め方向に入射する光が増加する。そして、斜め方向に入射する光の増加と光の回折との相乗効果により、配線に對して光の照射側と反対側に光を効率よく回り込ませることができる。また、アクティブマトリクス基板1に照射される光を拡散光として光強度の面内分布を均一にすることができる。尚、図8に示す構成において、拡散板7と光源6とが一体形成されていてもよい。30

#### 【0067】

##### 【発明の効果】

本発明のアクティブマトリクス基板は、以上のように、上記信号線及び/又は走査線に、開口部が形成されている構成である。

#### 【0068】

それゆえ、上記アクティブマトリクス基板を用いた電磁波検出器では、アクティブマトリクス基板の裏面に光源を設置する前提のもと、光源から発せられた光は、信号線や走査線の配線に設けられた開口部を通過する。そして、上記開口部を通過する光の回折により、配線に對して光の照射側と反対側にも光を回り込ませることができ、配線抵抗を上げることなく、電荷がトラップされている場所に効率良く光を照射することができるという効果を奏する。40

#### 【0069】

また、上記アクティブマトリクス基板においては、上記開口部は、上記信号線及び/又は上記走査線の延伸方向に沿って設けられたスリットである構成とすることができる。

#### 【0070】

それゆえ、格子状に形成された画素電極同士の間隙に効率良く光を照射することができるという効果を奏する。

#### 【0071】

また、上記アクティブマトリクス基板においては、上記信号線及び/又は上記走査線は、上記信号線と上記走査線との交差部において線幅が細くなるように形成されている構成と50

することができる。

【0072】

それゆえ、信号線と走査線との交差部の面積が小さくなり、信号線と走査線との配線容量（主に交差部に発生する寄生容量）を低減することができ、S/Nの優れた電磁波検出器を実現できるという効果を奏する。

【0073】

また、上記アクティブマトリクス基板においては、上記信号線及び／又は走査線と上記画素電極との間には、層間絶縁膜が介在している構成とすることができる。

【0074】

それゆえ、光源から発せられた光は、配線の内部の開口部を通過した後、層間絶縁膜の内部を通過する間に、回折によって信号線や走査線の裏側により光が回り込み易くなり、電荷がトラップされている場所にさらに効率良く光を照射することができるという効果を奏する。

10

【0075】

また、本発明の電磁波検出器は、以上のように、上記アクティブマトリクス基板と、上記アクティブマトリクス基板の上面に形成された半導体膜と、上記半導体膜の上面に形成されたバイアス電極とを備えており、上記アクティブマトリクス基板の上記半導体膜が形成された面とは反対の面側に、上記アクティブマトリクス基板を照射し得る光源を備えている構成である。

【0076】

20

それゆえ、アクティブマトリクス基板において配線に開口部を持たない従来構成に比べ、実質的な配線幅が同じであっても、配線の裏側にある半導体膜に効率よく光を照射することができ、配線抵抗を上げることなく、電荷がトラップされている場所に効率良く光を照射することができるという効果を奏する。

【0077】

また、上記電磁波検出器においては、上記アクティブマトリクス基板と上記光源との間に、上記光源からの照射光を拡散光に変換する拡散手段を備えている構成とすることができる。

【0078】

30

それゆえ、光源から発せられた光がアクティブマトリクス基板への入射前に拡散手段によって拡散され、斜め方向への入射光が生成される。これにより、信号線や走査線の上部に光が回り込み易くなり、半導体膜において電荷がトラップされている場所にさらに効率良く光を照射することができるという効果を奏する。

【図面の簡単な説明】

【図1】本発明の一実施形態を示すものであり、図1(a)は電磁波検出器の1画素単位の構造を示す断面図、図1(b)はその平面図である。

【図2】図2(a)は走査線とゲート電極との形状を示す平面図、図2(b)は信号線とソース電極との形状を示す平面図、図2(c)は電荷容量線と電荷容量電極との形状を示す平面図である。

【図3】図3(a)は従来のアクティブマトリクス基板の構造における半導体膜への光照射領域を示す図であり、図3(b)は本発明のアクティブマトリクス基板の構造における半導体膜への光照射領域を示す図である。

40

【図4】本発明の他の実施形態を示すものであり、電磁波検出器の1画素単位の構造を示す平面図である。

【図5】本発明のさらに他の実施形態を示すものであり、電磁波検出器の1画素単位の構造を示す平面図である。

【図6】本発明のさらに他の実施形態を示すものであり、電磁波検出器の1画素単位の構造を示す平面図である。

【図7】本発明のさらに他の実施形態を示すものであり、電磁波検出器の1画素単位の構造を示す平面図である。

50

【図8】本発明のさらに他の実施形態を示すものであり、光源とアクティブマトリクス基板との間に拡散板を設けた電磁波検出器の構造を示す断面図である。

【図9】電磁波検出器の検出原理を示す図である。

【図10】従来の電磁波検出器を示すものであり、図10(a)は電磁波検出器の1画素単位の構造を示す断面図、図10(b)はその平面図である。

【図11】電磁波検出器において、隣接する画素収集電極間における間隙を示す平面図である。

【図12】従来の電磁波検出器において、アクティブマトリクス基板の裏面に光源を配置する場合の構成を示す断面図である。

【符号の説明】

- |         |               |

|---------|---------------|

| 1       | アクティブマトリクス基板  |

| 2       | 半導体膜          |

| 3       | バイアス電極        |

| 4       | TFT(スイッチング素子) |

| 5       | 蓄積容量          |

| 6       | 光源            |

| 7       | 拡散板(拡散手段)     |

| 11      | ガラス基板(基板)     |

| 12      | 走査線           |

| 18      | 信号線           |

| 20      | 層間絶縁膜         |

| 21      | 画素電極          |

| 121・181 | 開口部           |

10

20

【図1】

【図2】

(a)

(b)

(c)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(51)Int.Cl. F I

**G 0 1 T 1/24 (2006.01)** G 0 1 T 1/24

(72)発明者 和泉 良弘

大阪府大阪市阿倍野区長池町 22番22号 シャープ株式会社内

(72)発明者 佐藤 賢治

京都府相楽郡精華町光台3-9 株式会社島津製作所内

審査官 恩田 春香

(56)参考文献 特開平09-009153 (JP, A)

特開平10-256558 (JP, A)

特開2002-026300 (JP, A)

特開平09-101538 (JP, A)

特開2000-269475 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14 -27/148

G01T 1/24

H01L 29/786

H01L 31/09

H04N 5/335