(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5383353号

(P5383353)

(45) 発行日 平成26年1月8日(2014.1.8)

(24) 登録日 平成25年10月11日(2013.10.11)

(51) Int.Cl.

F 1

HO3K 17/08 (2006.01)

HO3K 17/687 (2006.01)HO3K 17/08

HO3K 17/687C

A

請求項の数 6 (全 17 頁)

(21) 出願番号 特願2009-160513 (P2009-160513)

(22) 出願日 平成21年7月7日 (2009.7.7)

(65) 公開番号 特開2011-18960 (P2011-18960A)

(43) 公開日 平成23年1月27日 (2011.1.27)

審査請求日 平成24年2月17日 (2012.2.17)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100103894

弁理士 家入 健

(72) 発明者 福原 淳

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

(72) 発明者 満田 剛

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

審査官 栗栖 正和

最終頁に続く

(54) 【発明の名称】異常検出時急速放電回路

## (57) 【特許請求の範囲】

## 【請求項 1】

電源端子と出力端子の間に接続され、当該出力端子に接続される負荷に電流を出力する出力トランジスタを、システムの異常時にオフする保護回路であって、

前記出力トランジスタのゲート電極と前記電源端子との間に接続され、前記システムの異常時に、前記ゲート電極の電荷を前記電源端子に放電する第1の放電部と、

前記ゲート電極と前記出力端子との間に接続され、前記システムの異常時に、前記第1の放電部が前記放電を行った後に、前記ゲート電極の電荷を前記出力端子に放電する第2の放電部と、

を有し、

前記第1の放電部は、前記ゲート電極にドレインが接続され、ゲート・ソース間をショートしたデプレッション型トランジスタと、前記デプレッション型トランジスタの前記ゲート・ソースにベースが接続され、前記出力トランジスタの前記ゲート電極にコレクタが接続され、前記電源端子にエミッタが接続された寄生バイポーラトランジスタとを備え、

前記第2の放電部は、前記出力トランジスタの前記ゲート電極にドレインが接続され、前記出力トランジスタのソース電極にソースが接続され、前記システムの異常時にオンするための信号がゲートに与えられるエンハンスメント型トランジスタを備える保護回路。

## 【請求項 2】

前記第1の放電部は、N型の基板領域にP型のウェルが形成され、前記ウェル内に形成されたN型トランジスタを含み、前記N型トランジスタは、前記出力トランジスタの前記

10

20

ゲート電極にドレインが接続されており、前記寄生バイポーラトランジスタは、前記ドレインをコレクタとし、前記ウェルをベースとし、前記基板領域をエミッタとする第1寄生バイポーラトランジスタにより形成される請求項1記載の保護回路。

【請求項3】

前記N型トランジスタは、前記ドレインをコレクタとし、前記ウェルをベースとし、ソースをエミッタとする第2寄生バイポーラトランジスタと、前記ソースをコレクタとし、前記ウェルをベースとし、前記基板領域をエミッタとする第3寄生バイポーラトランジスタを更に有し、前記第2及び第3寄生バイポーラトランジスタにより、前記ゲート電極の電荷を前記電源端子に放電する経路が更に形成され、

前記第1の放電部は、更に、前記基板領域に形成されたP型トランジスタを含み、前記P型トランジスタは、前記N型トランジスタと前記出力端子との間に接続され、ソースをエミッタとし、前記基板領域をベースとし、ドレインをコレクタとする第4寄生バイポーラトランジスタを有し、前記第2及び第4寄生バイポーラトランジスタにより、前記ゲート電極の電荷を前記出力端子に放電する経路が更に形成される請求項2記載の保護回路。

10

【請求項4】

前記出力トランジスタ、前記デプレッション型トランジスタ及び前記エンハンスメント型トランジスタはN型である請求項1乃至3のいずれか1項記載の保護回路。

【請求項5】

前記第1の放電部は、N型の基板領域にP型のウェルが形成され、前記ウェル内に形成されたダイオードを含み、

20

前記ダイオードは、前記出力トランジスタの前記ゲート電極にカソードが接続され、前記デプレッション型トランジスタの前記ゲート・ソースにアノードが接続されており、前記寄生バイポーラトランジスタは、前記カソードをコレクタとし、P型のウェルをベースとし、N型の基板領域をエミッタとする寄生バイポーラトランジスタにより形成される請求項1記載の保護回路。

【請求項6】

前記出力トランジスタの前記ゲート電極と前記ソース電極との間に接続され、前記システムの正常時に前記出力トランジスタをオフする他のデプレッション型トランジスタを更に有する請求項1乃至5のいずれか1項記載の保護回路。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関し、特に異常を検出して急速ターンオフする機能を有する半導体装置に関する。

【背景技術】

【0002】

近年、自動車用電装部品に代表される、大電流を駆動するようなスイッチ機能を有するシステムに、半導体装置が用いられるようになってきている。また、大電流を駆動するシステムにおいては、例えば負荷がショートし大電流が流れのような異常が発生した場合には、システムを保護するために、過熱や過電流等を検出して、スイッチを自己オフする機能を有する。

40

【0003】

異常検出時の自己オフ動作で重要なのが、ターンオフ時に発生する熱損失を低減することである。なぜなら、異常検出時には既に大きく発熱している可能性が高いため、ターンオフ時の熱損失が大きいと破壊する恐れがあるためである。したがって、異常検出時のオフ動作では、急速にターンオフすることが肝要である。

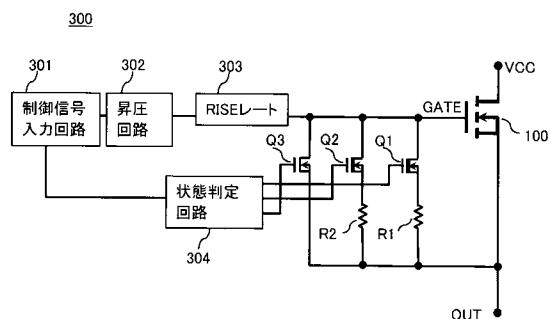

【0004】

特許文献1には、急速にターンオフする出力回路の技術が開示されている。図7は特許文献1に記載の技術の出力回路の構成を示す図である。図7に示すように、出力回路300は、電源端子と出力端子との間に接続された出力MOS100を有する。出力MOS1

50

0 0 は回路のスイッチ機能を有するN型のエンハンスマントトランジスタである。トランジスタQ 1とトランジスタQ 2はN型のデブレッショナまたはエンハンスマントトランジスタである。トランジスタQ 3はN型のエンハンスマントトランジスタである。抵抗R 1及び抵抗R 2は、それぞれトランジスタQ 1及びトランジスタQ 2と、出力端子との間に接続されている。これにより、出力MOS 1 0 0のゲート端子と出力端子との間に、それぞれトランジスタQ 1～Q 3により、3つの放電経路が形成されている。放電経路を選択することによって出力MOS 1 0 0のゲート電極の電荷の放電を制御する、状態判定回路3 0 4を有する。また、通常時に出力MOS 1 0 0を制御するブロックとして、制御信号入力回路3 0 1、昇圧回路3 0 2及びR I S E レート3 0 3を有する。

## 【0 0 0 5】

10

通常時は、制御信号入力回路3 0 1に出力MOS 1 0 0をオンオフする信号が入力され、それに基づいて昇圧回路3 0 2が昇圧電圧をR I S E レート3 0 3を介してG A T Eに出力する。通常時に出力MOSをオフする際は、制御信号入力回路3 0 1からの信号に基づき、昇圧回路3 0 2が動作を停止し、状態判定回路3 0 4が電源端子と出力端子間の電圧を検出する。出力回路3 0 0は、トランジスタQ 1と抵抗R 1で構成された放電経路と、トランジスタQ 2と抵抗R 2で構成された放電経路と、トランジスタQ 3で構成される放電経路とを有している。状態判定回路3 0 4から出力される信号に基づき、それぞれの放電経路のいずれか、あるいは複数をアクティブにし、出力MOSのゲート電荷を出力端子に放電することで、出力MOSをオフさせる。

## 【0 0 0 6】

20

状態判定回路3 0 4は例えば電源端子と出力端子の間の電圧を測定して過電流が流れている否かを検出することで異常を検出する。この場合には、制御信号入力回路3 0 1にMOS 1 0 0を強制的にオフするためのオフ信号を入力する。また、状態判定回路3 0 4から出力される信号に基づき、3つの放電経路のいずれか、あるいは複数をアクティブにし、出力MOSのゲート電荷を出力端子に放電することで、出力MOSをオフさせる。

## 【0 0 0 7】

30

通常時のターンオフはトランジスタQ 1をアクティブにする。過電流状態での急速ターンオフはトランジスタQ 3だけ、あるいはトランジスタQ 1及びトランジスタQ 2を同時にアクティブにする。通常時より電流が大きく、過電流より小さいときのターンオフ時には、トランジスタQ 2だけ、あるいはトランジスタQ 1も同時にアクティブにすることで、スルーレートを調整する。

## 【0 0 0 8】

ここで、過電流状態では、特にエンハンスマントトランジスタであるトランジスタQ 3の動作が重要である。出力MOSのゲート電荷をトランジスタQ 3が急速に放電することで、急速ターンオフを実現する。次に、トランジスタQ 3の動作について具体的に説明する。ここでは、

- (1) トランジスタQ 3だけをアクティブにして急速ターンオフ動作を実現する場合

- (2) トランジスタQ 1～Q 3を全てアクティブにして急速ターンオフ動作を実現する場合

について説明する。

40

## 【0 0 0 9】

(1) トランジスタQ 3だけをアクティブにして急速ターンオフ動作を実現する場合

トランジスタQ 3のゲート・ソース間電圧をV<sub>g s 3</sub>、閾値電圧をV<sub>t h n</sub>とすると、トランジスタQ 3をオンさせるには、V<sub>g s 3</sub> > V<sub>t h n</sub>とする必要がある。ゲート電圧をV<sub>x</sub>、Q 3の閾値電圧をV<sub>t h n</sub>、出力電圧をO U Tとすると、V<sub>x</sub> - O U T > V<sub>t h n</sub>よりV<sub>x</sub> > O U T + V<sub>t h n</sub>を満たす電位レベルの信号をゲートに印加する必要があり、その信号を状態判定回路で生成する必要がある。

## 【0 0 1 0】

ここで、O U T電位は、電源端子の電圧をV<sub>C C</sub>とし、出力MOSのオン抵抗をR<sub>o n</sub>とし、出力MOSが駆動している電流をI<sub>o u t</sub>とすると、O U T = V<sub>C C</sub> - I<sub>o u t</sub>・

50

$R_{on}$  である。1例として、 $V_{CC} = 12V$ 、 $I_{out} = 70A$ 、 $R_{on} = 10m\Omega$ 、 $V_{thn} = 1V$ の場合を考えると、 $OUT = 12V - 70A \times 10m\Omega = 11.3V$ であるから  $V_x > 11.3V + 1V = 12.3V$  となり、 $V_x$  は電源電圧  $V_{CC}$  以上の電位である必要がある。これは一例であり、 $V_{CC}$  以上の電圧を印加しなくてもトランジスタ Q3 はオンしうるが、 $V_{CC}$  以下の電圧でオンする場合は、ターンオフ動作初期は飽和領域で動作するため、放電開始直後は放電電流が制限される。トランジスタ Q3 だけで放電開始直後から急速に放電するには、トランジスタ Q3 が十分に電流を駆動できるようにゲートに高い電圧を印加する必要があり、 $V_x$  に電源電圧  $V_{CC}$  以上の電圧を印加しなければならず、ブートストラップなどの昇圧回路が必要となる。

## 【0011】

10

(2) トランジスタ Q1 乃至 Q3 を全てアクティブにして急速ターンオフを実現する場合

トランジスタ Q3 のゲートには電源電圧レベルの電位を印加し、同時に Q1、Q2 をアクティブ状態にする。トランジスタ Q1、トランジスタ Q2 がデブレッシュントランジスタである場合には、電源電圧  $V_{CC}$  もしくは、出力電圧  $OUT$  と同レベルの電位を印加すればトランジスタ Q1 とトランジスタ Q2 はオンする。トランジスタ Q1 とトランジスタ Q2 によって出力 MOS のゲート電荷が放電され、一定量の電荷が放電されると、 $OUT$  電位が低下し始める。すると、Q3 もオンできる状態となる。さらに放電が進み  $OUT$  が低下して、 $V_{gs3} > V_{ds3} - V_{thn}$ 、すなわち  $V_x - OUT > GATE - OUT + V_{thn}$  ( $GATE$  は、出力 MOS のゲート電極の電位) を満たすとトランジスタ Q3 は線形領域で動作するため、トランジスタ Q3 は大きな放電電流を流せるようになる。

20

## 【0012】

このように、トランジスタ Q1 ~ Q3 を用いて急速放電動作を実現する際には、ターンオフ直後はトランジスタ Q3 を必ずしもオンする必要は無く、そのためゲートに印加する電圧  $GATE$  は電源電圧  $V_{CC}$  でよく、ブートストラップのような特別な回路は必要ない。しかしながら、ターンオフ直後の放電はトランジスタ Q1 とトランジスタ Q2 が担っており、トランジスタ Q1 とトランジスタ Q2 はデブレッシュントランジスタであるため、放電電流を大きくするにはトランジスタサイズを大きくする必要がある。

## 【先行技術文献】

30

## 【特許文献】

## 【0013】

## 【特許文献 1】特開 2005-123666 号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0014】

上述したように、図 7 に示す従来の出力回路において、トランジスタ Q3 のみで急速放電動作を実現するには、ブートストラップのような昇圧回路が必要である。また、トランジスタ Q1 ~ Q3 をオンして急速放電動作を実現するには、オフ動作初期の放電を担うトランジスタ Q1 とトランジスタ Q2 のトランジスタサイズを大きくする必要がある。いずれも面積が増大するという問題点がある。

40

## 【課題を解決するための手段】

## 【0015】

本発明に係る保護回路は、電源端子と出力端子の間に接続され、当該出力端子に接続される負荷に電流を出力する出力トランジスタを、システムの異常時にオフする保護回路であって、前記出力トランジスタの前記ゲート電極と前記電源端子との間に接続され、前記システムの異常時に、前記ゲート電極の電位を電源電位と等しくなるまで放電させる第1の放電部と、前記ゲート電極の電位を出力電位と等しくなるまで放電させる第2の放電部とを有する。

## 【0016】

本発明に係る出力トランジスタのターンオフ方法は、電源端子と出力端子の間に接続さ

50

れ、当該出力端子に接続される負荷に電流を出力する出力トランジスタを、システムの異常時にターンオフする出力トランジスタのターンオフ方法であって、前記システムの異常を検出したら、前記出力トランジスタの前記ゲート電極を電源電位と等しくなるまで放電させ、前記出力トランジスタのゲート電極の電位を出力電位と等しくなるまで放電させる。

【発明の効果】

【0017】

寄生バイポーラトランジスタを積極的に活用し、かつ放電初期にゲート電荷を電源端子に放電することで、急速ターンオフ動作を小さな面積で実現できる。

【図面の簡単な説明】

10

【0018】

【図1】実施の形態1にかかるハイサイド出力回路の回路図である。

【図2】実施の形態1にかかる保護回路の回路図である。

【図3】実施の形態1にかかるシリコン素子の断面図である。

【図4】実施の形態1に係る制御信号生成回路の回路図である。

【図5】実施の形態2にかかる回路図と、シリコン素子の断面図である。

【図6】実施の形態にかかるハイサイド出力回路を変形した回路図である。

【図7】従来の出力回路を示す回路図である。

【発明を実施するための形態】

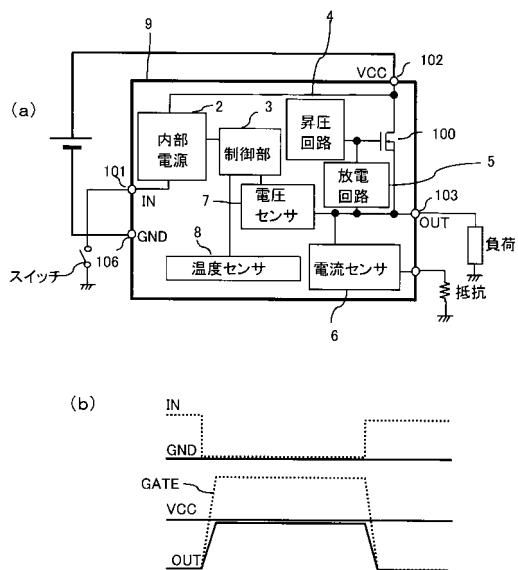

【0019】

20

実施の形態1

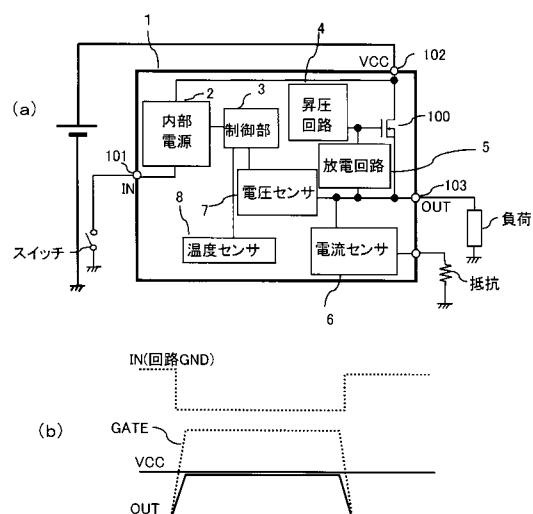

以下、図面を参照して本発明の実施の形態について説明する。図1(a)は、本発明の実施の形態に係るハイサイド出力回路1を示すブロック図である。本実施の形態に係るハイサイド出力回路1は、電源端子102と出力端子103の間に接続され、出力端子103に接続される負荷に電流を出力する出力MOS100を有している。またハイサイド出力回路1は、システムの異常を検出する異常検出回路と、異常検出回路がシステムの異常を検出した場合に、出力MOS100を急速オフする保護回路とを有する。

【0020】

本実施の形態においては、この保護回路は、放電回路5に含まれる。また、異常検出回路として、電圧センサ7、温度センサ8、及び電流センサ6が設けられている。ハイサイド出力回路1は、その他、内部電源2、制御部3、昇圧回路4等を有している。

30

【0021】

放電回路5は、入力がオフ(非アクティブ)になったときや異常検出時に出力MOS100や負荷への通電を遮断するために、出力MOS100のゲート電極と出力端子103間の電位差が0Vとなるように、出力MOS100のゲート電荷を出力端子103に放電する。

【0022】

昇圧回路4は、通常動作時において出力MOS100のオンオフを行う。内部電源2は外部からの電源電圧を直接受ける必要のない回路に電源を供給する。制御部3は外部からの制御信号と回路内部で検知した異常状態と正常復帰の際に他のブロックをコントロールする。

40

【0023】

さらに、ハイサイド出力回路1は、上述したように、システムの異常を検出する異常検出回路として、負荷に流れる負荷電流をモニタする電流センサ6と、出力MOS100の温度をモニタする温度センサ8と、出力端子103の電圧OUTをモニタする電圧センサ7を有する。これらの異常検出回路は、回路内部の異常を検出した場合、すなわち、電流センサ6であれば、負荷に流れる負荷電流の大きさが異常であること、電圧センサ7であれば、出力端子103の電圧OUTが異常であること、温度センサ8であれば、出力MOS100の温度が異常であることを検出すると、異常検出信号を制御部3及び放電回路5に出力する。なお、本実施の形態においては、電流センサ6、電圧センサ7、及び温度セン

50

サ 8 を有するものとして説明するが、システムの異常を検出する手段としてはこれらのうち少なくとも 1 つ以上を有していればよい。

【 0 0 2 4 】

図 1 ( b ) は、ハイサイド出力回路 1 が正常時にオンオフするときの電位の変化を示すタイミングチャートであり、それぞれ入力電位 I N 、出力 M O S 1 0 0 のゲート電位 G A T E 、電源電圧 V C C 、出力電圧 O U T の電位を示している。スイッチ S がオンし入力電圧 I N がグランドレベルになると、昇圧回路 4 が電源電圧 V C C より高い昇圧電圧を生成し、出力 M O S 1 0 0 のゲート端子に供給する。これにより、出力 M O S 1 0 0 がオンして負荷に電流が流れる。

【 0 0 2 5 】

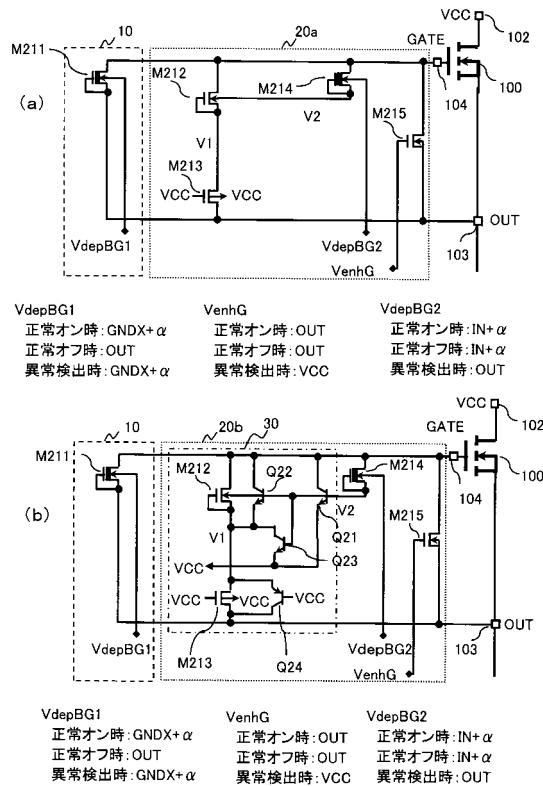

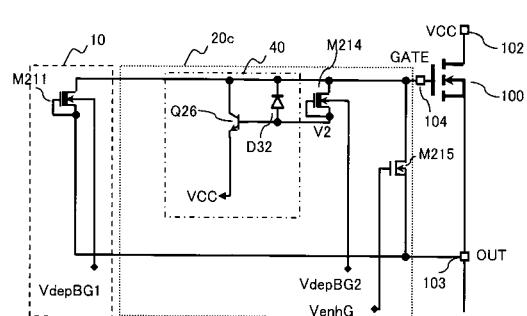

次に、本実施の形態にかかる放電回路 5 について詳細に説明する。図 2 ( a ) は、本発明の実施の形態に係る放電回路 5 を示す回路図である。図 2 ( a ) に示すように、放電回路 5 は、正常時のオフ動作を行う通常オフ回路 1 0 と、異常時に出力 M O S 1 0 0 の急速オフ動作を行う保護回路 ( 以下、急速オフ回路 という。 ) 2 0 a とを有する。

【 0 0 2 6 】

急速オフ回路 2 0 a は、出力 M O S 1 0 0 のゲート電極 1 0 4 と電源端子 1 0 2 との間に接続され、システムの異常時に、ゲート電極 1 0 4 の電位 G A T E を電源電圧 V C C と等しくなるまで放電する第 1 の放電部と、出力 M O S 1 0 0 のゲート電極とソース電極との間に接続され、システムの異常時に、ゲート電極の電荷を出力電圧 O U T と等しくなるまで放電する第 2 の放電部とを有する。

【 0 0 2 7 】

ここで、図 2 ( a ) は急速オフ回路 2 0 a のシリコン素子の表面の要素のみを示した図であるが、図 2 ( b ) は、第 2 トランジスタ M 2 1 2 及び第 3 トランジスタ M 2 1 3 の寄生バイポーラトランジスタも合わせて示す図である。

【 0 0 2 8 】

第 1 の放電部は、出力 M O S トランジスタ 1 0 0 のゲート電極にドレインが接続されゲート・ソース間をショートしたデプレッショントランジスタ M 2 1 4 と、出力 M O S トランジスタ 1 0 0 のゲート電極にドレインが接続されゲート・ソース間をショートしたエンハンスマントトランジスタ M 2 1 2 と、第 2 トランジスタ M 2 1 2 と出力 M O S トランジスタ 1 0 0 のソース電極の間に接続されたエンハンスマントトランジスタ M 2 1 3 とを有し、第 2 トランジスタ M 2 1 2 の寄生バイポーラトランジスタ Q 2 1 ~ Q 2 3 により、ゲート電極の電位を電源電圧と等しくなるまで放電し、第 3 トランジスタ M 2 1 3 の寄生バイポーラトランジスタ Q 2 4 により、ゲート電極の電位 G A T E が出力電圧 O U T と等しくなるまで電荷を放電する。

第 2 の放電部は、出力 M O S 1 0 0 のゲート電極とソース電極との間に接続されたトランジスタ M 2 1 5 を有する。

【 0 0 2 9 】

出力 M O S 1 0 0 は N 型のエンハンスマントトランジスタであり、そのドレインは電源端子 1 0 2 に接続され、そのソースは出力端子 1 0 3 に接続される。通常オフ回路のトランジスタ M 2 1 1 と、第 1 トランジスタ M 2 1 4 は N 型のデプレッショントランジスタであり、ゲート・ソースがショートされており、定電流源として動作する。第 2 トランジスタ M 2 1 2 は N 型のエンハンスマントトランジスタであり、寄生バイポーラトランジスタを活用するために配置している。第 3 トランジスタ M 2 1 3 は P 型のエンハンスマントトランジスタであり、正常時やターンオン時に第 1 トランジスタ M 2 1 4 が出力 M O S 1 0 0 のゲート電荷を出力端子 1 0 3 に放電してしまわないために配置している。トランジスタ M 2 1 5 は N 型のエンハンスマントトランジスタであり、そのソースは出力端子 1 0 3 に接続される。

【 0 0 3 0 】

V d e p B G 1 、 V d e p B G 2 、 V e n h G は、制御信号を示し、後述する図 4 ( a ) 、 ( b ) 、 ( c ) 、 ( d ) の各回路を使用して生成される。

10

20

30

40

50

## 【0031】

次に、寄生バイポーラトランジスタについて説明する。図2(b)には、4つの寄生バイポーラトランジスタQ21、Q22、Q23、Q24を示しており、これらは急速オフ時に動作する。

## 【0032】

第1乃至第3寄生バイポーラトランジスタQ21～Q23は、第2トランジスタM212の寄生バイポーラトランジスタであり、第4寄生バイポーラトランジスタQ24は、第3トランジスタM213の寄生バイポーラトランジスタである。

## 【0033】

第1寄生バイポーラトランジスタQ21は、第1トランジスタM214の電流をベース電流とし出力MOS100のゲート電極の電荷を電源端子102に放電する。第2寄生バイポーラトランジスタQ22は、第1トランジスタM214の電流をベース電流とし、第3及び第4寄生バイポーラトランジスタQ23、Q24に電流を供給する。10

## 【0034】

第3寄生バイポーラトランジスタQ23は、第1トランジスタM214からの電流をベース電流とし、第2寄生バイポーラトランジスタQ22からの電流により出力MOS100のゲート電極の電荷を電源端子102に放電する。第4寄生バイポーラトランジスタQ24は、第2寄生バイポーラトランジスタQ22からの電流により出力MOS100のゲート電極の電荷を出力端子103に放電する。

## 【0035】

一般に、トランジスタの縦方向に形成されるQ21、Q23の増幅度hfe1は大きく、横方向に形成されるQ22、Q24のhfe2は小さい。20

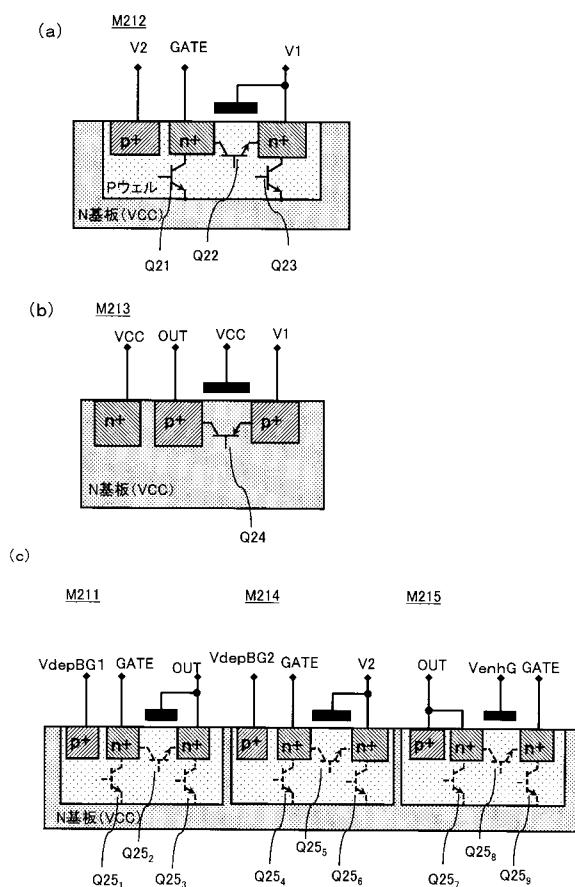

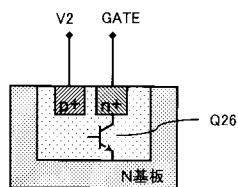

## 【0036】

図3に、本発明の実施の形態に係るシリコン素子を示す断面図を示す。図3(a)は第2トランジスタM212を示す断面図である。寄生バイポーラトランジスタQ21は、トランジスタM212のドレインをコレクタとし、基板領域であるN基板をエミッタとし、N基板上に形成されたPウェルをベースとして機能する。また寄生バイポーラトランジスタQ23は、第2トランジスタM212のソースをコレクタとし、N基板をコレクタとし、Pウェルをベースとして機能する。また寄生バイポーラトランジスタQ22は第2トランジスタM212のドレインをコレクタとし、ソースをエミッタとし、Pウェルをコレクタとしている。30

## 【0037】

図3(b)は、第3トランジスタM213を示す断面図である。寄生バイポーラトランジスタQ24は、第3トランジスタM213のソースをエミッタとし、ドレインをコレクタとし、N基板をベースとしている。

## 【0038】

図3(c)はトランジスタM211、M214、M215を示す断面図である。トランジスタM211、M214及びM215は、N型トランジスタであるため縦方向の寄生バイポーラトランジスタQ25<sub>1</sub>～Q25<sub>9</sub>が存在する。トランジスタM214のバックゲート電圧VdepBG2は、トランジスタM214のソース電位(MOS100のゲート電位GATE)、及びトランジスタM214のドレイン電位(電圧V2)より電位が低いため、この寄生バイポーラトランジスタQ25<sub>1</sub>～Q25<sub>9</sub>は動作しない。トランジスタM211及びM215も同様である。40

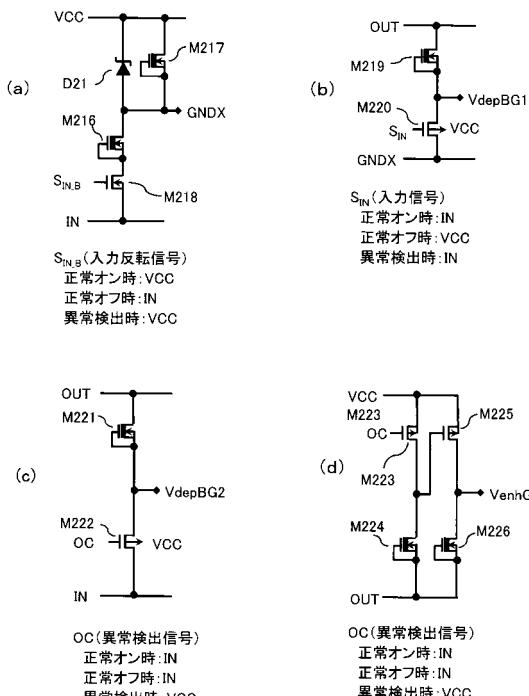

## 【0039】

図4(a)乃至図4(d)は、本発明の実施の形態に係る制御信号生成回路を示す図である。図4(a)は、電源電圧VCCからGNDX電圧を生成する回路を示す。トランジスタM216及びM217は、N型のデプレッショントランジスタである。トランジスタM218はN型のエンハンスマントトランジスタであり、ダイオードD21はツェナーダイオードである。

## 【0040】

10

20

30

40

50

図4 (b) に示す制御信号生成回路は、VCC - GNDX間で動作し、入力信号S<sub>IN</sub>を受けて、図2 (a)、(b)のトランジスタM211のバックゲートを制御する信号V<sub>d e p B G 1</sub>を生成する回路である。トランジスタM219はN型のデプレッショントランジスタであり、トランジスタM220はP型のエンハンスマントトランジスタである。

図4 (c) に示す制御信号生成回路は、異常検出信号OCを受けて、図2 (a)、(b)のトランジスタM214のバックゲートを制御する信号V<sub>d e p B G 2</sub>を生成する回路である。トランジスタM221はN型のデプレッショントランジスタであり、トランジスタM222はP型のエンハンスマントトランジスタである。

#### 【0041】

図4 (d) に示す制御信号生成回路は、異常検出信号OCを受けて、図2 (a)、(b)のトランジスタM215のゲートを制御する制御信号V<sub>e n h G</sub>を生成する回路である。トランジスタM223及びM225は、P型のエンハンスマントトランジスタであり、トランジスタM224及びM226はN型のデプレッショントランジスタである。

#### 【0042】

次に、各要素の動作について説明する。まず初めに、図4 (a)、(b)、(c)、(d)の動作について説明する。ここで、入力信号S<sub>IN</sub>、異常検出信号OCについて定義する。

(1) 正常オン時 (入力がアクティブ、異常検出が非アクティブ)

入力信号S<sub>IN</sub> = IN、異常検出信号OC = IN

(2) 正常オフ時 (入力が非アクティブ、異常検出が非アクティブ)

入力信号S<sub>IN</sub> = VCC、OC = IN (3) 異常検出時 (入力がアクティブ、異常検出が非アクティブ)

入力信号S<sub>IN</sub> = IN、異常検出信号OC = VCC

#### 【0043】

(1) 正常オン時

図4 (a) に示すトランジスタM218は、ゲートに入力の反転信号S<sub>IN\_B</sub> = VCCを受けているためフルオンしており、トランジスタM216は定電流源として動作している。ダイオードD21のブレークダウン電圧をV<sub>ZE</sub>とすると、GNDX = VCC - V<sub>ZE</sub>となる。正常オン時にはトランジスタM217も定電流を流しており、従ってトランジスタM216には、トランジスタM217の定電流とダイオードD21に流れる電流が流れれる。

#### 【0044】

図4 (b) に示すトランジスタM219は定電流として動作している。また、トランジスタM220はゲートにS<sub>IN</sub> = GNDをうけてオンしており、V<sub>d e p B G 1</sub>は" L " レベルとなる。ただし、本実施の形態における放電回路は、N基板上にPウェルを形成するため、P型トランジスタのバックゲートであるn<sup>+</sup>をN基板の電位VCCに接続する必要がある。そのため、トランジスタM220の接続状態では、バックゲート効果が働き、V<sub>d e p B G 2</sub> = GNDXとはならず、例えばGNDXより2V程度高い電圧となる。以降、この状態をV<sub>d e p B G 2</sub> = GNDX+と記載する。

#### 【0045】

図4 (c) に示すトランジスタM222はOC = INを受けており、図4 (b) と同様の動作であり、V<sub>d e p B G 2</sub> = IN+となる。図4 (d)において、トランジスタM223はOC = INを受けており、トランジスタM223とトランジスタM224とで構成しているインバータよりVCC電位が出力される。さらにトランジスタM225とトランジスタM226とで構成されているインバータよりOUT電位が出力される。入力と出力のレベルはいずれも" L " レベルであるが、入力電圧INから出力電圧OUTにレベルシフトされている。

#### 【0046】

(2) 正常オフ時

図4 (a) に示すトランジスタM218はゲートに入力反転信号S<sub>IN\_B</sub> = VCCを

10

20

30

40

50

受けており、トランジスタM218はカットオフする。従って、トランジスタM216及びM217もオフすることになりドレイン・ソース間電圧が0Vになる。従ってGNDX = VCCとなる。図4(b)に示すトランジスタM220は入力信号S<sub>IN</sub> = INを受けおりカットオフする。そのためトランジスタM219もオフし、V<sub>ds</sub> = 0Vとなるため、V<sub>depBG1</sub> = OUTとなる。図4(c)及び図4(f)においては、通常オフ時は、通常オン時と状態が変わらずOC = INとなるため、V<sub>depBG2</sub> = GNDX + 、V<sub>enhG</sub> = OUTとなる。

#### 【0047】

##### (3) 異常検出時

図4(a)、図4(b)においては、通常オン時と同様にS<sub>IN\_B</sub> = VCC、S<sub>IN</sub> = INとなるため、GNDX = VCC - V<sub>ze</sub>、V<sub>depBG1</sub> = GNDX + となる。図4(c)においては、トランジスタM222がゲートにOC = VCCを受けているため、トランジスタM222がカットオフし、V<sub>depBG2</sub> = OUTとなる。図4(d)においては、トランジスタM223がゲートにOC = VCCを受け取り、2段のインバータを介して、V<sub>enhG</sub> = VCCが出力される。

#### 【0048】

以上より、正常オン時、正常オフ時、異常検出時、に出力される信号はそれぞれ以下のようになる。

##### (1) 正常オン時

入力信号S<sub>IN</sub> = IN、異常検出信号OC = IN

V<sub>depBG1</sub> = GNDX +

V<sub>depBG2</sub> = IN +

V<sub>enhG</sub> = OUT

##### (2) 正常オフ時

入力信号S<sub>IN</sub> = VCC、異常検出信号OC = IN

V<sub>depBG1</sub> = OUT

V<sub>depBG2</sub> = IN +

V<sub>enhG</sub> = OUT

##### (3) 異常検出時

入力信号S<sub>IN</sub> = IN、異常検出信号OC = VCC

V<sub>depBG1</sub> = GNDX +

V<sub>depBG2</sub> = OUT

V<sub>enhG</sub> = VCC

#### 【0049】

次に、これらの信号が入力される図2(b)の放電回路の動作について説明する。

##### (1) 正常オン時

トランジスタM211はバックゲートにV<sub>depBG1</sub> = GNDX + を受けているので、バックゲート-ソース間電圧V<sub>bs211</sub> = V<sub>depBG1</sub> - OUTとなる。通常オン時、出力MOSトランジスタ100はフルオンしているため、OUT = VCCである。よって、V<sub>bs211</sub> = (GNDX + ) - VCC = (VCC - V<sub>ze</sub> + ) - VCC = - V<sub>ze</sub> + となる。V<sub>ze</sub> = 5V、+ = 2VとするとV<sub>bs211</sub> = - 3Vとなり、カットオフする。

#### 【0050】

また、第2トランジスタM212は、ゲート・ソース間がショートされているため、状態にかかわらずオフする。第3トランジスタM213は、ゲートにVCCを受けているので、第2トランジスタM212と同様に、状態に拘わらずオフする。トランジスタM214は、バックゲートにIN + を受けているので、例えば、バックゲート-ソース間電圧V<sub>bs214</sub> = V<sub>depBG2</sub> - OUT = (IN + ) - VCC = - VCC + となり、VCC = 12Vとし + = 2VとすればV<sub>bs214</sub> = - 10Vとなり、カットオフする。

#### 【0051】

10

20

30

40

50

トランジスタM214がカットオフしているため、寄生バイポーラトランジスタQ21～Q23のベース電流がゼロであり、オフしている。また、第2トランジスタM212とトランジスタM214がカットオフしているため、寄生バイポーラトランジスタQ24にも電流が流れず、オフしている。トランジスタM215はゲートにVenhG=OUTの電位を受けており、ゲート・ソース間電圧Vgs215=0Vであるからカットオフしている。以上の通り、全てのトランジスタがオフしているため、出力MOS100のゲート電荷は放電されず、正常なオン状態が維持される。

#### 【0052】

##### (2) 正常時のオフ動作

正常オフ時は、トランジスタM211はバックゲートにVdepBG1=OUTの信号を受けてるので定電流として動作し、出力MOS100のゲート電荷を出力端子103に放電する。第2トランジスタM212と第3トランジスタM213とトランジスタM214とトランジスタM215は正常オン時と状態が変わらないためオフする。また、寄生バイポーラトランジスタQ21～Q24もオフする。以上の通り、トランジスタM211のみが定電流としてオンし、出力MOS100のゲート電荷を放電してオフさせる。このトランジスタM211の電流能力を調整することで、ターンオフ時のスルーレートを調整することができる。

#### 【0053】

##### (3) 異常検出時のオフ動作

異常検出時は、トランジスタM211は通常オン時と同様にカットオフしている。また、第2トランジスタM212と第3トランジスタM213は、正常オン時、正常オフ時と同様にカットオフしている。

#### 【0054】

まず、システムの異常時に、ゲート電位GATEを電源電位VCCと等しくなるまで放電させる第1の放電部について説明する。第1トランジスタM214は、バックゲートに出力端子103の電位OUTを受け、定電流として動作する。第1トランジスタM214の電流は、寄生バイポーラトランジスタQ21～Q23のベース電流となる。寄生バイポーラトランジスタQ21は、第1トランジスタM214から受けたベース電流をhfe1倍し、出力MOS100のゲート電荷を電源端子102に放電する。

#### 【0055】

また、寄生バイポーラトランジスタQ22も同様にベース電流をhfe2倍した電流を寄生バイポーラトランジスタQ23と寄生バイポーラトランジスタQ24に流そうとする。ただし、寄生バイポーラトランジスタQ22は横方向のバイポーラトランジスタのため、電流の増幅率は寄生バイポーラトランジスタQ23と比較すると低い。寄生バイポーラトランジスタQ23も第1トランジスタM214のベース電流を受けており、寄生バイポーラトランジスタQ22の電流の一部を出力MOS100のゲート電荷を電源端子102へ放電電流として流す。

#### 【0056】

また、寄生バイポーラトランジスタQ24は、エミッタからベースに寄生バイポーラトランジスタQ22の電流の一部が流れるため、寄生バイポーラトランジスタQ22の電流の一部を出力MOS100のGATEから出力端子103へ放電電流として流す。ただし、寄生バイポーラトランジスタQ23と寄生バイポーラトランジスタQ24が流す電流は、コレクタ側にある寄生バイポーラトランジスタQ22によって決まり、Q22は増幅率が低いため、寄生バイポーラトランジスタQ23、Q24が流せる放電電流は、寄生バイポーラトランジスタQ21ほど大きくない。これらの動作より出力MOS100のGATEから電源端子102に電荷を放電する。

#### 【0057】

次に、ゲート電極の電位GATEを出力電位OUTと等しくなるまで放電させる第2の放電部について説明する。第1の放電部が出力MOS100のゲート電荷を電源端子102へ放電すると、出力MOS100のゲート電圧GATEが低下し始め、一定量のゲート

10

20

30

40

50

電荷が放電されると OUT 電位が低下し始める。トランジスタ M215 は、 $V_{enhG} = V_{CC}$  をゲートに受けているため、出力電圧 OUT が低下してトランジスタ M215 のゲート・ソース間電圧  $V_{gs215} = V_{CC} - OUT > V_{thn}$  となるとオンし、放電に寄与する。さらに出力電圧 OUT が低下し、 $V_{gs215} > V_{ds215} - V_{thn}$  ( $V_{CC} - OUT > (GATE - OUT) > V_{thn}$ ) となると、トランジスタ M215 は線形領域で動作するため、大きな放電電流を流すことができるようになる。こうして第 2 の放電部は、出力 MOS100 のゲート電位が OUT の電位と等しくなるまで電荷を放電させる。

#### 【0058】

以上の異常検出時の動作をまとめると、ターンオフ動作初期は、第 1 の放電部である寄生バイポーラトランジスタ Q21～Q24 が OUT のゲート電荷を電源端子 102 に放電し、OUT のゲート電極の電荷を出力端子 103 に放電することで OUT の電位が低下する。次に第 2 の放電部であるトランジスタ M215 がオンし、残りの OUT のゲート電荷を出力端子 103 に放電することで OUT MOS100 がオフする。このように、第 1 の放電部と第 2 の放電部により、ゲート電荷を放電させるため、急速ターンオフを実現することができる。

10

#### 【0059】

なお、トランジスタ M211、M214、M215 は N 型トランジスタであるため縦方向の寄生バイポーラトランジスタ Q25<sub>1</sub>～Q25<sub>9</sub> が存在する。しかし、トランジスタ M214 のバックゲートの電位  $V_{depBG2}$  は、そのソース端子の電圧 GATE、及びドレイン端子の電圧  $V_2$  より電位が低いため、寄生バイポーラトランジスタは動作しない。トランジスタ M211 とトランジスタ M215 も同様である。

20

#### 【0060】

また、ベース電流となる第 1 トランジスタ M214 の電流が寄生バイポーラトランジスタ Q21～Q23 のベースにどのように配分されるかは、第 1 トランジスタ M214 のソースから寄生バイポーラトランジスタ Q21～Q23 のそれぞれのベースまでの抵抗によって決まる。OUT MOS100 の GATE からの放電電流を大きくするには、電流をより大きく増幅することができる、寄生バイポーラトランジスタ Q21 のベース電流を大きくするのが効果的であり、第 1 トランジスタ M214 のソースから寄生バイポーラトランジスタ Q21 のベースまでの抵抗が小さくなるように考慮することが望ましい。

30

#### 【0061】

次に、本実施の形態にかかる変形例について説明する。上述の実施の形態では、図 4 (c) の制御信号生成回路を OUT - GND 間に設ける構成としたが、OUT - GNDX 間に構成しても、同様の急速オフ動作の効果は得られる。ただし、GND 電圧ではなく、GNDX 電圧とすると、通常オフ時にも  $V_{depBG2} = OUT$  となるため、第 1 トランジスタ M214 がオンし、寄生バイポーラトランジスタ Q21～Q24 が動作し、オフ動作開始直後に急速に放電が進む。

#### 【0062】

ただし、OUT MOS100 のゲート電圧 GATE が電源電圧  $V_{CC}$  の電位付近まで低下すると、寄生バイポーラトランジスタ Q21～Q23 による OUT MOS100 のゲート電極から電源端子 102 への放電が止まり、寄生バイポーラトランジスタ Q24 のみがゲート電極の電荷 GATE を出力端子 103 へ放電し続ける。寄生バイポーラトランジスタ Q24 は増幅率が低いため、第 1 トランジスタ M214 の電流を大きく増幅しない。またトランジスタ M215 はゲートに OUT 電圧を受けてカットオフしているため、M215 による急速な放電は行われない。寄生バイポーラトランジスタ Q21～Q23 の放電が停止した後は寄生バイポーラトランジスタ Q24 とトランジスタ M211 によってスルーレートが決まるため、ターンオフ動作の途中からはスルーレートが抑制される。

40

#### 【0063】

寄生バイポーラトランジスタ Q21～Q24 の動作によりターンオフ初期はスルーレートが高いのでノイズが発生する可能性があるが、アプリケーションによっては特に問題に

50

ならない可能性もある。また、図4(c)の回路であれば、OUT-GNDX間に構成できる。

#### 【0064】

##### 実施の形態2

次に、本発明にかかる実施の形態2について説明する。上述の実施の形態1で述べたように、第2トランジスタM212の寄生バイポーラトランジスタQ21を利用して急速放電動作を実現したが、第2トランジスタM212のチャネル領域は放電動作に寄与しておらず、また寄生バイポーラトランジスタQ22～Q24によって構成される放電経路は、寄生バイポーラトランジスタQ21より電流増幅率が低い。そのため、第1トランジスタM214の電流は寄生バイポーラトランジスタQ22～Q24のベースに流さず、寄生バイポーラトランジスタQ21のベースに流すことが望ましい。そこで、本実施の形態においては、その点を改良する。

#### 【0065】

図5(a)は、本発明の実施の形態2にかかる放電回路を示す図である。なお、図5(a)に示す放電回路において、図2(b)に示す実施の形態1にかかる放電回路と同一の構成要素には、同一の符号を付しその詳細な説明は、省略する。

#### 【0066】

図5(a)に示す放電回路は、正常時のオフ動作を行う通常オフ回路10と、異常時に出力MOS100の急速オフを実行する急速オフ回路20cを有する。図2(a)と同様に、出力MOS100はN型のエンハンスマントトランジスタであり、そのドレインは電源端子102に接続され、そのソースは出力端子103に接続される。トランジスタM211とトランジスタM214はN型のデブレッショントランジスタであり、ゲート・ソースがショートされており、定電流源として動作する。トランジスタM215はN型のエンハンスマントトランジスタであり、そのソースは出力端子103に接続される。ダイオードD32はp<sup>+</sup>とn<sup>+</sup>とで構成される。寄生バイポーラトランジスタQ26は、ダイオードD32を追加することによって形成される。図5(a)におけるVdepBG1、VdepBG2、VenhGは制御信号であり、上述の図4(a)、(b)、(c)、(d)の各制御信号生成回路を使用して生成される。

#### 【0067】

図5(b)は、ダイオードD32を示す断面図である。寄生バイポーラトランジスタQ21は、ダイオードD32のカソードをコレクタとし、Pウェルをベースとし、N基板をエミッタとしている。

#### 【0068】

次に、本実施の形態にかかる放電回路の動作について説明する。本実施の形態における正常時のオフ動作は、実施の形態1のそれと同様である。

#### 【0069】

次に、異常検出時のオフ動作について示す。実施の形態1と同様、第1トランジスタM214はバックゲートにOUT電圧を受け、定電流として作用する。

#### 【0070】

第1の放電部の動作について説明する。第1トランジスタM214の電流は、寄生バイポーラトランジスタQ26のベース電流となる。寄生バイポーラトランジスタQ26は、第1トランジスタM214からの受けたベース電流をhfe1倍し、出力MOS100のゲート電荷を電源端子102に放電する。

#### 【0071】

次に、第2の放電部の動作について説明する。第1の放電部が出力MOS100のゲート電極の電荷を電源端子102へ放電すると、出力MOS100のゲート電位GATEが低下し始め、一定量のゲート電荷が放電されるとOUT電位が低下し始める。トランジスタM215は、VenhG = VCCをゲートに受けているため、出力端子103の電位が低下してトランジスタM215のゲート・ソース間電圧Vgs215 = VCC - OUT > Vthnとなるとオンし、放電に寄与する。さらにOUTが低下し、Vgs215 > Vd

10

20

30

40

50

s 2 1 5 - V t h n ( V C C - O U T ) > ( G A T E - O U T ) > V t h n となると、トランジスタ M 2 1 5 は線形領域で動作するため、大きな放電電流を流すことが出来るようになる。第 2 の放電部は、出力 M O S 1 0 0 のゲート電極の電位 G A T E を出力電圧 O U T の電位と等しくなるまで放電させる。

【 0 0 7 2 】

以上の異常検出時の動作をまとめると、ターンオフ動作初期は、第 1 放電部の第 1 トランジスタ M 2 1 4 の電流が全て寄生バイポーラトランジスタ Q 2 6 のベース電流となって、寄生バイポーラトランジスタ Q 2 6 が出力 M O S 1 0 0 のゲート電荷を電源端子 1 0 2 に放電し、出力 M O S 1 0 0 のゲート電荷を出力端子 1 0 3 に放電することで出力端子 1 0 3 の電位が低下する。次に、第 2 放電部を構成するトランジスタ M 2 1 5 がオンし、残りの出力 M O S 1 0 0 のゲート電荷を出力端子 1 0 3 に放電することで出力 M O S 1 0 0 がオフする。このように、第 1 放電部及び第 2 放電部により、ゲート電荷を放電するようにしたので、急速オフを実現することができる。

【 0 0 7 3 】

本実施の形態においては、実施の形態 1 のように、トランジスタ M 2 1 2 のような N 型エンハンスマントトランジスタを配置することで寄生バイポーラトランジスタを得るのではなく、図 2 ( b ) 中の寄生バイポーラトランジスタ Q 2 1 に相当するバイポーラトランジスタだけを生成できるように、p<sup>+</sup>、n<sup>+</sup> で構成されるダイオード D 3 2 を配置した。P ウェル中に形成されたダイオードを配置することで図 2 ( b ) に示した寄生バイポーラトランジスタ Q 2 1 と等価の寄生バイポーラトランジスタ Q 2 6 が得られ、実施の形態 1 と同様の効果が得られる。また、図 2 ( b ) で存在していたトランジスタ M 2 1 4 と出力端子 1 0 3 との間に存在していた経路がなくなるため、第 3 トランジスタ M 2 1 3 も不要になる。

【 0 0 7 4 】

実施の形態 2 においては、第 1 の放電経路において、第 1 トランジスタ M 2 1 4 の電流が全て寄生バイポーラトランジスタ Q 2 6 のベース電流となるため、第 1 トランジスタ M 2 1 4 の電流が全て h f e 1 倍増幅される。したがって、実施の形態 1 より放電電流を大きくすることが可能となる。また、図 2 ( b ) の第 3 トランジスタ M 2 1 3 や、図 3 ( a ) に示したトランジスタのチャネル領域や寄生バイポーラトランジスタ Q 2 3 を生成していた n<sup>+</sup> 領域が不要となるため、より小さな面積で急速オフ回路を実現することができる。

【 0 0 7 5 】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、図 6 ( a ) は、本発明の実施の形態に係る他のシステムを示すブロック図である。図 1 ( a ) に示すハイサイド出力回路は、G N D 端子 1 0 6 を有していないが、図 6 ( a ) に示す本実施の形態にかかるハイサイド出力回路は、G N D 端子を有している。このような G N D 端子を有する回路であっても、上述と同様の放電回路により、出力 M O S の急速オフ動作を実現することができる。ここで、図 6 ( a ) に示すハイサイド出力回路は、G N D 端子を有するため、図 4 に示す各回路は、入力電圧 I N の代わりに G N D 電位を使用することができる。

【 符号の説明 】

【 0 0 7 6 】

- 1 ハイサイド出力回路

- 2 内部電源

- 3 制御部

- 4 昇圧回路

- 5 放電回路

- 6 電流センサ

- 7 電圧センサ

- 8 溫度センサ

10

20

30

40

50

9 ハイサイド出力回路

10 通常時の放電回路

20 a、20 b、20 c 放電回路

100 出力MOSトランジスタ

101 入力端子

102 電源端子

103 出力端子

106 GND端子 M211 N型のデプレッショントランジスタ

M212 N型のエンハンスマントトランジスタ

M213 P型のエンハンスマントトランジスタ 10

M214 N型のデプレッショントランジスタ

M215 N型のエンハンスマントトランジスタ

VdepBG1、VdepBG2、VenhG 制御信号

Q21～Q26 寄生バイポーラトランジスタ

Pウェル P型の領域

N基盤 N型の基盤領域

S<sub>IN</sub> 入力信号

S<sub>IN\_B</sub> 入力反転信号

OC 異常検出信号

S スイッチ

301 制御信号入力回路 20

302 昇圧回路

303 RISEレート

304 状態判定回路

Q1、Q2 N型のデプレッショントランジスタ

Q3 N型のエンハンスマントトランジスタ

【図1】

【図2】

【図3】

【図4】

【図5】

|                       |            |                     |

|-----------------------|------------|---------------------|

| VdepBG1               | VenhG      | VdepBG2             |

| 正常オン時: GNDX+ $\alpha$ | 正常オン時: OUT | 正常オン時: IN+ $\alpha$ |

| 正常オフ時: OUT            | 正常オフ時: OUT | 正常オフ時: IN+ $\alpha$ |

| 異常検出時: OUT+ $\alpha$  | 異常検出時: VCC | 異常検出時: OUT          |

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開2008-172940(JP,A)

特開2005-123666(JP,A)

特開平03-166816(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00 - 17/70