(12)发明专利

(10)授权公告号 CN 108220882 B

(45)授权公告日 2020.06.30

(21)申请号 201711281075.1

(74)专利代理机构 北京同立钧成知识产权代理

(22)申请日 2017.12.06

有限公司 11205

(65)同一申请的已公布的文献号

代理人 杨贝贝 岌建明

申请公布号 CN 108220882 A

(51) Int.CI.

C23C 14/16(2006.01)

(43)申请公布日 2018.06.29

C23C 14/34(2006.01)

(30)优先权数据

H05K 9/00(2006.01)

2016-240856 2016.12.13 JP

(56)对比文件

2017-227203 2017.11.27 JP

CN 105463386 A, 2016.04.06,

(73)专利权人 芝浦机械电子装置株式会社

CN 1450604 A, 2003.10.22,

地址 日本神奈川县横浜市荣区笠间二丁目

US 2004/0047108 A1, 2004.03.11,

5番1号(邮递区号:247-8610)

CN 101803460 A, 2010.08.11,

(72)发明人 伊藤昭彦 加茂克尚 松中繁树

审查员 马婧

藤田笃史

权利要求书1页 说明书17页 附图7页

(54)发明名称

成膜装置

(57)摘要

本发明提供一种可以简单的构成抑制电子零件的加热的成膜装置。本发明包括：搬送部，在腔室内循环搬送电子零件；成膜处理部，成膜于电子零件；托盘，由搬送部搬送，具有载置面；及载置部，载置于载置面，用来搭载电子零件，载置部包括：保持片，一面具备具有粘着性的粘着面，另一面具备不具有粘着性的非粘着面；及密接片，一面具备密接于非粘着面的具有粘着性的第1密接面，另一面具备密接于托盘的载置面的具有粘着性的第2密接面，粘着面具有用来贴附电子零件的贴附区域，第1密接面至少跨及与贴附区域对应的非粘着面的区域的整体而密接。

35

1. 一种成膜装置,其特征在于包括:

腔室,其为供溅射气体导入的容器;

成膜处理部,设置于所述腔室内,具有通过溅射而使成膜材料堆积来进行成膜的溅射源,并且通过所述溅射源而成膜于多个电子零件;

托盘,设置于所述成膜处理部的处理区域,具有载置面;及

载置部,载置于所述载置面,用来搭载所述多个电子零件,

所述载置部包括:

保持片,一面具备具有粘着性的粘着面,另一面具备不具有粘着性的非粘着面;及

密接片,一面具备密接于所述非粘着面的具有粘着性的第1密接面,另一面具备密接于所述托盘的载置面的具有粘着性的第2密接面,

所述粘着面具有用来贴附所述多个电子零件的贴附区域,贴附有对所述贴附区域的外缘的一部分或全部进行规定的框架,所述第1密接面至少跨及与所述贴附区域对应的非粘着面的区域的整体而密接,

若将所述第1密接面与所述非粘着面的接着力设为Fa、将所述第2密接面与所述载置面的接着力设为Fb,则为Fa<Fb。

2. 一种成膜装置,其特征在于包括:

腔室,其为供溅射气体导入的容器;

搬送部,设置于所述腔室内,循环搬送多个电子零件;

成膜处理部,具有通过溅射而使成膜材料堆积于由所述搬送部循环搬送的所述多个电子零件来进行成膜的溅射源,并且通过所述溅射源而成膜于所述多个电子零件;

托盘,由所述搬送部搬送,具有载置面;及

载置部,载置于所述载置面,用来搭载所述多个电子零件,

所述载置部包括:

保持片,一面具备具有粘着性的粘着面,另一面具备不具有粘着性的非粘着面;及

密接片,一面具备密接于所述非粘着面的具有粘着性的第1密接面,另一面具备密接于所述托盘的载置面的具有粘着性的第2密接面,

所述粘着面具有用来贴附所述多个电子零件的贴附区域,贴附有对所述贴附区域的外缘的一部分或全部进行规定的框架,所述第1密接面至少跨及与所述贴附区域对应的非粘着面的区域的整体而密接,

若将所述第1密接面与所述非粘着面的接着力设为Fa、将所述第2密接面与所述载置面的接着力设为Fb,则为Fa<Fb。

3. 根据权利要求1或2所述的成膜装置,其特征在于:所述第1密接面除了与所述贴附区域对应的非粘着面的区域的整体以外,还进而密接于与所述框架对应的非粘着面的区域。

4. 根据权利要求1或2所述的成膜装置,其特征在于:所述密接片是由所述第1密接面相对于所述非粘着面的剥离阻力小于所述第2密接面相对于所述载置面的剥离阻力的材质形成。

5. 根据权利要求1或2所述的成膜装置,其特征在于:所述密接片的热传导率为0.1W/(m•K)以上。

## 成膜装置

### 技术领域

[0001] 本发明是涉及一种成膜装置。

### 背景技术

[0002] 以移动电话为代表的无线通信设备中,搭载有许多作为电子零件的半导体装置。为了防止对通信特性的影响,半导体装置谋求抑制电磁波向外部的泄露等电磁波对内外的影响。因此,一直使用具有对电磁波的屏蔽功能的半导体装置。

[0003] 一般而言,半导体基板是通过在作为用于对安装基板进行中转的基板的中介层(interposer)基板上搭载半导体芯片,并利用树脂将所述半导体芯片密封而形成。开发有一种通过在所述密封树脂的上表面及侧面设置导电性的电磁波屏蔽膜而赋予屏蔽功能的半导体装置(参照专利文献1)。

[0004] 此种电磁波屏蔽膜可设为多种金属材料的层叠膜。例如,已知有在形成有不锈钢(SUS)膜的基础上形成Cu膜,进而在其上形成SUS膜的层叠结构的电磁波屏蔽膜。

[0005] 关于电磁波屏蔽膜,为了获得充分的屏蔽效果,需要降低电阻率。因此,对电磁波屏蔽膜要求某种程度的厚度。关于半导体装置,一般而言,若为 $1\mu\text{m} \sim 10\mu\text{m}$ 左右的膜厚,则可获得良好的屏蔽特性。就所述SUS、Cu、SUS的层叠结构的电磁波屏蔽膜而言,已知若为 $1\mu\text{m} \sim 5\mu\text{m}$ 左右的膜厚,则可获得良好的屏蔽效果。

[0006] 现有技术文献

[0007] 专利文献

[0008] 专利文献1国际公开第2013/035819号公报

### 发明内容

[0009] 发明所要解决的问题

[0010] 作为电磁波屏蔽膜的形成方法,已知有镀敷法。但是,镀敷法需要前处理步骤、镀敷处理步骤、及水洗之类的后处理步骤等湿式步骤,因此不可避免半导体装置的制造成本的上升。

[0011] 因此,作为干式步骤的溅射法受到瞩目。作为利用溅射法的成膜装置,提出有使用等离子体进行成膜的等离子体处理装置。等离子体处理装置将惰性气体导入配置有靶材的真空容器,施加直流电压。使经等离子体化的惰性气体的离子与成膜材料的靶材碰撞,并使自靶材赶出的材料堆积于工件来进行成膜。

[0012] 一般的等离子体处理装置被用于可在几十秒至几分钟的处理时间内形成的厚度为 $10\text{nm} \sim \text{数}100\text{nm}$ 的膜的形成中。但是,如上所述,作为电磁波屏蔽膜,需要形成微米级厚度的膜。由于溅射法是使成膜材料的粒子堆积于成膜对象物上来形成膜的技术,因此所形成的膜越厚,膜的形成所需的时间越长。

[0013] 因此,为了形成电磁波屏蔽膜,需要比一般的溅射法更长的几十分钟至一小时左右的处理时间。例如,就SUS、Cu、SUS的层叠结构的电磁波屏蔽膜而言,为了获得 $5\mu\text{m}$ 的膜厚,

有时需要一小时多的处理时间。

[0014] 如此,使用等离子体的溅射法中,在所述处理时间内,作为半导体装置的外包装的封装体会一直暴露于等离子体的热中。结果,至获得厚度5μm的膜为止,有时会将封装体加热至200℃上下。

[0015] 另一方面,关于封装体的耐热温度,若为几秒~几十秒左右的暂时加热,则为200℃左右,但在加热超过几分钟的情况下,一般为150℃左右。因此,难以使用一般的利用等离子体的溅射法来形成微米级的电磁波屏蔽膜。

[0016] 为了应对所述情况,考虑在等离子体处理装置上设置用来抑制半导体封装体的温度上升的冷却装置。所述情况下,装置构成复杂化、大型化。

[0017] 本发明的目的在于提供一种可以简单的构成抑制电子零件的加热的成膜装置。

[0018] 解决问题的技术手段

[0019] 为了达成所述目的,本发明包括:腔室,其为供溅射气体导入的容器;成膜处理部,设置于所述腔室内,具有通过溅射而使成膜材料堆积来进行成膜的溅射源,并且通过所述溅射源而成膜于电子零件;托盘,设置于所述成膜处理部的处理区域,具有载置面;及载置部,载置于所述载置面,用来搭载所述电子零件,所述载置部包括:保持片,一面具备具有粘着性的粘着面,另一面具备不具有粘着性的非粘着面;及密接片,一面具备密接于所述非粘着面的具有粘着性的第1密接面,另一面具备密接于所述托盘的载置面的具有粘着性的第2密接面,所述粘着面具有用来贴附所述电子零件的贴附区域,所述第1密接面至少跨及与所述贴附区域对应的非粘着面的区域的整体而密接。

[0020] 另外,本发明包括:腔室,其为供溅射气体导入的容器;搬运部,设置于所述腔室内,循环搬运电子零件;成膜处理部,具有通过溅射而使成膜材料堆积于由所述搬运部循环搬运的所述电子零件来进行成膜的溅射源,并且通过所述溅射源而成膜于电子零件;托盘,由所述搬运部搬运,具有载置面;及载置部,载置于所述载置面,用来搭载所述电子零件,所述载置部包括:保持片,一面具备具有粘着性的粘着面,另一面具备不具有粘着性的非粘着面;及密接片,一面具备密接于所述非粘着面的具有粘着性的第1密接面,另一面具备密接于所述托盘的载置面的具有粘着性的第2密接面,所述粘着面具有用来贴附所述电子零件的贴附区域,所述第1密接面至少跨及与所述贴附区域对应的非粘着面的区域的整体而密接。

[0021] 在所述保持片的粘着面贴附有对所述贴附区域的外缘的一部分或全部进行规定的金属制的框架,所述第1密接面除了与所述贴附区域对应的非粘着面的区域的整体以外,还可进而密接于与所述框架对应的非粘着面的区域。

[0022] 若将所述第1密接面与所述非粘着面的接着力设为Fa、将所述第2密接面与所述载置面的接着力设为Fb,则可为Fa<Fb。

[0023] 所述密接片可由所述第1密接面相对于所述非粘着面的剥离阻力小于所述第2密接面相对于所述载置面的剥离阻力的材质形成。

[0024] 所述密接片的热传导率可为0.1W/(m·K)以上。

[0025] 发明的效果

[0026] 根据本发明,可提供一种可以简单的构成抑制电子零件的加热的成膜装置。

## 附图说明

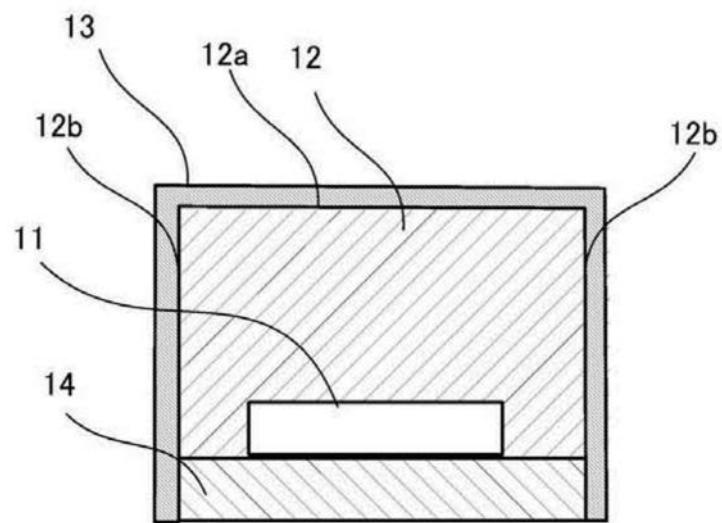

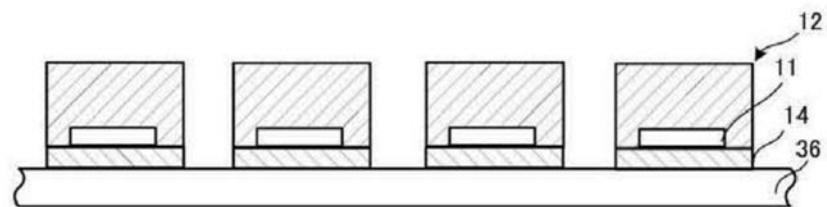

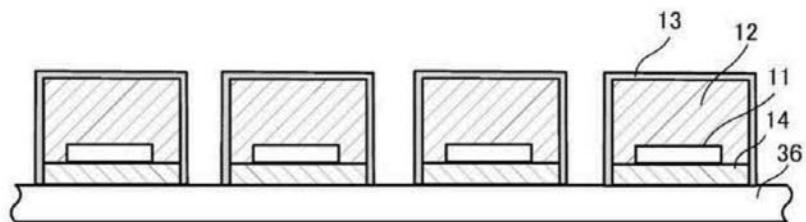

- [0027] 图1是表示实施方式的电子零件的示意剖面图。

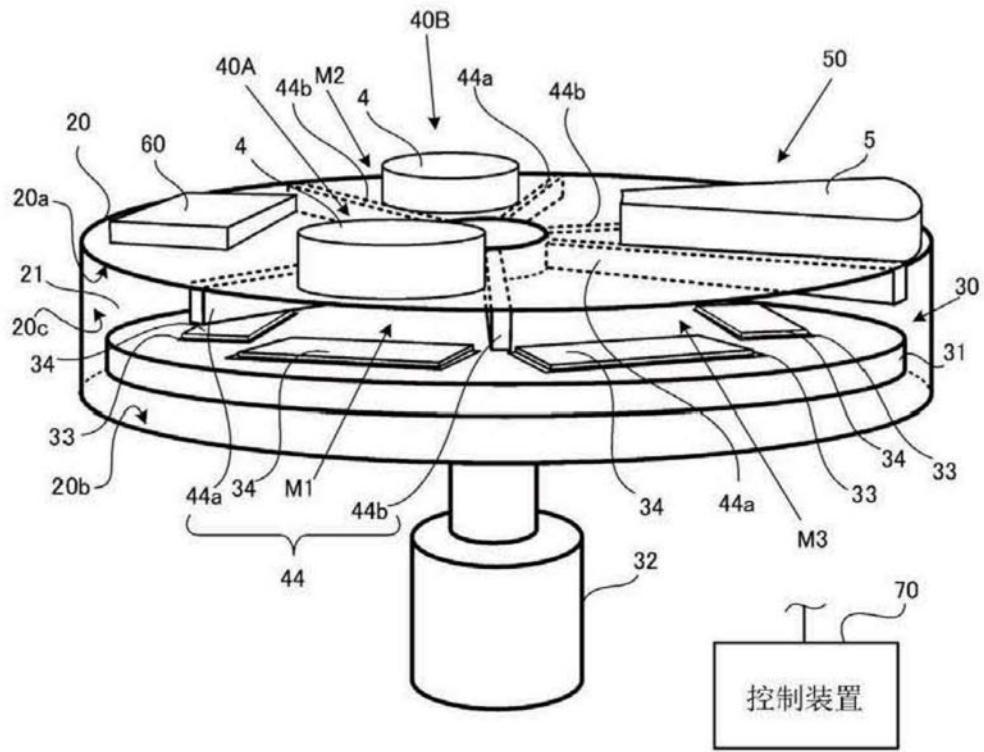

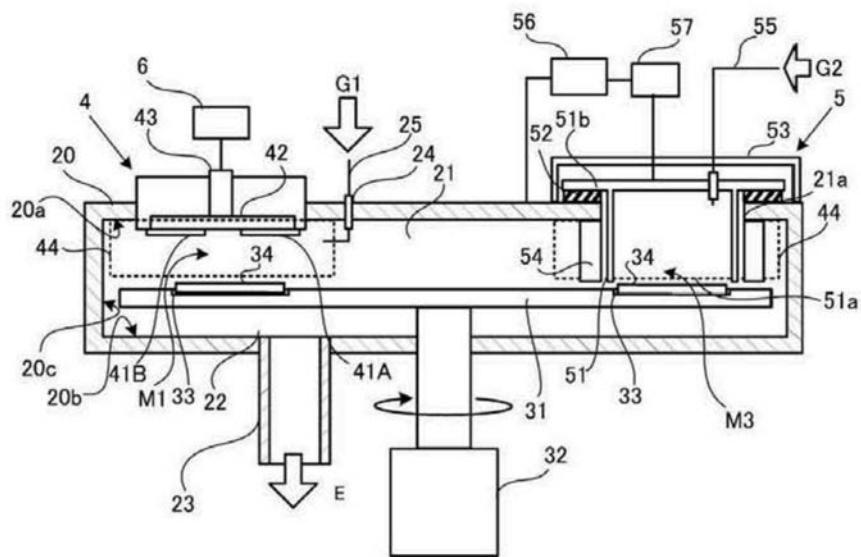

- [0028] 图2是实施方式的成膜装置的透视立体图。

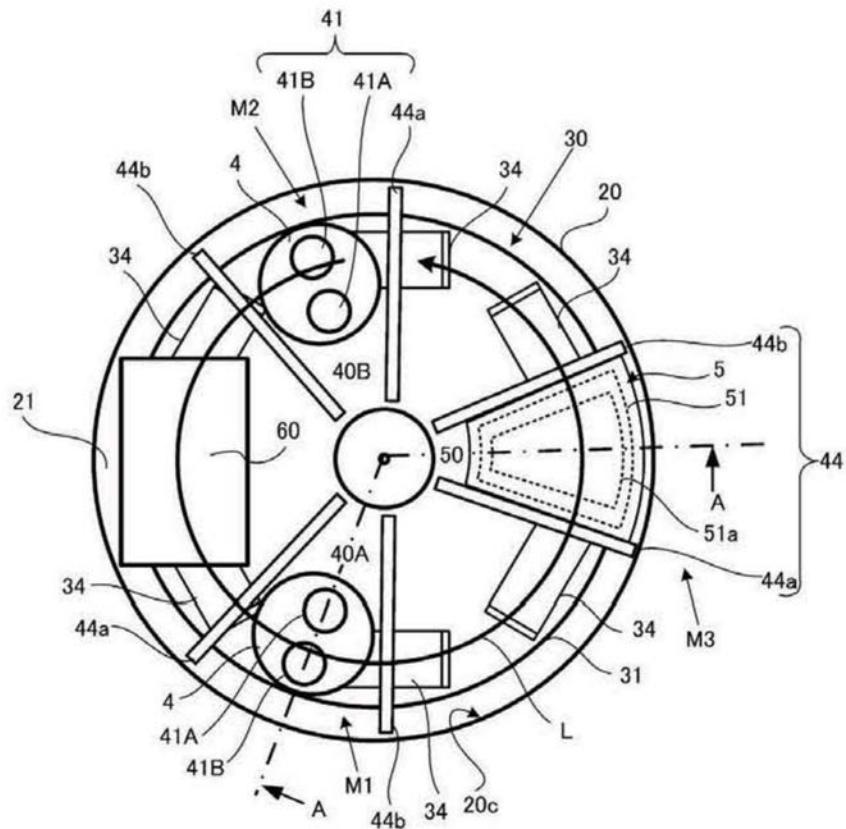

- [0029] 图3是实施方式的成膜装置的透视平面图。

- [0030] 图4是图3的A-A示意纵剖面图。

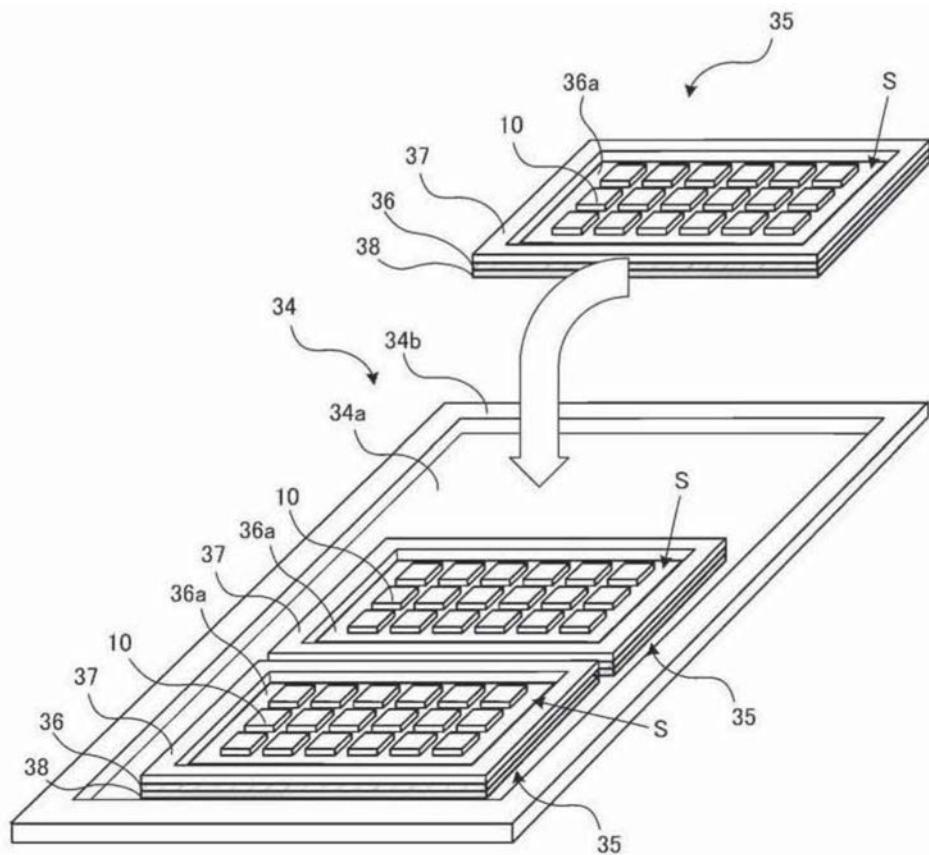

- [0031] 图5是表示配置有电子零件的托盘的立体图。

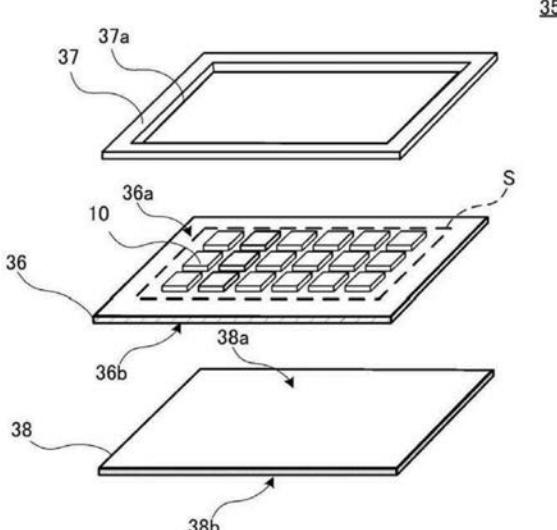

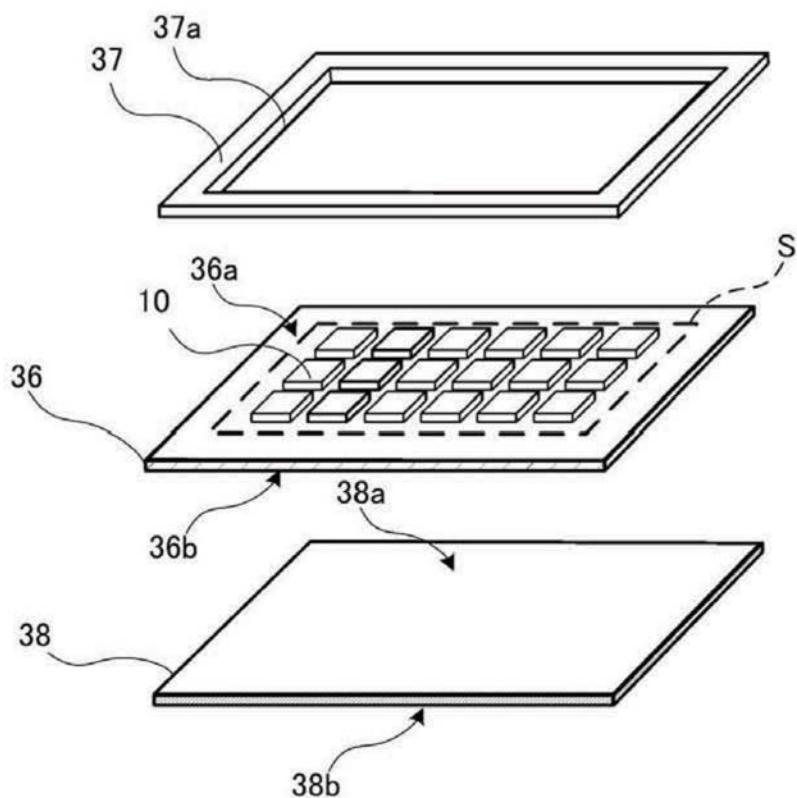

- [0032] 图6是表示载置部的构成的分解立体图。

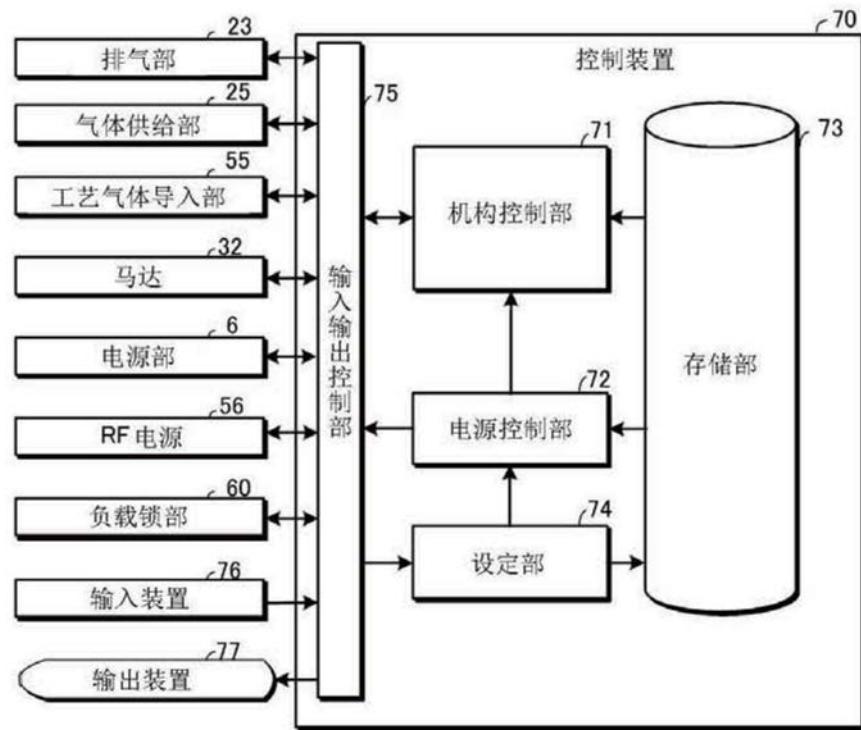

- [0033] 图7是表示实施方式的控制装置的方块图。

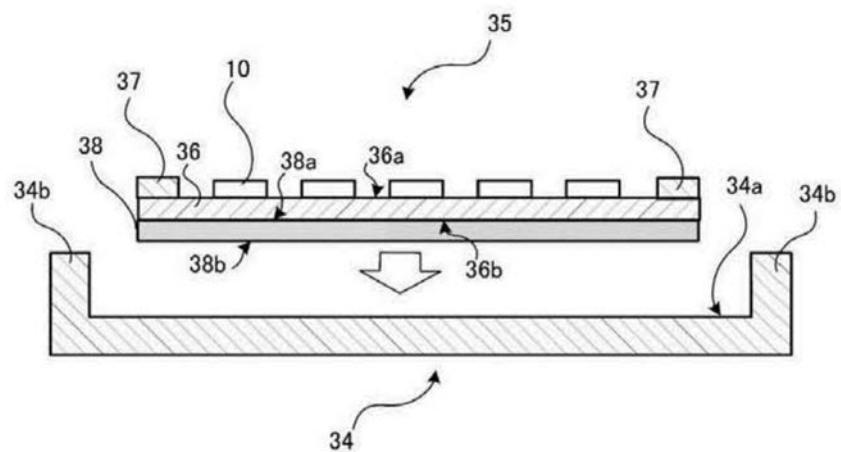

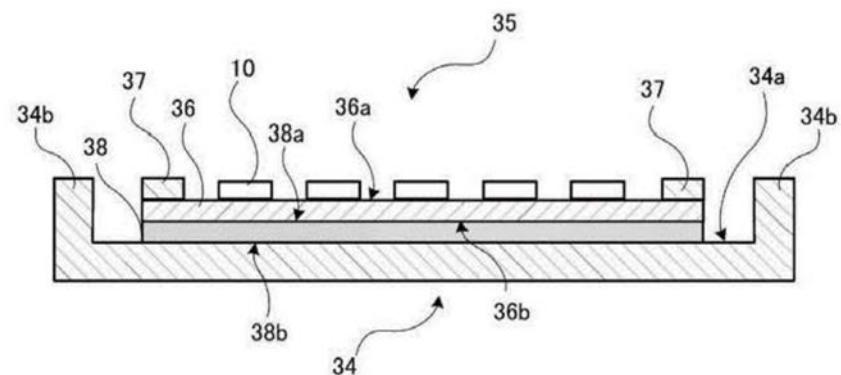

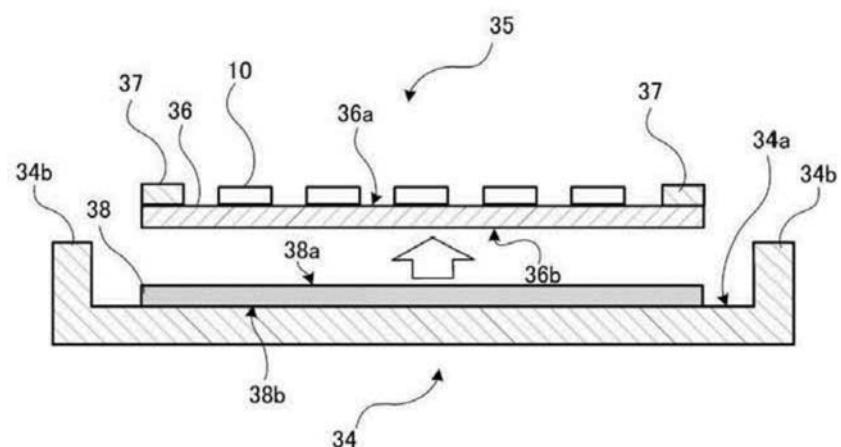

- [0034] 图8(a)～图8(c)是表示载置部对于托盘的载置与密接片的分离的说明图。

- [0035] 图9(a)～图9(b)是表示对于电子零件的成膜的说明图。

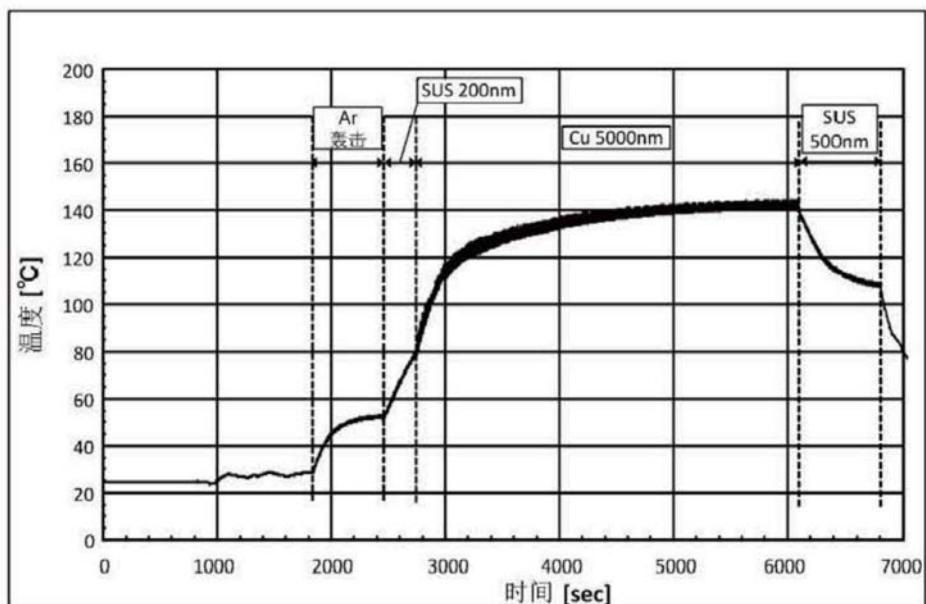

- [0036] 图10是表示比较例的随着时间的经过的温度变化的图表。

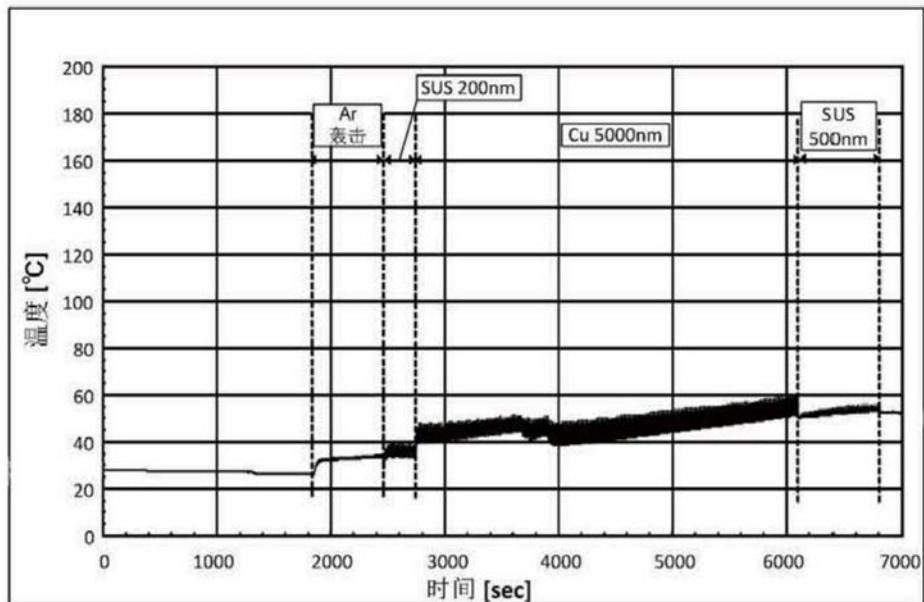

- [0037] 图11是表示实施例的随着时间的经过的温度变化的图表。

- [0038] 符号的说明

- [0039] 10:电子零件

- [0040] 11:元件

- [0041] 12:封装体

- [0042] 12a:顶面

- [0043] 12b:侧面

- [0044] 13:电磁波屏蔽膜

- [0045] 14:基板

- [0046] 100:成膜装置

- [0047] 20:腔室

- [0048] 20a:顶板

- [0049] 20b:内底面

- [0050] 20c:内周面

- [0051] 21:真空室

- [0052] 21a:开口

- [0053] 22:排气口

- [0054] 23:排气部

- [0055] 24:导入口

- [0056] 25:气体供给部

- [0057] 30:搬送部

- [0058] 31:旋转台

- [0059] 32:马达

- [0060] 33:保持部

- [0061] 34:托盘

- [0062] 34a:载置面

- [0063] 34b:周壁部

- [0064] 35:载置部

- [0065] 36:保持片

- [0066] 36a:粘着面

- [0067] 36b:非粘着面

- [0068] 37:框架

- [0069] 37a:贯通孔

- [0070] 38:密接片

- [0071] 38a:第1密接面

- [0072] 38b:第2密接面

- [0073] 40、40A、40B:成膜处理部

- [0074] 4:溅射源

- [0075] 41、41A、41B:靶材

- [0076] 42:背板

- [0077] 43:电极

- [0078] 44:划分部

- [0079] 44a、44b:壁板

- [0080] 5:处理单元

- [0081] 50:表面处理部

- [0082] 51:筒形电极

- [0083] 51a:开口部

- [0084] 51b:凸缘

- [0085] 52:绝缘构件

- [0086] 53:外壳

- [0087] 54:屏蔽体

- [0088] 55:工艺气体导入部

- [0089] 56:RF电源

- [0090] 57:匹配盒

- [0091] 6:电源部

- [0092] 60:负载锁部

- [0093] 70:控制装置

- [0094] 71:机构控制部

- [0095] 72:电源控制部

- [0096] 73:存储部

- [0097] 74:设定部

- [0098] 75:输入输出控制部

- [0099] 76:输入装置

- [0100] 77:输出装置

- [0101] E:排气

- [0102] L:搬送路径

- [0103] M、M1、M2:成膜部位

- [0104] M3:处理部位

- [0105] G:反应气体

- [0106] G1:溅射气体

- [0107] G2:工艺气体

- [0108] S:贴附区域

- [0109] A-A:示意纵剖面方向

## 具体实施方式

- [0110] 参照附图对本发明的实施方式(以下,称为本实施方式)进行具体说明。

- [0111] 电子零件

- [0112] 如图1所示,本实施方式的成为成膜对象的电子零件10具有密封元件11的封装体12。元件11为半导体芯片、二极管、晶体管、电容器、表面声波(Surface Acoustic Wave, SAW)滤波片等表面安装零件。以下的说明中,以将半导体芯片作为元件11的一例进行说明。此处所述的半导体芯片是作为将多个电子元件集成化的集成电路而构成者。

- [0113] 元件11搭载于基板14的表面。基板14在包含陶瓷、玻璃、环氧树脂等的板的表面形成有电路图案。元件11与电路图案通过焊料而连接。

- [0114] 对基板14的安装有元件11的表面以覆盖元件11的方式利用合成树脂进行密封,由此构成封装体12。封装体12的形状为大致长方体形状。

- [0115] 本实施方式中,在如上所述的电子零件10的顶面12a及侧面12b形成电磁波屏蔽膜13。电磁波屏蔽膜13是由导电性的材料形成的遮蔽电磁波的膜。为了获得屏蔽效果,电磁波屏蔽膜13只要至少形成于封装体12的顶面12a即可。原因在于:侧面12b的电磁波屏蔽膜13接地。此外,封装体12的顶面12a是与安装于制品的面相反的一侧的外表面。

- [0116] 在水平载置的情况下,顶面12a成为位于最高位置的上表面,但在进行安装时,有朝向上方的情况,也有不朝向上方的情况。侧面12b是相对于顶面12a而以不同的角度形成的外周面。顶面12a与侧面12b之间可形成角,也可通过曲面而连续。

- [0117] 成膜装置

- [0118] 参照图2~图7对本实施方式的成膜装置100进行说明。成膜装置100是通过溅射而在各个电子零件10的封装体的12的外表面形成电磁波屏蔽膜13的装置。如图2所示,成膜装置100是如下装置:若旋转台31旋转,则保持部33所保持的托盘34上的电子零件10以圆周的轨迹移动,在经过与溅射源4对向的位置时,使自靶材41(参照图3)溅射的粒子附着来进行成膜。

- [0119] 如图2及图3所示,成膜装置100包括:腔室20、搬送部30、成膜处理部40A、成膜处理部40B、表面处理部50、负载锁部60、控制装置70。

- [0120] 腔室

- [0121] 腔室20是供反应气体G导入的容器。反应气体G包含溅射用的溅射气体G1、各种处理用的工艺气体G2(参照图4)。以下的说明中,在不对溅射气体G1、工艺气体G2加以区别的情况下,有时称为反应气体G。溅射气体G1是用来利用通过施加电力而产生的等离子体,使所产生的离子等与靶材41碰撞而对电子零件10的封装体12实施溅射的气体。例如,可将氩气等惰性气体用作溅射气体G1。

[0122] 工艺气体G2是用来进行利用蚀刻或灰化的表面处理的气体。以下,有时将此种表面处理称为逆溅射。工艺气体G2可根据处理的目的而适当变更。例如,在进行蚀刻的情况下,可使用氩气等惰性气体作为蚀刻气体。在本实施方式中,利用氩气来进行电子零件10的表面的清洗与粗面化处理。例如,通过对表面进行清洗及以纳米级进行粗面化处理,可提高膜的密接力。

[0123] 腔室20的内部空间形成真空室21。所述真空室21是具有气密性、可通过减压而设为真空的空间。例如,如图2及图4所示,真空室21是由腔室20的内部的顶板20a、内底面20b及内周面20b形成的圆柱形状的密闭空间。

[0124] 如图4所示,腔室20具有排气口22、导入口24。排气口22是用来确保真空室21与外部之间的气体流通而进行排气E的开口。所述排气口22例如形成于腔室20的底部。在排气口22处连接有排气部23。排气部23具有配管及未图示的泵、阀等。通过利用所述排气部23的排气处理,而将真空室21内减压。

[0125] 导入口24是用来将溅射气体G1导入至真空室21的靶材41附近的开口。在所述导入口24处连接有气体供给部25。对各靶材41各设置有一个气体供给部25。另外,除了配管以外,气体供给部25还具有未图示的反应气体G的气体供给源、泵、阀等。通过所述气体供给部25而将溅射气体G1自导入口24导入至真空室21内。此外,如后述,在腔室20的上部设置有供表面处理部50插入的开口21a。

#### [0126] 搬送部

[0127] 搬送部30设置于腔室20内,是以圆周的轨迹循环搬送电子零件10的装置。循环搬送是指使搭载有电子零件10的托盘34以圆周的轨迹环绕移动。将通过搬送部30而托盘34进行移动的轨迹称为搬送路径L。搬送部30具有旋转台31、马达32、保持部33。另外,保持部33保持搭载有载置部35的托盘34。

[0128] 旋转台31是圆形的板。马达32是对旋转台31提供驱动力并使其以圆的中心为轴进行旋转的驱动源。保持部33是保持由搬送部30搬送的后述的托盘34的构成部。在旋转台31的顶面,多个保持部33配设于圆周等配位置。例如,各保持部33保持托盘34的区域是以与旋转台31的圆周方向的圆的切线平行的朝向来形成,且在圆周方向上等间隔地设置。更具体而言,保持部33是保持托盘34的槽、孔、凸起、夹具、固定器等。可通过机械吸盘(mechanical chuck)、粘着吸盘来构成。

[0129] 如图5所示,托盘34是具有平坦的载置面34a的构件。载置面34a是方形状的平板的一平面。在载置面34a的周缘部形成有周壁部34b。周壁部34b是呈包围载置面34a的方形状隆起的框。作为托盘34的材质,优选为设为热传导性高的材质、例如金属。本实施方式中,将托盘34的材质设为不锈钢(SUS)。此外,托盘34的材质例如也可设为热传导性佳的陶瓷或树脂或者这些的复合材。

[0130] 载置部35载置于托盘34的载置面34a,是用来搭载电子零件10的构件。载置部35具有保持片36、框架37、密接片38。如图6所示,保持片36是平坦的片,且一面具备具有粘着性的粘着面36a。粘着面36a遍及保持片36的一面的整体。粘着面36a具有用来贴附电子零件10的贴附区域S。本实施方式中,保持片36是方形,贴附区域S是小于保持片36的外缘的方形状的区域。但是,也可将贴附区域S设为保持片36的整个面。保持片36的另一面是不具有粘着性的非粘着面36b。非粘着面36b例如可设为具有圆滑性的面。

[0131] 框架37贴附于保持片36的粘着面36a，是划出贴附区域S的外缘的一部分或全部的构件。作为框架37的材质，优选为设为热传导性高的材质、例如金属。本实施方式中，将框架37的材质设为SUS。此外，也可与托盘34同样地将框架37的材质例如设为热传导性佳的陶瓷或树脂或者这些的复合材。托盘34的材质与框架37的材质可一致，也可不同。本实施方式的框架37包围贴附区域S而规定贴附区域S的外缘的全部。框架37是方形状的板状构件，且在中央处形成有方形状的贯通孔37a。所述贯通孔37a的内缘与贴附区域S的外缘一致。框架37的外形与保持片36的外形一致。

[0132] 保持片36的粘着面36a在框架37的底面以彼此的外形一致而堵塞贯通孔37a的底面侧的方式被贴附。因此，粘着面36a的贴附区域S自框架37的顶面侧的贯通孔37a露出。

[0133] 如图5及图6所示，多个电子零件10粘着保持于框架37内的所露出的贴附区域S上。多个电子零件10不仅在顶面12a，而且也在侧面12b以形成膜的方式空出间隔而呈矩阵状整列配置。

[0134] 如图6所示，密接片38是平坦的片，且一面具有第1密接面38a，另一面具有第2密接面38b。第1密接面38a是密接于保持片36的非粘着面36b的具有粘着性的面。第1密接面38a至少跨及与贴附区域S对应的非粘着面36b的区域的整体而密接。所谓与贴附区域S对应的非粘着面36b的区域，是指成为贴附区域S的正后面的非粘着面36b的区域。另外，第1密接面38a也密接于与框架37对应的非粘着面36b的区域。即，第1密接面38a在也扩及至成为框架37的正后面的非粘着面36b的区域的范围内密接。本实施方式中，框架37、保持片36、密接片38的外形尺寸一致。

[0135] 第2密接面38b是密接于托盘34的载置面34a的具有粘着性的面。本实施方式中，框架37、保持片36、密接片38全部是以外形一致的方式层叠，第2密接面38b整体密接于托盘34。

[0136] 此处，若将第1密接面38a与保持片36的非粘着面36b的接着力设为Fa、将第2密接面38b与托盘34的载置面34a的接着力设为Fb，则为Fa<Fb。此外，例如优选为设为 $2 \leq (Fb - Fa)$ 。另外，可由保持片36的非粘着面36b相对于第1密接面38a的剥离阻力小于托盘34的载置面34a相对于第2密接面38b的剥离阻力的材质形成。例如，优选为将Fa设为0.02 (N/宽度25mm) ~ 0.03 (N/宽度25mm)、将Fb设为4 (N/宽度25mm) ~ 7 (N/宽度25mm)。但是，本发明并不限于这些值。另外，密接片38优选为将热传导率设为0.1W/(m·K)以上。此外，热传导率越高越佳，但只要有1W/(m·K)左右，则可获得良好的冷却效果。

[0137] 作为保持片36、密接片38的材质，考虑设为具有耐热性的合成树脂。例如，可使用聚对苯二甲酸乙二酯(Polyethylene Terephthalate, PET)、聚萘二甲酸乙二酯(Polyethylene Naphthalate, PEN)、聚酰亚胺(Polyimide, PI)等，但并不限于这些。关于粘着面36a、第1密接面38a、第2密接面38b，考虑相对于片表面应用接着剂或设为使表面产生接着性的接着面。作为接着剂或接着面的材质，例如可使用硅酮系、丙烯酸系的树脂以及胺基甲酸酯树脂、环氧树脂等具有接着性的各种材料。

[0138] 如图5及图6所示，多个电子零件10呈矩阵状贴附于载置部35的粘着面36a的贴附区域S内。准备多个此种载置部35，经由密接片38而载置于托盘34的载置面34a，由此使密接片38的第2密接面38b密接于载置面34a。但是，载置部35也可单一载置于托盘34。

[0139] 如此，通过保持部33所保持的托盘34、载置部35、密接片38而将电子零件10定位于

旋转台31上。此外,本实施方式中,设置有六个保持部33,因此在旋转台31上以60°的间隔来保持六个托盘34。但是,保持部33可为一个,也可为多个。

[0140] 成膜处理部

[0141] 成膜处理部40A、成膜处理部40B是对由搬送部30搬送的电子零件10进行成膜的处理部。以下,在不对多个成膜处理部40A、成膜处理部40B加以区别的情况下,以成膜处理部40的形式进行说明。如图4所示,成膜处理部40具有溅射源4、划分部44、电源部6。

[0142] (溅射源)

[0143] 溅射源4是通过溅射而使成膜材料堆积于电子零件10来进行成膜的成膜材料的供给源。溅射源4具有靶材41、背板(backing plate)42、电极43。靶材41是由堆积于电子零件10来成为膜的成膜材料形成,与搬送路径L隔开而设置于对向的位置。关于本实施方式的靶材41,如图3所示,两个靶材41A、靶材41B在与搬送方向正交的方向即旋转台31的旋转的半径方向上排列。以下,在不对靶材41A、靶材41B加以区别的情况下,设为靶材41。靶材41的底面侧与通过搬送部30进行移动的电子零件10隔开且对向。此外,作为可通过两个靶材41A、靶材41B而使成膜材料附着的执行区域的处理区域的大小大于旋转台31的径方向上的托盘34的大小。

[0144] 如后所述,成膜材料例如使用Cu、Ni、Fe、SUS等。但是,若为通过溅射进行成膜的材料,则可应用各种材料。另外,靶材41例如为圆柱形状。但是,也可为长圆柱形状、角柱形状等其他形状。

[0145] 背板42是保持靶材41的构件。电极43是用来自腔室20的外部对靶材41施加电力的导电性构件。此外,溅射源4中视需要而适当具备磁铁、冷却机构等。

[0146] (划分部)

[0147] 划分部44是对利用溅射源4使电子零件10成膜的成膜部位M1、成膜部位M2、进行表面处理的处理部位M3加以划分的构件。以下,在不对成膜部位M1、成膜部位M2加以区别的情况下,以成膜部位M的形式进行说明。如图3所示,划分部44具有自搬送路径L的圆周的中心、即搬送部30的旋转台31的旋转中心,呈放射状配设的方形的壁板44a、壁板44b。壁板44a、壁板44b例如在夹隔靶材41的位置设置于真空室21的顶板。划分部44的下端空出电子零件10经过的空隙,与旋转台31对向。通过存在所述划分部44,而可抑制反应气体G及成膜材料扩散至真空室21。

[0148] 成膜部位M包含溅射源4的靶材41,是由划分部44所划分的空间。更具体而言,如图3所示,自平面方向来看,成膜部位M1、成膜部位M2、处理部位M3是由划分部44的壁板44a、壁板44b与腔室20的内周面20c所包围的扇形空间。成膜部位M1、成膜部位M2、处理部位M3的水平方向的范围成为由一对壁板44a、壁板44b所划分的区域。此外,成膜材料以膜的形式堆积于经过成膜部位M中的与靶材41对向的位置的电子零件10。所述成膜部位M是进行大部分成膜的区域,但即便是超出成膜部位M的区域,也会有来自成膜部位M的成膜材料的泄露,因此并非完全没有膜的堆积。即,进行成膜的处理区域成为稍微广于成膜部位M的区域。

[0149] (电源部)

[0150] 电源部6是对靶材41施加电力的构成部。通过利用所述电源部6对靶材41施加电力,而使溅射气体G1等离子体化,可使成膜材料堆积于电子零件10。在本实施方式中,电源部6例如是施加高电压的直流(Direct Current, DC)电源。此外,在为进行高频溅射的装置

的情况下,也可设为射频(Radio Frequency,RF)电源。旋转台31与接地的腔室20为相同电位,通过对靶材41侧施加高电压而产生电位差。由此,使可动的旋转台31为负电位,因此避免与电源部6连接的困难性。

[0151] 多个成膜处理部40通过使成膜材料选择性堆积,而形成包含多个成膜材料的层的膜。尤其,本实施方式中,包含与不同种类的成膜材料对应的溅射源4,通过使成膜材料选择性堆积,而形成包含多种成膜材料的层的膜。所谓包含与不同种类的成膜材料对应的溅射源4,包括所有的成膜处理部40的成膜材料不同的情况,也包括多个成膜处理部40为共同的成膜材料而其他与此不同的情况。所谓使成膜材料一种一种地选择性堆积,是指在任一种成膜材料的成膜处理部40进行成膜的期间,其他成膜材料的成膜处理部40不进行成膜。另外,所谓成膜中的成膜处理部40或成膜部位M,是指对成膜处理部40的靶材41施加电力,而呈电子零件10可进行成膜的状态的成膜处理部40或成膜部位M。

[0152] 本实施方式中,在搬送路径L的搬送方向上,夹隔表面处理部50而配设有两个成膜处理部40A、成膜处理部40B。成膜部位M1、成膜部位M2对应于两个成膜处理部40A、成膜处理部40B。这些成膜处理部40A、成膜处理部40B中,成膜处理部40A的成膜材料为SUS。即,成膜处理部40A的溅射源4具备包含SUS的靶材41A、靶材41B。另一成膜处理部40B的成膜材料为Cu。即,成膜处理部40B的溅射源4具备包含Cu的靶材41A、靶材41B。本实施方式中,在任一成膜处理部40进行成膜处理的期间,其他成膜处理部40不进行成膜处理。

[0153] 表面处理部

[0154] 表面处理部50是对由搬送部30搬送的电子零件10进行表面处理即逆溅射的处理部。所述表面处理部50设置于由划分部44所划分的处理部位M3。表面处理部50具有处理单元5。参照图3及图4对所述处理单元5的构成例进行说明。

[0155] 处理单元5具备自腔室20的上部至内部而设置的筒形电极51。筒形电极51是角筒状,一端具有开口部51a,另一端被封闭。筒形电极51以具有开口部51a的一端朝向旋转台31的方式介隔绝缘构件52而安装于在腔室20的顶面所设置的开口21a。筒形电极51的侧壁在腔室20的内部延伸存在。

[0156] 在筒形电极51的与开口部51a相反的一端设置有向外方突出的凸缘51b。绝缘构件52被固定于凸缘51b与腔室20的开口21a的周缘之间,由此气密地保持腔室20的内部。绝缘构件52只要有绝缘性即可,并不限定于特定的材料,例如可包含聚四氟乙烯(Polytetrafluoroethylene,PTFE)等材料。

[0157] 筒形电极51的开口部51a配置于旋转台31的与搬送路径L相向的位置。旋转台31作为搬送部30来搬送搭载有电子零件10的托盘34并经过与开口部51a对向的位置。此外,筒形电极51的开口部51a的大小大于旋转台31的径方向上的托盘34的大小。

[0158] 如图3所示,若自平面方向来看,则筒形电极51成为自旋转台31的半径方向的中心侧朝向外侧扩径的扇形。所谓此处所述的扇形,是指扇子的扇面的部分的形状。筒形电极51的开口部51a也同样地为扇形。关于旋转台31上的托盘34经过与开口部51a对向的位置的速度,在旋转台31的半径方向上,越朝向中心侧越慢,越朝向外侧越快。因此,若开口部51a仅为长方形或正方形,则在半径方向的中心侧与外侧,电子零件10经过与开口部51a对向的位置的时间产生差。通过使开口部51a自半径方向的中心侧朝向外侧扩径,可将经过开口部51a的时间设为一定,可均等地进行后述的等离子体处理。但是,若经过的时间的差为不引

起制品上问题的程度,则也可为长方形或正方形。

[0159] 如上所述,筒形电极51贯通腔室20的开口21a,一部分露出至腔室20的外部。如图4所示,所述筒形电极51的露出至腔室20的外部的部分被外壳53覆盖。通过外壳53而气密地保持腔室20的内部的空间。筒形电极51的位于腔室20的内部的部分即侧壁的周围由屏蔽体54覆盖。

[0160] 屏蔽体54是与筒形电极51同轴的扇形的角筒,且大于筒形电极51。屏蔽体54连接于腔室20。具体而言,屏蔽体54自腔室20的开口21a的边缘竖立设置,朝向腔室20的内部而延伸的端部位于与筒形电极51的开口部51a相同的高度。屏蔽体54与腔室20同样地作为阴极发挥作用,因此可利用电阻少的导电性金属构件来构成。屏蔽体54也可与腔室20一体地成型,或者也可使用固定金属零件等而安装于腔室20。

[0161] 屏蔽体54是用来使等离子体在筒形电极51内稳定地产生而设置。屏蔽体54的各侧壁是以与筒形电极51的各侧壁介隔规定的间隙而大致平行地延伸的方式设置。若间隙变得过大,则电容变小,或在筒形电极51内所产生的等离子体会进入间隙,因此理想的是间隙尽可能小。但是,即便间隙变得过小,筒形电极51与屏蔽体54之间的电容也会变大,因此欠佳。间隙的大小可根据产生等离子体所需的电容来适当设定。此外,图4仅图示了屏蔽体54及筒形电极51的在半径方向上延伸的两个侧壁面,但在屏蔽体54及筒形电极51的在圆周方向上延伸的两个侧壁面之间也可设置与半径方向的侧壁面相同大小的间隙。

[0162] 另外,在筒形电极51连接有工艺气体导入部55。除了配管以外,工艺气体导入部55还具有未图示的工艺气体G2的气体供给源、泵、阀等。通过所述工艺气体导入部55而将工艺气体G2导入至筒形电极51内。如上所述,工艺气体G2可根据处理的目的而适当变更。

[0163] 在筒形电极51连接有用来施加高频电压的RF电源56。在RF电源56的输出侧串联连接有作为匹配电路的匹配盒57。RF电源56也连接于腔室20。若由RF电源56施加电压,则筒形电极51作为阳极发挥作用,腔室20、屏蔽体54及旋转台31作为阴极发挥作用。匹配盒57通过使输入侧及输出侧的阻抗匹配,可使等离子体的放电稳定化。此外,腔室20或旋转台31接地。连接于腔室20的屏蔽体54也接地。RF电源56及工艺气体导入部55均经由设置于外壳53的贯通孔而连接于筒形电极51。

[0164] 若将作为工艺气体G2的氩气自工艺气体导入部55导入至筒形电极51内,并由RF电源56对筒形电极51施加高频电压,则氩气被等离子体化,从而产生电子、离子及自由基等。

[0165] (负载锁部)

[0166] 负载锁部60是在维持真空室21的真空的状态下,通过未图示的搬送单元,自外部将经由载置部35而搭载有未处理的电子零件10的托盘34搬入至真空室21,并将经由载置部35而搭载有处理完的电子零件10的托盘34搬出至真空室21的外部的装置。所述负载锁部60可应用周知的结构,因此省略说明。

[0167] 控制装置

[0168] 控制装置70是对成膜装置100的各部加以控制的装置。所述控制装置70例如可由专用的电路或者以规定的程序进行动作的计算机等来构成。即,关于与溅射气体G1及工艺气体G2对于真空室21的导入及排气相关的控制、电源部6、RF电源56的控制、旋转台31的旋转的控制等,其控制内容已程序化,且通过可编程逻辑控制器(Programmable Logic Controller,PLC)或中央处理器(Central Processing Unit,CPU)等处理装置来执行,可对

应于多种多样的成膜样式。

[0169] 作为具体控制内容,可列举:成膜装置100的初始排气压力、溅射源4的选择、对于靶材41及筒形电极51的施加电力、溅射气体G1及工艺气体G2的流量、种类、导入时间及排气时间、成膜时间、马达32的旋转速度等。

[0170] 参照假想的功能方块图即图7,对用来以所述方式执行各部的动作的控制装置70的构成进行说明。即,控制装置70包括:机构控制部71、电源控制部72、存储部73、设定部74、输入输出控制部75。

[0171] 机构控制部71是控制排气部23、气体供给部25、工艺气体导入部55、搬送部30的马达32、负载锁部60等的驱动源、阀、开关、电源等的处理部。电源控制部72是控制电源部6、RF电源56的处理部。

[0172] 控制装置70以在任一种成膜材料的成膜处理部进行成膜的期间,其他成膜材料的成膜处理部不进行成膜的方式选择性控制成膜处理部40。即,电源控制部72在对成膜处理部40A的靶材41施加电压来进行成膜的期间,不进行对成膜处理部40B的靶材41的电压的施加。另外,在对成膜处理部40B的靶材41施加电压进行成膜的期间,不进行对成膜处理部40A的靶材41的电压的施加。

[0173] 存储部73是存储本实施方式的控制中所需的信息的构成部。设定部74是将自外部输入的信息设定于存储部73的处理部。输入输出控制部75是控制与成为控制对象的各部之间的信号的转换或输入输出的接口(interface)。

[0174] 进而,在控制装置70连接有输入装置76、输出装置77。输入装置76是用来使操作员经由控制装置70来操作成膜装置100的开关、触摸屏、键盘、鼠标等输入单元。例如,可通过输入单元来输入进行成膜的溅射源4的选择。

[0175] 输出装置77是使用来确认装置的状态的信息呈操作员可视认的状态的显示器、灯、仪表(meter)等输出单元。例如,可将与正在进行成膜的溅射源4对应的成膜部位M1、成膜部位M2、正在进行表面处理的处理部位M3与未进行成膜或处理的部位加以区别地显示于输出装置77。

[0176] 动作

[0177] 以下,除了所述图1~图7以外,还参照图8(a)~图8(c)、图9(a)~图9(b)来对如上所述的本实施方式的动作进行说明。此外,虽未进行图示,但成膜装置100是通过输送机、机械臂等搬送单元来进行经由载置部35而搭载有电子零件10的托盘34的搬入、搬送、搬出。

[0178] 如图5、图8(a)所示,电子零件10空出间隔而呈矩阵状排列贴附于载置部35中的框架37内的贴附区域S上。此种多个载置部35搭载于托盘34的载置面34a。由此,如图8(b)所示,密接片38的第2密接面38b密接于载置面34a。此外,如后所述,也可为相对于如贴附于载置面34a的密接片38、通过涂敷、涂布或加工等而形成于载置面34a的密接片38的设置于载置面34a的密接片38,贴附贴附于框架37的保持片36的非粘着面36b的方式。即,保持片36贴附于设置于托盘34的密接片38等,保持片36与密接片38在载置部35载置于托盘34的过程中进行一体化的构成也包含于载置部35具有保持片36与密接片38的方式中。在为通过贴附、涂敷、涂布或加工等而形成于载置面34a的密接片38的情况下,密接片38与托盘34的边界面成为第2密接面38b。

[0179] 多个托盘34通过负载锁部60的搬送单元而依次搬入至腔室20内。旋转台31使空的

保持部33依次移动至自负载锁部60搬入的搬入部位。保持部33对由搬送单元搬入的托盘34分别单独地加以保持。如此,如图2及图3所示,搭载有成为成膜对象的电子零件10的托盘34全部被载置于旋转台31上。

[0180] 参照图3及图4对如上所述相对于导入至成膜装置100的电子零件10的成膜处理进行说明。此外,以下的动作是通过表面处理部50对电子零件10的表面进行清洗及粗面化后,通过成膜处理部40A、成膜处理部40B而在电子零件10的表面形成电磁波屏蔽膜13的一例。电磁波屏蔽膜13是通过交替地层叠SUS层、Cu层而形成。直接形成于电子零件10的SUS层成为提高与模制树脂、Cu的密接度的基底。中间的Cu层是具有遮蔽电磁波的功能的层。最上层的SUS层是防止Cu锈等的保护层。

[0181] 首先,排气部23通过对真空室21进行排气来减压而形成为真空。旋转台31旋转并达到规定的旋转速度。电子零件10在处理单元5中,经过与筒形电极51的开口部51a对向的位置。处理单元5中,将作为工艺气体G2的氩气自工艺气体导入部55导入至筒形电极51,并由RF电源56对筒形电极51施加高频电压。通过施加高频电压,氩气被等离子体化,从而产生电子、离子及自由基等。等离子体自作为阳极的筒形电极51的开口部51a流至作为阴极的旋转台31。通过等离子体中的离子碰撞经过开口部51a下的电子零件10的表面,从而表面被清洗及粗面化。并且,在表面处理部50的表面处理时间经过后,停止表面处理部50。即,停止来自工艺气体导入部55的工艺气体G2的供给、利用RF电源56的电压的施加。

[0182] 其次,成膜处理部40A的气体供给部25将溅射气体G1供给至靶材41的周围。所述状态下,保持部33所保持的电子零件10以画圆的轨迹在搬送路径L上移动,并经过与溅射源4对向的位置。

[0183] 其次,仅在成膜处理部40A,电源部6对靶材41施加电力。由此,溅射气体G1等离子体化。在溅射源4,通过等离子体而产生的离子与靶材41碰撞而射出成膜材料的粒子。因此,在经过成膜处理部40A的成膜部位M1的电子零件10的表面,在每次所述经过时,成膜材料的粒子堆积而生成膜。此处,形成SUS层。此时,虽然电子零件10经过成膜处理部40B的成膜部位M2,但成膜处理部40B未对靶材41施加电力,因此不进行成膜处理,电子零件10未被加热。另外,在成膜部位M1、成膜部位M2以外的区域,电子零件10也未被加热。如此,在未被加热的区域,电子零件10放出热。

[0184] 在成膜处理部40A的成膜时间经过后,停止成膜处理部40A。即,停止电源部6对靶材41的电力施加。并且,成膜处理部40B的电源部6对靶材41施加电力。由此,溅射气体G1等离子体化。在溅射源4,通过等离子体而产生的离子与靶材41碰撞而射出成膜材料的粒子。因此,在经过成膜处理部40B的成膜部位M2的电子零件10的表面,在每次所述经过时,成膜材料的粒子堆积而生成膜。此处,形成Cu层。所述层成为电磁波屏蔽膜13的层的一部分。此时,虽然电子零件10经过成膜处理部40A的成膜部位M1,但成膜处理部40A未对靶材41施加电力,因此不进行成膜处理,电子零件10未被加热。另外,在成膜部位M1、成膜部位M2以外的区域,电子零件10也未被加热。如此,在未被加热的区域,电子零件10放出热。

[0185] 在成膜处理部40B的成膜时间经过后,停止成膜处理部40B。即,停止电源部6对靶材41的电力施加。并且,成膜处理部40A的电源部6对靶材41施加电力。由此,溅射气体G1等离子体化。在溅射源4,通过等离子体而产生的离子与靶材41碰撞而射出成膜材料的粒子。因此,在经过成膜处理部40A的成膜部位M1的电子零件10的表面,在每次所述经过时,成膜

材料的粒子堆积而生成膜。此处,形成SUS层。此时,虽然电子零件10经过成膜处理部40B的成膜部位M2,但成膜处理部40B未对靶材41施加电力,因此不进行成膜处理,电子零件10未被加热。另外,在成膜部位M1、成膜部位M2以外的区域,电子零件10也未被加热。如此,在未被加热的区域,电子零件10放出热。

[0186] 在成膜处理部40A的成膜时间经过后,停止成膜处理部40A。即,停止电源部6对靶材41的电力施加。如此,通过反复进行成膜处理部40A、成膜处理部40B的成膜,从而形成层叠有SUS膜、Cu膜、SUS膜的膜。此外,进而,通过反复进行相同的成膜,也可形成多于三层的膜。由此,根据图9(a)所示的状态,如图9(b)所示,在电子零件10的封装体12的顶面及侧面形成电磁波屏蔽膜13。

[0187] 在如上所述的成膜处理的期间,旋转台31继续旋转并持续循环搬送搭载有电子零件10的托盘34。并且,成膜处理结束后,搭载有电子零件10的托盘34通过旋转台31的旋转而依次定位于负载锁部60,并通过搬送单元而搬出至外部。如图8(c)所示,载置部35通过保持片36自密接片38剥落而自所搬出的托盘34剥落。即,密接片38自载置部35分离。如此,残留于托盘34的密接片38可直接进行再利用。即,其次,通过使搭载有要处理的电子零件10的保持片36的非粘着面36b密接于托盘34上的密接片38的第1密接面38a而将托盘34搬入至真空室21内,从而可与所述同样地进行成膜处理。即便为此种方式,也通过将保持片36贴附于密接片38,而构成包含密接片38的载置部35,并构成具有载置部35的成膜装置100。也可在多次使用中,在密接片38的粘着力降低后,将密接片38自托盘34剥下,并将包含新的密接片38的载置部35载置于托盘34。密接片38的可使用的次数可预先通过实验等来设定。在替换密接片38时,仅更新密接片38,关于保持片36及框架37,可再利用两者,也可仅再利用任一者而将另一者更新,还可使用两者均为新者。此外,可在剥下保持片36后,不再利用密接片38而将密接片38自托盘34剥下,而设为一次性。即,可每次将残留于托盘34的密接片38剥下而废弃,并将包含密接片38的载置部35载置于托盘34。

[0188] 进行电子零件的加热的原因

[0189] 如上所述,电子零件10可在未被加热的区域放出热。所述热的放出主要是通过热经由载置部35而传导至托盘34来进行。但是,如本实施方式,在不具有密接片38的情况下,产生以下的问题。

[0190] (1)在载置部35的保持片36的底面无粘着性的情况下

[0191] 在载置部35的保持片36的上表面设置有贴附电子零件10的粘着面36a,但保持片36的底面不具有粘着性。因此,若仅仅将载置部35载置于托盘34的载置面34a,则在保持片36的底面与载置面34a之间产生间隙。即,在保持片36的表面与载置面34a的表面具有微细的凹凸,因此所接触的面积会成为整体的10%左右。未接触的空间为真空,因此不存在热传导。因此,电子零件10的热难以传递至托盘34。

[0192] (2)在载置部35的底面具有粘着性的情况下

[0193] 为了处理所述(1)的问题,考虑使保持片36的底面持有粘着性。如此,可使载置部35密接于托盘34的载置面34a,保持片36的底面与载置面34a之间的间隙大幅减少,因此热传导性提高。但是,所述情况下,在成膜处理后,需要将载置部35的保持片36的底面自托盘34的载置面34a剥离的步骤。在将载置部35自载置面34a剥离时,难以使力均匀地传递至所粘着的面,因此局部施加剥离力而有框架37、保持片36产生应变的可能性。如此,若框架37

或保持片36产生应变，则电子零件10的配置面的平坦度消失，或在电子零件10的配置间隔产生偏差，因此对以后的拾取等步骤造成阻碍。

[0194] 另外，在将电子零件10自保持片36拾取时，利用销一个一个自保持片36的底面向上推而剥下，因此若底面具有粘着性，则粘着剂附着于销而导致销的接触位置、接触面积发生变化，由此无法进行正确的拾取。进而，在将所接触的销自保持片36剥离时，保持片36在附着于销的状态下被拉伸，其后，若粘着剂的粘着力大于保持片36的张力而剥离，由此导致被弹开，则有对电子零件10带来位置偏移或剥离等影响的可能性。

[0195] 提高电子零件的放热的理由

[0196] 本实施方式中，载置部35的保持片36的粘着面36a的相反侧的面为不具有粘着性的非粘着面36b。然而，使所述保持片36介隔密接片38而密接于托盘34的载置面34a。因此，电子零件10的热经由保持片36、密接片38而传递至托盘34。因此，电子零件10的加热得到抑制。

[0197] 另外，第1密接面38a与非粘着面36b的接着力小于第2密接面38b与载置面34a的接着力。因此，在使保持片36自托盘34脱离时，在第2密接面38b密接于载置面34a的状态下，保持片36容易自第1密接面38a剥离。因此，框架37、保持片36难以产生应变。保持片36的与粘着面36a相反的一侧为非粘着面36b，因此在拾取电子零件10时，也不产生保持片36附着于销的问题。

[0198] 作用效果

[0199] 本实施方式包括：腔室20，其为供溅射气体G1导入的容器；搬送部30，设置于腔室20内，循环搬送电子零件10；成膜处理部40，具有通过溅射而使成膜材料堆积于由搬送部30循环搬送的电子零件10来进行成膜的溅射源4，并且通过溅射源4而成膜于电子零件10；托盘34，由搬送部30搬送，具有载置面34a；及载置部35，载置于载置面34a，用来搭载电子零件10。

[0200] 载置部35包括：保持片36，一面具备具有粘着性的粘着面36a，另一面具备不具有粘着性的非粘着面36b；及密接片38，一面具备密接于非粘着面36b的具有粘着性的第1密接面38a，另一面具备密接于托盘34的载置面34a的具有粘着性的第2密接面38b，粘着面36a具有用来贴附电子零件10的贴附区域S，第1密接面38a至少跨及与贴附区域S对应的非粘着面36b的区域的整体而密接。

[0201] 因此，来自电子零件10的热经由保持片36及密接片38而传递至托盘34，从而效率良好地放热，因此可不使装置构成复杂化、大型化而抑制电子零件10的加热。另外，无须使用来进行冷却的电力，从而维护也变得容易。

[0202] 在保持片36的粘着面36a贴附有对贴附区域S的外缘的一部分或全部进行规定的框架37，第1密接面38a除了与贴附区域S对应的非粘着面36b的区域的整体以外，还进而密接于与框架37对应的非粘着面36b的区域。

[0203] 因此，来自框架37的热也经由保持片36及密接片38而传递至托盘34，从而效率良好地放热。与保持片36相比，框架37为硬质，因此在将保持片36自密接片38剥离时，框架37所包围的贴附区域S稳定，可抑制对于电子零件10的影响。但是，在成膜处理等时，框架37也与电子零件10同样地被加热。本实施方式中，关于框架37，也可获得密接片38的冷却效果。

[0204] 另外，若将第1密接面38a与非粘着面36b的接着力设为Fa、将第2密接面38b与载置

面34a的接着力设为F<sub>b</sub>,则为F<sub>a</sub><F<sub>b</sub>。更优选为:由第1密接面38a相对于非粘着面36b的剥离阻力小于第2密接面38b相对于载置面34a的剥离阻力的材质形成。

[0205] 因此,在将密接片38自载置部35分离时,密接片38残留于托盘34侧,且容易剥离保持片36。可以轻微的力将保持片36自密接片38剥离,因此可抑制保持片36的变形。

[0206] 另外,密接片38的热传导率为0.1W/(m·K)以上。由此,可促进电子零件10的放热,并可防止加热。

[0207] 试验结果

[0208] 以下对使用本实施方式的成膜装置与比较例的成膜装置,以如上所述的顺序实际实施成膜处理的动作并测定温度而得的试验结果进行说明。但是,在载置部未载置电子零件。关于温度,当作膜的温度=电子零件的温度,以热电偶对保持片的温度进行测定。电磁波屏蔽膜的各层的成膜条件如表1所示。此外,Ar轰击也称为离子轰击,且为利用Ar的清洗、粗面化处理,相当于所述表面处理。

[0209] 表1

| 膜材料 | 部位 | 靶材材料  | 靶材厚度<br>[nm] | 成膜速度<br>[nm/s] | 台旋转速度<br>[rpm] | 施加电力       |            | Ar<br>气体<br>流量<br>[scem] | RF (筒形电极)<br>施加电力 [W] | 成膜时间<br>[s] |

|-----|----|-------|--------------|----------------|----------------|------------|------------|--------------------------|-----------------------|-------------|

|     |    |       |              |                |                | 41A<br>[W] | 41B<br>[W] |                          |                       |             |

|     | M3 | Ar 轰击 |              |                | 30             |            |            | 150.0                    | 300                   | 600.0       |

| SUS | M1 | SUS   | 200.00       | 0.73           | 6              | 2300       | 3000       | 120.0                    |                       | 280         |

| Cu  | M2 | Cu    | 5000.00      | 1.40           | 6              | 2300       | 3000       | 100.0                    |                       | 3570        |

| SUS | M1 | SUS   | 500.00       | 0.73           | 6              | 2300       | 3000       | 120.0                    |                       | 690         |

[0211] (比较例)

[0212] 比较例中,使用PET膜作为保持片,不使用密接片而进行成膜。将所述结果示于图10中。所述试验中,通过表面处理而上升至50℃左右,在基底层的SUS的成膜中上升至80℃左右,进而在Cu的成膜中上升至145℃左右。其后的保护层SUS的成膜中下降至110℃左右。

[0213] 关于通常的半导体封装体,若超过150℃,则构成封装体的树脂容易破坏。因此,加热至接近150℃的145℃左右的情况欠佳。尤其,若超过100℃,则有自保持片与密接片产生水分或接着剂的气体放出、阻力值上升等使膜质劣化的可能性。因此,在为此种成膜装置的情况下,优选为具有冷却机构。

[0214] (实施例)

[0215] 实施例中,使用PET膜作为保持片,并使用PET膜作为密接片来进行成膜。将所述结果示于图11中。所述试验中,在表面处理中,上升停留于35℃左右,在基底层的SUS的成膜中仅上升至40℃左右,进而在Cu的成膜中仅上升至60℃左右。其后的保护层的SUS的成膜中,下降至50℃左右。如此,可知本发明中,可大幅抑制温度上升。此外,图10、图11中,因混入了噪声的关系,有测定值在微细的时间间隔中上下变动的部位,但整体的倾向不发生改变。

[0216] 其他实施方式

[0217] 本发明并不限定于所述实施方式,也包括如下方式。

[0218] (1)所述实施方式中,将保持片36、密接片38设为平坦,但其是指平板状,并不限定

于其表面为平滑。保持片36的粘着面36a、密接片38的第1密接面38a、第2密接面38b是具有粘着性的面,因此存在微细的凹凸。进而,也可将密接片38的第1密接面38a、第2密接面38b设为具有槽的形状。例如,在第1密接面38a及第2密接面38b的一者或两者形成与外部连通的槽。槽优选为小至不妨碍冷却效果的程度。通过设置此种槽,而有如下效果:在将保持片36与密接片38贴合时,即便在密接面形成气泡,气泡也容易自槽脱出。另外,所述情况下,密接片38的由槽所划分的形状可设为四边形等多边形状,也可设为圆形、椭圆形等闭合曲线形状。进而,托盘34的载置面34a也并不限于平坦面。也可预先形成载置面34a与密接片38的第2密接面38b分别彼此吻合的凹凸,而实现由表面积的扩大所带来的热传导性的提高。

[0219] (2) 关于成膜材料,可应用可通过溅射而成膜的各种材料。例如,作为电磁波屏蔽膜,也可使用Al、Ag、Ti、Nb、Pd、Pt、Zr等。进而,作为磁体,可使用Ni、Fe、Cr、Co等。进而,另外,作为基底的密接层,可使用SUS、Ni、Ti、V、Ta等,作为最表层的保护层,可使用SUS、Au等。

[0220] (3) 封装体12的方式例如可应用球栅阵列 (Ball Grid Array, BGA)、栅格阵列 (Land Grid Array, LGA)、小外形封装 (Small Outline Package, SOP)、四面扁平封装 (Quad Flat Package, QFP)、晶圆级封装 (Wafer Level Package, WLP) 等目前或将来可利用的所有方式。即便设为进行电子零件10与外部的电性连接的端子,例如也考虑设置于底面的BGA等半球状者或LGA等平面状者、设置于侧面的SOP、QFP的细板状者等,但可应用目前或将来可利用的所有端子,且也不追究其形成位置。另外,密封于电子零件10的内部的元件11可为单个,也可为多个。

[0221] (4) 成膜部位的靶材的数量并不限于两个。可将靶材设为一个,也可设为三个以上。另外,成膜部位可设为两个以下,也可设为四个以上。

[0222] (5) 由搬送部同时搬送的托盘、电子零件的数量、对其加以保持的保持部的数量至少为一个即可,并不限于所述实施方式中例示的数量。即,可为一个电子零件循环而反复进行成膜的方式,也可为两个以上的电子零件循环而反复进行成膜的方式。

[0223] (6) 利用蚀刻或灰化的清洗或表面处理也可在独立于具有成膜部位的腔室的腔室进行。此外,在进行氧化处理或后氧化处理的情况下,可使用氧作为工艺气体G2。在进行氮化处理的情况下,可使用氮气作为工艺气体G2。

[0224] (7) 所述实施方式中,设为旋转台31在水平面内进行旋转的一例。但是,搬送部的旋转面的朝向并不限于特定的方向。例如,也可设为在垂直面内进行旋转的旋转面。进而,搬送部所具有的搬送单元并不限于旋转台。例如,也可设为具有保持工件的保持部的圆筒形状的构件以轴为中心进行旋转的旋转体。另外,循环搬送的轨迹并不限于圆周。广泛包括利用无端状的搬送路径来进行循环搬送的方式。例如,可为矩形或椭圆,也可包含屈曲或弯曲的路径。搬送路径例如也可通过输送机等来构成。

[0225] 进而,本发明为如下成膜装置100,所述成膜装置100包括:腔室20,其为供溅射气体G1导入的容器;成膜处理部40,设置于腔室20内,具有通过溅射而使成膜材料堆积来进行成膜的溅射源4,并且通过溅射源4而成膜于电子零件10;托盘34,设置于成膜处理部40的处理区域,具有载置面34a;及载置部35,载置于载置面34a,用来搭载电子零件10,且只要具有如上所述的载置部35即可。因此,也可为不循环搬送电子零件10而以静止的状态进行成膜的成膜装置。也可将经由载置部35而搭载有电子零件10的托盘34搬入,并设置于处理区域,不使相对于靶材41的相对位置发生变化而进行溅射。

[0226] (8) 所述实施方式中,设为使成膜材料一种一种地选择性堆积来进行成膜。但是,本发明并不限于此,只要可通过使成膜材料选择性堆积而形成包含多个成膜材料的层的膜即可。因此,也可同时堆积两种以上的成膜材料。例如,有时利用Co、Zr、Nb的合金来形成电磁波屏蔽膜。在此种情况下,可同时选择多个成膜处理部中,将Co作为成膜材料的成膜处理部、将Zr作为成膜材料的成膜处理部及将Nb作为成膜材料的成膜处理部来进行成膜。

[0227] 并且,所述情况下,可以圆周的轨迹中,在成膜中的成膜部位以外的部分经过的轨迹比这些的成膜中在成膜部位经过的轨迹更长的方式,来选择用于成膜的成膜处理部、或者设定对成膜处理部加以划分的划分部的配置。

[0228] 即,在选择多个一种或多种成膜处理部来进行成膜、或者选择单一的成膜处理部来进行成膜的任一情况下,均可以圆周的轨迹中,在成膜中的成膜部位以外的部分经过的轨迹比成膜中在成膜部位经过的轨迹更长的方式,来选择用于成膜的成膜处理部、或者设定对成膜处理部加以划分的划分部的配置。

[0229] (9) 以上已对本发明的实施方式及各部的变形例进行了说明,但所述实施方式或各部的变形例仅作为一例而提出,并不意图限定发明的范围。上文所述的这些新颖的实施方式能以其他各种方式实施,在不脱离发明的主旨的范围内可进行各种省略、替换、变更。这些实施方式及其变形包含于发明的范围或主旨内,并且包含于权利要求所记载的发明内。

10

图1

100

图2

图3

图4

图5

35

图6

图7

图8(a)

图8(b)

图8(c)

图9 (a)

图9 (b)

图10

图11