(12)

# Offenlegungsschrift

(21) Aktenzeichen: **10 2014 003 690.1**

(22) Anmeldetag: 14.03.2014

(43) Offenlegungstag: 18.09.2014

(51) Int Cl.: **G06F 9/30 (2006.01)**

G06E 9/318 (2006.01)

---

### (30) Unionspriorität:

13/844.881

16.03.2013 US

(72) Erfinder:

Rash, William C., Saratoga, Calif., US; Toll, Bret L., Hillsboro, Oreg., US; Hahn, Scott D., Portland, Oreg., US; Hinton, Glenn J., Portland, Oreg., US

(71) Anmelder:

Intel Corporation, Santa Clara, Calif., US

(74) Vertreter:

Vertreten:

**BOEHMERT & BOEHMERT Anwaltspartnerschaft mbB - Patentanwälte Rechtsanwälte, 28209 Bremen, DE**

Prüfungsantrag gemäß § 44 PatG ist gestellt.

**Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen**

(54) Bezeichnung: **Prozessoren, Verfahren und Systeme zur Befehlsemulation**

(57) Zusammenfassung: Ein Prozessor enthält unter einem Aspekt Dekodierlogik zum Erhalten eines ersten Befehls und zum Bestimmen, dass der erste Befehl emuliert werden soll. Der Prozessor enthält auch emulationsmodusbewusste Nachdekomodier-Befehlsprozessorlogik, die mit der Dekodierlogik gekoppelt ist. Die emulationsmodusbewusste Nachdekomodier-Befehlsprozessorlogik soll ein oder mehrere Steuer signale verarbeiten, die aus einem Befehl dekomodiert werden. Der Befehl ist einer aus einem Satz von einem oder mehreren Befehlen, die zum Emulieren des ersten Befehls verwendet werden. Die ein oder mehreren Steuersignale sollen durch die emulationsmodusbewusste Nachdekomodier-Befehlsprozessorlogik anders verarbeitet werden, wenn ein Emulationsmodus vorliegt, als wenn kein Emulationsmodus vorliegt. Andere Vorrichtungen sind ebenfalls offenbart, ebenso wie Verfahren und Systeme.

**Beschreibung**

Hintergrund

Technisches Gebiet

**[0001]** Hier beschriebene Ausführungsformen beziehen sich allgemein auf Prozessoren. Insbesondere beziehen sich hier beschriebene Ausführungsformen allgemein auf Befehlsemulation in Prozessoren.

Hintergrundinformation

**[0002]** Prozessoren weisen gewöhnlich Befehlssatzarchitekturen (instruction set architectures (ISA)) auf. Die ISA stellt allgemein den Teil der Architektur des Prozessors dar, der sich auf Programmieren bezieht. Die ISA enthält gewöhnlich die nativen Befehle, Architekturregister, Datentypen, Addressierungsmodi und ähnliches der Prozessoren. Ein Teil der ISA ist der Befehlssatz. Der Befehlssatz enthält allgemein Makrobefehle oder Befehle auf ISA-Ebene, die dem Prozessor zur Ausführung bereitgestellt werden. Eine Ausführungslogik und andere Pipeline-Logik ist enthalten, um die Befehle des Befehlssatzes zu verarbeiten. Oftmals kann der Umfang solcher Ausführungs- und Pipeline-Logik beträchtlich sein. Gewöhnlich ist der Umfang solcher Logik umso größer, je mehr Befehle in dem Befehlssatz vorliegen und je komplexer und/oder spezieller die Befehle in dem Befehlssatz sind. Solche Hardware kann dazu tendieren, die Herstellungskosten, die Größe und/oder den Stromverbrauch der Prozessoren zu erhöhen.

Kurze Beschreibung der Zeichnungen

**[0003]** Die Erfindung kann am besten durch Bezugnahme auf die folgende Beschreibung und beigefügten Zeichnungen verstanden werden, die verwendet werden, um die Ausführungsformen der Erfindung zu veranschaulichen. In den Zeichnungen zeigt:

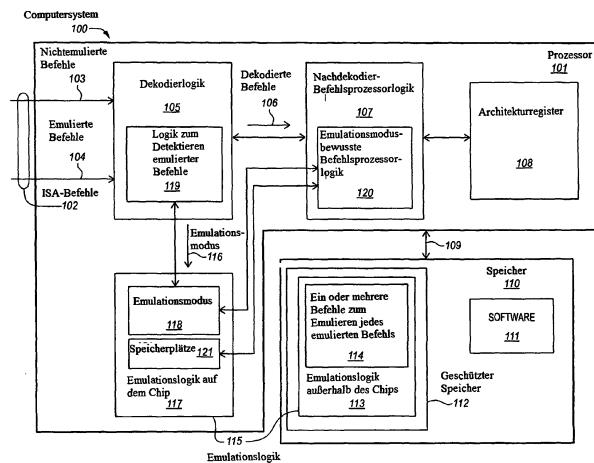

**[0004]** **Fig. 1** ein Blockdiagramm einer Ausführungsform eines Computersystems,

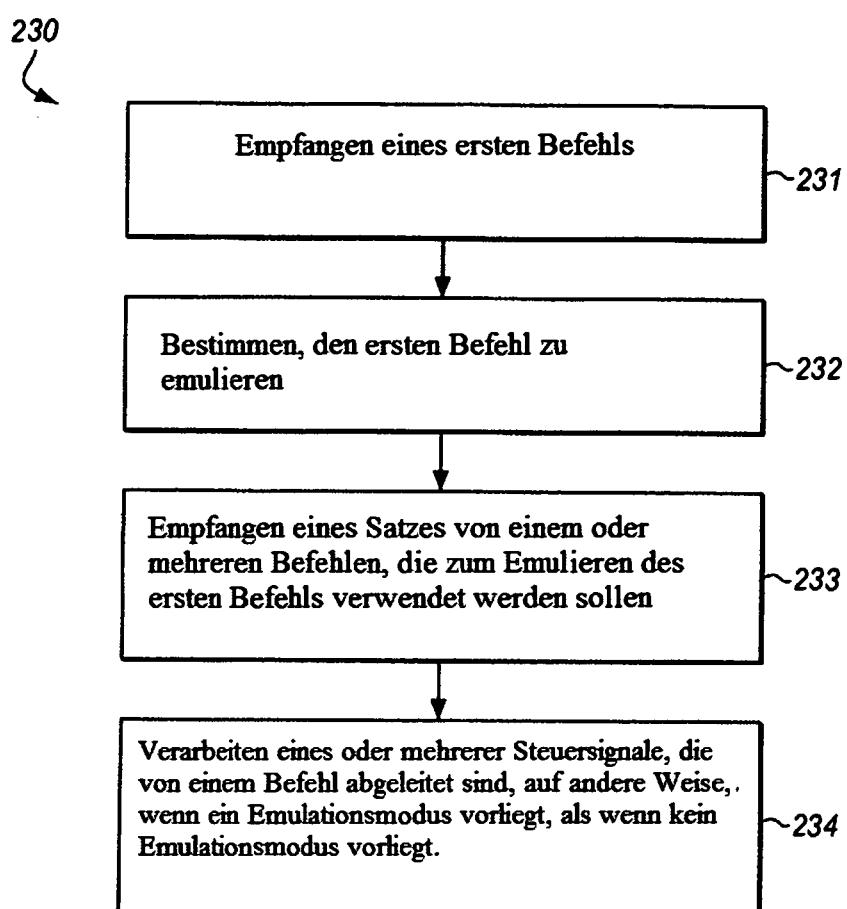

**[0005]** **Fig. 2** ein Blockflußdiagramm einer Ausführungsform eines Verfahrens zum Emulieren eines Befehls in einem Prozessor,

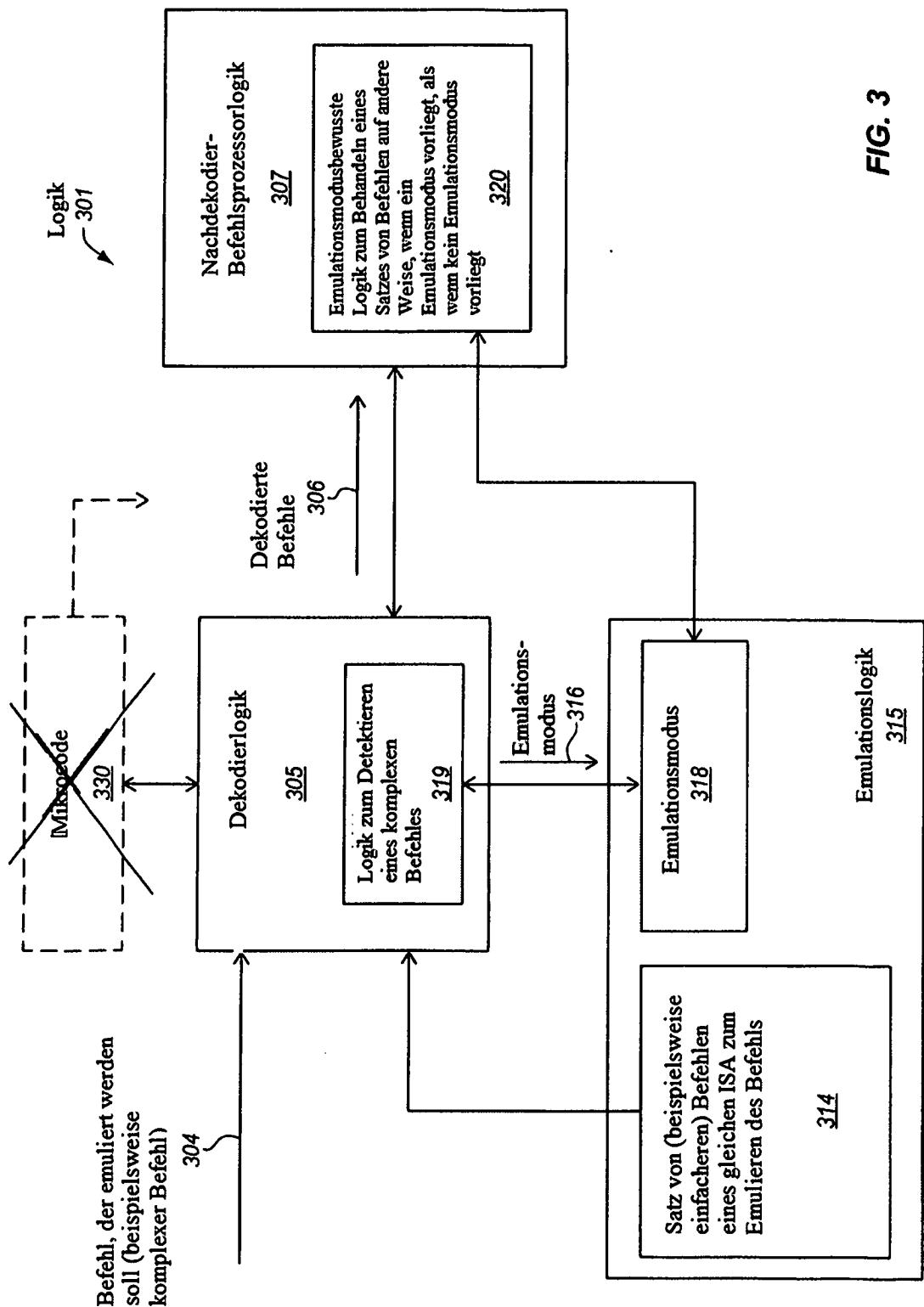

**[0006]** **Fig. 3** ein Blockdiagramm, das eine Ausführungsform von Logik zum Emulieren eines Befehls mit einem Satz eines oder mehrerer Befehle zeigt,

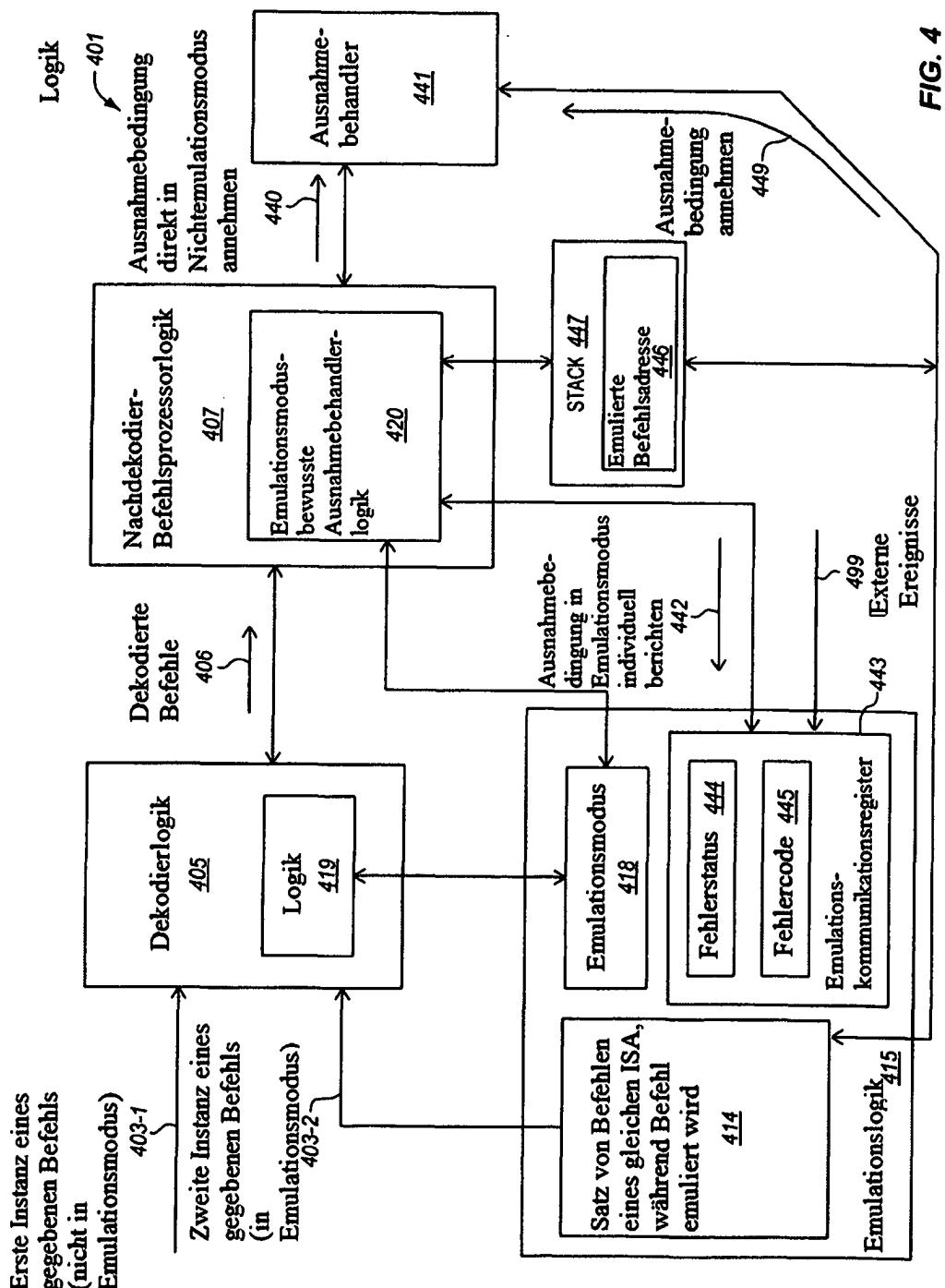

**[0007]** **Fig. 4** ein Blockdiagramm, das eine Ausführungsform von Logik zeigt, um einem Prozessor zu ermöglichen, Ausnahmebedingungen anders zu behandeln, wenn er sich in einem Emulationsmodus befindet, als wenn er sich nicht in dem Emulationsmodus befindet,

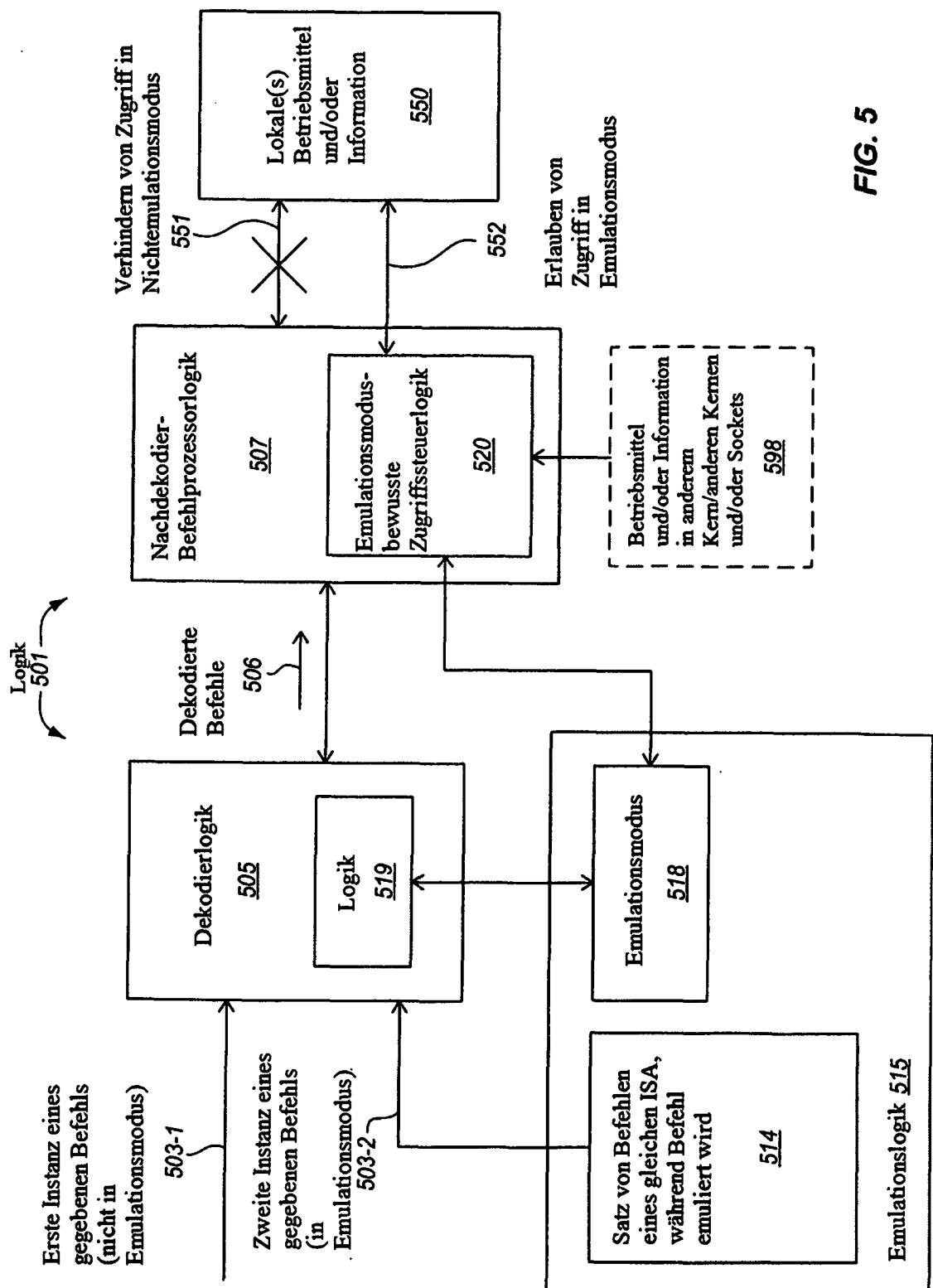

**[0008]** **Fig. 5** ein Blockdiagramm, das eine Ausführungsform von Logik zeigt, um einem Prozessor zu ermöglichen, auf (ein) Betriebsmittel und/oder Information anders zuzugreifen, wenn er sich in einem Emulationsmodus befindet, als wenn er sich nicht in dem Emulationsmodus befindet,

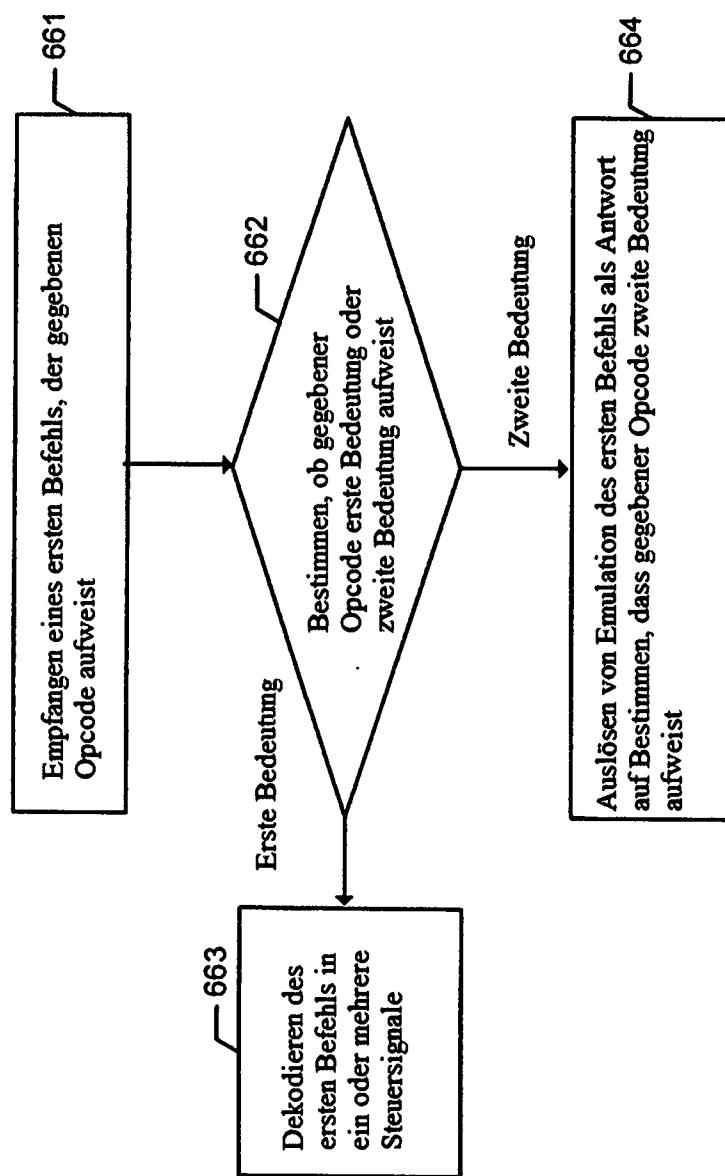

**[0009]** **Fig. 6** ein Blockflussdiagramm einer Ausführungsform eines Verfahrens, das durch und/oder in einem Prozessor durchgeführt wird,

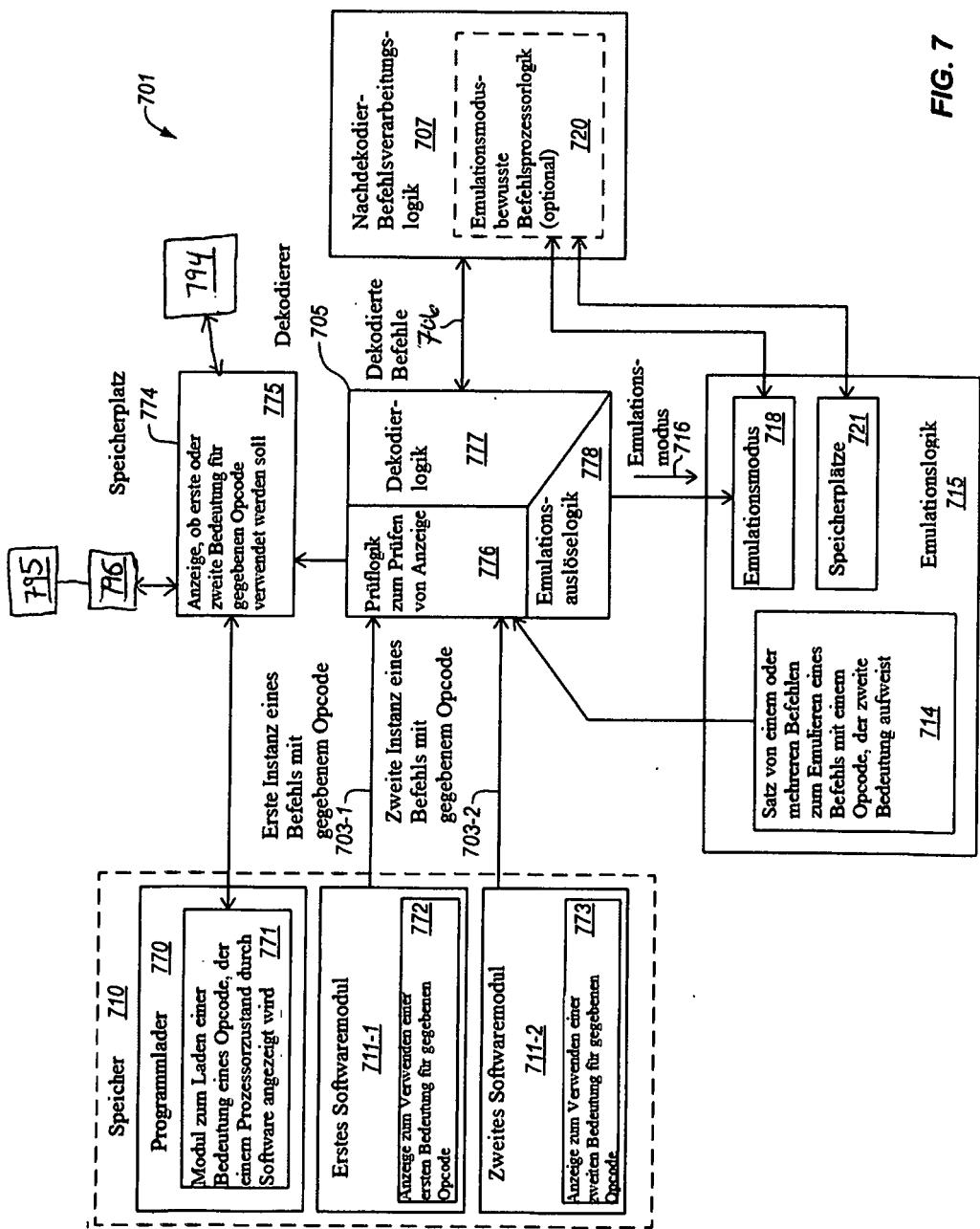

**[0010]** **Fig. 7** ein Blockdiagramm, das eine Ausführungsform von Logik zeigt, um einem Opcode zu ermöglichen, unterschiedliche Bedeutungen zu haben,

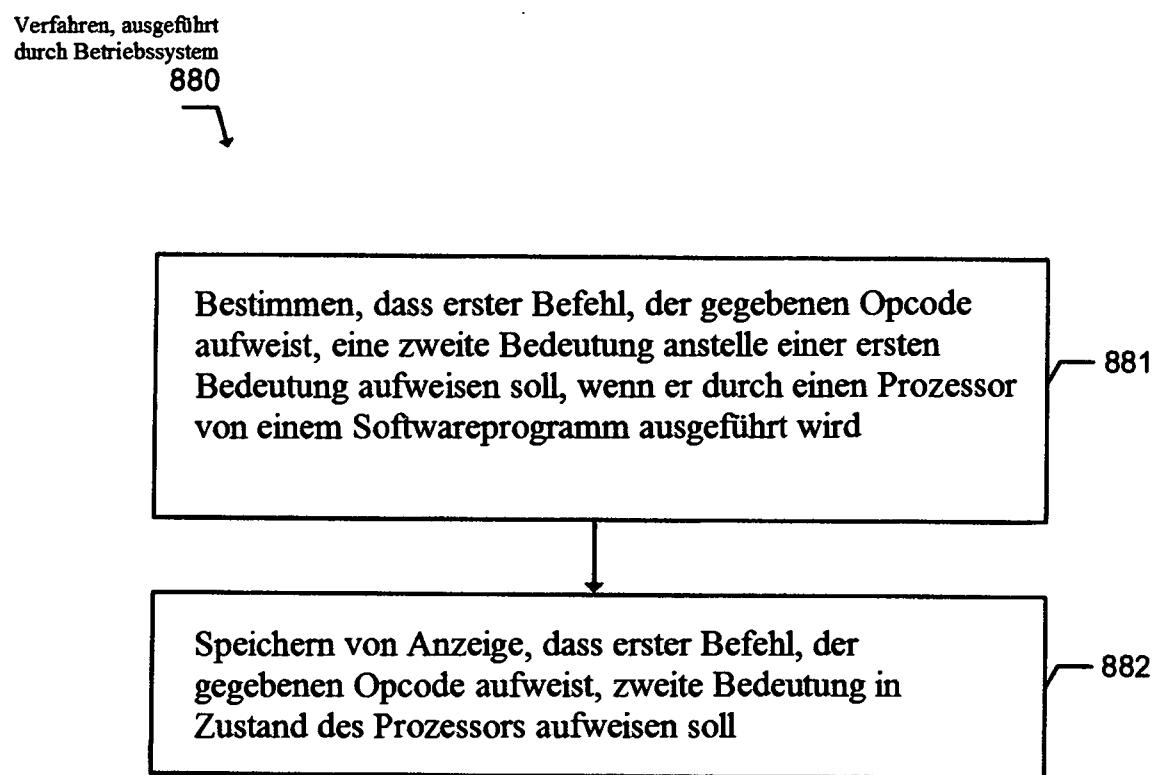

**[0011]** **Fig. 8** ein Blockflussdiagramm einer Ausführungsform eines Verfahrens, das durch ein Betriebssystemmodul durchgeführt werden kann,

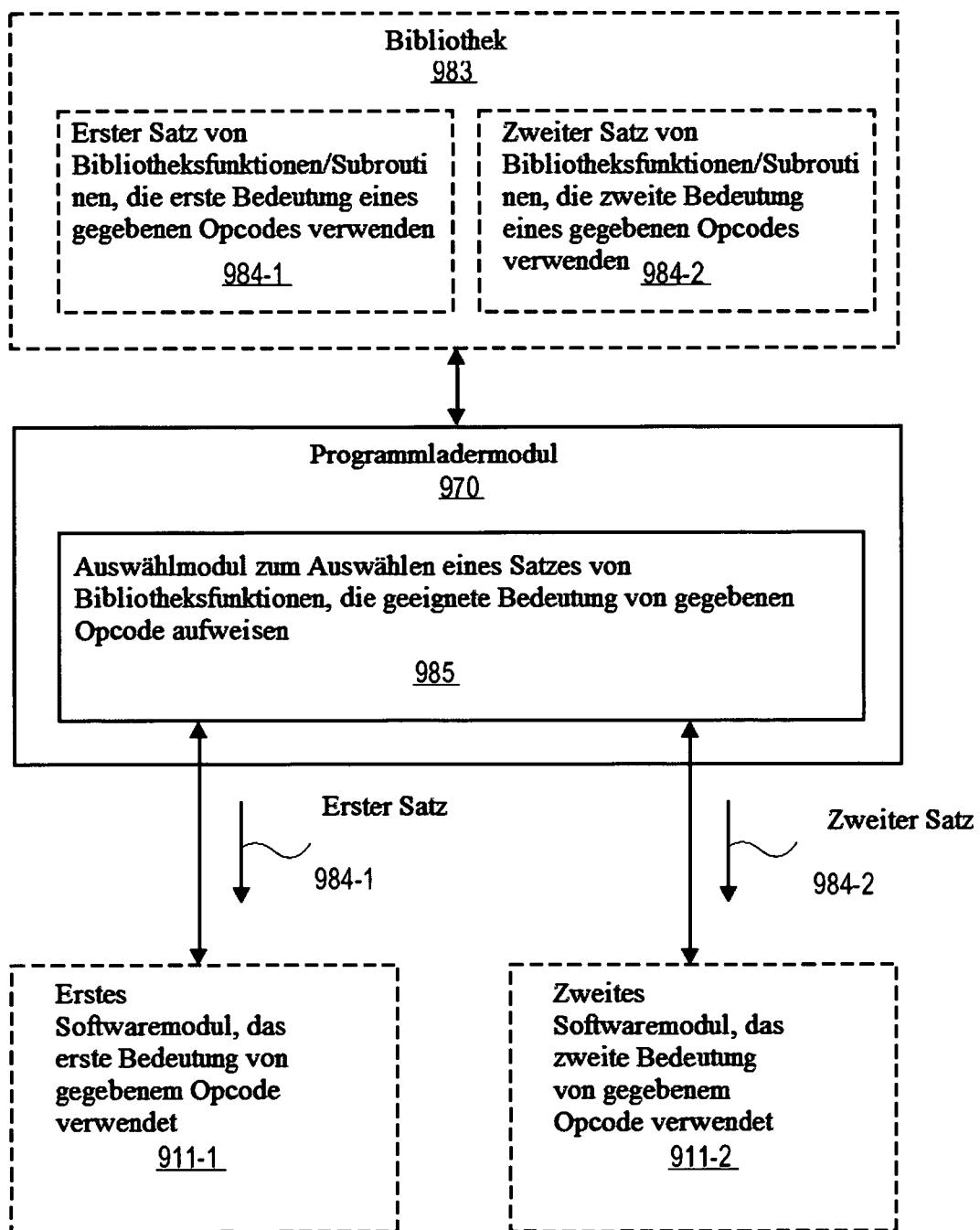

**[0012]** **Fig. 9** ein Blockdiagramm einer Ausführungsform eines Programmadermoduls einschließlich eines Auswahlmoduls, das betrieben werden kann, um einen Satz einer oder mehrerer Funktionen, Subroutinen oder andere Teile einer Softwarebibliothek auszuwählen, die eine Bedeutung eines gegebenen Op-codes haben, die für Software geeignet ist, die sie verwenden wird,

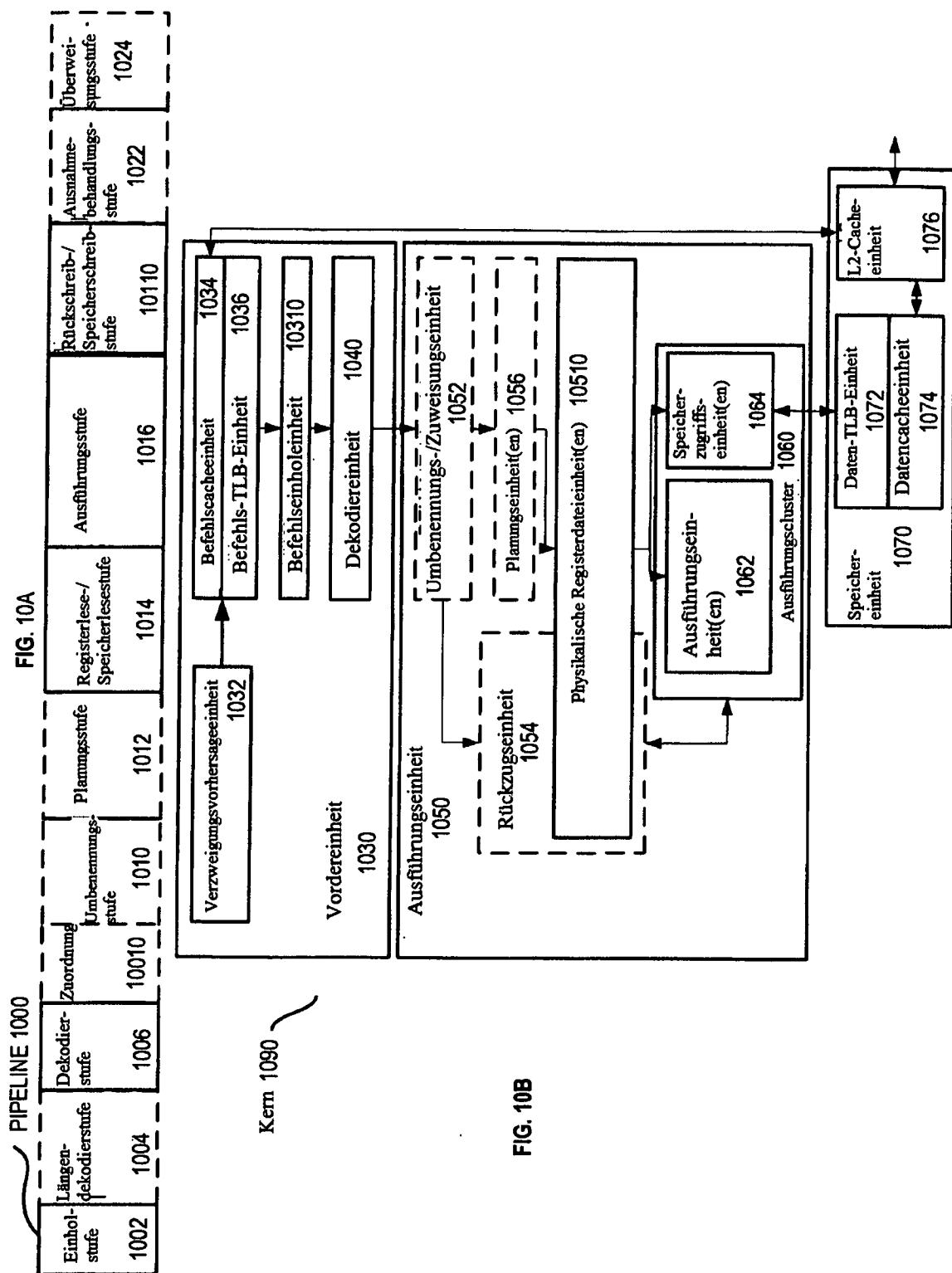

**[0013]** **Fig. 10A** ein Blockdiagramm, das sowohl eine beispielhafte geordnete Pipeline als auch eine beispielhafte ungeordnete Ausgabe-(issue)/Ausführungs-Pipeline mit Registerumbenennung gemäß Ausführungsformen der Erfindung zeigt,

**[0014]** **Fig. 10B** ein Blockdiagramm, das sowohl eine beispielhafte Ausführungsform eines geordneten Architekturkerns als auch einen ungeordneten Ausgabe-/Ausführungsarchitekturkern mit Registerumbenennung, der in einem Prozessor aufgenommen werden soll, gemäß Ausführungsformen der Erfindung zeigt,

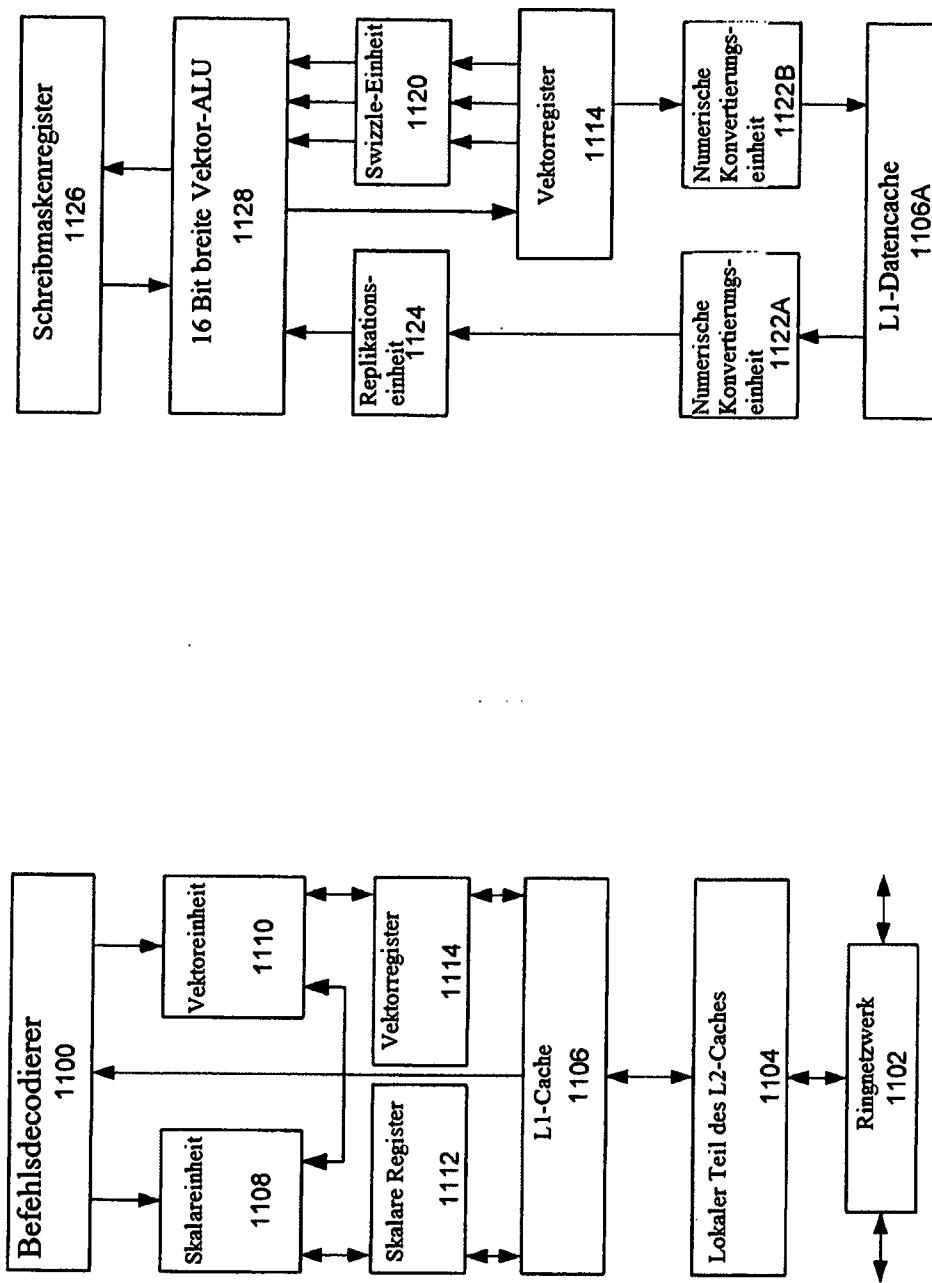

**[0015]** **Fig. 11A** ein Blockdiagramm eines einzelnen Prozessorkerns gemeinsam mit seiner Verbindung zu dem Schaltnetzwerk auf dem Chip und mit seinem lokalen Teil des Level-2(L2)-Caches gemäß Ausführungsformen der Erfindung,

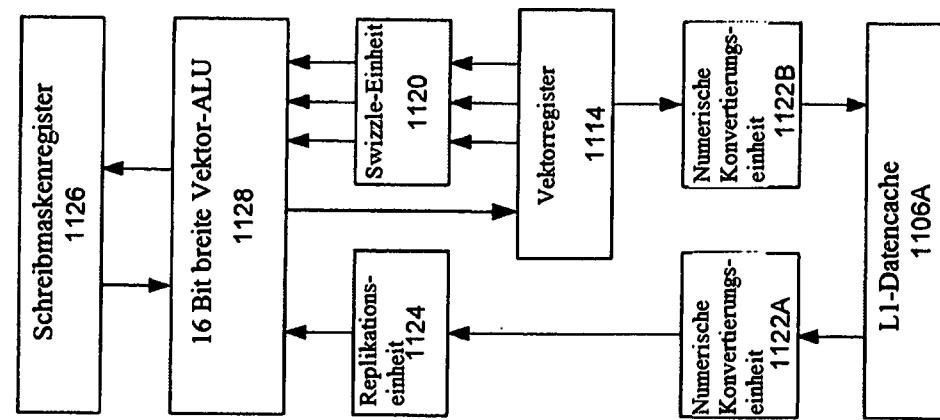

**[0016]** **Fig. 11B** eine erweiterte Ansicht des Prozessorkerns aus **Fig. 11A** gemäß Ausführungsformen der Erfindung,

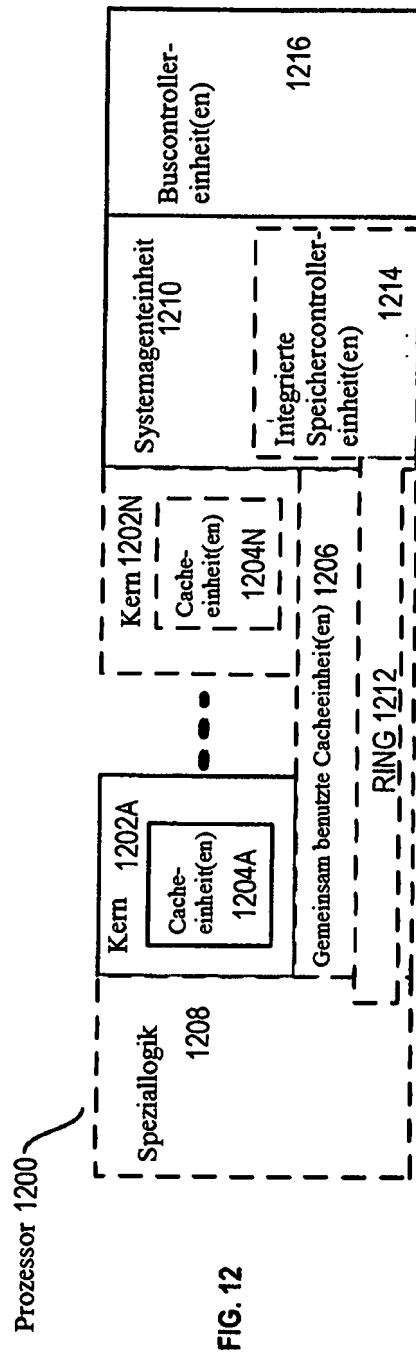

**[0017]** **Fig. 12** ein Blockdiagramm eines Prozessors, der mehr als einen Kern, einen integrierten Speichercontroller und integrierte Grafikvorrichtung gemäß Ausführungsformen der Erfindung enthalten kann,

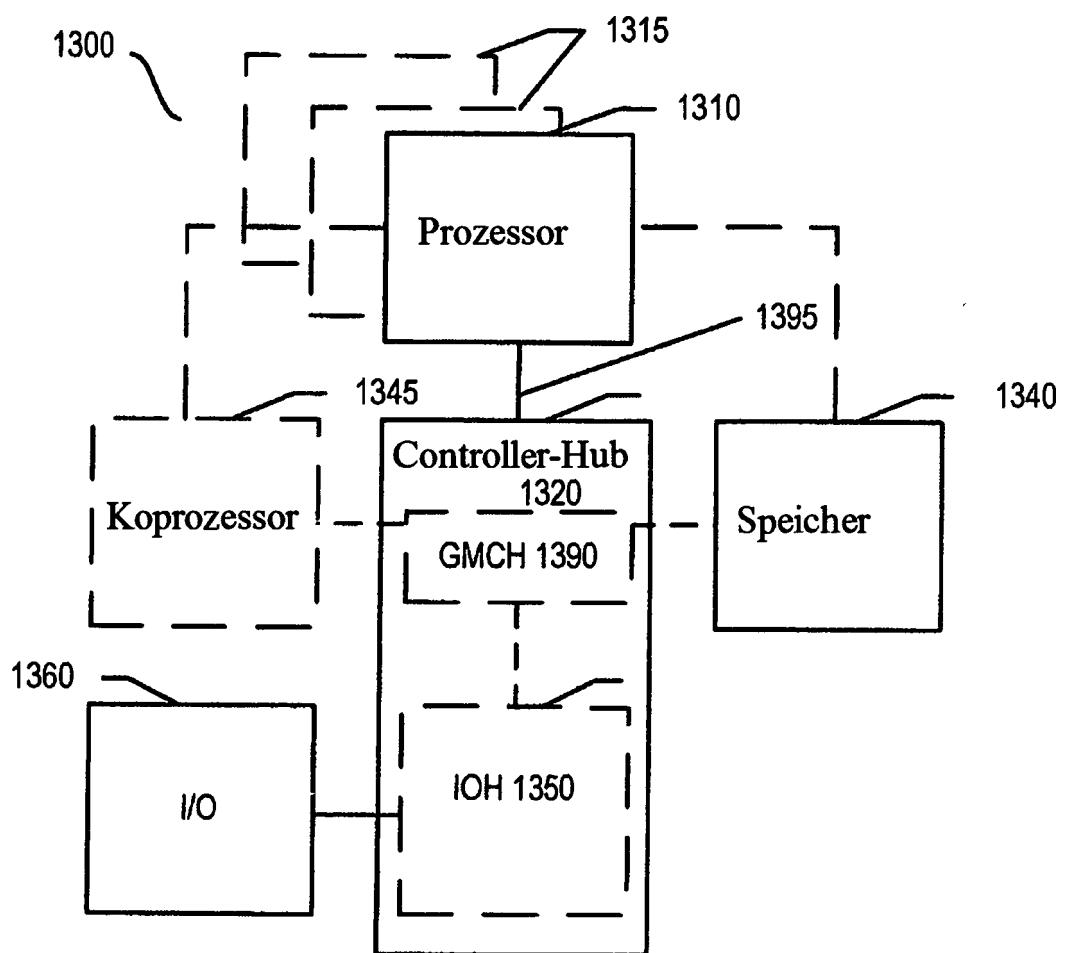

**[0018]** **Fig. 13** ein Blockdiagramm eines Systems gemäß einer Ausführungsform der vorliegenden Erfindung,

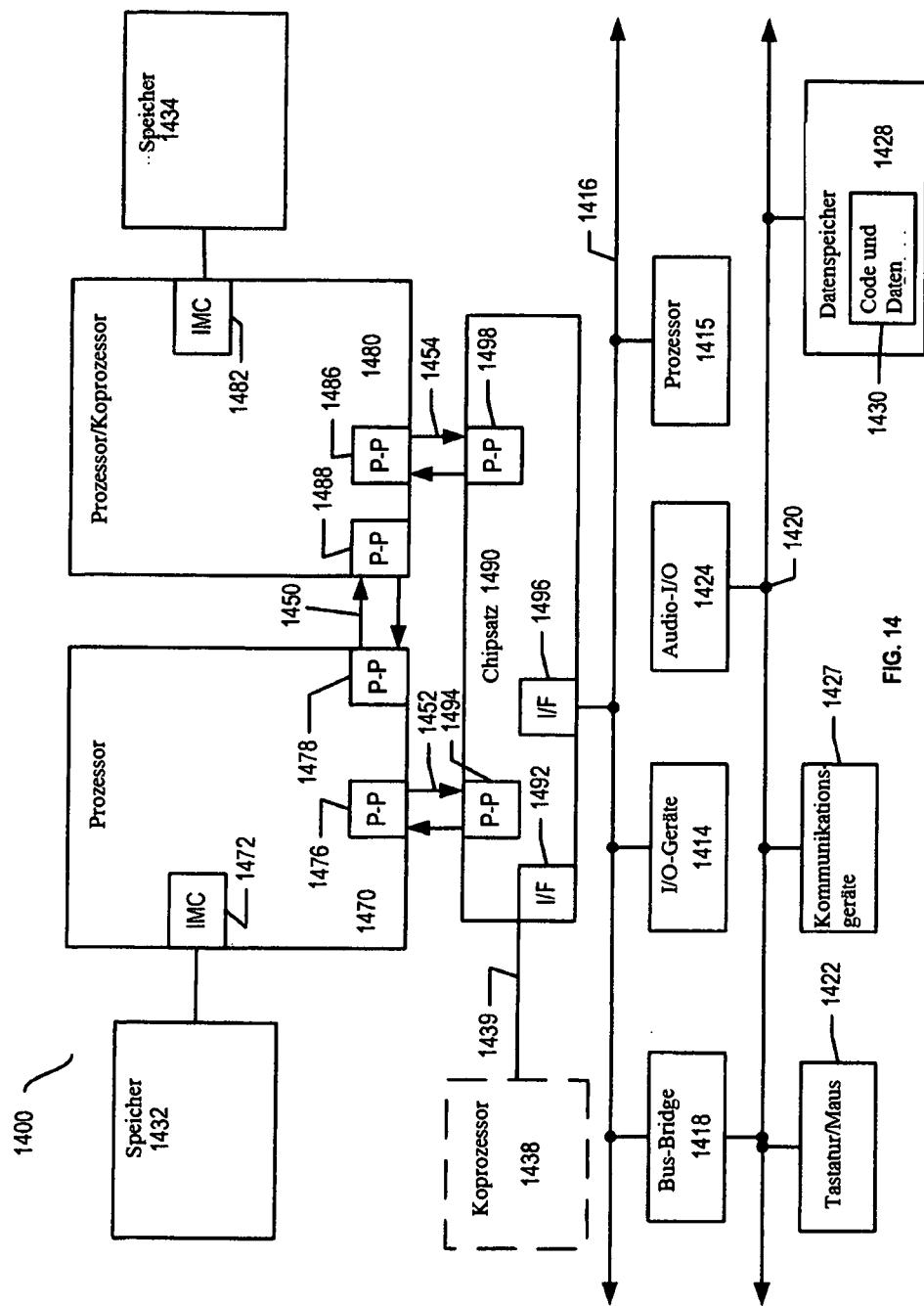

**[0019]** **Fig.** 14 ein Blockdiagramm eines ersten konkreten beispielhaften Systems gemäß einer Ausführungsform der vorliegenden Erfindung,

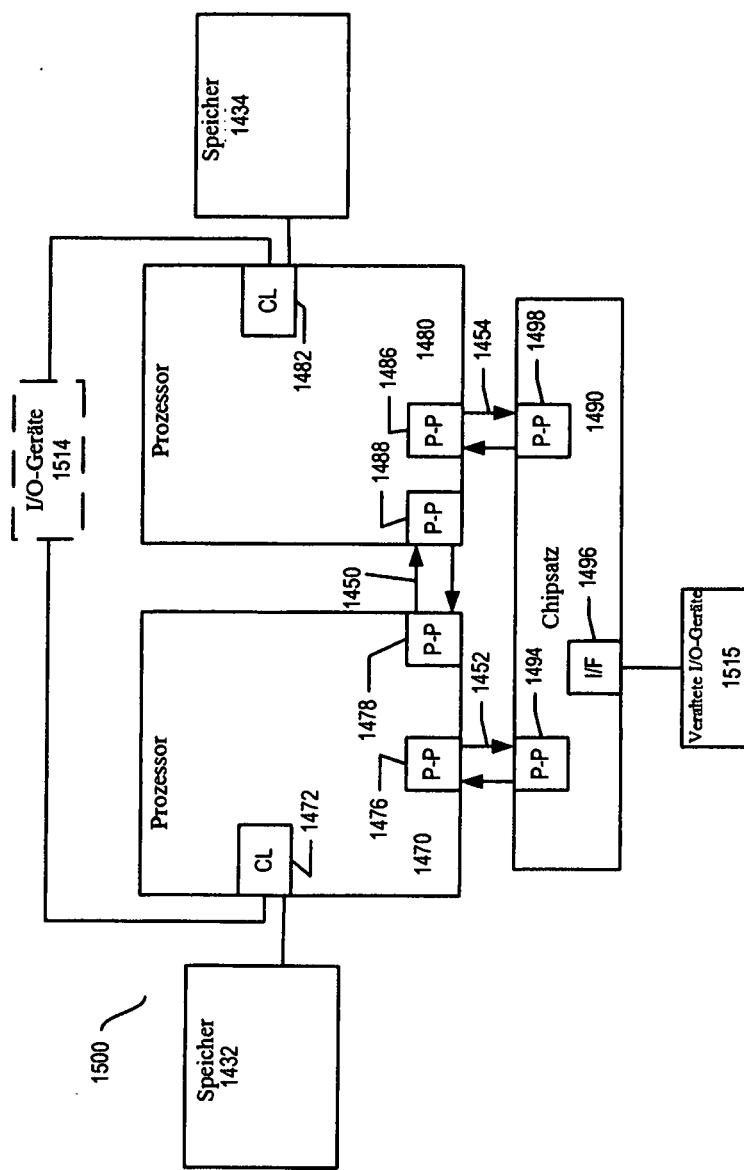

**[0020]** **Fig.** 15 ein Blockdiagramm eines zweiten konkreten beispielhaften Systems gemäß Ausführungsformen der vorliegenden Erfindung,

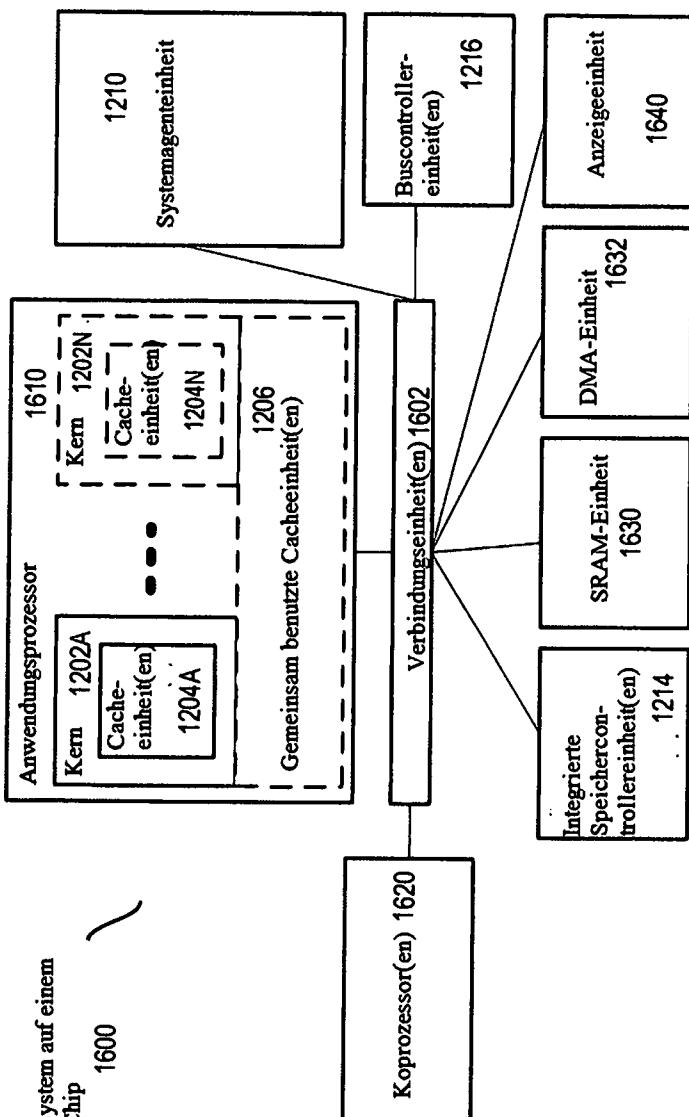

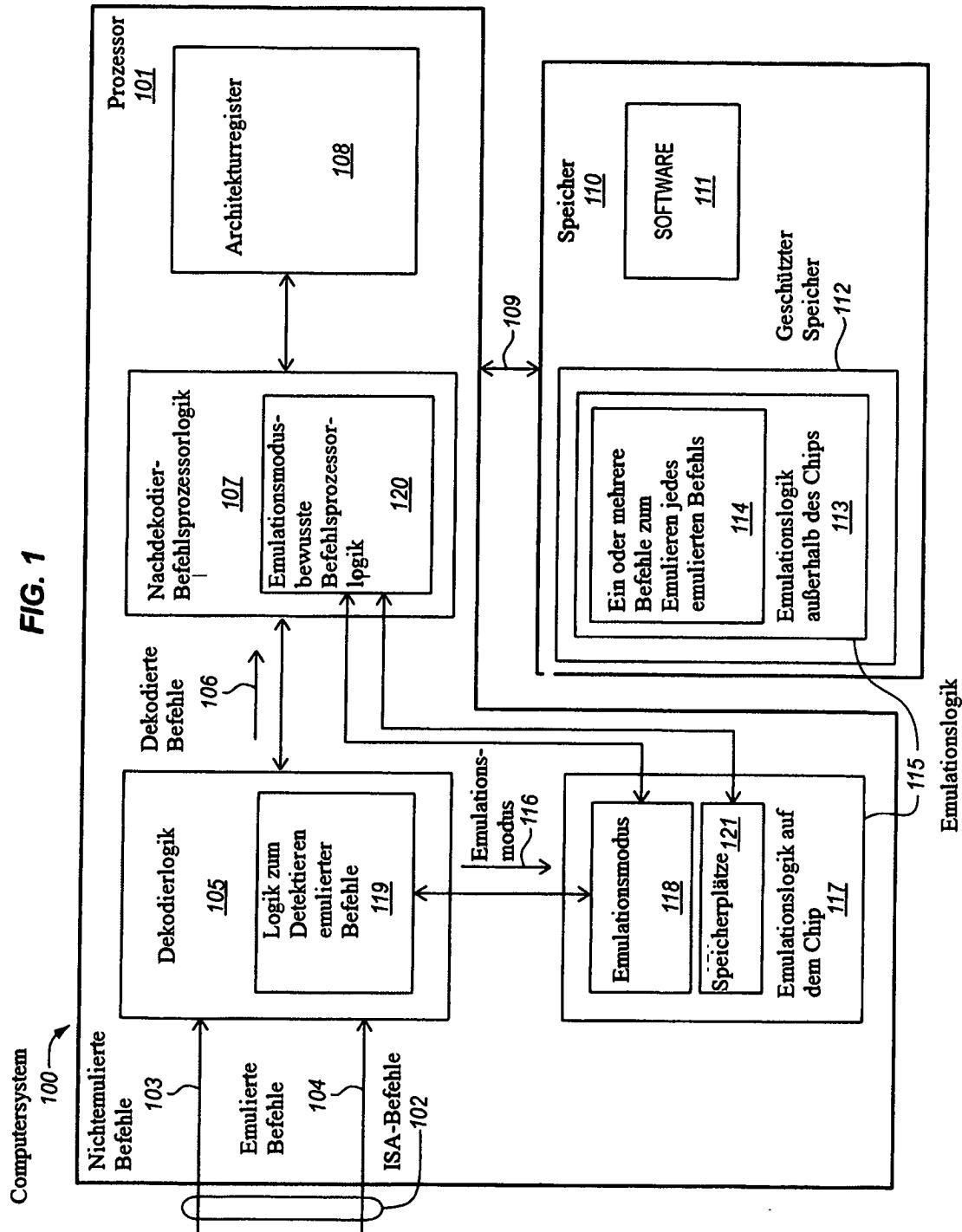

**[0021]** **Fig.** 16 ein Blockdiagramm eines SoC gemäß einer Ausführungsform der vorliegenden Erfindung,

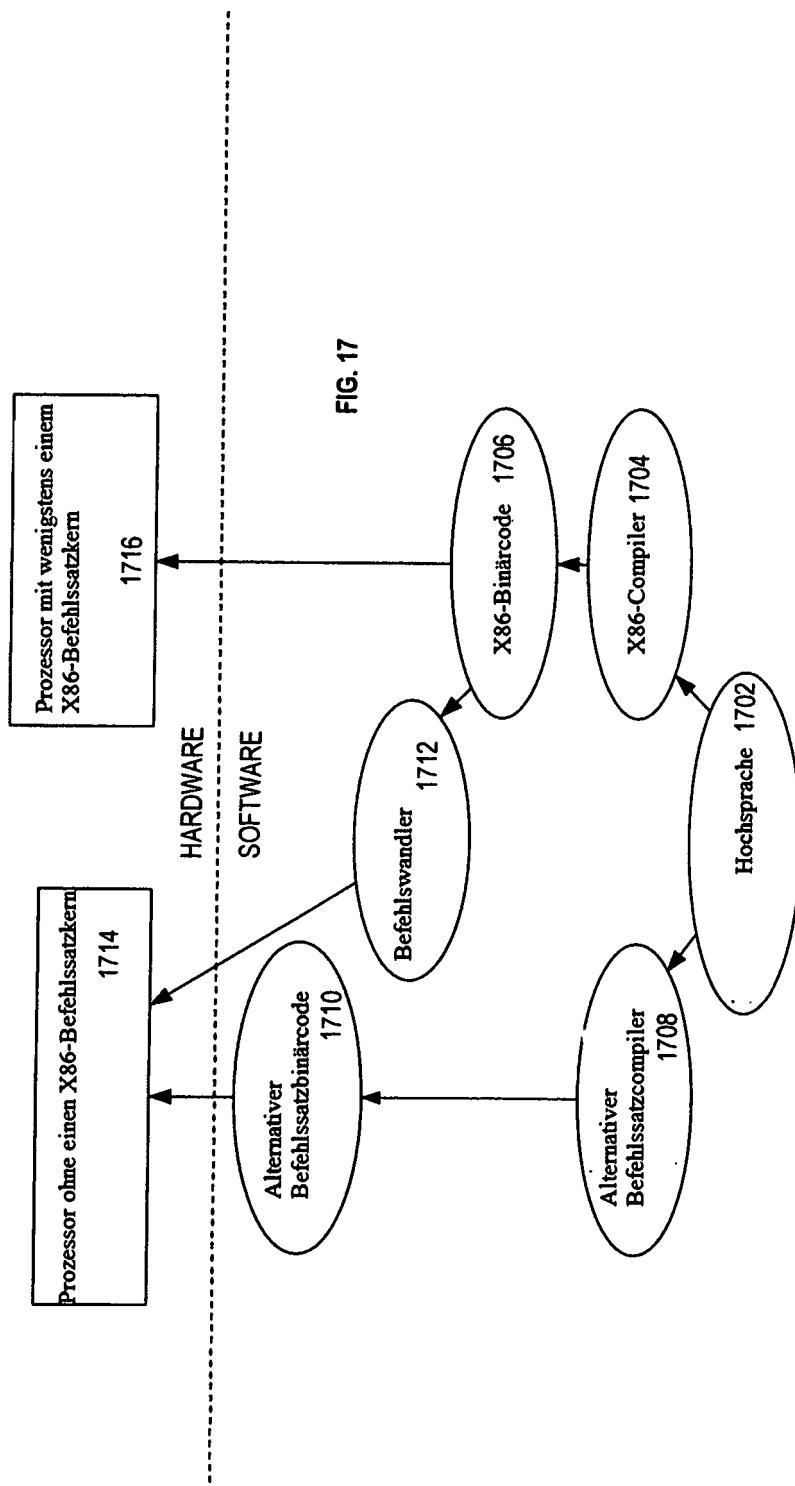

**[0022]** **Fig.** 17 ein Blockdiagramm, das die Verwendung eines Softwarebefehlswandlers zum Umwandeln von Binärbefehlen in einem Quellbefehlssatz zu Binärbefehlen in einem Zielbefehlssatz gemäß Ausführungsformen der Erfindung gegenüberstellt.

#### Ausführliche Beschreibung von Ausführungsformen

**[0023]** Vorliegend sind Prozessoren, Verfahren und Systeme zur Befehlsemulation offenbart. In der folgenden Beschreibung sind zahlreiche spezifische Details dargelegt (beispielsweise spezifische emulationsmodusbewußte Logik, Ansätze zum Behandeln von Ausnahmebedingungen, Typen privilegierter Betriebsmittel und Information, Logikimplementierungen, Mikroarchitekturdetails, Operationssequenzen, Logikpartitionierungs-/Integrationsdetails, Hardware-/Softwarepartitionierungsdetails, Prozessorkonfigurationen, Typen und Wechselbeziehungen von Systemkomponenten und ähnliche). Jedoch versteht sich, dass Ausführungsformen der Erfindung ohne diese spezifischen Details umgesetzt werden können. In anderen Beispielen sind wohlbekannte Schaltungen, Strukturen und Techniken nicht im Detail gezeigt, um das Verständnis dieser Beschreibung nicht zu verschleiern.

**[0024]** **Fig.** 1 zeigt ein Blockdiagramm einer Ausführungsform eines Computersystems **100**. In verschiedenen Ausführungsformen kann das Computersystem einen Desktopcomputer, Laptopcomputer, Notebookcomputer, Tabletcomputer, Netbook, Smartphone, Personal Digital Assistant, Mobiltelefon, Server, Netzwerkvorrichtung (beispielsweise Router oder Switch), mobiles Internetgerät (Mobile Internet Device (MID)), Medienabspielgerät, Smart-Fernsehgerät, Set-top-Box, Videospielcontroller oder anderen Typ elektronischer Vorrichtung darstellen.

**[0025]** Das Computersystem enthält eine Ausführungsform eines Prozessors **101**. In einigen Ausführungsformen kann der Prozessor ein Vielzweckprozessor sein. Beispielsweise kann der Prozessor ein Vielzweckprozessor des Typs sein, der gewöhnlich als eine zentrale Prozessoreinheit (central processing unit (CPU)) verwendet wird. In anderen Ausführungsformen kann der Prozessor ein Spezialprozessor sein. Beispiele für geeignete Spezialprozessoren schließen Koprozessoren, Grafikprozessoren, Kommunikationsprozessoren, Netzwerkprozessoren, Kryptografieprozessoren, eingebettete Prozessoren und digitale Signalprozessoren (DSPs) ein, um lediglich einige Beispiele zu nennen, ohne auf diese beschränkt zu sein. Der Prozessor kann irgendeiner von verschiedenen Prozessoren mit komplexem Befehlssatz (complex instruction set computing (CISC)), verschiedenen Prozessoren mit reduziertem Befehlssatz (reduced instruction set computing (RISC)), verschiedenen Prozessoren mit sehr langem Befehlswort (very long instruction word (VLIW)), verschiedenen Hybriden derselben oder vollständig anderen Prozessortypen sein.

ren, Kommunikationsprozessoren, Netzwerkprozessoren, Kryptografieprozessoren, eingebettete Prozessoren und digitale Signalprozessoren (DSPs) ein, um lediglich einige Beispiele zu nennen, ohne auf diese beschränkt zu sein. Der Prozessor kann irgendeiner von verschiedenen Prozessoren mit komplexem Befehlssatz (complex instruction set computing (CISC)), verschiedenen Prozessoren mit reduziertem Befehlssatz (reduced instruction set computing (RISC)), verschiedenen Prozessoren mit sehr langem Befehlswort (very long instruction word (VLIW)), verschiedenen Hybriden derselben oder vollständig anderen Prozessortypen sein.

**[0026]** Das Computersystem enthält außerdem eine Ausführungsform eines Speichers **110**, der mit dem Prozessor **101** durch einen Kopplungsmechanismus **109** gekoppelt ist. Jeder konventionelle Kopplungsmechanismus, der im Stand der Technik zum Koppeln eines Prozessors und eines Speichers bekannt ist, ist geeignet. Beispiele für solche Mechanismen schließen Schaltverbindungen, Busse, Hubs, Speichercontroller, Chipsätze, Chipsatzkomponenten und ähnliche sowie Kombinationen derselben ein, ohne auf diese beschränkt zu sein. Der Speicher kann eine oder mehrere Speichervorrichtungen entweder des gleichen oder unterschiedlicher Typen aufweisen. Ein gewöhnlich verwendet Speichertyp, der für Ausführungsformen geeignet ist, ist dynamischer Speicher mit wahlfreiem Zugriff (dynamic random access memory (DRAM)), obwohl andere Speichertypen (beispielsweise Flashspeicher) alternativ verwendet werden können.

**[0027]** Der Speicher **110** kann darin Software **111** gespeichert aufweisen. Die Software kann beispielsweise ein oder mehrere Betriebssysteme (operating system (OS)) und eine oder mehrere Anwendungen enthalten. Im Betrieb kann ein Teil der Software in den Prozessor geladen und auf dem Prozessor zum Ablauen gebracht werden. Wie gezeigt, kann der Prozessor ISA-Befehle **102** eines Befehlssatzes des Prozessors empfangen. Beispielsweise kann eine Befehlseinholeeinheit die ISA-Befehle einholen. Die ISA-Befehle können Makrobefehle, Assemblerbefehle, Befehle auf Maschinenebene oder andere Befehle darstellen, die an den Prozessor geliefert werden, um dekodiert und ausgeführt zu werden. Wie gezeigt, können die ISA-Befehle in einigen Ausführungsformen sowohl nichtemulierte Befehle **103** als auch einen oder mehrere Typen emulierter Befehle **104** enthalten.

**[0028]** Der Prozessor enthält eine Dekodierlogik **105**. Die Dekodierlogik kann auch als eine Dekodiereinheit oder ein Dekodierer bezeichnet werden. Die Dekodierlogik kann die ISA-Befehle **102** empfangen. Im Falle der nichtemulierten Befehle **103** kann die Dekodierlogik die Befehle relativ höherer Ebenen dekodieren und einen oder mehrere Mikrobefehle, Mikro-

operationen, Mikrocode-Zugangspunkte relativ niedriger Ebene oder andere Befehle relativ niedriger Ebene oder Steuersignale, die von den ISA-Befehlen abgeleitet sind, ausgeben. In der Zeichnung sind diese als dekodierte Befehle **106** gezeigt. Die dekodierten Befehle, die von dem Dekodierer ausgeben werden, können die ISA-Befehle höherer Ebene, die in den Dekodierer eingegeben werden, widerspiegeln, darstellen und/oder von diesen abgeleitet sein, und können die ISA-Befehle durch eine oder mehrere Operationen niedrigerer Ebene (beispielsweise auf Schaltungsebene oder Hardwareebene) implementieren. Der Dekodierer kann unter Verwendung verschiedener unterschiedlicher Mechanismen implementiert sein, einschließlich Mikrocode-Nurlesespeicher (read only memories (ROMs)), Wertetabellen, Hardwareimplementierungen, programmierbarer Logikarrays (PLAs) und anderer Mechanismen, die verwendet werden, um Dekodierer, die im Stand der Technik bekannt sind, zu implementieren, ohne auf diese beschränkt zu sein.

**[0029]** Eine Nachdekodier-Befehlsprozessorlogik **107** ist mit der Dekodierlogik gekoppelt. Die Nachdekodier-Befehlsprozessorlogik kann einen Nachdekodierabschnitt der Befehlsverarbeitungspipeline des Prozessors darstellen. Die Nachdekodier-Befehlsprozessorlogik kann die dekodierten Befehle **106** empfangen und verarbeiten. Gewöhnlich kann die Nachdekodier-Befehlsprozessorlogik eine Registerlese- und/oder Speicherleselogik, Ausführungslogik, Register- und/oder Speicherrückschreiblogik und Ausnahmebehandlerlogik enthalten, obwohl die Logik von einer Architektur zur anderen variieren kann und der Schutzbereich der Erfindung nicht auf solche Logik beschränkt ist. In einigen Ausführungsformen kann, beispielsweise im Falle einer ungeordneten Prozessorpipeline, die Nachdekodier-Befehlsprozessorlogik optional andere Logik enthalten, wie etwa beispielsweise Zuweisungslogik, Umbenennungslogik, Planungslogik, Rückzugs- oder Überweisungslogik oder ähnliche.

**[0030]** Der Prozessor enthält auch einen oder mehrere Sätze architektonisch sichtbarer oder Architekturregister **108**. Die architektonisch sichtbaren Register stellen Register dar, die für Software und/oder einen Programmierer und/oder die Register, die durch die ISA-Befehle **102** angegeben werden, um Operanden zu bestimmen, sichtbar sind. Diese Architekturregister werden anderen nichtarchitektonischen oder nichtarchitektonisch sichtbaren Registern in einer gegebenen Mikroarchitektur (beispielsweise temporäre Register, die von Befehlen, Umordnungspuffern, Rückzugsregistern etc. verwendet werden) gegenübergestellt. Diese Architekturregister stellen allgemein Prozessorspeicherplätze auf dem Chip dar, die betrieben werden können, um Daten zu speichern. Diese Architekturregister werden hier oft einfach als Register bezeichnet. Beispielsweise kön-

nen die Architekturregister einen Satz Vielzweckregister, einen Satz Register mit gepackten Daten, einen Satz Fließkommaregister, einen Satz Ganzzahlregister oder irgendeine Kombination derselben einschließen. Die Architekturregister können auf unterschiedliche Arten in unterschiedlichen Mikroarchitekturen unter Verwendung wohlbekannter Techniken implementiert sein und sind nicht auf irgendeinen bestimmten Schaltungstyp beschränkt. Beispiele geeigneter Typen von Architekturregistern schließen eigene physikalische Register, dynamisch zugewiesene physikalische Register unter Verwendung von Registerumbenennung und Kombinationen derselben ein, ohne auf diese beschränkt zu sein.

**[0031]** Die Nachdekodier-Befehlsprozessorlogik **107** ist mit den Registern **108** gekoppelt. Die Nachdekodier-Befehlsprozessorlogik kann Daten von den Registern empfangen und Daten in diese schreiben oder speichern. Beispielsweise kann die Registerleselogik Daten aus Registern lesen, die als Quelloperanden von Befehlen angezeigt sind, und/oder kann die Rückschreiblogik Ergebnisse in Register schreiben oder speichern, die als Zieloperanden der Befehle angezeigt sind. Die Nachdekodier-Befehlsprozessorlogik ist außerdem mit dem Speicher **110** gekoppelt und kann Daten von dem Speicher empfangen und in diesen speichern. Beispielsweise kann die Speicherleselogik Daten aus Speicherplätzen lesen, die durch Befehle angezeigt sind, und/oder kann die Speicherrückschreiblogik Daten in Speicherplätze schreiben, die durch Befehle angezeigt sind.

**[0032]** Unter erneuter Bezugnahme auf **Fig. 1** können die emulierten Befehle **104** auch an die Dekodierlogik **105** geliefert werden. Im Gegensatz zu den nichtemulierten Befehlen **103** können die emulierten Befehle **104** nicht vollständig durch die Dekodierlogik dekodiert und als entsprechende dekodierte Befehle **106** der Nachdekodier-Befehlsprozessorlogik **107** bereitgestellt werden. Vielmehr kann die Emulationslogik **115** in einigen Ausführungsformen bereitgestellt werden, um den/die emulierten Befehl(e) **104** zu emulieren. Im Stand der Technik werden verschiedene unterschiedliche Begriffe für solche Emulation verwendet, wie etwa beispielsweise Befehlsübersetzung, binäre Übersetzung, Codemorphing, Befehlsinterpretation und ähnliche. Der Begriff Emulation wird hier breit verwendet, um diese unterschiedlichen Begriffe, die in der Industrie verwendet werden, zu umfassen.

**[0033]** Wie gezeigt, kann die Emulationslogik **115** in einigen Ausführungsformen zwischen teilweise auf dem Chip befindlicher Logik **117** und teilweise außerhalb des Chips befindlicher Emulationslogik verteilt werden, obwohl dies nicht notwendig ist. In anderen Ausführungsformen kann die gesamte Emulationslogik **115** optional auf dem Chip sein, oder kann ein größerer Teil optional außerhalb des Chips sein, ob-

wohl typischerweise wenigstens ein Teil der Emulationslogik auf dem Chip ist (beispielsweise ein Emulationsmodus **118**, irgendeine emulationsmodusbewußte Befehlsprozessorlogik **120** in der Pipeline etc.). Die Emulationslogik auf dem Chip ist fest, speicherresident oder liegt permanent mit dem Prozessor auf dem Chip vor. Gewöhnlich liegt die Emulationslogik mit dem Prozessor auf dem Chip vor, selbst wenn der Prozessor ausgeschaltet ist, vor einem Bootvorgang und/oder zum Zeitpunkt der Fertigstellung der Herstellung. Beispiele geeigneter Emulationslogik auf dem Chip schließt Hardware (beispielsweise integrierte Schaltungen, Transistoren etc.), Firmware (beispielsweise ROM auf dem Chip, EPROM, Flashspeicher oder anderen permanenten oder nichtflüchtigen Speicher und nichtflüchtige Befehle, die darin gespeichert sind) oder eine Kombination derselben ein, ohne auf diese beschränkt zu sein.

**[0034]** Die Emulationslogik **113** außerhalb des Chips kann in dem Speicher **110** enthalten sein. Die Emulationslogik außerhalb des Chips kann mit der Emulationslogik auf dem Chip gekoppelt sein oder auf andere Weise mit dieser in Kommunikation stehen. In einigen Ausführungsformen kann die Emulationslogik außerhalb des Chip in einem geschützten Bereich oder einem Abschnitt **112** des Speichers enthalten sein. In einigen Ausführungsformen kann der geschützte Abschnitt zur Verwendung durch Hardware auf dem Chip und/oder Firmwarelogik allein des Prozessors, jedoch nicht für die Software **111**, die auf dem Prozessor ausgeführt wird, reserviert sein. Beispielsweise kann in einigen Ausführungsformen die Emulationslogik **117**, die emulationsmodusbewußte Befehlsprozessorlogik **120** und/oder andere potentielle Prozessorlogik auf dem Chip in der Lage sein, auf die Emulationslogik **113** außerhalb des Speichers zuzugreifen und diese zu verwenden, jedoch kann die Software **111** (beispielsweise ein Betriebssystem oder eine Anwendung), die auf dem Prozessor läuft, nicht in der Lage sein, auf die Emulationslogik **113** außerhalb des Chips zuzugreifen oder diese zu verwenden. In einigen Ausführungsformen kann die Emulationslogik außerhalb des Chips vor Zugriff und Modifikation durch Anwendungen, das Betriebssystem, einen virtuellen Maschinenmanager, falls vorhanden, und/oder I/O-Vorrichtungen geschützt sein und/oder für diese unsichtbar sein. Dies kann dabei helfen, Sicherheit zu fördern.

**[0035]** Die Dekodierlogik enthält Logik **119**, um den emulierten Befehl **104** zu detektieren oder erkennen. Beispielsweise kann der Dekodierer den emulierten Befehl anhand eines Opcodes detektieren. In einigen Ausführungsformen kann der Dekodierer bei Detektieren des emulierten Befehls ein Emulationsmodussignal **116** (beispielsweise ein Emulationsfangsignal) an die Emulationslogik **115** liefern. Wie gezeigt, kann die Emulationslogik einen Emulationsmodus **118** aufweisen. Als Beispiel kann der Emulations-

modus ein oder mehrere Bits oder Steuerelemente in einem Steuer- oder Konfigurationsregister des Prozessors enthalten, um anzuzeigen, ob der Prozessor (beispielsweise die Logik **105**, **107** etc.) in dem Emulationsmodus ist oder nicht. In einigen Ausführungsformen kann der Emulationsmodus **118** nach Erhalt des Emulationsmodussignals **116** von dem Dekodierer angenommen werden, das anzeigt, dass ein emulierter Befehl **104** emuliert werden soll.

**[0036]** In einigen Ausführungsformen kann die Dekodierlogik **105** außerdem andere Information bereitstellen, die mit dem Befehl assoziiert ist, der für die Emulationslogik **115** emuliert wird. Beispiele solcher Information schließen potentiell Operandenbezeichner (beispielsweise Quell- oder Zielregisteradressen oder Speicherplätze), Speicheraddresiermodi, unmittelbare Addressen, Konstanten zur Ausführungsbeschleunigung und/oder andere Information, die von dem emulierten Befehl **104** stammt und/oder mit diesem assoziiert ist, ein. Als Beispiel kann jede Information, die von dem emulierten Befehl stammt und/oder mit diesem assoziiert ist, der für das Emulationssystem nützlich ist, um dem Emulationssystem zu ermöglichen, den emulierten Befehl **104** zu emulieren, potentiell bereitgestellt werden.

**[0037]** In einigen Ausführungsformen kann die Emulationslogik **115** einen anderen Satz eines oder mehrerer Befehle **114** enthalten, um jeden anderen Typ des emulierten Befehls **104** zu emulieren. Beispielsweise kann ein erster Satz eines oder mehrerer Befehle **114** bereitgestellt werden, um einen ersten Befehl **104** zu emulieren, der einen ersten Opcode aufweist, und kann ein zweiter, anderer Satz eines oder mehrerer Befehle **114** bereitgestellt werden, um einen zweiten, anderen Befehl **104** zu emulieren, der einen zweiten, anderen Opcode aufweist. In einigen Ausführungsformen kann jeder Satz wenigstens drei Befehle enthalten. In der gezeigten Ausführungsform kann der Satz eines oder mehrerer Befehle **114** in der Emulationslogik **113** außerhalb des Chips enthalten sein, obwohl dies nicht notwendig ist. In anderen Ausführungsformen können die Befehle **114** auf dem Chip bereitgestellt werden (beispielsweise in einem permanenten oder nichtflüchtigen Speicher der Emulationslogik **117** auf dem Chip). In noch weiteren Ausführungsformen kann ein Teil der Befehle **114** auf dem Chip bereitgestellt werden (beispielsweise in der Emulationslogik auf dem Chip), und kann ein Teil außerhalb des Chips bereitgestellt werden (beispielsweise in der Emulationslogik außerhalb des Chips).

**[0038]** In einigen Ausführungsformen kann jeder der Befehle des Satzes einen oder mehrere Befehle **114**, die verwendet werden, um den emulierten Befehl **104** zu emulieren, von der Emulationslogik **115** eingeholt oder auf andere Weise empfangen und der Dekodierlogik **105** bereitgestellt werden. In einigen Ausführungsformen kann jeder der Befehle des Satzes von

einem oder mehreren Befehlen **114**, die zum Emulieren des emulierten Befehls **104** verwendet werden, aus einem gleichen Befehlssatz stammen wie der emulierte Befehl **104**. Die Dekodierlogik **105** kann betrieben werden, jeden aus dem Satz von einem oder mehreren Befehlen **114** in entsprechende dekodierte Befehle **106** zu dekodieren. Die dekodierten Befehle können der Nachdekodier-Befehlsprozessorlogik **107** bereitgestellt werden.

**[0039]** Die Nachdekodier-Befehlsprozessorlogik enthält eine Ausführungsform einer emulationsmodusbewussten Befehlsprozessorlogik **120**. Wie gezeigt, kann die emulationsmodusbewusste Befehlsprozessorlogik mit dem Emulationsmodus **118** gekoppelt sein oder diesen auf andere Weise kennen. In einigen Ausführungsformen kann die emulationsmodusbewusste Befehlsprozessorlogik betrieben werden, um wenigstens einige der dekodierten Versionen der Befehle **114** wenigstens auf einige andere Arten zu verarbeiten, wenn der Prozessor in dem Emulationsmodus ist, als wenn der Prozessor nicht in dem Emulationsmodus ist. Es gibt verschiedene unterschiedliche Aspekte, unter denen die Verarbeitung anders sein kann. In einigen Ausführungsformen kann Störungs- oder Fehlerbehandlung anders durchgeführt werden, wenn der Emulationsmodus vorliegt, als wenn der Emulationsmodus nicht vorliegt. In anderen Ausführungsformen kann Zugriff auf bestimmte Typen von Betriebsmitteln und/oder Information, wie etwa beispielsweise sichere, privilegierte oder auf andere Weise zugriffsgesteuerte Betriebsmittel und/oder Information, anders behandelt werden, wenn der Emulationsmodus vorliegt, als wenn der Emulationsmodus nicht vorliegt. Beispielsweise kann Zugriff auf die Betriebsmittel und/oder Information ermöglicht werden, wenn der Emulationsmodus vorliegt, aber nicht ermöglicht werden, wenn der Emulationsmodus nicht vorliegt.

**[0040]** Wenn der Emulationsmodus vorliegt, kann die Nachdekodier-Befehlsprozessorlogik auf Speicherplätze **121** zugreifen. In der gezeigten Ausführungsform sind die Speicherplätze **121** Teil der Emulationslogik **117** auf dem Chip. Alternativ können die Speicherplätze in der Emulationslogik außerhalb des Chips enthalten sein oder teilweise in der Emulationslogik auf dem Chip und teilweise in der Emulationslogik außerhalb des Chips enthalten sein. Die Speicherplätze können verwendet werden, um temporäre Variablen, Zwischenergebnisse und/oder Ausführungszustand, der mit der Ausführung des Satzes von Befehlen **114** assoziiert ist, zu speichern. Dies kann helfen, zu vermeiden, dass der Ausführungszustand des ursprünglichen Programms, das den emulierten Befehl **104** enthält, gespeichert werden muss, und/oder kann helfen, solchen Ausführungszustand (beispielsweise den Inhalt der Architekturregister **108**) daran zu hindern, durch die Verarbeitung des Satzes von Befehlen **114** fehlerhaft zu werden. In einigen

Ausführungsformen können die Speicherplätze **121** Architekturregister emulieren, obwohl dies nicht notwendig ist. In einigen Ausführungsformen kann der Inhalt der Speicherplätze **121** vom Zugriff durch Anwendungen, Betriebssysteme, virtuellen Maschinenmanagern, I/O-Vorrichtungen, Interrupts und ähnlichen unabhängig, isoliert und/oder geschützt sein. Bei Abschluss des Satzes von Befehlen **114** kann der Architekturzustand des Prozessors aktualisiert werden (beispielsweise kann ein Ergebnis der Speicherplätze **121** in die Register **108** gespeichert werden). Dies kann mit niedrigem Latenzzugriff erfolgen. Gewöhnlich kann dies verwendet werden, um die Änderung im Architekturzustand, die aufgetreten wäre, und/oder das Verhalten des Prozessors, das erfolgt wäre, wenn der emulierte Befehl **104** tatsächlich direkt ausgeführt worden wäre, zu approximieren, imitieren, nachzubauen oder auf andere Weise zu emulieren.

**[0041]** Um ein Verschleiern der Beschreibung zu vermeiden, wurde ein relativ einfacher Prozessor **101** gezeigt und beschrieben. In anderen Ausführungsformen kann der Prozessor optional andere wohlbekannte Komponenten enthalten. Es gibt buchstäblich zahlreiche unterschiedliche Kombinationen und Konfigurationen von Komponenten in Prozessoren, und die Ausführungsformen sind nicht auf irgendeine bestimmte Kombination oder Konfiguration beschränkt. Der Prozessor kann eine integrierte Schaltung oder einen Satz eines oder mehrerer Halbleiterplatten oder -chips darstellen (beispielsweise eine einzelne Leiterplatte oder Chip oder ein Paket, das zwei oder mehr Leiterplatten oder Chips enthält). In einigen Ausführungsformen kann der Prozessor ein System-on-Chip (SoC) und/oder einen Chip-Multiprozessor (CMP) darstellen.

**[0042]** Einige Prozessoren verwenden relativ komplexe Operationen. Beispielsweise führen einige Befehle mehrere Speicherzugriffe anstatt lediglich einen einzelnen Speicherzugriff durch. Ein Beispiel ist ein Befehl zum Vektoreinholen, um einen Vektor von Datenelementen aus einem Speicher zu holen. Als ein weiteres Beispiel können bestimmte Befehle zahlreiche Datenelementvergleiche durchführen, anstatt ein einzelnes Paar von Datenelementen oder Paare entsprechenden der Datenelementen in zweigepackten Daten zu vergleichen. Beispiele sind Vektorkonfliktbefehle und Zeichenkettenverarbeitungsbefehle. Ein Ansatz ist, solche komplexen Operationen vollständig in Hardware zu implementieren. Jedoch kann die Menge an benötigter Hardware tendenziell beträchtlich sein, was dazu führen kann, Herstellungs-kosten, Chipgröße und Stromverbrauch zu erhöhen. Ein weiterer Ansatz ist, solche komplexen Operationen wenigstens teilweise in Mikrocode zu implementieren. Die Verwendung von Mikrocode kann helfen, die Menge an benötigter Hardware zu reduzieren, um solche komplexen Operationen zu implementieren,

und/oder kann helfen, bestimmte existierende Hardware wiederzuverwenden. Jedoch benutzen einige Prozessoren keinen Mikrocode (beispielsweise keinen Mikrocode zum Implementieren irgendeines Befehls eines Befehlssatzes).

**[0043]** In einigen Ausführungsformen kann ein relativ komplexerer Befehl mit dem Satz eines oder mehrerer relativ einfacherer Befehle emuliert werden. Die Begriffe komplexer und einfacher sind relative Begriffe, keine absoluten Begriffe, die zueinander relativ sind. Vorteilhafterweise kann dies potentiell helfen, die Menge an Hardware zu reduzieren, die benötigt wird, um den komplexeren Befehl zu implementieren, und/oder kann helfen, Wiederverwendung existierender Hardware zu ermöglichen, die von den ein oder mehreren Befehlen verwendet wird, die verwendet werden, um den komplexeren Befehl zu emulieren. In einigen Ausführungsformen kann die Emulation des komplexeren Befehls mit den ein oder mehreren einfacheren Befehlen verwendet werden, um eine Mikrocode-ähnliche Implementation des komplexeren Befehls bereitzustellen, selbst wenn der Prozessor in einigen Ausführungsformen nicht konfiguriert sein kann, um Mikrocode zu verwenden, und/oder nicht konfiguriert sein kann, Mikrocode zu verwenden, um den komplexeren Mikrobefehl zu implementieren.

**[0044]** **Fig. 2** zeigt ein Blockflussdiagramm einer Ausführungsform eines Verfahrens **230** zum Emulieren eines Befehls in einem Prozessor. In einigen Ausführungsformen können die Operationen und/oder Verfahren aus **Fig. 2** durch den Prozessor aus **Fig. 1** und/oder innerhalb dieses Prozessors durchgeführt werden. Die Komponenten, Strukturen und spezifischen optionalen Details, die hier für den Prozessor aus **Fig. 1** beschrieben sind, gelten optional für die Operationen und/oder Verfahren aus **Fig. 2**. Alternativ können die Operationen und/oder Verfahren aus **Fig. 2** ähnlichen oder ganz anderen Prozessor und/oder innerhalb dieses Prozessors durchgeführt werden. Darüber hinaus kann der Prozessor aus **Fig. 1** Operationen und/oder Verfahren durchführen, die ähnlich oder anders sind als die aus **Fig. 2**.

**[0045]** Das Verfahren schließt Empfangen eines ersten Befehls an Block **231** ein. In einigen Ausführungsformen kann der erste Befehl an einem Dekodierer empfangen werden. Das Verfahren schließt Bestimmen des Emulierens des ersten Befehls an Block **232** ein. In einigen Ausführungsformen kann der Dekodierer bestimmen, den ersten Befehl zu emulieren, indem bestimmt wird, dass ein Opcode des ersten Befehls in einem Satz eines oder mehrerer Opcodes für zu emulierende Befehle vorliegt. Das Verfahren schließt an Block **233** Empfangen eines Satzes eines oder mehrerer Befehle ein, die zum Emulieren des ersten Befehls verwendet werden sollen. In einigen Ausführungsformen kann der Satz von Befehlen an

dem Dekodierer von Emulationslogik auf dem Chip oder Emulationslogik außerhalb des Chips oder einer Kombination derselben empfangen werden. In einigen Ausführungsformen kann jeder Befehl aus einem gleichen Befehlssatz wie der erste Befehl stammen. Das Verfahren schließt Verarbeiten eines oder mehrerer Steuersignale an Block **234** ein, die von einem Befehl des Satzes anders abgeleitet sind, wenn ein Emulationsmodus vorliegt, als wenn kein Emulationsmodus vorliegt.

**[0046]** Dies kann in unterschiedlichen Ausführungsformen auf unterschiedliche Weise vorgenommen werden. In einigen Ausführungsformen können Ausnahmebedingungen, denen während einer Verarbeitung eines Befehls des Satzes begegnet wird, unterschiedlich behandelt werden. In einigen Ausführungsformen kann die Verarbeitung eines Befehls des Satzes Zugriff auf Information und/oder Betriebsmittel ermöglichen, die dem gleichen Befehl (d. h. einem Befehl, der den gleichen Opcode aufweist andernfalls nicht zugänglich wären, wenn dies nicht innerhalb eines Emulationsmodus vorgenommen wird.

**[0047]** **Fig. 3** zeigt ein Blockdiagramm, das eine Ausführungsform der Logik **301** zum Emulieren eines Befehls (beispielsweise eines komplexen Befehls) **304** mit einem Satz eines oder mehrerer Befehle (beispielsweise einfacherer Befehle) **314** zeigt. In einigen Ausführungsformen kann die Logik aus **Fig. 3** in dem Prozessor und/oder dem Computersystem aus **Fig. 1** enthalten sein. Alternativ kann die Logik aus **Fig. 3** in einem ähnlichen oder anderen Prozessor oder Computersystem enthalten sein. Darüber hinaus kann der Prozessor und/oder das Computersystem aus **Fig. 1** ähnliche oder andere Logik als die aus **Fig. 3** enthalten.

**[0048]** Ein Befehl (beispielsweise ein komplexer Befehl) **304**, der emuliert werden soll, kann für die Dekodierlogik **305** bereitgestellt werden. Die Dekodierlogik kann eine Logik **319** zum Detektieren des Befehls **304** enthalten, um beispielsweise zu detektieren, dass ein Opcode des Befehls **304** in dem Satz von Opcodes für Befehle, die zu emulieren sind, enthalten ist. Wie gezeigt, kann der Prozessor in einigen Ausführungsformen keinen Mikrocode **330** aufweisen. Die Dekodierlogik kann ein Emulationsmodussignal **316** für die Emulationslogik **35** bereitstellen. In verschiedenen Ausführungsformen kann die Emulationslogik **315** Logik auf dem Chip, Logik außerhalb des Chips oder sowohl auf dem Chip als auch außerhalb des Chips enthalten. Die Emulationslogik kann als Antwort auf das Emulationsmodussignal in einen Emulationsmodus **318** eintreten.

**[0049]** Die Emulationslogik enthält außerdem einen Satz eines oder mehrerer einfacherer (beispielsweise einfacherer) Befehle **314**, die verwendet werden können, um den (beispielsweise komplexeren) Be-

fehl **304** zu emulieren. In einigen Ausführungsformen können die ein oder mehreren Befehle **314** aus dem gleichen Befehlssatz wie der Befehl **304** stammen. In einigen Ausführungsformen können die ein oder mehreren Befehle **314** mit anderen Befehlen identisch sein, die dekodiert und ausgeführt werden, wenn kein Emulationsmodus vorliegt. Um den (beispielsweise komplexen) Befehl **304** zu emulieren, kann jeder der ein oder mehreren (beispielsweise einfacheren) Befehle **314** an die Dekodierlogik geliefert werden. Die Dekodierlogik kann jeden der Befehle **314** als einen oder mehrere dekodierte Befehle **306** dekodieren.

**[0050]** Eine Nachdekodier-Befehlsprozessorlogik **307** kann die dekodierten Befehle **306** erhalten, die den Befehlen **314** entsprechen. Die Nachdekodier-Befehlsprozessorlogik kann eine Ausführungsform der emulationsmodusbewussten Logik **320** enthalten. Wie gezeigt, kann die emulationsmodusbewusste Logik in einigen Ausführungsformen mit dem Emulationsmodus **318** gekoppelt sein oder diesen auf andere Weise kennen. In einigen Ausführungsformen kann die emulationsmodusbewusste Logik betrieben werden, um die dekodierten Befehle **306**, die den Befehlen **314** entsprechen, anders zu verarbeiten, wenn der Prozessor in dem Emulationsmodus **318** ist, als wenn der Prozessor nicht in dem Emulationsmodus ist. In einigen Ausführungsformen kann Störungs- oder Fehlerbehandlung anders durchgeführt werden, wenn der Emulationsmodus vorliegt, als wenn der Emulationsmodus nicht vorliegt. Beispielsweise kann die Logik **320** optionale Aspekte verwenden, die unten für **Fig. 4** diskutiert sind. In anderen Ausführungsformen kann Zugriff auf bestimmte Betriebsmittel und/oder Information selektiv bereitgestellt werden, wenn der Emulationsmodus vorliegt, aber nicht, wenn der Prozessor nicht in dem Emulationsmodus ist. Beispielsweise kann die Logik **320** optionale Aspekte verwenden, die unten für **Fig. 5** diskutiert sind.

**[0051]** Vorteilhafterweise kann in einigen Ausführungsformen ein komplexerer Befehl durch einen Satz einfacherer Befehle/Operationen implementiert sein. Vorteilhafterweise kann dies potentiell helfen, die Menge an Hardware zu reduzieren, die benötigt wird, um den komplexeren Befehl zu implementieren, und/oder kann helfen, Wiederverwendung existierender Hardware zu ermöglichen, die von den ein oder mehreren Befehlen verwendet wird, die verwendet werden, um den komplexeren Befehl zu emulieren. In einigen Ausführungsformen kann die Emulation des komplexeren Befehls mit den ein oder mehreren einfacheren Befehlen verwendet werden, um eine Mikrocode-ähnliche Implementation des komplexeren Befehls bereitzustellen, obwohl der Prozessor in einigen Ausführungsformen nicht konfiguriert sein kann, um Mikrocode zu verwenden und/oder nicht konfiguriert sein kann, Mikrocode zu verwenden, um den komple-

xeren Befehl zu implementieren. In einigen Ausführungsformen können die einfacheren Befehle/Operationen sogar aus dem gleichen Befehlssatz stammen wie der komplexere Befehl.

**[0052]** Solche Emulation komplexerer Befehle mit einfachen Befehlen ist lediglich ein Beispiel für einen möglichen Grund, einen Befehl zu emulieren. In anderen Ausführungsformen kann der emulierte Befehl einer sein, der relativ weniger häufig verwendet wird (beispielsweise selten verwendet wird), und kann mit einem oder mehreren Befehlen emuliert werden, die relativ häufiger verwendet werden. Vorteilhafterweise kann dies potentiell helfen, die Menge an Hardware, die benötigt wird, um den selten verwendeten Befehl zu implementieren, zu reduzieren, und/oder kann helfen, Wiederverwendung existierender Hardware zu ermöglichen, die von den ein oder mehreren Befehlen verwendet wird, die verwendet werden, um den selten verwendeten Befehl zu emulieren. In noch weiteren Ausführungsformen kann der emulierte Befehl ein älterer und/oder veralteter Befehl sein und/oder kann einer sein, der im Begriff ist, zu veralten, und kann mit den ein oder mehreren anderen Befehlen emuliert werden. Vorteilhafterweise kann die Emulation helfen, dem Befehl, der veraltet, zu ermöglichen, weiterhin ausgeführt zu werden und somit Rückwärtskompatibilität für Software bereitzustellen, während gleichzeitig potentiell geholfen wird, die Menge an Hardware zu reduzieren, die benötigt wird, um den veralteten Befehl zu implementieren, und/oder geholfen wird, Wiederverwendung existierender Hardware zu ermöglichen, die von den ein oder mehreren Befehlen verwendet wird, die verwendet werden, um den veralteten Befehl zu emulieren. Noch weitere Verwendungen der hier offebarten Emulation werden Durchschnittsfachleuten ersichtlich sein, die die vorliegende Offenbarung zur Kenntnis nehmen.

**[0053]** **Fig. 4** zeigt ein Blockdiagramm, dass eine Ausführungsform von Logik **401** zeigt, um einem Prozessor zu ermöglichen, Ausnahmebedingungen anders zu behandeln, wenn ein Emulationsmodus vorliegt, als wenn kein Emulationsmodus vorliegt. In einigen Ausführungsformen kann die Logik aus **Fig. 4** in dem Prozessor und/oder dem Computersystem aus **Fig. 1** und/oder der Logik aus **Fig. 3** enthalten sein. Alternativ kann die Logik aus **Fig. 4** in einem ähnlichen oder anderen Prozessor oder Computersystem enthalten sein. Darüber hinaus kann der Prozessor und/oder das Computersystem aus **Fig. 1** und/oder die Logik aus **Fig. 3** ähnliche oder andere Logik als die aus **Fig. 4** enthalten.

**[0054]** Eine erste Instanz **403-1** eines gegebenen Befehls (beispielsweise eines Befehls, der einen gegebenen Opcode aufweist) wird an die Dekodierlogik **405** geliefert, wenn der Prozessor nicht in einem Emulationsmodus **418** ist. Eine zweite Instanz **403-2**

des gleichen gegebenen Befehls (beispielsweise eines anderen Befehls, der den gleichen gegebenen Opcode aufweist) wird an die Dekodierlogik geliefert, wenn der Prozessor in dem Emulationsmodus **418** arbeitet. Die zweite Instanz **403-2** des gegebenen Befehls kann als Antwort auf einen Dekodierer, der den emulierten Befehl erhält, aus einem Satz eines oder mehrerer Befehle **414** bereitgestellt werden, die verwendet werden, um einen emulierten Befehl zu emulieren. Der Satz von Befehlen kann in einer Emulationslogik **415** enthalten sein, die auf dem Chip, außerhalb des Chips oder teilweise auf dem Chip und außerhalb des Chips ist. Die Emulationslogik **515** kann jede der optionalen Charakteristiken aufweisen, die hier an anderer Stelle für die Emulationslogik erwähnt werden. Die Dekodierlogik kann (beispielsweise einen identischen Satz) eines oder mehrerer dekodierter Befehle für jeden der ersten **403-1** und zweiten Instanzen **403-2** des gegebenen Befehls bereitstellen.

**[0055]** Die Nachdekodier-Befehlsprozessorlogik **407** kann den/die dekodierten Befehl(e) **406** erhalten. Die Nachdekodier-Befehlsprozessorlogik weist eine emulationsmodusbewusste Ausnahmebehandlerlogik **420** auf. Die emulationsmodusbewusste Ausnahmebehandlerlogik kann betrieben werden, um Ausnahmebedingungen auf eine emulationsmodusbewusste Weise zu behandeln/verarbeiten. Wie hier verwendet, bezieht sich der Begriff "Ausnahmebedingung" grob auf verschiedene unterschiedliche Typen von Ausnahmebedingungen, die auftreten können, während Befehle verarbeitet werden. Beispiele solcher Ausnahmebedingungen schließen Ausnahmen, Interrupts, Störungen (faults), Fangstellen (traps) und ähnliche ein, ohne darauf beschränkt zu sein. Die Begriffe Ausnahme, Interrupt, Fault und Trap werden im Stand der Technik häufig auf verschiedene Art verwendet. Der Begriff "Ausnahme" wird vermutlich häufiger verwendet, um sich auf eine automatisch erzeugte Steuerungsübergabe an eine Behandlerroutine als Antwort auf Rechteverletzungen, Rechteausnahmen, Page-Faults, Speicherschutzstörungen, Division durch Null, versuchte Ausführung eines ungültigen Opcodes und andere solche Ausnahmebedingungen zu beziehen.

**[0056]** In einigen Ausführungsformen kann, wenn eine Rechteverletzung, ein Page-Fault, eine Speicherschutzstörung, eine Division durch Null, eine versuchte Ausführung eines ungültigen Opcodes oder andere Ausnahmebedingung auftritt, wenn die erste Instanz **403-1** des gegebenen Befehls verarbeitet wird, wenn der Prozessor nicht in dem Emulationsmodus **418** arbeitet, der Prozessor im wesentlichen herkömmliches Behandeln der Ausnahmebedingung durchführen. Beispielsweise kann die Ausnahmebedingung in einigen Ausführungsformen direkt angenommen **440** werden, wobei eine Steuerung an eine Ausnahmebehandlerroutine **441** übergeben wird. Gewöhnlich kann die Ausnahmebehandlerroutine teil

eines Betriebssystems, eines virtuellen Maschinenmonitors oder anderer privilegierter Software sein. Beispiele solcher Behandlerroutinen schließen Page-Fault-Handler, Fehler-Handler, Interrupt-Handler und ähnliche ein, ohne darauf beschränkt zu sein.

**[0057]** Andererseits kann in einigen Ausführungsformen, wenn eine Berechtigungsverletzung, Page-Fault, Speicherschutzstörung, Division durch Null, versuchte Ausführung eines ungültigen Opcodes oder andere Ausnahmebedingung auftritt, wenn die zweite Instanz **403-2** des gegebenen Befehls verarbeitet wird, wenn der Prozessor in dem Emulationsmodus **418** arbeitet, der Prozessor im wesentlichen unkonventionelle Behandlung der Ausnahmebedingung durchführen. Beispielsweise kann die Ausnahmebedingung in einigen Fällen nicht direkt angenommen werden. In einigen Ausführungsformen kann die Logik **420** einen Mechanismus zum Unterdrücken einer andernfalls automatischen Steuerübertragung an eine Ausnahmebehandlerroutine enthalten, die andernfalls aus der Ausnahmebedingung resultieren würde. Die Steuerung braucht nicht direkt von dem Emulationsprogramm zu der Ausnahmebehandlerroutine **441** übertragen zu werden. Vielmehr kann die emulationsmodusbewusste Ausnahmebehandlerlogik **420** in einigen Ausführungsformen Steuerungsübertragung an den Ausnahmebedingungsbehandler **441** vorübergehend unterdrücken und die Ausnahmebedingung indirekt berichten **442**. In einigen Ausführungsformen kann die emulationsmodusbewusste Ausnahmebehandlerlogik **420** die Ausnahmebedingung durch ein oder mehrere Emulationskommunikationsregister **443** indirekt berichten. Die ein oder mehreren Kommunikationsregister können verwendet werden, um Information zwischen der Emulationslogik und dem Programm zu kommunizieren, für das der ursprüngliche Befehl emuliert wird.

**[0058]** In einigen Ausführungsformen kann die emulationsmodusbewusste Ausnahmebeandlerlogik **420** als Antwort auf Auftreten der Ausnahmebedingung, wenn ein Emulationsmodus vorliegt, eine Anzeige der Ausnahmebedingung in einer Ausnahmebedingung oder einem Fehlerstatusflag(s), -feld oder -register **444** speichern. Beispielsweise kann ein einzelnes Bit oder Flag einen ersten Wert (beispielsweise auf binäre Eins gesetzt) aufweisen, um anzuzeigen, dass eine Ausnahmebedingung aufgetreten ist, oder kann einen zweiten Wert (beispielsweise zu binärer Null gelöscht) aufweisen, um anzuzeigen, dass keine Ausnahmebedingung aufgetreten ist. In einigen Ausführungsformen kann die emulationsmodusbewusste Ausnahmebeandlerlogik **420** als Antwort auf Auftreten der Ausnahmebedingung, wenn der Emulationsmodus **418** vorliegt, einen Fehlercode für die Ausnahmebedingung in einem Fehlercodefeld oder -register **445** speichern. Der Fehlercode kann

weitere Information über den Fehler bereitstellen, wie etwa beispielsweise einen Typ des Fehlers und optional weitere Details, um Kommunizieren der Beschaffenheit der Ausnahmebedingung zu unterstützen. Alternativ kann, anstatt die Kommunikationsregister zu verwenden, die Information auf andere Weise signalisiert oder bereitgestellt werden (beispielsweise in Speicher gespeichert werden, durch ein elektrisches Signal berichtet werden etc.).

**[0059]** In einigen Ausführungsformen kann die emulationsmodusbewusste Ausnahmebehandlerlogik **420** außerdem eine Anzeige der Adresse (beispielsweise den Befehlszeiger) des Befehls, der emuliert wird (d. h. desjenigen, der die zweite Instanz **403-2** veranlasste, an die Dekodierlogik **405** gesendet zu werden) bereitstellen. Beispielsweise kann in einigen Ausführungsformen die Adresse **446** des Befehls, der emuliert wird, oben auf dem Stack **447** gespeichert werden. Speichern der Adresse eines gegebenen Befehls, der emuliert wird, auf dem Stack anstatt derjenigen eines der Befehle, die verwendet werden, um diesen gegebenen Befehl zu emulieren, kann dazu führen, dass die Rückgabe von dem Ausnahmebehandler an den emulierten Befehl anstatt an einen der Befehle zurückkehrt, die verwendet werden, um diesen emulierten Befehl zu emulieren. Wenn andernfalls die Rückgabe von dem Ausnahmebehandler an einen der Befehle gerichtet wäre, die verwendet werden, um diesen Befehl zu emulieren, kann dies potentiell ein Problem verursachen. Beispielsweise kann Software (beispielsweise eine Anwendung, ein Betriebssystem etc.) die Befehle nicht kennen, die verwendet werden, um diesen gegebenen Befehl zu emulieren, und kann die assoziierte Adresse nicht erkennen. Das Betriebssystem kann erkennen, dass Steuerfluss an einen unbekannten, ungültigen, risikanten oder nicht erlaubten Ort übertragen wird, und kann potentiell versuchen, die Übertragung zu verhindern.

**[0060]** In einigen Ausführungsformen kann der Satz von Befehlen **414** den Fehlerstatus **444** und/oder den Fehlercode **445** überwachen. Beispielsweise können die Befehle **414** in einigen Ausführungsformen den Fehlerstatus **444** und den Fehlercode **445** aus den Emulationskommunikationsregistern **443** lesen, um die Ausnahmebedingung und Angaben über die Ausnahmebedingung in Erfahrung zu bringen. Wenn der Fehlerstatus **444** eine Ausnahmebedingung anzeigt, kann der Satz von Befehlen **414** in einigen Ausführungsformen die Ausnahmebedingung **449** annehmen. Beispielsweise können einer oder mehrere der Befehle **414** ausgeführt werden, um den Fehlerstatus zu prüfen und Steuerung an den Ausnahmebehandler zu übergeben, wenn ein Fehler angezeigt wird. In einigen Ausführungsformen kann dies einschließen, dass der Satz von Befehlen **414** Steuerung an den Ausnahmebehandler **441** übergibt. In einigen Ausführungsformen kann Information über die Ausnah-

mebedingung (beispielsweise der Fehlercode **445**) für den Ausnahmebehandler **441** bereitgestellt werden. In einigen Ausführungsformen kann die emulierte Befehlsadresse **446** auch an den Ausnahmebehandler **441** geliefert und/oder wenigstens oben auf dem Stack erhalten werden. Die emulierte Befehlsadresse **446** kann von dem Ausnahmebehandler **441** nach Rückgabe vom Behandeln der Ausnahmebedingung verwendet werden. Vorteilhafterweise kann das Betriebssystem oder eine andere Fehlerbehandlerroutine denken, dass der Befehl, der emuliert wird, die Quelle des Fehlers ist.

**[0061]** In einigen Ausführungsformen kann die Emulationslogik Logik zum Testen und zum Berichten, ob Speicherzugriff in dem Befehl korrekt funktioniert, enthalten oder den Typ der Ausnahmebedingung angeben, die entstehen kann. Beispielsweise kann ein spezieller Befehl enthalten sein, um eine Speicheradresse mit emulierten Adressrechten zu testen, um festzustellen, ob die Speicheradresse gültig ist (beispielsweise, ob die Seite vorliegt) und ob das Programm ausreichende Zugriffsrechte besitzt, um den Speicherplatz zu lesen und/oder um den Speicherplatz zu modifizieren. Falls irgendwelche Tests scheitern, kann die Emulationslogik Steuerung an den richtigen Interruptbehandler mit einer Rückgabeadresse übergeben, als ob der Befehl, der emuliert wird, direkt Steuerung an den Ausnahmebehandler übergeben hätte. Als ein weiteres Beispiel kann ein Zustandsautomat eine bedingte Speichertransaktion durchführen, die anzeigt, ob die Speicheroperation gültig wäre. Dies kann verwendet werden, um zu bestimmen, wann eine Speicheroperation durchgeführt werden kann unter der Annahme, dass keine Ausnahme entsteht. Dies kann außerdem verwendet werden, um zu bestimmen, wie viele Bytes eines Befehlsstreams oder einer Zeichenkette aus Befehlsinformation auf sichere Weise ohne Ausnahmen gelesen werden können. Beispielsweise kann dies verwendet werden, um zu testen und zu bestimmen, ob eine Befehlslänge gelesen werden kann oder nicht, oder ob ein Teil der Befehlslänge einen Seitenfehler verursachen würde oder nicht. Die Emulationslogik kann Logik enthalten, um mit Befehlen umzugehen, die mehrere Seiten umfassen, und/oder wenn eine Seite nicht im Speicher vorliegt.

**[0062]** In einigen Ausführungsformen kann die Emulationslogik Logik enthalten, um einen zwischenzeitigen Ausführungsinterruptstatus bereitzustellen, so dass Ausführung der Emulation anhalten und später an dem Zwischenpunkt fortfahren kann. Dies kann insbesondere vorteilhaft sein, wenn Befehle emuliert werden, die lange Dauern oder Ausführungszeiten einschließen. In einigen Ausführungsformen kann der Satz von Befehlen, die verwendet werden, um bestimmte Typen von Befehlen (beispielsweise Zeichenkettenbefehle bewegen, Befehle einholen und andere mit langen Operationen) zu emu-

lieren, den Ausführungszustand der Software aktualisieren, die den Befehl aufweist, der emuliert wird, um eine gegenwärtige Fortschrittsstufe wiederzugeben. Beispielsweise kann die Operation an einem Zwischenpunkt unterbrochen werden, und kann der Satz von Befehlen, die zur Emulation verwendet werden, ein Flag oder Statusbit in dem gespeicherten Maschinenzustand durch den Ausnahmebehandler setzen (beispielsweise in einem Prozessorstatusregister), so dass bei Rückgabe der Emulationscode in der Lage sein kann, das Flag oder Statusbit zu testen, um zu bestimmen, dass er Ausführung von einem Zwischenzustand aus fortsetzt. Das Flag oder Statusbit kann unterbrochene Ausführung anzeigen. Auf diese Weise kann das Programm, wenn es von einem Ausnahmebehandler zurückkehrt, nachdem eine Ausnahmebedingung behandelt wurde, Ausführung an einer zwischenzeitigen Fortschrittsstufe fortsetzen, wo es aufgehört hatte. In einigen Fällen kann ein Befehl (beispielsweise ein Befehl zum Bewegen einer Zeichenkette) Register modifizieren, um einen Zwischenzustand der Operation wiederzugeben, so dass nach einer Unterbrechung Ausführung von dem Zwischenzustand aus fortgesetzt werden kann.

**[0063]** **Fig. 5** zeigt ein Blockdiagramm, das eine Ausführungsform einer Logik **501** zeigt, um einem Prozessor zu ermöglichen, auf Betriebsmittel und/oder Information auf andere Weise zuzugreifen, wenn er in einem Emulationsmodus ist, als wenn er nicht in einem Emulationsmodus ist. In einigen Ausführungsformen kann die Logik aus **Fig. 5** in dem Prozessor und/oder dem Computersystem aus **Fig. 1** und/oder aus **Fig. 3** enthalten sein. Alternativ kann die Logik aus **Fig. 5** in einem ähnlichen oder anderen Prozessor oder Computersystem enthalten sein. Darüberhinaus können der Prozessor und/oder das Computersystem aus **Fig. 1** und/oder die Logik aus **Fig. 3** ähnliche oder andere Logik als die aus **Fig. 5** enthalten.

**[0064]** Eine erste Instanz **503-1** eines gegebenen Befehls (beispielsweise eines Befehls, der einen gegebenen Opcode aufweist) wird einer Dekodierlogik **505** bereitgestellt, wenn der Prozessor nicht in einem Emulationsmodus **518** ist. Eine zweite Instanz **503-2** des gleichen gegebenen Befehls (beispielsweise eines anderen Befehls, der den gleichen gegebenen Opcode aufweist) wird der Dekodierlogik bereitgestellt, wenn der Prozessor in dem Emulationsmodus **518** arbeitet. Die zweite Instanz **503-2** des gegebenen Befehls kann als Antwort darauf, dass ein Dekodierer den emulierten Befehl erhält, von einem Satz eines oder mehrerer Befehle **514** bereitgestellt werden, die verwendet werden, um einen emulierten Befehl zu emulieren. Der Satz von Befehlen kann in der Emulationslogik **515** enthalten sein, die auf dem Chip, außerhalb des Chips oder teilweise auf dem Chip und außerhalb des Chips sein kann. Die Emulationslogik **515** kann jede der optionalen Charakteristiken auf-

weisen, die hier an anderer Stelle für die Emulationslogik erwähnt werden.

**[0065]** Eine Nachdekodier-Befehlsprozessorlogik **507** kann den/die dekodierten Befehl(e) **506** erhalten, die der zweiten Instanz **503-2** entsprechen. Die Nachdekodier-Befehlsprozessorlogik enthält eine emulationsmodusbewusste Zugriffssteuerlogik **520**. Die emulationsmodusbewusste Zugriffssteuerlogik kann betrieben werden, Zugriff auf ein oder mehrere Betriebsmittel und/oder Information **550** auf eine Weise zu steuern, die über den Emulationsmodus informiert ist. In einigen Ausführungsformen kann, wenn der Prozessor nicht in dem Emulationsmodus arbeitet, die Nachdekodier-Befehlsprozessorlogik **507** die erste Instanz **503-1** des gegebenen Befehls mit im wesentlichen herkömmlichem Zugriff auf das/die Betriebsmittel und/oder Information **550** verarbeiten. Wie gezeigt, kann in einigen Ausführungsformen Zugriff auf Betriebsmittel und/oder Information **550** verhindert werden **551**, wenn die erste Instanz **503-1** des gegebenen Befehls verarbeitet wird, wenn kein Emulationsmodus vorliegt. Verhindern von Zugriff auf das/die Betriebsmittel und/oder Information, wenn kein Emulationsmodus vorliegt, kann aus irgendeinem von verschiedenen möglichen Gründen angemessen sein, wie etwa beispielsweise, um die Sicherheit von Information und/oder Betriebsmittel(n) zu schützen, weil der gegebene Befehle allgemein nicht auf diese(s) Betriebsmittel und/oder Information zuzugreifen braucht und man das/die Betriebsmittel und/oder Information lediglich bei Bedarf oder aus anderen Gründen bereitstellen will.

**[0066]** Hingegen kann in einigen Ausführungsformen, wenn die zweite Instanz **503-2** des gegebenen Befehls verarbeitet wird, wenn in dem Emulationsmodus **518** gearbeitet wird, die Nachdekodier-Befehlsprozessorlogik im wesentlichen unkonventionellen Zugriff auf das/die Betriebsmittel und/oder Information **550** (beispielsweise auf eine Weise, die anders ist, als wenn ein Nichtemulationsmodus vorliegt) verwenden. Beispielsweise kann, wie in der gezeigten Ausführungsform gezeigt, Zugriff auf das/die Betriebsmittel und/oder Information **550** erlaubt werden **552**, wenn die zweite Instanz **503-2** des gegebenen Befehls verarbeitet wird, wenn der Emulationsmodus **518** vorliegt. Als Beispiel kann der Emulationsmodus **518** der Logik **507** und/oder der Logik **520** ermöglichen, einen speziellen Hardwarezustand zu haben, der selektiven Zugriff auf die Information und/oder Betriebsmittel für diesen gegebenen Befehl ermöglicht, wenn Emulationsmodus vorliegt. Beispielsweise können ein oder mehrere Zugriffsberechtigungsbits bereitgestellt und konfiguriert werden, wenn der Emulationsmodus vorliegt, um einem Zustandsautomaten zu ermöglichen, auf die Information zuzugreifen.

**[0067]** Verschiedene unterschiedliche Typen von Information und/oder Betriebsmittel(n) **550** werden betrachtet. Beispiele eines geeigneten/geeigneter Betriebsmittel und/oder Information schließen (ein) sicherheitsbezogene(s) Betriebsmittel und/oder Information (beispielsweise Sicherheitslogik), (ein) verschlüsselungs- und/oder entschlüsselungsbezogene (s) Betriebsmittel und/oder Information (beispielsweise Verschlüsselungslogik und/oder Entschlüsselungslogik), (ein) Zufallsgeneratorbetriebsmittel und/oder -information (beispielsweise Zufallsgeneratorlogik), (ein) Betriebsmittel und/oder Information, die für Berechtigungs- oder Ringstufen reserviert sind, die einem Betriebssystem und/oder virtuellen Maschinenmonitor entsprechen, und ähnliches ein, ohne darauf beschränkt zu sein.

**[0068]** Ein weiteres Beispiel eines geeigneten/geeigneter Betriebsmittel(s) und/oder Information schließt (ein) Betriebsmittel und/oder Information in einem anderen physikalischen Prozessor oder logischen Prozessor (beispielsweise einen Kern, Hardwarethread, Threadkontext etc.) als dem physikalischen oder logischen Prozessor ein, der die Nachdekodier-Befehlsprozessorlogik **507** aufweist. Die unterschiedlichen physikalischen oder logischen Prozessoren können entweder in den gleichen oder unterschiedlichen Sockets sein. Als Beispiel kann, wenn ein Emulationsmodus vorliegt, eine emulationsmodusbewusste Steuerlogik **520** in der Lage sein, auf Information und/oder Betriebsmittel eines anderen Kerns in einem anderen Socket (beispielsweise Anfordern eines Status des Kerns) zuzugreifen, der nicht für die Nachdekodier-Befehlsprozessorlogik **507** zur Verfügung steht, wenn kein Emulationsmodus vorliegt.

**[0069]** Vorteilhafterweise kann die emulationsmodusbewusste Zugriffssteuerlogik **520** helfen, wenigstens einigen der Befehle **514** zu ermöglichen, selektiv auf (ein) bestimmte(s) Betriebsmittel und/oder Information zuzugreifen, wenn der Emulationsmodus vorliegt, die normalerweise nicht für die gleichen Befehle des Befehlssatzes zur Verfügung stünden, wenn kein Emulationsmodus vorliegt. Sicherheit kann trotzdem aufrechterhalten werden, da die Emulationslogik auf dem Chip und/oder in einem geschützten Abschnitt des Speichers sein kann.

**[0070]** In einigen Ausführungsformen können einige Ausführungslevel, beispielsweise Sicherheitsausführungsstufen, daran gehindert sein, solche Emulation zu verwenden, um auf diese(s) Betriebsmittel und/oder Information zuzugreifen. Beispielsweise braucht nicht sämtlichen Ausführungszuständen erlaubt zu werden, emulierte Opcodes zu verwenden. Spezielle Sicherheitsausführungsstufen können nicht zertifizierbar sicher sein, wenn solche Interrupts oder Ausführung auf niedriger Ebene erlaubt wird. Stattdessen können, wenn solche Ausführungsstufen oder Si-

cherheitsausführungsstufen ähnlichen Zugriff benötigen, ihn diese stattdessen durch Verwenden von Hardwareprimitiven implementieren, die für Emulationssoftware zur Verfügung stehen.

**[0071]** In einigen Ausführungsformen kann Befehlsemulation verwendet werden, um Bereitstellen unterschiedlicher Bedeutungen für einen gegebenen Opcode eines Befehls zu unterstützen. Makrobefehle, Maschinensprachbefehle und andere Befehle eines Befehlssatzes weisen oftmals einen Operationscode oder Opcode auf. Der Opcode stellt allgemein einen Teil des Befehls dar, der verwendet wird, um den konkreten Befehl und/oder die Operation anzugeben, die als Antwort auf den Befehl durchgeführt werden soll. Beispielsweise kann ein Opcode eines gepackten Multiplizierbefehls anders sein als ein Opcode eines gepackten Addierbefehls. Allgemein weist der Opcode mehrere Bits in einem oder mehreren Feldern auf, die logisch, wenn nicht physikalisch, zusammen angeordnet sind. Oftmals ist es wünschenswert, zu versuchen, die Opcodes relativ kurz oder so kurz wie möglich zu halten, während die gewünschte Anzahl von Befehlen/Operationen ermöglicht wird. Relativ lange Opcodes tendieren dazu, die Größe und/oder Komplexität des Dekodierers zu vergrößern, und tendieren auch allgemein dazu, die Befehle zu verlängern. Für eine feste Anzahl an Bits in einem Opcode kann allgemein lediglich eine feste Anzahl unterschiedlicher Befehle/Operationen identifiziert werden. Es gibt verschiedene Tricks, die im Stand der Technik bekannt sind, um zu versuchen, den Opcode am besten zu nutzen, beispielsweise durch Verwenden von Escape-Codes und ähnlichem. Nichtsdestoweniger ist die Anzahl von Befehlen, die mit einem Opcode eindeutig identifiziert werden können, allgemein beschränkter als wünschenswert ist. Allgemein können neue Befehle nicht kontinuierlich dem Opcode-Raum des Prozessors hinzugefügt werden, ohne an einem Punkt irgendwann keine Opcodes mehr zur Verfügung zu haben.

**[0072]** Auslastungen ändern sich mit der Zeit. Auf ähnliche Weise ändern sich gewünschte Befehle und gewünschte Befehlsfunktionalitäten mit der Zeit. Neue Befehlsfunktionalitäten werden gewöhnlich fortwährend zu Prozessoren hinzugefügt. Auf ähnliche Weise werden einige Befehle/Operationen mit der Zeit relativ weniger nützlich und/oder weniger häufig benutzt und/oder weniger wichtig. In einigen Fällen, wenn Befehle/Operationen ausreichend begrenzten Nutzen oder Wichtigkeit haben, können sie veraltet sein. Veraltungs ist ein Begriff, der im Stand der Technik gewöhnlich verwendet wird, um einen Status zu bezeichnen, der auf eine Komponente, eine Struktur, eine Charakteristik oder Vorgehen angewendet wird, um darauf hinzuweisen, dass sie/es allgemein vermieden werden sollte, oftmals weil sie/es im Begriff ist, verworfen oder ersetzt zu werden und/

oder in der Zukunft nicht zur Verfügung stehen oder unterstützt werden kann.

**[0073]** Gewöhnlich können solche Befehle/Operationen veralten, anstatt sofort entfernt zu werden, um zu helfen, vorübergehende Rückwärtskompatibilität zu liefern (beispielsweise existierendem oder überliefertem Code Weiterbetrieb zu ermöglichen). Dies kann Zeit einräumen, um den Code mit den Ersatzbefehlen/-operationen in Einklang zu bringen, und/oder Zeit einräumen, den existierenden oder überlieferten Code auszusondern. Oftmals braucht Aussen- oder von Befehlen/Operationen aus einem Befehlsatz viel Zeit, beispielsweise in der Größenordnung von Jahren, wenn nicht Jahrzehnten, um Zeit zu geben, alte Programme ausreichend zu entfernen. Herkömmlicherweise könnte der Wert des Opcodes des veralteten Befehls der veralteten Operation allgemein nicht wiedererlangt und für einen anderen Befehl/eine andere Operation wiederverwendet werden, bis eine so lange Zeitperiode verstrichen ist. Andererseits können, falls überlieferte Software zum Ablauf gebracht wurde, Befehle, die den Opcode-Wert aufweisen, den Prozessor veranlassen, die Ersatzoperation anstelle der beabsichtigten veralteten Operation durchzuführen, was ein fehlerhaftes Ergebnis zur Folge haben könnte.

**[0074]** In einigen Ausführungsformen kann Befehlsemulation verwendet werden, um Bereitstellen unterschiedlicher Bedeutungen für einen gegebenen Opcode eines Befehls zu unterstützen. In einigen Ausführungsformen kann der gegebene Opcode des Befehls mit unterschiedlichen Bedeutungen interpretiert werden. In einigen Ausführungsformen können mehrere Opcode-Definitionen für den gegebenen Opcode unterstützt werden. Beispielsweise kann der gegebene Opcode mit einer Bedeutung interpretiert werden, die ein Softwareprogramm, das den Befehl aufweist, beabsichtigt. Als Beispiel kann ein älteres oder überliefertes Softwareprogramm anzeigen, dass Befehle mit dem gegebenen Opcode eine ältere, überlieferte oder veraltete Bedeutung haben sollen, und kann ein neueres Softwareprogramm anzeigen, dass Befehle mit dem gegebenen Opcode eine neuere Bedeutung haben sollen. In einigen Ausführungsformen kann die ältere oder veraltete Bedeutung emuliert werden, während die neuere Bedeutung in Steuersignalen dekodiert und direkt auf der Pipeline des Prozessors ausgeführt werden kann. Vorteilhaftweise kann dies in einigen Ausführungsformen helfen, früheres Wiedererlangen und Wiederverwendung von Opcodes, die veraltet sind, zu ermöglichen, während trotzdem Rückwärtskompatibilität bereitgestellt wird, die älteren Programmen ermöglicht, immer noch mit einem veralteten Opcode abzulaufen, während dem veralteten Opcode ermöglicht wird, auch für neuere Programme mit einer anderen Bedeutung verwendet zu werden, um beim Verbessern von Leistung zu helfen.

**[0075]** **Fig. 6** zeigt ein Blockflußdiagramm einer Ausführungsform eines Verfahrens **660**, das durch einen und/oder in einem Prozessor durchgeführt wird. In einigen Ausführungsformen können die Operationen und/oder das Verfahren aus **Fig. 6** durch den und/oder in dem Prozessor aus **Fig. 1** und/oder der Logik aus **Fig. 3** oder **Fig. 7** durchgeführt werden. Die Komponenten, Strukturen und spezifischen optionalen Details, die hier für den Prozessor und die Logik beschrieben sind, gelten optional auch für die Operationen und/oder Verfahren aus **Fig. 6**. Alternativ können die Operationen und/oder Verfahren aus **Fig. 6** durch einen und/oder innerhalb eines ähnlichen oder ganz anderen Prozessors oder Logik durchgeführt werden. Darüberhinaus kann der Prozessor aus **Fig. 1** und/oder die Logik aus **Fig. 3** oder **Fig. 7** ähnliche oder andere Operationen und/oder Verfahren als die aus **Fig. 6** durchführen.

**[0076]** Das Verfahren schließt Empfangen eines ersten Befehls an Block **661** ein, der einen gegebenen Opcode aufweist. In einigen Ausführungsformen kann der erste Befehl an dem Dekodierer empfangen werden. Eine Bestimmung kann an Block **662** vorgenommen werden, ob der gegebene Opcode eine erste Bedeutung oder eine zweite Bedeutung aufweist. In einigen Ausführungsformen kann die erste Bedeutung eine erste Opcode-Definition und die zweite Bedeutung eine zweite, andere Opcode-Definition sein. Wie weiter unten erläutert wird, kann dies in einigen Ausführungsformen einschließen, dass der Dekodierer eine Anzeige, beispielsweise in einem Flag, Statusregister oder anderem Speicherplatz auf dem Chip, lesen oder prüfen kann, ob der gegebene Opcode die erste Bedeutung oder die zweite Bedeutung aufweist. Wie weiter unten erläutert wird, kann in einigen Ausführungsformen Software (beispielsweise ein Programmiermodul eines Betriebssystemmoduls) die Anzeige in dem Flag, Statusregister oder anderem Speicherplatz auf dem Chip speichern, wenn Software geladen wird, um von dem Prozessor zum Ablauf gebracht zu werden. Als Beispiel kann die Software Metadaten (beispielsweise ein Objektmodulformat) enthalten, um anzugeben, ob die Software den gegebenen Opcode erwartet oder spezifiziert, die erste Bedeutung oder zweite Bedeutung aufzuweisen.

**[0077]** Unter erneuter Bezugnahme auf **Fig. 6** kann, falls die Bestimmung an Block **662** ergibt, dass der gegebene Opcode die erste Bedeutung aufweist, das Verfahren zu Block **663** forschreiten. An Block **663** kann der erste Befehl in einem oder mehrere Mikrobefehle, Mikrooperationen oder andere Befehle oder Steuersignale niedrigerer Ebene dekodiert werden. In einigen Ausführungsformen kann der Dekodierer diese(n) Befehl(e) oder diese(s) Steuersignal(e) an die Nachdekodier-Befehlsprozessorlogik (beispielsweise Ausführungseinheiten etc.) ausgeben. Die Nachdekodier-Befehlsprozessorlogik kann die

se Befehle verarbeiten, typischerweise viel schneller, als wenn stattdessen Emulation verwendet werden würde. In einigen Ausführungsformen kann die erste Bedeutung für nicht-veraltete Opcode-Bedeutungen, relativ neuere Opcode-Bedeutungen, relativ häufiger verwendete Opcode-Bedeutungen, Opcode-Bedeutungen, die Leistung stärker beeinflussen, oder ähnliche verwendet werden.

**[0078]** Umgekehrt kann, falls die Bestimmung an Block **662** ergibt, dass der gegebene Opcode die zweite Bedeutung aufweist, das Verfahren zu Block **664** forschreiten. Bei Block **664** kann Emulation des ersten Befehls herbeigeführt werden. Beispielsweise kann der Dekodierer ein Emulationsfangsignal liefern oder auf andere Weise einen Emulationsmodus an die Emulationslogik signalisieren. Anschließend kann ein Satz von einem oder mehreren Befehlen der Emulationslogik, die zum Emulieren des ersten Befehls verwendet werden sollen, wobei der Opcode die zweite Bedeutung aufweist, dem Dekodierer geliefert und in dem Emulationsmodus verarbeitet werden. Dies kann im Wesentlichen wie hier an anderer Stelle beschrieben vorgenommen werden. In einigen Ausführungsformen kann die zweite Bedeutung für veraltete Opcode-Bedeutungen, Opcode-Bedeutungen, die im Begriff sind, zu veralten oder vor der Aussonderung stehen, relativ ältere Opcode-Bedeutungen, relativ weniger häufig verwendete Opcode-Bedeutungen, Opcode-Bedeutungen, die weniger stark Leistung beeinflussen, oder ähnliche verwendet werden.

**[0079]** **Fig. 7** zeigt ein Blockdiagramm, das eine Ausführungsform der Logik **701** zeigt, um einem gegebenen Opcode zu ermöglichen, unterschiedliche Bedeutungen aufzuweisen. In einigen Ausführungsformen kann die Logik aus **Fig. 7** in dem Prozessor und/oder dem Computersystem aus **Fig. 1** und/oder der Logik aus **Fig. 3** enthalten sein. Alternativ kann die Logik aus **Fig. 7** in einem ähnlichen oder anderen Prozessor oder Computersystem enthalten sein. Darüberhinaus kann der Prozessor und/oder das Computersystem aus **Fig. 1** und/oder die Logik aus **Fig. 3** ähnliche oder andere Logik als die aus **Fig. 7** enthalten.

**[0080]** Ein Speicher **710** enthält ein erstes Softwaremodul **711-1**, ein zweites Softwaremodul **711-2** und ein Betriebssystemmodul **797**, das ein Programmladermodul **770** aufweist. In einigen Ausführungsformen enthält das erste Softwaremodul eine Anzeige **772** zum Verwenden einer ersten Bedeutung für einen gegebenen Opcode, und enthält das zweite Softwaremodul eine Anzeige **773** zum Verwenden einer zweiten, anderen Bedeutung für den gegebenen Opcode. Als Beispiel können die ersten und zweiten Softwaremodule jeweils ein Objektmodulformat, andere Metadaten oder eine oder mehrere Datenstrukturen enthalten, die diese Anzeigen **772**, **773** enthal-

ten. Das Programmladermodul kann betrieben werden, um das erste Softwaremodul und das zweite Softwaremodul zur Ausführung auf einem Prozessor zu laden. Wie gezeigt, kann das Programmladermodul in einigen Ausführungsformen ein Modul **771** enthalten, um eine Bedeutung des gegebenen Opcodes, der von dem konkreten Softwaremodul angezeigt wird, auf den Prozessor als Prozessorzustand zu laden. In einigen Ausführungsformen kann das Modul **771** betrieben werden, um die Anzeige **772**, wenn das erste Softwaremodul geladen wird, oder die Anzeige **773**, wenn das zweite Softwaremodul geladen wird, auf einen Speicherplatz **774** auf dem Chip als eine Anzeige **775** zu laden, ob die erste oder zweite Bedeutung für den gegebenen Opcode verwendet werden soll. Der Speicherplatz auf dem Chip ist mit einem Dekodierer **705** gekoppelt oder auf andere Weise für diesen zugänglich.

**[0081]** In einigen Ausführungsformen kann, beispielsweise im Falle eines alten Softwaremoduls, das Softwaremodul keine explizite Anzeige zum Verwenden einer gegebenen Bedeutung für den gegebenen Opcode aufweisen. Beispielsweise kann die Software vor der Existenz der neueren Bedeutung geschrieben worden sein. In einigen Ausführungsformen kann das Modul **771** und/oder der Programmlader **770** betrieben werden, um festzustellen, ob das Softwaremodul die erste oder zweite Bedeutung des gegebenen Opcodes verwenden muß. Beispielsweise kann dies aus einer Merkmalsliste, die in dem Programm eingebettet ist, dem Format des Programms, dem Alter des Programms oder dem Jahr, in dem das Programm erstellt wurde, oder anderer solcher Information in den Metadaten und/oder in dem Softwaremodul festgestellt werden. Beispielsweise kann, falls das zweite Softwaremodul **711-2** alte Software ist, die vor Einführung/Definition der ersten Bedeutung des gegebenen Opcodes erstellt wurde, das Programmladermodul und/oder das Betriebssystemmodul betrieben werden, um festzustellen, dass das zweite Softwaremodul die zweite Bedeutung und nicht die erste Bedeutung des gegebenen Opcodes verwenden muss. Das Modul **771** kann betrieben werden, um die Anzeige **775** in dem Speicherbereich auszuschalten oder auszuwechseln (swap), wenn Software ausgeschaltet oder ausgewechselt wird.

**[0082]** Um dies weiter beispielhaft zu zeigen, wird eine erste Instanz **703-1** eines Befehls betrachtet, wobei der gegebene Opcode einem Dekodierer **705** von dem ersten Softwaremodul **711-1** bereitgestellt wird. Das erste Softwaremodul enthält die Anzeige **772** zum Verwenden der ersten Bedeutung für den gegebenen Opcode, den das Modul **771** in dem Speicherplatz **774** vorhalten kann. Der Dekodierer enthält eine Prüflogik **776**, die mit dem Speicherplatz **774** gekoppelt ist, um die Anzeige **775** darauf zu prüfen, ob die erste oder zweite Bedeutung für den gegebenen Opcode verwendet werden soll. Die Prüflogik

gik kann auf den Speicherplatz zugreifen oder aus diesem lesen und bestimmen, dass die erste Bedeutung für den gegebenen Opcode verwendet werden soll, wenn die erste Instanz des Befehls von dem ersten Softwaremodul verarbeitet wird. In einigen Ausführungsformen kann der Speicherplatz **774** mehrere unterschiedliche Speicherplätze enthalten, um mehrere Anzeigen zu speichern, die jeweils einem anderen Opcode entsprechen. Als Antwort kann die Dekodierlogik **777** des Dekodierers den Befehl unter der Annahme der ersten Bedeutung des gegebenen Opcodes dekodieren. Ein oder mehrere dekodierte Befehle **706** oder ein oder mehrere andere Steuersignale können von dem Dekodierer an die Nachdekodier-Befehlsprozessorlogik **707** geliefert werden, die diese verarbeiten kann.

**[0083]** Eine zweite Instanz **703-2** eines Befehls mit dem gleichen gegebenen Opcode kann dem Dekodierer **705** von dem zweiten Softwaremodul **711-2** geliefert werden. Das zweite Softwaremodul enthält die Anzeige **773** zum Verwenden der zweiten Bedeutung für den gegebenen Opcode, den das Modul **771** an dem Speicherplatz **774** erhalten kann. Die Prüflogik **776** kann die Anzeige **775** prüfen und bestimmen, dass die zweite Bedeutung für den gegebenen Opcode verwendet werden soll, wenn die zweite Instanz des Befehls von dem zweiten Softwaremodul verarbeitet wird. Als Antwort kann die Emulationsauslöselogik **778** Emulation der zweiten Instanz des Befehls **703-2** auslösen. Beispielsweise kann die Emulationsauslöselogik ein Emulationsfangsignal durchführen oder auf andere Weise einen Emulationsmodus **718** signalisieren. Ein Satz von einem oder mehreren Befehlen **714**, die verwendet werden, um die zweite Instanz des Befehls, der den gegebenen Opcode mit der zweiten Bedeutung aufweist, zu emulieren, kann an den Dekodierer von einer Emulationslogik **715** geliefert werden. Die Emulationslogik kann auf dem Chip, außerhalb des Chips oder teilweise auf dem Chip und teilweise außerhalb des Chips vorliegen. Die Emulationslogik **715** kann jede der Charakteristiken aufweisen, die hier an anderer Stelle für Emulationslogik beschrieben ist.

**[0084]** In einigen Ausführungsformen kann/können der/die Befehl(e) **714** aus dem gleichen Befehlssatz wie der Befehl, der den gegebenen Opcode aufweist, stammen. In einigen Ausführungsformen kann der Dekodierer jeden dieser Befehle dekodieren und sie als dekodierte Befehle **706** oder andere Steuersignale an die Nachdekodier-Befehlsprozessorlogik liefern. In einigen Ausführungsformen kann die Nachdekodier-Befehlsprozessorlogik eine emulationsmodusbewusste Befehlsprozessorlogik **720** enthalten, die ähnlich oder identisch hier an anderer Stelle beschrieben sein kann (beispielsweise diejenigen aus einer der **Fig. 1** oder **Fig. 3 bis Fig. 5**). Wie gezeigt, kann die emulationsmodusbewusste Befehlsprozessorlogik mit dem Emulationsmodus **718** gekoppelt

sein oder diesen auf andere Weise kennen. Darüber hinaus kann die emulationsmodusbewusste Befehlsprozessorlogik mit Speicherplätzen **721** der Emulationslogik gekoppelt sein und Daten aus diesen lesen und in diese schreiben.

**[0085]** In einigen Ausführungsformen kann die Logik **796** enthalten sein, um ein Prozessormerkmalsidentifizierungsregister **795** anhand der Anzeige **775** an dem Speicherplatz **774** zu aktualisieren. Ein Beispiel eines geeigneten Prozessormerkmalsidentifizierungsregister ist ein für CPU IDentification (CPUID) verwendetes. Die Logik **796** kann mit dem Speicherplatz **774** und mit dem Prozessormerkmalsidentifizierungsregister **795** gekoppelt sein. Das Prozessormerkmalsidentifizierungsregister kann durch einen Prozessormerkmalsidentifizierungsbefehl (beispielsweise einen CPUID-Befehl) eines Befehlssatzes des Prozessors lesbar sein. Software kann die Anzeige der Bedeutung des Opcodes aus dem Prozessormerkmalsidentifizierungsregister durch Ausführen des Prozessoridentifizierungsbefehls lesen.